# Univac<sup>®</sup> LARC PROGRAMMING

# THE COMPUTING UNIT

MAY 1961

**Remington Rand Univac®** Division of sperry rand corporation

UNIVAC ENGINEERING CENTER . PHILADELPHIA

# CONTENTS

Heading

Title

Page

# SECTION 1. INTRODUCTION

# SECTION 2. LOGICAL OPERATION OF THE

# COMPUTING UNIT

| 2-1.<br>2-2. | General                                   | 2-1  |

|--------------|-------------------------------------------|------|

| 2-2.         | The Control Unit.                         | 2-2  |

| -            | Instruction Registers                     | 2-3  |

| 2-4.         | Control Counters                          | 2-4  |

| 2-5.         | The B Adder                               | 2-5  |

| 2-6.         | Memory Address Decoders                   | 2-5  |

| 2-7.         | Operation Decoder                         | 2-6  |

| 2-8.         | The Arithmetic Unit                       | 2-6  |

| 2-9.         | Fast Registers                            | 2-6  |

| 2-10.        | Addressable Flip-Flops                    | 2-7  |

| 2-11.        | The High-Speed Bus                        | 2-7  |

| 2-12.        | Execution of an Instruction               | 2-8  |

| 2-13.        | Instruction Overlapping                   | 2-9  |

| 2-14.        | Control of Errors, Contingencies, and the |      |

|              | Tracing Mode                              | 2-11 |

# SECTION 3. INSTRUCTION DETAILS

| 3-1.  | Instruction Format                                  | 3-1  |

|-------|-----------------------------------------------------|------|

| 3-2.  | Index Register Format                               | 3-2  |

| 3-3.  | Operands                                            | 3-3  |

| 3-4.  | Floating-Point Arithmetic                           | 3-4  |

| 3-5.  | Program Conventions                                 | 3-6  |

| 3-6.  | Data-Transfer Instructions                          | 3-7  |

| 3-7.  | Fixed-Point Arithmetic Instructions                 | 3-12 |

| 3-8.  | Unconditional-Transfer-of-Control                   | •    |

|       | Instructions.                                       | 3-21 |

| 3-9.  | Conditional-Transfer-of-Control                     | 0 -1 |

|       | Instructions.                                       | 3-23 |

| 3-10. | Extract Instructions.                               | 3-31 |

| 3-11. | Shift Instructions.                                 | 3-36 |

| 3-12. | Index Desigter Medification Tests at the            |      |

| J-12+ | Index-Register-Modification Instructions. $\bullet$ | 3-40 |

| Heading      | Title                                          | Page        |

|--------------|------------------------------------------------|-------------|

| 3-13.        | Floating-Point Arithmetic Instructions         | 3-44        |

| 3-14.        | Conversion Instructions                        | 3-60        |

| 3-15.        | Visual-Display Instructions                    | 3-64        |

| 3-16.        | Flip-Flop Instructions.                        | 3-66        |

| 3-17.        | Miscellaneous Instructions                     | 3-68        |

| SI           | ECTION 4. OPERATIONS OF INPUT-OUTPUT EQUIPMENT |             |

| 4-1.         | General                                        | 4-1         |

| 4-2.         | Data Codes                                     | 4-3         |

| 4-3.         | Magnetic Drums                                 | 4-3         |

| 4-4.         | Magnetic Tapes                                 | 4-7         |

| 4-5.         | Line Printer                                   | 4-9         |

| 4-6.         | Electronic Page Recorder                       | 4-9         |

|              | SECTION 5. OPERATING PROCEDURES                |             |

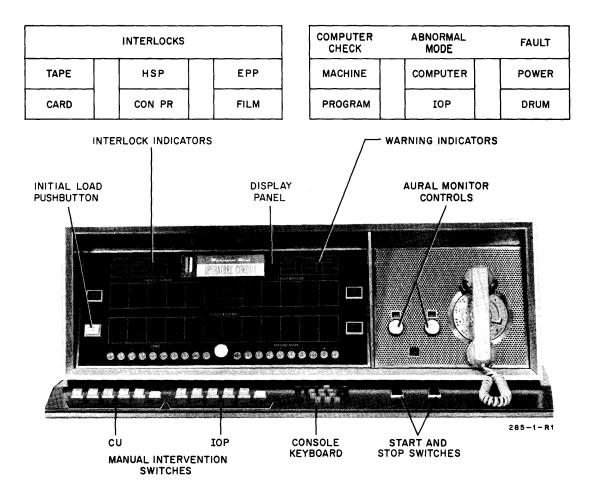

| 5-1.         | Operator's Stations                            | 5-1         |

| 5-2.         | Operator's Console                             | 5-1         |

| 5-3.         | Display Panel                                  | 5-2         |

| 5-4.         | Controls                                       | 5-3         |

| 5-5.         | Console Keyboard                               | 5-4         |

| 5-6.         | Console Printer                                | 5-5         |

| 5-7.         | Paper Tape Handling                            | 5-5         |

| 5-8.         | Tape Preparation                               | 5-5         |

| 5-9.         | Tape Reading                                   | 5-7         |

| 5-10.        | Program Load Procedures                        | 5-11        |

| 5-11.        | Load Procedure 1                               | 5-11        |

| 5-12.        | Load Procedure 2                               | 5-11        |

| 5-13.        | Load Procedure 3                               | 5-11        |

|              | SECTION 6. INDIRECT ADDRESSING                 |             |

|              | SECTION 7. CONTINGENCIES, ERRORS, AND          |             |

|              | TRACING MODES                                  |             |

| 7-1.<br>7-2. | Introduction                                   | 7-1<br>7-1  |

| 7-3.         | Contingency Flip-Flops                         | 7-4         |

| 7-4.         | Errors.                                        | 7-6         |

| 7-5.<br>7-6. | Error Flip-Flops                               | 7-9<br>7-13 |

|              |                                                | / 19        |

APPENDIX A. NUMERICAL LIST OF INSTRUCTIONS

APPENDIX B. ADDRESSABLE FLIP-FLOPS IN THE

# COMPUTING UNIT

APPENDIX C. REMINGTON RAND UNIVAC

# PROCESSOR PROGRAM

| C-1. | Magnetic Drum Summary Orders            | C-6  |

|------|-----------------------------------------|------|

| C-2. | Magnetic Tape Summary Orders            | C-8  |

| C-3. | Line Printer Summary Orders             | C-10 |

| C-4. | Electronic Page Recorder Summary Orders | C-12 |

| C-5. | Miscellaneous Summary Orders            | C-15 |

# **ILLUSTRATIONS**

| Figure | Title                                       | Page |

|--------|---------------------------------------------|------|

| 2-1.   | Computing Unit Block Diagram                | 2-3  |

| 2-2.   | Allocation of Time Slots on the High-Speed  |      |

|        | Bus                                         | 2-7  |

| 2-3.   | Instruction Overlapping                     | 2-10 |

| 2-4.   | Sequencing of an Unconditional-Transfer-of- |      |

|        | Control Instruction                         | 2-11 |

| 5-1.   | Operator's Console                          | 5–2  |

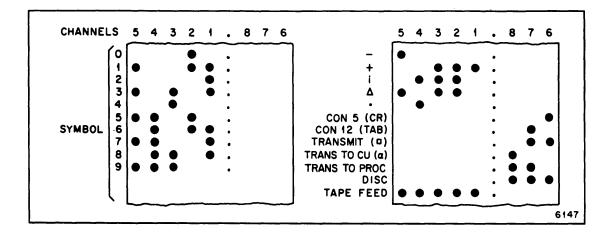

| 5-2.   | Tape Symbols                                | 5-7  |

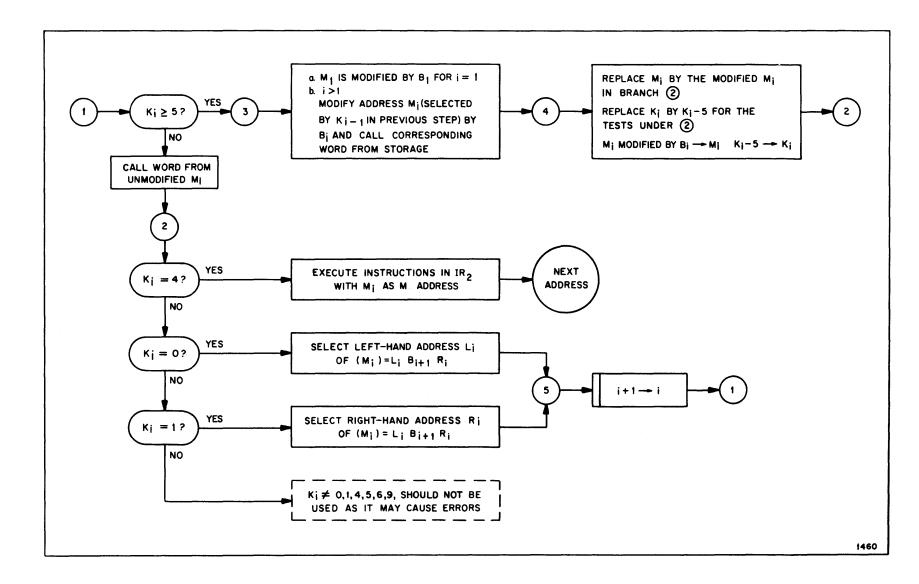

| 6-1.   | Address Selection in Indirect Addressing    | 6-4  |

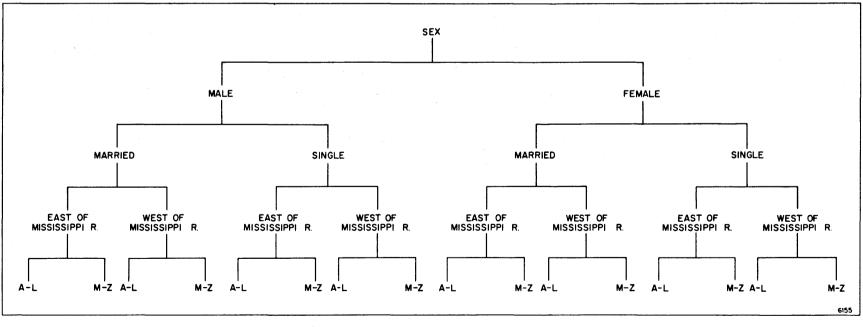

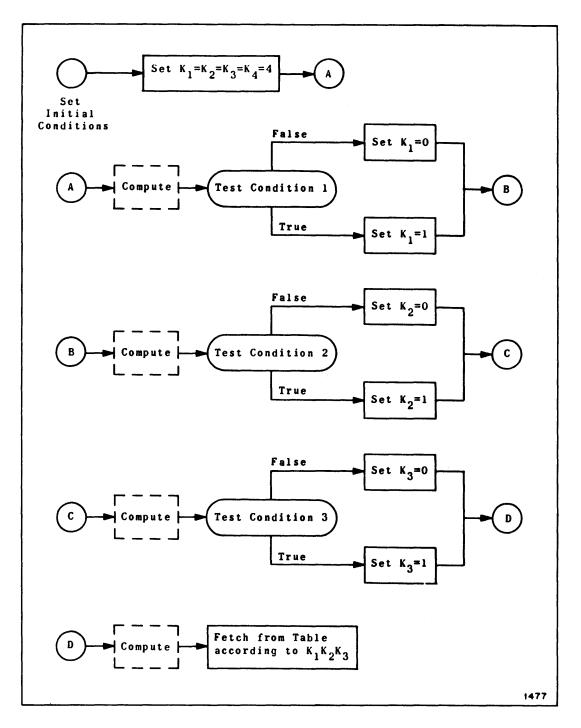

| 6-2.   | Example of Classification Tree              | 6-9  |

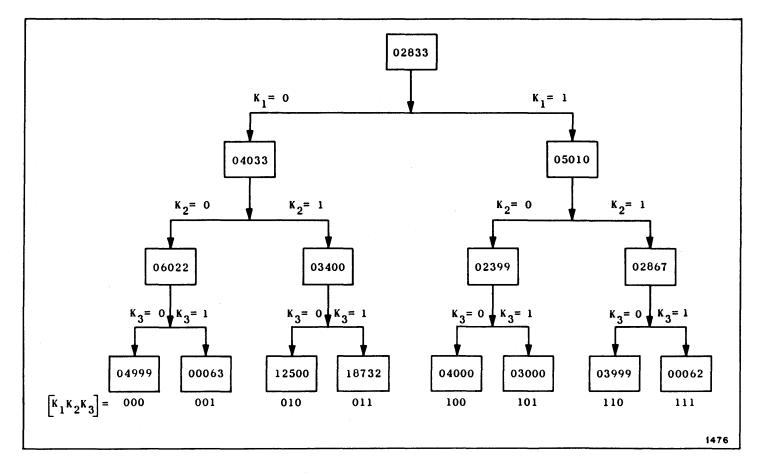

| 6-3.   | Indirect-Address Tree                       | 6-11 |

| 6-4.   | Determining Indirect Addressing Sequence    | 6-12 |

|        |                                             |      |

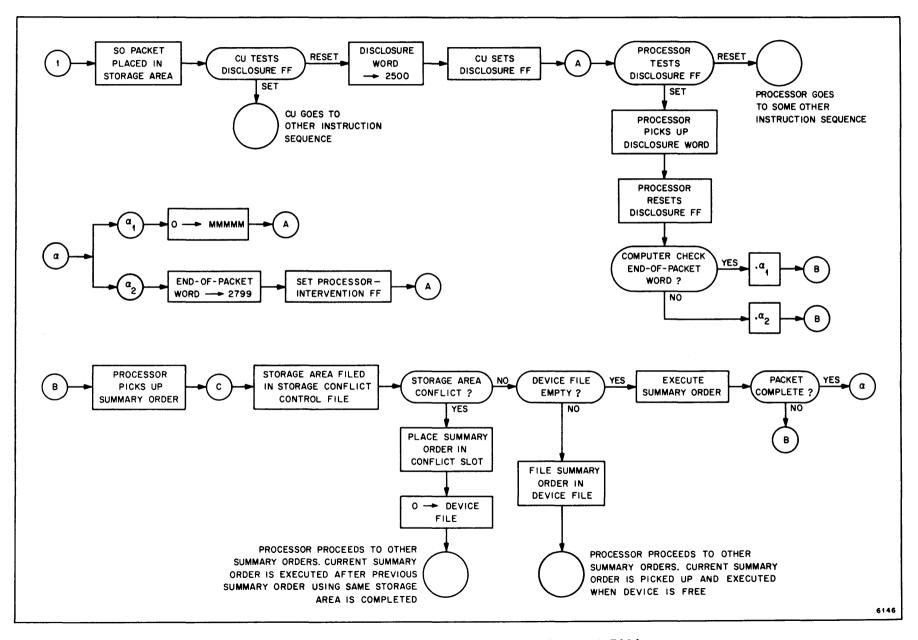

| C-1.   | Summary Order Execution and Filing          | C-5  |

TABLES

| Table        | Title                                               | Page |

|--------------|-----------------------------------------------------|------|

| 4-1.         | Larc Computer Codes                                 | 4-4  |

| 5-1.         | Console Printer Characters and Actions              | 5-6  |

| 6-1.<br>6-2. | The Table                                           | 6-10 |

|              | Tree                                                | 6-10 |

| 7-1.         | Contents of 02600 After Transfer to 02601<br>Occurs | 7-7  |

| C-1.         | Alphanumeric Code for the Console Printer .         | C-17 |

# SECTION 1 INTRODUCTION

The Univac<sup>®</sup> Larc\* Computing System basically comprises two units, the Computing Unit,\*\* and the processor. The Computing Unit is the primary computer; the processor (a secondary computer) handles the input-output operations. The two units are programmed independently, requiring only a minimum of intercommunication.

This programming manual is designed to provide the experienced programmer with the information necessary to write programs for the Larc Computing Unit. The publication <u>Univac Larc Programming</u>, The Processor provides similar information for programming the processor. Both manuals assume a familiarity with the essential features of the system. General information is available in the publication <u>Univac Larc System</u>, <u>General</u> Description.

The manual begins by introducing the programmer to the function of the Computing Unit in the system (section 2). This preliminary matter explains how instructions are sequenced, in general how errors and contingencies affect a program, and how the various parts of an instruction word are employed.

The main body of the manual (section 3) presents the Computing Unit instruction repertory. The individual instructions are described by class; information that applies in general to instructions in a class is given at the beginning of each class. A condensed list of all the instructions is found in appendix A.

<sup>\*</sup> Trademark of the Sperry Rand Corporation.

<sup>\*\*</sup> A Larc system may contain one or two Computing Units. This manual is written for the Larc System, serials 1 and 2, which contains one Computing Unit.

Section 4, on input-output operations, describes the numeric and alphanumeric codes and the input-output equipment including suggestions for the use of each of the devices. The method of communication between processor and Computing Unit is described in detail.

Operating procedures are discussed in section 5. The programmer must be familiar with this information in order to instruct the operator during debugging and final runs. Subjects such as program loading, manual intervention, visual display, and paper tape handling are covered in this section.

Section 6 consists of a complete discussion of indirect addressing. Included are the reasons for using indirect addressing, a description of the method of coding it, and coded examples of its use.

Details of tracing modes, errors, and contingencies are available in section 7. In this section, the addressable flip-flops are discussed at length, with information on the way in which they are set, tested, and reset. (A complete list of addressable flip-flops is found in appendix B.) Suggestions are made as to procedures which may be followed in the routines handling these operations.

The procedures to follow in utilizing the processor program written by Remington Rand are described in appendix C. This appendix includes an explanation of the summary orders or pseudo-code converted by the processor program into processor instructions.

# **SECTION 2**

# LOGICAL OPERATION OF THE COMPUTING UNIT

# 2-1. GENERAL

The Larc computer is an extremely high-speed computing device. Its high speed is obtained in part by using overlapping instructions, that is, the computer does not wait until an instruction has been executed before extracting the next from storage. Consequently, instructions follow each other rather closely through the stages of the control unit. In fact, as many as four instructions may be in the control unit at any one time.

This overlapping of instructions of course increases the complexity of the computer and imposes certain sequencing restrictions on the programmer. In some cases by careless use of instructions a programmer may increase the running time of his program. In rare instances errors can be caused by failing to observe the restrictions. Section 3 of this manual points out the more obvious restrictions on every individual instruction.

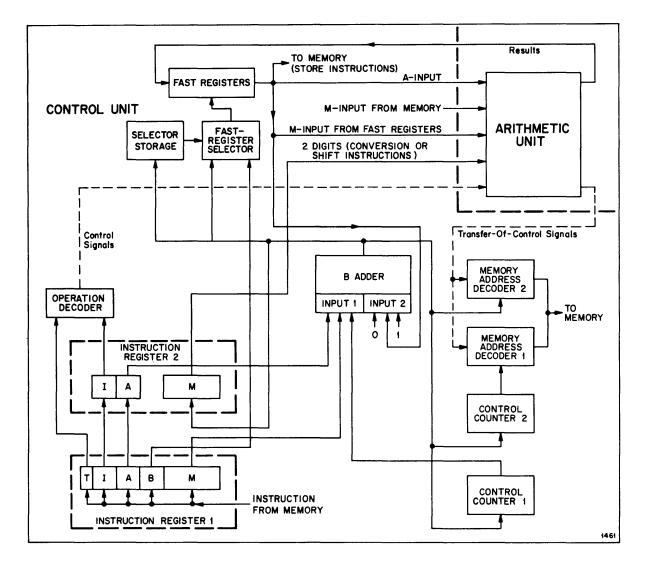

This section presents a simplified description of the Computing Unit control operations. (See figure 2-1 for a block diagram of the major units in the Computing Unit.) Because the main function of the control unit is the sequencing and execution of instructions, each component of this unit is explained and its function is described. A brief outline of the sequencing of instructions is given and a typical instruction is followed through the various stages of modification, decoding, and execution. The section ends with a brief introduction to the error and contingency routines and the tracing mode.

With this background information the programmer will be able to understand more clearly the necessity of precautions in the sequencing of instructions and in many instances will be able to work out for himself the effect of certain sequences on his program.

Before the programmer can fully understand the remainder of this section, he must be aware of the structure of the Larc Computing Unit instruction word. Hence, a brief description follows. (Further information on this topic will be found in section 3.) A Larc word consists of 12 characters. A generalized instruction word is shown as follows:

# T II AA BB MMMMM

The T digit, which need not be numeric, is known as the tracing digit. Certain values of this character lead to abnormal operation of the control unit. In general, the tracing digit will usually be a period, which will cause normal operation. The reader may assume in the discussions that follow that the tracing digit is a period unless otherwise stated.

The two I, or instruction, digits determine the operation that is to be carried out. The instruction (operation) code is discussed fully in section 3. In the present section any particular instruction code used will be explained as it appears.

The two A digits specify the address of a fast, or A, register. Fast registers are fast-access, 12-digit storage registers. Besides serving as fast-access storage, they also have some special properties which are explained in section 3. In this section the reader may assume that in any operation one of the operands will be the contents of the fast register specified by the A digits of the instruction.

The M digits of an instruction usually specify a main storage address from which the second operand of many instructions is extracted. The M digits may also specify the number of shifts in a shift instruction or the address to which control is transferred in a transfer-of-control instruction.

The B digits also specify the address of a fast register. In this case the contents of the register are used to modify the M address of the instruction. The five least-significant digits of the B fast register are known as the modifiers and are added to the M digits of the instruction to produce the modified address. Any carry produced outside the five least-significant-digit positions is ignored. Hence, an address can be increased or decreased by modification. For example, if the modifier 99999 is added to the address 06500, the modified address will be 06499. Note that modification does not alter the instruction in its storage location; the modification takes place only in the control unit. Note also that the fast registers used in modification are the same fast registers used to hold operands.

The general pattern of an arithmetic operation is that an operand from a fast register (A) and an operand from a main storage location (M) enter the control unit and the result is sent back to the fast register.

This brief explanation of instructions is sufficient to enable the reader to follow the arguments presented in the rest of this section.

# 2-2. THE CONTROL UNIT

The control unit may be generally described as the heart of the computer. (See figure 2-1.) Its functions are to fetch instructions from memory in correct sequence, to decode them, to bring operands from core storage and fast registers, to perform a variety of arithmetical and logical operations on the operands, and to return the results to storage. Figure 2-1 is, of course, a highly simplified diagram and shows only a few of the many interconnections of the control unit. More complete diagrams are included in the relevant logic manuals.

The individual major components making up the control unit are described in paragraphs 2-3 through 2-7.

Figure 2-1. Computing Unit Block Diagram

# 2-3. INSTRUCTION REGISTERS

There are two instruction registers in the Larc system control unit. They are special storage registers which hold instructions while they are being decoded. All instructions entering the control unit pass through these two registers.

Instruction register 1 (IR1) is the preliminary storage register and accepts instructions directly from memory. While an instruction is waiting

in IR1, its M address is modified by the contents of the specified B register.

Instruction register 2 (IR2) is the final storage register for instructions. This register receives the I and A digits from the first instruction register and also stores the modified M address. After modification takes place the B digits are no longer required and are not stored in IR2. The instruction is held in IR2 until the final decoding is completed and the necessary information for execution of the instruction has been brought into the control unit.

#### 2-4. CONTROL COUNTERS

A control counter is used to control the extraction of instructions from storage and to ensure that they are extracted in correct sequence. Because of the overlapping operations in the Larc Computing Unit two control counters, numbers 1 and 2, are required. One is used in the normal sequencing of instructions; the other is used when a transfer-of-control instruction is being decoded.

Control counter 1 (C1) contains the five-digit address of the instruction in IR1. In a normal sequence of instructions, that is, a sequence containing no transfers of control, the address in C1 is increased by 1 after each instruction has been executed causing the control counter to fetch the next instruction and store it in IR1.

When a transfer-of-control instruction is decoded, the modified M address is sent to control counter 2 (C2). If transfer takes place, the contents of Cl and C2 are interchanged so that Cl contains the first address of the new sequence of instructions, and C2 contains the address of the next instruction following the transfer-of-control instruction. If the transfer of control does not take place (C2) and (C1) are not exchanged. In either case, the contents of C2 remain unaltered until the next transferof-control instruction is decoded. Thus, at any stage in a program C2 contains the address of the instruction to which control was not transferred during the execution of the previous transfer-of-control instruction. If in instructions 80 and 81, B-modifier increment (or decrement) and transfer, no transfer of control takes place, (C2) is advanced to M + 1 before the control unit proceeds to the next instruction.

Example:

Storage location 25 contains a test-for-zero instruction.

$(00025) = .72 \ 01 \ 00 \ 00010$

The instruction tests the contents of fast register Ol. If the contents equal zero, control is transferred to storage location 10; if the contents do not equal zero the control unit continues with the next instruction in sequence, address 00026.

Initially, therefore,  $00026 \longrightarrow C1$  and  $00010 \longrightarrow C2$ .

If (01) = 0, then (C1) and (C2) are interchanged; that is, after the transfer of control:

$$(C1) = 00010$$

(C2) = 00026

If (01)  $\neq$  0, then (C1) and (C2) are unchanged; that is, after the completion of the instruction:

(C1) = 00026(C2) = 00010

In the first case, the next instruction to be executed will be taken from storage location 10; in the second case it will be taken from storage location 26.

This explanation of the operation of the control counters is simplified intentionally and is inexact in one or two particulars. For the programmer's use it is entirely sufficient, however.

#### 2-5. THE B ADDER

The B adder is a five-digit parallel adder whose primary function is the B-modification of M addresses. The adder also performs many other operations during the fetching, decoding, and execution of an instruction. Taking the execution of a simple instruction as an example, the first operation performed by the B adder is the addition of the number 00001 to the five-digit address in Cl. This produces the address of the next instruction to be brought into IR1.

The B adder is also used to interchange the contents of Cl and C2 after a transfer-of-control instruction, and for various incrementing and decrementing operations.

#### 2-6. MEMORY ADDRESS DECODERS

There are two memory address decoders in a Larc control unit. They are used to decode storage location addresses before fetching words from storage. The memory address decoders in fact partially decode the M address, selecting the cabinet, the storage unit within the cabinet, and partially selecting the storage location. The decoded information is sent over the address lines to the selected storage unit where the final decoding of the storage location takes place.

Memory address decoder 2 (MAD2) receives from the B adder the addresses it is to decode. These may be addresses of instructions or of operands. MAD2 also receives control signals which direct it to decode the next instruction address in sequence when a transfer of control is not required. Memory address decoder 1 (MAD1) receives the addresses it is to decode from control counter 2. These addresses are only decoded and sent to the memory when control signals are received indicating that a conditional transfer of control is to occur.

#### 2-7. OPERATION DECODER

The operation decoder decodes the operation code bits of an instruction in IR2. The decoding process generates control signals which govern the rest of the circuits during the execution of the instruction.

The decoder is also used to decode the tracing-mode digit from IR1. Depending on the character, control signals are generated to signal tracing mode, indirect-addressing mode, or normal operation.

# 2-8. THE ARITHMETIC UNIT

The arithmetic unit (AU) carries out all the arithmetic and logic operations in the Computing Unit. Before the AU can execute an instruction it needs operands and information about the operation to be performed. Control information enters the AU before the operands in order to give the unit sufficient time to prepare its circuits. The information derived from the decoding of the operation digits of the instruction, arrives in the form of control signals from the operation decoder.

There are two input channels to the AU for operands. These channels are known as the M-input and the A-input. In general, operands for the first input come from the memory location specified by the M digits of the instruction, whether these refer to a storage location or to a fast register. Operands for the second input come from the fast register specified in the A-digit positions of the instruction word. The two operands arrive at the AU simultaneously.

In shift and conversion instructions no operand is supplied to the Minput channel. Only the two least-significant M digits, after modification, are used and they specify the number of shifts to be performed or the conversion scale factor. They enter the AU by a special input line from IR2.

The output from the AU may be results which are sent to fast registers or storage locations, or may be control signals which govern transfer-ofcontrol operations. Error and contingency signals are also generated by the AU.

The AU operates independently after it has been supplied with operands and control signals.

# 2-9. FAST REGISTERS

The fast registers in the Larc Computing Unit, known as A registers or B registers according to whether they are used as arithmetic registers or index registers, do not have their addresses decoded by the memory address decoders, but by a special unit known as the fast-register selector. This unit accepts pairs of digits from the instruction registers or from the B adder and selects the fast register specified. The selector prepares the fast register to accept information or to transmit it when the appropriate control signal is received. In some cases fast-register-result addresses are temporarily stored in a two-digit storage before being sent to the fast-register selector. The two-digit storage is known as the selector storage unit.

# 2-10. ADDRESSABLE FLIP-FLOPS

Flips-flops are one-bit storage devices which, at any time, are in either an on (set) condition or an off (reset) condition. In the Larc computing system there are many of these storage devices (not shown in figure 2-1) which are used for a variety of control purposes.

Appendix B to this manual comprises a list of addressable flip-flops in the computing unit, that is, the flip-flops which can be addressed by an instruction. The list also indicates the degree of control the programmer has over the flip-flops, that is, whether he can test, set, or reset them.

The flip-flops in the Larc system have many functions. Some are solely for the use of the programmer and are entirely under his control; others are used for indicating errors or contingencies and may only be tested and reset by the programmer. Still others serve as a means of communication between Computing Unit and processor.

# 2-11. THE HIGH-SPEED BUS

The high-speed bus is a fast-transfer channel between the main storage units and the rest of the system. It is used by the Computing Unit, by the central processor, and by the synchronizers of the various input-output units by way of the processor dispatcher.

It requires 1/2 microsecond to transfer a word on the high-speed bus. Thus, during every memory cycle (4 microseconds) the bus can handle eight words. These 1/2-microsecond periods, or time slots, are allocated in a special way to the various units using the bus. Figure 2-2 shows how the eight time slots in a 4-microsecond memory cycle are distributed.

| TIME SLOTS (1/2-MICROSECOND EACH) |                                     |                                 |                         |             |                                     |                                 |                         |

|-----------------------------------|-------------------------------------|---------------------------------|-------------------------|-------------|-------------------------------------|---------------------------------|-------------------------|

| 0                                 | 1                                   | 2                               | 3                       | 4           | 5                                   | 6                               | 7                       |

| CENTRAL<br>PROCESSOR              | COMPUTING<br>UNIT 1<br>INSTRUCTIONS | COMPUTING<br>UNIT 2<br>OPERANDS | PROCESSOR<br>DISPATCHER | [NOT USED ] | COMPUTING<br>UNIT 2<br>INSTRUCTIONS | COMPUTING<br>UNIT 1<br>OPERANDS | PROCESSOR<br>DISPATCHER |

|                                   |                                     |                                 |                         |             |                                     |                                 | 146                     |

Figure 2-2. Allocation of Time Slots on the High-Speed Bus

# 2-12. EXECUTION OF AN INSTRUCTION

In order to illustrate the over-all operation of the control unit a simple instruction will be traced through the unit. Figure 2-1 shows a simplified block diagram of the control circuits and reference should be made to this figure in following the explanation in the succeeding paragraphs.

It is assumed that initially the address in Cl is 00400, and that storage location 00401 contains the following instruction:

T

I

A

B

M

.

01

05

12

00100

and that fast register 12 contains:

000 00 00 00050

The instruction tells the control unit to add the contents of storage location 00100 (modified by the contents of fast register 12) to the contents of fast register 5 and leave the result in register 5.

First, the contents of C1 (00400) are sent to input 1 of the B adder and the number 00001 is selected for the second input. The output of the B adder is the sum of the two inputs, or 00401, the address of the next instruction. This address is returned to C1 to be stored until required for selection of the next instruction after 00401. The address is also sent to MAD2 where the cabinet and storage unit containing storage location 00401 are selected. The partially decoded information is sent from the memory address decoder over the address lines to the relevant storage unit.

In the storage unit the final decoding is done and the selected word (00401) is transmitted over the high-speed bus to IR1.

As the instruction digits enter IR1 the tracing-mode digit (.) enters the operation decoder and is decoded to signify normal operation. Simultaneously, the two B digits of the instruction are sent to the fastregister selector, which decodes the digits and selects the correct fast register (register 12). The selector causes the five least-significant digits of the register (00050) to be transmitted to input 2 of the B adder. While the B-register selection takes place, the M digits of the instruction in IR1 (00100) are sent to input 1 of the B adder, and at the same time, the I and the A digits of IR1 proceed to IR2.

The two five-digit numbers arrive simultaneously at the adder and a sum is formed. The result (OO150), which is the modified M address of the instruction, is sent to the M-digit positions of IR2, which now contains the instruction with the modified M address replacing the original M address. (The T digit and the B digits of the instruction are not retained after modification has taken place.) The modified M address is also sent to MAD2 which decodes the operand address. The operand is eventually transmitted from storage to the M-input of the AU. The operation digits of the instruction in IR2 enter the operation decoder where signals are generated to direct the remaining stages of the instruction. In particular, control signals are sent to the AU to prepare it to handle the operands.

While the M address is being decoded the two A digits of the instruction are routed from IR2 through the B adder to the fast-register selector. The selector causes the contents of the specified A register (register 5) to enter the A-input of the AU. Simultaneously, the other operand enters the M-input channel from the high-speed bus. The AU has now been provided with all the information it requires and therefore carries out the addition and enters the sum in the AU result register.

Meanwhile, the A digits of the instruction have entered the B adder for the second time and on leaving are retained in the selector storage unit. When the result of the operation has been stored in the AU result register, the two A digits go from selector storage to the fast-register selector where they are decoded to select the fast register which receives the result. In this case the result is stored in fast register 5, the Aoperand register. (This is not the case, however, for all instructions.) The old contents of the A register are deleted and the new result is read in from the AU result register.

# 2-13. INSTRUCTION OVERLAPPING

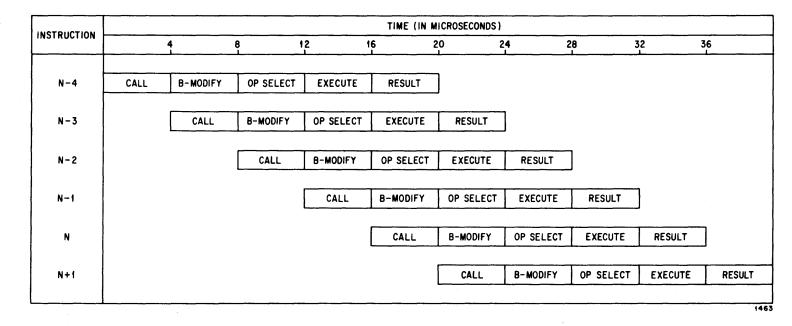

It was stated in the introduction to this section that instructions are not processed serially by the control unit but overlap in time with preceding and succeeding instructions. The preceding paragraph explained how a single instruction was decoded and executed. The many stages in the process can be reduced to five basic operations, named in order, call instruction, B modification, operand select, execute, and result. Each of these operations can be considered to require 4 microseconds to carry out. The 4-microsecond time unit, known as a memory cycle, is the time actually required to read a word from or into a storage location.

Figure 2-3 shows a series of instructions passing through the above five stages. The instructions are staggered by a period of 4 microseconds. When instruction N is being called from storage, the previous instruction N - 1 is having its M address modified, the operands for N - 2 are being brought from memory, the AU is executing N - 3 and the results of N - 4 are being stored. In the next memory cycle, N + 1 is called from memory, N is B-modified, and so on.

The chart in figure 2-3 shows a series of simple instructions where the total execution time for each instruction is approximately 20 microseconds. Some more complex instructions, of course, take longer than 20 microseconds and succeeding instructions are delayed accordingly. Note that although each instruction takes about 20 microseconds to pass through the control unit, the next instruction is called after only 4 microseconds have elapsed. That is, for all practical timing purposes a simple instruction has an execution time of 4 microseconds. In fact, because the basic memory cycle is 4 microseconds and the time slots are fixed, any execution time is a multiple of 4 microseconds.

Figure 2-3. Instruction Overlapping

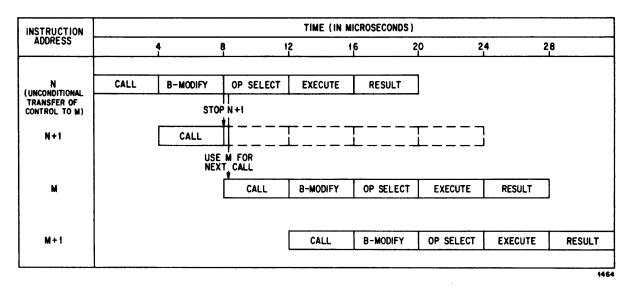

As an example of the use of the chart in figure 2-3, consider a sequence of instructions which contains an unconditional-transfer-of-control instruction. (See figure 2-4.) This instruction (N) merely transfers control to the instruction in the storage location specified by the modified M address of the transfer-of-control instruction. The instruction following the control transfer (N + 1) will therefore never be needed. However, due to the overlap of instructions, the instruction in location N + 1 will in fact be called for before the computer has fully decoded the unconditional-transfer instruction (operand-select cycle). Therefore, when the control unit has decoded the control-transfer instruction. a signal is sent which prevents instruction N + 1 from entering the first instruction register. The instruction specified by the M digits of the unconditionaltransfer-of-control instruction will be called for in the next memory cycle. Thus, a memory cycle has been lost during the transfer of control. An unconditional-transfer-of-control instruction therefore has an effective execution time of 8 microseconds.

Figure 2-4. Sequencing of an Unconditional-Transfer-of-Control Instruction

# 2-14. CONTROL OF ERRORS, CONTINGENCIES, AND THE TRACING MODE

These three topics are dealt with at length in section 7. However, this section gives a useful brief description of the function of the control unit in these three areas.

An error is usually caused by a computer failure of some kind. However, incorrect programming also can cause errors to occur; for example, if an instruction contains the address of a non-existent storage location in the M-digit positions an error will be signified when the instruction is executed. There are several error flip-flops in the computer, each relating to a specific error. When the control unit detects an error it sets the related flip-flop or flip-flops. This automatically sets the master error flip-flop during the instruction result time. When the master error flip-flop has been set, the control unit stores an unconditional-transferof-control instruction in storage location 02600 which serves as a return jump to the program. (The M digits of this instruction usually contain the address of the next instruction after the one in which the error occurred, but this is not always so.) Control is then transferred to the instruction in address 02601. Obviously, some routine for diagnosing errors must be in the computer with its first address at 02601. A general discussion of error routines is given in section 7. In general, however, when an error occurs the computer does not complete the instruction causing the error before entering the error routine, although in a few cases the instruction is actually completed. (See note, page 7-3.)

A contingency is caused by some programming error; overflow and sign anomalies are examples. The control unit handles contingencies in the same way as it does errors, that is, one or more contingency flip-flops are set, causing the master contingency flip-flop to be set. The address of the next instruction after the one in which a contingency occurred is stored as the M address of an unconditional-transfer-of-control instruction in 02700 and control is transferred to the instruction in address 02701. A contingency routine must be stored in the computer with its first instruction in storage location 02701. A general discussion of contingency routines is given in section 7.

When contingencies occur the address stored in 02700 is always that of the next instruction. An instruction in which a contingency occurs is always completed (and in a few cases the next instruction also is completed) before the computer enters the contingency routine.

The first character of an instruction, known as the tracing digit, is usually a period. Its presence causes normal execution of the instruction. The first character may also be any of the digits 1 through 9 or the ignore symbol (i).

There are nine tracing mode flip-flops in the Computing Unit corresponding to the digits 1 through 9. They may be set as the result of programmed instructions. Whenever the control unit decodes an instruction with one of the digits 1 through 9 in the tracing position, the corresponding flip-flop is tested. If it is in the reset state, the computer continues in normal operation exactly as if a period had been present. If, however, the flip-flop is in the set state, the computer enters the tracing mode before the instruction is executed.

When the computer enters the tracing mode control is in fact transferred to the error routine exactly as if an error had occurred. The error routine must be so written as to detect the tracing mode and transfer to a special tracing routine. This facility is designed to assist a programmer in debugging programs. The tracing routine, for example, may be programmed to print out the contents of certain registers before returning to the program. A general discussion of tracing routines is found in section 7. It is important to notice that instructions with tracing digits behave like any other instructions as long as the corresponding flip-flops are reset.

An ignore symbol (i) in the tracing position always causes the computer to enter the indirect-addressing mode. The M address of the instruction does not specify the operand but specifies a word where the operand address may be found. The indirect-addressing mode is, in fact, more complex than this and a full explanation is found in section 6. The indirectaddressing mode does not use a separate routine as does the error, contingency, and tracing modes. The extraction of indirect addresses is carried out solely by the control unit circuits.

# SECTION 3 INSTRUCTION DETAILS

The purpose of this section is to introduce the instruction repertory of the Larc Computing Unit. Instructions are presented by class and are described according to their normal use. The execution time in microseconds is specified for each instruction. The times given allow for overlap and each time is, in fact, the period that elapses from the end of the previous instruction to the end of the current instruction. (See appendix A for a condensed numerical list of instructions.)

# **3-1. INSTRUCTION FORMAT**

The format of an instruction word for the Larc Computing Unit has already been described in section 2. Also in that section the mode of execution of an instruction was outlined. In this section, descriptions of the operation of individual instructions are designed specifically for the programmer's use. They are not intended to be precise descriptions of computer logic. In particular, as the contents of control counter 1 (C1) depend not only on the instruction being executed, but also on the two following (see figure 2-3), this control counter will not be mentioned in instruction descriptions. In order to avoid using Cl, a hypothetical control counter C will be used. The contents of the hypothetical counter C, otherwise written as (C), will be the address of the instruction being executed; the symbolic notation, (C) + 1  $\longrightarrow$  C, means continue with the next instruction in sequence; and  $M \longrightarrow C$  means transfer control to the instruction in storage location M. The programmer must remember that in fact there is no control counter such as C, and that C has been introduced merely as a device to simplify descriptions.

It will have been noted that there are three addresses in the Computing Unit instruction word. Two of these (A and B) are fast-register addresses and the third (M) may be either a fast-register address or a core-storage address. If any of these addresses in an instruction word exceeds the maximum available, errors will usually occur when the instruction is decoded. In a few instructions some of the addresses are not used and may exceed the maximum without causing errors. However, note that in all instructions modification will invariably take place and hence the M digits of the instruction must be numeric even if they are not needed. For the same reason the B address must always specify a fast register and the M digits of the fast register must also be numeric. The original description of a Computing Unit instruction word as given in section 2 requires some amplification. The T digit is known as the tracing digit and may be one of the characters 1 through 9, period (.), or ignore symbol (i). If the tracing digit is one of the digits 1 through 9 and the corresponding tracing flip-flop is set, the execution of an instruction is delayed while the computer enters the tracing mode. (This mode is fully explained in section 7.) If the tracing digit is a period (.), the instruction is executed normally. In the examples contained in this section the tracing digit will always be a period. If the tracing digit is ignore (i), the computer operates in the indirect addressing mode. (This mode is more fully explained in section 6.)

The five M digits of an instruction word usually contain the address of a storage location. The addresses range from 00000 to Lim M; Lim M may vary from system to system but never exceeds 97499. The M digits may, however, be used to address a fast register. In this case the address would be of the form 999AA, where AA is a normal fast-register address.

The A and the B digits of an instruction usually specify fast-register addresses. These range from Ol to Lim A; Lim A never exceeds 99. In the Larc system (serials 1 and 2), Lim A is, in fact, less than 99. The references to Lim A in the manual therefore assume this fact. Note, however, that in a Larc system with a full complement of fast registers, certain of the error conditions listed in this manual will not apply.

For example, in a double-precision store instruction (paragraph 3-6), the use of 78 as the A address will cause errors if Lim A is equal to 78, but 99 as the A address will not cause errors if Lim A is equal to 99. The reason for this is that when the A address (99) is incremented by 1 to give the address for the second half of the store, the resulting two-digit address will be 00.

The contents of a fast register may either be interpreted as a normal operand or as a counter and modifier. In the latter case the fast register is referred to as an index register. It should be noted that any fast register may be used as an index register.

# **3-2. INDEX REGISTER FORMAT**

The contents of a fast register used as an index register have the following format:

### NNN DDDD $\triangle \triangle \triangle \triangle$

The three N digits are known as a cycle counter. The repertory of the computer contains index-register instructions which reduce the counter of an index register and test it for zero. The five  $\triangle$  digits are known, collectively, as the address modifier. These are the digits that are used in an instruction to modify the M address. The D digits are used by index register instructions to increment or decrement the address modifier.

There is one special fast register (address 00) in the Larc Computing Unit which may be used to supply an operand consisting of a period and 11 decimal zeros (.0000000000). This operand is permanently stored in the computer and cannot be changed by the programmer.

#### 3-3. OPERANDS

In arithmetic operations the Larc Computing Unit interprets the operands as numbers. Numbers may be stored in the Larc computer in four distinct ways as follows:

- (1) Single-precision, fixed-point fractions.

- (2) Double-precision, fixed-point fractions.

- (3) Single-precision, floating-point numbers.

- (4) Double-precision, floating-point numbers.

A single-precision, fixed-point number has the following format:

# S<sub>A</sub>XXXXXXXXXXX

where S is the sign digit and X represents any decimal digit. The decimal point is automatically taken to be between the sign and the most significant decimal digit. A single-precision, fixed-point operand is thus a signed ll-digit fraction.

A double-precision, fixed-point number consists of two Larc computer words and has the following format:

# S XXXXXXXXXX S XXXXXXXXXX

This number represents a signed, 22-digit fraction. The decimal point is automatically taken to be between the sign and the most significant decimal digit of the left-hand, or most significant word. In double-precision arithmetic instructions the most significant word is addressed; the least significant word is always taken from the next higher storage location or fast register. The signs in both halves of a double-precision operand should agree.

A single-precision, floating-point number in the Larc Computing Unit has the following format:

# SEE XXXXXXXX

where S and X have the same interpretation as before and the E digits represent an excess-50 power of ten, or exponent. The decimal point is taken to be between the E digits and the most significant decimal digit. A single-precision, floating-point number thus represents a signed, ninedigit fraction raised to some power of ten (EE - 50). The operand should always be normalized, that is, the most significant X digit should not equal zero. Floating-point results produced by the computer are normalized automatically. The fractional part of a floating-point number will in the future be referred to as the mantissa.

The ranges of a single-precision, floating-point number (N) are as follows:

$$-.999999999 \times 10^{49} \le N \le -.1 \times 10^{-50}$$

and

$$1 \times 10^{-50}$$

< N < .999999999 ×  $10^{49}$

40

The format of a double-precision, floating-point number is:

SEE XXXXXXXXX S XXXXXXXXXX

This number represents a floating-point number with a mantissa of 20 decimal digits. The decimal point is taken to be in the most significant word immediately following the exponent. The signs of both words should agree and the mantissa should be normalized.

The ranges of a double-precision, floating-point number (N) are as follows:

and

The rules for addressing a double-precision, floating-point number are the same as those for a double-precision, fixed-point number.

The character in the sign position of a number should be one of the following:

- (1) Zero (0), indicating that the number is positive.

- (2) Minus (-), indicating that the number is negative.

- (3) Period (.), indicating a special use of the number. (This is explained further in paragraphs 3-7 and 3-13.)

Variations in the use of the sign digit depend on the type of operation. They will be discussed under the appropriate headings in the instruction repertory.

The format of Larc alphanumeric words is discussed in section 4 in connection with input-output equipment operations.

# 3-4. FLOATING-POINT ARITHMETIC

The instruction repertory of the Larc Computing Unit contains instructions which carry out arithmetic operations on floating-point numbers. Some general aspects of floating-point arithmetic are reviewed here.

Overflow, as understood in the fixed-point sense, does not occur in floating-point operations. Whenever the mantissa would overflow it is shifted right and the exponent is increased by 1. However, if the exponent becomes greater than its maximum permissible value (99), an exponent overflow contingency will occur. In a similar way, if the result is found to be non-normalized, the computer shifts the mantissa to the left and decreases the exponent accordingly. If the exponent is decreased so that it becomes less than zero, an exponent underflow contingency will occur.

Normally, the result exponent after overflow or underflow has occurred will be meaningless. If the programmer needs to have this information, he may use the following general rule: calculate the result by using the true floating-point representations of the operands (that is, subtract the excess 50 from the exponents), add 50 to the result exponent, and take the ten's complement if the excess-50 result exponent is negative. (For example, the computer representation of an excess-50 exponent of -34 would be 66.) This will give the result exponent.

The following table gives the range of result exponents for all floating-point operations in which an exponent overflow or underflow contingency occurs:

| Operation                                  | Exponent Range<br>(overflow) | Exponent Range<br>(underflow) |

|--------------------------------------------|------------------------------|-------------------------------|

| Add or subtract (single precision)         | 00                           | 99-91                         |

| Add or subtract (double precision)         | 00                           | 99-80                         |

| Multiply (single or double pre-<br>cision) | 00-48                        | 99-49                         |

| Divide (single or double precision)        | 00-50                        | 99-51                         |

If the computer uses non-normalized operands in a floating-point computation it is possible for contingencies to occur. Hence, the floatingpoint representation of zero requires special treatment, as zero cannot be normalized. In the Larc Computing Unit, positive or negative zero will cause contingencies but the computer is designed to handle absolute zero (period and 11 zeros) without causing contingencies. In all cases where a zero is required, the programmer should use absolute zero or a small positive or negative number to avoid contingencies.

If an exponent underflow contingency occurs in a program, control will be transferred to the contingency routine. In designing a contingency routine the programmer must decide what he wishes to do in case of underflow. Underflow is caused by results too small to be in the range of floatingpoint numbers. The contingency routine must replace the erroneous result by some approximation to the actual value, either a small positive or negative number ( $.1 \times 10^{-50}$  or  $-.1 \times 10^{-50}$ ), or absolute zero. It is possible for a floating-point computation to result in zero. For example, if the two operands below are added, the result will be as shown:

| Operands |      | 347263157<br>347263157 |

|----------|------|------------------------|

| Result   | 0 41 | 00000000               |

The initial result in the arithmetic unit would, of course, be:

# 0 50 00000000

In attempting to normalize, the arithmetic unit would shift the mantissa nine places to the left and reduce the exponent by the number of shifts. In failing to normalize, the arithmetic unit would set the zero floatingpoint adder result contingency flip-flop and transfer control to the contingency routine. This routine must be designed to replace the zero result by some approximation of the true result. If we assume that, on the average, there is an error of 5 in the tenth place of the mantissa, the approximate result before normalizing would be:

# 0 50 00000000 5

Therefore an approximate result of:

# 0 41 50000000

would be the best approximation to replace the zero result. The additional time required by the contingency routine each time a zero result occurs would be a very small percentage of the complete program running time. In special cases, the programmer may wish to use absolute zero to replace a zero produced by addition or subtraction, but in general, the above procedure tends to reduce the accumulation of error terms.

# **3-5. PROGRAM CONVENTIONS**

The following programming conventions are used in the remainder of this manual:

- M The five M digits of an instruction. These digits usually specify a core-storage address or a fast-register address.

- A The two A digits of an instruction. These digits usually specify a fast-register address.

- B The two B digits of an instruction. These digits always specify the address of a fast register which is to be used as an index register.

- $A_{\Delta}$  The two A digits of the word in fast register A.

- $A_{\rm \tiny R}$   $\,$  The two B digits of the word in fast register A.

The two A digits and the two B digits of the word in fast regis-A<sub>AB</sub> ter A. AM The five M digits of the word in fast register A. The tracing digit and the two instruction-designator digits (TII) Α<sub>T</sub> of the word in fast register A. The same notation is used to denote a portion of the word in MA storage location M; that is,  $M_{\Delta}$ ,  $M_{B}$ ,  $M_{\Delta B}$ ,  $M_{M}$ , and  $M_{T}$ . ٠ 1 The address of a double precision word stored in two storage locations or two fast registers. A' = A and A + 1M' = M and M + 1() The contents of (M) means the contents of storage location M. () i The initial contents of ()f The final contents of

The absolute value or magnitude of |(M)| means the magnitude of the contents of storage location M.

Floating-point operation (M)  $\oplus$  (A) denotes the floating point addition of (M) and (A).

Rdd Rounded result.

# **3-6. DATA-TRANSFER INSTRUCTIONS**

Instructions in this class transfer words of data from fast storage to memory, from.memory to fast storage or from one fast register to another. Data-transfer instructions are of two types: single precision, in which the contents of one location are transferred and double precision, in which the contents of two adjacent locations are transferred. In double-precision transfers the word addressed by the instruction forms one half of the operand and the next higher word in the memory or fast storage forms the other half.

$\frac{\text{STORE S} 40 4 \mu \text{s}}{\text{T} 40 \text{ AA BB MMMMM}}$   $(A) \longrightarrow M$

Transfer the contents of fast register A to storage location M. The contents of fast register A are not changed.

The instruction will transfer words comprising any combination of legitimate Larc characters.

Storing the contents of fast register 00 is a legitimate operation; it will place in the specified storage location a word consisting of a period in the sign position and 11 decimal zeros. For convenience, this number will in the future be referred to as absolute zero, but the programmer should note that in a few instances the quantity will have no numerical significance.

Words may be stored in a fast register by writing the M address as 999AA, where AA is a fast-register address. For example, the instruction . 40 03 00 99921 will store the contents of fast register 03 in fast register 21. The M address 99900 should not be used in any store instruction because it will cause errors. Fast register 00 is a special-purpose register which cannot be written into.

$\frac{\text{STORE NEGATIVE SN 41 } 4 \mu \text{s}}{\text{T 41 AA BB MMMMM}}$  $-(\text{A}) \longrightarrow \text{M}$

Transfer the negative value of the contents of fast register A to storage location M. The contents of fast register A are not changed.

Only the sign of the word is altered during the transfer. The alteration of the sign takes place according to the rules expressed in the following table:

| Sign | of | Word | in | Α | 0 | - | • |

|------|----|------|----|---|---|---|---|

| Sign | of | Word | in | М | - | 0 | • |

If the sign of the operand is a character other than (0), (-), or (.), a sign-anomaly contingency will occur. The store operation will take place and a zero will be deposited in the sign position of M.

The other 11 characters in the word transferred may be any combination of legitimate Larc characters.

$\frac{\text{STORE MAGNITUDE SM 42 4} \mu \text{s}}{\text{T 42 AA BB MMMMM}}$  $|(\text{A})| \longrightarrow \text{M}$

Transfer the absolute value of the contents of fast register A to storage location M. The contents of fast register A are not changed.

The instruction will transfer words comprising any combination of legitimate Larc characters. Only the sign of the word is altered during the transfer; the sign is always changed to a decimal zero, regardless of its original value.

Note that the instruction . 42~00~BB~MMMMM will store a word consisting of 12 decimal zeros in storage location M.

STORE, DOUBLE PRECISION SS 45  $8\mu s$ T 45 AA BB MMMMM (A)  $\longrightarrow$  M (A + 1)  $\longrightarrow$  M + 1

Transfer the contents of fast register A to storage location M; then, transfer the contents of fast register A + 1 to storage location M + 1. The contents of fast register A and A + 1 are not changed. The contents of the fast register may be any combination of legitimate Larc characters.

As in the single-precision store instructions, words may be stored in fast registers by writing the M address as 999AA, where AA is a fastregister address. For example, the instruction . 45 13 00 99916 will store the contents of fast register 13 in fast register 16, and the contents of fast register 14 in fast register 17.

The double-precision store instruction virtually operates as two single-precision store instructions in sequence. This gives unusual results when an instruction such as . 45 12 00 99913 is executed. In this case, the contents of fast register 12 are stored in fast register 13, and the contents of fast register 13 are then stored in fast register 14. The net effect of the double-precision store instruction is to transfer the contents of fast register 12 to fast registers 13 and 14. In particular, the instruction . 45 00 00 99901 will store absolute zero in fast registers 01 and 02.

There is a special restriction on the use of a double-precision store instruction in the last word position of a memory unit, that is, in storage locations 02499, 04999, etc. If a double-precision store instruction in one of these locations has as its M address the address of the instruction, the next instruction to be executed will be taken from the first location of the next memory unit before the second half of the store takes place. For example, if in location 02499 there is the instruction . 45 06 00 02499, the next instruction will be taken from 02500 before the contents of fast register 07 have been stored there.

This is contrary to the normal case in which such an instruction is held in any location other than the last word position of a memory unit. In this case the next instruction will be the new contents of the second storage location. It will be seen that the use of Lim A or Lim M as A or M addresses in any double-precision store instruction will cause errors. The second half of the store will then be dealing with nonexistent fast registers or storage locations.

| STORE | NEGATIVE, | DOU  | IBLE | PREC | ISION | SSN | 46 | 8µs |

|-------|-----------|------|------|------|-------|-----|----|-----|

|       | Т         | 46   | AA   | BB   | MMMMM |     |    |     |

|       |           | -    | (A)  |      | М     |     |    |     |

|       | -         | (A + | • 1) |      | M + 1 |     |    |     |

Transfer the negative value of the contents of fast register A to storage location M; then, transfer the negative value of the contents of fast register A + 1 to storage location M + 1. The contents of fast registers A and A + 1 are not changed.

The sign of each word transferred is altered independently. The signs are altered according to the rules expressed in the following table:

| Sign | of | Word | in | Α | 0 | - | • |

|------|----|------|----|---|---|---|---|

| Sign | of | Word | in | M | - | 0 | • |

. .

If the sign of either word is a character other than (0), (-), or (.), a sign-anomaly contingency will occur.

If the signs of both words are incorrect, both halves of the store operation will take place and a O will be deposited in the sign positions of M and M + 1. If the sign of the second word (A + 1) only is incorrect, storage of the first word will take place normally and storage of the second word will be carried out with a O deposited in the sign position of M + 1. If the sign of the first word (A) only is incorrect and M is the address of a storage location, storage of the first word will take place and a O will be deposited in the sign position of M; storage of the second word will take place normally. If the sign of the first word (A) only is incorrect and M is the address of a fast register, the storage of the first word will take place and a O will be deposited in the sign position of M; storage of the second word will take place and a O will be deposited of the first word will take place and a O will be deposited in the sign position of M; storage of the second word will take place with the following rules for the sign digit established by the rules expressed in the following table:

| Sign of Word in A + 1   | 0 | - | •                      |

|-------------------------|---|---|------------------------|

| Sign of Word in $M + 1$ | 0 | 0 | Bad parity combination |

The bad parity combination will not cause errors until a further attempt to use fast register M + 1 is made.

The other 11 characters in each word are transferred unchanged, and may be any combination of legitimate Larc characters.

The double-precision, store-negative instruction virtually operates as two single-precision store instructions in sequence. This gives unusual results in an instruction such as . 46 12 00 99913. In this case, the negative value of the contents of fast register 12 are stored in fast register 13, and the negative value of the contents of fast register 13 is then stored in fast register 14. The net effect of the instruction is to transfer the negative value of the contents of fast register 12 to fast register 13, and the original contents of fast register 12 to fast register 14.

The special restriction on the use of a double-precision store instruction in the last word position of a memory unit applies also to the double-precision, store-negative instruction.

> STORE MAGNITUDE, DOUBLE PRECISION SSM 47  $8\mu s$ T 47 AA BB MMMMM  $|(A)| \longrightarrow M$  $|(A + 1)| \longrightarrow M + 1$

Transfer the absolute value of the contents of fast register A to storage location M; then, transfer the absolute value of the contents of fast register A + 1 to storage location M + 1. The contents of fast registers A and A + 1 are not changed.

The instruction will transfer words comprising any combination of legitimate Larc characters. Only the signs of the two words are altered during the transfer. These are always changed to decimal zeros regardless of their original values.

The instruction . 47 12 00 99913 will have the net effect of transferring the absolute value of the contents of fast register 12 to fast registers 13 and 14.

The special restriction on the use of a double-precision store instruction in the last word position of a memory unit applies also to the double-precision, store-magnitude instruction. However, it is unlikely that the programmer would use this instruction to store instruction words as the tracing digit of the stored instruction would be zero, causing errors if the instruction were executed.

$\frac{\text{FETCH F} 43 4 \mu \text{s}}{\text{T} 43 \text{ AA BB MMMMM}}$   $(M) \longrightarrow A$

Transfer the contents of storage location M to fast register A. The contents of storage location M are not changed.

The instruction will transfer words comprising any combination of legitimate Larc characters.

Words may be fetched from a fast register by writing the M address as 999AA, where AA is a fast-register address. In particular, the instruction . 43 01 00 99900 will have exactly the same effect as the instruction . 40 00 00 99901.

Note that in this instruction the fast-register address OO is not a valid A address. Errors will occur if any attempt is made to write into this fast register.

FETCH, DOUBLE PRECISION FF 48  $8\mu$ s T 48 AA BB MMMMM (M)  $\longrightarrow$  A (M + 1)  $\longrightarrow$  A + 1

Transfer the contents of storage location M to fast register A; then, transfer the contents of storage location M + 1 to fast register A + 1. The contents of storage locations M and M + 1 are not changed.

The contents of the two words transferred may be any combinations of legitimate Larc characters.

As in the single-precision fetch instruction, words may be fetched from fast registers by writing the M address as 999AA, where AA is a fastregister address. For example, the instruction . 48 16 00 99902 will transfer the contents of fast register 02 to fast register 16, and transfer the contents of fast register 03 to fast register 17.

The double-precision fetch instruction virtually operates as two single-precision fetch instructions in sequence. This gives unusual results when an instruction such as . 48 17 00 99916 is executed. In this case the contents of fast register 16 are transferred to fast register 17, and then the contents of fast register 17 are transferred to fast register 18. The net effect of the instruction is to transfer the contents of fast register 16 to fast registers 17 and 18. In particular, the instruction . 48 01 00 99900 will transfer absolute zero to fast registers 01 and 02.

It will be seen that the use of Lim A or Lim M as A or M addresses in the double-precision fetch instruction will cause errors. The second half of the store will then be dealing with nonexistent fast registers or storage locations.

# **3-7. FIXED-POINT ARITHMETIC INSTRUCTIONS**

Instructions in this class perform basic arithmetic operations on words representing fixed-point fractions. Single-precision instructions are considered first, followed by double-precision instructions. The mnemonic of every instruction in this class contains an X. Read the X as 'fixed point'.

Characters in the nonsign positions of operands should be numeric only. If one or more of the nonsign positions of an operand contain a non-numeric character, an error will occur and no result will be stored. The M operand may be a fast register.

In any fixed-point addition or subtraction in which the signs of the operands are either (0) or (-), a zero result will take the sign of the A operand.

If either operand in a fixed-point addition or subtraction contains a (.) in the sign-digit position, the absolute value of the result will be the sum of the absolute values of the operands, and the sign of the result will be given by the appropriate sign table.

If a sign-anomaly contingency occurs in any fixed-point arithmetic instruction, the sign of the result will be (0). In a fixed-point addition or subtraction in which a sign-anomaly contingency occurs, the absolute value of the result will be the sum of the absolute values of the operands.

| ADD, | F | IXED  | <b>P</b> 01 | NT  | AX | 01  | 4μs |

|------|---|-------|-------------|-----|----|-----|-----|

|      | т | 01    | AA          | BB  | MM | MMM |     |

|      |   | (M) + | - (A        | ) — |    | A   |     |

Add the fixed-point fraction in storage location M to the fixed-point fraction in fast register A. Store the sum, with correct sign, in fast register A. The contents of storage location M are not changed.

The sign position in either word may contain any of the characters (0), (-), (.), or one of the digits 1 through 9. The sign of the result is governed by the rules expressed in the following table.

| Sign of<br>Word in | Sign of Word in M |          |          |          |         |  |  |  |

|--------------------|-------------------|----------|----------|----------|---------|--|--|--|

| A                  | 0                 | -        | •        | l thru 9 | i. ∆. + |  |  |  |

| 0                  | 0                 | 0/-      | 0        | l thru 9 | С       |  |  |  |

| -                  | 0/-               | -        | -        | l thru 9 | С       |  |  |  |

| •                  | 0                 | -        | •        | l thru 9 | C       |  |  |  |

| l thru 9           | l thru 9          | l thru 9 | l thru 9 | С        | С       |  |  |  |

| i. ∆. +            | С                 | С        | С        | C        | C       |  |  |  |

# NOTE

The letter C shows that a sign-anomaly contingency will occur. When the sign of the result can only be determined by the calculation, it is shown as O/-.

If the absolute value of the sum is greater than 1, a fixed-point overflow contingency will occur.

| NEGAT I VE   | ADD | ), F | IXED | <b>P</b> 01 | NT | NX  | 11 | 4μs |

|--------------|-----|------|------|-------------|----|-----|----|-----|

|              | Т   | 11   | AA   | BB          | MM | MMM |    |     |

| -(M) + (A) A |     |      |      |             |    |     |    |     |

Add the negative value of the fixed-point fraction in storage location M to the fixed-point fraction in fast register A and store the sum, with correct sign, in fast register A. The contents of storage location M are not changed. More simply, subtract the fixed-point fraction in storage location M from the fixed-point fraction in fast register A.

The sign position in either word may contain any of the characters (0), (-), (.), or one of the digits 1 through 9. The sign of the result is governed by the rules expressed in the following table:

| Sign of<br>Word in | Sign of Word in M |          |          |          |         |  |  |

|--------------------|-------------------|----------|----------|----------|---------|--|--|

| A                  | 0                 | -        | •        | l thru 9 | i, ∆, + |  |  |

| 0                  | 0/-               | 0        | 0        | l thru 9 | С       |  |  |

| -                  | -                 | 0/-      | -        | l thru 9 | С       |  |  |

| •                  | -                 | 0        | •        | l thru 9 | C       |  |  |

| l thru 9           | l thru 9          | l thru 9 | l thru 9 | С        | С       |  |  |

| i, A, +            | С                 | С        | С        | С        | С       |  |  |

#### NOTE

The letter C shows that a sign-anomaly contingency will occur. When the sign of the result can only be determined by the calculation, it is shown as O/-.

If the absolute value of the difference is greater than 1, a fixedpoint overflow contingency will occur.

MULTIPLY, FIXED-POINT ROUNDED MXR 20 8µs

T 20 AA BB MMMMM

$[(M) \times (A)]$  Rdd  $\longrightarrow$  A

Multiply the fixed-point fraction in fast register A by the fixedpoint fraction in storage location M; store the rounded single-length product, with correct sign, in fast register A. Rounding is accomplished in the usual way. The most significant digit of the least significant half of the double-length product is examined; if it is greater than or equal to five, 1 is added to the least significant digit of the most significant half of the product. If the digit is less than five, the most significant half of the product is not altered. In either case the most significant half of the product is stored as the final result. The contents of storage location M are not changed. The sign positions of each operand must contain one of the characters (0), (-), or (.). The sign of the result is governed by the rules expressed in the following table:

| Sign of<br>Word in | Sign of Word in M |   |   |          |         |  |  |

|--------------------|-------------------|---|---|----------|---------|--|--|

| A                  | 0                 | - | • | l thru 9 | i, ∆, + |  |  |

| 0                  | 0                 | - | • | С        | C       |  |  |

| -                  | -                 | 0 | • | С        | C       |  |  |

| •                  | •                 | • | • | С        | C       |  |  |

| l thru 9           | C                 | С | С | С        | C       |  |  |

| i, ∆, +            | С                 | С | С | С        | C       |  |  |

NOTE

The letter C shows that a sign-anomaly contingency will occur.

No overflow contingency can occur in this instruction as the absolute value of the result is always less than that of either operand.

MULTIPLY, FIXED-POINT EXTENDED MXE 21 12µs

T 21 AA BB MMMMM

(M) x (A) — A'

Multiply the fixed-point fraction in fast register A by the fixedpoint fraction in storage location M; store the result as a doubleprecision, fixed-point fraction in fast registers A and A + 1. The signs of (A) and (A + 1) in the result are equal. The contents of storage location M are not changed.

The sign position of each operand must contain one of the characters (0), (-), or (.). The sign of the result is governed by the rules expressed in the following table:

| Sign of      | Sign of Word in M |   |   |          |         |  |  |

|--------------|-------------------|---|---|----------|---------|--|--|

| Word in<br>A | 0                 | - | • | l thru 9 | i, ∆, + |  |  |

| 0            | 0                 | - | • | С        | С       |  |  |

| -            | -                 | 0 | • | С        | С       |  |  |

| •            | •                 | • | • | С        | С       |  |  |

| l thru 9     | С                 | С | С | С        | C       |  |  |

| i, ∆, +      | C                 | С | С | С        | С       |  |  |

# NOTE

The letter C shows that a sign-anomaly contingency will occur.

No overflow contingency can occur in this instruction as the absolute value of the result is always less than that of either operand.

If the A address of the instruction is equal to Lim A, an error will occur.

## DIVIDE, FIXED POINT DX 30 32µs

T 30 AA BB MMMMM

(A) ÷ (M) → A

Divide the fixed-point fraction in fast register A by the fixed-point fraction in storage location M; store the quotient in fast register A with correct sign. The remainder is not retained and the quotient is not rounded. The contents of storage location M are not changed.

The sign position of each operand must contain one of the characters (0), (-), or (.). The sign of the result is governed by the rules expressed in the following table:

| Sign of<br>Word in | Sign of Word in M |   |   |          |         |  |  |

|--------------------|-------------------|---|---|----------|---------|--|--|

| A                  | 0                 | - | • | l thru 9 | i, ∆, + |  |  |

| 0                  | 0                 | - | • | С        | С       |  |  |

| -                  | -                 | 0 | • | с        | С       |  |  |

| •                  | •                 | • | • | С        | С       |  |  |

| l thru 9           | С                 | С | С | С        | С       |  |  |

| i, ∆, +            | С                 | С | C | С        | С       |  |  |

NOTE

The letter C shows that a sign-anomaly contingency will occur.

If the absolute value of the dividend is greater than or equal to that of the divisor, then the absolute value of the quotient will be greater than, or equal to, 1. This condition will cause a fixed-point overflow contingency to occur. An attempt to divide by a zero divisor will also result in an overflow.

DIVIDE, FIXED-POINT EXTENDED DXE 31 36µs

T 31 AA BB MMMMM (A)  $\div$  (M)  $\longrightarrow$  A Remainder  $\longrightarrow$  A + 1

Divide the fixed-point fraction in fast register A by the fixed-point fraction in storage location M; store the quotient, with the correct sign, in fast register A. Store the remainder, with the sign of the dividend, in fast register A + 1. The contents of M are not changed.

The sign position of each operand must contain one of the characters (0), (-), or (.). The sign of the result is governed by the rules expressed in the following table:

| Sign of      |   | Sign of Wor |   |          | d in M  |  |  |

|--------------|---|-------------|---|----------|---------|--|--|

| Word in<br>A | 0 | -           | • | l thru 9 | i, ∆, + |  |  |

| 0            | 0 | -           | • | С        | С       |  |  |

| -            | - | 0           | • | с        | С       |  |  |

| •            | • | •           | • | С        | С       |  |  |

| l thru 9     | С | С           | С | С        | С       |  |  |

| i, ∆, +      | С | C           | С | С        | С       |  |  |

#### NOTE

The letter C shows that a sign-anomaly contingency will occur.

$Overflow\ may\ occur\ in\ this\ instruction\ under\ the\ same\ conditions\ as\ in\ the\ DX\ instruction.$

If the programmer wishes to continue the division process to obtain a double-precision result, he may divide the remainder by the original

divisor. For example, the pair of instructions . 31 04 00 02300 and . 31 05 00 02300 will store the double-precision quotient of (04) divided by (02300) in fast registers 04 and 05.

If the A address of the instruction is equal to Lim A, an error will occur.

ADD, FIXED-POINT, DOUBLE PRECISION AAX 05 12µs

T 05 AA BB MMMMM