## Univac<sup>®</sup> LARC PROCESSOR

## MAGNETIC TAPE SYNCHRONIZER SYSTEM

UNIVAC ENGINEERING CENTER . PHILADELPHIA

# Univac<sup>®</sup> LARC PROCESSOR

### MAGNETIC TAPE SYNCHRONIZER SYSTEM

UNIVAC ENGINEERING CENTER • PHILADELPHIA

JULY 1961

#### CONTENTS

| Heading        | Title                                           | Page         |

|----------------|-------------------------------------------------|--------------|

|                |                                                 |              |

|                | SECTION 1. INTRODUCTION                         |              |

| 1-1.           | Purpose and Scope of Manual                     | 1-1          |

| 1-2.           | Organization of the Tape Synchronizer<br>System | 1-3          |

| 1-3.           | Tape Compatibility Features                     | 1-4          |

| 1-4.           | Plastic and Metal Tape                          | 1-4          |

| 1-5.           | Code Translation                                | 15           |

| 1-6.           | Data Block Lengths                              | 1-5          |

| 1-7.           | Pulse Densities                                 | 1-5          |

| 1-8.           | Space Between Blocks                            | 1-5          |

| 1-9.           | Basic Operations                                | 1-5          |

| 1-10.<br>1-11. | Read Operation                                  | 1-5<br>1-7   |

| 1-11.          | Check-Read Operation                            | 1-7          |

| 1-13.          | Rewind Operations                               | 17           |

| 1-14.          | Simultaneous Operations                         | 17           |

| 1-15.          | Tape Synchronizer                               | 1-8          |

| 116.           | Uniservo Control Circuits                       | 1-8          |

| 1-17.          | Read-Write Control Circuits                     | 1-8          |

| 1-18.          | Read Circuits                                   | 18           |

| 1-19.          | Write Circuits                                  | 1-8          |

| 1-20.          | Tape Positioning Checker                        | 1-9          |

| 1-21.<br>1-22. | Shared Circuits                                 | 1-9<br>1-9   |

| 1-22.          | Timing Signal Generator                         | 1-9          |

| T-70.          |                                                 | 19           |

| 1-24.          | Larc-To-Univac Translator and Output            | 1 /          |

|                | Checker                                         | 1-10         |

| 1-25.          | Mode Decoder                                    | 1-10         |

| 1-26.          | Program Control                                 | 1-10         |

| 1-27.          | Illustration Conventions                        | 1-12         |

| 128.           | Block Diagrams                                  | 1-12         |

| 1-29.          | Timing Diagrams                                 | 1-12         |

| 1-30.          | Simplified Logic Diagrams                       | 1-12         |

| 1-31.<br>1-32. | Blocks                                          | 1-13<br>1-13 |

| 133.           | Signal Paths                                    | 1-13         |

| 1-34.          | Polarities                                      | 1-13         |

| 1-35.          | Circuit Restrictions                            | 1-13         |

| 1-36.          | Drawing Numbers                                 | 1-13         |

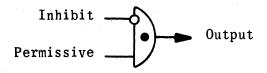

| 137.           | Inhibit                                         | 1-13         |

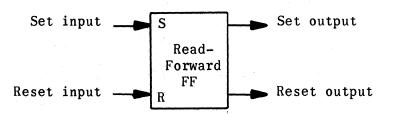

| 1-38.          | Flip-Flops                                      | 1-13         |

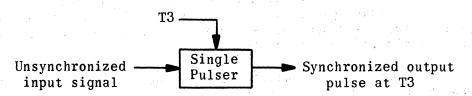

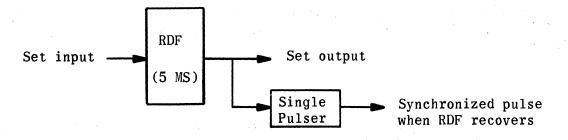

| 1-39.       Single Pulser                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Heading | Title                                     | Page                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------------------------------------|------------------------|

| 1-40.       Retriggerable Delay Flop       1-14         1-41.       Pulseformers       1-14         1-42.       Other Logic Circuit Elements       1-15         1-43.       Relays and Switches       1-15         SECTION 2. UNISERVO CONTROL CIRCUITS         2-1.       General Organization and Function of Control Circuits       2-1         2-2.       Over-all Operation       2-2         2-3.       Uniservo Tape Unit Selection       2-2         2-4.       Uniservo Tape Unit Availability       2-5         2-5.       Rewind and Rewind-Interlock Operations       2-6         2-6.       Read, Check-Read, and Write Operations       2-9         2-7.       Error Control       2-9         2-8.       Presetting Signal       2-10         2-9.       Select Control Circuits       2-12         2-11.       Uniservo-Control-Circuits-Available       2-12         2-12.       FIR and BIR Flip-Flop       2-12         2-13.       First-Block Flip-Flop       2-12         2-14.       Uniservo Selection-Completed Flip-         2-15.       Uniservo Interlock Flip-Flop       2-12         2-16.       Thyratron Control Circuits       2-15         2-17.                  |         |                                           |                        |

| 1-40.       Retriggerable Delay Flop       1-14         1-41.       Pulseformers       1-14         1-42.       Other Logic Circuit Elements       1-15         1-43.       Relays and Switches       1-15         SECTION 2. UNISERVO CONTROL CIRCUITS         2-1.       General Organization and Function of Control Circuits       2-1         2-2.       Over-all Operation       2-2         2-3.       Uniservo Tape Unit Selection       2-2         2-4.       Uniservo Tape Unit Availability       2-5         2-5.       Rewind and Rewind-Interlock Operations       2-6         2-6.       Read, Check-Read, and Write Operations       2-9         2-7.       Error Control       2-9         2-8.       Presetting Signal       2-10         2-9.       Select Control Circuits       2-11         2-10.       Status Control Circuits       2-12         2-11.       Uniservo-Control-Circuits-Available       2-12         2-12.       FIR and BIR Flip-Flops       2-12         2-13.       First-Block Flip-Flop       2-14         2-14.       Uniservo Selection-Completed Flip-         2-15.       Uniservo Control - Error Flip-Flop       2-15         2-17.              | 1-39.   | Single Pulser                             |                        |

| 1-41.       Pulseformers       1-14.         1-42.       Other Logic Circuit Elements       1-15         1-43.       Relays and Switches       1-15         SECTION 2. UNISERVO CONTROL CIRCUITS         2-1.       General Organization and Function of Control Circuits       2-1         2-2.       Over-all Operation       2-2         2-3.       Uniservo Tape Unit Selection       2-2         2-4.       Uniservo Tape Unit Availability       2-5         2-5.       Rewind and Rewind-Interlock Operations       2-9         2-6.       Read, Check-Read, and Write Operations       2-9         2-7.       Error Control       2-10         2-9.       Select Control Circuits       2-12         2-10.       Status Control Circuits       2-12         2-11.       Uniservo-Control-Circuits-Available       2-12         2-12.       FIR and BIR Flip-Flop       2-12         2-13.       First-Block Flip-Flop       2-14         2-14.       Uniservo-Available Flip-Flop       2-14         2-15.       Uniservo Interlock Flip-Flop       2-15         2-17.       Uniservo Control Circuits       2-17         2-18.       Thyratron Control Circuits       2-16                 | 1-40.   |                                           | 1-14                   |

| 1-42.       Other Logic Circuit Elements       1-15         1-43.       Relays and Switches       1-15         SECTION 2. UNISERVO CONTROL CIRCUITS         2-1.         General Organization and Function of Control Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1-41.   |                                           | 1-14                   |

| 1-43.       Relays and Switches 1-15         SECTION 2. UNISERVO CONTROL CIRCUITS         2-1.       General Organization and Function of Control Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |                                           | 1-15                   |

| 2-1.       General Organization and Function of Control Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1-43.   |                                           | 115                    |

| trol Circuits       2-1         2-2.       Over-all Operation       2-2         2-3.       Uniservo Tape Unit Selection       2-2         2-4.       Uniservo Tape Unit Availability       2-5         2-5.       Rewind and Rewind-Interlock Operations       2-6         2-6.       Read, Check-Read, and Write Operations       2-9         2-7.       Error Control       2-9         2-8.       Presetting Signal       2-10         2-9.       Select Control Circuits       2-10         2-10.       Status Control Circuits       2-10         2-11.       Uniservo-Control-Circuits-Available       2-11         2-10.       Status Control Circuits       2-12         2-11.       Uniservo-Control-Circuits-Available       2-12         2-12.       FIR and BIR Flip-Flops       2-12         2-13.       First-Block Flip-Flop       2-14         2-14.       Uniservo Selection-Completed Flip-       2-14         2-15.       Uniservo Control-Error Flip-Flop       2-15         2-17.       Uniservo Control Circuits       2-17         2-18.       Thyratron Control       2-18         2-20.       Write, Read, Forward, and Backward       2-18         2-21.                  |         | SECTION 2. UNISERVO CONTROL CIRCUITS      | en andre de<br>Regione |

| trol Circuits       2-1         2-2.       Over-all Operation       2-2         2-3.       Uniservo Tape Unit Selection       2-2         2-4.       Uniservo Tape Unit Availability       2-5         2-5.       Rewind and Rewind-Interlock Operations       2-6         2-6.       Read, Check-Read, and Write Operations       2-9         2-7.       Error Control       2-9         2-8.       Presetting Signal       2-10         2-9.       Select Control Circuits       2-10         2-10.       Status Control Circuits       2-10         2-11.       Uniservo-Control-Circuits-Available       2-12         2-12.       FIR and BIR Flip-Flops       2-12         2-13.       First-Block Flip-Flop       2-14         2-14.       Uniservo Available Flip-Flop       2-14         2-15.       Uniservo Interlock Flip-Flop       2-14         2-16.       Uniservo Control-Error Flip-Flop       2-15         2-17.       Uniservo Control Circuits       2-17         2-18.       Thyratron Control Circuits       2-17         2-19.       Operation Control       2-18         2-20.       Write, Read, Forward, and Backward       2-18         2-21.                            | 2-1.    | General Organization and Function of Con- |                        |

| 2-2.       Over-all Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         | trol Circuits                             | 2-1                    |

| 2-3.       Uniservo Tape Unit Selection 2-2         2-4.       Uniservo Tape Unit Availability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2-2.    |                                           | 2-2                    |

| 2-4.       Uniservo Tape Unit Availability 2-5         2-5.       Rewind and Rewind-Interlock Operations 2-6         2-6.       Read, Check-Read, and Write Operations 2-9         2-7.       Error Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |                                           |                        |

| 2-5.       Rewind and Rewind-Interlock Operations       2-6         2-6.       Read, Check-Read, and Write Operations       2-9         2-7.       Error Control       2-9         2-8.       Presetting Signal       2-10         2-9.       Select Control Circuits       2-10         2-9.       Select Control Circuits       2-11         2-10.       Status Control Circuits       2-12         2-11.       Uniservo-Control-Circuits-Available       2-12         2-12.       FIR and BIR Flip-Flops       2-12         2-13.       First-Block Flip-Flop       2-14         2-14.       Uniservo-Available Flip-Flop       2-14         2-15.       Uniservo Selection-Completed Flip-         Flop       2-15       2-14         2-16.       Uniservo Control-Error Flip-Flop       2-15         2-17.       Uniservo Control Circuits       2-16         2-19.       Operation Control       2-18         2-20.       Write, Read, Forward, and Backward       2-18         2-21.       Rewind and Rewind-Interlock Pickup       2-18         2-22.       Pickup Ending       2-19         2-23.       Centerdrive Control Circuits       2-20 <t< td=""><td></td><td></td><td></td></t<> |         |                                           |                        |

| 2-6.       Read, Check-Read, and Write Operations       2-9         2-7.       Error Control       2-9         2-8.       Presetting Signal       2-10         2-9.       Select Control Circuits       2-10         2-9.       Select Control Circuits       2-11         2-10.       Status Control Circuits       2-12         2-11.       Uniservo-Control-Circuits-Available       2-12         2-12.       FIR and BIR Flip-Flops       2-12         2-13.       First-Block Flip-Flop       2-14         2-14.       Uniservo-Available Flip-Flop       2-14         2-15.       Uniservo Selection-Completed Flip-         Flop       Flop       2-15         2-17.       Uniservo Control-Error Flip-Flop       2-15         2-18.       Thyratron Control Circuits       2-17         2-19.       Operation Control       2-18         2-20.       Write, Read, Forward, and Backward       2-18         2-21.       Rewind and Rewind-Interlock Pickup       2-18         2-22.       Pickup Ending       2-10         SECTION 3.       SHARED CIRCUITS       3-1         3-2.       Mode Decoder       3-1         3-3.       Tape Timing Signal Generator in the L                     |         |                                           |                        |

| 2-7.       Error Control       2-9         2-8.       Presetting Signal       2-10         2-9.       Select Control Circuits       2-10         2-10.       Status Control Circuits       2-11         2-10.       Status Control Circuits       2-12         2-11.       Uniservo-Control-Circuits-Available       2-12         2-12.       FIR and BIR Flip-Flops       2-12         2-13.       First-Block Flip-Flop       2-14         2-14.       Uniservo-Available Flip-Flop       2-14         2-15.       Uniservo Selection-Completed Flip-         Flop        2-15         2-17.       Uniservo Control Circuits       2-14         2-16.       Uniservo Control-Error Flip-Flop       2-15         2-17.       Uniservo Control Circuits       2-15         2-18.       Thyratron Control Circuits       2-17         2-19.       Operation Control       2-18         2-20.       Write, Read, Forward, and Backward       2-18         2-21.       Rewind and Rewind-Interlock Pickup       2-18         2-22.       Pickup Ending       2-19         2-23.       Centerdrive Control Circuits       2-20         SECTION 3.       SHARED CIRCUI                                   |         | -                                         |                        |

| 2-8.       Presetting Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |                                           |                        |

| 2-9.       Select Control Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |                                           |                        |

| 2-10.       Status Control Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |                                           |                        |

| 2-11.       Uniservo-Control-Circuits-Available<br>Flip-Flop       2-12         2-12.       FIR and BIR Flip-Flops       2-12         2-13.       First-Block Flip-Flop       2-14         2-14.       Uniservo-Available Flip-Flop       2-14         2-15.       Uniservo Selection-Completed Flip-<br>Flop       2-14         2-16.       Uniservo Control-Error Flip-Flop       2-15         2-17.       Uniservo Control-Error Flip-Flop       2-15         2-18.       Thyratron Control Circuits       2-17         2-19.       Operation Control       2-18         2-20.       Write, Read, Forward, and Backward       2-18         2-21.       Rewind and Rewind-Interlock Pickup       2-18         2-22.       Pickup       2-19         2-23.       Centerdrive Control Circuits       2-19         2-23.       Centerdrive Control Circuits       3-1         3-2.       Mode Decoder       3-1         3-3.       Tape Timing Signal Generator in the Larc<br>System, Serial 1       3-3                                                                                                                                                                                            |         |                                           |                        |

| Flip-Flop       2-12         2-12.       FIR and BIR Flip-Flops       2-12         2-13.       First-Block Flip-Flop       2-14         2-14.       Uniservo-Available Flip-Flop       2-14         2-15.       Uniservo Selection-Completed Flip-<br>Flop       2-14         2-16.       Uniservo Interlock Flip-Flop       2-15         2-17.       Uniservo Control-Error Flip-Flop       2-15         2-18.       Thyratron Control Circuits       2-18         2-20.       Write, Read, Forward, and Backward       2-18         2-21.       Rewind and Rewind-Interlock Pickup       2-18         2-21.       Pickup Ending       2-19         2-23.       Centerdrive Control Circuits       2-20         SECTION 3. SHARED CIRCUITS         3-1         3-1.       General       3-1         3-2.       Mode Decoder       3-1         3-3.       Tape Timing Signal Generator in the Larc<br>System, Serial 1       3-3                                                                                                                                                                                                                                                                    |         |                                           | <u> </u>               |

| 2-12.       FIR and BIR Flip-Flops                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2-11.   |                                           | 9_19                   |

| 2-13.       First-Block Flip-Flop       2-14         2-14.       Uniservo-Available Flip-Flop       2-14         2-15.       Uniservo Selection-Completed Flip-<br>Flop       2-14         2-16.       Uniservo Interlock Flip-Flop       2-15         2-17.       Uniservo Control-Error Flip-Flop       2-15         2-18.       Thyratron Control Circuits       2-17         2-19.       Operation Control       2-18         2-20.       Write, Read, Forward, and Backward       2-18         2-21.       Rewind and Rewind-Interlock Pickup       2-18         2-22.       Pickup Ending       2-19         2-23.       Centerdrive Control Circuits       2-20         SECTION 3.         SHARED CIRCUITS         3-1.       General       3-1         3-2.       Mode Decoder       3-1         3-3.       Tape Timing Signal Generator in the Larc       3-3                                                                                                                                                                                                                                                                                                                              | 0 10    |                                           |                        |

| 2-14.Uniservo-Available Flip-Flop 2-142-15.Uniservo Selection-Completed Flip-<br>Flop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |                                           |                        |

| 2-15.Uniservo Selection-Completed Flip-<br>Flop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |                                           |                        |

| Flop2-142-16.Uniservo Interlock Flip-Flop2-152-17.Uniservo Control-Error Flip-Flop2-152-18.Thyratron Control Circuits2-172-19.Operation Control2-182-20.Write, Read, Forward, and Backward2-182-21.Rewind and Rewind-Interlock Pickup2-182-22.Pickup Ending2-192-23.Centerdrive Control Circuits2-20SECTION 3.SHARED CIRCUITS3-1.General3-13-2.Mode Decoder3-13-3.Tape Timing Signal Generator in the Larc<br>System, Serial 13-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | - 7     |                                           | 2-14                   |

| 2-16.Uniservo Interlock Flip-Flop2-152-17.Uniservo Control-Error Flip-Flop2-152-18.Thyratron Control Circuits2-172-19.Operation Control2-182-20.Write, Read, Forward, and Backward<br>Pickup2-182-21.Rewind and Rewind-Interlock Pickup2-182-22.Pickup Ending2-192-23.Centerdrive Control Circuits2-20SECTION 3.SHARED CIRCUITS3-1.General3-13-2.Mode Decoder3-13-3.Tape Timing Signal Generator in the Larc<br>System, Serial 13-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2-15.   |                                           | 2.14                   |

| 2-17.Uniservo Control-Error Flip-Flop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |                                           |                        |

| 2-18.       Thyratron Control Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |                                           |                        |

| 2-19.       Operation Control       2-18         2-20.       Write, Read, Forward, and Backward       2-18         Pickup       2-18       2-18         2-21.       Rewind and Rewind-Interlock Pickup       2-18         2-22.       Pickup Ending       2-19         2-23.       Centerdrive Control Circuits       2-20         SECTION 3. SHARED CIRCUITS         3-1.       General       3-1         3-2.       Mode Decoder       3-1         3-3.       Tape Timing Signal Generator in the Larc       3-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |                                           |                        |

| 2-20.       Write, Read, Forward, and Backward<br>Pickup       2-18         2-21.       Rewind and Rewind-Interlock Pickup       2-18         2-22.       Pickup Ending       2-19         2-23.       Centerdrive Control Circuits       2-20         SECTION 3. SHARED CIRCUITS         3-1.       General       3-1         3-2.       Mode Decoder       3-1         3-3.       Tape Timing Signal Generator in the Larc       3-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |                                           |                        |

| Pickup       2-18       2-18         2-21.       Rewind and Rewind-Interlock Pickup       2-18         2-22.       Pickup Ending       2-19         2-23.       Centerdrive Control Circuits       2-20         SECTION 3. SHARED CIRCUITS         3-1.       General       3-1         3-2.       Mode Decoder       3-1         3-3.       Tape Timing Signal Generator in the Larc       3-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |                                           | 2-18                   |

| 2-21.       Rewind and Rewind-Interlock Pickup .       2-18         2-22.       Pickup Ending .       2-19         2-23.       Centerdrive Control Circuits .       2-20         SECTION 3. SHARED CIRCUITS         3-1.       General .       3-1         3-2.       Mode Decoder .       3-1         3-3.       Tape Timing Signal Generator in the Larc       3-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2-20.   |                                           | 0.10                   |

| 2-22.       Pickup Ending       2-19         2-23.       Centerdrive Control Circuits       2-20         SECTION 3.       SHARED CIRCUITS         3-1.       General       3-1         3-2.       Mode Decoder       3-1         3-3.       Tape Timing Signal Generator in the Larc       3-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0.0-    | Pickup                                    |                        |

| <ul> <li>2-23. Centerdrive Control Circuits</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |                                           |                        |

| SECTION 3. SHARED CIRCUITS<br>3-1. General                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |                                           |                        |

| 3-1.       General                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2-23.   | Centerdrive Control Circuits              | 2-20                   |

| 3-2.Mode Decoder3-13-3.Tape Timing Signal Generator in the Larc<br>System, Serial 13-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         | SECTION 3. SHARED CIRCUITS                |                        |

| 3-2.Mode Decoder3-13-3.Tape Timing Signal Generator in the Larc<br>System, Serial 13-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |                                           |                        |

| 3-3. Tape Timing Signal Generator in the Larc<br>System, Serial 1 3-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3-1.    |                                           |                        |

| System, Serial 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3-2.    | Mode Decoder                              | 3-1                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3-3.    | Tape Timing Signal Generator in the Larc  |                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |                                           |                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3-4.    | Tape Cycling Unit                         | 3-3                    |

| 3-5. Binary Counters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |                                           | 35                     |

| 3-6. Tape Cycling Unit Error Checking 3-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |                                           | 35                     |

| 3-7. Tape Timing Signal Generator in the Larc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |                                           |                        |

| System, Serial 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | - • •   |                                           | 37                     |

| 3-8. Tape Cycling Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3-8-    | Tape Cycling Unit                         |                        |

| 3-9. Binary Counters $3-7$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |                                           |                        |

iv

| <br>Heading | Title                                                                                                                      | Page         | - |

|-------------|----------------------------------------------------------------------------------------------------------------------------|--------------|---|

|             |                                                                                                                            |              |   |

| 3-10.       | Generation of Timing Signals T78RC                                                                                         |              |   |

|             | and T910RC                                                                                                                 | 3-7          |   |

| 3-11.       | Cycling Unit Error Checking                                                                                                | 3-8          |   |

| 3-12.       | Function of Timing Signal Generator Out-                                                                                   |              |   |

|             | puts                                                                                                                       | 38           |   |

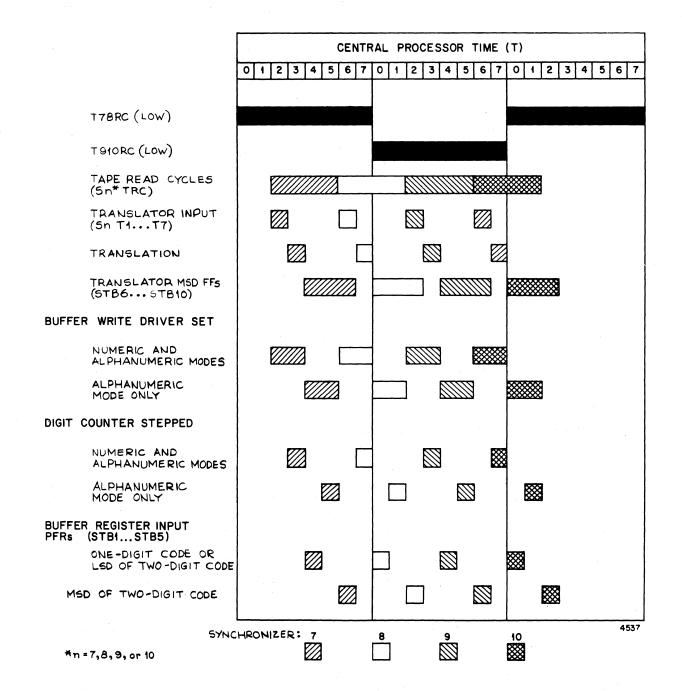

| 3-13.       | Tape Read Cycle Timing                                                                                                     | <b>3–</b> 10 |   |

| 3-14.       | Tape Write Cycle Timing                                                                                                    | <b>3–</b> 10 |   |

| 3-15.       | Clear Cycle Timing                                                                                                         | 311          |   |

| 3-16.       | Larc-To-Univac Translator and Output                                                                                       |              |   |

|             | Checker                                                                                                                    | 311          |   |

| 3-17.       | Translator Inputs                                                                                                          | 3-12         |   |

| 3-18.       | One-Digit-Translate Flip-Flop                                                                                              | 315          |   |

| 3-19.       | Decoding Gates                                                                                                             | 315          |   |

| 3-20.       | Encoding Buffers                                                                                                           | <b>3–</b> 16 |   |

| 3-21.       | Tape Output Odd-Even Checker                                                                                               | 317          |   |

| 3-22.       | Univac-To-Larc Translator and Input                                                                                        |              |   |

|             | Checker                                                                                                                    | 3-17         |   |

| 3-23.       | $Timing \dots \dots$ | 3-20         |   |

| 3-24.       | Auxiliary Decoding                                                                                                         | 3-21         |   |

| 3-25.       | MSD Translation                                                                                                            | 321          |   |

| 3-26.       | One-Digit and LSD Translation                                                                                              | 3-22         |   |

| 3-27.       | Error Checking                                                                                                             | 3-24         |   |

| 3-28.       | Input Odd-Even Checker                                                                                                     | 3-24         |   |

| 3-29.       | Untranslatable-Digit Checker                                                                                               | 3-25         |   |

| 3-30.       | Distribution of Error Signals .                                                                                            | 3-25         |   |

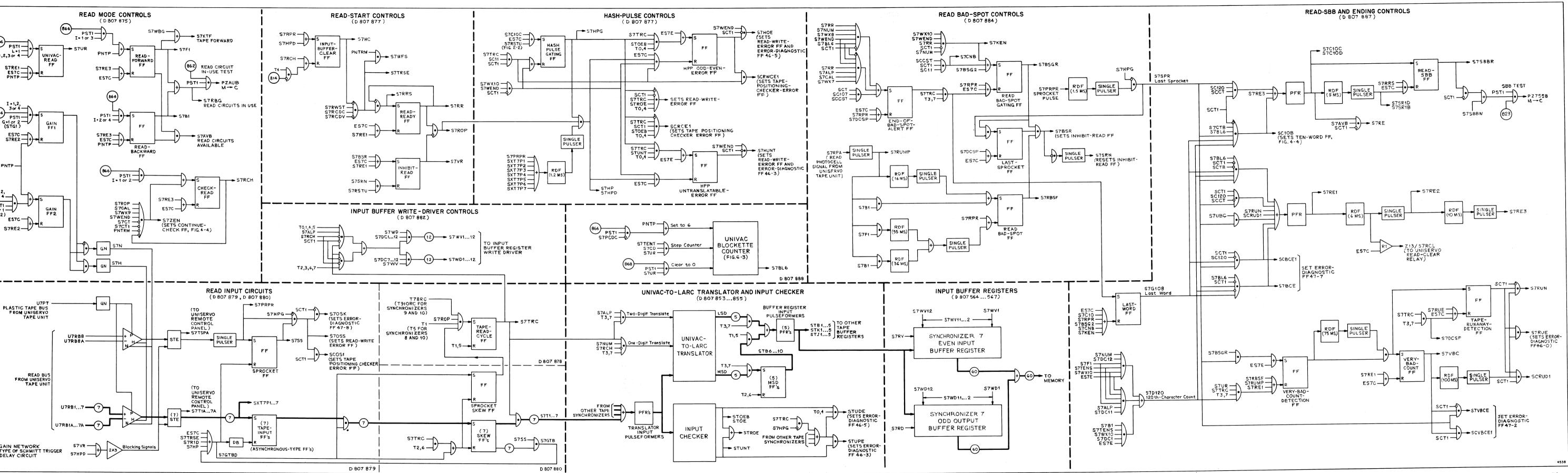

#### SECTION 4. READ-WRITE CONTROL CIRCUITS

| 4-1.  | General                           | 4-1  |

|-------|-----------------------------------|------|

| 4-2.  | Read-Write Mode Controls          | 4-2  |

| 4-3.  | Digit-Count Controls              | 4-2  |

| 4-4.  | Operating Sequences               | 4-3  |

| 4-5.  | Forward Numeric                   | 4-3  |

| 4-6.  | Backward Numeric                  | 4-3  |

| 4-7.  | Forward Alphanumeric              | 4-3  |

| 48.   | Backward Alphanumeric             | 4-4  |

| 4-9.  | Digit Counter Code                | 4-4  |

| 4-10. | Mode Control                      | 4-5  |

| 4-11. | Clearing                          | 4-6  |

| 4-12. | Stepping                          | 4-6  |

| 413.  | Word-End Detection                | 4-9  |

| 4-14. | Checking                          | 4-9  |

| 4-15. | Buffer Register Controls          | 4-10 |

| 4-16. | Memory-Request Flip-Flop          | 4-10 |

| 4-17. | Word-Driver Flip-Flop             | 4-11 |

| 4-18. | Word-Count Controls               | 4-12 |

| 4-19. | Word Counter                      | 4-12 |

| 4-20. | Alphanumeric-Compensate Flip-Flop | 4-14 |

| 4-21. | Read-Write Status Controls        | 4-15 |

| 4-22. | Availability Control              | 4-15 |

| 4-23. | Read-Write Start Control          | 4-16 |

|       |                                   |      |

v

|    | Heading | Title                              | Page |     |

|----|---------|------------------------------------|------|-----|

|    |         |                                    |      |     |

|    | 4-24.   | Ten-Word and SBB Control           | 4-16 |     |

|    | 4-25.   | Continue Control                   | 4-17 |     |

|    | 4-26.   | Read Operation                     | 4-18 |     |

|    | 4-27.   | Check-Read Operation               | 421  |     |

|    | 4-28.   | Write Operation                    | 4-21 |     |

|    | 4-29.   | Error Control                      | 4-22 |     |

|    |         |                                    |      |     |

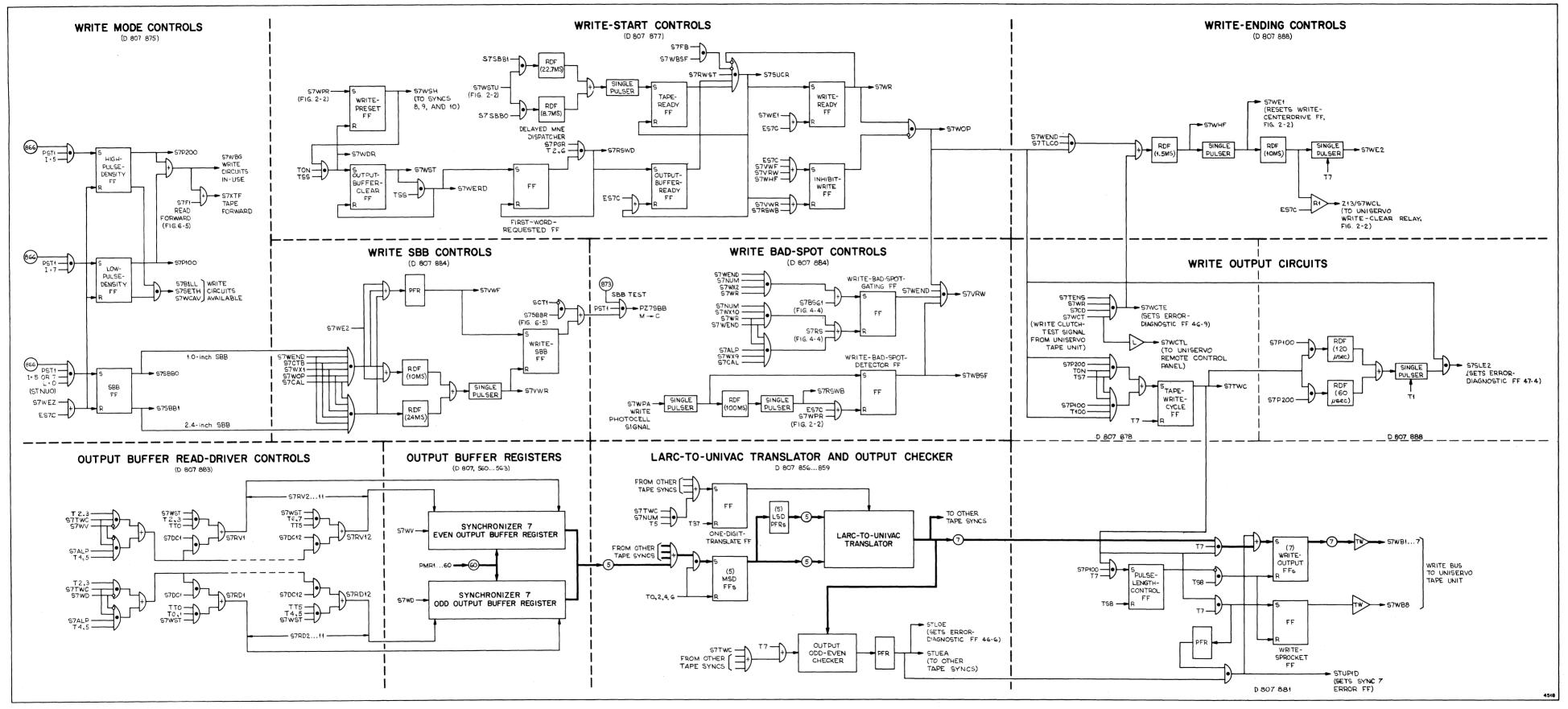

|    |         | SECTION 5. WRITE CIRCUITS          |      |     |

|    | 5-1.    | General                            | 5-1  |     |

|    | 5-2.    | Write Mode Controls                | 5-2  |     |

|    | 5-3.    | Pulse-Density Flip-Flops           | 5-2  |     |

|    | 5-4.    | SBB Flip-Flop                      | 5-2  | · . |

|    | 5-5.    | Wrïte-Start Controls               | 5-3  |     |

|    | 5-6.    | Output Buffer Ready Controls       | 5-3  |     |

|    | 5-7.    | Tape Ready Controls                | 5-4  |     |

|    | 5-8.    | Write Operate Controls             | 5-5  |     |

|    | 5-9.    | Output Buffer Read-Driver Controls | 5-6  |     |

|    | 5-10.   | Write Output Circuits              | 5⊶7  |     |

|    | 5-11.   | Larc System, Serial 1              | 5-7  |     |

| •. | 5-12.   | Larc System, Serial 2              | 5-11 |     |

|    | 5-13.   | Write SBB Controls                 | 5-11 |     |

|    | 5-14.   | Write Bad-Spot Controls            | 5-12 |     |

|    | 5-15.   | Write-Ending Controls              | 5-14 |     |

|    |         |                                    |      |     |

|    |         | SECTION 6. READ CIRCUITS           |      |     |

|    | 6-1.    | General                            | 6-1  |     |

|    | 6-2.    | Read Mode Controls                 | 6-2  |     |

|    | 6-3.    | Gain Flip-Flops                    | 6-2  |     |

|    | 6-4.    | Univac-Read Flip-Flop              | 6-2  |     |

|    | 6-5.    | Read Direction Flip-Flops          | 6-3  |     |

|    | 6-6.    | Check-Read Flip-Flop               | 6-3  |     |

|    | 6-7.    | Read-Start Controls                | 6-3  |     |

|    | 6-8.    | Read Input Circuits                | 6-4  |     |

|    | 6-9.    | Input Buffer Write-Driver Controls | 6-8  |     |

|    | 6-10.   | Hash-Pulse Controls                | 6-9  |     |

|    | 6-11.   | Hash-Pulse Period                  | 6-9  |     |

|    | 6-12.   | Hash-Pulse Detection               | 6-10 |     |

|    | 6-13.   | Hash-Pulse Deletion                | 6-10 |     |

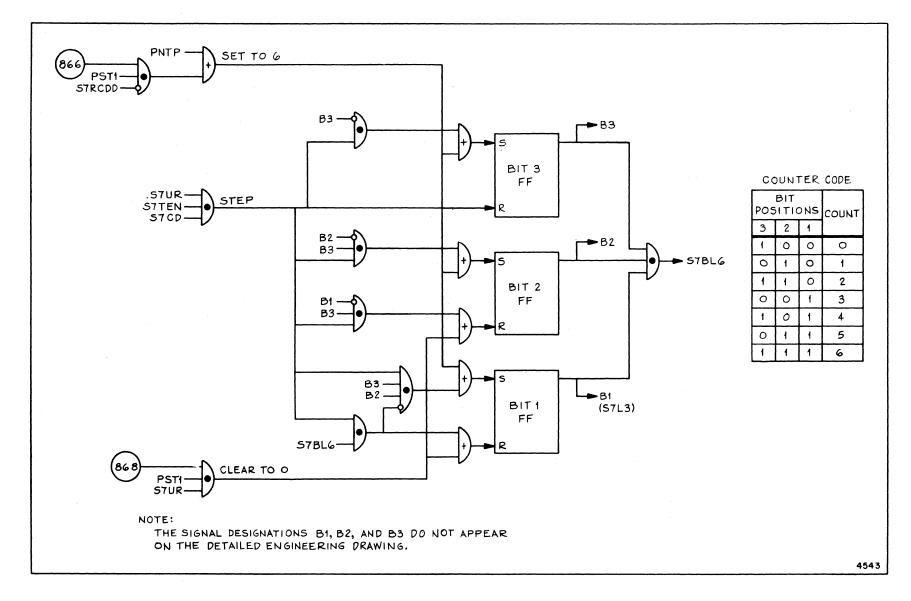

|    | 6-14.   | Univac Blockette Counter           | 6-11 |     |

|    | 6-15.   | Read Bad-Spot Controls             | 6-12 |     |

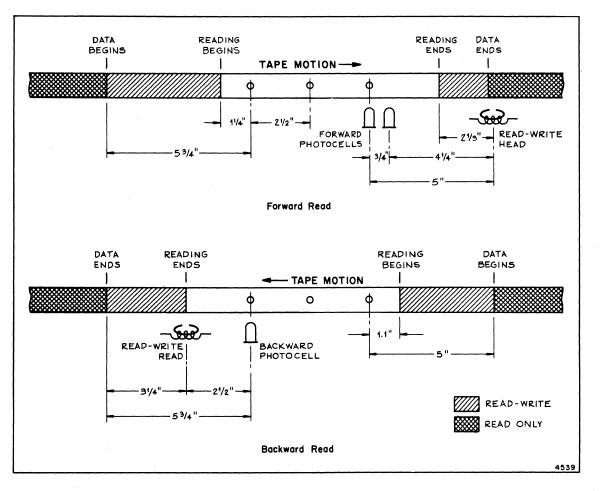

|    | 6-16.   | Forward Read                       | 6-14 |     |

|    | 6-17.   | Backward Read                      | 6-15 |     |

|    | 6-18.   | Read-SBB and Ending Controls       | 6-16 |     |

|    | 6-19.   | SBB Detection                      | 6-17 |     |

|    | 6-20.   | Read-Ending Sequence               | 6-17 |     |

Read-Ending Sequence . . . . . .

SBB Sequence

6-18

6-18

6-18

vi

6-21.

6-22.

6-23.

Title

#### Page

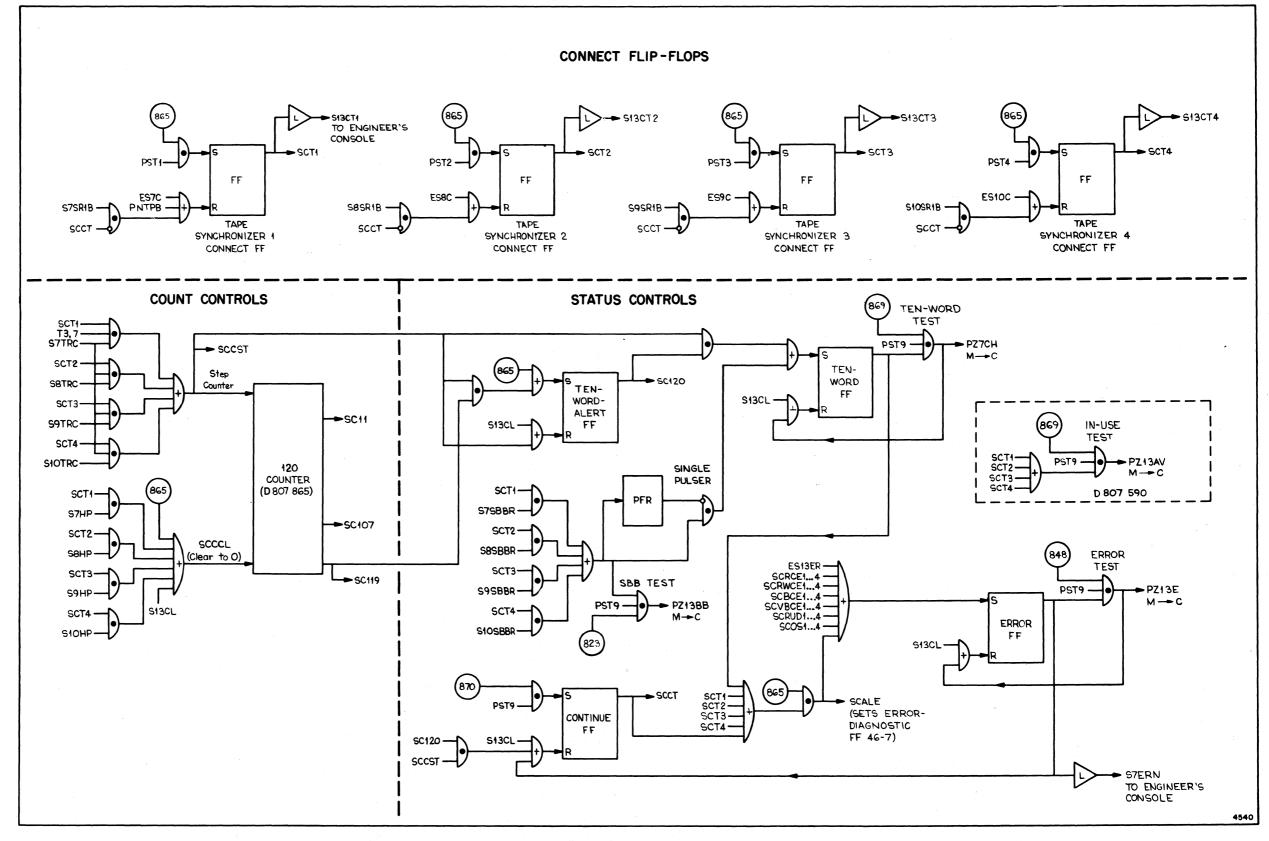

#### SECTION 7. TAPE POSITIONING CHECKER

| 7-1. | General                  | 7-1 |

|------|--------------------------|-----|

|      | Connect Flip-Flops       | 7-2 |

| 7-3. | Count Controls           | 7-2 |

| 7-4. | Status Controls          | 7-2 |

|      | Ten-Word-Alert Flip-Flop | 7-3 |

| 7-6. | Ten-Word Flip-Flop       | 7-3 |

| 7-7. | Continue Flip-Flop       | 7-4 |

| 78.  |                          | 74  |

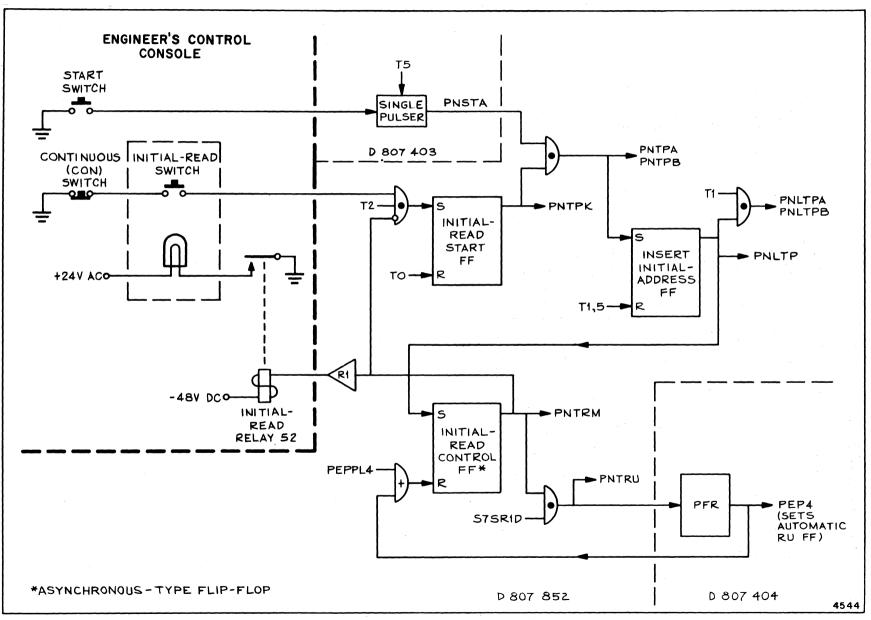

#### APPENDIX. INITIAL-READ CIRCUITS

| A-1. | General                          | • | • | ٠ | • | • | A-1 |

|------|----------------------------------|---|---|---|---|---|-----|

| A-2. | Initial-Read-Start Flip-Flop     |   |   |   |   |   | A⊶2 |

| A-3. | Insert-Initial-Address Flip-Flop | • | • | • | • | • | A-2 |

| A-4. | Initial-Read-Control Flip-Flop . | ٠ | • | ٠ | ٠ | ٠ | A-4 |

#### **ILLUSTRATIONS**

| <br>Figure | Title                                                               | Page |

|------------|---------------------------------------------------------------------|------|

| 1-1.       | Magnetic Tape Synchronizer System, Block                            |      |

|            | Diagram                                                             | 1-2  |

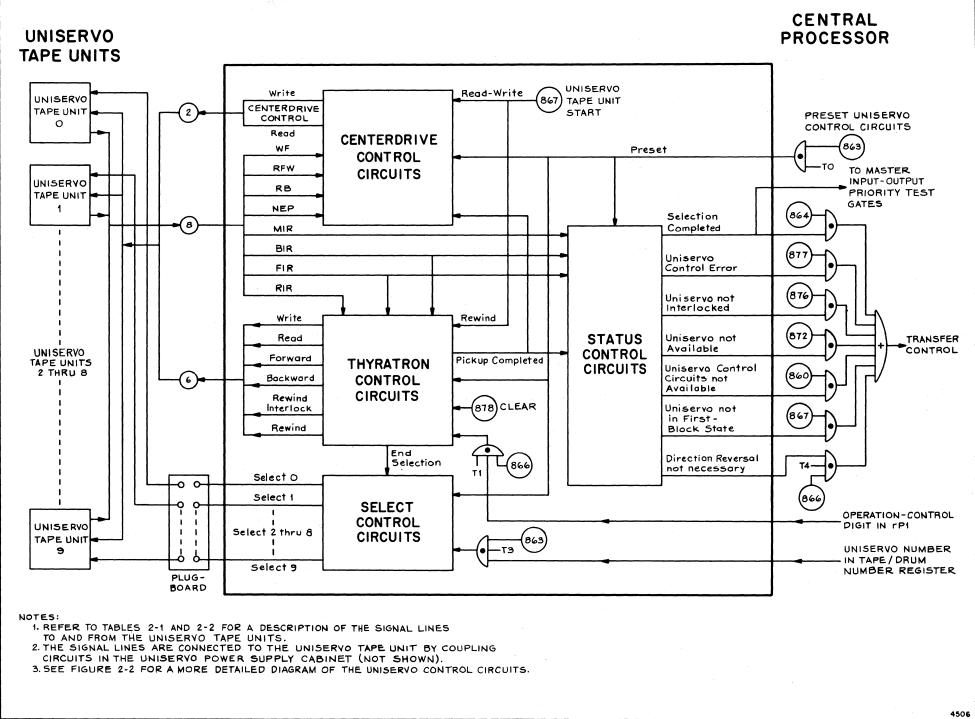

|            | Uniservo Control Circuits, Block Diagram .                          | 2-7  |

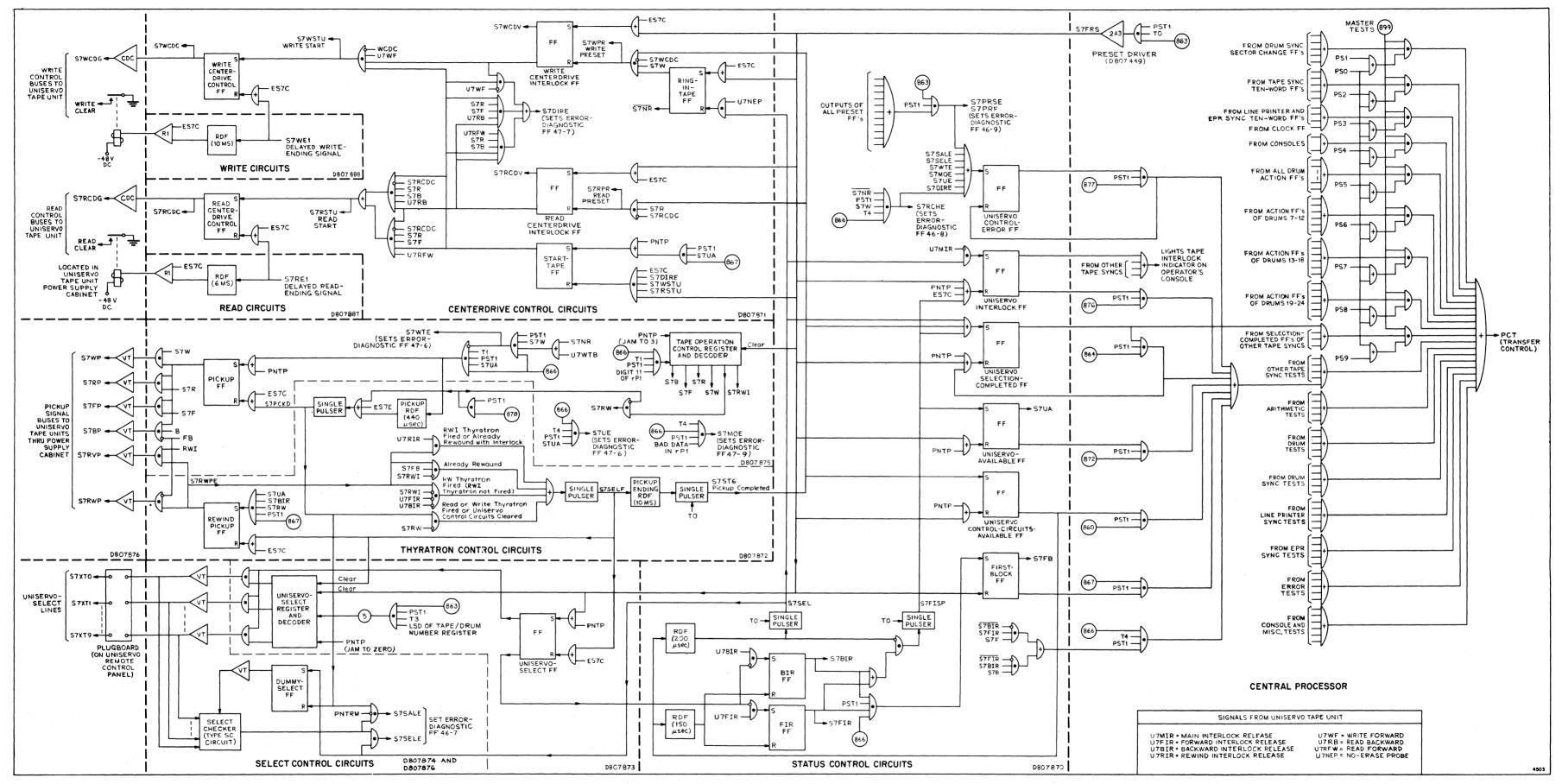

| 2-2.       | Uniservo Control Circuits, Simplified                               | 0.00 |

|            | Logic Diagram                                                       | 223  |

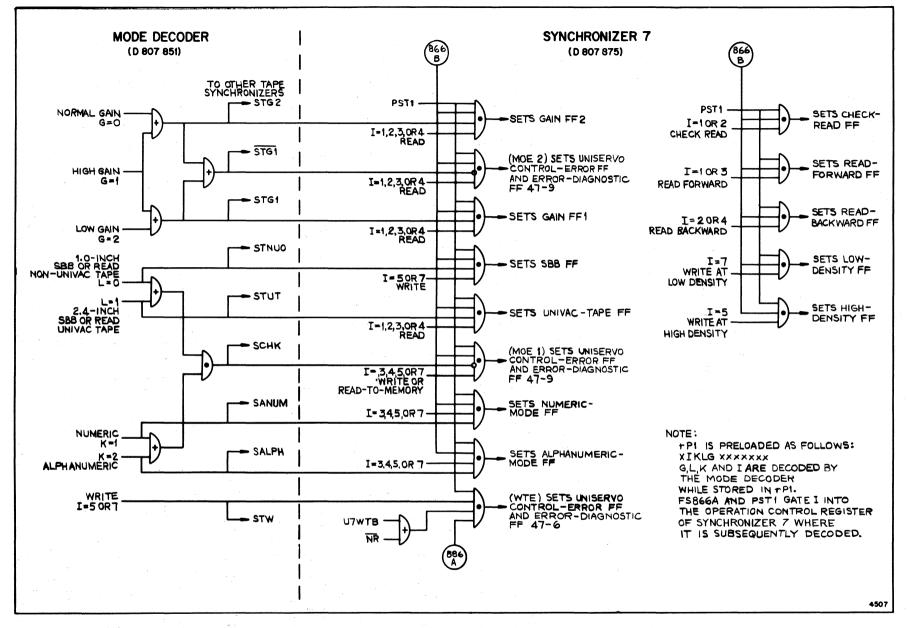

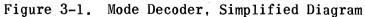

| 3-1.       | Mode Decoder, Simplified Diagram                                    | 3-2  |

| 3-2.       | Tape Timing Signal Generator in Larc                                |      |

|            | System, Serial 1 (D807 850)                                         | 34   |

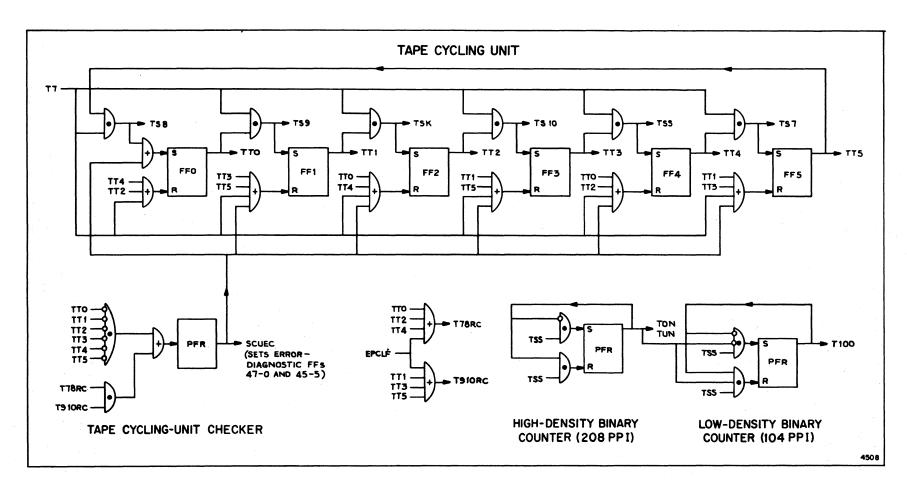

| 3-3.       | Tape Timing Signal Generator in Larc<br>System, Serial 2 (D807 950) | 3-6  |

| 3-4.       | Tape Timing Signal Generator Outputs                                | 5-0  |

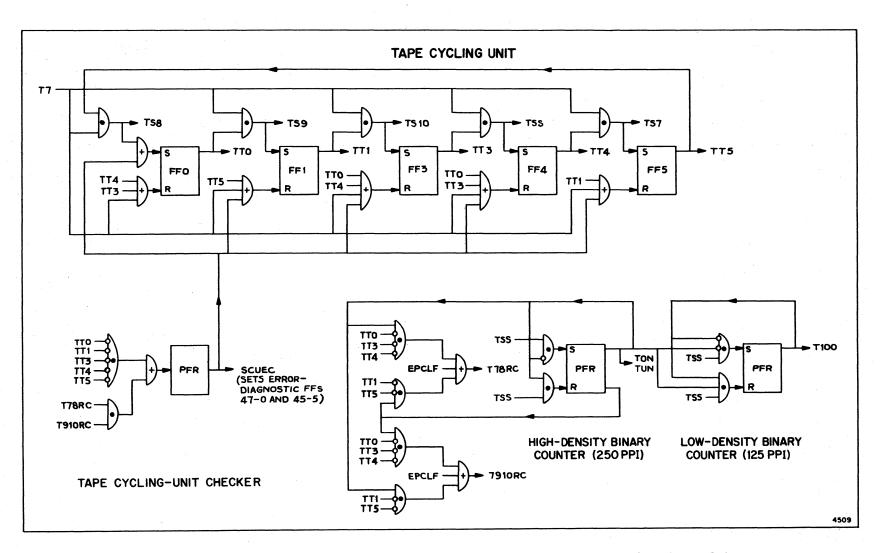

| U          | (Larc System, Serials 1 and 2)                                      | 39   |

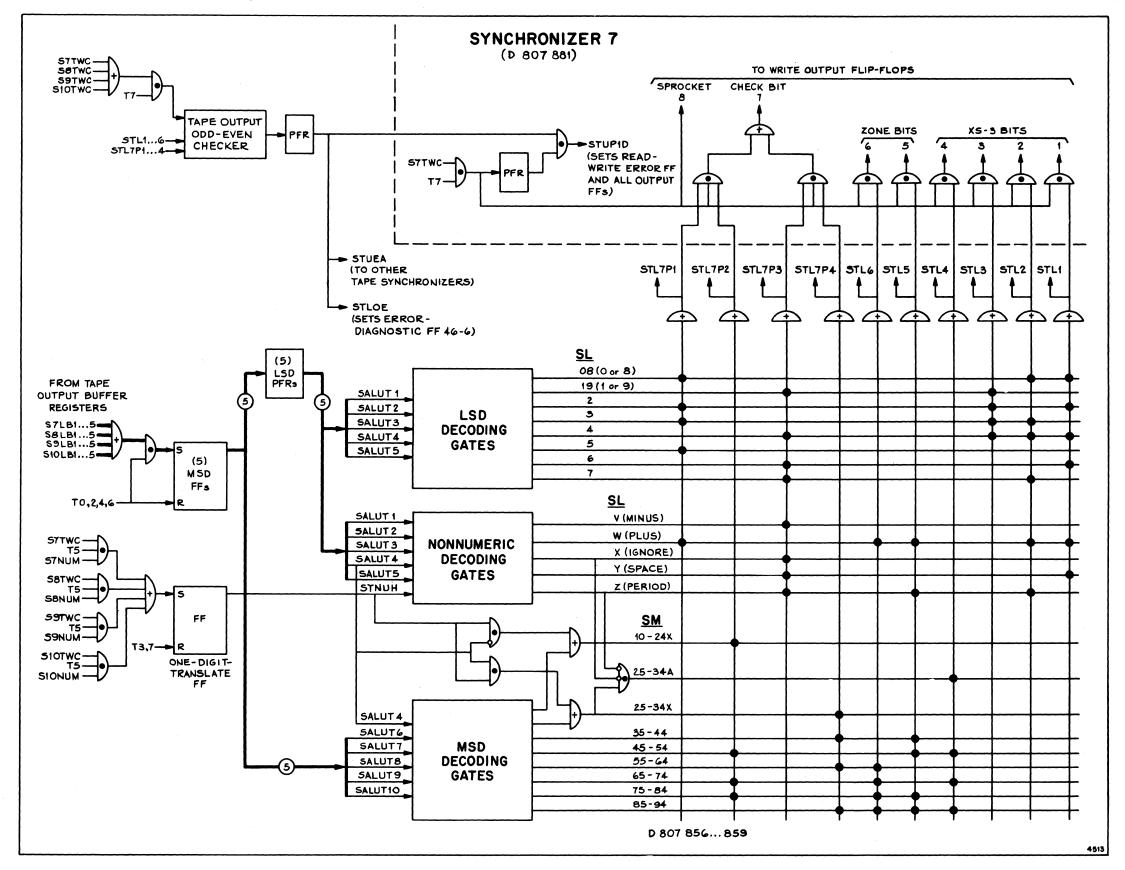

| 3-5.       | Larc-to-Univac Translator and Output                                |      |

| <b>-</b> . | Checker                                                             | 313  |

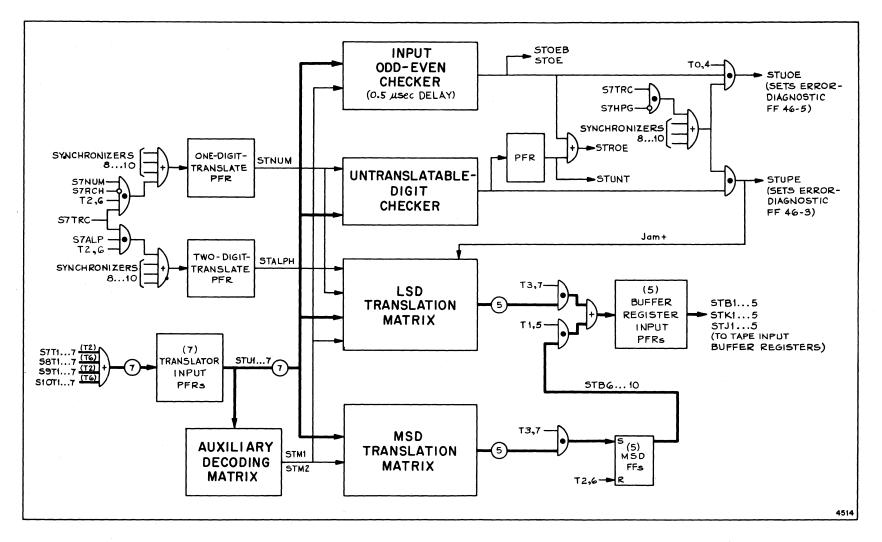

| 3-6.       | Univac-to-Larc Translator and Input                                 | 319  |

|            | Checker (D 807 853855)                                              | J-17 |

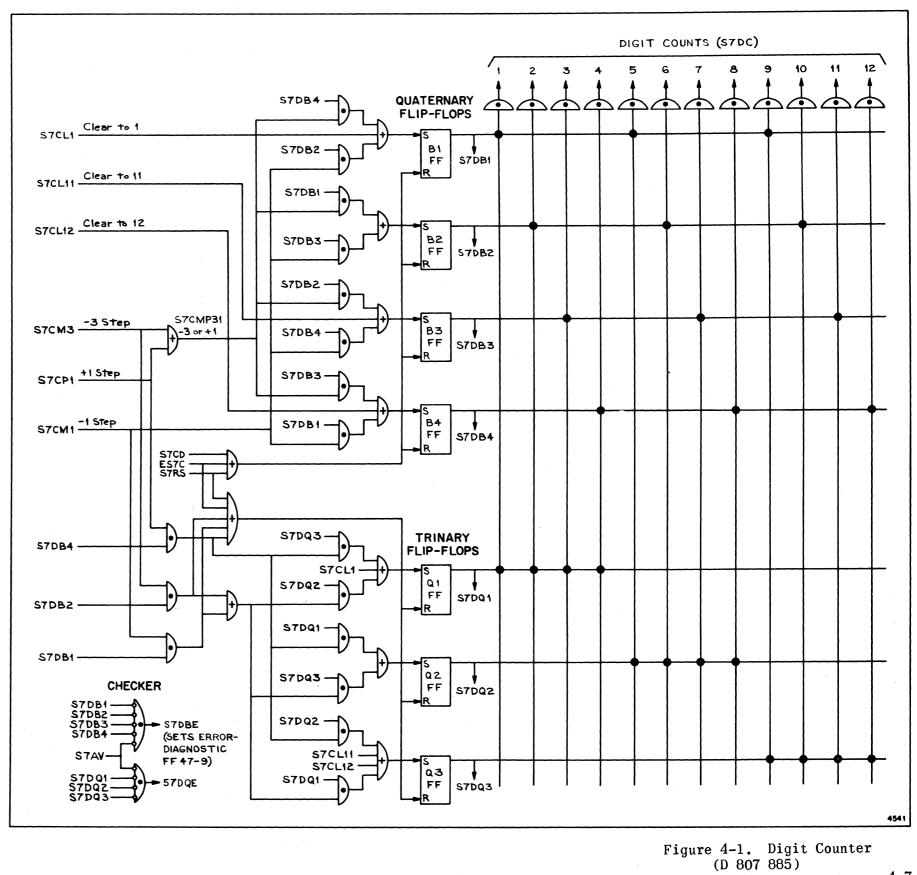

| 4-1.       | Digit Counter (D 807 885)                                           | 4-7  |

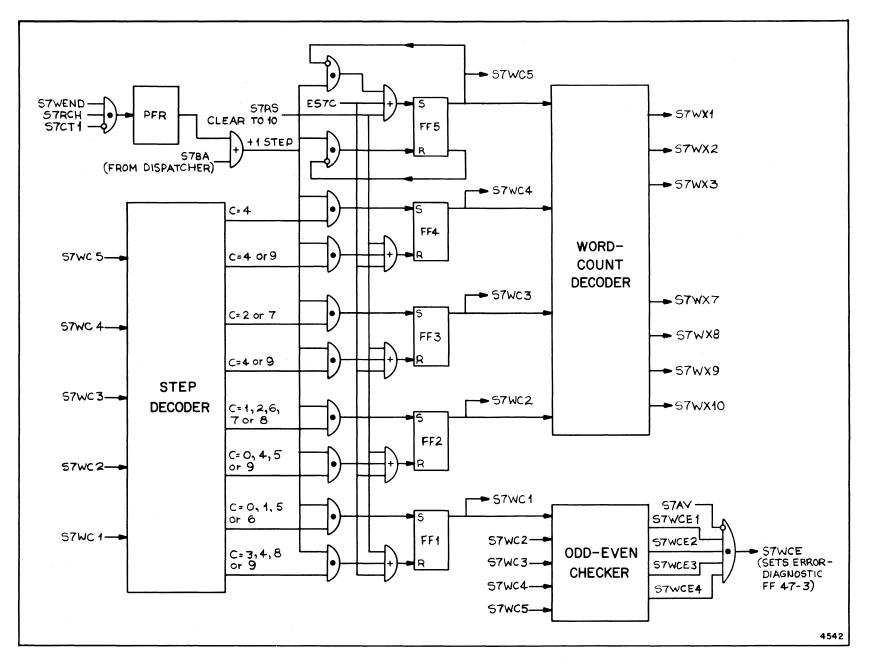

| 4-2.       | Word Counter (D 807 886)                                            | 4-13 |

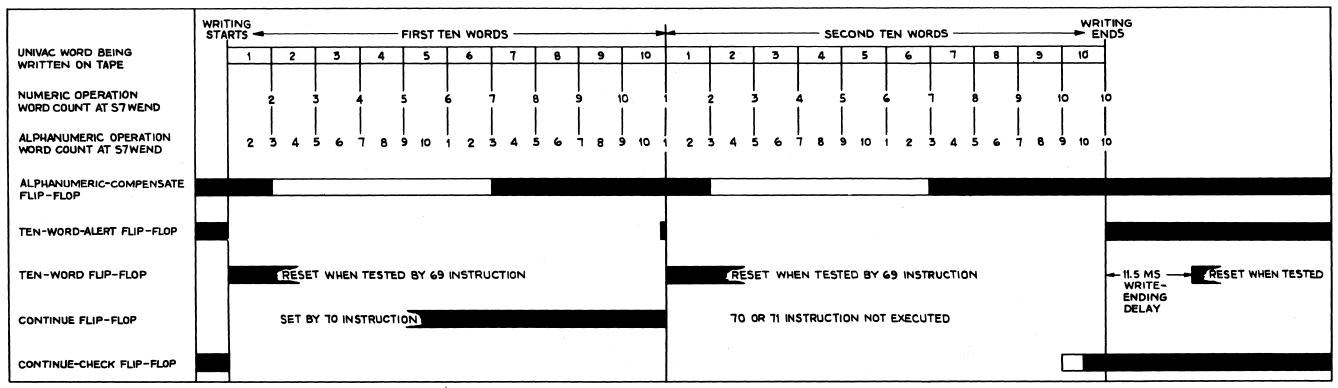

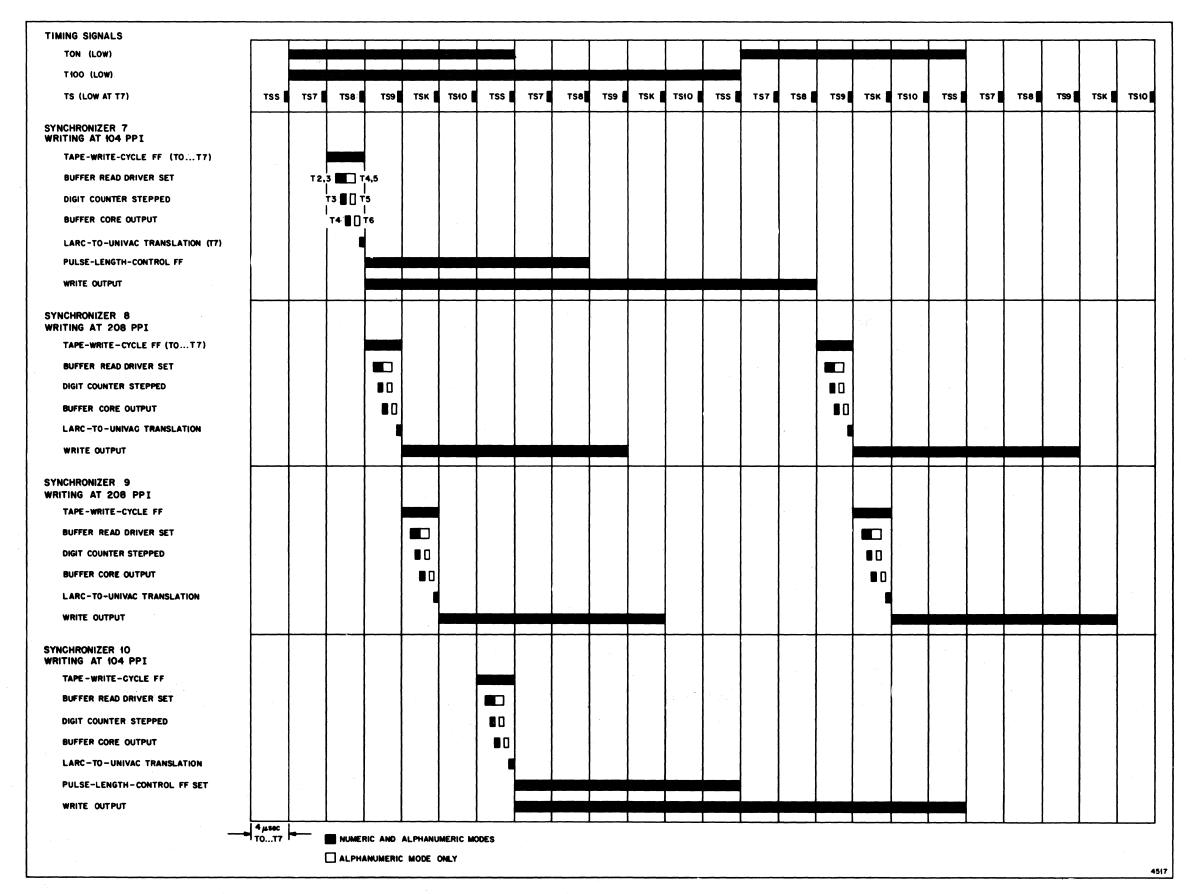

|            | Read and Write Word Timing                                          | 4-19 |

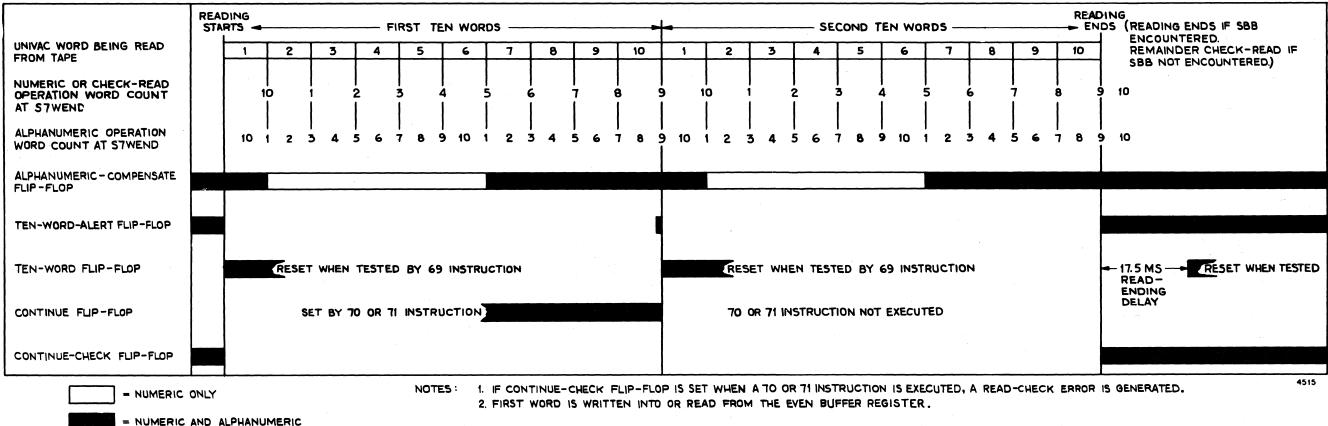

| 4-4.       | Read-Write Control Circuits                                         | 4-25 |

| Figure | Title                                                 | Page |

|--------|-------------------------------------------------------|------|

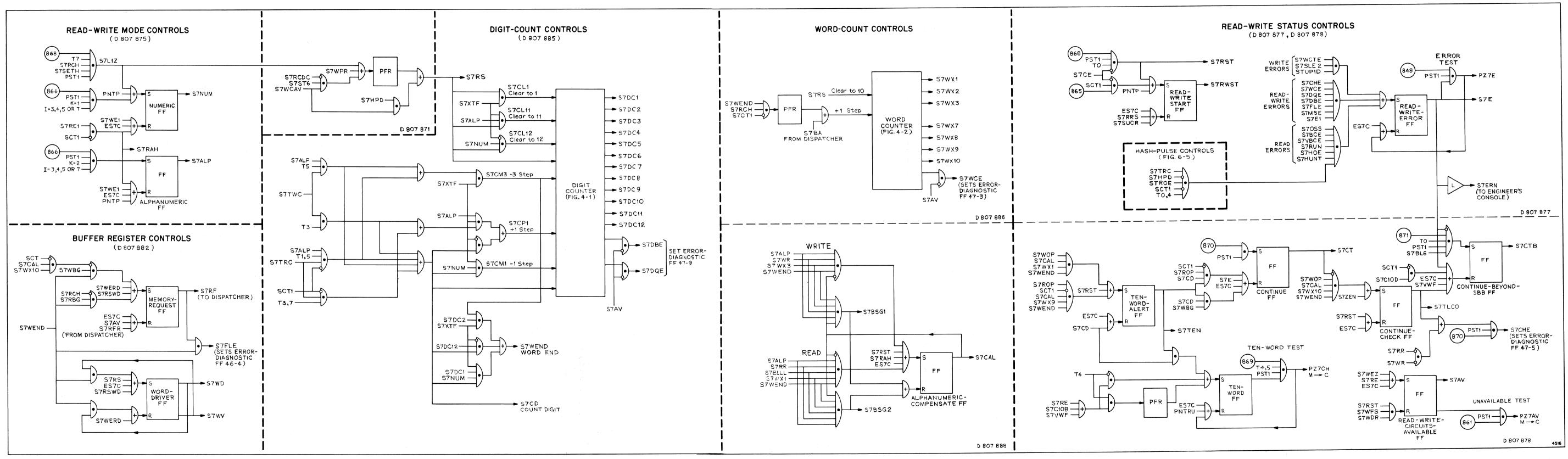

| 5-1.   | Write Cycle Timing, Larc System, Serial 1 .           | 5-9  |

| 5-2.   | Write Circuits, Simplified Logic Diagram .            | 5-17 |

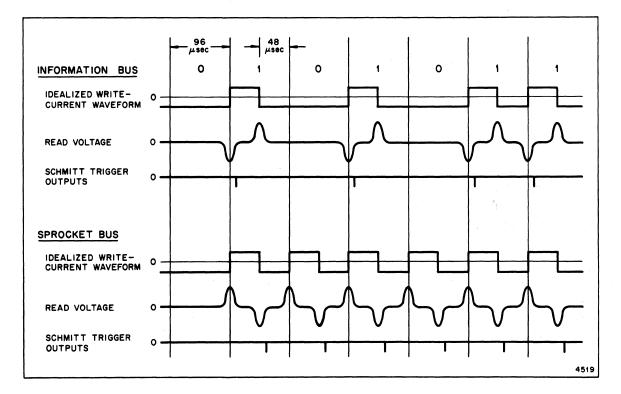

| 6-1.   | Read and Write Waveforms at 104 PPI                   | 6-5  |

| 6-2.   | Input Timing for Four Consecutive Read                |      |

|        | Cycles on Different Synchronizers                     | 6-7  |

| 6-3.   | Univac Blockette Counter (D 807 888)                  | 6-13 |

| 6-4.   | Tape Bad Spots                                        | 6-15 |

| 6-5.   | Read Circuits, Simplified Block Diagram               | 6-21 |

| 7-1.   | Tape Positioning Checker (D 807 865 and<br>D 807 866) | 7-7  |

| A-1.   | Initial-Read Circuits (D 807 852)                     | A-3  |

#### **TABLES**