SPERRY RAND

# UNIVAC

REAL-TIME SYSTEM

# PROCESSOR AND Storage

PROGRAMMERS REFERENCE This manual is published by the Univac Division of Sperry Rand Corporation in loose leaf format. This format provides a rapid and complete means of keeping recipients apprised of UNIVAC<sup>®</sup> Systems developments. The information presented herein may not reflect the current status of the programming effort. For the current status of the programming, contact your local Univac Representative.

The Univac Division will issue updating packages, utilizing primarily a page-for-page or unit replacement technique. Such issuance will provide notification of software changes and refinements. The Univac Division reserves the right to make such additions, corrections, and/or deletions as, in the judgment of the Univac Division, are required by the development of its Systems.

UNIVAC is a registered trademark of Sperry Rand Corporation.

This document was produced using UNADS. This system has been developed by the Applications Section of Product Support Operations as a research project for the Systems Programming Department of the Data Processing Division of Univac.

PAGE:

# **CONTENTS**

| CO | NTENTS                                                                                                                                                   | 1 to 3      |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 1. | INTRODUCTION                                                                                                                                             | 1-1 to 1-1  |

| 2. | MAIN STORAGE                                                                                                                                             | 2-1 to 2-2  |

| 3. | COMMAND/ARITHMETIC SECTION                                                                                                                               | 3-1 to 3-13 |

|    | 3.1. INTRODUCTION                                                                                                                                        | 3-1         |

|    | 3.2. REGISTERS                                                                                                                                           | 3-1         |

|    | 3.3. DESIGNATORS                                                                                                                                         | 3-2         |

|    | 3.4. INSTRUCTION TYPES AND FORMATS                                                                                                                       | 3-3         |

|    | 3.5. ADDRESSING                                                                                                                                          | 3-5         |

|    | 3.6. STORAGE PROTECTION (GUARD MODE LIMITS)                                                                                                              | 3-8         |

|    | 3.7. PRIVILEGED INSTRUCTIONS                                                                                                                             | 3-9         |

|    | 3.8. FLOATING POINT NUMBERS                                                                                                                              | 3-9         |

|    | 3.9. INTERRUPTS                                                                                                                                          | 3-10        |

|    | 3.9.1. Parity Fault Interrupts - Locations 21 <sub>8</sub> , 22 <sub>8</sub> , 27 <sub>8</sub> , 31 <sub>8</sub> , 32 <sub>8</sub> , and 40 <sub>8</sub> | 3-10        |

|    | 3.9.2. Supervisor Call Interrupt - Location 208                                                                                                          | 3-11        |

|    | 3.9.3. Day Clock Interrupt - Locations 23 <sub>8</sub> and 24 <sub>8</sub>                                                                               | 3-12        |

|    | 3.9.4. Real Time Clock Interrupt - Locations 25 <sub>8</sub> and 26 <sub>8</sub>                                                                         | 3-12        |

|    | 3.9.5. Guard Mode Interrupt - Location 30                                                                                                                | 3-12        |

3.9.5. Guard Mode Interrupt - Location 30<sub>8</sub> 3.9.6. Power Loss Interrupt - Location 33<sub>6</sub>

| 3.9.6.  | Power Loss Interrupt - Location 338                         | 3-12 |

|---------|-------------------------------------------------------------|------|

| 3.9.7.  | Floating Floating Point Underflow Interrupt - Location 348  | 3-12 |

| 3.9.8.  | Floating Point Overflow Interrupt - Location 358            | 3-12 |

| 3.9.9.  | Interrupt Lockout Timeout Interrupt - Location 418          | 3-12 |

| 3.9.10. | ISI External Interrupts - Locations 1408-1778 and 2408-2778 | 3-13 |

| 3.9.11. | ISI Internal Interrupts - Locations 1008-1378 and 2008-2378 | 3-13 |

3.9.11. ISI Internal Interrupts - Locations  $100_8$ -137 $_8$  and  $200_8$ -237 $_8$  3.9.12. ESI Interrupts - Locations  $36_8$  and  $37_8$ 3-13

#### 4. INPUT/OUTPUT SECTION

4-1 to 4-21

| 4.1.         | INTRODUCTION           | 4-1 |

|--------------|------------------------|-----|

| 4.2.         | GENERAL DESCRIPTION    | 4-1 |

| 4.3.         | FUNCTIONAL OPERATION   | 4-1 |

| 4.4.         | CHANNEL OPERATION      | 4-3 |

| 4.5.         | I/O CHANNEL PRIORITY   | 4-3 |

| 4.6.         | INPUT/OUTPUT INTERFACE | 4-4 |

| 4.7.         | IOM RESPONSE TIME      | 4-5 |

| <b>4</b> .8. | OPERATING MODES        | 4-5 |

| UP <b>-</b> 7627 |    | 418-III PROCESSOR AND STORAGE                                                                                           |                       | Contents      |

|------------------|----|-------------------------------------------------------------------------------------------------------------------------|-----------------------|---------------|

|                  |    |                                                                                                                         |                       |               |

|                  |    |                                                                                                                         |                       |               |

|                  |    | 4.8.1. Internally Specified Indexing (ISI)                                                                              |                       | 4-6           |

|                  |    | 4.8.1.1. Programmed Activation of an I/O Channel - ISI N                                                                | Mode                  | 4-6           |

|                  |    | 4.8.1.2. ISI Buffer Control Word Formats                                                                                |                       | 4-7           |

|                  |    | 4.8.1.3. ISI Input/Output Activity                                                                                      |                       | 4-9           |

|                  |    | 4.8.1.4. ISI External Interrupt                                                                                         |                       | 4-10          |

|                  |    | 4.8.1.5. ISI Monitor Interrupts                                                                                         |                       | 4-10          |

|                  |    | 4.8.2. Externally Specified Indexing (ESI)                                                                              |                       | 4-10          |

|                  |    | 4.8.2.1. Programmed Activation of an I/O Channel - ESI I                                                                | Mode                  | 4-13          |

|                  |    | 4.8.2.2. ESI Buffer Control Word Formats                                                                                |                       | 4-13          |

|                  |    | 4.8.2.3. Terminal Buffer Condition Halfword                                                                             |                       | 4-16          |

|                  |    | 4.8.2.4. Terminal Buffer Condition Fullword                                                                             | <b>( 0</b> ) <b>(</b> | 4-17          |

|                  |    | 4.8.2.5. Terminal Condition Fullword or Halfword With Bu<br>4.8.2.6. ESI Buffer Termination Interrupt and External Inte | -                     | 4-17          |

|                  |    | 4.8.2.6. ESI Buffer Termination Interrupt and External Inte<br>4.8.2.7. ESI Interrupt Table Pointer                     | errupt rabiling       | 4-18<br>4-19  |

|                  |    | 4.8.2.7. ESI Interrupt                                                                                                  |                       | 4-19          |

|                  |    | 4.8.2.9. ESI Parity Error Handling                                                                                      |                       | 4-20          |

|                  |    | 4.8.2.10. ESI External Interrupt Word Transfers                                                                         |                       | 4-21          |

|                  |    | 4.9. REAL TIME CLOCK                                                                                                    |                       | 4-21          |

|                  |    | 4.10. INITIAL LOAD                                                                                                      |                       | 4-21          |

|                  |    |                                                                                                                         |                       |               |

|                  | 5. | OPERATORS CONSOLE                                                                                                       |                       | 5-1 to 5-3    |

|                  |    | 5.1 GENERAL                                                                                                             |                       | 5-1           |

|                  |    | 5.2. DAY CLOCK                                                                                                          |                       | 5-2           |

|                  |    |                                                                                                                         |                       |               |

|                  |    | APPENDICES                                                                                                              |                       |               |

|                  | Α. | NORMAL AND COMPATIBLE CHANNELS                                                                                          |                       | A-1 to A-3    |

|                  |    |                                                                                                                         |                       |               |

|                  | В. | ISI INPUT, OUTPUT, AND FUNCTION MODE CHAN                                                                               | NEL ACTIVITY          | B-1 to B-3    |

|                  |    |                                                                                                                         |                       | · · · · · · · |

|                  |    |                                                                                                                         |                       |               |

|                  | C. | FORMAT OF RESERVED LOCATIONS                                                                                            |                       | C-1 to C-1    |

|                  |    |                                                                                                                         |                       |               |

|                  |    |                                                                                                                         |                       |               |

|                  | D. | INSTRUCTION REPERTOIRE SUMMARY                                                                                          |                       | D-1 to D-7    |

|                  |    |                                                                                                                         |                       |               |

|                  |    |                                                                                                                         |                       |               |

|                  | Ε. | MAINTENANCE PANEL                                                                                                       |                       | E-1 to E-4    |

|                  |    |                                                                                                                         |                       | ·             |

|                  |    |                                                                                                                         |                       |               |

PAGE:

Contents

-

PAGE:

## FIGURES

| 2-1.         | Main Storage Allocation                  | 2-1  |

|--------------|------------------------------------------|------|

| 3-1.         | Type I Instruction Addressing Techniques | 3-7  |

| 4-1.         | One I/O Channel                          | 4-4  |

| <b>4-2</b> . | ESI Data Transmission                    | 4-12 |

#### TABLES

| 4-1. | I/O Channel Control Signals                        | 4-5 |

|------|----------------------------------------------------|-----|

| 4-2. | Time Between Subsystem Request and IOM Acknowledge | 4-5 |

| 5-1. | Console Signal Code Reference                      | 5-2 |

| A-1. | Normal Channel Data Transfer Rates                 | A-2 |

| A-2. | Compatible Channel Data Transfer Rates             | A-3 |

PAGE:

# **1. INTRODUCTION**

This document describes the three individual hardware components of the UNIVAC 418-III Real-Time System. These hardware sections and the order of their presentation are as follows:

- Main Storage

- Command/Arithmetic Section

- Input/Output Section

Section 2 of this manual describes main storage and discusses the interfacing between it, the Command/Arithmetic, and the Input/Output sections. In Section 3 the Command/Arithmetic Section is discussed in more detail, and Section 4 describes the Input/Output Section.

1

# 2. MAIN STORAGE

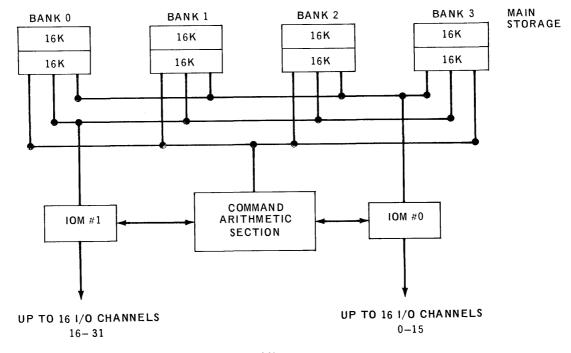

Main storage is divided into four banks each consisting of one or two modules. Each module has four bays, each containing 4096 eighteen-bit words of storage. The UNIVAC 418-III main storage is divided into 18-bit addressable words. Up to 131,072 words (4 banks, 2 modules each) may be addressed by the Command/Arithmetic section. Each storage bank has three access paths, one to the Command/Arithmetic (C/A) Section and one to each Input/Output Module (IOM). In this manner, parallel access to storage bank. Regardless of the physical distribution of various modules, addressing is always continuous.

Figure 2-1 illustrates the parallel paths available to each bank. If any bank is being accessed by two or more of the access paths, only one at a time is honored.

Figure 2-1. Main Storage Allocation

SECTION:

2

2

PAGE:

In addition to the ferrite core storage, the UNIVAC 418-III System uses several high speed integrated general registers (IGR) located in the IOM's. Read/restore cycle time for main storage is 750 nanoseconds, and for integrated storage, 186 nanoseconds. These IGR registers are assigned fixed addresses which duplicate the corresponding core storage addresses. Locations 300<sub>8</sub> through 477<sub>8</sub> are the corresponding IGR and core storage locations. The C/A section accesses the IGR storage whenever an address in this range is specified, whereas the I/O sections address the corresponding core storage locations.

PAGE

# **3. COMMAND/ARITHMETIC SECTION**

## 3 1. INTRODUCTION

The Command/Arithmetic Section (C/A section) consists of the hardware necessary to enable certain functions to be performed whenever it is given control. These functions are obtained from main storage as are the necessary operands.

In addition to having access to main storage, the C/A section has certain storage registers and designators which allow it to perform its various functions. These are described only to the extent necessary for the programmer to understand how the hardware works.

Appendix D summarizes the instruction repertoire for the UNIVAC 418-III System. For a detailed description of each function, refer to UNIVAC 418-III Assembler, Programmers Reference Manual, UP-7599 (current version).

### 3.2. REGISTERS

The following is a brief description of the registers of the C/A section.

• Instruction Address Register

The Instruction Address Register (IAR) contains the address of the next instruction to be performed. The IAR is not program accessible.

• Arithmetic Accumulators

There are two arithmetic accumulators, A Upper (AU) and A Lower (AL), which can be operated upon under program control. Each accumulator is 18 bits long: they can be used jointly as one 36-bit accumulator (A register).

• Index Registers

Eight Index Registers are available for use (only one at a time) as address modifiers. The index registers are program accessible and are storage locations  $1_8$  through  $10_8$ .

• B Register

The B Register contains the contents of the active index register and is used by the hardware whenever an indexed instruction is executed. The B Register is not program accessible.

• Index Register Pointer

The Index Register Pointer contains the main storage address of the currently active index register.

PAGE:

Special Register

The Special Register (SR) is used to specify interbay (4K storage segment) addressing. The SR contents are under program control. (See 3.5 for description of SR operation.)

• K0 Register

The K0 register is used for internal purposes and is not accessible to programmed instructions; it may be inspected from the maintenance panel. During the execution of a shift instruction, K0 contains the shift count.

• Z Register

The Z register is used for internal purposes and is not accessible to programmed instructions; it may be inspected from the maintenance panel. For most instructions, Z contains the operand address.

• Storage Limits Registers

Two 9-bit registers, called Storage Limits Upper and Storage Limits Lower, are used to contain the addresses of the upper and lower boundaries of an area which is protected by the Guard Mode. An area so placed under Guard Mode becomes the only area in which the C/A section may cause the contents of any location to be changed. The Storage Limits Registers are loaded as a result of the LGM instruction.

## 3.3. DESIGNATORS

The following is a description of the designators of the C/A section.

• Compare Designator

The Compare Designator is a bi-stable, three-stage register whose state is determined by the execution of any of the COMPARE instructions (f = 02, 03, 06, 07). The results of the COMPARE instructions are recorded by the Compare Designator as follows:

- The COMPARE stage is set upon the execution of any of the COMPARE instructions.

- The LESS THAN stage is set if a COMPARE instructions finds (AL) less than the contents of the addressed storage location (f = 02, 03), or [(AU)[AND](AL)] less than the logical product of (AU) and the contents of the address storage location (f = 06, 07).

- The EQUALS stage is set if a COMPARE instruction finds (AL) equal to the contents of the addressed storage location (f = 02, 03) or [(AU)[AND(AL)] equal to the logical product of (AU) and the contents of the addressed storage location (f = 06, 07).

The COMPARE stage is cleared by the execution of any instruction other than the arithmetic JUMP instructions (f = 60 through 67). Thus, if the results of a COMPARE instruction are to be successfully tested, it must be immediately followed by one or more of the JUMP instructions.

PAGE:

When the COMPARE stage of the Compare Designator is set, or while processing a COMPARE instruction, all interrupts are locked out to avoid the possibility of inadvertently clearing the COMPARE stage. It should be noted that the arithmetic JUMP instructions have significantly different operations if executed when the COMPARE stage is not set.

• Borrow Designator

The Borrow Designator is a bi-stable, single-stage element whose state is determined by the execution of either a double-length ADD instruction (f = 20, 21), or a double-length SUBTRACT instruction (f = 22, 23). If an end-around borrow would be required during the execution of either of these instructions, it is inhibited and the Borrow Designator is set. The Borrow Designator remains set until the subsequent execution of another double-length ADD or double-length SUBTRACT instruction.

The condition of the Borrow Designator may be tested by the TEST NO BORROW instruction (f = 5051). When the Borrow Designator is set, interrupts are not locked out.

• Overflow Designator

The Overflow Designator is a bi-stable, single-stage element which is set when an overflow occurs during the execution of any of the following instructions:

ADD AL (f = 14, 15) SUBTRACT AL (f = 16, 17) ADD A (f = 20, 21) SUBTRACT A (f = 22, 23) DIVIDE A (f = 26, 27) ROUND A (f = 5060) ADD AL PLUS CONSTANT (f = 71) FLOATING POINT DIVIDE (f = 5005)

The state of the Overflow Designator is tested by either the TEST OVERFLOW instruction (f = 5052) or the TEST NO OVERFLOW instruction (f = 5053). The execution of either instruction automatically clears the Borrow Designator. When the Overflow Designator is set, interrupts are not locked out.

• Guard Mode Designator

The Guard Mode Designator is a bi-stable, single-stage element set as a result of the LGM (f = 5065) instruction. When the Guard Mode Designator is set by the LGM instruction, any write reference to the storage area outside of the limits set, with the exception of addresses  $00_8$  through  $17_8$ , will cause a Guard Mode Interrupt. If a privileged instruction is attempted while in Guard Mode, the function will be inhibited and a Guard Mode Interrupt will be generated. The generation of any interrupt will release Guard Mode and clear the Guard Mode Designator.

## 3.4. INSTRUCTION TYPES AND FORMATS

Instructions for the UNIVAC 418-III System have two parts, the function field and the operand field. The contents of the function field indicates to the C/A section which operation is to be performed; the contents of the operand field supplies the C/A section

PAGE:

with the necessary information to enable it to perform the function. The instruction repertoire is the set of all recognized functions.

The UNIVAC 418-III instructions fall into three distinct types, designated I, II, and III. Type I instructions are identified by function codes 02 through 27, 32, 33, and 40 through 47. Type II instructions are identified by function codes 30, 31, 34 through 37, and 51 through 76. Type III instructions are identified by function codes 5000 through 5077.

• Type I Instructions

The Type I instruction format is:

|   | f     | u    |  |

|---|-------|------|--|

| 1 | .7 12 | 11 0 |  |

where: f is the six-bit function code

u is the 12 low-order bits of the operand address.

• Type II Instructions

The Type II instruction format is:

| ĺ |    | f  | u or z |   |

|---|----|----|--------|---|

|   | 17 | 12 | 11     | 0 |

where: f is the six-bit function code

u is the 12 low-order bits of the operand address

z is the 12 low-order bits of an 18-bit sign-extended operand.

When f indicates that the 12 low-order bits are to be interpreted as the actual operand, the 18-bit operand is formed by using z and propagating the contents of bit 11 to the six high-order bits. This is commonly referred to as sign extension.

• Type III Instructions

The characteristic of a Type III instruction is the use of a major function code of 50 and a minor function code between 00 and 77. Type III instructions may be subdivided into two distinct categories, each with a slightly different format.

PAGE:

Туре Ш-а

|    | f  |    | m |   |   | ĸ |   |

|----|----|----|---|---|---|---|---|

| 17 | 12 | 11 |   | 6 | 5 |   | 0 |

where: f is 50

m is the minor function code

K is zero or a constant less than 64.

Type III-b

|    | f      |    |    |    | m |   |   | Unused |   |

|----|--------|----|----|----|---|---|---|--------|---|

| 17 |        |    | 12 | 11 |   | 6 | 5 |        | 0 |

|    | Unused |    | 1  |    |   | ι | ı |        |   |

| 17 |        | 13 | 12 | 11 |   |   |   |        | 0 |

where: f is 50

m is the minor function code

I is 0 if indexing is not used

I is 1 if indexing is used

u is the 12 low-order bits of the operand address.

Type III-b instructions are 2-word (36-bit) instructions.

In addition to the foregoing formats there are several Type III-a instructions which use the contents of one or more storage locations following their occurrence for specific data. These are principally the I/O instructions. Control is transferred to the storage location following the data words used by them.

## 3.5. ADDRESSING

The operand fields of Type I, Type II, and Type III-b instructions contain 12 bits. The UNIVAC 418-III main storage is logically divided into bays, each containing 4096 eighteen-bit words, and may be expanded to a maximum of 32 bays; therefore, each Type I, Type II, or Type III-b instruction provides sufficient space to specify any address within a bay. The bay which contains the desired address is determined by certain rules outlined in the following discussion.

When an instruction is executed which is in the last storage location of a bay, program control passes to the first location of the next bay unless it is a skip or jump type

PAGE:

6

instruction. If it is a skip type instruction, control passes to the first or second location of the next bay depending on whether or not the skip condition is met. If it is a jump type instruction, control passes to the storage location specified in the next bay. This is tantamount to saying that as long as forward jumps are made, it does not matter where the instruction is located in storage.

In order to enable certain instructions to access any address in storage, the SR (Special Register) may be used to specify which bay is to be used. The Special Register is active or inactive depending on whether bit 4 is set to one or to zero; bit 4 is not a part of the bay identification. Bits 5 and 3 through 0 of SR are the bay bits.

#### **Example:**

To set the SR active to bay 25 (31<sub>8</sub>), the binary number 543210 (71<sub>8</sub>) must

be stored in SR because bit 4 (SR active bit) must be set to 1. The desired address is derived by ignoring bit 4 and treating bit 5 as though it were in bit position 4. By doing this,  $71_8$  becomes  $31_8$  (111001<sub>2</sub>  $\rightarrow$  11001<sub>2</sub>).

To set the SR active to bay 5 (5<sub>8</sub>), the binary number 010101 (25<sub>8</sub>) must be

stored in SR.

In order to set the Special Register active to bay 3, the instruction

| LABEL OP |                   | OPERATION | OPERA | OPERAND |    |

|----------|-------------------|-----------|-------|---------|----|

| 1        | 10                | 20        | 30    | 40      | 50 |

|          | <u>i   [L,S,R</u> |           |       |         | 1  |

is executed. To set it active to bay 31 (32nd bay), the instruction

<u>\_\_\_\_\_</u>

#### is executed. To inactivate the Special Register the instruction

may be executed.

When the C/A section makes reference to the storage location corresponding to the index register specified in the IRP, the B Register is accessed instead (see 3.2).

When the C/A section makes reference to the addresses  $300_8$  through  $477_8$ , the contents of the corresponding IGR storage location is accessed instead.

• Type I Instructions

Type I instructions are SR-sensitive and indexable, meaning that if SR is active, the bay specified by its contents is accessed, and that the contents of the active index register are used to modify the operand address if the function code is odd.

If SR is not active (bit 4 is zero), the bay to be accessed is that in which the instruction itself resides; the bay bits are taken from the five high order bits of the Instruction Address Register.

PAGE:

If the function code (f) is odd, indexing is specified. This means that the full 18-bit contents of the active index register are arithmetically added to the (positive) 17-bit operand address. Figure 3-1 illustrates the various addressing techniques for Type I instructions.

| LABEL | 10                                                      | OPERATION<br>20                               | 30                               | OPERAND                                                       | 40                                                     | COM<br>50 |

|-------|---------------------------------------------------------|-----------------------------------------------|----------------------------------|---------------------------------------------------------------|--------------------------------------------------------|-----------|

|       | <u> </u>                                                | <b> 0</b>                                     | <u> </u>                         | LINE                                                          |                                                        | <u></u>   |

|       | <u>,  <b>L</b>L</u>                                     |                                               | 0,0,1,1,1,1,1                    | L,I,N,E, 2                                                    |                                                        |           |

|       | <b>L</b>   <b>S</b>   <b>R</b>                          | <u> </u>                                      | 3                                |                                                               | <u></u>                                                | <u> </u>  |

|       | <u>, ,   <b>L</b>, L, ,</u>                             |                                               | <b>D</b> _ <b>O</b>              | L <sub>1</sub> 1 <sub>1</sub> N <sub>1</sub> E <sub>1</sub> 4 |                                                        | 1.1.1.1.1 |

|       | <u> </u>   L <sub>1</sub> S <sub>1</sub> R <sub>1</sub> |                                               | <u> </u>                         | L,I,N,E,5                                                     |                                                        | <u> </u>  |

|       | L B                                                     |                                               | 3,0,0,0,0,),                     | LINE 6                                                        |                                                        | <u> </u>  |

|       | <u>,   <b>L</b>, <b>L</b>,  </u>                        |                                               | 1,0,0,,,,,,,,,                   |                                                               | ,<br><u>1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 </u>     |           |

|       |                                                         |                                               | 0, , , , , , , , , 1.            |                                                               | <u></u>                                                | <u> </u>  |

|       | <u>, ,                                  </u>            | <b></b>                                       | I _ O _ O                        | L_I_N_E9                                                      | <u> </u>                                               | <u></u> _ |

|       |                                                         |                                               | 3 <u> </u>                       | L,I,N,E, 1                                                    | 0, , ] , , , , ,                                       |           |

|       |                                                         | <u>, , , , , , , , , , , , , , , , , , , </u> | 1,0,0, , , , ,                   |                                                               | <u>1</u>                                               | <u></u>   |

|       |                                                         | <u> 0</u>                                     |                                  | L <sub>1</sub> I <sub>1</sub> N <sub>1</sub> E <sub>1</sub> 1 | 2                                                      | <u> </u>  |

|       | <u>  L<sub>1</sub>B<sub>1</sub> </u>                    | <u></u> ((                                    | $0_1 1_1 0_1 0_1 0_1 0_1 )_1  .$ |                                                               | <u>3</u> , , <u>, , , , , , , , , , , , , , , , , </u> |           |

|       | <u>, ,                                  </u>            |                                               | I,0,0, , , , , ,  .              | L, I , N, E, 1                                                | 4                                                      |           |

Figure 3-1. Type I Instruction Addressing Techniques

If line 1 were to be located at address 020000, the following storage references would be made:

| LINE NO. | EFFECTIVE U            | ADDRESS REFERENCED |

|----------|------------------------|--------------------|

| 2        | 0100 + 020000          | 020100             |

| 4        | 0100 + 030000          | 030100             |

| 7        | 0100 + 020000 + 030000 | 050100             |

| 9        | 0100 + 000000 + 030000 | 030100             |

| 11       | 0100 + 030000 + 030000 | 060100             |

| 14       | 0100 + 020000 - 010000 | 010100             |

• Type II Instructions

Type II instructions are never SR sensitive, differing in this respect from Type I instructions. Regardless of the contents of SR, the bay referenced is the one in which the instruction resides.

PAGE:

Some Type II instructions are index sensitive; this allows them to access other bays by using the active index register to modify the address obtained by combining  $U_{11-0}$  and IAR<sub>17-12</sub>.

Three instructions (LBK, LLK, and ALK) do not make a second storage access. The sign-extended value of the operand field is used as the operand.

• Type III instructions

The Type III-a instructions do not require an operand. The Type III-b instructions resemble the Type I instructions: they are SR and index sensitive. When I is set to 1, indexing is used: when it is set to 0, no indexing is used.

### 3.6. STORAGE PROTECTION (GUARD MODE LIMITS)

To ensure program protection, a selected area of storage may be placed under Guard Mode Limits through the use of the LGM (f = 5065) instruction. When the Guard Mode is active, any attempt to store into a storage address outside the range set by the LGM instruction causes a Guard Mode Interrupt at address  $30_8$ . Two 9-bit registers, Storage Limits Upper and Storage Limits Lower, may be loaded with the upper and lower bounds of an area of storage to be placed under Guard Mode. For this purpose, storage is divided into 256-word blocks. The LGM is a privileged instruction and may not be used by the programmer.

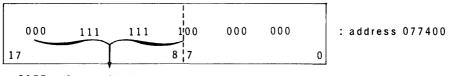

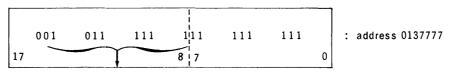

When the nine high-order bits of a 17-bit storage address are placed in Storage Limits Lower, the first address of that block is the lower bound of the Guard Mode Limits. When the nine high-order bits of a 17-bit storage address are placed in Storage Limits Upper, the last address of that block is the upper bound of the Guard Mode Limits. For example, the instruction

| LABEL |         |                   | OPERATION          | OPERAND |         |

|-------|---------|-------------------|--------------------|---------|---------|

|       | 1       | 10                | 20                 | 30      | 40      |

|       |         | 1 . 1 <b>L</b> .G |                    |         |         |

|       | iiiiii. | <b> + .</b> 0     | <b>2 7 7 1 7 7</b> | <u></u> | <u></u> |

prevents storage outside the range of addresses  $077400_8$  to  $0137777_8$ ; any attempted violation of this restriction causes a Guard Mode Interrupt instead.

0177 = Storage-Limits -Lower Contents

0277 = Storage-Limits-Upper Contents

Upon the occurrence of any interrupt, the Guard Mode Designator is cleared (disabled), so that all of main storage becomes accessible to subroutines gaining control through the

PAGE

interrupt locations.

Because locations 0 through  $17_8$  are never under guard mode protection, it is always possible to use them for storage. The index registers are part of that category and are actually located at addresses 1 through  $10_8$ .

# 3.7. PRIVILEGED INSTRUCTIONS

Privileged instructions are those which are needed by an operating (controlling) system in order to perform its job; they are considered inappropriate for use in normal (user) programs. The appearance of any of these instructions in any user program would have an unpredictable and probably disastrous effect.

When the Guard Mode Designator is set, through the use of an LGM instruction, any attempt to execute a privileged instruction causes a Guard Mode Interrupt instead. The privileged instruction is not executed or initiated.

The privileged instructions are:

- 5011 Load Input Channel (LIC)

- 5012 Load Output Channel (LOC)

- 5013 Load External Function Channel (LFC)

- 5015 Stop Input on Channel (STIC)

- 5016 Stop Output on Channel (STOC)

- 5021 Test Input Channel (TIC)

- 5022 Test Output Channel (TOC)

- 5023 Test Function Channel (TFC)

- 5024 Wait For Interrupt (WFI)

- 5025 Wait For Interrupt (WFI)

- 5056 Stop On Key Setting (SK) Ignored when in Guard Mode.

- 5065 Load Guard Mode (LGM)

- 5066 Set Audible Alarm (SAA)

- 5067 Enable ESI Interrupts (EEI)

### 3.8. FLOATING POINT NUMBERS

Floating point numbers are 2-word, 36-bit constants; they consist of a mantissa and a characteristic. The format of a floating point number is:

| r - 1 |       |       |      |

|-------|-------|-------|------|

|       |       |       |      |

| s     | с     |       | m    |

|       |       |       |      |

| 35 3  | 34 27 | 26 18 | 17 0 |

where:

s is the sign bit c is the 8 characteristic bits m is the 27 mantissa bits.

The mantissa (m) contains the 27 significant bits of the floating point number. The magnitude of the mantissa is either zero or between  $.4_8$  and  $.77777777_8$ , normalized so that the most significant bit is a one. The characteristic is the value of c in the expression  $2^{c-2008*m}$ . The high-order bit of c (bit 34) is the sign bit of the characteristic. When  $c_{34}=1$ , the characteristic is positive; when  $c_{34}=0$ , the characteristic is negative. The sign bit (s) is zero when the floating point number is greater than zero (positive); it is one when the number is less than zero (negative). The magnitude (positive equivalent) of a

PAGE:

negative number is its one's complement.

Take, for example, the number 2.0. It can be rewritten in floating point form as:

2.0 \* 10<sup>0</sup>, or 20. \* 10<sup>-1</sup>, or .20 \* 10<sup>1</sup>, and many others.

In the above examples, 0, -1, and 1 are the characteristics; 2.0, 20., and .20 are the mantissas. The three expressions represent the same quantities, illustrating that the mantissa and characteristic may be manipulated so that the value of the number remains unchanged. The octal representation of this number is:

$$2.0 * 10^0 = .2_8 * 2^3$$

To normalize, the mantissa is multiplied by 2, and the characteristic is decreased by one.

The floating point format is:

#### 002400000000<sub>8</sub>

Finally, to indicate that the power of the characteristic is positive, the characteristic is biased to obtain  $20240000000_8$ . In the same manner, -2.0 is represented as  $57537777777_8$ .

#### 3.9. INTERRUPTS

Interrupts are internally generated signals which cause the C/A section to interrupt its normal sequence of instructions (governed by Instruction Address Register contents), and to take the next instruction from a predetermined address in main storage. The contents of the IAR are not changed until the interrupt instruction is executed. An SLJ or SLJI instruction is placed in the interrupt locations, which captures the value of IAR in order to allow normal processing to continue when the interrupt processing coding is completed.

Whenever an interrupt is generated and control passes to the appropriate interrupt location, the Guard Mode designator is cleared, and all subsequent interrupts are held back until the C/A section executes an AAI or EJI instruction.

A summary of all reserved storage locations, including the interrupt locations, is contained in Appendix C.

#### 3.9.1. Parity Fault Interrupts – Locations 21<sub>8</sub>, 22<sub>8</sub>, 27<sub>8</sub>, 31<sub>8</sub>, 32<sub>8</sub>, and 40<sub>8</sub>

Parity errors, whenever they occur during an access of storage by either the C/A or the I/O sections, result in an interrupt. If a parity error occurs when the C/A section accesses main storage, the instruction at location 278 is executed. If a parity error occurs when the C/A section accesses IGR storage, the instruction at location 408 is executed.

If a parity error occurs when the I/O section accesses either main storage (data transfer) or IGR storage (BCW's), the address of the storage location which was being read is placed in locations  $22_8$  and  $32_8$  for IOM #0 and IOM #1 respectively and s the instruction at location  $21_8$  or  $31_8$  is executed, depending on whether IOM #0 or IOM

PAGE

# 1 was doing the transfer.

Detection of a C/A storage parity error results in execution of the instruction at address  $27_8$ . This may be the result of a fault at either of two possible locations in storage. It could be the address at which the next instruction is located, or it could be the address referenced as a result of the operation being performed. In order to determine the address referenced, the following sequence is used:

- (1) If a parity error occurs when reading the contents of the captured IAR address (captured through an SLJ instruction at location 27<sub>8</sub>), the error has occurred at the captured IAR address.

- (2) If the parity error did not occur at the captured IAR address, a main storage search must be initiated. Instead of reading all of storage to determine which address might possibly have been referenced by some instruction, or instead of trying to find which effective address the interrupted instruction had referenced, a special hardware sequence can be initiated.

An LOC instruction to Channel 0 can be performed with the BCW's set to the range to be tested (between 000000 and  $177777_8$ ). Channel 0 scans the first 65K of storage until an error is found.

When an error is detected, IOM #0 stores the address of the error in storage location  $22_8$  and interrupts the C/A section and causes it to read the instruction from storage address  $21_8$ . Address  $21_8$  contains a jump to the IOM #0 parity subroutine, which captures and evaluates the address of the parity error.

Channel 0 does not scan beyond the point of error until the subroutine releases the interrupt lockout. The IOM then resumes scanning the remainder of storage starting at the ERROR location + 2 for parity errors; the address following each error is not checked. Channel 0 can scan 65K of storage in approximately 50 milliseconds or more.

If it is desired to scan upper storage (65K - 131K), the monitor interrupt from the foregoing instruction is used to reinitiate the LOC on Channel 0 with the BCW's set to the range to be tested (between  $200000_8$  and  $377777_8$ ).

NOTE: If an error occurs during the read of a jump instruction, the instruction has been executed. If a LOC is used on channel 0, the C/A is locked out during the transfer time, because the IOM now operates at the maximum transfer speed (1.33 million words per second).

#### 3.9.2. Supervisor Call Interrupt - Location 20<sub>8</sub>

When an instruction with the function codes 00, 01, 77, 5000, 5001, or 5077 is attempted, the instruction at location  $20_8$  is executed. If the optional hardware for the convert or floating point instructions is not present, these function codes also cause a Supervisor Call Interrupt whenever they are executed.

PAGE:

# 3.9.3. Day Clock Interrupt - Locations 23<sub>8</sub> and 24<sub>8</sub>

When the Day Clock is attached, location  $24_8$  is incremented every 6 seconds. Every minute an interrupt at location  $23_8$  is generated.

# 3.9.4. Real Time Clock Interrupt - Locations 258 and 268

The Real-Time Clock (RTC) decrements the contents of location  $26_8$  every 200 microseconds. When the contents of location  $26_8$  becomes zero, an interrupt at location  $25_8$  is generated, and the contents of location  $26_8$  become  $777776_8$ .

#### 3.9.5. Guard Mode Interrupt - Location 30<sub>8</sub>

When the Guard Mode designator is active and an attempt is made by the C/A section to store into a main storage or IGR location which is outside the limits specified by the storage limits registers, the instruction at location  $30_8$  is executed instead of the attempted store instruction.

When the Guard Mode designator is active and one of the privileged instructions is attempted, the interrupt is generated and the instruction is not executed.

#### 3.9.6. Power Loss Interrupt - Location 338

A Power Loss Interrupt results from loss of input power. The Operating System then has at least 0.6 millisecond to store any vital information prior to stopping. When the interrupt is generated, control passes to location 338.

#### 3.9.7. Floating Floating Point Underflow Interrupt - Location 348

When a floating point instruction is executed and the resulting characteristic has a value of less than zero, a floating point underflow interrupt is generated which causes the instruction at location  $34_8$  to be executed.

#### 3.9.8. Floating Point Overflow Interrupt - Location 358

When a floating point instruction is executed which would cause the resulting characteristic to have a value greater than  $377_8$ , a floating point overflow interrupt is generated which cause the instruction at location  $35_8$  to be executed.

#### 3.9.9. Interrupt Lockout Timeout Interrupt - Location 418

If the C/A section does not release the interrupt lockout within the period of time set by the timeout delay, while in Guard Mode, control is passed to location  $41_8$ , and the instruction previously stored there is executed. The timeout delay is approximately 100 to 200 microseconds.

PAGE:

# 3.9.10. ISI External Interrupts - Locations 1408-1778 and 2408-2778

When a peripheral device connected to an ISI channel transmits an External Interrupt (through the EI signal), the data transmitted is placed in location  $160_8+CHNO$  or  $260_8+CHNO-16$ , and the instruction located at address  $140_8+CHNO$  or  $240_8+CHNO-16$  is executed. CHNO represents the channel number by which the device is attached to either IOM #0 or IOM #1 respectively.

#### 3.9.11. ISI Internal Interrupts - Locations 1008-1378 and 2008-2378

As a result of the Monitor bit in the BCWT location, each IOM generates an Internal Interrupt whenever the BCW's become equal and the ISI Internal Interrupt locations receive control as a result. There is one interrupt location for each channel of each IOM for both input and output.

#### 3.9.12. ESI Interrupts - Locations 368 and 378

When an ESI table entry is made, an ESI interrupt is generated whenever the ESI interrupt lockout designator for that IOM is enabled. If interrupts are withheld as a result of any previous interrupt or PAI instruction, the ESI interrupt is delayed until interrupts are again enabled.

If the ESI interrupt lockout designator is set, no ESI interrupt is generated as a result of a new ESI table entry. Depending on which IOM is updating the ESI table, an ESI interrupt causes the instruction at location  $36_8$  or  $37_8$  to be executed and the ESI interrupt lockout designator for that IOM to be set.

PAGE:

# 4. INPUT/OUTPUT SECTION

# 4.1. INTRODUCTION

This section provides a description of the Input/Output Section of the UNIVAC 418-III Real-Time System. It presents a detailed definition of the data transfer characteristics and of the functional operation of the Input/Output Section. A thorough knowledge of the Input/Output Section is necessary to take full advantage of the operating capabilities of the system.

## 4.2. GENERAL DESCRIPTION

The Input/Output Section consists of one or two functionally independent Input/Output Modules, IOM #0 and IOM #1. Each IOM is designed to permit I/O data transfers to be independent of the operation of the Command/Arithmetic Section of the UNIVAC 418-III System. See Section 2 for interface with main storage.

Input/Output Module IOM #0 has at least eight I/O channels; this number may be increased to 16 in groups of four. Expansion beyond 16 channels to a maximum of 32 requires the addition of IOM #1. IOM #1 can be added with or without expansion of IOM #0. Except for the following, both Input/Output Modules are functionally identical.

- IOM #0 contains the logic for decrementation of the Real-Time Clock and generation of the Real-Time Clock Interrupt.

- IOM #0, channels 0 and 1, contains the logic for communication with the day clock and the operator's console.

- Channels 16 and 17 of IOM #1 can operate in paired channel mode only.

# 4.3. FUNCTIONAL OPERATION

All references to input or output are made with respect to an IOM. Input describes a data transfer via an input channel from a subsystem through the IOM to main storage. Output describes a data transfer via an output channel from main storage through the IOM to a subsystem. Any number of subsystems are capable of both input and output data transfers; however, bidirectional transfers do not occur simultaneously. Each IOM contains a set of high speed Integrated General Registers which are used as storage for control words. Each IOM contains from eight to sixteen 18-bit input/output channels. Depending on the peripheral subsystem, these channels can be used singly or in pairs in order to provide a broader data path. Each IOM operates independently of the other, affording two-way simultaneity of input/output and storage with an aggregate capacity of 1.33 million 18-bit word transfers per second per module. Main storage provides separate data paths to and from each IOM.

PAGE:

2

Each IOM provides the data paths and the control circuitry necessary for direct communication between main storage and the input/output devices. That portion of the circuitry and the data path which is necessary to connect a peripheral subsystem with main storage is called a channel. Each channel allows transfers of data in either direction between main storage and the devices on that channel. Each channel contains 36 data lines, 18 for input and 18 for output.

Most peripheral subsystems utilize both the input and corresponding output lines of the same channel. Data transfers on these subsystems may be made in either direction over a single channel, but not simultaneously. Similarly, data transfers may not occur at the same time through two different channels on the same IOM. If, however, the main storage buffer areas for input/output transfers through channels of different IOM's are located in different main storage banks, these data transfers can occur at the same instant. When two or more subsystems request data transfers at the same time, each IOM performs as a multiplexer with a combined transfer rate of up to 1.33 million 18-bit words per second. If there are two IOM's and separate storage banks, the transfer rate capability is 2.66 million 18-bit words.

Each IOM functions as a small processor. Programmed instructions, executed by the Command/Arithmetic Section, load index values into the Buffer Control Words located in the IOM and also establish desired peripheral subsystem activity. From that point on, the IOM scans the input/output channels automatically, accepting data from and passing data to the subsystem at the normal rate of the subsystem. When a peripheral subsystem requests a data transfer, the contents of the Buffer Control Words for that channel are used as a main storage address, and the transfer occurs. At the same time, the IOM updates the contents of the Buffer Control Word and tests for a terminal condition. This entire operation requires only the time of one memory cycle, 750 nanoseconds. The Buffer Control Words are located in the high speed Integrated General Registers.

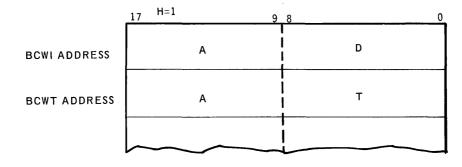

The number of data words transferred between a subsystem and main storage, and the address of the locations to or from which they are transferred is controlled by two Buffer Control Words (BCW) which are associated with each data transfer operation. The Initial Buffer Control Word (BCWI) contains the current storage address of the operation. As each data word transfer occurs, the BCWI is incremented or decremented by one, depending upon a bit specified in the Terminal Buffer Control Word (BCWT). The BCWT contains the last (terminal) address of the buffer. The data transfer activity stops and the channel is deactivated when the BCWI and the BCWT are equal.

Each channel operates in one of three states: input, output, or function. The input and output states are used when transferring data to or from main storage. The channel can alternate between the input and the output states on consecutive memory cycles. The function state is the means by which the Command/Arithmetic Section establishes initial communication with a peripheral subsystem and is basically an output state. During this state, the Command/Arithmetic Section causes the IOM to transfer one or more function words to a peripheral subsystem. These function words direct the subsystem to perform the desired operation.

When one or more channels are active, the IOM, independent of program control, scans the channels in decreasing numerical sequence, in search of input and output data request signals presented by a subsystem. Upon finding a data request signal on an active channel, the IOM controls the transfer of a word between a main storage location and the requesting subsystem. Consecutive transfers of data words to or from a subsystem are performed at a rate governed by the subsystem.

PAGE:

# 4.4. CHANNEL OPERATION

A single channel of the Input/Output Section provides 18-bit parallel communication between the IOM and a subsystem. (See Appendix A for a description of normal and compatible channels.)

Logically combining any pair of sequentially numbered even and odd channels (4 and 5, for example, but not 3 and 4, or 5 and 6) into a single 36-bit channel allows 36-bit parallel communication between the IOM and a subsystem.

When operating with paired channels, the control lines associated with the odd numbered channel have control of all data transfers. The most significant half of the 36-bit word is carried by the odd numbered channel; the least significant half is carried by the even numbered channel.

### 4.5. I/O CHANNEL PRIORITY

Although all I/O channels may be available for communication between the IOM and the subsystems at the same time, only one channel of one IOM is actually transferring data at any given instant. However, since the subsystem handles data more slowly than the main storage and the IOM, it is possible for the IOM to keep all or many of the subsystems operating simultaneously.

The rate of consecutive transfers of data words to or from a subsystem is governed by the subsystem when it is ready to send or receive a data word. When two or more subsystems are currently active, they may also be simultaneously presenting data transfer requests (ODR's, IDR's or both) to the IOM. In order to resolve the conflict of simultaneous requests, a priority control network is used within the IOM.

When an I/O scan is performed and two or more I/O data transfer requests are present, the request from the highest numbered channel is serviced first by the IOM. Any request for I/O data transfer from the same channel is skipped for one I/O scan cycle during the next I/O scan. This allows service for the lower numbered channels of the IOM. The next request serviced is from the highest numbered channel requesting service at the time of the next I/O scan. The scan for a new operation takes place 275 ns before the last pass of the current operation is complete and every 125 ns thereafter.

The following functional priorities are established in each IOM:

- (1) Output Data Transfer

- (2) Input Data Transfer

- (3) Main Memory and IGR Parity Errors

- (4) Real-Time Clock Interrupt (IOM #0)

- (5) Day Clock Interrupt (IOM #0)

- (6) ESI External Interrupt

- (7) ISI External Interrupt

- (8) External Function Monitor or Output Monitor

- (9) Input Monitor

- (10) I/O Instructions and arithmetic references to the high speed integrated general register (IGR) in that IOM.

PAGE:

# 4.6. INPUT/OUTPUT INTERFACE

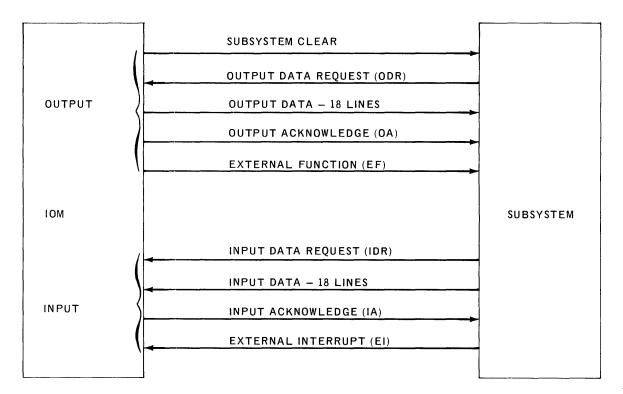

Each input/output channel between main storage and subsystems is bidirectional; transfers of data and control signals may take place in either direction between main storage and the subsystem on any channel. Each channel has 36 data lines, 18 for input data and 18 for output data, to permit parallel reading or writing of full 18-bit data words on a nonsimultaneous basis. In addition to the data lines, various control lines are used for transmitting control signals between a subsystem and the I/O Section. The lines of an I/O channel are shown in Figure 4-1 and described in Table 4-1.

Figure 4–1. One I/O Channel

PAGE:

| SIGNAL<br>NAME         | ORIGIN    | FUNC TION                                                                            |

|------------------------|-----------|--------------------------------------------------------------------------------------|

| Subsystem<br>Clear     | IOM       | Clears subsystem on that I/O channel.                                                |

| Output Data<br>Request | Subsystem | Indicates to I/O Section that subsystem is ready to receive a data or function word. |

| Output<br>Acknowledge  | IOM       | Indicates to subsystem that a data word is on the output data lines.                 |

| External<br>Function   | IOM       | Indicates to subsystem that an External Function Word is on the output data lines.   |

| Input Data<br>Request  | Subsystem | Indicates to IOM that a data word is on the input data lines.                        |

| Input<br>Acknowledge   | IOM       | Indicates to subsystem that a data word has been accepted by I/O Section.            |

| External<br>Interrupt  | Subsystem | Indicates to IOM that a Status word is on the input data lines.                      |

Table 4-1. I/O Channel Control Signals

# 4.7. IOM RESPONSE TIME

The interval between a subsystem I/O request and the leading edge of an IOM acknowledge signal is given in Table 4-2.

| OPERATION                  | CHANNEL         |                 |

|----------------------------|-----------------|-----------------|

|                            | COMPATIBLE      | NORMAL          |

| Internally Specified Index |                 |                 |

| 18 bit output              | 1.562 μsec      | 1.312 $\mu sec$ |

| 36 bit output              | 2.312 µsec      | 2.062 µsec      |

| 18 bit input               | 0.687 µsec      | 0.687 µsec      |

| 36 bit input               | 1.437 µsec      | 1.437 $\mu$ sec |

| Externally Specified Index |                 |                 |

| Output or Input            | 2.937 $\mu sec$ | 2.937 μsec      |

Table 4–2. Time Between Subsystem Request and IOM Acknowledge

### 4.8. OPERATING MODES

A channel in the I/O Section can operate in either one of the two following modes.

$f_{17-12} = 6$ -bit function code (50)

К<sub>5-0</sub>

$m_{11-6} = 6$ -bit minor function code (11, 12, 13)

= 6-bit channel number (00 through 31)

PAGE

- Internally Specified Indexing (ISI)

- Externally Specified Indexing (ESI)

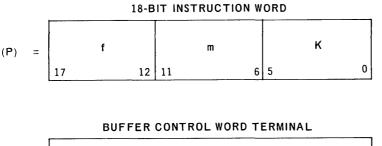

The formats for the I/O instructions 5011 (LOAD INPUT CHANNEL), 5012 (LOAD OUTPUT CHANNEL), and 5013 (LOAD EXTERNAL FUNCTION CHANNEL) require three memory addresses. The first address is used to store the instruction, the next two succeeding addresses are used to store the buffer limit designators and the modifier and monitor designators. The following illustration shows these details.

#### $(P+3) \rightarrow P$

17

(P+2) =

Execution of the Stop Input on Channel instruction (5015) deactivates the input channel specified by the K field of the instruction. Execution of the Stop Output on Channel instruction (5016) deactivates the output channel specified by the K field of the instruction. Pending monitor interrupts for the terminated channel are cleared.

0

#### 4.8.1. Internally Specified Indexing (ISI)

All channels, 18 or 36 bit, can operate in an ISI mode. This mode allows input or output on a given channel to one device at a time. All data is sent to or read from one continuous buffer area. Each channel is assigned two pairs of Buffer Control Words (BCW) locations. Any output request on a channel is hardware directed to the location of the first pair of BCW's for that channel. Any input request is directed to the second pair. The BCW's contain the terminal and initial addresses of the main storage locations assigned to the buffer, and certain control bits.

#### 4.8.1.1. Programmed Activation of an I/O Channel - ISI Mode

An input or output channel in ISI Mode is activated when one of the following instructions is executed:

- Load Input Channel (LIC) (5011)

- Load Output Channel (LOC) (5012)

PAGE:

• Load External Function Channel (LFC) (5013)

Execution of the LIC instruction activates the input channel specified by the K field of the instruction and causes the two succeeding addresses to be stored in the input buffer control word addresses for the designated channel.

Execution of the LOC or LFC instruction activates the output channel specified by the K field of the instruction and causes the two succeeding addresses to be stored in the output buffer control word addresses for the designated channel. If the instruction is an LFC, an External Function is forced out on the specified channel.

When a channel is activated, data words are transmitted between main storage and a subsystem through the IOM in response to data requests presented by the subsystem on that channel. During the period in which a channel is active, the address of each location in main storage to or from which an I/O data word is transferred is specified by the current contents of the BCWI associated with the channel. As each data word is transferred to or from a location in main storage, the contents of the BCWI is incremented or decremented. When the BCWI equals the BCWT (the least significant 15 bits of each word are compared), the data transfer activity on the related channel is automatically terminated.

#### 4.8.1.2. ISI Buffer Control Word Formats

All External Function Buffer Control Words and ISI Buffer Control Words are stored in high speed Integrated General Registers (IGR) associated with the I/O channel and consist of a terminal address word and a initial address word in the following formats:

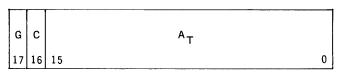

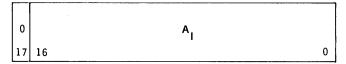

$A_T$ : The address of the last word in the buffer, less the high order address bit

$A_{I}$ : The 17-bit address of the first word in the buffer (becomes the present address)

G: A<sub>I</sub> modifier

G = 0:  $A_I$  is incremented by one for each buffer word transfer. G = 1:  $A_I$  is decremented by one for each buffer word transfer.

NOTE: Each paired channel transfer causes two buffer word transfers.

- M: Monitor

- M = 0: The channel terminates when the present address equals the terminal address (bits 15 0)

- M = 1: The channel terminates when the present address equals the terminal address, and a monitor interrupt is generated for the associated channel.

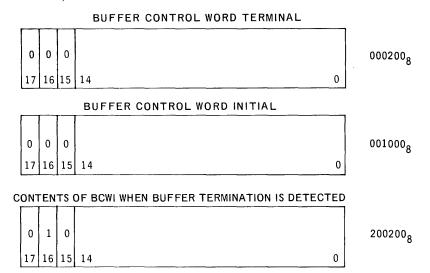

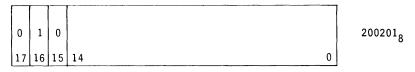

A normal update of BCWI occurs when buffer termination is detected. The final address value stored at the BCWI location for the foregoing example is:

If a BCWI specifies an address in the upper 65K (bit 16 set to 1) of main storage, and if the lower address bits (15-0) contain a larger value than contained in the BCWT, the BCWI wraps around zero as shown in the following example of an incrementing buffer. The IOM does not check for this condition.

PAGE:

8

PAGE:

#### 4.8.1.3. ISI Input/Output Activity

Two modes of activity are performed on an output channel. In one mode of output channel activity (Function Mode), data words called External Function words are transferred from main storage through the active output channel to a subsystem. The External Function Word (EF word) is decoded by the subsystem's control section, and the subsystem is consequently conditioned to perform a specific task, or an input or output data transfer operation. Also, in the Function Mode, data words called Identifier (ID) words are transferred through the active output channel after an appropriate function word has been transferred to the subsystem. The ID word is used in the performance of a Search-Read operation in a subsystem; the ID word is an image of a word being searched for in the subsystem. An output channel is activated for operation in the Function Mode by execution of the Load External Function Channel (LFC) instruction.

In the other mode of output channel activity (Output Mode), data words, called output data, are transferred from main storage via the active output channel to the subsystem. If the subsystem is a magnetic tape subsystem, the output data is written on the magnetic tape; if it is a high speed printer subsystem, the output data is printed on paper, etc. An output channel is activated for operation in Output Mode by execution of the Load Output Channel (LOC) instruction.

Similarly, two types of activity are performed on an input channel. In one type of input channel activity (Input Mode), data words, called input data, are transferred from the subsystem through the active input channel to main storage. If the subsystem is a magnetic tape subsystem, the input data is read from the magnetic tape; if it is a card subsystem, the input data is read from cards, etc. An input channel is activated for operation in Input Mode by execution of the Load Input Channel (LIC) instruction.

In the other type of input channel activity (External Interrupt Mode), the subsystem presents a word, called the External Interrupt Status Word to the IOM through the input channel. An external Interrupt Status Word is a coded word which is generated in the subsystem's control section. This word indicates to the program the

PAGE:

successful completion of either a specific task or an input or output operation, or the occurrence of an abnormal condition in the subsystem. It is not necessary to execute a channel activating instruction for the channel to transfer an External Interrupt Status Word to the IOM.

Appendix B is a detailed description of sequence for Input, Output, and Function Mode activity of an IOM.

#### 4.8.1.4. ISI External Interrupt

A subsystem notifies the Command/Arithmetic Section of an abnormal condition or of the normal completion of an operation by placing an External Interrupt Status Word on the input data lines and an External Interrupt (EI) signal on the appropriate line of the input channel. The input channel on which an EI signal is presented is selected to be serviced by the IOM priority network. If more than one channel presents an EI signal, the EI on the highest numbered channel is serviced first, then the next in descending order, and so on. The IOM services the input channel presenting an EI signal as follows:

- (1) It transfers the External Interrupt Status Word from the input data lines to a fixed address location in main storage for the channel on which the EI signal is generated.

- (2) It places an Input Acknowledge (IA) signal on the appropriate input channel line.

- (3) It interrupts the normal sequence of instruction execution in the C/A section thereby causing the C/A section, upon completion of the execution of the current instruction, to load automatically an instruction from the ISI External Interrupt fixed address location.

- (4) All ISI interrupts and the ESI tabling notification interrupt are disabled.

The subsystem reacts to the IA signal by returning to its 'at rest' state.

No specific instruction is needed to activate an input channel before an EI signal and an External Interrupt Status Word are presented to the IOM.

#### 4.8.1.5. ISI Monitor Interrupts

When the IOM detects that the BCWT and BCWI are equal and the M flag (bit 16 of BCWT) is set, a monitor interrupt is generated. The monitor interrupts are serviced systematically by the IOM priority network. If more than one channel simultaneously present a monitor interrupt, the one on the highest numbered channel is serviced first. When a monitor interrupt is serviced by the C/A section, the next instruction executed is obtained from the monitor interrupt fixed address locations. Monitor interrupts awaiting service are not cleared by the execution of LOC, LIC, or LFC instructions.

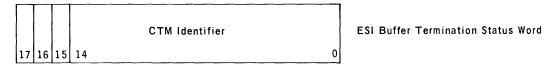

#### 4.8.2. Externally Specified Indexing (ESI)

The ESI mode of I/O Channel operation is selected for a paired channel to which a Communication Terminal Module Control Subsystem (CTMC) is connected and to

PAGE

4

which in turn up to 16 Communication Terminal Modules (CTM) may be added. Each CTM comprises two or four Communication Line Terminals (CLT).

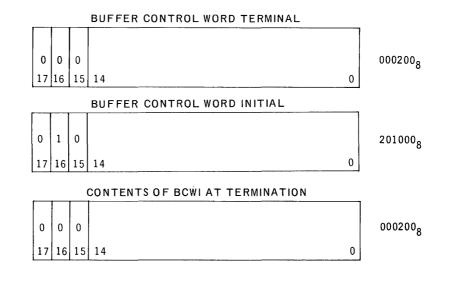

When a channel is operating in the ESI mode, 18 bits are transmitted, bit-parallel, between main storage and the CTM by way of the IOM and the CTMC Subsystem. Data transmissions to or from a number of CTM's are multiplexed on one I/O channel through the operation of the CTMC subsystem.

Channels operating in ESI must be in paired channel mode. Data and external function words are transmitted on the even numbered channel of the pair. Control signal lines of the odd channel control input and output transfers. External functions are transmitted through the even channel External Function line.

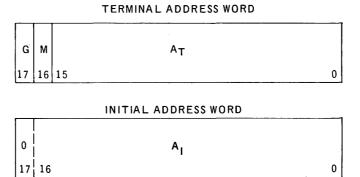

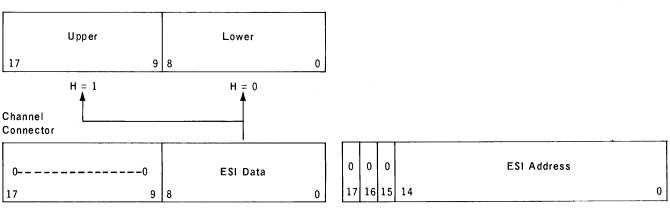

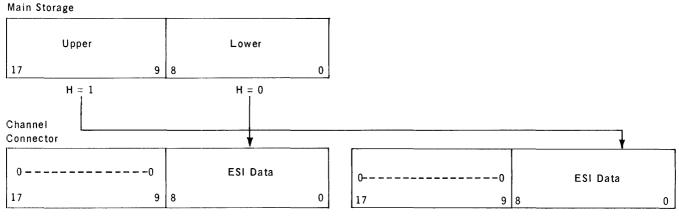

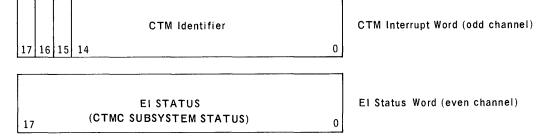

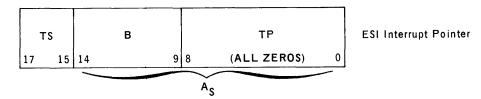

Accompanying each data transfer between the CTMC and the processor is an ESI address identifying which pair of BCW's is to be used to control the data transfer. The ESI address has the following format:

| 0  |    | BIAS |   |   | PRIORITY |   |

|----|----|------|---|---|----------|---|

| 16 | 15 |      | 6 | 5 |          | 0 |

The low order six bits of the ESI address identify the CLT to or from which data is to be transferred. All input CLT's have odd priority codes, and all output lines have even priority codes as indicated by bit 0.

The bias bits are fixed at a specific value at system installation time; they specify the high order portion of the beginning address of the Buffer Control Word (BCW) table.

Since each line requires two successive BCW's it is necessary for the IOM to double the value of the ESI address when referencing the Buffer Control Words.

Figure 4-2 is a schematic representation of the ESI data transmission.

PAGE:

Figure 4-2. ESI Data Transmission

A CTM that is prepared to perform an output operation presents a request to the CTMC when the CTM is ready to receive output data. The CTMC, which continuously scans all CTM's for service requests, locks onto the interface of the CTM requesting service and stays locked until the transfer of one data word to that CTM is complete. If more than one CTM is requesting service at the same time, they are serviced according to priority.

In order to serve a CTM which has requested to output data, the the CTMC presents an ODR to the IOM by way of the appropriate line of the odd output channel. At the same time, the CTMC presents a 15-bit ESI value (bits 14 - 0) to the IOM by way of the odd input channel of the pair.

The ESI value is left shifted (to positions 15 to 1) in the IOM to permit double BCW's. (Address bit 16 is selectable, by connection of a jumper wire in each IOM, to locate BCW's for all ESI devices on the IOM in either of the 65K segments of main storage.) The biased ESI value specifies the absolute address of the location in main storage where the BCWT associated with the particular CTM is stored.

The IOM then obtains the BCWT and BCWI from the locations in main storage specified by the biased ESI value. The IOM then obtains the output data from the location in main storage specified by the contents of the BCWI.

The data is placed on the even channel output data lines and transmitted with an Output Acknowledge (OA) signal via the CTMC to the CTM. Also, the BCWI is tested for the terminal condition, updated, and then restored in the main storage location from which it was obtained. After the CTM receives the output data and OA signal, the CTMC then

PAGE:

seeks another CTM to service.

A CTM that is conditioned to perform an input operation presents a request to the CTMC when it is ready to send input data. The CTMC locks onto the CTM's interface and services multiple requests on a priority basis.

When a particular CTM which is requesting service for an input is serviced, the CTMC presents an IDR to the IOM via the appropriate line of the odd channel. It also presents a 15-bit ESI value on the input lines of the odd channel. The ESI value and fetching of the BCWT and BCWI are handled in the same manner as an output transfer. The IOM then stores the input data in the main storage location specified by the contents of the BCWI and also transmits an IA signal via the appropriate line of the odd input channel. The BCWI is tested for the terminal condition, updated, and then restored in the main storage location from which it was obtained.

#### 4.8.2.1. Programmed Activation of an I/O Channel - ESI Mode

An input or an output channel in ESI Mode is activated when one of the following instructions is executed:

- Load Input Channel (LIC) (5011)

- Load Output Channel (LOC) (5012)

Execution of the LIC instructions activates the input channel specified by the K field (odd channel of the pair must be specified) of the instruction and causes the two succeeding addresses to be skipped.

Execution of the LOC instruction activates the output channel specified by the K field (odd channel of the pair must be specified) of the instruction and causes the two succeeding addresses to be skipped.

Any one or more of the CTM's connected to a CTMC can be caused to perform, or to stop performing, an input or output operation, as a result of programmed execution of the LFC instruction.

The execution of the LFC for ESI is similar to the operation described for ISI. (See Appendix B.) The LFC word for ESI is composed of three bits of the seven-bit CLT selection code, and a three-bit function code that determines what action the CLT will take.

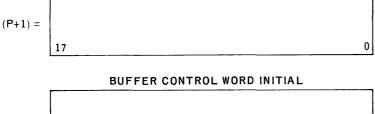

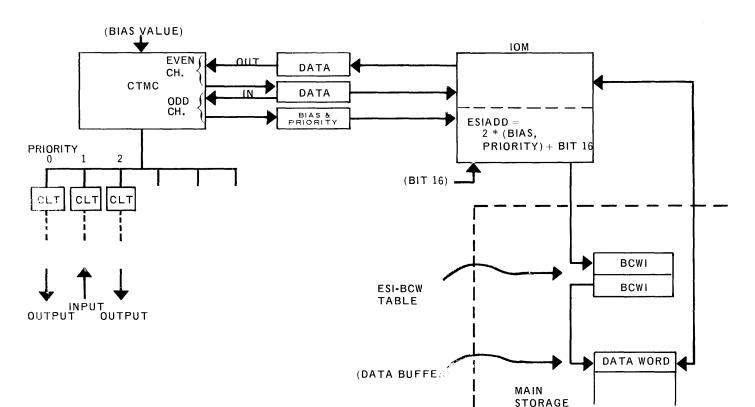

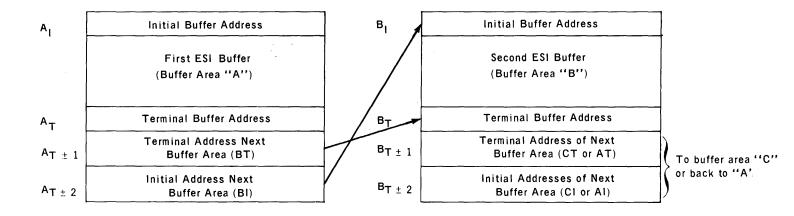

#### 4.8.2.2. ESI Buffer Control Word Formats

The Buffer Control Word (BCW) used in the ESI Mode of I/O Channel operation may have either of two formats. One of the formats is used with I/O operations on channels in ESI Mode that are wired to transfer one I/O data character per 18-bit main storage address. The other format is used with I/O operations on the channels in ESI Mode that are wired to pack two I/O data characters per 18-bit storage address.

PAGE:

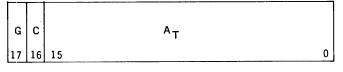

Fullword ESI Buffer Control Words (18-bit Main Storage Transfers)

BUFFER CONTROL WORD TERMINAL

#### BUFFER CONTROL WORD INITIAL

- $A_T$ : Bits 15 0 of the address of the last word in the buffer

- $A_{I}$ : The address of the first word in the buffer (becomes the present address)

- G: A<sub>I</sub> modifier

G = 0:  $A_I$  is incremented by one for each buffer word transfer.

- G = 1:  $A_I$  is decremented by one for each buffer word transfer.

- C: Chain

- C = 0: The buffer is terminated when the present address equals the terminal address.

- C = 1: The contents of the address  $A_T$  + 1 and  $A_T$  + 2 are stored as new buffer control words for the corresponding device, and buffer termination does not occur. See 4.8.2.5 for an example of ESI data chaining.

NOTE: If G = 1,  $A_T + 1$  and  $A_T + 2$  become  $A_T - 1$  and  $A_T - 2$ .

• Halfword ESI Buffer Control Words (9-Bit Main Storage Transfers)