DIGITAL COMPUTER LABORATORY UNIVERSITY OF ILLINOIS URBANA, ILLINOIS

# INTRODUCTION TO THE THEORY OF DIGITAL MACHINES

Math., E.E. 294 Lecture Notes

by

W. J. Poppelbaum

#### CHAPTER I

#### DIGITAL COMPUTERS AND NUMBER SYSTEMS

### 1.1 Analog Computers and Digital Computers

A computer is a calculating machine capable of accepting numerical data and performing upon them mathematical operations such as addition, taking the square root, etc. The computer can also accept non-numerical data by establishing, via a code, a correspondence between the information at its input and the numbers used inside. The mechanism involved in computation can use any one of the common physical agents (mechanics, electricity, etc.).

The data inside the machine can be in the form of continuously variable measurements, such as voltages in a given range, angles; we then talk of an <u>analog computer</u> (example: slide-rule). If the data are in the form of discrete numbers (assembly of a finite number of multi-valued digits), we speak of a <u>digital computer</u> (example: desk calculator). With such a computer nearly unlimited precision can be obtained even when standard hardware is used, while the results of pure analog computation are usually only known within a fraction of a per cent. It should be remarked that combinations of the two principles are possible and used in some installations.

#### General Organization of a Digital Machine

A digital computer can take the simple form of a desk calculator using toothed wheels. In the decimal system these wheels would have ten discrete positions, 0 ... 9. Individual operations are then controlled by a human operator, customarily using a writing pad which contains the list of instructions to be performed, the numbers to be operated on and the intermediate results. The time for multiplying two numbers of 10 decimal digits each is of the order of 10 seconds; the time necessary to write down the result and for pushing the keys can be almost neglected.

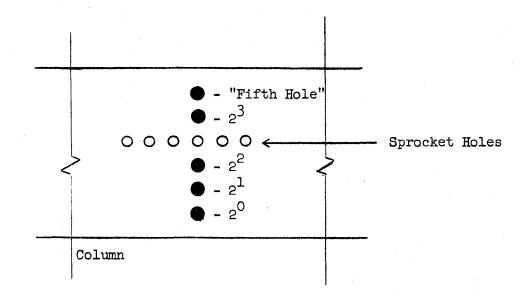

In an electronic computer the digits are represented by the electrical states of electronic circuits, i.e., circuits using transistors. Usually these circuits (called <u>flipflops</u> and assembled in <u>registers</u>) have two states (e.g., a high voltage output or a low voltage output), which means that only two discrete

-1-

values, 0 and 1, are available per digit. We must then use the <u>binary system</u> in which the numbers 1, 2, 3, 4, 5 etc. are represented by 1, 10, 11, 100, 101 etc.

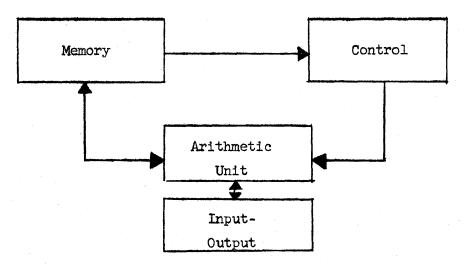

The time for multiplying two numbers of 30 binary digits (--->in precision to 10 decimal digits) is of the order of 10 - 100 microseconds; manual control and the use of a pad to jot down intermediate results would be very inefficient. The writing pad is replaced by a memory (in principle a great number of flipflop registers) which stores from the outset the list of instructions and which, by way of a control-unit, established the electrical connections necessary to perform the operations. The memory is also used to store back the intermediate results. An electronic machine will be automatic at the same time, in the sense that it proceeds all on its own through the problem due to the stored program. The part of the machine corresponding to the desk calculator is called the arithmetic unit. The latter is usually connected to the input-output equipment (tapes with holes or magnetic coating with reading and writing devices). As the name implies, this input-output equipment allows the machine to communicate with the outside world, e.g., store numbers in the memory after having read holes punched in tapes (or cards), or punch holes corresponding to the memory contents at the end of a problem. This general layout of the computer is the same for installations as widely different as the "Illiac" and the IBM 650.

Figure 1-1 below summarizes the general organization.

Figure 1-1

General Organization of a Digital Computer

-2-

# The "Thinking" Ability of Computers

The astonishing usefulness of a modern computer is due to the possibility of having it make simple decisions. These are usually of the following form:

- If number in register A > number in register B, follow instructions stored in list 1 in memory (e.g., locations 56, 57, 58 ...);

- 2. If number in register A < number in register B, follow instructions stored in list 2 in memory (e.g., locations 82, 83, 84 ...).

The transfer from one list to another depending on the contents of registers is called a conditional transfer, jump or branch.

#### Example 1

Take the numerical calculation of the value of a function expressed as a series. The number of terms we have to take in order to obtain a fixed precision varies with the value of the argument. We can decide that we are going to calculate up to the n<sup>th</sup> term where this term is smaller than a given quantity  $\delta$ . After being through with the calculations of each term, we shall test and see if it is bigger than  $\delta$ . If so, we shall go on to the next term; if not, we shall form the sum of all the terms calculated up to this stage, and then proceed with the rest of the problem.

#### Example 2

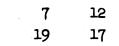

Suppose that 4 numbers e.g. 19, 7, 12 and 17 are stored in memory locations 1, 2, 3 and 4 respectively and that we want to put them in increasing order. This is done by a process known as "merging". First 19 and 7 are ordered by a command of the type "subtract memory location 2 from memory location 1 if the result is positive interchange their contents, otherwise leave the order". Similarly memory locations 3 and 4 are ordered. Now we have two ordered lists

We compare the top members: The smaller one is 7. This we put on top of the "merged list" and strike out the corresponding number in the array, giving

-3-

## 19 17

We know that 17 follows 12 (this list being partially ordered) so the only question is: does 19 follow 12 or 17? This can be decided by two more decisions of the type used before and the problem is solved in a language suitable for a computer.

The ability to exercise "judgment" and to choose between two alternatives saves a great amount of time, but, of course, the programmer must write down the details of what to do in each case before the computation starts. It is possible to extend this ability to judge in such a way that the computer virtually assembles its own program (list of instructions) once the list of <u>subroutines</u> is given and the general method of calculation is prescribed in symbolic form. This is called automatic programming.

## 1.2 Fundamental Computer Vocabulary

#### Serial and Parallel Machines

As mentioned, the numbers are stored in register, i.e., sets of flipflops. In order to calculate, the digital computer shifts the digits from one register to another, adds, subtracts, multiplies or divides the contents of two registers and transfers the result to a third. We can see that all arithmetic operations can be performed if we provide an adder, equipment which takes the negative of a number held in a register (subtracting the digits means adding the negative) and shift facilities which transfer into another register and simultaneously give a displacement of digits by one digit position to the right or left. Since multiplication is a series of additions and shifts, and division a series of subtractions and shifts, such an arithmetic unit would be capable of performing the four operations of arithmetic.

There are two fundamentally different methods for transmitting the digits from one register to the other (or through the adder). If a separate wire is used for each digit and all digits are transmitted simultaneously, we speak of <u>parallel</u> operation. If the digits are "sensed" one after the other and transmitted through a single wire, we speak of serial operation. To illus-

-4-

trate the latter case, we can think of a selector mechanism which always connects the flipflops having the same position in the order 1-1, 2-2, 3-3 ... n-n. Telephone systems use serial transfer of information.

It turns out that parallel operation gives higher computation speeds, while serial operation cuts down the amount of equipment used. It is difficult to ascertain the proportion in which we gain speed or reduce equipment in going from one system to the other. For n digital positions the gain is certainly less than a factor n.

## Synchronous and Asynchronous Operation

In a <u>synchronous</u> machine there exists a central unit called a <u>clock</u> which determines by its signals the moment at which the steps necessary to perform an operation (such as addition, shifts, etc.) are initiated and terminated. For each type of operation we need a fixed number of cycles of the clock whether, in practice, the intermediate steps were long or short (the length usually depends on the numbers involved).

In an <u>asynchronous</u> machine there is no clock to sequence the steps. This can be attained by having each step send out an "end signal" which initiates the next step (<u>kinesthetic machine</u>). There are systems of various degrees of asynchronism, ranging from those in which the times of action of a set of circuits are simulated in a delay device (i.e., in which the end signal or reply-back signal is simply the previous end signal delayed by a sufficient amount of time to allow the set of circuits to operate properly; this amounts to a local clock), to systems in which the operation of each set of circuits is examined by a checking circuit which gives end signals if, and only if, the operation has really been performed. A special type of asynchronous machine is the "<u>speedindependent</u>" machine in which an element may react as slowly as it likes without upsetting the end result. One way to obtain speed independence is to build a "<u>totally sequential</u>" machine in which only one element acts at a time; this would have to be a serial machine.

It should be mentioned that often only a part of the computer is asynchronous. In "Illiac", for example, the arithmetic unit is asynchronous while the (electrostatic) memory is synchronous. In the IBM 650, both the arithmetic unit and the (drum) memory are synchronous.

-5-

## Two-Level DC and Pulse Representation

Information, i.e., digit values, can be represented inside the machine by two different methods. Suppose that we have agreed upon a binary machine using only the values "O" and "1" for each digit. We can then decide to represent these values by sending pulses (of approximately rectangular shape and a duration of the order of  $0.1 - 10 \ \mu s$ ) from one register to the other. In such a <u>pulse</u> <u>machine</u> the presence of a pulse would mean "1", the absence, "O", (the inverse convention could be made too). Usually these pulses are sent (or not sent) at fixed intervals, i.e., a pulse machine is, in most cases, a synchronous machine (example: IBM 650).

In a <u>direct-coupled</u> machine we would represent the values of a digit by a given dc level. For instance, "1" would mean -20v and "0" would mean Ov (Illiac system). Any other correspondence would, of course, be just as good. The name "direct-coupled" stems from the fact that, contrary to pulse machines, no coupling capacitors may be used in the circuits for these cannot transmit dc levels. Note that current levels can be substituted for voltage levels in a dc representation.

Which design philosophy is chosen in a given machine depends on whether we would like to have simple circuits which are harder to service (pulse machines) or more elaborate circuits which are very convenient when it somes to checking their operation (dc-coupled machines). In a pulse machine we must inject pulses and observe their combinations and modifications as they go through the circuits. In a dc-coupled machine we only have to check for the proper behavior of each element using a voltmeter.

It is sometimes alleged that the two level dc representation allows faster operation since the signal only has to change once in order to transmit one <u>bit</u> (= binary digit) of information, while in a pulse the signal has to go up <u>and</u> down. This view is erroneous because the <u>duty cycle</u> of the active elements (transistors, tubes) is as much as "1" in a dc system (i.e., these elements can be on all the time) and less than 0.5 in a pulse system (rise time  $\sim$  fall time, no tops and valleys in a fast system!). At equal average power dissipation, the speeds of the two systems are comparable.

-6-

### 1.3 Memory Systems. Single and Multiple Address Machines

At a first glance it may seem to be useful to have separate memories for numbers and orders (instructions). But if we take account of the fact that the memory stores also intermediate results and that conditional transfers of control often make the sequential read-out of orders impossible anyway, it seems preferable to use the same memory for both orders or numbers (common name "words"). Each order then has to specify the locations of the numbers it has to operate upon; the numerical specification of a memory location is called an <u>address</u>. The storage of orders and numbers in the same memory also makes possible modifications of orders during the calculation.

These memories or <u>stores</u> as they are also called, are divided into two kinds: so-called "<u>random access</u>" memories in which any word can be directly attained and the "<u>back-up</u>" memories in which a given word is contained in a long list which must be scanned. Typically the random access memory consists of magnetized cores (number of bits per word x number of word cores!) the state of magnetization of which represents 0 or 1. Reading out such a memory consists in setting the cores to a standard state and observing the change of magnetization by induced voltages. Another way of storing information in a random access memory is to transform each word into a sequence of dim or bright spots on a TV tube: these cathode-ray-tube memories (also called Williams-tube memories) must be regenerated periodically because they are volatile.

Back-up memories consist almost invariably of magnetic drums or magnetic tapes. In both cases each word is transformed into a sequence of magnetized or unmagnetized spots on a magnetic coating i.e. we have really a glorified tape-recorder. It is evident that both these systems are sequential in nature because we must wait for the drum (tape) to be in the correct position in order to start reading by means of a series of fixed reading heads.

Many modern computers contain a <u>buffer</u> memory between the arithmetic unit and the random access memory in which a certain amount of advanced processing can be done. These "memory plus simplified arithmetic unit" systems are called "look aheads" or "advanced control". They use as their storage medium simplified flipflops ("flow-gating' in Illiac II) or specially fast core memories.

Since all arithmetic operations involve two numbers, a and b, and give a result, c, (c = a + b, a - b, ab, a/b), we would need in the general case five pieces of information for each order:

-7-

- 1) the address of a;

- 2) the address of b;

- 3) the kind of operation to be performed;

- 4) the address to which c shall be sent;

- 5) the address of the next order.

For obvious reasons the above system is called a "4-address system". One can simplify the procedure enormously by introducing certain conventions:

- the address of a is a fixed register in the arithmetic unit (which one may depend on the type of order);

- 2) the address of b is to be given as above;

- 3) the kind of operation is specified as before;

- c is left in a fixed register unless the order specifies that it is to be sent to the memory, in which case a is taken to be in a fixed register;

- 5) the address of the next order is the number immediately following, unless a specific order to "transfer control" is given. The only address specified is then that of the next order; a, b and c are not involved.

A system which uses the above conventions is called a <u>single-address</u> <u>system</u>. It is easy to see that making only part of these conventions, one can obtain two-address and three-address systems.

### 1.4 Past and Present Digital Computers

Calculators of the mechanical type date back to Pascal, who, in 1642 invented an adding machine using toothed wheels to represent numbers. Leibnitz, in 1671, extended the principles used to obtain multiplication. The first time desk calculator was produced by Thomas de Colmar in 1820.

At this time Charles Babbage in England conceived the idea of using punched cards to direct a giant desk calculator in its efforts. The idea of storing programs for looms on cards had been introduced by J. M. Jaccard in 1804: patterns were produced by operating the weft selectors according to rows of punched holes in an endless belt. This machine had such advanced features as transfers of control. On demand the machine would ring a bell an attendant would present to it tables of logarithms, sines etc., again in the form of punched cards. Unhappily the project was abandoned after having spent about \$200,000 on it.

The first working model of a stored program computer was built by Howard Aiken at Harvard: The Harvard Automatic Sequence Control Calculator Mark I. It was used during World War II. It contained a 60' shaft to drive the diverse mechanical units. Bell Laboratories then produced several computers using relays rather than toothed wheels. All these were superseded by ENIAC, built by the Moore School of Electronics at the University of Pennsylvania using tubes exclusively (1946). Remington Rand soon came out with a commercial machine, Univac I and IBM, with some some delay, with its model 650 which is still widely used. Meanwhile John von Neumann, Burks and Goldstine made plans for a very comprehensive machine for the IAS in Princeton: Illiac I is a copy of this machine.

Recently three still more ambitious projects have been completed. IBM has designed its STRETCH computer (150,000 transistors), Remington Rand the LARC (60,000 transistors) and the University of Illinois Illiac II or NIC (30,000 transistors). All these machines have gone to the extreme limit of speed where their dimensions (via the propagation time of electrical signals of 1 mµs/foot) set a bound to their times: All three machines can multiply in less then 10 µs.

Table 1-1 gives some characteristics of well-known machines.

## 1.5 Positional Notation

## Integer Bases

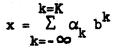

Let  $b \neq 0$ ,  $\pm 1$  be the base or <u>radix</u> of the system. This means that each digit can have n values  $\alpha$  ranging from 0 to n-1 where n = |b|. Denoting by  $\alpha$  the value of  $\alpha$  in the k<sup>th</sup> position and by K the upper limit of k, we can then represent

(1-1)

-9-

# Table 1-1

# Characteristics of Some Well-known Computers

| Name        | Country     | Manufacturer       | Timing   | Multiplication<br>Time | Memory  | Address | <u>A.U.</u> |

|-------------|-------------|--------------------|----------|------------------------|---------|---------|-------------|

| LGP 30      | U.S.A.      | Librascope         | synchr.  | 24000 µs               | drum    | 1       | serial      |

| IBM 650     | U.S.A.      | IBM                | synchr.  | 19000 µs               | drum    | 2       | serial      |

| IBM 704     | U.S.A.      | IBM                | synchr.  | 228 µs .               | cores   | 1       | parallel    |

| Illiac      | U.S.A.      | Univ. of Illinois  | asynchr. | 700 µs                 | el. st. | 1       | parallel    |

| Univac 1103 | U.S.A.      | Remington-Rand     | synchr.  | 290 <b>µs</b>          | cores   | 2       | parallel    |

| Edsac II    | Gr. Br.     | Univ. of Cambridge | synchr.  | 300 µв                 | cores   | 1       | parallel    |

| Besm        | U.S.S.R.    | Inst. Prec. Mech.  | synchr.  | 270 µs                 | el. st  | 3       | parallel    |

| Ermeth      | Switzerland | Polytechn. Zurich  | synchr.  | 16000 µs               | drum    | 1       | parallel    |

$$\alpha_{\mathbf{K}} \alpha_{(\mathbf{K}-1)} \cdots \alpha_{\mathbf{0}} \cdot \alpha_{(-1)} \cdots \qquad (1-2)$$

The "radix" point being immediately to the right of the  $b^0 = 1$  position.

#### Example

3.14 in base 10 is  $3 \times 10 + 1 \times 10^{-1} + 4 \times 10^{-2}$ . In order to distinguish it from 3.14 in base 7 (i.e.  $3 \times 7 + 1 \times T' + 4 \times 10^{-2}$ ) we can write  $3.14_{10}$  and  $3.14_7$  respectively.

The question comes up if any positive number x can be represented by an expansion of the form (1-1) for any value of b (positive or negative) different from 0 and 1. The answer to this problem is given by

<u>Theorem 1</u>: If b is integral  $(\geq 0)$  and  $|b| \neq 1,0$ , any positive number x has an expansion of the form (1-1).

<u>Proof</u>: If expansions exist for x' and x", there exists an expansion for the sum x' + x" which is obtained by the well-known process of "adding each column and taking account of the carries". This latter point is obvious for b > 0. If b is < 0, we can observe that the signs of the terms in (1-1) alternate. Let us take three terms

$$-\alpha'_{(2n+1)} |b|^{2n+1} + \alpha'_{(2n)} |b|^{2n} -\alpha'_{(2n-1)} |b|^{2n-1}$$

in the expansion of x' and

$$-\alpha"_{(2n+1)} |b|^{2n+1} + \alpha"_{(2n)} |b|^{2n} -\alpha"_{(2n-1)} |b|^{2n-1}$$

in that of x" and suppose that to the right of these terms no carries were necessary, i.e. let  $|b|^{2n-1}$  be the term in which for the first time  $\alpha'_{(2n-1)} + \alpha''_{(2n-1)}$  exceeds |b|. In order to carry we have to form  $|b| \times (-|b|^{2n-1}) = -|b|^{2n}$  out of terms to the left. This can be done by observing that  $-|b|^{2n} = -|b|^{2n+1} + (|b| - 1) |b|^{2n}$ . Therefore the carry only influences the two terms to the left. This still holds if the three terms chosen have the sequence of signs -, +, -. A step by step process allows us

therefore to absorb all carries when we form x' + x'', i.e., we can write down explicitly the expansion of the sum. Now we only have to prove that there is always an  $x^* > 0$  as small as we like in the set of all expansions of the form (1-1): this is quite obvious. By summing a sufficient number of these "small  $x^*$  - expansions" we can then come as close as we like to a given x.

#### Positive Fractional Bases. The Most Economical Base

It is not hard to prove that we can extend the above arguments to positive bases of any kind (rational or irrational) if we take

- 1) b > 0.5 (still excluding 1)

- 2) n = 2 minimum and generally n = 2 + [b] [2 + [b] b], where [b] is the greatest integer contained in b. (The above function gives the next highest integer!)

We can then supplement Theorem 1 by

Theorem 2: If b is any non-integral positive number, any arbitrary number x has an expansion of the form (1-1).

<u>Proof</u>: We can always scale down x by division by  $b^{m}$  (m = integer) in such a way that x < 1. Furthermore by the transformation B = 1/b we can reduce the case b < 1 to the case b > 1. Then the expansion will only start to the right of the point and we can find the  $\alpha$ 's by multiplying both sides by b and comparing integral parts.

#### Example

Express  $2_{10}$  in base  $\frac{2}{3}$ . We start by finding the expression in base  $\frac{3}{2}$ , giving us n = 2 i.e. the possible values of  $\alpha_k$  are 0 and 1. Let us first scale 2 by division by  $(\frac{3}{2})^m$  to obtain a quantity less than one: visibly m = 2 is sufficient. Our problem now looks as follows

$$\frac{2}{\left(\frac{3}{2}\right)^2} = \alpha_{-1} \left(\frac{3}{2}\right)^{-1} + \alpha_{-2} \left(\frac{3}{2}\right)^{-2} + \alpha_{-3} \left(\frac{3}{2}\right)^{-3} + \dots$$

By successive multiplication by  $(\frac{3}{2})$  and comparing integer parts we find

$$\alpha_{-1} = 1, \alpha_{-2} = 0, \alpha_{-3} = 0, \alpha_{-4} = 1$$

etc. i.e.

-12-

$$\frac{2}{\left(\frac{3}{2}\right)^2} = 1 \left(\frac{3}{2}\right)^{-1} + 0 \left(\frac{3}{2}\right)^{-2} + 0 \left(\frac{3}{2}\right)^{-3} + 1 \left(\frac{3}{2}\right)^{-4} + \dots$$

or

$$2 = 1 \left(\frac{2}{3}\right)^{-1} + 0 \left(\frac{2}{3}\right)^{0} + 0 \left(\frac{2}{3}\right)^{1} + 1 \left(\frac{2}{3}\right)^{2} + \dots$$

which means that

$$2_{10} = \dots 100 \cdot 1$$

$(\frac{2}{3})$

Note that for a base < 1 the smaller terms lie to the left of the radix point.

An important practical question is: which base b is such that the minimum amount of equipment is necessary to express a given number of numbers M. Let the number of digits be m, then  $M = b^{m}$  (actually  $M = n^{m}$ , but we can take  $b^{m}$  as an approximation). Also bm (actually nm) is an estimate of the amount of equipment necessary. The problem is thus: find b such that bm is minimum subject to the condition  $b^{m} = M$ . Setting bm = u we have

$$u = \frac{b}{lub} \cdot lnM$$

For the most economical b we have  $\frac{du}{db} = 0$ , i.e.

$$\frac{(b \cdot \frac{1}{b} - \ln b) \ln M}{(\ln b)^2} = 0$$

That is:  $\ln b = 1$ , giving b = e = 2.71828....

It is interesting to fix  $M = 10^6$  and to calculate bm for  $b = 2, 3, 4, \ldots$ . The results are given in

## Table 1-2

| b  | bm    |

|----|-------|

| 2  | 39.20 |

| 3  | 38.24 |

| 4  | 39.20 |

| 10 | 60.00 |

-13-

We see therefore that base 2 is a good choice: for once the system dictated by the electronic nature of the number representation is also nearly the most efficient.

## Arithmetic in Other Bases

One can show quite easily that all arithmetic operations can be performed in other bases (see F. E. Hohn, "Applied Boolean Algebra") as long as we take account of the modification of the addition and multiplication table.

#### Example

In base 5 these two tables look as follows:

| + | 0 | l  | 2  | 3  | 4   |     |  | x | 0 | l | 2  | 3  | 4  |

|---|---|----|----|----|-----|-----|--|---|---|---|----|----|----|

| 0 | 0 | l  | 2  | 3  | 4   |     |  | 0 | 0 | 0 | 0  | 0  | 0  |

| 1 | l | 2  | 3  | 4  | 10  | · . |  | l | 0 | 1 | 2  | 3  | 4  |

| 2 | 2 | 3  | 4  | 10 | 11. |     |  | 2 | 0 | 2 | 4  | 11 | 13 |

| 3 | 3 | 4  | 10 | 11 | 12  |     |  | 3 | 0 | 3 | 11 | 14 | 22 |

| 4 | 4 | 10 | 11 | 12 | 13  |     |  | 4 | 0 | 4 | 13 | 22 | 31 |

|   |   |    |    |    |     |     |  |   |   |   |    |    |    |

The multiplication of 143202<sub>5</sub> by 2431<sub>5</sub> can be done by multiplying 143202 by 2 (giving 341404 taking account of the fact that whenever the sum is more than 5, carries are generated), then adding to it - shifted by one digit position - the product of 143202 by 4 etc.

## Conversion of Positive Integers from One Integer Base to Another

It is possible to convert from a base b to a base d by successive divisions by d: the remainders are retained, the first remainder being the least significant digit.

To see this we consider the two equivalent representations of the chosen integer:

$$\sum_{k=0}^{k=K} \alpha_k b^k = \sum_{l=0}^{l=L} \beta_l d^l$$

-14-

Suppose that the  $\alpha_k$  are known and that we want to calculate the  $\beta_1$ . Division by d yields

$$\frac{1}{d} \sum_{k=0}^{k=K} \alpha_k b^k = \beta_L d^{L-1} + \dots + \beta_2 d^k + \beta_1 + \frac{\beta_0}{d},$$

showing that  $\beta_0$  is the remainder after the first division. The same reasoning applies to further divisions. After L + 1 divisions we have then found  $\beta_L \cdots \beta_1 \beta_0$ . Note that all operations are performed in the base b.

There is a special case if  $d = b^m$  (m = integer), e.g. if we convert from binary to octal (2<sup>3</sup>) or sexadecimal (2<sup>4</sup>) bases. The digits can then be arranged in groups of m and each group converted separately:

$$\dots + \alpha_{(2m-1)} b^{2m-1} + \dots + \alpha_{m} b^{m} + \alpha_{(m-1)} b^{m-1} + \dots + \alpha_{1} b + \alpha_{0}$$

$$= \dots + [\alpha_{(2m-1)} b^{m-1} + \dots + \alpha_{m}] b^{m} + [\alpha_{(m-1)} b^{m-1} + \dots + \alpha_{0}] b^{0}$$

## Conversion of Positive Fractions from One Integer Base to Another

The method for converting fractions is quite similar to that for integers, except that successive multiplications by d are performed. To see this we consider the two equivalent representations of the chosen fraction:

$$\sum_{k=1}^{k=K} \alpha_k b^{-k} = \sum_{l=1}^{l=L} \beta_l d^{-l}$$

Suppose that the  $\alpha_k$  are known and that we want to calculate the  $\beta_1.$  Multiplication by d yields

$$d \sum_{k=1}^{k=K} \alpha_k b^{-k} = \beta_{(-1)} + \beta_{(-2)} d^{-1} + \cdots + \beta_{(-K)} d^{-K+1}$$

Showing that  $\beta_{(-1)}$  is the integer part after the first multiplication. The same reasoning applies to further multiplications.

## 1.6 Representation of Numbers in Computers

### Fixed Point and Floating Point Computers

If the base of the number system is b (integral), the registers in the computer contain, for each digit, devices having either b states or a number of combinations of states > b, b out of which are used. The important thing is to have a one to one correspondence between the numerical value of a digit and the states (or combination of states). If m is the number of digits used, all integers between 0 and  $b^{m}$  can then be represented by combinations of digit-values. Usually of course, the representation is such that the successive devices indicate the numerical value of the digits in positional notation.

Rational fractions could be represented by indicating two integers in a given order. Practically this would not be convenient. Since irrational quantities must be represented by approximations anyway, it is usual to use a limited number of digits in the expansion of the rational or irrational quantity to the base b.

Since the product of two numbers of m digits will have more than m digits, the result of multiplications could not always be held in the registers. To avoid the difficulty, all numbers in a problem can be scaled down so that their absolute value is less than one: this means that a "radix point" (decimal point, binary point) is placed in a fixed position in the register and that all admissible numbers must be such that their non-zero digits lie to the right of this point. It should be noted that "<u>overflow</u>" can still occur in division: it is the task of the programmer to avoid this overflow by proper scaling. A computer using the above system of representation is called a <u>fixed point</u> <u>computer</u> for obvious reasons. Often it is possible to consider a given device as an <u>integral computer</u> (representing only integers, point to the right of the least significant digit) or as a <u>fractional computer</u> (with all numbers scaled down, point to the left of the most significant digit) at will: only the interpretation of the digits has to be modified.

In a <u>floating point computer</u> each number x (fraction <u>or</u> integer) is divided into two parts and written in the form

$x = zb^y$  with |z| < 1.

-16-

The registers are then split up and hold z and y separately. Of course, there are limits to the magnitude of the numbers one can represent, since y < m (number of digits in the register). Note that the sign of y must be recorded too.

Floating-point computers are most useful when the magnitude of the numbers involved in a calculation varies widely or when this magnitude is not too well known at the outset, meaning that accurate scaling becomes difficult. Their disadvantage is that fundamental operations like addition or subtraction become quite involved: augend and addend must first be shifted so that their exponents are the same.

Illiac is a fixed-point computer, but it is possible to make it behave like a (slower) floating-point computer by special programming.

#### Representation of Negative Numbers in Computers

There are two common ways of representing negative numbers in a positive base-system (for negative bases the problem is trivial): as signed absolute values or as complements.

The signed absolute value system is difficult to apply in computers (especially of the parallel type). There are two reasons: in a subtraction the computer has no means of recognizing which term has the higher absolute value, meaning that the sign of the difference may have to be changed after the operation. Furthermore the simple process of "counting down" becomes awkward: one has to sense the passage through zero and then change from subtractions to additions, modifying the sign indication. It is interesting to note that the absolute value system implies a "schizophrenic zero": + 0 = -0.

In the complement-system the fact is used that the numbers in the registers are always finite, e.g. a 10-decimal-digit integral machine can hold  $10^{10}$  -1 = 9999 999 999 but not  $10^{10}$ : it performs operations modulo  $10^{10}$ . We can therefore add  $10^{10}$  to any number and the machine representation will not change; to represent a given number initially outside the range we can therefore add or subtract integral multiples of  $10^{10}$ . For example we can represent -3 by  $-3 + 10^{10} = 0\ 000\ 000\ 007$ . As can be seen easily all operations of addition and subtraction can then be performed without contradiction.

-17-

Instead of taking the complement with respect to  $10^{10}$  (called ten's complement), we can take the complement with respect to  $10^{10}$  -1 (called nine's complement). This has some technical advantages: all the digits are treated alike. We see that the ten's complement can be obtained from the nine's complement by adding one unit in the least significant digit. Using the nine's complement introduces a "schizophrenic zero" since 0 000 000 000 and 9 999 999 999 represent the same number.

When the sum of two numbers exceeds  $10^{10}$  -1 the machine no longer indicates the sum modulo  $10^{10}$  -1 but modulo  $10^{10}$ : we can correct this state of affairs by adding one unit to the extreme right-hand digit. This procedure is called end-around carry.

All reasonings in the preceding paragraphs can be applied in the binary system. The two interesting complements are then the two's complement and the one's complement. The latter again necessitates the end-around carry and a schizophrenic zero. It has however the advantage that complementation simply means changing zeros to ones and vice-versa: this can be done without going through the adder.

## Specific Example of a 40-Digit Binary Fixed-Point Representation (Illiac System)

We shall assume that each register holds 40 binary digits and that the binary points is between the first and the second digit on the left. We shall call the digits  $y_0 y_1 \cdots y_{39}$ : then the numbers represented will have the form

We shall only represent numbers the absolute value of which is less than one. All positive numbers will then have a machine representation equal to their binary expansion:

$$\mathbf{x} = \sum_{i=1}^{39} \mathbf{x}_i 2^{-i} = 0 \cdot \mathbf{x}_1 \mathbf{x}_2 \cdots \mathbf{x}_{39}$$

will be represented by setting  $y_0 = 0$  and  $y_1 = x_1$  for  $i = 1 \dots 39$ . The highest positive number we can represent in this way is equal to  $1 - 2^{-39}$  i.e. slightly less than one.

-18-

To represent negative numbers, we add 2. The negative number

$$x = -\sum_{i=1}^{39} x_i 2^{-i} = -0 \cdot x_1 x_2 \cdots x_{39}$$

will therefore be first transformed into the two's complement which we shall call  $\overline{x}$ . Then  $\overline{x} = x + 2$  i.e.

- -

$$\overline{\mathbf{x}} = \mathbf{x} + 2^{0} + 2^{-1} + \dots + 2^{-39} + 2^{-39}$$

$$= 2^{0} + (1 - \mathbf{x}_{1}) 2^{-1} + \dots + (1 - \mathbf{x}_{39}) 2^{-39} + 2^{-39}$$

$$= 2^{0} + \sum_{i=1}^{39} \mathbf{z}_{i} 2^{-i}$$

The representation of this is obtained by setting  $y_0 = 1 (2^0)$  and  $y_1 = z_1$  for  $i = 1 \dots 39$ . The smallest number we can represent is -1. It is now clear why  $y_0$  is called the <u>sign digit</u>: if  $y_0 = 0$  the number is positive, if  $y_0 = 1$  the number is negative.

Let us examine the general relationship between x and the  $y_i$  representation of the machine. For this let us go back to negative numbers:

$$x = \overline{x} - 2 = 2^{0} + \sum_{i=1}^{39} y_{i} 2^{-i} - 2 = -1 + \sum_{i=1}^{39} y_{i} 2^{-i}$$

,

while for positive numbers we have simple

$$x = \sum_{i=1}^{39} y_i 2^{-i}$$

therefore in all cases

$$x = -y_0 + \sum_{i=1}^{39} y_i 2^{-i}$$

(1-3)

-19-

Finally it should be noted how the z<sub>i</sub>'s have been obtained in the case of negative numbers:

$$\sum_{i=1}^{39} z_i 2^{-i} = \sum_{i=1}^{39} (1 - x_i) 2^{-i} + 2^{-39}$$

$\sum_{i=1}^{39} (1 - x_i) 2^{-i}$  is the one's complement of x: this can be seen by remarking that one's are changed to zeros and vice-versa or by taking the complement of x with respect to  $1 - 2^{-39}$ . We can summarize by saying: the machine representation of a negative number  $-0 \cdot x_1 \dots x_{39}$  is the one's complement

1.  $(1 - x_1) \dots (1 - x_{39})$  plus one added in the least significant digit.

#### CHAPTER II

### LOGICAL ELEMENTS AND THEIR CONNECTION

#### 2.1 The Fundamental Logical Elements

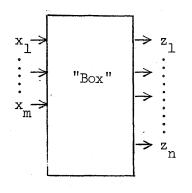

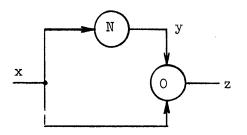

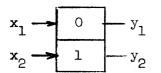

We shall call "logical element" or "decision element" a circuit having m inputs  $x_1 \dots x_m$  and n outputs  $y_1 \dots y_n$ , each input and each output existing only at two possible voltage levels  $v_0$  and  $v_1$ , which will be called "0" level and "1" level respectively. It will be supposed for the moment that all elements are dc-coupled and that the circuits are asynchronous. All lines and nodes can then only exist at the "0" or "1" level.

Each logical element can be defined in a static sense by giving its <u>equilibrium table</u>, i.e. the complete list of simultaneously possible input and output values. This does not necessarily imply that different input combinations give different output combinations or that the output is uniquely determined by the input combination: the element may be a storage element and retain information.

If the equilibrium table contains all possible input combinations and the outputs are uniquely determined by the inputs, we shall speak of a "truth table" and of the element as a "simple logical element" (or combinational element).

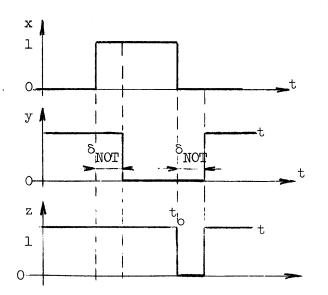

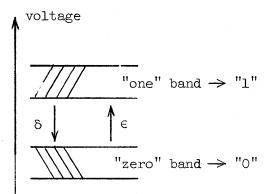

In practice the "O" and "l" levels for different lines may be different and instead of associating "O" with the level  $v_0$  and "l" with level  $v_1$  it may be necessary to associate "O" with a voltage range  $(\overline{v_0}, v_0)$  and "l" with a voltage range  $(\overline{v_1}, v_1)$ , the ranges being nonoverlapping. Also it may be necessary to speak of current ranges instead of voltage ranges.

-21-

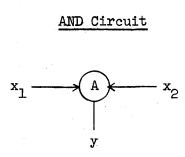

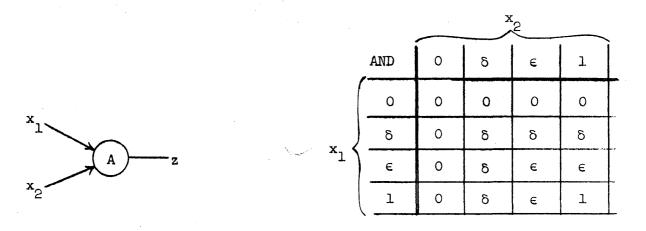

# AND-Circuit, OR-Circuit, NOT-Circuit and Flipflop

We shall examine in this section four fundamental logical elements, three of them (AND, OR, NOT) being "simple logical elements"; the flipflop being of the storage element type.

| Truth Table |  |  |  |  |  |  |

|-------------|--|--|--|--|--|--|

| 7           |  |  |  |  |  |  |

| <b>)</b> .  |  |  |  |  |  |  |

| )           |  |  |  |  |  |  |

| )           |  |  |  |  |  |  |

| L           |  |  |  |  |  |  |

|             |  |  |  |  |  |  |

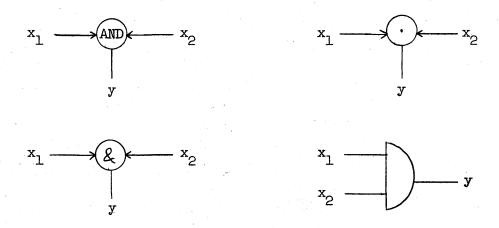

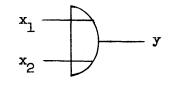

Figure 2-1 AND Circuit

## In order for the output y to be a "l" both inputs $x_1 \text{ and } x_2$ Description: must be "l".

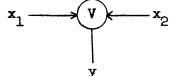

Remark: Other symbols used for this circuit are:

The generalization to multi-input AND's is evident.

-22-

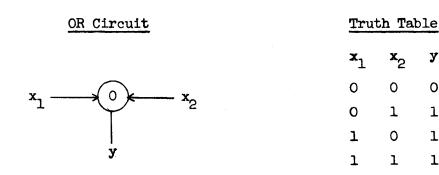

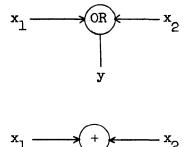

Figure 2-2 OR Circuit

In order for the output y to be a "l" it is sufficient Description: that either  $x_1 \stackrel{\text{or}}{\leftarrow} x_2$  be a "1".

Remark: Other symbols used for this circuit are:

У

0

1

1

1

The generalization is multi-input OR's is evident.

У

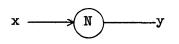

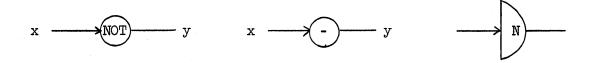

NOT Circuit

Truth Table

Figure 2-3 NOT Circuit

Description: The input is the inverse of the output.

-23-

Remark: Other symbols used for this circuit are:

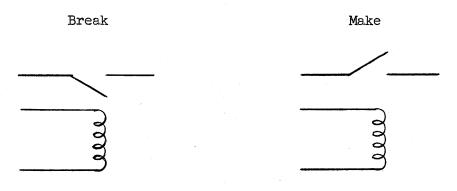

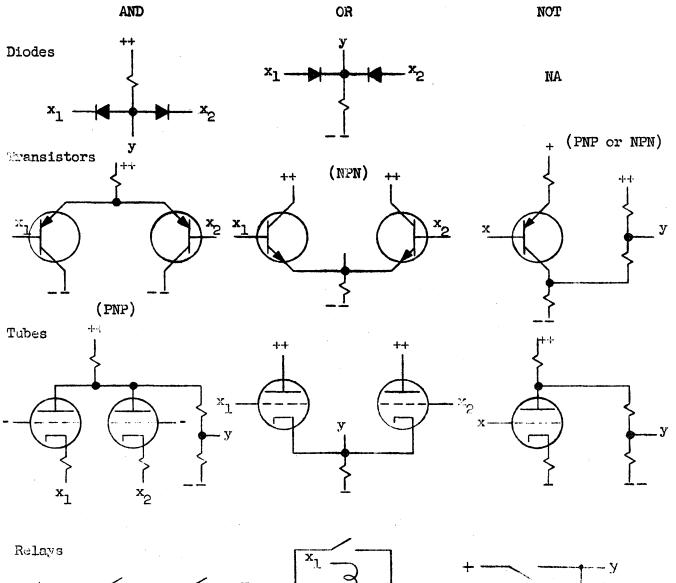

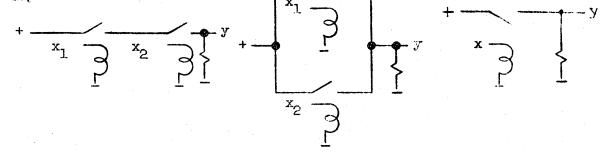

Figure 2-5 below shows how the physical equivalent of these three fundamental circuits can be obtained by the use of diodes, transistors, tubes and relays. It is assumed that two-level dc voltage representation is used with the more positive level corresponding to "1" (so-called "positive logic"). Relays are usually equipped with a contact that is made when the winding is energized ("make" contact) and with one that is broken under these conditions ("break" contact). Figure 2-4 shows these two possibilities symbolically.

Note that a diode NOT is not available: This is due to the fact that dc inversion is only possible in amplifiers. It should also be noted that by going from positive logic to negative logic the circuits producing AND now produce OR and vice versa except in the case of relays. The symbol ++ is meant to indicate a voltage in the lov range, the symbol + a voltage in the lv range. A similar convention applies to -- and -.

فر

AND, OR and NOT and their Hardware Equivalents

for Positive Logic

-25-

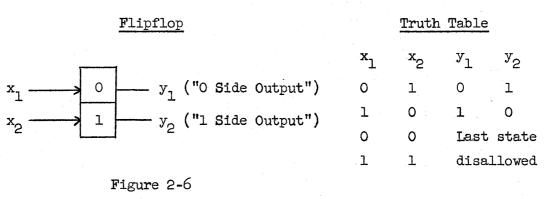

<u>Description</u>: If  $x_1$  and  $x_2$  are different,  $y_1 = x_1$  and  $y_2 = x_2$  (meaning that  $x_1 = 1 \rightarrow y_1 = 1$  etc.). If  $x_1 = x_2 = 0$ ,  $y_1$  and  $y_2$  stay in the preceding state if this has been caused by  $x_1 \neq x_2$ . If the input transition is from 1 1 to 0 0 the outputs will be different, but the two solutions 0 1 and 1 0 are possible; applying the 1 1 input is therefore not recommended.

The flipflop is an element of fundamental importance because it is able to "remember" the state, once it is set: usually both  $x_1$  and  $x_2$  are kept at "0". When  $x_1$  goes to "1" and back again, the element will remain in the state

$\begin{array}{c} y_1 = 1 \\ y_2 = 0 \end{array} \right\} \quad \text{called "O" state of the flipflop.}$

When  $x_{o}$  goes to "1" and back again, the element will remain in the state

$$y_1 = 0$$

$y_2 = 1$  called "1" state of the flipflop.

Practically the input combination  $l \ ($ and therefore the transition  $l \ l \rightarrow 0 \ 0$  which leaves the flipflop in an indeterminate state) never occurs. The state of the flipflop will therefore be "0" or "1" (representing the two possible values of a binary digit), according to the preceding combination.

-26-

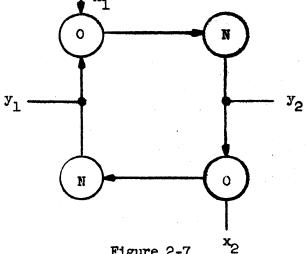

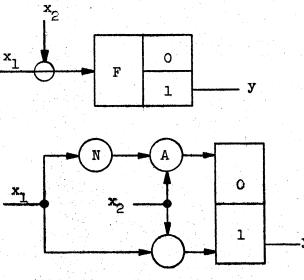

It is interesting to note that a flipflop of the above type can be obtained by a combination of two OR's and two NOT's according to Figure 2-7.  $\mathbf{x}_1$

# 2.2 Gating - Shifting - Counting

## Gating and Shifting

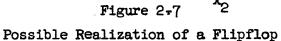

In order to transfer the digits held in one flipflop to another one, we can use the system indicated in Figure 2-8: two AND circuits are used to control the flow of information. For obvious reasons the procedure is called double gating.

Figure 2-8 Double Gating -27When u is made a "l" (gates enabled), the AND circuit connected to the output of the left flipflop which is "l" will apply this to the corresponding input of the right flipflop. When u goes back to "0", the right flipflop stays set.

The other system uses only one AND circuit as a gate but sets the right flipflop to a standard state (e.g. "O") before the gating begins: v is made "l" for a short time and "clears" the right flipflop. After v has gone back to "O", us is made "l". If the state at the left is "l"

Clearing and Gating

the output of the AND circuit becomes a "1" and sets the right flipflop to "1". If the state of the left flipflop is "0", the right flipflop stays in its preceding (cleared) state, i.e. "0". One can, of course, clear to "1" and transfer "0".

The operation of shifting moves the information contained in a register one digital position to the left or to the right. A way to do this is indicated in Figure 2-10, which repeats the pattern of Figure 2-8:

Figure 2-10 Shifting with a Single Register

-28-

The duration of the gating signal u must be carefully chosen: if it is too short, no transfer occurs, if it is too long, transfer over two digital positions may take place.

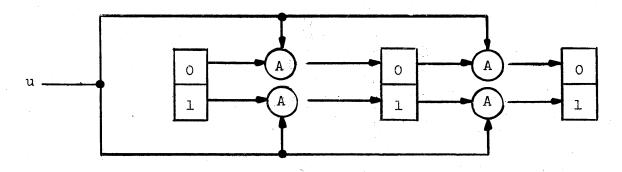

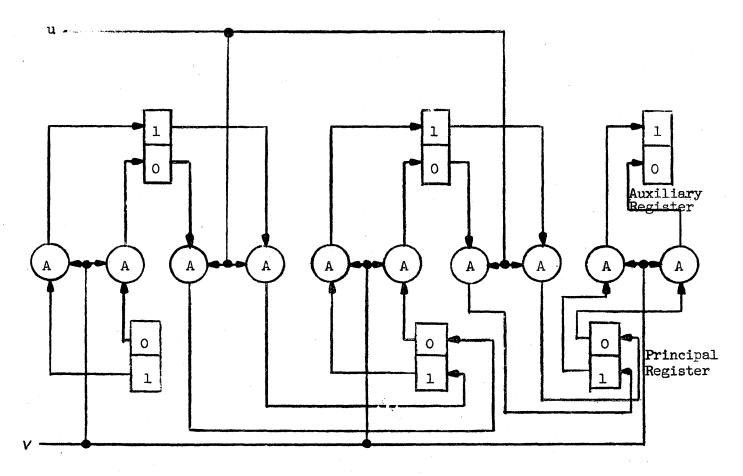

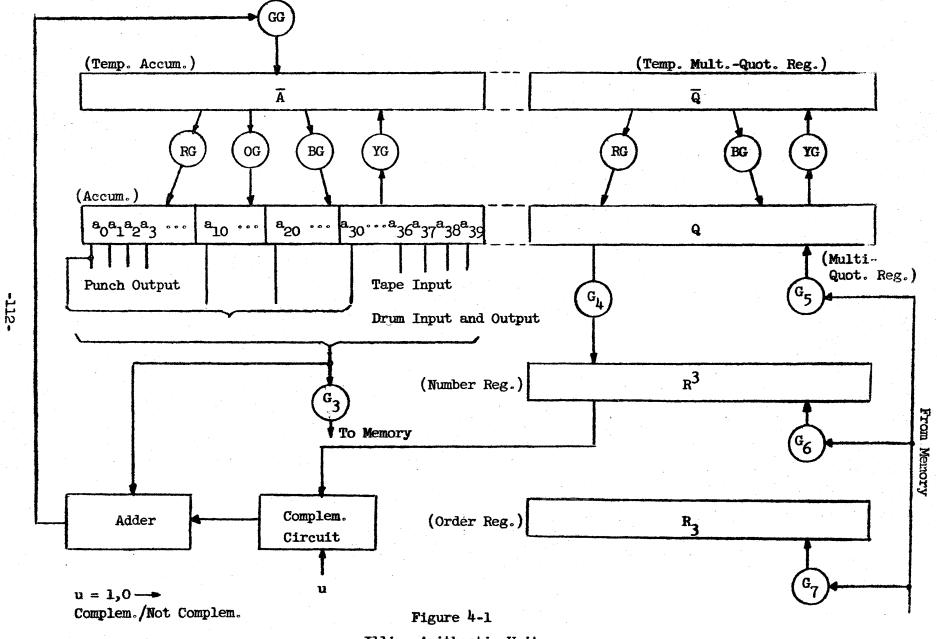

In order to suppress the maximum duration condition, it is feasible to shift in two operations, using an auxiliary register. Figure 2-ll shows the layout. First v is made "1": this produces a transfer of information "straight up". After v has gone back to "0", u is made "1": this produces a transfer of information "right down". The combined effect is that of a right shift. Illiac uses this doubleshifting system, i.e. the registers in which shifting is necessary have an auxiliary or "temporary" register attached to them. Instead of using double gating, Illiac uses clearing and gating.

Figure 2-11 Double Shifting

-29-

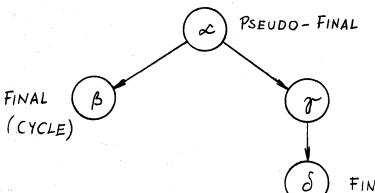

## Counting

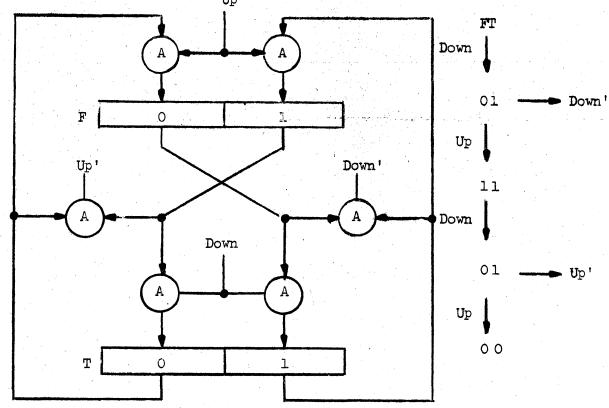

A binary counter is a frequency divider in the sense that each stage has two inputs ("up" and "down") and two outputs ("up prime" and "down prime") and that for a sequence of "1" signals applied successively to down-up-down-up it gives just <u>one</u> "1" on "down prime" and <u>one</u> on "up prime" i.e. divides the number of applied "1's" by two. With n cascaded stages we can then divide the number of "1's" by 2<sup>n</sup>.

One stage of such an asynchronous binary counter is given in Figure 2-12. At the beginning of the process both flipflops (called "false toggle" -F and "true toggle" -T respectively) are set to 0. The "up" pulse sets F to agree with T while the "down" pulse sets T to disagree with F. The sequence of states is thus 0 0, 0 1, 1 1, 1 0 and back to 0 0. If we connect the 0 1 and 1 0 output signals as "up prime" and "down prime" to a similar circuit, we will have achieved a frequency reduction by 2.

-30-

### 2.3 Adding and Subtracting

When adding two binary digits  $x_i$  and  $y_i$  we obtain a sum digit  $s_i$  and a carry digit  $c_{i-1}$ . The relation between  $x_i$ ,  $y_i$ ,  $s_i$  and  $c_{i-1}$  is given by the table below.

| Bina    | Table          |                |      |

|---------|----------------|----------------|------|

|         |                |                |      |

| x.<br>i | y <sub>i</sub> | <sup>s</sup> i | °i-l |

| 0       | 0              | 0              | 0    |

| 0       | l              | l              | 0    |

| 1       | 0              | 1              | 0    |

| l       | 1              | 0              | l    |

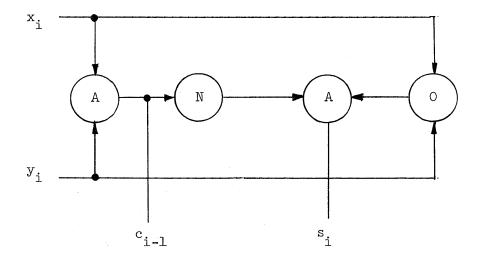

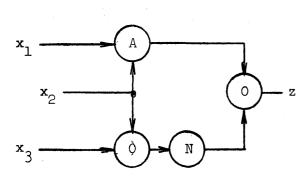

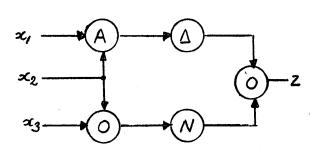

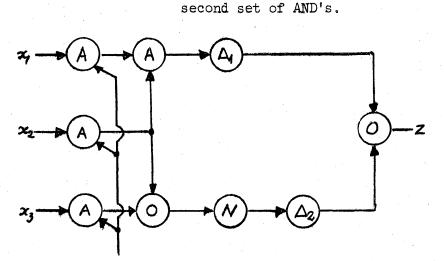

Later on we shall discuss methods which permit us to find the combinations of AND, OR and NOT circuits having given properties by deductive reasoning. Here we shall simply give the result: Fig. 2-13 shows what is called a "half adder." We see by direct inspection that (as required by the table)  $c_{i-1}$  is only "1" when both  $x_i$  and  $y_i$  are "1."  $s_i$  is "1" when  $x_i$  or  $y_i$  is "1," for then the inputs to the right AND circuit are both ones.

Figure 2-13. Half-Adder

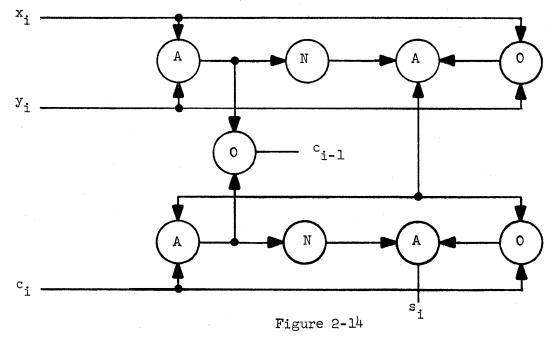

In order to obtain the logical diagram for one digital position of a binary adder, we have to use 2 half-adders since we have to add in the carry c<sub>i</sub> from the preceding stage according to the adjoining table. Figure 2-14 gives the layout: as can be seen, the sum output of the

| Binary         | Addition       | Table          | with           | Carry-in         |

|----------------|----------------|----------------|----------------|------------------|

| × <sub>i</sub> | y <sub>i</sub> | ° <sub>i</sub> | s <sub>i</sub> | c <sub>i-l</sub> |

| 0              | . 0            | 0              | 0              | 0                |

| 0              | 0              | 1              | 1              | 0                |

| 0              | l              | 0              | l              | 0                |

| 0              | 1 .            | 1              | 0              | 1                |

| l              | 0              | 0              | l              | 0                |

| l              | 0              | 1              | 0              | l                |

| 1              | 1              | 0              | 0              | 1                |

| 1              | 1              | 1              | l              | 1                |

|                |                |                |                |                  |

first half-adder and the carry-in are the inputs to the second half-adder. c<sub>i-1</sub> is taken from either one of the half-adders through an OR circuit this corresponds to the two possibilities of formation of carries.

Logical Diagram for One Digital Position of a Binary Adder

-32-

## Complementation and Subtraction

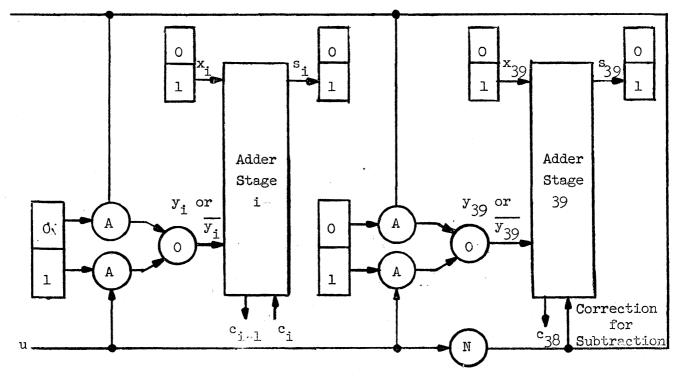

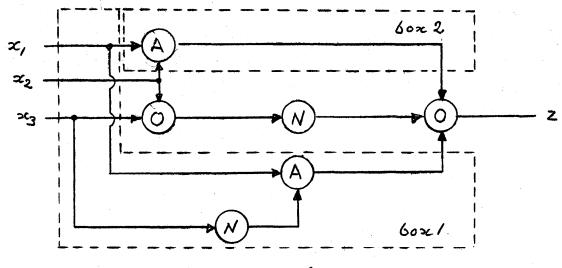

The inputs  $x_i$  and  $y_i$  in the preceding section come from two flipflops having the same digital position i but pertaining to two different registers. More precisely: x, and y, are taken from the "1 side output" of these flipflops. If we want the digitwise complements -which we shall denote by  $\overline{x_i}$  and  $\overline{y_i}$  respectively  $(x_i = 0 \ \overline{x_i} = 1, x_i = 1 \ \overline{x_i} = 0!)$ -we only have to take the "O side output". We saw in Section 1.6 that negative numbers are represented in Illiac as complements of 2 and that all one has to do to obtain the representation of -0,  $x_1 \dots x_{39}$  is to take the digitwise complement and then add one in the least significant position. Since subtraction is the addition of a negative number, we can switch from the addition x + y to the subtraction x - y by taking as inputs to the adderstages  $\overline{y_i}$  instead of  $y_i$ . To add one in the least significant position we provide the stage i = 39 with a carry input (which, of course, is not used in addition). Figure 2-15 shows how, by the use of a complementing circuit using two AND's and one OR per digit position, we can perform additions and subtractions. One adder stage is represented by a box with 3 inputs and 2 outputs. If u = 1 the circuit adds, if u = 0 the circuit subtracts.

## Figure 2-15

Addition and Subtraction Using Complementing Circuits

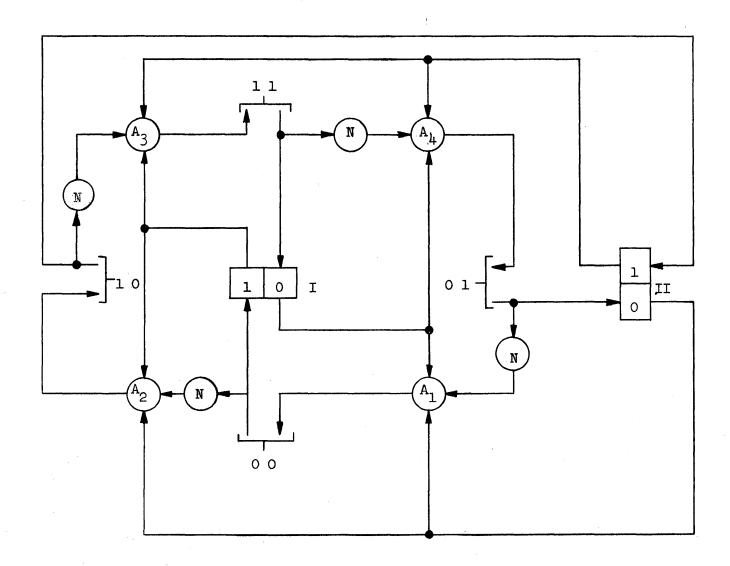

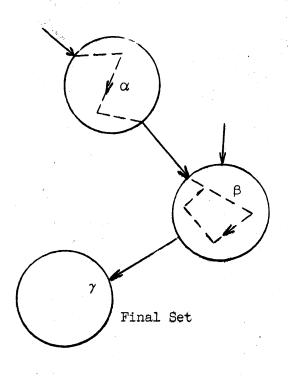

## 2.4 Decoding and Sequencing

In 2.2 we examined the clearing and gating procedure. It happens very often in an asynchronous computer of the Illiac type that a sequence of 4 signals "clear-gate-clear-gate" is required, these signals being non-overlapping and the next step being initiated only after we know that the preceding one has been completed. The four-step sequencing circuit of Figure 2-16 shows how the desired result is obtained.

First consider the combination of flipflops and four AND circuits  $A_1 \dots A_4$  i.e. leave the NOT circuits aside. The flipflops give 4 different combinations and for each combination one and only one AND circuit has a "1" output:

| <u>FF I</u> | <u>FF II</u> | Al | A_2 | <u>A</u> <u>3</u> | A <sub>4</sub> |

|-------------|--------------|----|-----|-------------------|----------------|

| 0           | 0            | l  | 0   | 0                 | 0              |

| 1           | 0            | 0  | 1   | 0                 | 0              |

| 1           | l            | 0  | 0   | 1                 | 0              |

| 0           | 1            | 0  | 0   | 0                 | l              |

|             |              |    |     |                   |                |

This output goes out into other parts of the machine and comes back with a "<u>return-signal</u>" or "<u>reply-back-signal</u>". We can imagine that a certain group of gates is enabled and that one of the gate outputs is used as a return signal. This return signal modifies one and only one flipflop and therefore produces the next combination, i.e. energizes the next AND circuit. If we now put in the NOT circuits (making 3 input AND circuits out of 2 input AND circuits) the next AND circuits can only give a "1" output, if the return signal of the preceding operation has gone back to "0": this guarantees non-overlapping "1" signals at the output of the AND circuits. Notice that connecting the returns to the outputs gives a "free-running" pulser with a 4 phase output.

-34-

Figure 2-16 Four Step Sequencing Circuit

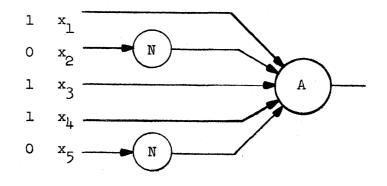

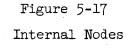

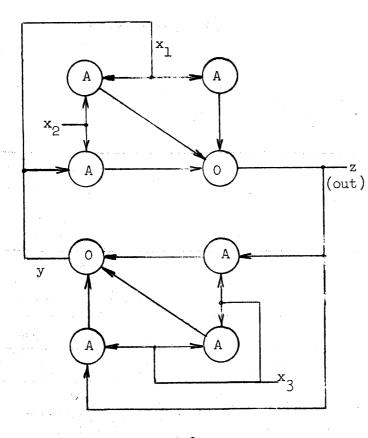

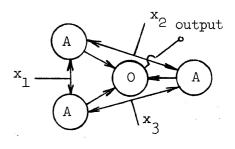

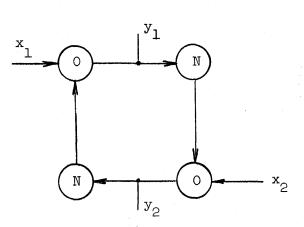

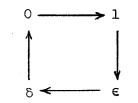

What is essentially done in the circuit of Figure 2-16 is that the two flipflops are cycled through all combinations of states, that each combination energizes one and only one AND circuit and that this signal (after some delay) steps the flipflops to their next state. This detection of certain combinations of output signals was already encountered in the last section in the asynchronous counter: such a detection of given combinations of signals is called <u>decoding</u>. The general problem of detecting whether n wires  $x_1 \\ \dots \\ x_n$  have a given combination of zeros and ones can be solved by the use of an n input AND circuit into which are led directly all those wires where a "1" is required, while those requiring a "0" a connected via a NOT circuit. Figure 2-17 shows a decoder for the input combination 10110 on five wires.

Figure 2-17 Decoder for a 10110 Combination

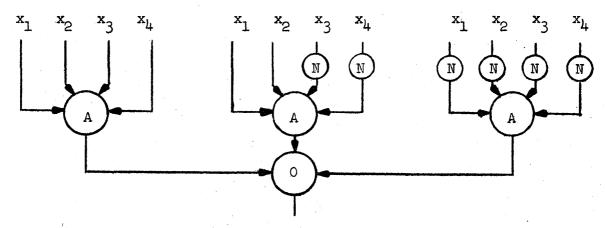

If it is desired to obtain a "1" output for several different combinations, one can clearly design a circuit as the one shown in Figure 2-17 for each combination and then combine the output of all AND's by a multiple input OR circuit. Figure 2-18 shows a circuit giving a "1" for the 3 input combinations 1111, 1101 and 0000.

Figure 2-18 Circuit Detecting Several Input Combinations

-36-

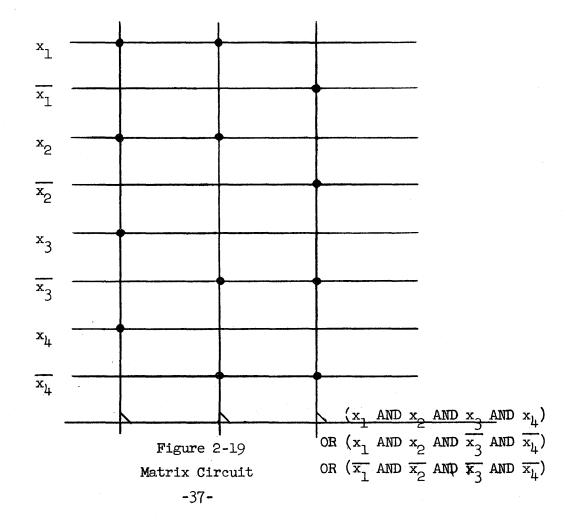

Since visibly for n inputs  $x_1 \cdots x_n$  the possible input lines to the AND's are either direct or complemented (i.e. inverted), all possible combinations n at a time can be formed by providing 2n lines  $x_1 \overline{x_1}, x_2 \overline{x_2} \cdots$  etc. and having one wire of each pair go to an n-input AND circuit. It is customary to symbolize such a decoding circuit by a matrix of 2n lines (the horizontal lines in Figure 2-19) connected to  $x, \overline{x_2} \cdots \overline{x_n}$  intersected by a second set of lines (the vertical lines in Figure 2-19) which symbolize the AND function, which input being used being determined by a dot at the appropriate intersection. Such a circuit is called a matrix circuit for obvious reasons.

<u>Remark</u>: Often the combination of the diverse AND outputs by an OR is symbolized by a line parallel to the 2n lines with short segments determining the choice of OR inputs. Figure 2-19 repeats 2-18 in this notation.

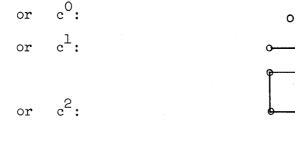

Often it is useful to introduce the notion of complexity of a circuit by the rule

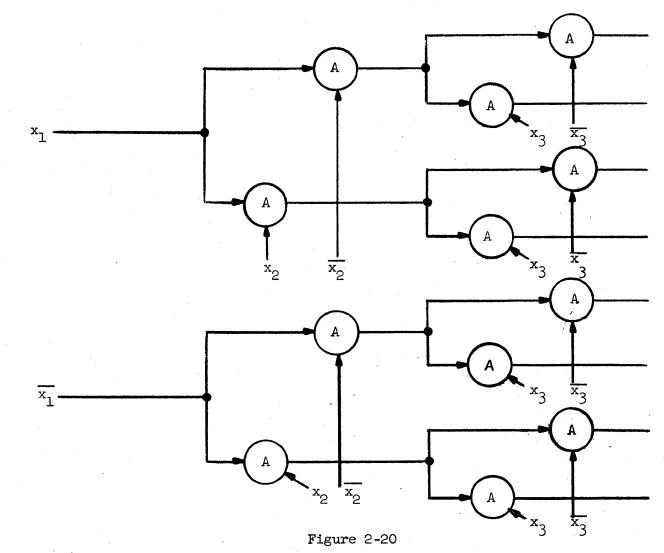

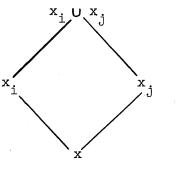

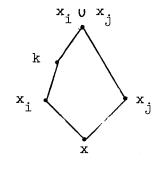

Supposing that we wanted to form all  $2^{4}$  input combinations in Figure 2-19, we would visibly need  $2^{4} \times 4 = 64$  inputs i.e. the complexity for an n-input circuit would be  $2^{n} \times n$ . It turns out that for n > 3 it becomes advantageous to decode by a <u>tree</u> or pyramid as shown in Figure 2-20. It is not too difficult to show that here all input combinations can be formed with complexity  $2^{n+2}$  - 8 which is less than  $n2^{n}$  if n > 3.

Tree or Pyramid Forming all Combinations of 3 Variables

-38-

#### 2.5 Complex Logical Elements

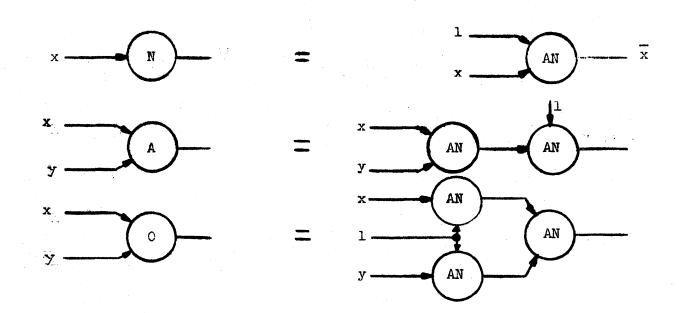

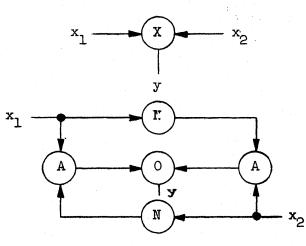

The preceding sections have shown that all the fundamental operations in a computer can be done using AND, OR, NOT and FF elements, the latter being actually a feedback combination of OR and NOT. It is easy to show that a single element, namely an AND-NOT or an OR-NOT (NOR) is sufficient to perform all functions: in order to do this we only have to show that AND, OR and NOT can be constructed. Figure 2-21 shows how AND-NOT's can be used.

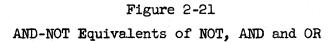

Usually it is not very wise to reduce all functions to combinations of AND-NOT or OR-NOT. To the contrary: designers often introduce new elements which can be made up out of simpler ones but which occur so often that a special name is given to them. We shall introduce them by their truth table together with an equivalent combination of AND's, OR's and NOT's.

# Equivalence Circuit

Description: The output is "1" if and only if the two inputs agree.

Exclusive OR

Figure 2-23 Exclusive OR and Equivalent

Description: The output is "1" if one or the other but not both of the inputs are "1".

### Truth Table

| x | <b>x</b> 2 | У |

|---|------------|---|

| 0 | 0          | 0 |

| 0 | 1          | 1 |

| 1 | 0          | 1 |

| 1 | 1          | 0 |

-40-

<u>Remark</u>: It is easily seen that an equivalence circuit becomes an exclusive OR or vice-versa if one of the inputs is inverted.

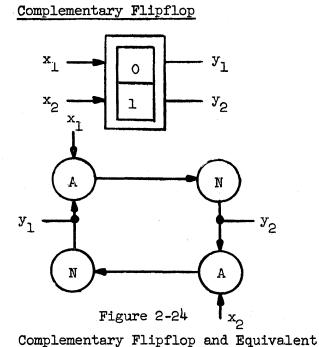

Truth Table

| ×1 | x <sup>5</sup> | у    | ъ      |

|----|----------------|------|--------|

| 0  | 1              | 0    | 1      |

| 1  | 0              | 1    | 0      |

| l  | l              | last | state  |

| 0  | 0              | disa | llowed |

<u>Description</u>: If  $x_1$  and  $x_2$  are different,  $y_1 = x_1$  and  $y_2 = x_2$ . If  $x_1 = x_2 = 1$ ,  $y_1$  and  $y_2$  stay in the preceding state if this has been caused by  $x_1 \neq x_2$ . If the input transition is from 0 0 to 1 1 the outputs will be different, but the two solutions 0 1 and 1 0 are possible; applying the 0 0 input is therefore not recommended.

<u>Remark</u>: The complementary flipflop differs from the flipflop discussed in 2.1 by the interchange of  $1 \ 1$  for 0 0 for the "hold" condition and that of 0 0 for 1 1 for the disallowed condition.

-41-

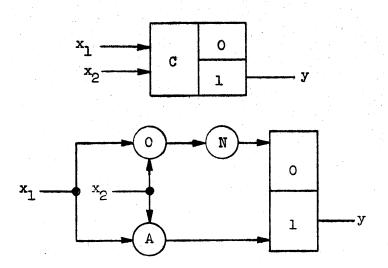

C Element

$\begin{array}{cccc}

\underline{\text{Truth Table}} \\

\mathbf{x}_1 & \mathbf{x}_2 & \mathbf{y} \\

0 & 0 & 0 \\

1 & 1 & 1 \\

0 & 1 & 1 \\

1 & 0 & 1 \\

1 & 0 & 1 \\

\end{array}$   $\begin{array}{c}

\text{Iast state} \\

1 & 0

\end{array}$

<u>Description</u>: When  $x_1$  and  $x_2$  coincide, the output follows the input. When  $x_1 \neq x_2$ , the last state is remembered.

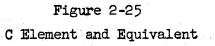

F Element

| Tru | th Tal | ble          |

|-----|--------|--------------|

| ×l  | ×2     | У            |

| 0   | 1      | 1            |

| 1   | 1      | 1            |

| 0   | 0      | last state   |

| 1   | 0      | A TUST STATE |

Figure 2-26 F Element and Equivalent

<u>Description</u>: If  $x_2 = 1$ , the output follows the input  $x_1$ . If  $x_2 = 0$ , the last state is remembered.

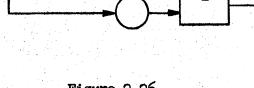

It will become apparent in the discussion of whole systems of logical elements that it is not possible to use great numbers of cascaded AND's or OR's (i.e. such circuits connected in series) because in many such circuits (diode circuits as shown in Figure 2-5) the signals are slowly thrown out of the permissible bands due to voltage drops etc. In order to "renormalize" such a signal it becomes then necessary to insert an amplifier or "level restorer". This can only be circumvented if a NOT circuit is present in the chain: we know from Figure 2-5 that this implies amplification. The two symbols of Figure 2-27 represent renormalizing amplifiers. It should be noted that logically these circuits have the same properties as a piece of wire, i.e. y = x.

Figure 2-27 Symbols for an Amplifier or Level Restorer (Non-inverting)

-43-

#### Separate Carry Storage

It is easily verified that the 1/2 adder AND-NOT-AND-OR combination of Figure 2-13 can be replaced by an exclusive OR in parallel with an AND: the latter will give the carry while the exclusive OR gives the sum. Figure 2-14 can therefore be redrawn as in Figure 2-28.

#### Figure 2-28

One Digit Position of a Binary Adder Using Exclusive OR's

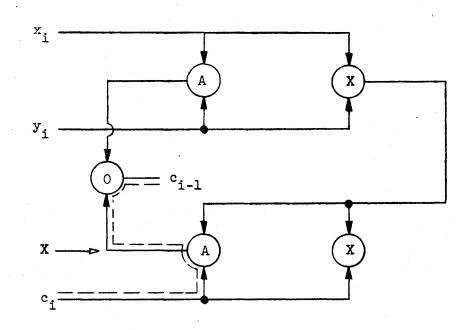

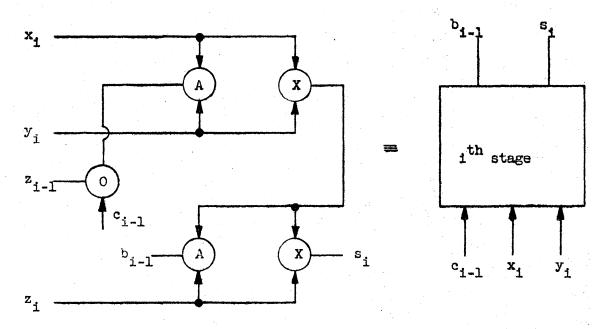

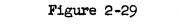

Quite visibly  $c_i$  influences  $c_{i-1}$  via the dotted path: this corresponds to the well known fact that if we add 0 and 1 in a given stage and there is a carry from the last digit position, there will be a "propagated carry". Under some circumstances a carry can possibly be propagated through the whole register i.e. from the least significant digit to the most significant digit. Such a propagation can take a great amount of time and operations in which repeated additions occur (like multiplication) are excessively slowed down. A way around this difficulty is to sever the carry propagation path in X and dump the output of the AND into a separate flipflop. If we make the input to the OR "O" we shall then simply have a "pseudo-sum" coming out of  $s_i$  while the carry is stored separately; considering the whole adder and its registers we would then have a register holding  $x_i$ 's, one holding  $y_i$ 's, a "pseudo-sum" register holding the  $s_i$ 's and finally a carry storage register holding the output - say  $b_{i-1}$  - of the lower AND. At each moment the read sum could be obtained by adding the "pseudo-sum" to the separate carries.

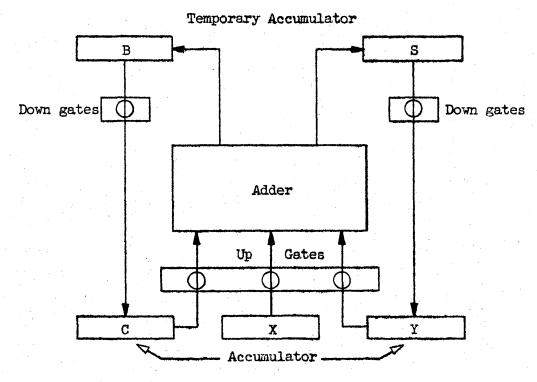

In order to be useful in repetitive addition it is desirable to have an adder which allows a number to be added to another one stored in the separate-carry-pseudo-sum manner. It is clear that this can be achieved by using the arrangement of Figure 2-29 in which the OR circuit is used to absorb the carries from a previous addition. The signal  $z_{i-1}$ coming out of this OR visibly only affects the next stage since the carries out of stage i (i.e. the signal b<sub>i-1</sub>) is again stored separately. Figure 2-30 gives the connections to be used if the number in X is to be added again and again to itself. Initially registers C and Y are cleared and then they hold successively (in pseudo-sum-separate-carry form) 2, 3 etc. times the contents of X: They correspond to what is ordinarily called the accumulator. Registers B and S are - together - the temporary accumulator. By alternating between the up and the down gates, we can cycle through as many additions as desired. At the end the sum is obviously obtained in two parts and more equipment is needed to "absorb the carries". One way of doing this is to use the contents of C and Y as the inputs to a classical adder.

## Borrow Storage Counter

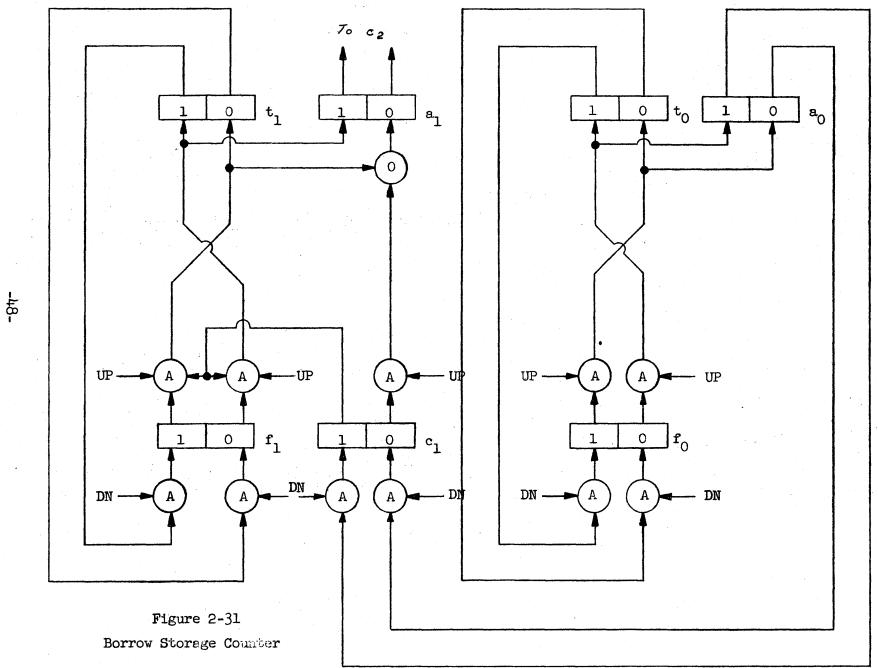

It is easy to see that problems of carry propagation also affect the counter of Figure 2-12, i.e. its speed of counting is limited by a possible carry propagation over all stages. D. E. Muller of the University of Illinois has extended the idea of separate carry storage

-45-

One Stage of a Separate Carry Storage Adder

Accumulator and Adder in a Separate Carry Storage System

to counters. Figure 2-31 shows the last two stages of such a counter. There are again two principal flipflops per stage: The true toggle t, and the false toggle f, and they are connected in the usual fashion, i.e. a down shift (DN-pulse) sets f, to agree with t, while an up shift (UP-pulse) sets t, to disagree with f. There is, however, a major difference: no decoding is used to obtain frequency division and furthermore the counter counts down from a number initially set in ... b2 b1 b0. This counting down would visibly necessitate borrows at certain stages of the game: These borrows are stored separately in ...  $a_2 a_1 a_0$  (or, after a down shift, in ...  $c_2 c_1 c_0$ ). The effect of such a borrow is to permit a shift from  $f_i$  into  $t_i$  and simultaneously  $a_i$ , while  $c_i = 0$  inhibits this transfer and sets  $a_i$  to 0. One can see (see table below) that if to these rules we add an "unconditional" last stage in which  $t_{\bigcap}$  and  $a_{\bigcap}$  always receive the complement of  $f_{\bigcap}$  on an up shift, the result will be a counting operation in which the number held at any given moment is

$[\dots t_2 t_1 t_0] - 2 [\dots a_2 a_1 a_0]$

At the beginning all registers are cleared to 0 and the number n to be counted down from is set into  $\dots t_2 t_1 t_0$ . At the end (i.e. after n UP and n DN pulses) the upper register indicate zero. One more down pulse is sufficient to also clear the lower register to zero, thus readying the counter for a new counting operation. In the table below the state of all flipflops is shown in counting down from 3. The column t indicates [...  $t_1 t_0$ ] while a indicates [...  $a_1 a_0$ ].

-47-

# Table 2-1

Operations in a Borrow Storage Counter

|    | tl             | al | to             | <sup>a</sup> O | t | 2a    |

|----|----------------|----|----------------|----------------|---|-------|

|    | f <sub>l</sub> | °l | f <sub>0</sub> |                |   |       |

|    | l              | 0  | l              | 0              | 3 | 0     |

|    | 0              | 0  | 0              |                |   | :<br> |

| ţ. | l              | 0  | l              | 0              | 3 | 0     |

| •  | 1              | 0  | 1              |                |   |       |

| ľ  | l              | 0  | 0              | 0              | 2 | 0     |

|    | 1              | 0  | l              |                |   |       |

| ł  | 1              | 0  | 0              | 0              | 2 | 0     |

| ŧ  | 1              | 0  | 0              |                |   |       |

|    | l              | 0  | l              | l              | 3 | 2     |

| ţ  | 1              | 0  | Ö              |                |   |       |

|    | · 1            | 0  | 1              | 1              | 3 | 2     |

| t  | . l            | l  | i              |                |   |       |

| ľ  | 0              | 0  | 0              | 0              | 0 | 0     |

| l  | . <b>1</b>     | l  | 1              | •              |   |       |

|    | 0              | 0  | 0              | 0              | 0 | 0     |

|    | 0              | 0  | 0              |                |   |       |

-49-

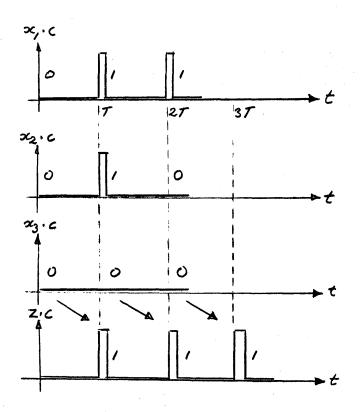

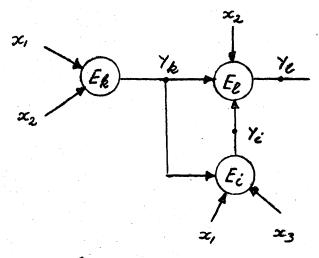

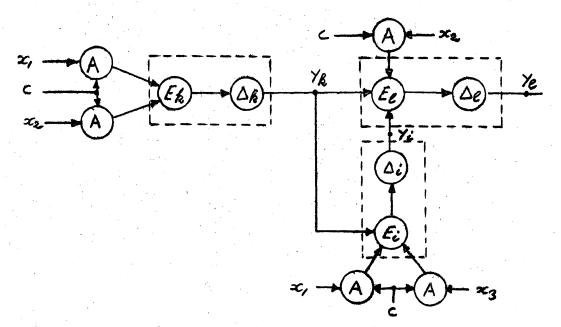

## Interlaced Sequencing

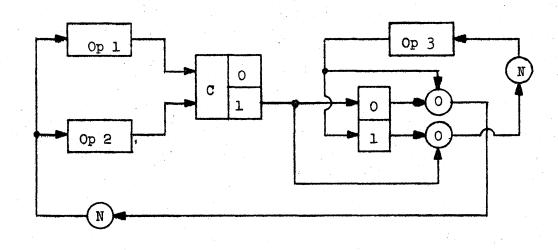

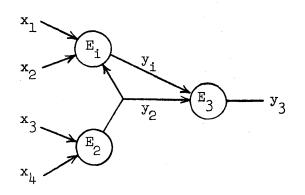

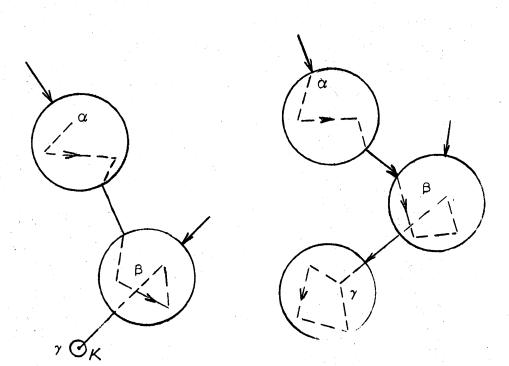

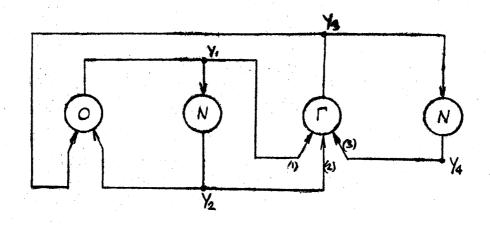

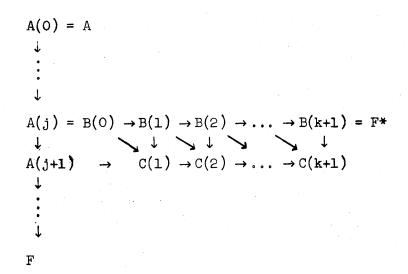

It is often necessary to alternate a given operation (Op 3) with two other (Op 1 and Op 2) in such a fashion that if and only if both Op 1 and Op 2 have occurred it becomes possible to do Op 3. Vice versa: Op 3 must be terminated before Op 1 or Op 2 can even start. In such circumstances we speak of interlacing and write

$$\begin{array}{c} Op 1 \\ \\ \\ Op 2 \end{array} \right\} Op 3 \left\{ \begin{array}{c} Op 1 \\ \\ \\ Op 2 \end{array} \right\} Op 3 \ldots$$

Figure 2-32 shows a possible sequencing circuit having all the required properties. It is "speed independent" in the sense that no requirements whatsoever have to be placed on the relative speeds of operation of the logical elements. We can think of the boxes marked Op 1 etc. as being simply in-phase amplifiers introducing a certain time lag (equal to the time required to do the corresponding operation).

Figure 2-32 Circuit for Interlaced Sequencing

-50-

The operation of this circuit is as follows. Suppose that Op 1 and Op 2 have occurred, injecting two "1" signals into the C-element: The output of this element now sets the flipflop into the "O" state thus making the input to the lower NOT "1" and the input to Op 1 and Op 2 "O" (after some time this makes the upper input to the flipflop "O" again). As the flipflop changes state, its lower output becomes zero and this zero, together with reply back zero mentioned above, finally allows the upper NOT to energize the input to Op 3. This sets the flipflop back into the one state, thus cutting off the input to Op 3 and after the output of Op 3 has also gone back to zero the lower NOT receives a zero input and starts up Op 1 and Op 2 again.

### 2.7 Dynamic (Synchronous) Logic

Up to now no major difficulties resulted from the fact that no information concerning the operation time of individual logical elements was available: we talked essentially about asynchronous circuitry. Very often savings in both time and equipment can be obtained by specifying the delays signals suffer in the logical circuitry, at least to the extent of making sure that an ordering relationship is known i.e. if two parallel signal paths are present it is known which one is faster. Often such an ordering is obtained by inserting into one of them suitably chosen delay elements. We shall discuss below some of the more common dynamic circuits.

Delay Element

У

Figure 2-33 Delay Element The delay element shown in Figure 2-33 is essentially an amplifier which is slowed down by capacitive loading of the output or intermediary points or it is a transmission line formed of lumped L and C elements adjusted to give a given delay between the input and the output. In the following discussions we shall assume that delay elements have amplification. Often  $\Delta$  indicates the time delay in seconds.

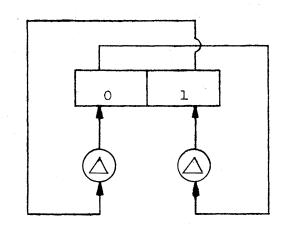

Free Running Multivibrator (Clock)

Figure 2-34 Free Running Multivibrator

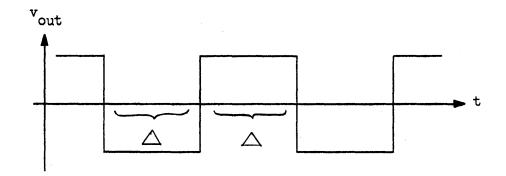

Figure 2-34 shows a flipflop whose outputs are coupled back to the opposite inputs via delay elements (here we shall assume them equal). Visibly the operation cycle consists of the following steps: suppose that the flipflop has just been set into the "1" state. After a given delay  $\Delta$  the new outputs i.e. 0 l will arrive at the input in the form 1 0 and switch the flipflop back to the "0" state. This gives a 1 0 output which comes back - after the delay - in the form 0 l which again sets the flipflop to "1". If the setting time of the flipflop can be neglected, the oscillations at either the "0" or the "1" side of the flipflop are as shown in Figure 2-35; they have the period  $2\Delta$ . The fact that the

#### Figure 2-35

Symmetric Oscillations of a Free Running Multivibrator

pulses are of regular duration makes such a free running multivibrator useful as a clock, i.e. a timing control for the operations in a computer. In the circuits below we shall often assume the existence of such a clock.

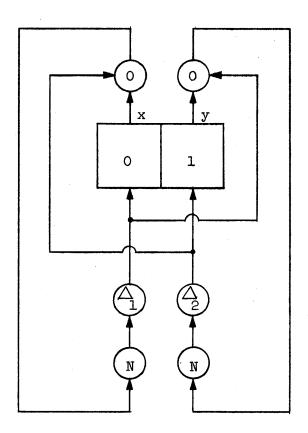

Actually there is trouble in the circuit of Figure 2-34 if the two delays are different and since it is impossible to design these delays to be exactly equal, it is better to make provision for the more general case. Figure 2-36 shows a possible solution and Figure 2-37 the waveforms. Note that this time the two outputs, X and Y, have no longer the same shape. The operation of this circuit can be understood from the "interlaced sequencing" circuit of Figure 2-32, except that Op 2 does not exist, making the C-element useless.

Figure 2-37

Asymmetric Oscillations of a Free Running Multivibrator (Positive Logic)

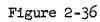

#### Regenerative Broadening

A common problem is to lengthen a pulse to make it as long as a clock pulse, i.e. to design a circuit which, if at the beginning of the clock pulse a "1" is present, stretches this "1" to the full extent of the clock pulse even if the sampled pulse disappears during this clock pulse. Figure 2-38 shows such an arrangement using an AND and an OR. Note that practically an amplifier is needed in the feedback loop.

Figure 2-38 Regenerative Broadening

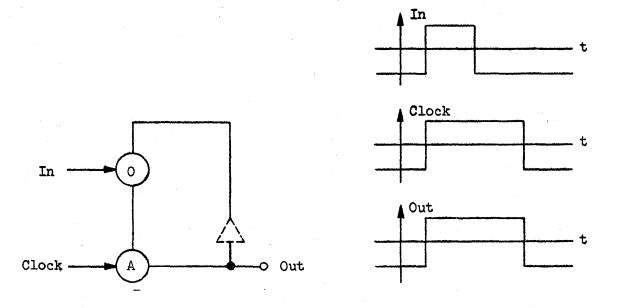

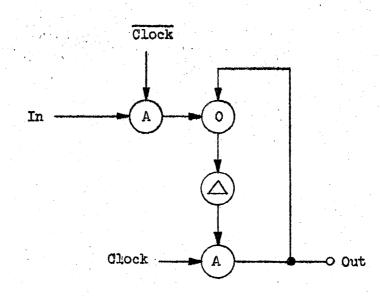

#### Latch Circuit

A more sophisticated version of the circuit described above is the latch, which differs in that the clock pulse cannot only "capture" a "1" and hold it even if the input goes back to "0", but also "capture" a "0" and hold it in the event that the zero actually changes to a one during the clock pulse. Figure 2-39 shows the layout: note that here a delay has to be used in order to make sure that the AND in the feedback loop can receive a "1" from the clock and also a "1" from the input sampled while the clock was still "0" (Clock = 1  $\rightarrow$  Clock = 0 and vice-versa!). It should also be remarked that this delay should be just long enough to allow sufficient overlap to start regeneration. Often the delay is obtained by a suitably designed amplifier (which must be used in the feedback loop as we saw above). This circuit,

Figure 2-39 Latch Circuit

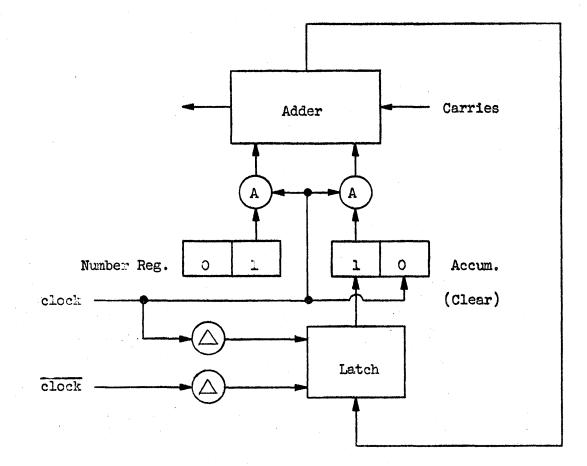

which can therefore latch onto a "1" or a "0"; conserves during the whole clock pulse the information present at its beginning. A useful application is shown in Figure 2-40 in which an accumulator register feeds information into an adder (the second input coming from a fixed number register). The output of the adder goes into a latch circuit. It is easily seen that no gates are needed between the adder and the latches preceding the accumulator, since the clock time can be chosen such that the output of the latches sets the accumulator, but that this new setting does not "race" through the adder to produce the next set of inputs, the latches having sampled the information at precisely the instant at which the adder settles down for the first time. The delay  $\Delta$  is chosen equal to the longest expected delay in the adder.

-56-

Figure 2-40 One Clock Period Adder Using a Latch

# 2.8 Synchronous Serial Operation

The full advantages of synchronous logic can be reaped by using a serial i.e. sequential processing of information pulses. This implies in particular that numbers are sent "least significant digit first". We shall discuss below some of the more frequently encountered circuits for serial operation.

### Delay Lines (Recirculating Registers)

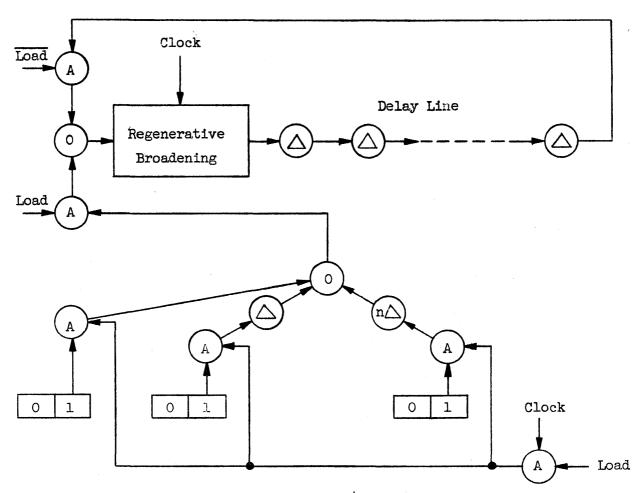

It is possible to use a transmission line of sufficient length to store sequences of pulses. Such a line can be thought of as a chain of delay elements: in order to store n pulses we need n times a delay equal to the period of the clock. The chain usually contains at its end a circuit for regenerative broadening. This has for effect not only to give to pulses a standard shape and length, but also to resynchronize them with the clock, i.e. to make sure that all pulses are still equally spaced after an indefinitely great number of passages through the line. It should be remarked that delay lines are often of the accustic type in order to circumvent size problems one would encounter with electric lines storing 1000 or more bits. The accustic delay line is simply a sound propagating rod connected between a loudspeaker and a microphone (called "transducers") at megacycle frequencies; bursts of sine waves are used rather than the modulating pulses themselves: This simplifies the design of the transducers.

The two main problems with recirculating registers are 1) to "load" the line by establishing in it a train of pulses conveying the information initially present in a set of flipflops 2) to "unload" the line by dumping into a set of flipflops the dynamic information "running off the end" of the line.

Figure 2-41 shows a possible loading mechanism. When both the load signal and a clock pulse occur, the information in the flipflops is made available to the line via the input OR in front of (or as one can see from Figure 2-38 actually part of) the regenerative broadening circuit which feeds the line (represented by a series of delay elements). Delays equal to one, two etc. times the clock period are inserted between the one-side output of the flipflops and a common collecting OR circuit. The latter goes into the input OR mentioned above via an AND which disconnects the flipflops in case no loading signal is present: in the absence of the load signal the upper AND closes the loop and makes sure that no information is lost. Note that more than one word can be stored and that a counter is required to time the load signal correctly so that a new word does not start in the middle of one already being recirculated.

-58-

Figure 2-41 Loading of a Line from a Flipflop Register

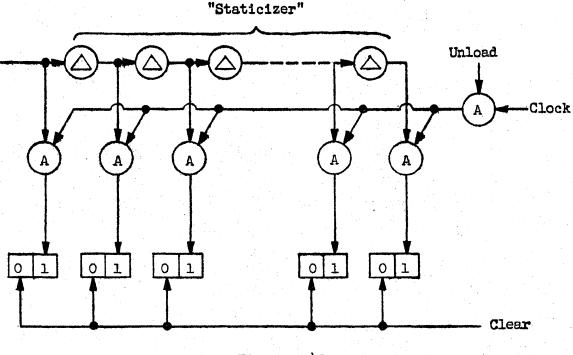

The unloading of a recirculating register can be most easily accomplished by tapping the line at one-clock-period intervals and sending the signals present at these taps simultaneously (via AND gates) into a set of previously cleared flipflops; Figure 2-42 shows the principle. In case of acoustical lines (or if one does not want to tap the main storage line) the dynamic information is actually switched to a separate (lumped-constant LC) delay line with taps, called a "staticizer".

A 12 .....

Figure 2-42 Unloading a Staticizer into a Flipflop Register

## Dynamic Flipflop

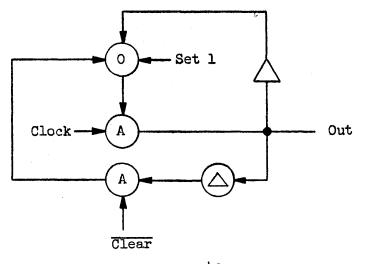

It is easily seen that a delay line giving a delay equal to one clock period coupled to a regenerative broadening circuit is simply a dynamic flipflop: once a pulse is trapped in this loop it will reappear periodically. It is usual to add an AND in the loop fed by the inverse of a clear signal in order to be able to set such a flipflop back to the 0 state in which no pulse ever appears. Figure 2-43 shows the arrangement.

Figure 2-43 Dynamic Flipflop

### Serial Adder

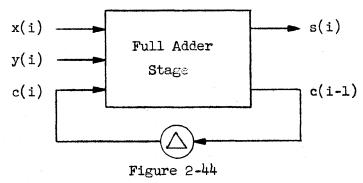

One of the main advantages of serial operation is that only one adder stage is necessary in order to produce a pulse train giving the sum of two pulse trains. Note that instead of speaking of the sum  $s_i$  in stage i we now talk about the i<sup>th</sup> pulse s(i) counted from the beginning of the train, or more exactly the i<sup>th</sup> clock-period, since no pulse occurs when the corresponding digit is zero. The same remark holds, of course, for the inputs x(i), y(i) and the carries. Adding in the carry from the preceding stage now is simply replaced by delaying the carry of the previous clock period. Figure 2-44 shows the extreme simplicity of a serial adder.

Serial Adder. All pulse trains are injected with the least significant digit first.

-61-

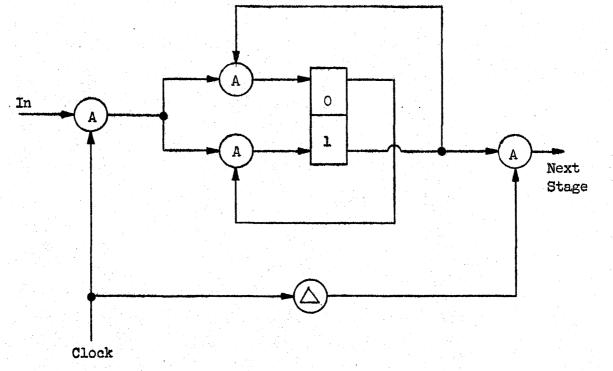

### Counter

Figure 2-45 shows how counting can be performed by using two AND's in front of a flipflop and controlling the second input from the opposite side of the flipflop output. Visibly such an arrangement will steer each incoming pulse to that side of the flipflop input which will produce a change - this means that for each incoming pulse the flipflop changes state. If we sample one of its sides (after the transient dies down, a delayed clock signal is used to control the output AND) we shall evidently obtain a pulse only for each second incoming pulse i.e. we actually have one stage of a binary counter.

Figure 2-45 One Stage of a Synchronous Counter

-62-

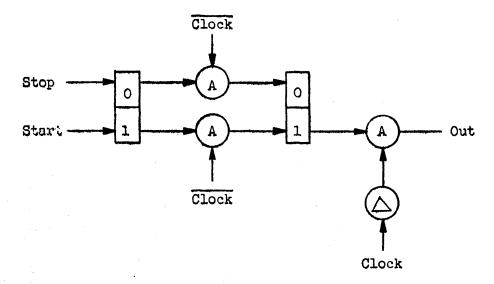

# Starting and Stopping a Sequence

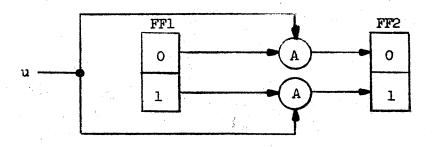

One of the problems that occurs in serial machines is to switch the output of a clock onto a line in such a fashion that no "half-pulses" occur, i.e. making sure that the switching occurs between two clock pulses. Figure 2-46 shows how this can be done. The idea is to set a first flipflop FF1 by the start/stop signals and to transfer this information on the next interval between clock-pulses to FF2; the latter cannot be changed while the clock pulse comes along since the input AND's cannot transmit information while the clock pulse is on. Note that the setting time of the flipflop may have to be taken care of by introducing a delay between the clock and the output AND.

Figure 2-46 Stopping and Starting a Pulse Sequence

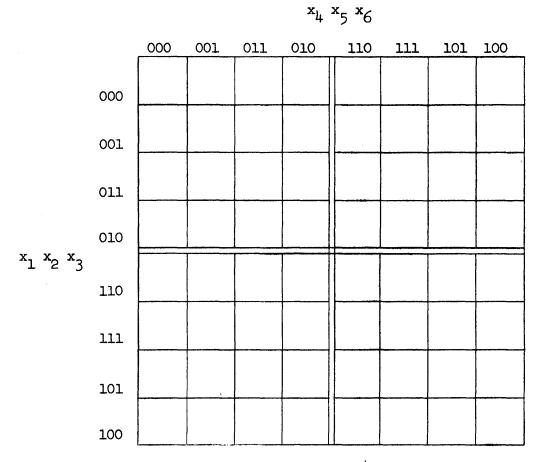

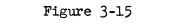

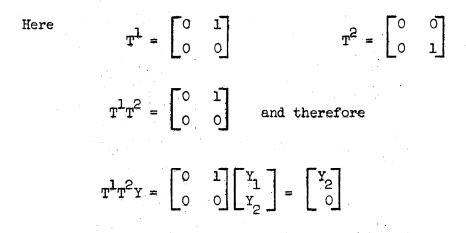

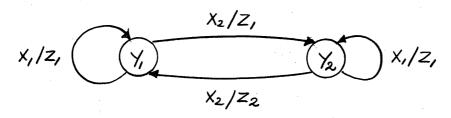

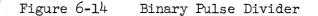

-63-