Contral No. A.W 127

# DESCRIPTION OF THE ASC SYSTEM HARDWARE

October 1970

TEXAS INSTRUMENTS' PROPRIETARY RIGHTS NOTICE

This document is the property of Texas Instituments Incorporated, is supplied to you fee informational purposes only, and shall be returned to Texas Instruments upon reducest, of when you have no further use for the document.

The information and/or drawings set forth in this document and all rights in and to inventions disclosed herein, and matents which might be granted thereon disclosing, employing, or covering the materials, methods, techniques, or apparatus described herein are the exclusive property of Texas Instruments Incorporated.

No reproduction shall be made of this document and no disclosure can be made to any other person, or if disclosed to an organization, to anyone outside of the organization, without the prior consent in writing of Texas instruments Incorporated.

Copyright © 1970, by Texas Instruments Incorporated

TEXAS INSTRUMENTS

#### PREFACE

This document describes the ASC System hardware as required by the system programming staff. It is also directed to all personnel associated with designing and configuring ASC Systems to be used as a primary reference source.

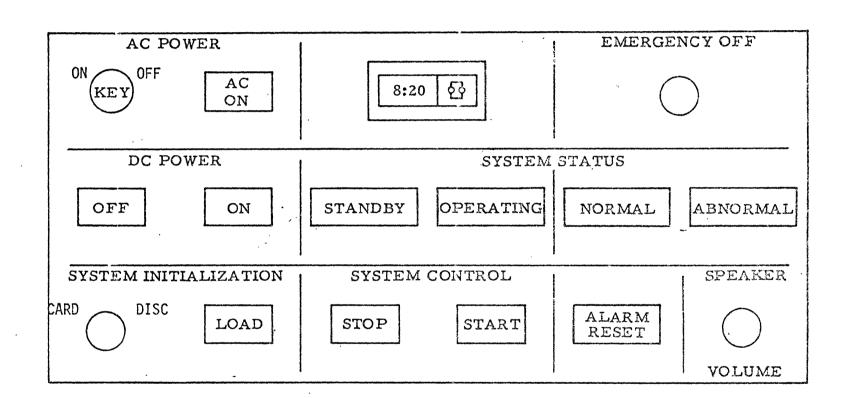

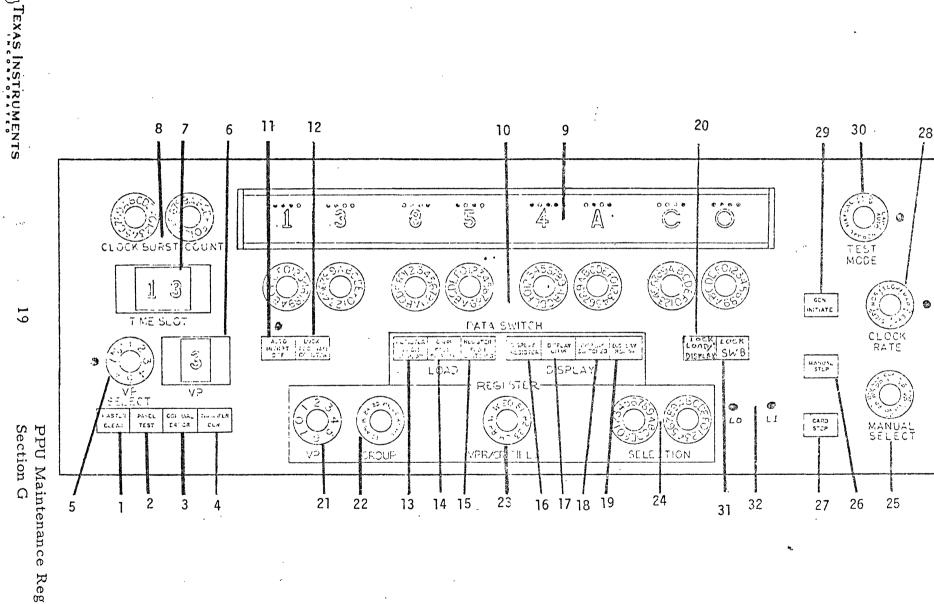

Section A describes the Memory System of the ASC including the Memory Control Unit, the Memory Modules, and the expansion features being incorporated into the system. Section B describes the Central Processor including the Memory Buffer Unit, the Instruction Processing Unit, and the Arithmetic Unit. This section also provides the CP instruction set, the timing analysis, and examples of vector instruction applications. Section C describes the Peripheral Processor including the Peripheral Processing Unit, the communication registers, the timing analysis, and the PP instruction set. Section D describes the Data Channel Units. Section E describes the ASC System operating panels, and the associated procedures. Section F describes the peripheral devices used with the system. Section G describes the maintenance provisions being designed into the system.

This document is designed to allow each part to be used alone. The overall list of effective pages following the Preface provides the effective date of the A page of each section. Changes, modifications, or additions will be issued as changed or added pages with the date of the change in the upper right hand corner of the changed page.

ii

#### CONTENTS

## INTRODUCTION

- SECTION A MEMORY SYSTEM

- SECTION BCENTRAL PROCESSORSECTION B1CENTRAL PROCESSOR DESCRIPTIONSECTION B2CENTRAL PROCESSOR TIMING ANALYSISSECTION B3CENTRAL PROCESSOR INSTRUCTION SET

- SECTION B4 EXAMPLES OF VECTOR INSTRUCTION APPLICATIONS

- SECTION C PERIPHERAL PROCESSOR

SECTION C1. PERIPHERAL PROCESSOR DESCRIPTION SECTION C2 COMMUNICATION REGISTERS DESCRIPTIONS SECTION C3 PERIPHERAL PROCESSOR TIMING ANALYSIS SECTION C4 PERIPHERAL PROCESSOR INSTRUCTION SET

- SECTION D DATA CHANNELS

- SECTION E OPERATING PANEL

- SECTION F PERIPHERAL DEVICES

- SECTION G MAINTENANCE

INTRODUCTION

# TABLE OF CONTENTS

.

| Title                                      | Page |

|--------------------------------------------|------|

| General Organization of ASC                | 1    |

| Use of Pipeline Concept                    | 3    |

| System Configuration and Hardware Features | 12   |

# GENERAL ORGANIZATION OF ASC

The ASC is an advanced computer designed especially for highvolume processing of well-ordered data in a multiprogramming environment. To achieve its extremely high processing speed, the computer utilizes a pipeline arithmetic section and a pipeline instruction section.

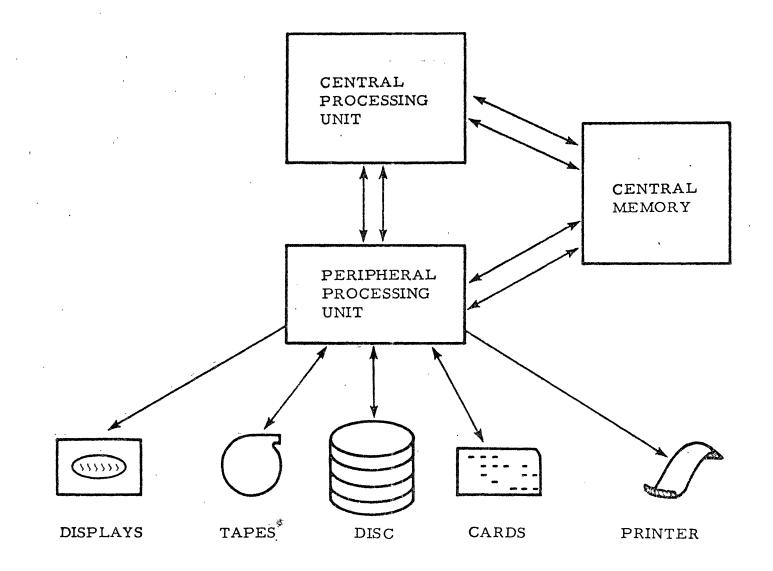

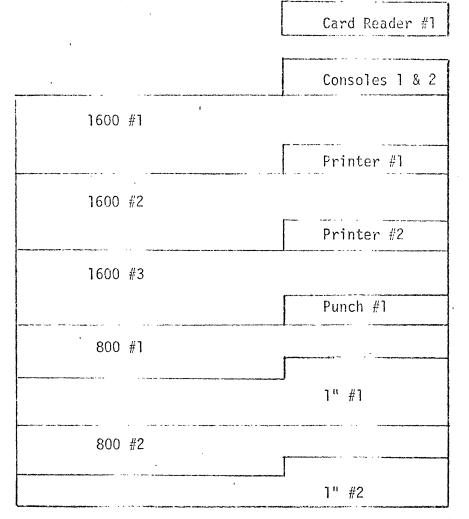

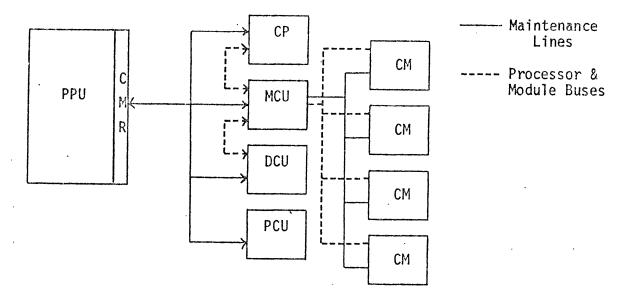

Organization of the ASC is illustrated in Figure 1. A Peripheral Processor links input/output equipment to a Central Processor and a Central Memory. The input/output equipment available for the system includes CRT keyboard/display units, magnetic tapes, magnetic discs, card equipment, and line printers.

The Peripheral Processor contains eight independent computers which control input/output devices and schedule work for the Central Processor.

The Central Processor provides the major execution facility of the system. The interface between Central Processor (CP) and Peripheral Processor (PP) consists of control communication links whereby the CP signals completion of jobs or its availability for other jobs and the PP initiates new jobs. All data and instruction for the CP are obtained through the Central Memory.

The Central Memory consists of high-speed semiconductor memory modules which have full cycle times of 160 nsec for 256-bit words. Since the ASC computer is a 32-bit/word computer, each memory cycle has access to eight computer words. The Central Memory interfaces with the CP and the Peripheral Processor.

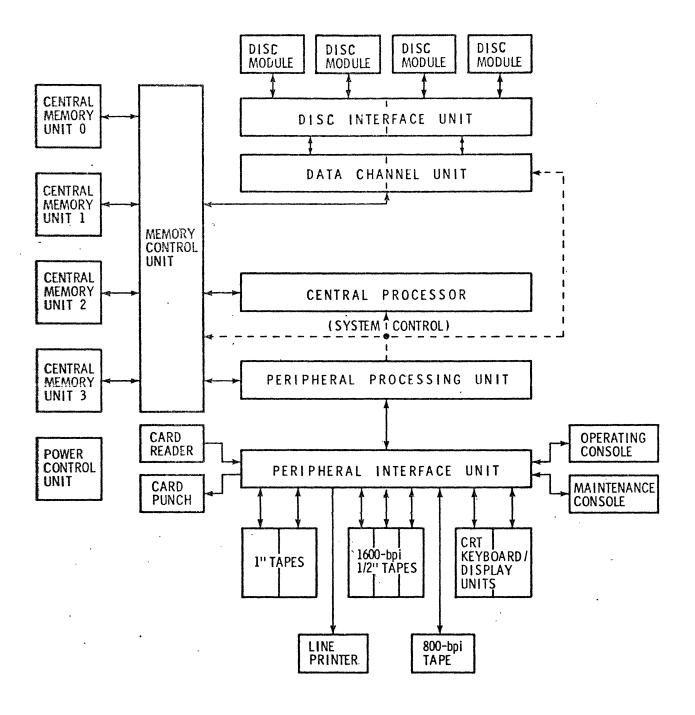

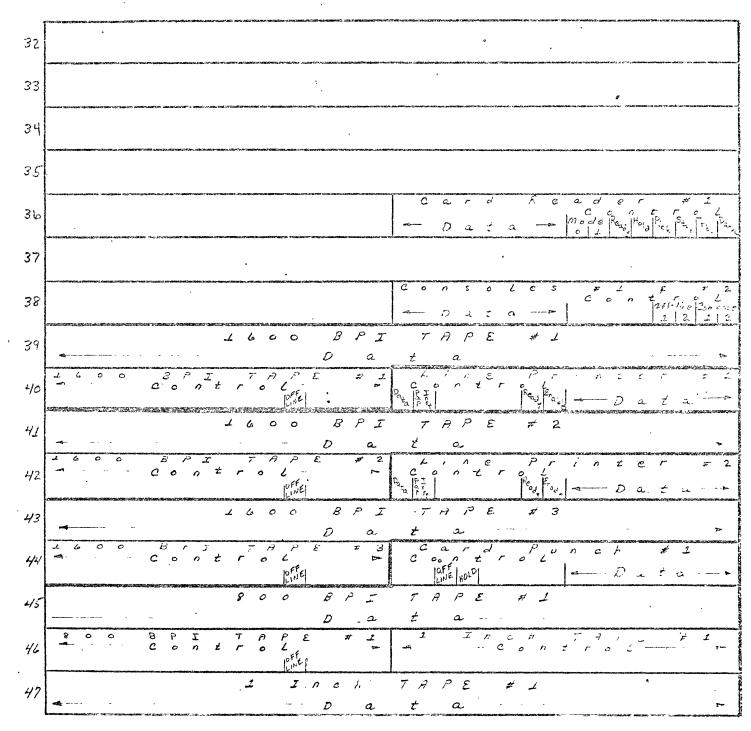

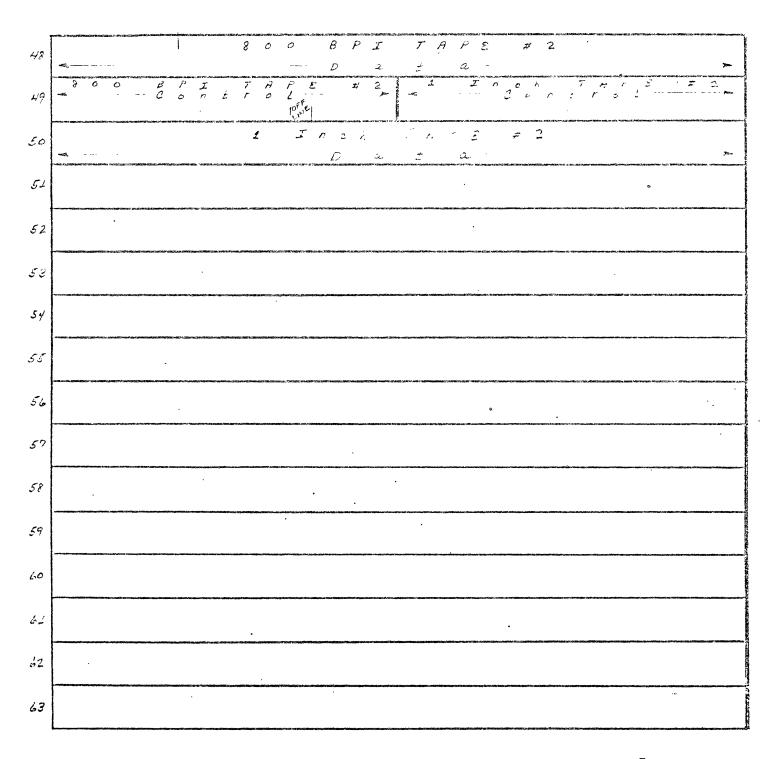

One ASC configuration is shown in Figure 2. This diagram indicates four memory units, each containing 16K words of storage; thus, the

Figure 1. ASC Organization

Figure 2. ASC System (Prototype)

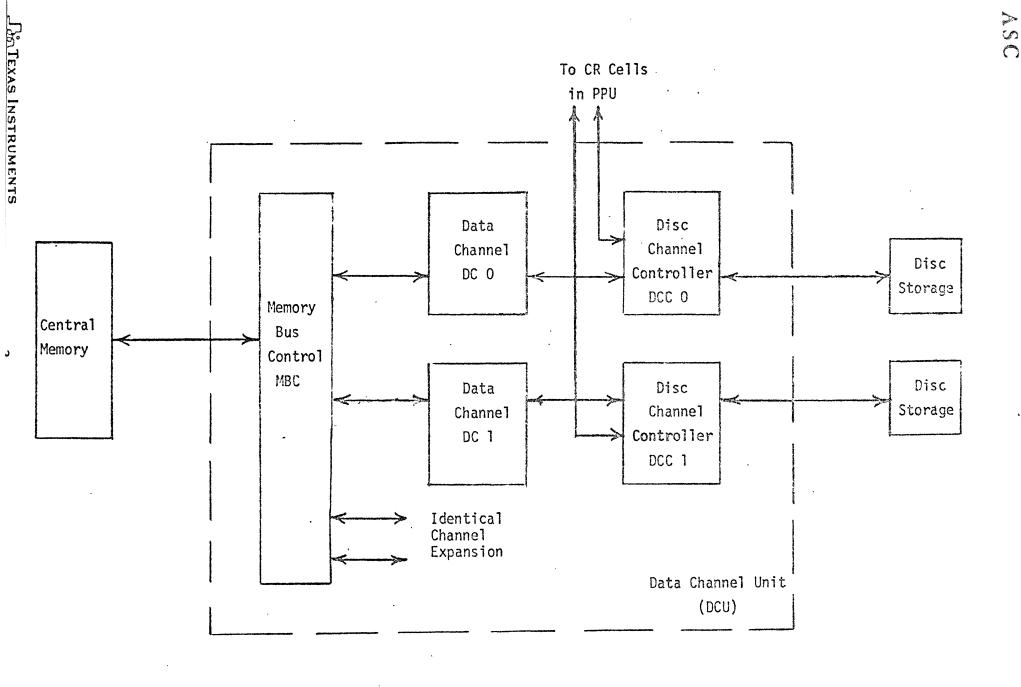

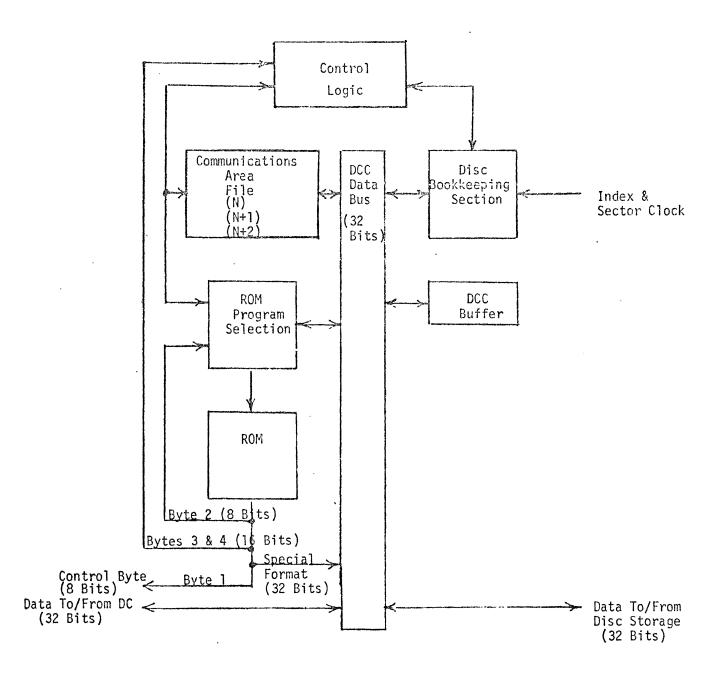

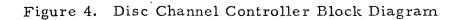

basic memory size is 65K words. These four modules are controlled by a memory control unit which multiplexes the memory units to the Central Processor, Peripheral Processor, or data channel unit which is a special high-speed device capable of sustaining the high data transfer rates required by the disc system. A significant feature of the ASC system is its utilization of a large disc file with word transfer rates of  $10^6$ /sec between it and the Central Memory. The disc file consists of four modules containing 25,000,000 words each.

### USE OF PIPELINE CONCEPT

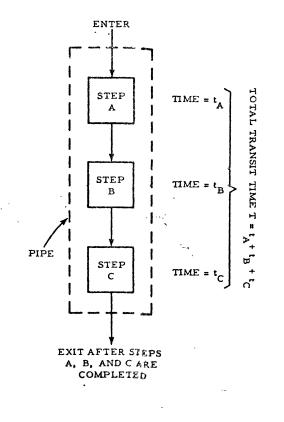

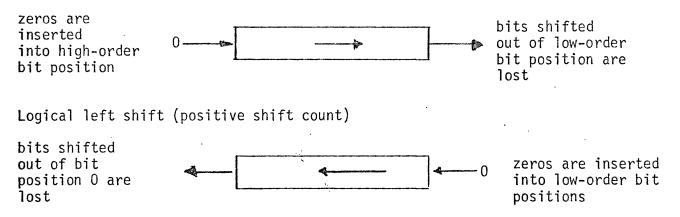

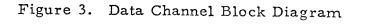

The pipeline concept being exploited in the Central Processor is illustrated by the example in Figure 3. This example shows a "pipe" which performs an operation consisting of three separate and distinct steps. This

Figure 3. Pipeline Concept

operation can be performed on an operand by entering it in the pipe and collecting the result at the exit after transit time T has elapsed. Thus, the time required to perform an operation is the sum of the individual step times  $t_A$ ,  $t_B$ , and  $t_C$ . If the steps are separate and distinct as stated, then the average operation time can be decreased by entering operands into the pipe so that different operands are at steps A, B, and C simultaneously. If a long series of operands are routed through the pipe so that the "fill-up" and "empty" times are negligible, the average time required for an operation will be

$$\frac{t_{A} + t_{B} + t_{C}}{3}$$

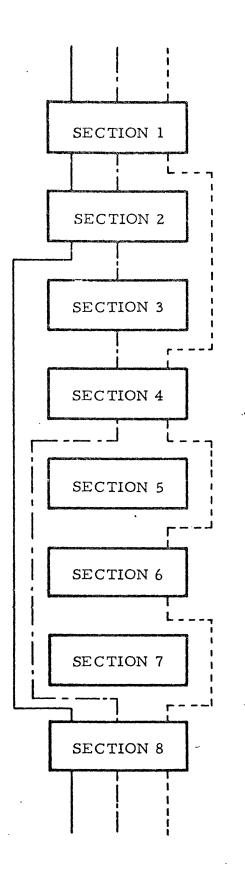

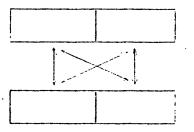

The ASC arithmetic unit is constructed from a number of "sections" (Figure 4), each of which can perform a separate arithmetic or logical operation in the same manner as the steps in the pipe of the previous example. These sections are connected in "pipe" fashion to generate a pipe for performing each instruction in the CP. Each section can be connected to any of the other sections, as required, to construct a pipe for executing any particular instruction. Figure 4 shows sections 1, 2, and 8 connected in a pipe by the solid line which may be the configuration required to perform an instruction. The dotted line connecting sections 1, 4, 6, and 8 illustrates a configuration which may be required to execute another instruction. In this fashion, the sections of the arithmetic unit are configuration of the arithmetic unit is established when the instruction and its operand are at the entry to the pipeline.

This pipeline concept is used in the design of the ASC because of its inherent ability to achieve high-speed operations on large volumes of well-ordered data. If the data are arranged so that a large number of identical operations are required in sequence, the pipeline can be filled, achieving an average operation speed equal to the time required for only one section of the pipe. This well-ordered type of data is represented by vector or array processing. For example, consider the vectors

$$A = a_1 + a_2 + a_3 + \dots + a_i$$

$$B = b_1 + b_2 + b_3 + \dots + b_i$$

A vector addition of A + B would result in the vector C where

$c_1 = a_1 + b_1$  $c_2 = a_2 + b_2$  $c_3 = a_3 + b_3$

$c_i = a_i + b_i$

The ASC instruction set contains vector and matrix instructions to perform such operations so that only one instruction is required to accomplish this operation on any length of vector. A conventional computer would require a series of instructions to achieve this same operation. This is illustrated in the following example:

- Conditions

- array A is stored in consecutive locations beginning at  $\alpha$

- array B is stored in consecutive locations beginning at  $\beta$

- array C is to be stored in consecutive locations beginning at Y

- each array consists of L elements

- The subroutine required for a conventional machine is

Enter Load I with 0 Load R from  $\alpha + (I)$ Add to R contents  $\beta$  + (I) Store R into  $\gamma$  + (I) Increment I Branch if  $I \neq L$ Exit

The time required to accomplish the function of each section in the ASC pipeline is 60 nsec; thus, for processing vector or array instructions, the average time per element is only 60 nsec. The CP interface with the Central Memory is designed to sustain this rate of data processing so that the pipeline can be utilized to its fullest extent.

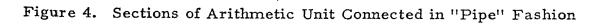

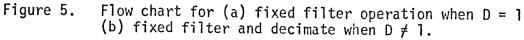

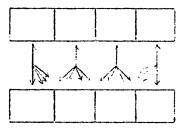

The CP interface with the Central Memory is shown schematically in Figure 5. There is one 256-bit data transfer bus between the CP and CM, which is shared by four CP storage buffers. Instructions are buffered in two storage files (IB and I), each containing eight computer words. One operand vector is buffered in two storage files (XB and X), each containing eight computer words, and the other operand vector is buffered in another set of storage files (YB and B). The resultant vector from the arithmetic unit is buffered in storage files ZB and Z in the same manner.

In addition to the pipeline construction of the arithmetic unit, the ASC employs a pipeline at the instruction processing level. Up to 12 instructions are in this pipeline at any time, so streams of instructions ready for execution are supplied at the exit of the instruction processing pipe in somewhat the same manner as streams of vector elements enter and exit from the arithmetic-unit pipe.

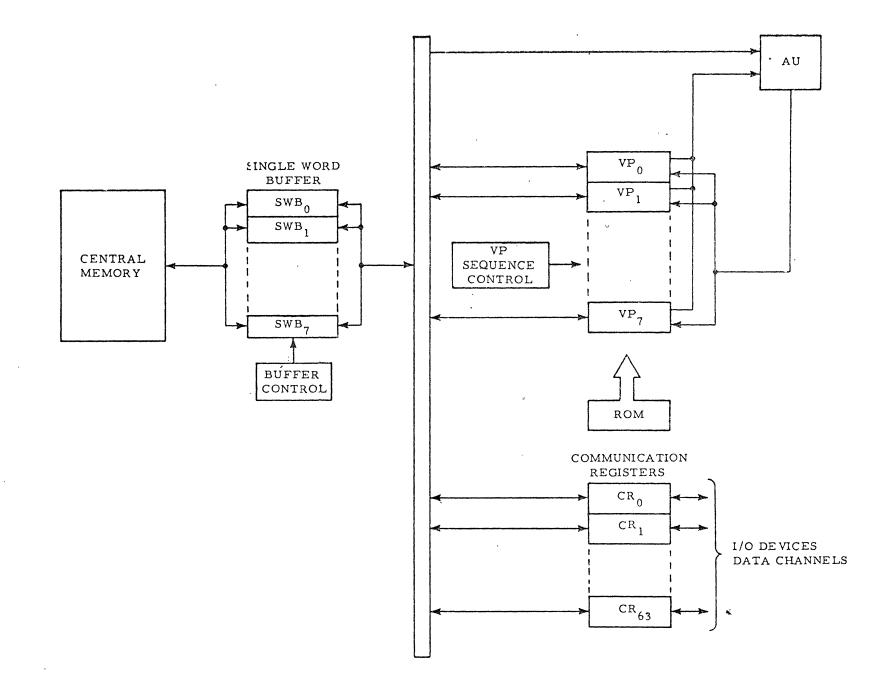

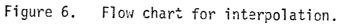

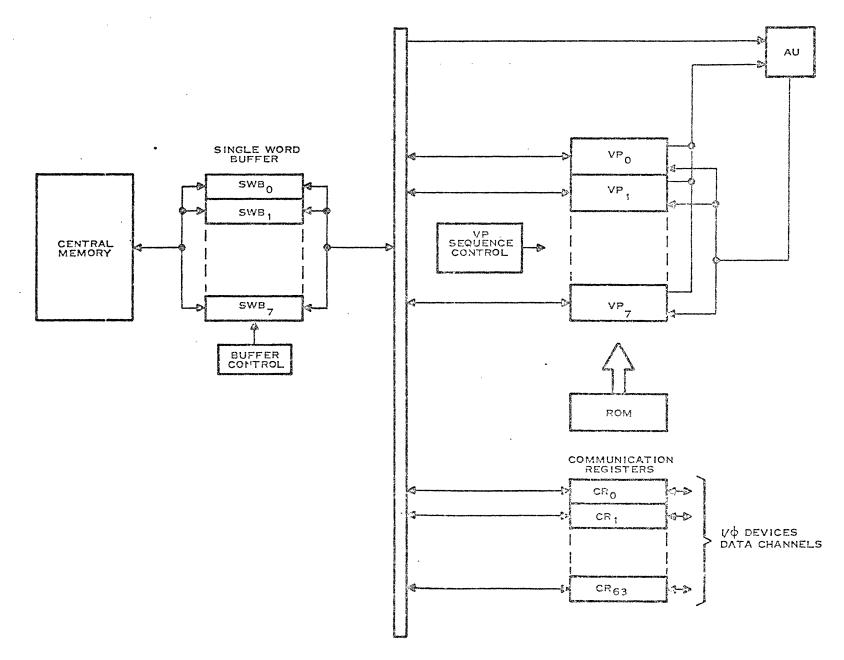

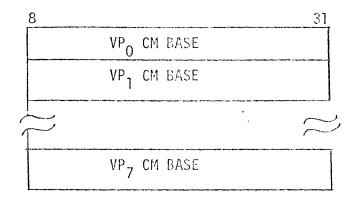

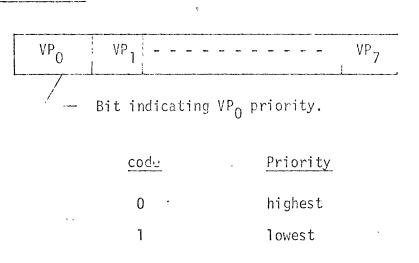

The Peripheral Processor provides communication with I/O devices, functions as system monitor, and fulfills job requests which do not require high arithmetic capability. Elements of the PP, shown in Figure 6, include one arithmetic unit which is shared by eight virtual processors, one of which is designated as the system monitor. Functions of the system monitor include assignment of system-control parameters, assignment of programs to each of the seven slave virtual processors, assignment of CP programs, and monitoring of the progress of all programs including the CP program.

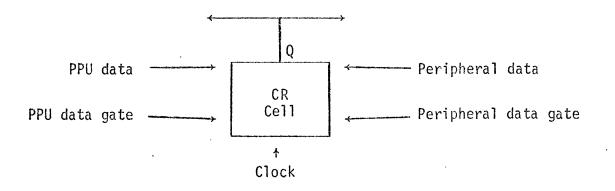

The virtual processors communicate with I/O devices, Central Processor, data channel, and other system components via 64 Communication Registers (CR) which are 32 bits in length and can be set or read by the virtual processor or an external device.

Associated with the virtual processor is a Read-Only Memory (ROM) containing fixed programs which are executed by the virtual processors. These programs are stored in the ROM because they are frequently used and require fast access.

Each virtual processor has a single-word buffer which acts as memory address register and memory data register for that processor. Central Memory access requests from these single-word buffers are granted on a priority basis.

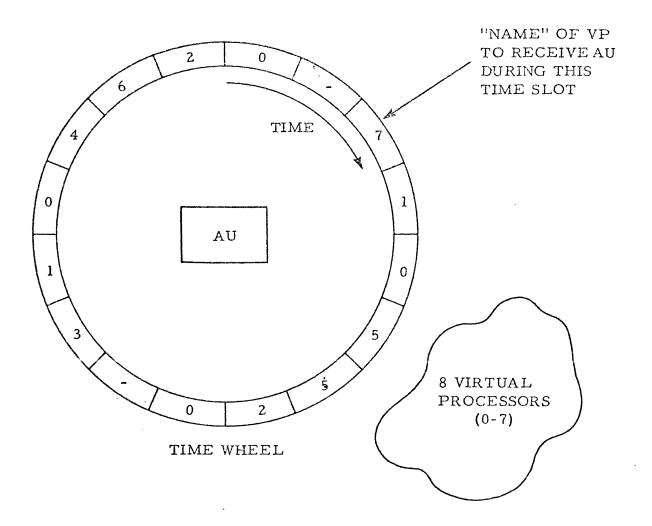

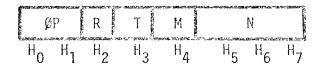

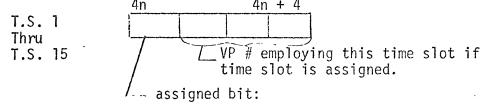

The virtual processors are operative and share the arithmetic unit as programmed by the system monitor. This sharing is accomplished by dividing the time into 16 time slots represented by the segments shown on the wheel in Figure 7. Time slots are assigned to the virtual processors according to their needs.

# SYSTEM CONFIGURATION AND HARDWARE FEATURES

The recommended physical configuration of the ASC requires Approximately 4000 sq. ft. Four airconditioning units, furnished as part of the ASC, supply cooling air to system components requiring special cooling.

Figure 6. ASC Peripheral Processor

# 1 ARITHMETIC UNIT

8 "VIRTUAL" PROCESSORS WHICH SHARE AU

Figure 7. Time Slots Permitting Virtual Processors To Share Arithmetic Unit

.

Normal airconditioning is also required to maintain a comfortable working area.

The extremely high speed of ASC operation is possible because of the advanced logic components which implement the system. These logic circuits are emitter-coupled integrated circuits having gate speeds of approximately 2 nsec.

ASC hardware features: a high-speed semiconductor memory; a direct-access fixed-head disc auxiliary storage system; Peripheral Processor which provides system control and external-internal communications; a rapid Central Processor for data manipulation, with the feature of hardware logic for vector-matrix operations; automatic, rapid, context switching for efficient multiprogramming; high-speed peripheral input/output devices; and remote online graphic terminals.

MEMORY SYSTEM

# MEMORY SYSTEM SECTION A CONTENTS

| INTRODUCTION              | 1 |

|---------------------------|---|

| MEMORY CONTROL UNIT       | 1 |

| EXPANDER/MULTIPLEXER UNIT | 6 |

| MEMORY UNITS              | 6 |

| 1                         |   |

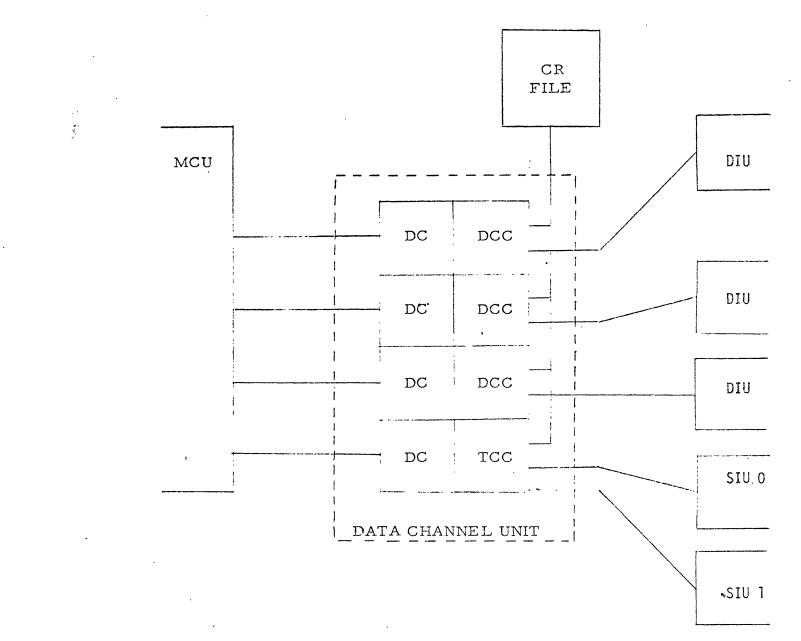

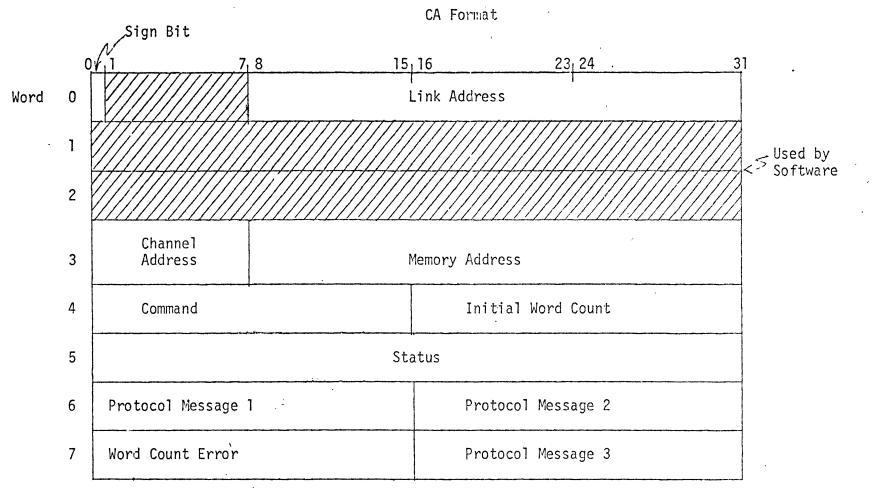

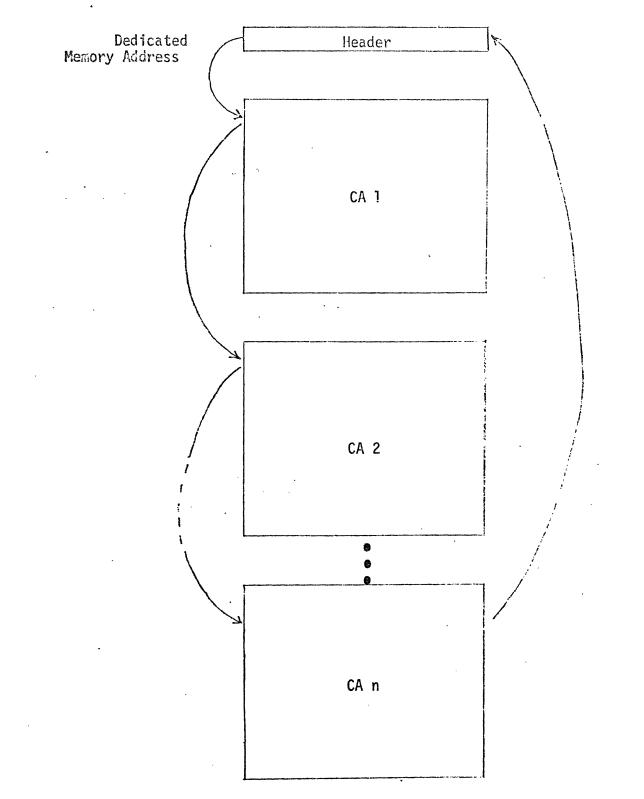

The Central Memory (CM) of the ASC system is configured from three basic units: the Memory Control Unit (MCU), the memory port Expander/Multiplexer (EX) and the selected Memory Units. Figure 1 illustrates a typical CM configuration.

# THE MEMORY CONTROL UNIT

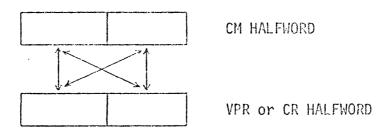

The MCU is organized as a two-way 256-bit/channel parallel access traffic net between eight independent processor ports and nine memory buses, with each processor having full accessibility to all memories.

The nine memory buses are organized to provide eight-way interleaving for the first eight buses with the ninth buses reserved for bulk storage. However, a patchboard is provided within the MCU to facilitate addressing patterns from no interleaving to eight-way interleaving.

The MCU provides the facilities for controlling access from the eight processor ports to a CM having a 24-bit address space (16 million words). In addition, each port contains the necessary hardware for performing the MAP and PROTECT address processing functions (described subsequently). Conflicts at the memory buses are resolved on either a fixed priority bases (i.e., each processor port is assigned a relative priority) or a distributed priority basis (i.e., all processor ports are assigned equal priority).

The unit is asynchronously designed to operate independently of cable delays, processor clock rates, and memory unit access and cycle times; however, these times can affect the memory bandwidth. For comparative purposes, the total bandwidth of CM is computed as  $BW_{CM} = No.$  of words/cycle X No. of Independent memories/Memory Cycle Time, and the bandwidth provided each processor port is  $BW_n = No.$  of Words/Cycle /2 X Processor Clock Period.

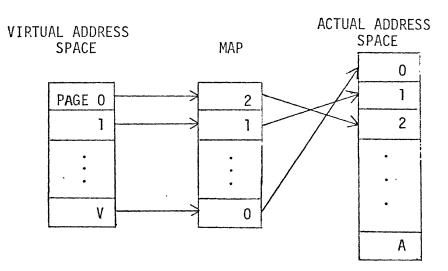

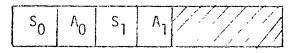

The Memory MAP provides for dynamic address relocation of Central Memory of the block (i.e., page) level. Contiguous virtual page addresses from the processors are transformed into discontiguous actual page addresses for more efficient use of CM resources. The MAP is physically a set of up to 64 eight-bit (page address) registers accessed via the virtual page address of an individual request. The contents of the register addressed replaces the most significant bits of the virtual address to form the actual page address. Figure 2 illustrates the Mapping procedure. The size of each "page" is a function of the size of CM being mapped. The minimum page size is 4K words with the maximum being 256K for full 24 bit addressing.

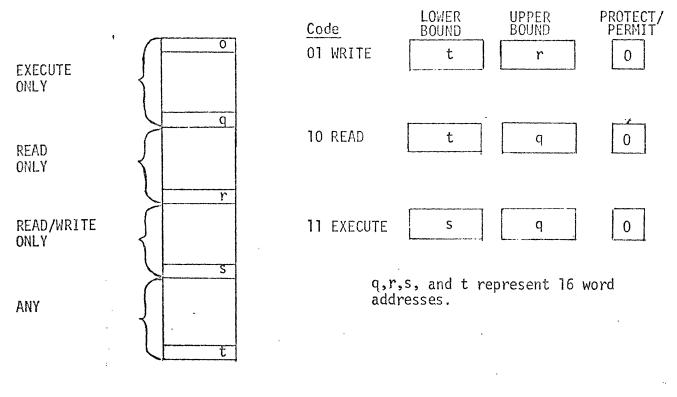

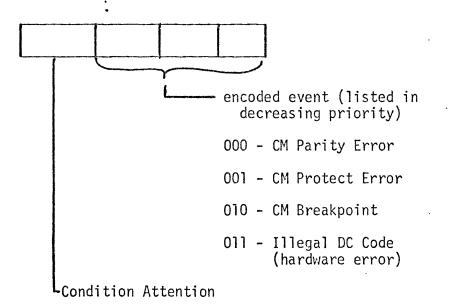

The PROTECT facilities consist of three 24-bit bounds register-pairs for defining the upper and lower bound of a protected CM segment. The MCU compares the address of each processor request to the contents of one of the bounds registerpairs selected via a two-bit code developed by the processor. For example, the three central processor categories are READ, WRITE, and EXECUTE. A request pointed toward a protected CM area is denied access to that location and the processor is notified of the attempted violation.

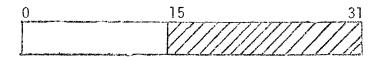

The bounds register-pairs can be used to define a variety of CM protection functions. Figure 3 illustrates a typical CM arrangement for the central processor port. Note that segments as small as 16 word groups may be defined.

The MAP provides an additional protection feature. If a processor utilizing the MAP feature accesses a MAP register containing actual page O, the request is denied access to CM and the processor is notified. Thus, the "O" code signifies that the requested page is not resident in the physical central memory.

FIGURE 2: MEMORY MAPPING

FIGURE 3: IMPLEMENTATION OF MEMORY PROTECTION

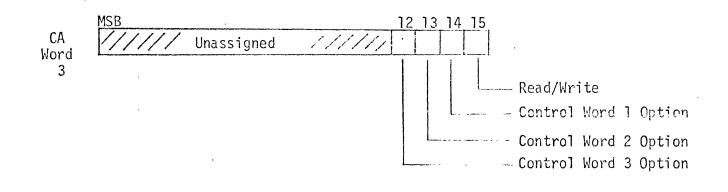

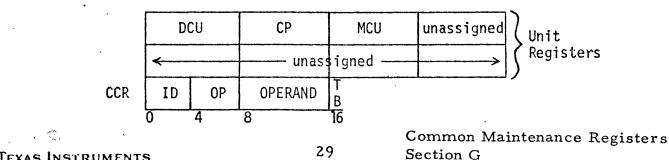

The MAP and PROTECT information for a particular processor is constructed in CM under control of the Operating System. The information is transferred to the MCU in response to a command from the PPU via the Common Command Register, or automatically via one of two "Context Switch" commands provided to the MCU from the automatic context switch logic in the central processor.

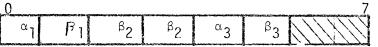

Command Command Register (CCR) operations cause the register addressed to be loaded with the contents of the location specified by the pointer in absolute CM location 38<sub>16</sub>, whereas the Context Switch command causes a set of predefined MAP and PROTECT registers to be loaded from the location specified by the pointer at CM location 28<sub>16</sub>. Figure 4 reflects the CM image of the MAP and PROTECT registers for use with the Context Switch command. A list of MCU CCR commands is presented in the maintenance section. CCR commands are also available to provide access to MCU control and address registers for maintenance and diagnostic purposes.

| Address | n               | n+1   | n+2     | n+3       | n+4                                 | n+5     | n+6       | n+7                   |

|---------|-----------------|-------|---------|-----------|-------------------------------------|---------|-----------|-----------------------|

| n       |                 | Lw Uw | Lr Ur   | Le Ue     |                                     | Lw Uw   | Lr Ur     | Le Ue                 |

| n+8     | $A_0 A_1 A_2$ . |       | • • • • | · · · A15 | A <sub>32</sub> A <sub>33</sub> · · | • • • • |           | · · · /47             |

| n+16    | A16A17A18 ·     | ••••• | • • • • | · · · A31 | A <sub>48</sub> A <sub>49</sub> · · | • • •   | • • • • • | · · · <sup>A</sup> 63 |

- Lw Lower Write Protect bound

- Uw Upper Write Protect bound Uw Upper Write Protect bound Lr Lower Read Protect bound Ur Upper Read Protect bound Le Lower Execute Protect bound Ue Upper Execute Protect bound An Value of Actual Page Number corresponding to Virtual Page n of MAP

.

FIGURE 4: CM IMAGE OF "CONTEXT SWITCH" MAP AND PROTECT REGISTERS

A.

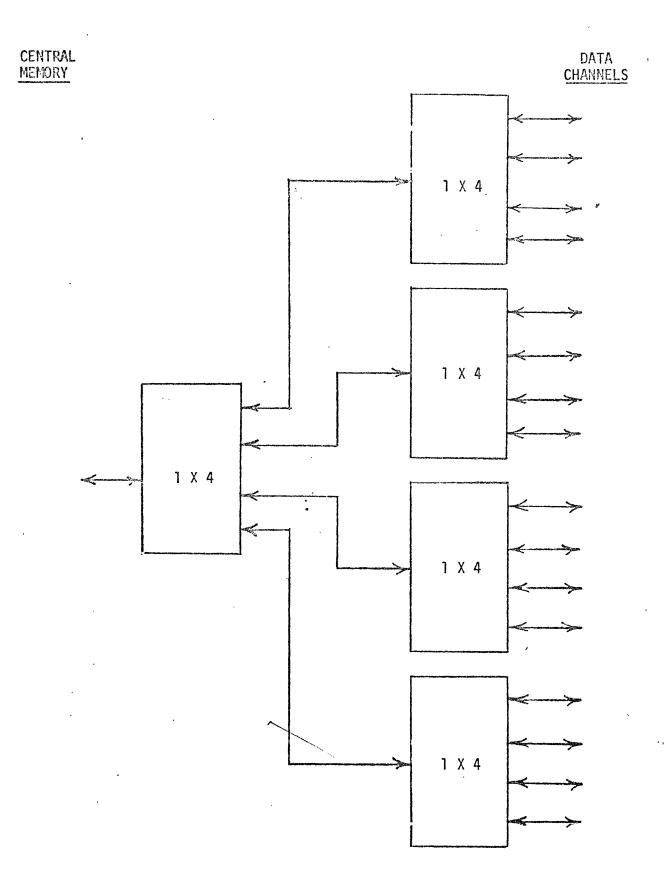

The EX adds the memory bus and the processor port expansion capabilities for configuring very large ASC Systems. The unit can be operated in any one of three distinct modes:

- Up to four "Processors" can be multiplexed onto one MCU processor port. In this sense, a "processor" can be a data channel or a processor bus. Of course, the basic bandwidth limitations must be observed.

- 2) One MCU memory bus can be expanded to accommodate up to four Memory Units.

- 3) A single processor's memory bus can be fanned out to allow the processor to access up to four different memory systems.

The EX's can be interfaced with each other (i.e., by "treeing") to provide expansions to 16 or up to 64.

Conflicts at the single port interface are also resolved on either a fixed or a distributed priority basis, in a similar manner to the MCU. These modes are selected by patch card wiring in the expander hardware.

#### THE MEMORY UNITS

The Memory Control Unit is designed to operate with Memory Units configured as eight-word (octet) storage devices. The TRANSLATOR PC board (patchboard) is "used to define the size of the unit on each memory port as well as the interleaving mode.

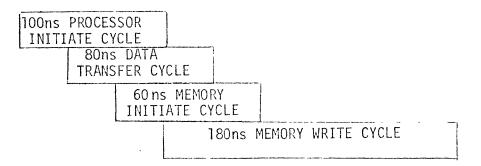

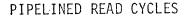

For the most effective use of ASC resources, the high speed storage devices should have access times in the range of 100-250 nanoseconds. However, the system will operate with slower memories and, due to the interleaving capability, the degradation of performance is not linear with respect to memory speed. Figure 5 illustrates the pipeline nature of memory requests with an assumed module access and cycle time of 140 nanoseconds.

The MCU also has the capability of reporting and testing the Parity logic normally provided with Memory Units.

The active element fast memory modules which are the standard ASC memory units have raw access and cycle times of 140 and 160 nanoseconds.

CM WRITE CYCLE

SECTION A

CENTRAL PROCESSOR DESCRIPTION

# TITLE

# GENERAL

PAGE

1

| 5        |

|----------|

| 5        |

| 7        |

| 7        |

| 9        |

| 10       |

| 11       |

| 11       |

| 12       |

| 12       |

| 12       |

|          |

| 13       |

|          |

| ٦ ٨      |

| 14       |

| 15<br>20 |

| 20       |

| 24       |

| 24       |

|          |

| 25       |

| 26       |

| 26       |

|          |

•

# GENERAL

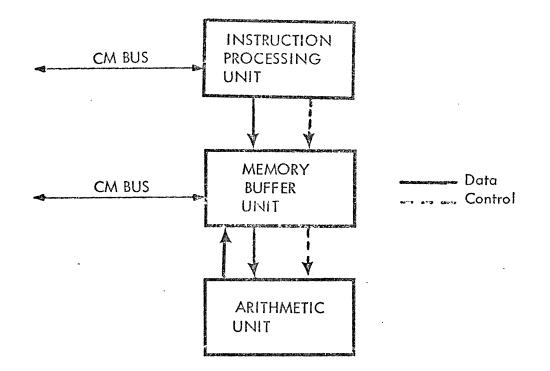

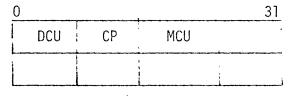

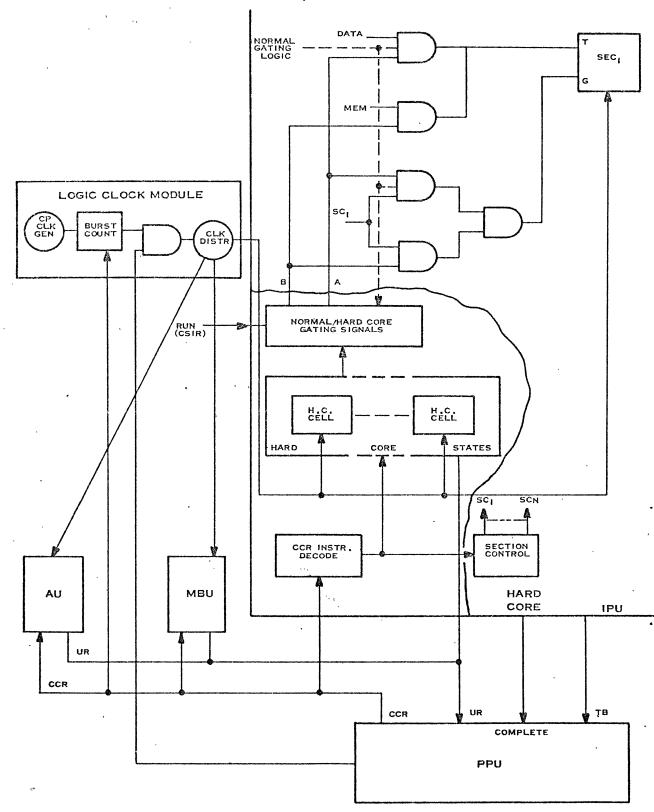

The Central Processor (CP) is comprised of the Instruction Processing Unit (IPU) to process the CP commands, the Memory Buffer Unit (MBU) to provide interfacing with the CM, and the Arithmetic Unit (AU) to perform the specified arithmetic operations. The interaction of these units is shown below:

#### INSTRUCTION PROCESSING UNIT

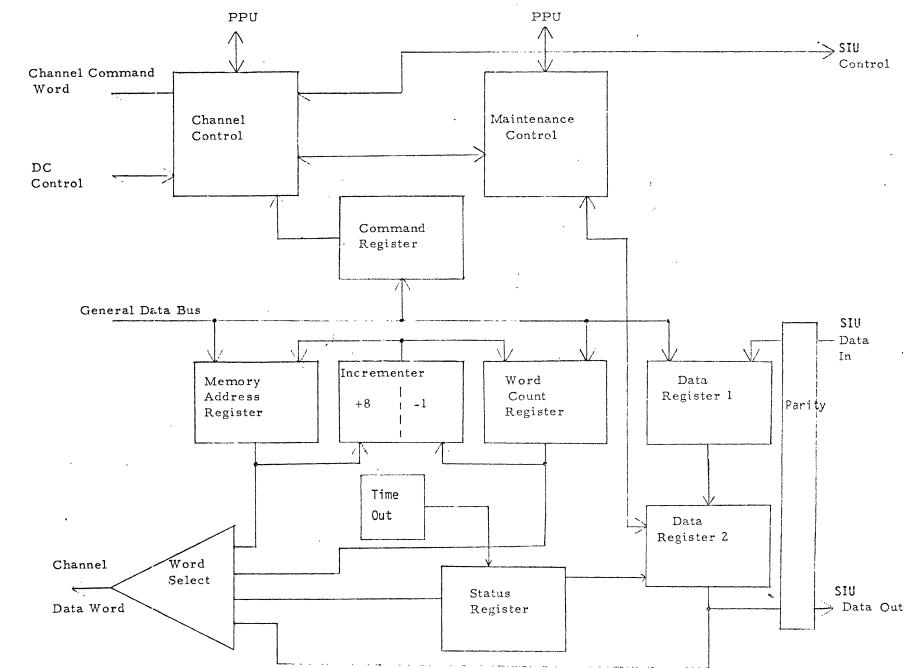

The primary function of the IPU is to supply a continuous stream of instructions to the MBU. The IPU block diagram is shown in Figure 1; it performs the following functions:

- 1. Instruction fetch

- 2. Instruction decode

- 3. Register operand selection

- 4. Effective address development through indexing and/or indirect addressing

- 5. Immediate operand development

- 6. Branch address development

General 1 Section B1

Figure 1. CP Block Diagram

.

- 7. Determination of branch condition

- 8. Storage of AU results into the register file

- 9. Scalar hazard and register conflict resolution

- 10. Generation of vector starting addresses

- 11. Transmittal of vector parameters to the MBU during vector initialization

### MEMORY BUFFER UNIT

The primary function of the MBU is to supply the AU with a continuous stream of operands for vector processing and provide for the storing of results of the vector operations. The MBU performs the following functions:

- 1. Accept the initial vector starting addresses and parameter information from the IPU.

- 2. Fetch the memory operands requested by scalar instructions.

- 3. Retention of 16 words in temporary X and Y buffer registers for possible "scratch pad" operations involving data contained in the two most recently referenced memory octets. This temporary storage capability increases by a factor of 1, 2 or 4 depending upon whether a times 1, times 2, or times 4 ASC configuration is installed.

- 4. Storage of register operands into central memory as a result of scalar store instructions.

- 5. Temporary retention of 8 words in the Z-buffer register for data destined for one central memory octet address. Data stored by this means is released to central memory when the octet address of write data at the Arithmetic Unit output is different than the octet address of the data contained in the Z-buffer registers. This temporary storage capability increases by a factor of 1, 2 or 4 depending upon whether a times 1, times 2, or times 4 ASC configuration is installed.

- 6. Update capability from the Z-buffer registers to the X or Y buffer registers for keeping the X and Y registers current when they are being used for "scratch pad" operations.

# ARITHMETIC UNIT

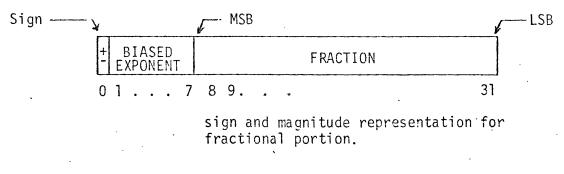

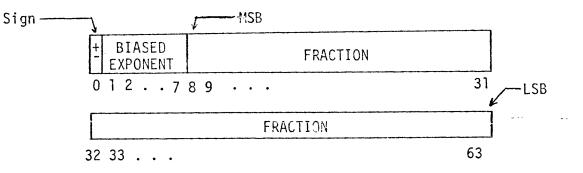

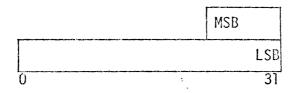

The primary function of the Arithmetic Unit is to perform the arithmetic operations specified by the operation code of the instruction currently at the AU level. The Arithmetic Unit is basically a sixty-four bit parallel operating unit which is split into two halves of thirty-two bits each. Double length operations are carried out using both thirty-two bit halves in parallel. Single length operations use the left half AU, while half length operations use only one half of the capability of the left half AU. The same AU is used for both fixed and floating point instructions. Fixed point numbers are represented as signed integers with negative numbers in 2's complement notation. Floating point numbers are in sign and magnitude with a base 16 exponent represented by an excess 64 binary number.

.

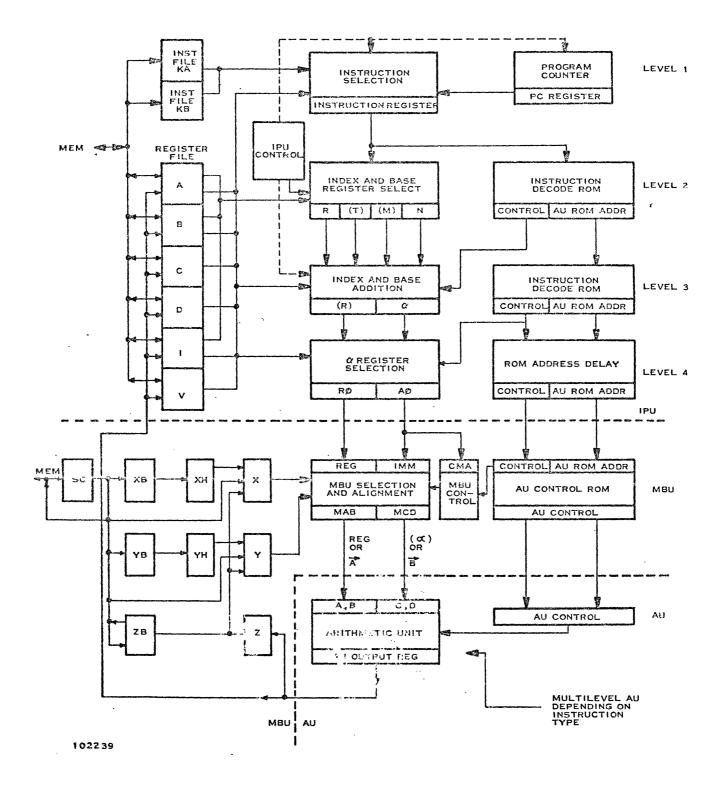

The Instruction Processing Unit functional areas with four pipeline levels are shown in Figure 2.

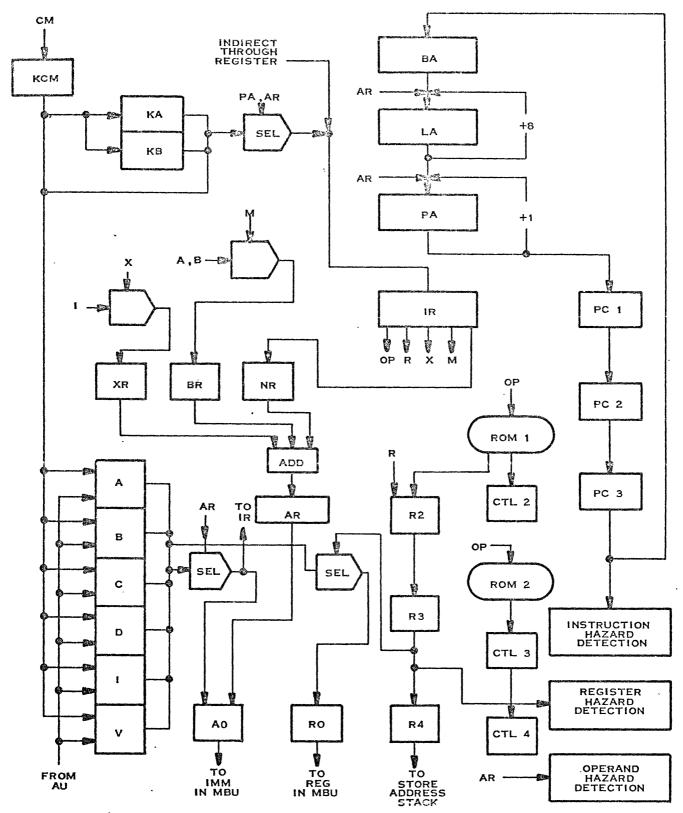

# INSTRUCTION FETCH

The instruction fetch function of the IPU is concerned with instruction lookahead into the next octet and instruction look-ahead along the branch path when the loop look-ahead control is active. The principal registers involved in the process of instruction fetching are the present address register (PA), the lookahead register (LA), and two eight-word instruction register files. The present address register contains the address of the instruction presently being selected from one of two eight-word instruction files. The look-ahead address register ordinarily contains the next instruction octet address ahead of the octet referenced by the present address register. Two eight-word instruction files ordinarily hold the present instruction octet and the next instruction octet.

An initial address is entered into the LA register for transmission to Central Memory via the address bus from the IPU. LA is then transferred to PA as the present address. When the address bus is released by CM, the look-ahead incrementing hardware advances the LA register by eight, equivalent to one octet look-ahead. The LA register sends this second address to CM immediately after the instructions has returned form CM.

The first octet of instructions recieved from CM is synchronized with the Central Processor clock at KCM. The octet is then transferred to file KA on the next clock. The second request for the look-ahead octet is synchronized at KCM when it arrives form CM, and then it is transferred to KB on the following clock.

One clock after the first octet is entered into file KA , the Instruction Register (IR) is loaded with the instruction word selected by the 3 least significant bits of PA. The PA register is incremented by one as each instruction is entered into the instruction register. When the 3 LSB's of PA are 111, the last word in file KA is entered into IR and the instruction look-ahead octet KB is selected. As this transfer occurs the contents of LA is transferred to PA and the LA register is advanced by eight to the address of the next look-ahead octet. This new look-ahead octet is requested from CM while instructions in the KB file are being executed. This process of overlapping instruction requests with instruction execution continues until a branch without look-ahead or an out-of-line indirect address request occurs.

In the case of a branch without look-ahead, the computed branch address replaces the contents of both the PA and LA registers. LA is requested from CM, then advanced by eight for the next look-ahead request and then the process described above is repeated.

102240

Figure 2. Instruction Processing Unit

ı

A branch with look-ahead is set up by placing the branch instruction at the target location of a Load Look-Ahead (LLA) instruction. This branch does not cause a delay in instruction fetching if both the branch instruction and LLA instruction are properly located with respect to octet boundaries. The LLA should be at the top of an octet and the target branch instruction should be at the bottom of an octet for optimum timing. A penalty of one clock time is paid for execution of the LLA instruction for each pass through the program loop if the LLA is located in this manner.

A Load Look-Ahead instruction enters a count into a look-ahead counter register (LC) in the IPU and enters the program address value of the LLA instruction presently being executed into a branch address register (BA). The count from the N-field of the LLA instruction corresponds to the difference of the instruction locations of the LLA and its target branch instruction. The counter is decremented for each instruction executed following the LLA. When the look-ahead counter is lowered to a value which would indicate that the target branch instruction has been requested by the instruction look-ahead and the look-ahead is now ready to be incremented by eight to the octet beyond the instruction octet which contains the branch instruction, then the look-ahead control will override the normal next octet increment of eight and place the contents of the branch address register (BA) into the look-ahead address register (LA ). This causes fetching of the octet which contains the LLA instruction and the loop control is re-initialized when the LLA instruction is executed again after the branch instruction returns the program to the LLA instruction. Loop control by use of an LLA instruction only applies to singular instruction loops up to 256 instructions including the LLA and the BRANCH.

A non-targeted branch instruction located between the LLA and the target branch instruction will inactivate the branch look-ahead control if the nontargeted branch instruction takes the branch path. If a non-targeted branch instruction does not branch, then an active branch look ahead remains active.

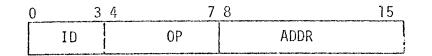

# INSTRUCTION DECODE

Instruction decode in the IPU is accomplished by the first of two Ready-only Memories (ROM). The ROM size is 256 words by 32-bits. The first ROM output is at level 2 of the pipeline and is used for <u>IPU</u> control. The second ROM is also used for control but in addition generates a field for use in driving the address inputs to a third ROM contained in the MBU. The third <u>ROM</u> is used to control the Arithmetic Unit. Outputs from both IPU ROM's contain preliminary instruction decoding information needed for the IPU and MBU. Such things as operand word size needed for register operand selection and effective address development are supplied by the ROM's.

# REGISTER OPERAND SELECTION

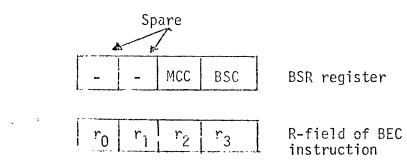

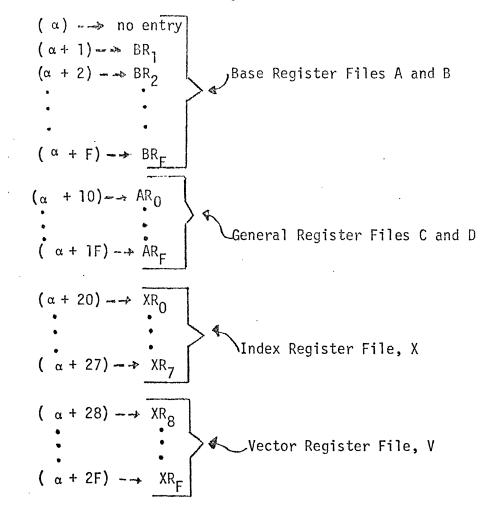

The register operand selection takes place in level 3. Register addresses within a group of registers are specified by the R-field of the instruction word. Register groups are specified by the instruction type as determined by

the operation code. The operation code is used as an address for the first ROM which in turn supplies the two additional bits needed for register group selection. These two bits augment the four R-field bits to form a six bit register address "for single length instructions. This six bit register address is applied to the input of a register selection network which can select any one of 48 single word registers in the register file.

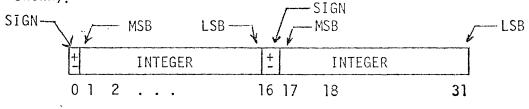

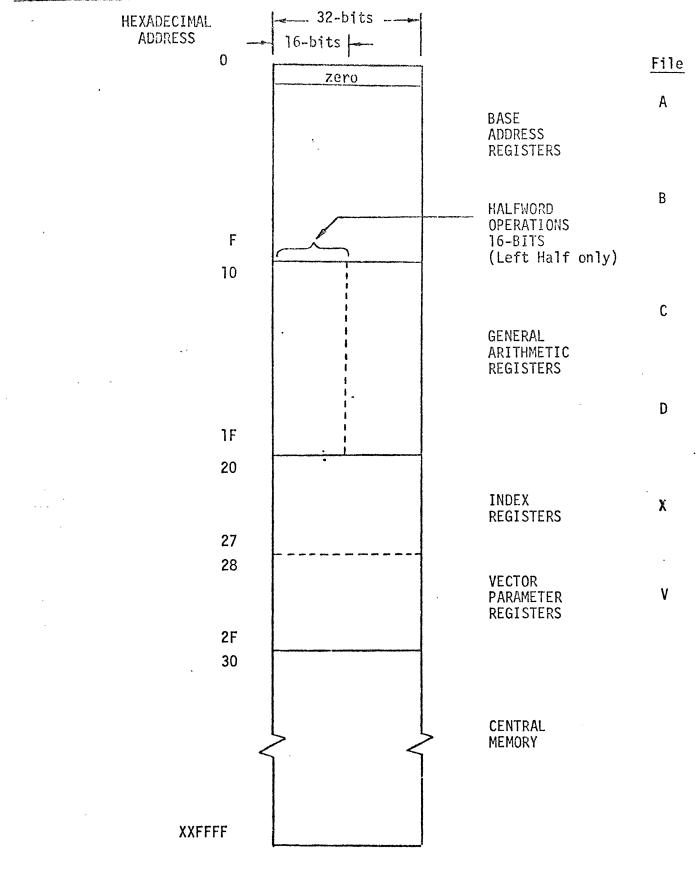

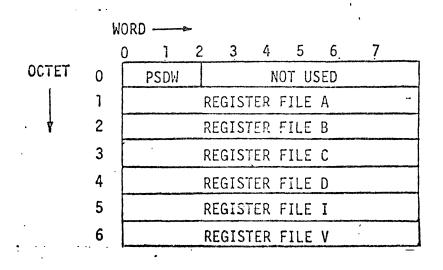

The program addressable registers in the Central Processor make up the register file. Each register is 32-bits in length. All registers in the file can be loaded or stored individually or in groups of eight registers at a time with a single instruction. There are six groups of eight registers:

| Register  | Group                                                              | Group       |

|-----------|--------------------------------------------------------------------|-------------|

| Locations | Function                                                           | Designated  |

| 00-07     | Base address registers                                             | A           |

| 08-0F     | Base address registers                                             | B           |

| 10-17     | General registers                                                  | C           |

| 18-1F     | General registers<br>Index registers<br>Vector parameter registers | D<br>I<br>V |

If the instruction word specifies a half length register operand, then the first ROM supplies an additional bit indicating which halfword is to be selected from the 6-bit singleleword address. If a doubleword register is specified, then one bit is dropped from the 6-bit register address and 64-bits are selected into the RØ register at level 4. Doubleword register operands are always selected from an even-odd singleword address pair.

Occasionally the effective address ( $\alpha$ ) is in the range  $\alpha < 2F$  and the M-field is equal to zero, in which case the  $\alpha$  addressed operand is selected from the register file. Operands of this nature are selected by the IPU after the effective address is developed. The register is selected using the 7 least significant bits of the AR register. These 7-bits include 6-bits of singleword address information plus one-bit for halfword selection if specified by the instruction type.

The output of the  $\alpha$  selection network enters up to 64-bits of data into the AØ register if doublewords are specified. AØ is transmitted directly to the MBU input register (IMM) for entry into the MBU output register (MCD) and then to the Arithmetic Unit. The AØ register is at level 4 of the IPU. The register operand for each instruction is carried along and held in the RØ register in parallel with and in the same time relationship as the operand in AØ.

### EFFECTIVE ADDRESS DEVELOPMENT

.

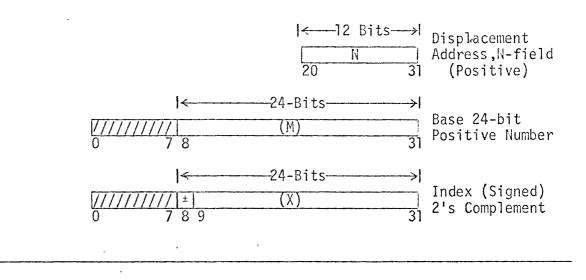

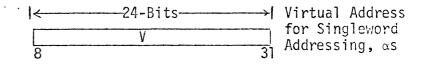

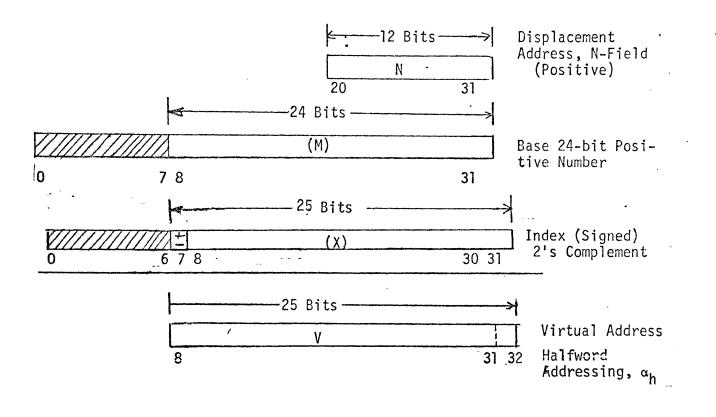

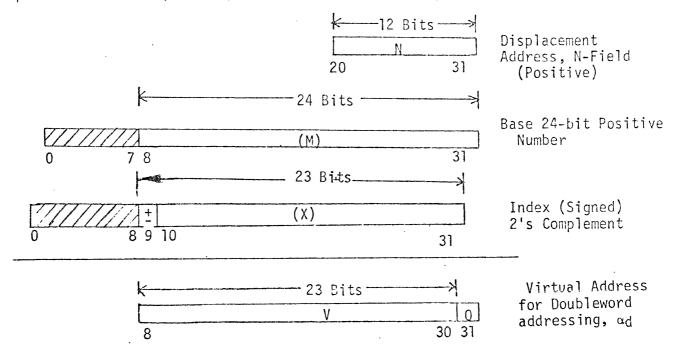

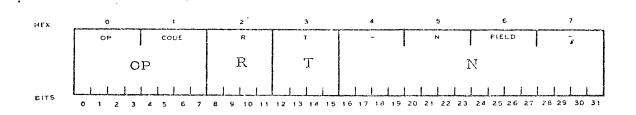

Effective address development through indexing and/or indirect addressing incorporates a major portion of the hardware in the IPU. The T, M, and N-fields of the instruction format specify the index register, base register, and address displacement, respectively. The MSB of the T-field is used to specify indirect addressing. An index register selected from an address by the 3 LSB's of the T-field is entered into the 25-bit XR register at level 2 in the IPU.

A base register selected from an address given by the M-field is entered into the 24-bit BR register at the same level. The N-field displacement is copied into the NR register. XR, BR, and NR form the three inputs to the index adder in level 3.

The XR register is shifted one bit position to the right, left, or not at all depending upon whether halfword, doubleword, or singleword addressing, respectively, is specified by the instruction code. The shifting takes place prior to addition in level 3.

The output of the index adder is entered into a 25-bit register, AR, which holds the effective address of the instruction presently at level 3. The LSB of AR is the halfword address selection bit. The LSB is forced to zero for singleword addresses and the two LSB's are forced to zero for doubleword addresses.

The 21 most significant bits of the 25-bit effective address register (AR) is sent to the Central Memory Address Requestor in the Memory Buffer Unit (MBU) if the addressed data is not presently residing in either the X or Y data registers of the MBU. If the addressed data is present in the X or Y registers, then the 4 LSB's of AR are sent to the MBU to perform the selection of the appropriate doubleword, singleword, or halfword from X or Y using 2, 3, or 4 of the four bits, respectively.

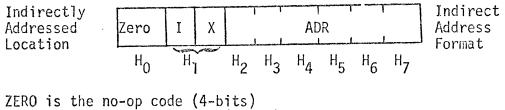

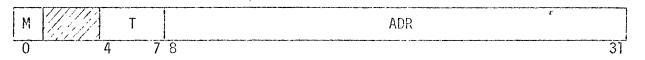

Indirect address requests cause transfer of the effective address register to the look-ahead address register (LA). The indirect address is requested from central memory by LA. The octet containing the indirect address is read from memory and entered into instruction file KCM. The indirect address is selected from KCM by AR. At this point, the instruction register contains the indirect address which is interpreted according to the indirect address format.

Bit positions 5 through, 7 of the indirect format specify the index register to be selected into pre-index register, XR. Bit positions 8 through 31 of this format specify the indirect address, designated ADR. The four most significant bits of the indirect address format (bit positions 0 through 3) must be zero to indicate a "no-operation" for the Arithmetic Unit. The 24-bits of ADR and XR are added in the index addition section of the IPU. The result appears in register AR.

If the indirect bit (bit position 4) of the indirect format is a one, then the contents of AR is a singleword central memory address which points to the next level of indirection. The next level indirect address is requested from central memory via the LA register path. The process described in the preceding paragraph is repeated for each level of indirect addressing.

If the indirect bit of the indirect format is zero, then the terminal indirect address has been reached and the index addition hardware of the IPU develops the address of the operand using displacement indexing according to the word size of the instruction being executed. The terminal indirect address is sent to the central memory address requestor in the MBU if the addressed data is not presently residing in either the X or Y data registers of the MBU. The 4 LSB's of the terminal indirect address are sent to the MBU word selection logic if the addressed data is present in either the X or Y data registers.

Subsequent scalar instructions from one of the instruction files follow the terminal indirect address into the IPU and normal instruction processing continues until another indirect, execute, or branch instruction is detected.

An exception to the above description on indirect addressing occurs for the case of a first level indirect address with  $\alpha \leq 2F$  and an M - field of zero. The first level indirect address is the address of the instruction word (the word with four non-zero most significant op code bits and indirect bit equal to one).

In this case, the value of the next level indirect address is selected from the register file and placed in the instruction register. After this, all subsequent levels of indirection are through central memory. Indirect references through the register file can occur only once for a given instruction.

# IMMEDIATE OPERAND DEVELOPMENT

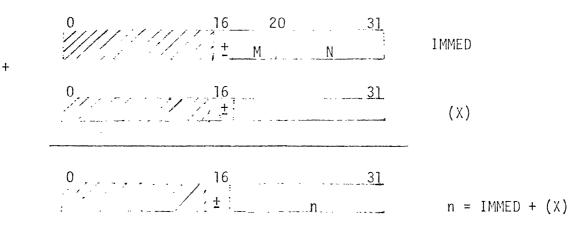

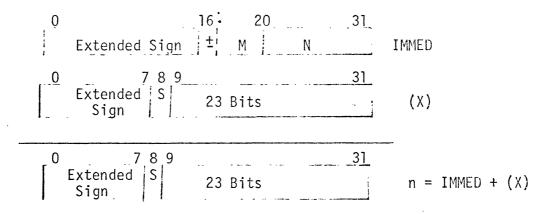

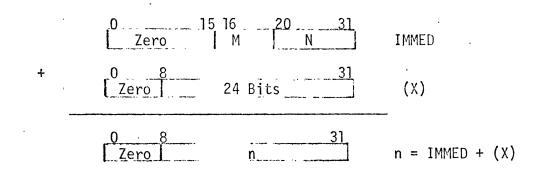

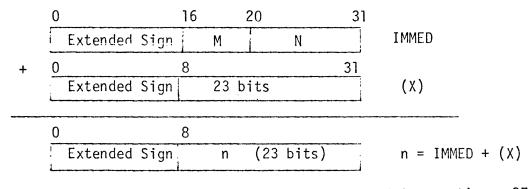

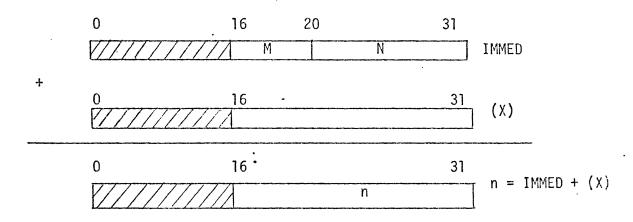

Immediate operand instructions use the index adder for modifying immediate values. The M and N-fields of the instruction word combine to form a 16-bit value which is added to a nonshifted index register selected from the T-field. Sign extension into the left halfword occurs prior to addition using the MSB of the M register for singleword arithmetic immediate operand instructions. Zeros replace sign extension for singleword logical immediate operand instructions. Halfword immediate instructions use only the right halfword of the result from the index adder.

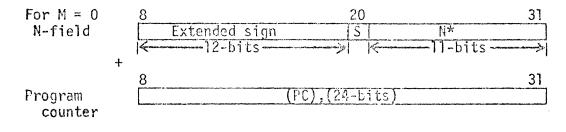

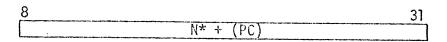

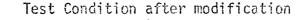

### BRANCH ADDRESS DEVELOPMENT

Branch address development takes place in the index adder of level 3 using inputs from the index selection register, XR, and base selection register, BR, of level 2. When the M-field of the branch intruction is zero, the program counter value replaces the base register value in BR. The branch address is taken relative to the program counter plus index (if specified by T).

Indirect branch addresses are developed similar to indirect operand, addresses with the exception that indirect branch instructions with  $\beta \leq 2F$  and M = 0 reference central memory and not the register file.

### DETERMINATION OF BRANCH CONDITION

Instructions of the type "Branch on Register Greater than" use a special adder unit in the IPU to determine the outcome of the branch test without having to wait for the Arithmetic Unit to perform the operation of adding to a register and testing the result with respect to the contents of another register. This special adder is incorporated in the IPU hardware and receives its inputs from the AØ and RØ registers at level 4.

For the branch instruction under discussion, the operation involves taking the singleword contents of the arithmetic register specified by the R-field and adding to it the contents of the arithmetic register specified by T. The result is compared with the contents of the arithmetic register specified by T plus one. In the IPU, this operation is accomplished in the branch test level by taking the register operand specified by R from the left half of 64-bit register RØ. The left half of 64-bit register AØ supplies the register addressed by T. The right half of register AØ supplies the register addressed by T plus one. These three singleword register values are added in the 3-input "branch test adder". The input from register T plus one is complemented (one's complement) before addition so that the addition which takes place is the evaluation of  $(G)_R + (G)_T - (G)_{T+1}$  using one's complement addition. The result of this addition will appear to be one less than the 2's complement addition of the same number. If one desires the sum to be greater than zero in 2's complement addition, then the sum must be greater than minus one in one's complement addition. Therefore, the outcome of the branch test for this instruction is true if the output of the one's complement addition is zero or positive. This can easily be determined from the sign position alone.

Many other branch and test instructions fall into the class that can take advantage of the branch test level. More specifically, all of the increment or decrement test and branch instructions can use this means for determining the outcome of the branch test without waiting for the increment or decrement operation to take place in the arithmetic unit. Conditional Branch instructions which compare the R-field value with the Condition Code or Result Code are of a different nature than the branch instructions just mentioned. The outcome of Conditional Branch instructions are known only if all previous instructions which set the Condition Code or Result Code have passed through the Arithmetic Unit. If the proper code has not been set, then the Branch on Comparison or Branch on Results instruction must wait in level 3 of the IPU until the code has been set by the AU. The branch address is held in the AR register of the index adder until the branch decision is made. Then, if the branch is taken, the branch address is transferred to the PA and LA registers and then central memory instructions along the branch path are requested.

## STORAGE OF AU RESULTS INTO THE REGISTER FILE

The IPU has the function of retaining the destination register address of all scalar instructions (vector instructions cannot store into the register file). These register addresses are held in a chain of 7-bit registers. Seven bits address all 48 singleword registers down to the halfword level. The chain of register addresses is as long as there are sections to the Central Processor pipeline. Additional bits are carried along for control.

The IPU provides the proper alignment from the AU to the register file for single, half, and double length register operand results. It also performs the selection enabling to the gate inputs of the register file.

# SCALAR MAZARD AND REGISTER CONFLICT RESOLUTION

These functions are described in Section B2. Scalar hazards occur when the effective operand address developed by an instruction is the same as the address of a store instruction which preceeds the read instruction and which has not yet passed completely through the Central Processor pipeline structure. The hazard condition will clear when the store instruction performs its write operation into central memory.

Register Conflicts exist when an instruction requires a register operand which is presently in the process of modification or is going to be modified by the Arithmetic Unit and which has not yet emerged from the AU output. The register conflict will resolve itself when the needed register is loaded with the result from the Arithmetic Unit and no other modification will occur to the contents of that register as a result of other instructions between the AU output and the instruction which requires that register.

# GENERATION OF VECTOR STARTING ADDRESSES

The index and base selection level and the index addition level develop the effective starting addresses for vector instructions from the vector starting addresses plus index values as specified by the vector parameter file. The generation of continuous addresses for sustaining vector operations is carried on by the Memory Buffer Unit. Section B2 and B3, vector timing and the vector parameter file descriptions in the instructions describe the operations to be performed for generating vector starting addresses.

# TRANSMITTAL OF VECTOR PARAMETERS TO THE MBU DURING VECTOR INITIALIZATION

The vector starting addresses contained in 29, 2A, & 2B and other vector parameters contained in register file addresses 28, 2C, 2D, 2E, 2F, and the 4 MSB's of 2A and 2B must be transmitted to the Memory Buffer Unit (MBU) prior to starting the first arguments of the vector operation through the Arithmetic Unit. Vector starting addresses are sent to central memory immediately after being received at the MBU and while the remaining vector parameters are still being transmitted from the IPU.

The parameters are selected via the A register operand selection network and gated into the A $\emptyset$  register of the IPU one word at a time. The output of A $\emptyset$  goes to the IMM register at the MBU input and from there the parameters are distributed to the operational registers (working registers) of the MBU. These operational registers control the vector address generating hardware in the MBU which sustains the vector operation.

When vector initialization is completed the IPU brings the next three scalar instructions, if such exist, down through levels 1, 2, and 3 of the IPU hardware. These instructions reside in the top of the IPU pipeline until the last element result of the vector operation has been sent to central memory.

Some vectors, namely Vector Order, Dot Product, Search, Compare, and Peak Pick, require special consideration. These vectors must be restarted at their beginning addresses when reinstated following a context switch operation if the switching occurred during their vector processing interval. For these vectors the IPU retains the vector instruction in level 3 and reserves level 2 for recomputing that vectors starting addresses. The following instruction after the vector resides in IPU level 1. The memory buffer unit (MBU) provides an interface between central memory and the arithmetic unit (AU). The communication with central memory is via a private port of the memory control unit (MCU). During scalar operations, data specified by effective addresses developed in the instruction processing unit (IPU) are fetched or stored as required. For most vector operations, two operand data strings are fetched while a result data string is stored. Addresses for systaining the vector operation are computed in the MBU using parameters initially specified by the vector parameter file in the IPU. 'Details for the one times ASC are described below. An overall block diagram of the Central Processor is depicted in Figure 1.

#### DATA PATHS IN MBU

Octets from central memory are received and synchronized in the register designated SC. A direct path is provided for transfer to either the X or Y registers from SC. The XH and XY registers provide a second level of buffering so that vector processing can be sustained at a high rate with a minimum of memory limiting. The SC register is always transmitted to its destination on the next clock after it is received from CM. The XB and YB registers provide a third level of buffering and are used to equalize the processing rate between the two operand paths. Both X and Y can also be stored in central memory for maintenance purposes.

Results from the AU which are to be stored in central memory are aligned and placed in the Z register. The Z register can be transferred to either X or Y so that memory references are not necessary for scalar memory opeands which reside in Z.

If the result of the output of the AU is in a different octet than the octet currently represented in Z, then Z must be transferred to the ZB register which in turn must be transferred to central memory. The transfer of Z to ZB must be held up until the previous write request no longer requires ZB. If ZB contains half words, it is possible to have incompletely specified single words. A path from SC to ZB is provided to permit half word fill-in from central memory.

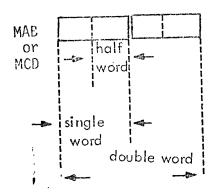

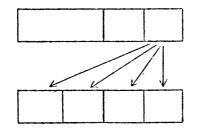

The register pairs designated MAB and MCD present two operands to the AU receiver registers. Each pair can contain half words, single words or doublewords. Their positioning is shown in Figure 3.

Figure 3. MBU Output Registers

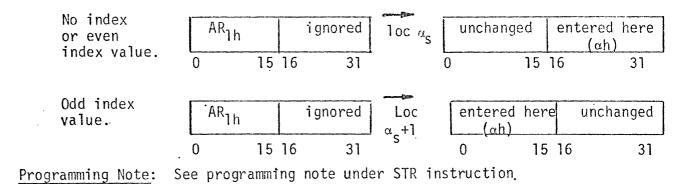

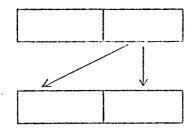

Selection networks are provided for both X and Y and are capable of selecting half words, single words, or double words. The outputs are therefore 64 bits wide. Single words are placed in the most significant bit positions. Half words are aligned and signs extended so that they appear as single words. The X register file selection can be transferred to either MAB or MCD. The transfer to MCD is for scalar requests of the X register file. The Y register file is transferred only to MCD.

Register and immediate operands from the IPU are received in the REG and IMM registers respectively. They can then be transferred to the MAB and MCD registers as required.

The MBU receives vector initialization data from the vector parameter file in the IPU via the IMM register. A path from IMM to MAB is required for vector A immediates.

### SCALAR OPERATION

During scalar operation the MAB register presents the IPU's register data to the AU while the MCD register presents the "memory" data. The "memory" data can be selected either from X or from Y or can be an immediate operand from the IPU.

The IPU sends two types of addresses, octet and element. The octet addresses are required when an octet is to be read or written and is not currently represented in the MBU. The four bit element addresses specify which elements are to be read or written. Operand addresses are accompanied by destination (X or Y) tag. Both operand and result addresses are accompanied by word size information. Scalar operations utilize part of the structure required for vector operations. Details, are discussed with vector operations.

### VECTOR PROCESSING

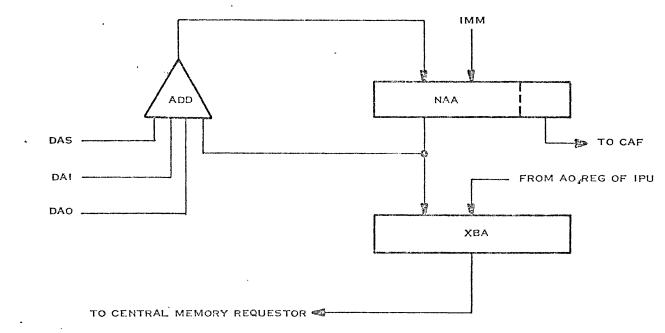

During vector operation, the X and Y registers present elements of vectors  $\vec{A}$  and  $\vec{B}$  to the AU. The addresses for these operand data strings are computed in the  $\vec{A}$  ADDRESS GENERATOR and the  $\vec{B}$  ADDRESS GENERATOR. A detailed diagram is shown in Figure 4 for the  $\vec{A}$  ADDRESS GENERATOR.

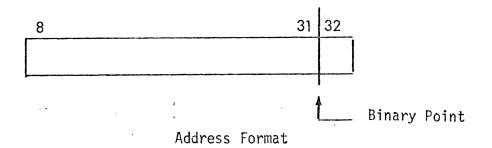

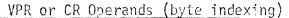

Successive addresses are the outputs of a 25 bit adder with the format shown below. This output is the sum of the last address and one of the increments corresponding to the self, inner, or outer loops. The increments associated with a self loop are one element increments and will be  $\pm 1/2$ ,  $\pm 1$  or  $\pm 2$  depending on word size. The inner loop increment is designated DAI. The outer loop increment is designated DAØ. Both DAI and DAØ are initially 16 bit signed 2's complement numbers in the vector parameter file. They are adjusted according to word size, sign extended, and then placed in 25 bit registers in the MBU.

The initial address (IA) is transferred to the NAA register from the IMM register. The generation process is capable of providing addresses for continuous processing of single word vector elements since a new address can be computed at the rate of one address per clock.

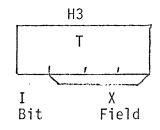

In order to minimize and frequently eliminate memory delay, a "three level" look ahead scheme is provided. The octet address being processed references data which is to replace the contents of the XB register. The address of an element must in some cases be formed 16 clocks prior to its use in the selection network. The XBA register receives a 21 bit octet address while a bit is set which initiates a memory request when appropriate. Octet comparisons are made between NAA and XBA. Memory requests are made only when a new octet is required.

The four bit element selection is stored in a file designated the circular address file (CAF). Since an additional 15 elements could be generated during the interval between the generation and use of a particular address, the CAF has space for 16 four bit entries. An additional three bit "TAG" must be stored for each entry. The first of these three bits indicates the presence of an address. The second bit indicates the end of a self loop. The third bit indicates the first address of a new octet.

102242

102241

# Figure 5. $\overrightarrow{C}$ Address Generator

Memory Buffer Unit 17 Section B1 The operand address register XBA is also used for scalar operation. Appropriate portions of the 25 bit addresses from the AR register in the IPU are transferred to the XBA register and the XA register. The IPU indicates whether or not the octet \_s currently in the X register. The XBA register is sent to the ØA register only if a new octet is required. The XA register is used to enable the X selection network.

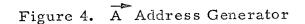

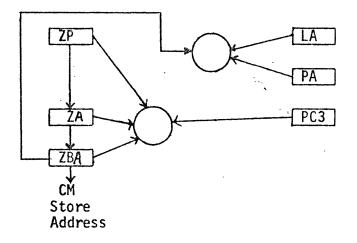

During vector operation, the Z register accepts elements of vector  $\vec{C}$  from the AU. The addresses for the output data string are computed in a section designated the  $\vec{C}$  ADDRESS GENERATOR. Addresses are generated one clock prior to their use (at the alignment network). Successive addresses are the outputs of a 25 bit adder in an arrangement similar to that for operand address generation. The initial (IC) is transferred to the NCA register where successive addresses are also placed. New octets are detected between NCA and ZA. If ZBA is available ZA can be transferred to record modification (down to half words) for both Z and ZB. Half word fill-in can then be accomplished when required. The ZB modification bits are combined in pairs to specify zone control bits for all ZB write operations. The ZA register is presented to the IPU during vector operation so that hazards can be detected in the IPU.

During scalar operation, addresses from ZP in the IPU are sent to ZA and ZEA. Since the IPU indicates octet changes, the MBU continually transmits the availability status of ZBA for write operations. When ZBA is not "busy", ZA can be transferred to ZBA and the write operation processed.

• Operation of the MBU is under control of the section designated the SEQUENCE CONTROL. Inputs to this section are status of the memory requestor, status of each ddress generator, and status of the loop counters. Three sets of loop counters are provided, two from operands and one for results. The inputs combined with the present state of the SEQUENCE CONTROL determine gate enables as well as the next state.

The AU control ROM is located in the MBU. Instruction codes are received from the IPU and used as addresses for the ROM which generates an array of signals which control the AU.

### CENTRAL MEMORY REQUESTS

All central memory requests are made through a controller designated the CENTRAL MEMORY REQUESTER. The CENTRAL MEMORY REQUESTER establishes priority for the three address generators and makes the appropriate requests to the MCU. It also provides for the distribution of read data upon arrival in the MBU. A maximum of four requests may be in some state of development during vector operation. Requests can also be processed for the hard core controller during maintenance operations.

### MEMORY BUFFER UNIT SUMMARY

Effective addresses developed by the index unit in the IPU are routed to the memory buffer unit. For most scalar instructions the memory buffer unit obtains one operand from the central memory location specified by the effective address and one operand from a register as presented from register selection. The memory buffer presents these operands to the arithmetic unit for processing. The arithmetic unit results replaces the register operands to the register file of the IPU. When results are to be stored into central memory, the memory buffer unit receives the effective address into which the data is to be stored and after AU processing provides for the storing operation.

For vector operations, the memory buffer unit supplies the consecutive operands to be processed and stores the results in central memory.

The memory buffer unit is comprised of two triple buffered eight-word register groups for reading and one double buffered eight-word register group for writing in the one times ASC system. Triple buffering is provided so that vector processing can be sustained at a high rate with a minimum of memory limiting.

For scalar operations, buffers X and Y are alternated for memory read operations. Buffer Z is used for memory write operations. In either case, the strategy is to invoke a memory cycle only when one is needed. For example, a read request for data within an octet currently residing in a buffer is terminated at the buffer. A write operation into a previously defined write octet is likewise terminated at the buffer. An actual read cycle occurs only when the required data is not within a current octet. An actual write operation occurs only when a new write octet is defined.

For vector operations, buffers X and Y supply strings of numbers to be processed and buffer Z accepts the resultant string of numbers.

ENERAL

The ASC Arithmetic Unit is basically a sixty-four bit oriented unit. The unit is used for both fixed and floating point instructions. Floating point numbers are in sign and magnitude along with an exponent represented by an excess 64 number.

A distinguishing feature of the ASC AU is the pipeline structure which allows efficient processing of vector instructions. There are seven exclusive partitions of pipeline involved, each of which is designed to provide an output every sixty nanoseconds. The seven sections are referred to as (1) Exponent Subtract, (2) Align, (3) Add, (4) Normalize, (5) Multiply, (6) Accumulate, and (7) Output.

The first four sections mentioned above are the basic structure of a floating point add instruction. Each of the sections perform parts of other instructions; however, they are primarily partitioned in this way to increase the floating point add time. Each of these sections is capable of operating on double length operands so that vector double length instructions can proceed at the clock rate. The align section is used to perform right shifts in addition to the floating point alignment for add. The normalize section is used for all normalization requirements and will also perform left shifts for fixed point operands. The add section employs second level look-ahead techniques to perform both fixed and floating point additions. This section is also used to add the pseudo sum and carry which is an output of the multiply section.

The multiply unit is able to perform a 32 by 32 bit multiplication in one clock time. The multiplier is also the basic operator for the divide instruction and double length operations for both of these instructions require several iterations through the multiply unit to obtain the result. Fixed point multiplications and single length floating point multiplications are available after only one pass through the multiplier. The output of the multiply unit is two words of 64 bits each, i.e., the pseudo-sum and pseudo-carry which must be added to the add section to obtain the proper solution. A double length multiplication will be performed by pipelining the three following sections: multiply, add, and accumulate. The accumulate section is similar to the add unit and is used for special cases such as VDP or any instruction which needs to form a running total. Double length multiplication is such a case, as three separate 32 x 32 bit multiplications will be performed and then added together in the accumulator in the proper bit positions. A double length multiplication would therefore require six clock times to yield an output while single length would require only four. A double length multiplication implies that two sixty-four bit floating point numbers (56 bits of fraction) are multiplied to yield a sixty-four bit result with the low order bits truncated after postnormalization. This multiplication ignores a possible round-off which is obtained by making a fourth pass with the two least significant halves of the operands. A fixed point multiplication will perform a 32 x 32 bit multiplication and yield a sixty-four bit result.

As would be expected, division is the most complex operation to be performed by the AU in the ASC. The method used takes advantage of the fast multiplication capabilities and employs an iteration technique which upon a specified number of multiplications will form the quotient to the desired accuracy. This method does not form a remainder. However, a remainder can be obtained under program control. Assuming X/Y = Q was the solution, the remainder can be formed by multiplying Y · Q and subracting from X;  $R = X - Y \cdot Q$ . The remainder will be accuracte to as many bits as the dividend X. For floating point operations, each of the operands, along with the result, are equal in length. For fixed point single length division, the divisor and result are 32 bits while the dividend is 64 bits in length.

The output section is used to gather outputs from all other sections and also to do simple transfers, Booleans, etc. which will require only one clock time for execution in the AU.

### FLOATING POINT OPERANDS

A guard digit consisiting of four least significant bits is provided to avoid loss of one hexadecimal digit of accuracy which would result from truncation prior double length additional and subtraction. The addition of these bits is sufficient since the only times normalization will be required with a possibility of loss of accuracy, the normalization will require a shift of only one hexadecimal digit. Normalized operands are required for the guard digit to be of maximum use. For example, in multiplication, given two operands which are normalized, the fractions will be  $2^{-4} < f < 1$ . The result will be  $2^{-8} < f < 1$ . Thus, the result will always require at the most one four-bit shift to normalize. The addition case is more involved but can be explained by discussing three possibilities. If the exponents are equal, no alignment is required therefore the guard digit is not necessary. If the exponents differ by one, the guard digit will retain significant information. Finally, if the exponents differ by more than one, it can be shown that the result to be normalized will require at most a shift of one hexadecimal digit. Thus, the guard digit contains information that can be retrieved.

The results of floating point operations treat overflow and underflow as suggested by the Share XXVII conference. Any overflow or underflow results in the correct mantissa and the exponent correct modulo 128. An output from the AU indicates overflow or underflow. The output can then be employed by taking proper action.

# STRUCTURE

Exponent Subtract - The exponent subtract section is primarily responsible for determining the proper inputs to the add section for use in floating and instructions. It is used for both scalar and vector operations and is also responsible for supplying proper input to the accumulator section for floating vectordot product instructions. This section determines the difference in the exponents of floating point operands or in the case of equal exponents, which mantissa is larger. Upon determining the larger number, the true or complement of the operands are gated into registers according to the operation to be performed such as Add, Subtract, Add Magnitude, etc. Also, at this time a seven bit subtracter determines the exponent difference which is used in the align section to properly align the floating point operands.

Since logic is required in this section to determine relative magnitudes of the mantissa, the test instructions for greater than, less than, or equal to are also performed in this section to avoid repetition of hardware.

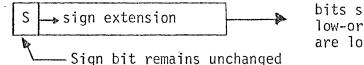

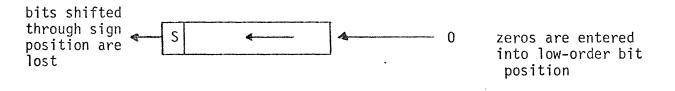

<u>Align</u> - The align section is in operation for all floating add instructions or for any right shift instruction. Floating point instructions are performed after one pass through the align section while fixed point shifts require two cycles.

The shift logic has provisions to allow any shift length which is a multiple of four to be performed in one cycle. Since floating point numbers are represented in hexadecimal digits, this will facilitate the very fast floating point additions. The length of right shift can be obtained from the instruction word for a shift instruction or from the exponent difference information as supplied by the exponent subtract section.

Fixed point right shifts are performed by first shifting in one cycle the largest multiple of four-bits contained within the shift value. Then, the residue of 0, 1, 2, or 3 bits is shifted on the next cycle. This results in a minimum of shift paths into each latch since the four bit paths already exist.

Add - The add section is shared for many instructions depending only upon which paths are selected into the section. Floating add instructions are entered by way of the align section. Fixed point add operands enter the arithmetic unit at the add section. The adder is also used to add the pseudo sum and carry from the multiply section to obtain any multiplication result.

The adder is 64 bits in length and contains second level look-ahead logic. The floating point numbers are in the proper format when entering the add section, however, the fixed point operands are modified to reflect either add, subtract, or add magnitude type instructions.

<u>Normalize</u> - The normalize section is employed for both floating add instructions and fixed point left shift instructions. Divisors are routed through this section to guarantee bit normalized inputs for divide instructions.

22

This section closely resembles the align section in that floating point operations require only one cycle while fixed point shifts require two. The major difference in the two sections is that the align section is given the information concerning length of shift for hexadecimal digits in floating point. The normalize section has to compute the length of shift required to normalize a floating point number by examining to determine which four bit group contains the most significant logical one. An adder is also required to update the exponent when a normalization takes place.

Fixed point left shift instructions are supplied with the length of left shift from the instruction word.

<u>Multiply</u> - The multiply section is required to operate on both floating and fixed point operands. The floating point numbers are represented in sign and magmitude where the fixed point numbers are in two's complement from. The method of multiplying is keyed to two's complement operands with the floating point multiplication performed by arbitrarily assigning positive signs during the multiplication and then applying the proper sign when multiplication is complete.

The multiplier is capable of multiplying any two numbers up to 32 bits in length in only one pass through the multiply section. The result is in the form of a pseudo sum and carry which must be added together to obtain the result. The sum and carry are added together in the add section which has been discussed separately.

The multiply section is also used to perform division by a sequence of multiplication operations.

<u>Accumulator</u> - The accumulator is a special purpose section which is employed when an vector operation is being performed requiring an accumulated total. A prime example of this is the Vector-Dot-Product instruction.

Like the add section which was previously described, the accumulator performs a second-level look-ahead to facilitate a fast addition.

<u>Output</u> - All results to be sent to the CP must be gated through the output section. Information could have originated in any one of the other sections of the AU with the exception of the multiply section.

Simple instructions such as Booleans, transfers, masks, etc. are performed in this section and gated out in one pass through the section.

# CENTRAL PROCESSOR TIMING ANALYSIS

# TABLE OF CONTENTS

# TITLE

-

# SCALAR INSTRUCTION TIMING

| ARITHMETIC UNIT                      | 1  |

|--------------------------------------|----|

| OPERAND FETCHING TIME                | 1  |

| REGISTER CONFLICT DELAY              | 7  |

| MULTIPLE STORE INSTRUCTION DELAY     | 9  |

| READ AFTER WRITE DELAY               | 10 |

| INDIRECT ADDRESS GENERATION TIME     | 11 |

| EXECUTE INSTRUCTION FETCHING         | 11 |

| INSTRUCTION FETCHING AFTER BRANCHING | 12 |

| INSTRUCTION HAZARD CONDITION         | 12 |

|                                      |    |

| CTOD INSTRUCTION TIMING              |    |

# VECTOR INSTRUCTION TIMING

.

-

,

| VECTOR PARAMETER FILE FETCH | - 15 |

|-----------------------------|------|

| MBU INITIALIZATION          | 16   |

| MEMORY OPERAND FETCH        | 16   |

| AU FILL                     | 17   |

| AU EMPTY                    | 17   |

.

Scalar instruction processing time in the Central Processor (CP) can be predicted with a fair degree of accuracy by considering the following factors:

- 1. Arithmetic Unit clock time

- 2. Operand fetching time

- 3. Register conflict delay

- 4. Multiple store instruction delay

- 5. Read after write delay

- 6. Indirect address generation time

- 7. Execute instruction fetching time

- 8. Instruction fetching time after a branch instruction without look ahead

- 9. Instruction hazard refetch time

# ARITHMETIC UNIT CLOCK TIMES

Arithmetic Unit clock times (Table 1) are defined as the number of clocks required to propagate input arguments through the AU, to the AU output registers. Certain instructions can be executed in sequence by the Arithmetic Unit without creating periods of inactivity or delays in pipeline flow. The instructions listed in Table 2 are divided into fourteen groups. Any single instruction in groups 2 through 11 may follow-any instruction in groups 1a and 1b without creating a delay due to different AU types.

# OPERAND FETCHING TIME

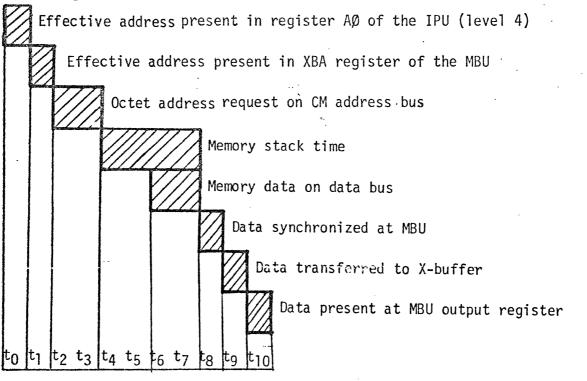

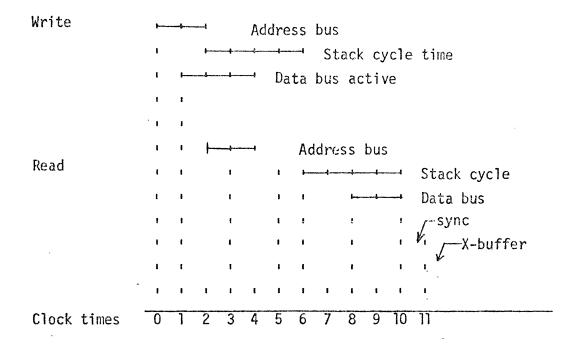

Operand fetching time refers to Central Memory access time for obtaining memory operands. This time is measured from the clock at which the effective address of the operand is at the address output register (AØ) of the Instruction Processing Unit (IPU) to the clock at which the requested operand resides in the output register of the Memory Buffer Unit (MBU). This time is normally ten clocks if there are no memory conflicts at the MCU or priority delays at the MBU memory controller as illustrated below:

Central Processor Clock Time

Scalar Instruction Timing 1 Section B2

# TABLE I. ARITHMETIC UNIT TIME REQUIREMENTS FOR SCALAR INSTRUCTIONS

| <u>LØAD</u> | L<br>LI<br>LH<br>LIH<br>LR     | <u>Cloc</u> | k <u>Times</u><br>1<br>1<br>1<br>1 | <u>ARITHMETIC</u> | A<br>AI<br>AH<br>AIH<br>AF        | <u>C100</u>                      | <u>2</u><br>2<br>2<br>2<br>2<br>2<br>5<br>5<br>5 |

|-------------|--------------------------------|-------------|------------------------------------|-------------------|-----------------------------------|----------------------------------|--------------------------------------------------|

|             | LL<br>LD                       |             | 1                                  |                   | AFD                               |                                  |                                                  |

|             | LM<br>LMH<br>LMF<br>LMD        |             | 2<br>2<br>1<br>1                   |                   | am<br>Amh<br>Amf<br>Amfd          |                                  | 2<br>2<br>5<br>5                                 |

|             | LN<br>LNH<br>LNF<br>LND        |             | 2<br>2<br>1<br>1                   |                   | S<br>SI<br>SH<br>SIH<br>SF<br>SFD |                                  | 2<br>2<br>2<br>5<br>5                            |

|             | LNM<br>LNMH<br>LNMF<br>LNMD    |             | 2<br>2<br>1<br>1                   |                   | SM<br>SMH<br>SMF<br>SMFD          |                                  | 2<br>2<br>5<br>5                                 |

| · .<br>:    | LF<br>LFM<br>XCH               |             | 1<br>*<br>2                        |                   | M<br>MI                           |                                  | 3                                                |

|             | LAM<br>LAE<br>LLA<br>LO        |             | 1<br>1<br>1<br>1                   |                   | MH<br>MIH<br>MF<br>MFD            | R-even<br>29                     | 3<br>3<br>3<br>4<br>6<br>R-odd<br>18             |

|             | ST<br>STH<br>STR<br>STL<br>STD |             |                                    |                   | D<br>DI<br>DH<br>DIH<br>DF<br>DFD | 29<br>29<br>18<br>18<br>15<br>25 | 18<br>18<br>18<br>18<br>15<br>25                 |

|             | SPS                            |             | 1                                  |                   |                                   |                                  |                                                  |

|             | STZ<br>STZH<br>STZD            |             | 1<br>1<br>1                        |                   |                                   |                                  |                                                  |

|             | STN<br>STNH<br>STNF<br>STND    |             | 2<br>2<br>1<br>1                   |                   |                                   |                                  |                                                  |

|             | STO<br>STOH                    |             | 1<br>1                             |                   |                                   |                                  |                                                  |

|             | STF<br>STFM                    |             | 1<br>*                             |                   |                                   |                                  |                                                  |

\*Determined by memory access time. An LF instruction requires six memory read cycles and an SF instruction requires six memory write cycles.

~

2

# TABLE 1 (CONTINUED)

| LØGICAL           | AND<br>ANDI<br>OR<br>ORI     | Clock Times<br>1<br>1<br>1<br>1 | TEST &<br>BRANCH                 | BCC<br>BRC<br>BEC<br>BAE     | <u>Clock Times</u><br>-<br>-<br>- |

|-------------------|------------------------------|---------------------------------|----------------------------------|------------------------------|-----------------------------------|

|                   | XOR<br>XORI<br>EQC<br>EQCI   | 1<br>1<br>1<br>1                | REG. MOD<br><u>&amp; TESTING</u> | IBZ<br>IBNZ<br>DBZ<br>DBNZ   | 2<br>2<br>2<br>2                  |

|                   | ANDD<br>ORD<br>XORD<br>EQCD  | ]<br>]<br>]                     |                                  | ISE<br>ISNE<br>DSE<br>DSNE   | 3<br>3<br>3<br>3                  |

| <u>SHIFT</u>      | SA<br>SAH<br>SAD             | 3<br>3<br>3                     |                                  | BCLE<br>BCG                  | 2<br>2                            |

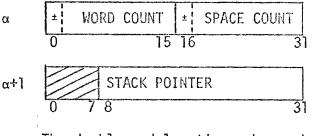

|                   | SL<br>SLH<br>SLD             | 3<br>3<br>3                     | <u>STACK</u>                     | PSH<br>PUL<br>MOD            | 3*<br>3*<br>3*                    |

|                   | SC<br>SCH                    | · . 3<br>3<br>3                 | SUB-ROUTINE<br>ANALYZE           | BLB<br>BLX<br>LEA            | . 1                               |

|                   | SCD<br>RVS                   | 6                               | ANALIZE                          | INT<br>XEC                   | ]<br>]<br>_                       |

| ARITH.<br>COMPARE | C<br>CI<br>CH<br>CIH         | 2<br>2<br>2<br>2                | CONVERSION                       | FLFX<br>FLFH<br>FDFX         | 5<br>5<br>5                       |

|                   | CF<br>CFD                    | 22                              |                                  | FXFL<br>FXFD<br>FHFL<br>FHFD | 4<br>4<br>4<br>4                  |

| LOGICAL           | CAND<br>CANDI<br>COR<br>CORI | ]<br>]<br>]                     | NORMALIZE                        | NFX<br>NFH                   | 3<br>3                            |

|                   | CANDD                        | 1                               | CALL                             | MCP<br>MCW                   | 1                                 |

|                   |                              |                                 | VECTOR                           | VECT (See                    | Vector Timing)                    |

\* Stack Instructions take multiple passes through CP pipeline.

.

| GROUP 1                                                    | a                                                 |                                   |                                  |                                           | GROUP 1                                           | lb                                                               |

|------------------------------------------------------------|---------------------------------------------------|-----------------------------------|----------------------------------|-------------------------------------------|---------------------------------------------------|------------------------------------------------------------------|

| L.<br>LI<br>LH<br>LR<br>LL<br>LD                           | AND<br>ANDI<br>OR<br>ORI<br>XOR<br>XORI<br>EQC    | CAND<br>CANDI<br>COR<br>CORI      |                                  |                                           | ST<br>STH<br>STR<br>STL<br>STD<br>STZ<br>STZH     |                                                                  |