LEXAS INSTRUMENTS NCORPORATED

# TEXAS INSTRUMENTS INCORPORATED

Semiconductor-Components Division

# **MOSFET** in Circuit Design

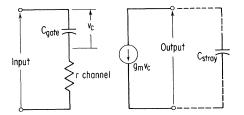

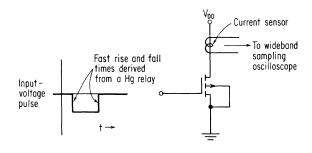

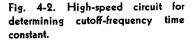

Metal-Oxide Semiconductor Field-Effect Transistors for Discrete and Integrated-Circuit Technology

**Robert H. Crawford**

№ Зааж Ній 43475 Texas Instruments Electronics Series McGraw-Hill Book Company

# MOSFET in Circuit Design

TEXAS INSTRUMENTS ELECTRONICS SERIES

MOSFET in Circuit Design

Texas 5 Instrument Incorperati

McGRAW-HILL

MOSFET in Circuit Design

### TEXAS INSTRUMENTS ELECTRONICS SERIES

Crawford

MOSFET IN CIRCUIT DESIGN

Delhom DESIGN AND APPLICATION OF TRANSISTOR SWITCHING CIRCUITS

The Engineering Staff of

Texas Instruments Incorporated CIRCUIT DESIGN FOR AUDIO, AM/FM, AND TV

The Engineering Staff of Texas Instruments Incorporated • SOLID-STATE COMMUNICATIONS

The Engineering Staff of Texas Instruments Incorporated • TRANSISTOR CIRCUIT DESIGN

Runyan • SILICON SEMICONDUCTOR TECHNOLOGY

Sevin • FIELD-EFFECT TRANSISTORS

# MOSFET in Circuit Design

# Metal-Oxide-Semiconductor Field-effect Transistors for Discrete and Integrated-circuit Technology

### **Robert H. Crawford**

Semiconductor Components Division Semiconductor Research and Development Laboratory Texas Instruments Incorporated

#### **MOSFET in Circuit Design**

Copyright © 1967 by Texas Instruments Incorporated. All Rights Reserved. Printed in the United States of America. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of Texas Instruments Incorporated. *Library of Congress Catalog Card Number* 67-16301.

13475

### 34567890 HDBP 7543210698

Information contained in this book is believed to be accurate and reliable. However, responsibility is assumed neither for its use or infringement of patents or rights of others which may result from its use. No license is granted by implication or otherwise under any patent right of Texas Instruments or others.

### Foreword

Until recently, field effect (unipolar) transistors have had relatively small usage as compared with junction (bipolar) transistors. While the earliest investigations of solid-state amplifying devices were in the direction of field-effect devices (majority carrier devices), the discovery and understanding of minority carrier injection across P-N junctions, led to the subsequent development of bipolar transistors. The bipolar transistor has proved to be an exceptional device, having properties which make it useful over a very broad range of applications. It also effectively made the transition from a two-sided structure to a one-sided structure required for monolithic integrated circuits, and is now the cornerstone of integrated circuits.

Why then, it is natural to ask, is there suddenly a new interest in field-effect devices, and particularly in the metal-oxide-semiconductor (MOSFET) type? The answer is twofold. First is the fact that our technology and understanding of surface oxides such as silicon dioxide  $(SiO_2)$  has increased to where very stable MOSFET devices can be reliably produced. Second, and most important, relates to large-scale integrated electronics (LSI). The semiconductor industry is moving rapidly toward integrating much more powerful logic and memory functions on silicon chips than today's production integrated circuits (which are typically three gates in a 14–16 lead package). It is in the domain of LSI that MOSFET technology has generated its greatest interest. The reason is simple one can put from five to seven times the functional complexity in a given area with MOSFET technology as is possible with bipolar technology. Coupled with this high functional density is the fact that exceptionally high yields can be achieved in the fabrication of large MOS integrated functions because of the relative simplicity of the process.

To go further in the discussion would begin to encroach on the author's excellent book; suffice it to say the area of MOSFET's is one of the most exciting in the semiconductor industry. Robert Crawford has prepared an excellent discussion of the MOSFET device and its application to integrated electronics. The reader will soon recognize that he is being given results of first-hand investiga-

### vi Foreword

tions—Robert Crawford indeed is a key contributor to the Texas Instruments MOSFET program.

This book is another in the Texas Instruments Electronics Series, published by the McGraw-Hill Book Company, in which we are attempting to bring the engineering and scientific audience up to date on subjects of significant current interest.

> RICHARD L. PETRITZ, Director Semiconductor Research and Development Laboratory Texas Instruments Incorporated

### Preface

The purpose of this book is to describe basic principles of the MOSFET—particularly as they apply to practical circuit design. The material presented here covers device theory and operation, device characteristics, and finally, device usage in discrete and integrated-circuit form. I have tried to encompass in a single text all the background material required by the design engineer to understand and appreciate MOSFET circuit design.

Material for this book was accumulated over a two-year period during which I was actively engaged in MOSFET circuit design within the MOS program of Texas Instruments Incorporated. It therefore includes much practical information gathered as a result of actual work with MOSFET circuits.

Device coverage within this book has been limited to the MOSFET and does not include the junction FET. There were two reasons for this approach. First, I believe the MOSFET is significant by itself and can stand alone. Second, junction FETS have been covered in an excellent book by L. J. Sevin, Jr.—"Fieldeffect Transistors," published by the McGraw-Hill Book Company as a part of the Texas Instruments Electronics Series.

The level of presentation is aimed at the practicing circuit-design engineer who has the responsibility of designing an MOSFET circuit. A general background in basic semiconductor theory and circuit design is assumed.

Chapter 1 is an introductory chapter written specifically for the person—such as the salesman, marketing man, or manager—who needs a broad understanding of MOSFET properties without going deeply into the theory. The last half of this chapter considers future trends in such areas as MOSFET technology, devices, and circuits.

Chapter 2 presents basic theory and operation of MOS field effects and derives descriptive equations for device behavior.

Chapter 3 considers the accuracy of the fundamental device equations, develops additional functional relationships, and deals analytically with mobility variation as a function of gate voltage.

Chapter 4 contains a description of the transient response of an MOSFET in a circuit.

Chapter 5 deals exclusively with the MOSFET in integrated-circuit form.

#### viii Preface

Basic concepts are presented, building blocks used in design are discussed, and an actual MOSFET integrated circuit is described in detail.

Chapter 6 covers the area of MOSFET usage in analog circuits and MOSFETbipolar combinations.

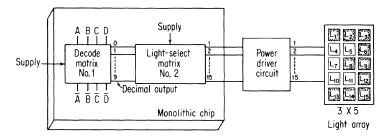

Like all authors, I am indebted to a number of individuals; without their assistance, this book could never have been written. My thanks are due mainly to Dr. R. M. Warner, Jr., and to Dr. J. R. Biard for their suggestions and help during the writing of the manuscript; to Dr. J. P. Mize for many valuable discussions on mobility; to John R. Miller, technical publications manager at Texas Instruments, for his editorial advice; to Louis Bartning for the design of the decoder shown in the text; to S. Naik for the design of the power MOSFET; to Clifford Arnell for the majority of photographs and measured data; to Mrs. Mary Chubin and Mrs. Eloise Ballard for cheerfully typing the manuscript; and, finally, to the management of Texas Instruments for providing an atmosphere conducive to the writing of this book.

Robert H. Crawford

## Contents

| FOREWOR<br>PREFACE<br>NOTATION |                                                        |

|--------------------------------|--------------------------------------------------------|

| Chapter 1                      | An Introduction to the World of the MOSFET 3           |

|                                | 1-1 Operation of the MOS                               |

|                                | 1-2 Characteristic Curves 6                            |

|                                | 1-3 Digital Circuits                                   |

|                                | 1-4 Speed                                              |

|                                | 1-5 Complementary Structures                           |

|                                | 1-6 The Future of MOS Technology                       |

|                                | BIBLIOGRAPHY                                           |

| Chapter 2                      | Theory of Operation                                    |

|                                | 2-1 Qualitative Analysis                               |

|                                | 2-2 Quantitative Analysis                              |

|                                | 2-3 Additional Consideration of the Threshold Voltage  |

|                                | 2-4 Summary of MOS Equations and Device Symbology. 47  |

|                                | BIBLIOGRAPHY                                           |

| Chapter 3                      | MOS Characteristics and Equation Interrelationships 51 |

|                                | 3-1 Saturation Region                                  |

|                                | 3-2 Triode Region                                      |

|                                | 3-3 Mobility                                           |

|                                | BIBLIOGRAPHY 69                                        |

| Chapter 4                      | Transient Response                                     |

|                                | 4-1 Cutoff Frequency                                   |

### x Contents

|           | 4-2   | Switching Speed of the MOS                  |   |   |   |   | 73<br>86 |

|-----------|-------|---------------------------------------------|---|---|---|---|----------|

| Chapter 5 | Basi  | c MOS Integrated-circuit Concepts           |   | • | • | • | 87       |

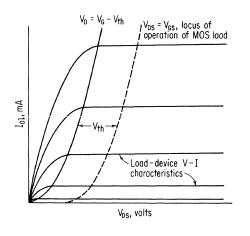

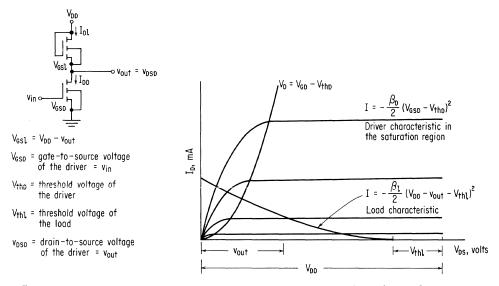

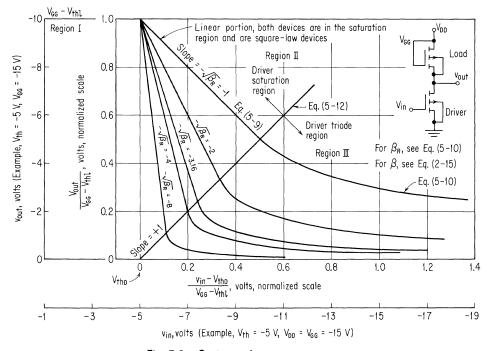

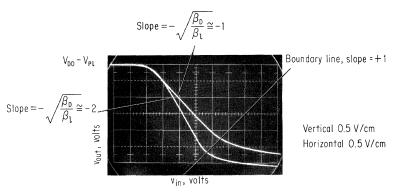

|           | 5-1   | The MOS as a Load Resistor.                 |   |   |   |   | 87       |

|           | 5 - 2 | MOS Inverter                                |   |   |   |   | 92       |

|           | 5 - 3 | Basic Building Blocks                       |   |   |   |   | 103      |

|           | 5-4   | Redundancy—Ideal for MOS Circuits           |   |   |   |   | 107      |

|           | 5 - 5 | Capacitor Storage for Simplified Circuitry. |   |   |   |   | 107      |

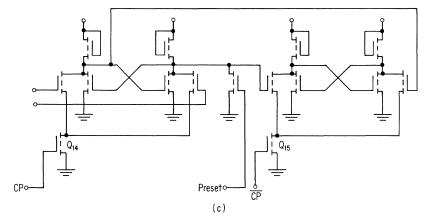

|           | 5-6   | Master-Slave Flip-flop                      |   |   |   |   | 111      |

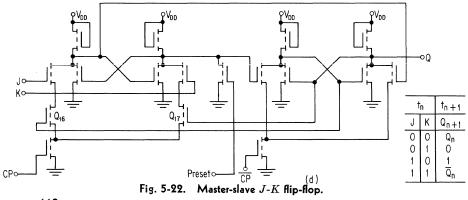

|           | 5 - 7 | Description of an Actual Integrated Circuit |   |   |   |   | 113      |

|           |       | BIBLIOGRAPHY                                |   |   |   |   | 118      |

| Chapter 6 | An    | alog Circuits                               |   | • | • | • | 119      |

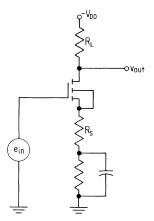

|           | 6-1   | Common-source Amplifier                     |   |   |   |   | 119      |

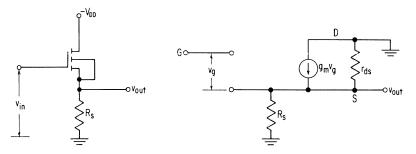

|           | 6-2   | Source Follower                             |   |   |   |   | 121      |

|           | 6-3   | Common-gate Amplifier (Grounded Gate) .     |   |   |   |   | 123      |

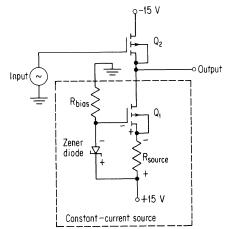

|           | 6-4   | Various Amplifier Configurations            |   |   |   |   | 124      |

|           |       | BIBLIOGRAPHY                                | · |   |   | · | 130      |

|           | APF   | PENDIX                                      | • |   |   |   | 131      |

|           |       | Conversion Table                            |   |   |   |   | 131      |

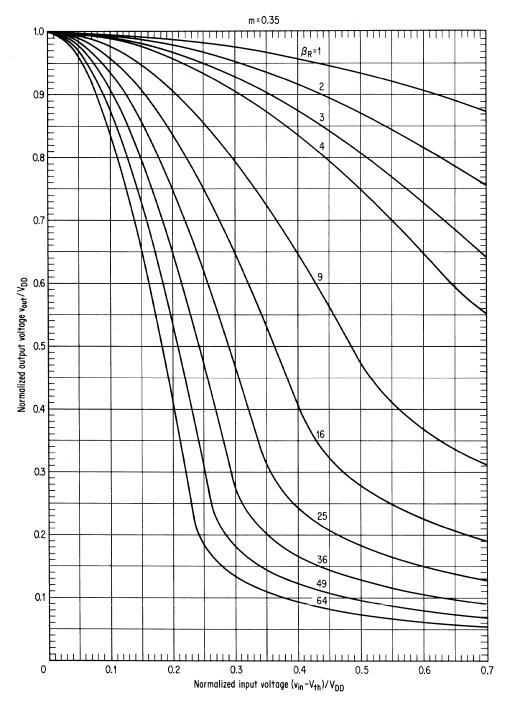

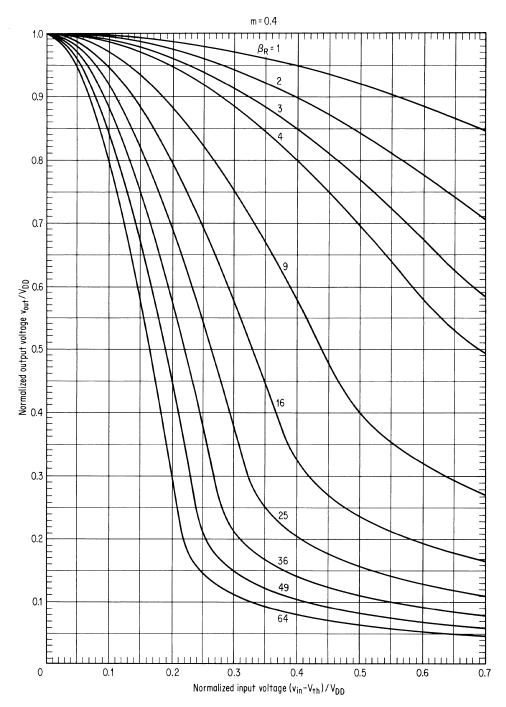

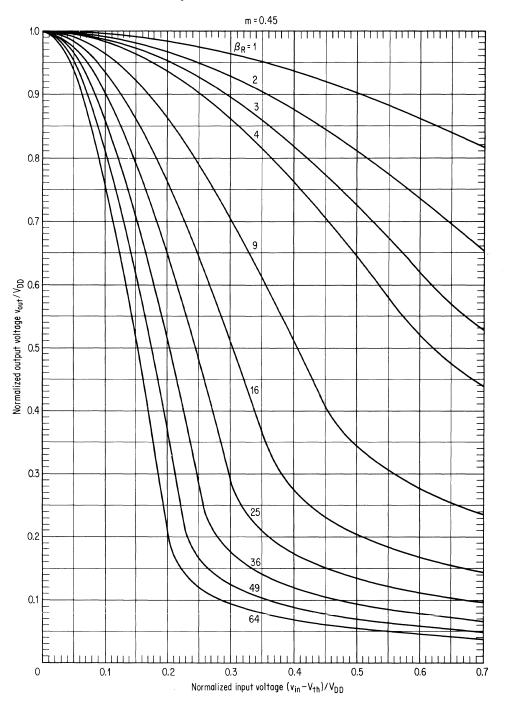

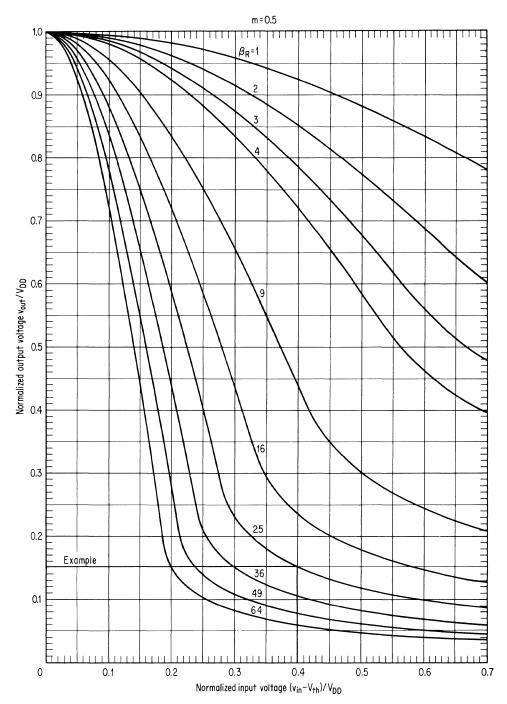

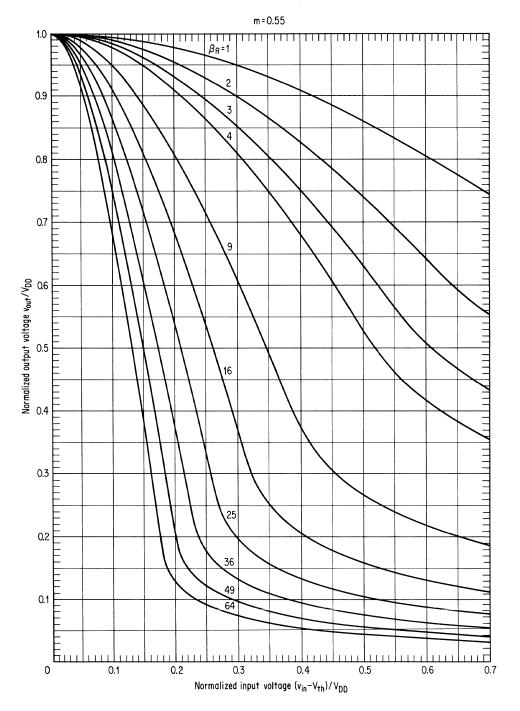

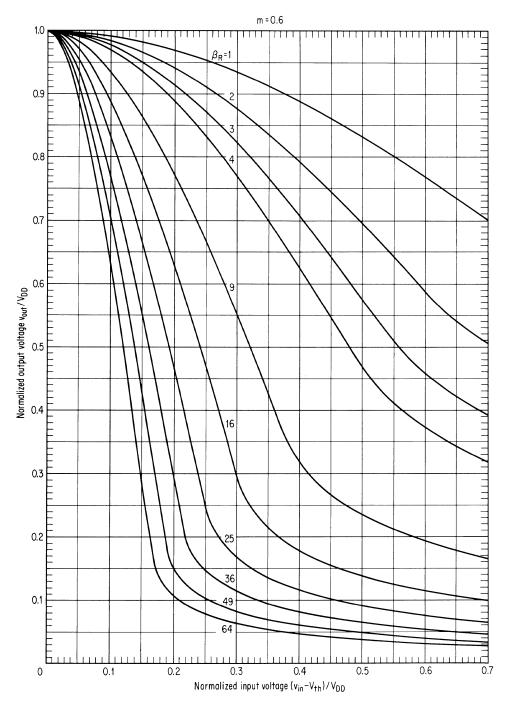

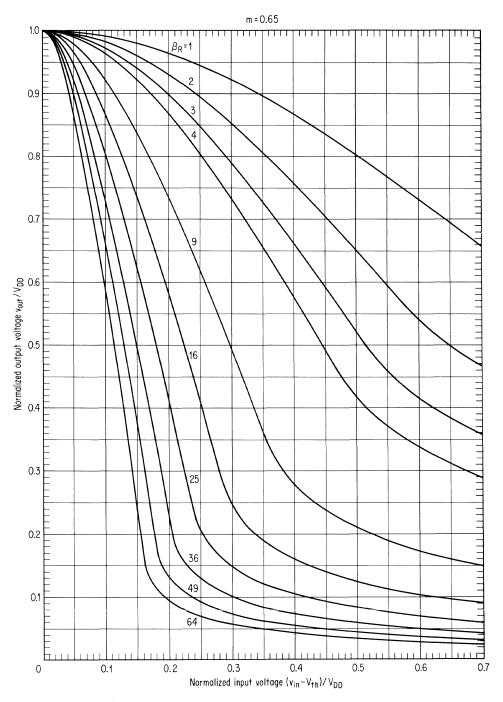

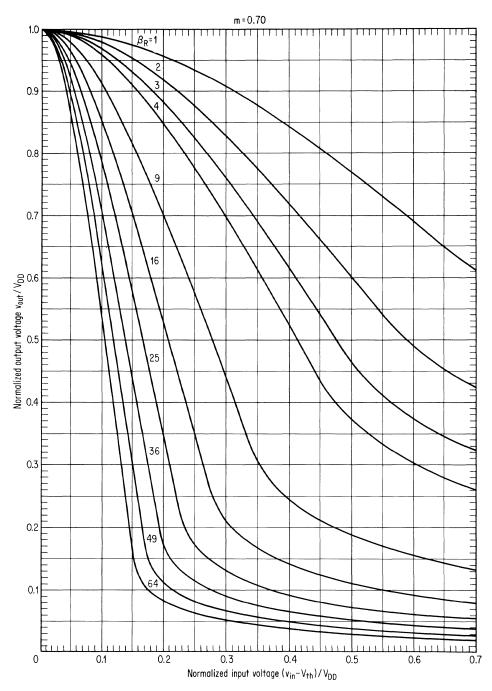

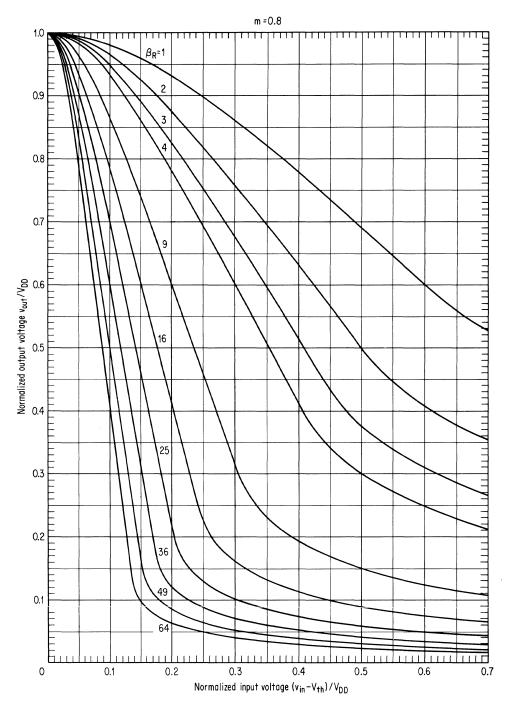

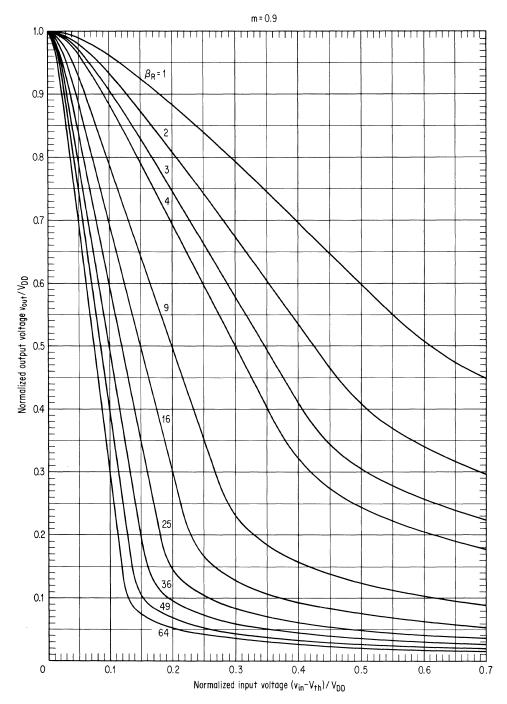

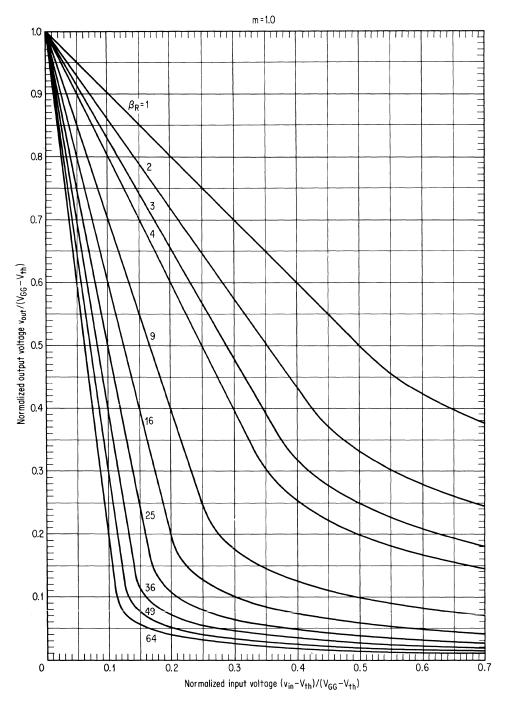

|           |       | Transfer Design Curves                      |   |   |   |   | 133      |

|           | INL   | DEX                                         |   |   |   |   | 145      |

### Notation

### A—area

- A<sub>v</sub>-voltage gain

- $\beta$ —"gain" term containing device constants; see Eq. (2-15).  $\beta_p$  is positive for P-channel devices, and  $\beta_n$  is negative for N-channel devices.

### $\beta(V_G)$ —indicates a dependency upon gate voltage

- $\beta_o$ —initial, low-voltage value

- $\beta_{R} \beta_{D} / \beta_{l}$ ; see Eqs. (5-9) and (5-10).

- C-capacitance

- $C_o$ —gate capacitance corresponding to the oxide layer over the channel area;  $C_o = A(\epsilon_{ox}/t_{ox})$ .

- $E_c$ —conduction-band energy level

- $E_F$ —Fermi energy level

- $E_i$ —intrinsic energy level; assumed to be at the center of the gap.

- $E_{ox}$ —oxide electric field

- $E_v$ —valence-band energy level

- $\epsilon_{ox}$ —oxide dielectric constant; assumed as  $\frac{1}{3}$  pF/cm (relative dielectric constant  $\cong 4$ ).

- $\epsilon_{s}$ —silicon dielectric constant; assumed as 1 pF/cm.

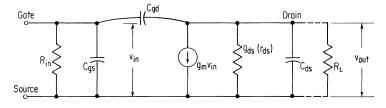

- $g_{ds}$ —drain conductance in the saturated region

- $g_{dt}$ —drain conductance in the triode region

$$g_m$$

—transconductance  $\equiv \frac{\partial I_D}{\partial V_G} \Big|_{V_D}$

$g_{mBG}$ —back-gate transconductance

$g_{mD}$ —transconductance of the driver device

- $g_{ml}$ —transconductance of the load MOS

- $g_{mo}$ —transconductance at  $I_{DSS}$  in a depletion-mode device

IC-integrated circuit

$I_D$ —drain current in the external terminal

$I_{DP}$ —drain current at the point of pinchoff

$I_{DSS}$ —drain current that flows when the gate is returned to the source

$J_c$ —channel current density

k—Boltzmann's constant

$K_1$ —constant; see Eq. (2-24). (+ for P channel, - for N channel)

- L—effective channel length (in direction of current flow)

- L'—length of the pinchoff region, measured from the edge of the channel at pinchoff to the edge of drain junction

- $L_T$ —channel length, measured from source junction to drain junction

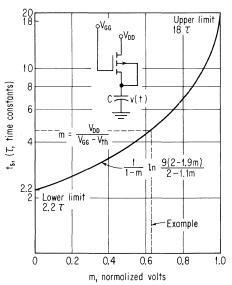

- m-voltage parameter in switching-time analysis; see Eq. (4-10)

- $N_A, N_D, N$ —doping levels

P-heavy P-type diffusion

- $\phi_{F}$ —Fermi function; the amount the Fermi level is displaced from the intrinsic level or the center of the gap (as measured in the bulk). Units are in volts. See Eq. (2-25).

- $\phi_s$ —Surface potential; the amount the intrinsic Fermi level, at the surface, has been bent with respect to the Fermi level.  $\phi_s$  is assumed zero in the flat-band case of Fig. 2-1e.

- q—electronic charge  $\cong 1.6 \times 10^{-19}$  coulomb

$Q_A$ —charge per unit area in the accumulation region

$Q_c$ —charge per unit area in the channel

$Q_D$ —charge per unit area in the depletion region

$Q_G$ —charge per unit area on the metal gate

$Q_I$ —charge per unit area in the inversion region

$Q_{ss}$ —See approximation No. 9 Chap. 2

$r_{ds}$ —drain resistance, saturation region

$r_{dt}$ —drain resistance, triode region

$R_p$ —parasitic resistance

$R_1 \parallel R_2$ —designation for  $R_1$  in parallel with  $R_2$

SR—shift register

$\theta$ —a constant in the mobility equation (3-28);  $\theta = \beta_o R_P$

- $\tau$ —time constant

- $t_{ox}$ —oxide thickness

- T-temperature

- $\mu$ —mobility; units are in cm<sup>2</sup>/V-sec.  $\mu_p$  has a positive sign;  $\mu_n$  has a negative sign.

$\mu(V_G)$ —indicates a dependency upon gate voltage

$\mu_o$ —initial low-voltage valve

v(t)—voltage as a function of time

$V_{BG}$ —back-gate bias

$V_D$ —voltage at the external drain terminal

$V'_D$ —intrinsic drain voltage, voltage at the internal drain terminal

$V_{DD}$ —drain supply voltage

$V_{DS}$ —drain-to-source voltage

$V_{G}$ —voltage at the external gate terminal

$V_{GG}$ —gate supply voltage

$V_{GS}$ —gate-to-source voltage

$V_{Ilk}$ —intrinsic threshold voltage; defined in Eq. (2-24)

$V_P$ —pinchoff voltage; see Eq. (2-18).

$V_P(v_o)$ —pinchoff voltage as a function of output voltage

$V_P(V_{BG})$ —pinchoff voltage as a function of back-gate bias  $V'_S$ —intrinsic source voltage, voltage at the internal source terminal

$V_{ss}$ —that portion of the threshold voltage due to  $Q_{ss}$

$V_{th}$ —threshold voltage; see Eqs. (2-22) and (2-27).

- $V_{thD}$ —threshold voltage of the driver device

- $V_{thl}$ —threshold voltage of the load device

$V_{th}(V_{BG})$ —threshold voltage as a function of back-gate bias; see Eq. (2-30).

$V_{th}(v)_{\tt out}$  —threshold voltage as a function of the output voltage

- V(y)—channel voltage as a function of the distance between source and chain

- W—channel width (perpendicular to current flow)

- $x_A$ —boundary between the accumulation region and the neutral bulk

$x_D$ —boundary between the depletion region and the neutral bulk

x, y, z-coordinates for the MOS structure; see Fig. 2-3.

To Michael

MOSFET in Circuit Design

# An Introduction to the World of the MOSFET

The metal-oxide semiconductor (MOS)\* field-effect transistor (FET) is a voltage-controlled device that exhibits an extremely high input resistance (in the range of  $10^{12}$  to  $10^{14} \Omega$ ). Unlike the junction FET, the MOS, with its insulated gate, maintains a high input resistance without regard to the magnitude or polarity of the input gate voltage. Even at elevated temperatures, the gate leakage is negligible—thus allowing the use of very large gate bias resistors in analog circuits or direct coupling in digital circuits.

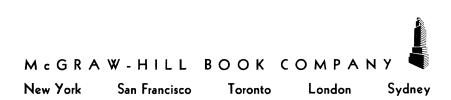

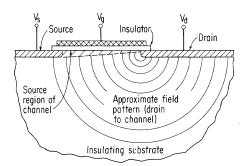

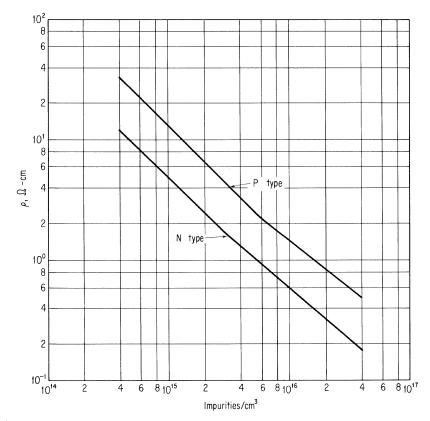

Construction of a P-channel MOS transistor is illustrated in the scale drawings of Fig. 1-1. Two highly doped P-type areas  $(10^{18}/\text{cm}^3 \text{ to } 10^{20}/\text{cm}^3 \text{ at the surface})$ are diffused into an N- type silicon substrate (1 to 10  $\Omega$ -cm). These two diffusions are referred to as the *source* and *drain* and are located in close proximity to each other (approximately 0.2 mil separation for a driver device and 1 to 2 mils separation for a load device). A thin (800 to 2,000 Å) insulating material, usually some type of silicon oxide, is placed over the surface of the silicon between the source and the drain, forming the gate dielectric material. Metal is evaporated over the surface of the slice, forming contacts, interconnecting leads, and the gate electrode.

Because of the conditions created by the interfacing, at the surface, of the silicon and oxide, usually all N-channel devices are initially on (at zero gate bias) and all P-channel devices are initially off. Since it is desirable to use an initially off device for switching or digital circuits, at present all commercial MOS inte-

<sup>\*</sup> Sometimes referred to as MIS, or metal-insulator semiconductor. Although other MOS structures exist, the MOS field-effect transistor dominates today's technology. In this book, the combination of letters "MOS" will refer to the transistor-type structure discussed in this chapter (see Fig. 1-1).

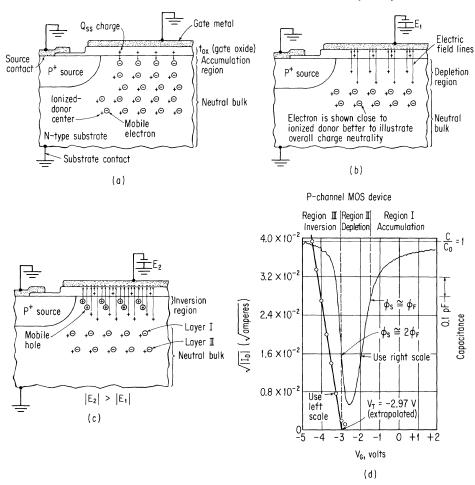

Fig. 1-1. Scale drawing of a typical MOS structure in cross section: (a)  $V_D = 0 V_j$  (b)  $V_D = -5 V_j$  (c)  $V_D = -15 V_j$  (d) change in scale showing the MOS in relation to the whole silicon wafer. The channel shown is exaggerated in the depth dimension. The source and substrate are both considered at ground potential.

grated circuits (ICs) are single-polarity P-channel units. For this reason, this book will deal almost exclusively with P-channel devices.

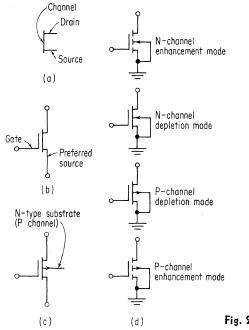

Figure 1-2 illustrates the symbol for the MOS (P-channel, enhancement-mode) that is used in this book. The source is the reference terminal, the gate is the control electrode, and the drain is the output of the device. These three leads are roughly analogous to the bipolar's emitter, base, and collector, respectively.

### 1-1 OPERATION OF THE MOS

With the drain and source grounded, the gate controls the charge in the *channel* —the region at the substrate surface between the source and the drain. A negative bias applied to the gate modifies conditions within the silicon. As the gate accumulates a negative charge, free electrons that are present in the N-type silicon are repelled, forming a depletion region. Once sufficient depletion has occurred, additional gate bias attracts positive mobile holes to the surface. When enough holes have accumulated in the channel area, the surface of the silicon changes from electron-dominated to hole-dominated material and is said to have *inverted*. Thus the situation now exists where the two P-diffused regions are connected together by a P-type inversion layer, or channel (hence the nomenclature "P-channel device"). A signal on the gate can modulate the number of carriers within the channel region, so that the gate, in effect, controls current flowing in the channel. For low values of drain voltage, the inversion layer extends across the entire channel, connecting the drain and source. Under this bias condition, drain current depends upon drain voltage as well as gate voltage. Notice that in Fig. 1-1a all the P regions, diffused or inverted, are isolated from the substrate material by a depletion layer.

For a constant gate voltage, an increase in the drain voltage alters the situation in the channel region. Drain current produces an IR drop along the channel. This drop is of such a polarity as to oppose the field within the oxide, produced by the gate bias. When the IR drop reaches a value to just reduce the field such that an inversion layer is no longer formed, the channel *pinches off* and the drain current tends to saturate at a constant value (independent of drain voltage). The device is said to be *in saturation*. As can be seen from Fig. 1-1b, the inversion layer is thickest at the source and decreases to zero thickness at the point of pinchoff.\* The voltage across the gate oxide just at the point of saturation is

\* Actually, the channel cannot go to zero thickness anywhere, for if it did, there would be no current, and there is, in fact, current when the device is in saturation. "Letting the channel go to zero" is an approximation that allows one to define pinchoff or threshold voltage.

### 6 MOSFET in Circuit Design

called the *pinchoff* or *threshold* voltage. Threshold voltage can be defined as the voltage across the gate oxide necessary to just produce inversion in the channel. Further increases in drain voltage drive the MOS harder into saturation. This is demonstrated in Fig. 1-1c, which shows an increase in the depletion regions associated with the drain and a reduction in channel length. Too much of an increase in drain voltage can cause the drain depletion region to *punch through* all the way to the source, resulting in unrestricted current flow if it is not limited by the external circuit.

### **1-2 CHARACTERISTIC CURVES**

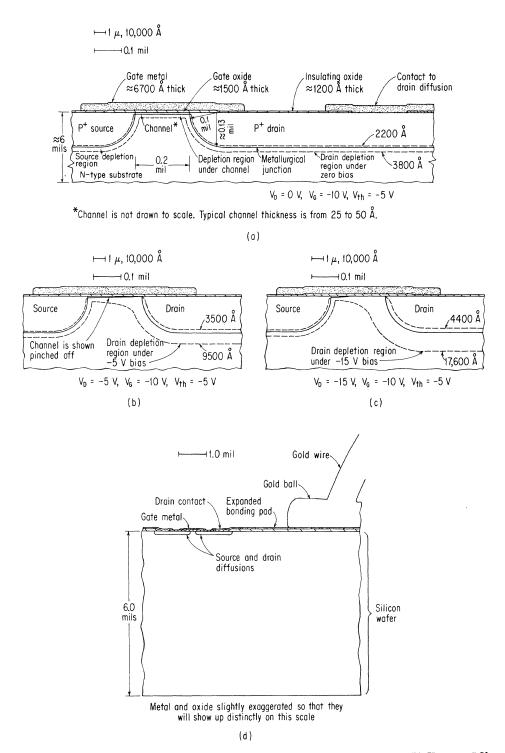

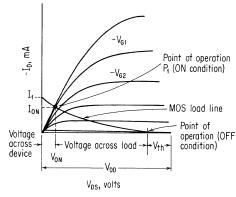

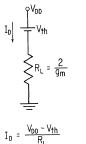

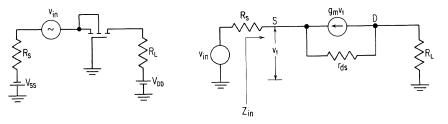

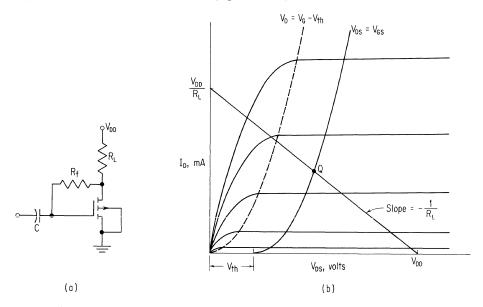

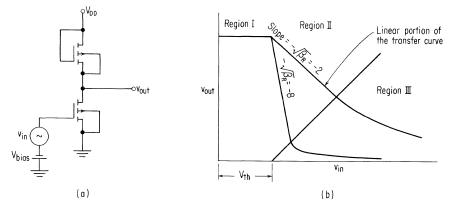

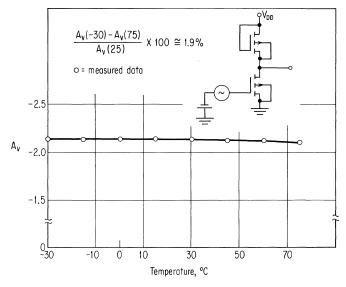

When the drain V-I characteristics are plotted for a family of gate voltages, the result is similar to the curves in Fig. 1-3. The important features of this figure are:

- 1. The control parameter is a voltage—as opposed to a current in the bipolar case. This implies high input resistance.

- 2. The input voltage and the output voltage and current all have the same sign, which allows for the convenient cascading of stages in digital circuits. A junction FET is an example of the opposite case.

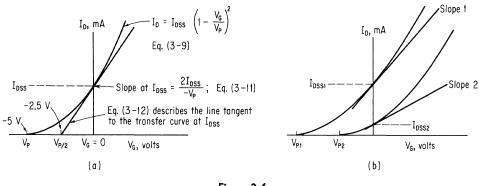

- 3. In Fig. 1-3a, -4 V must be applied to the gate before significant current flows. This characteristic is termed *enhancement-mode operation*. Figure 1-3b illustrates the *depletion-mode* case, where an initial current of  $-85 \,\mu\text{A}$  flows at zero gate bias.

- 4. The output-current variation for a given increment of gate voltage increases as the gate voltage is increased above the threshold voltage.

Fig. 1-3. MOS characteristic curves, P channel: (*a*) Enhancement-mode device. The three points on the curves represent the three operating points of Fig. 1-1. (*b*) Depletion-mode device.

It can be shown that the output current is proportional to the square of the input voltage. In fact, the MOS is often referred to as a square-law device.

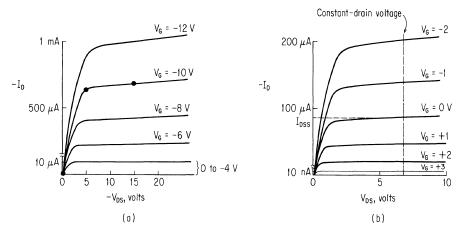

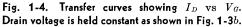

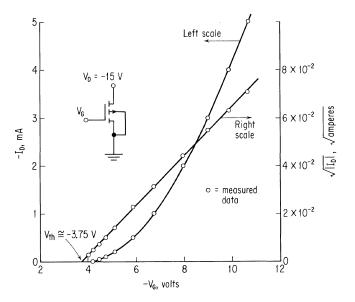

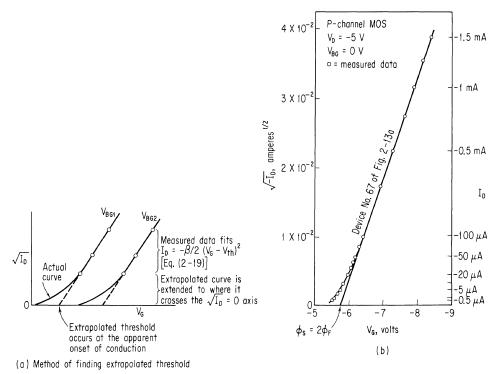

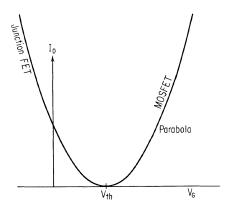

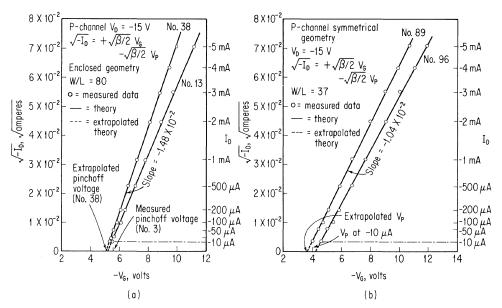

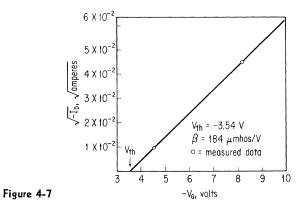

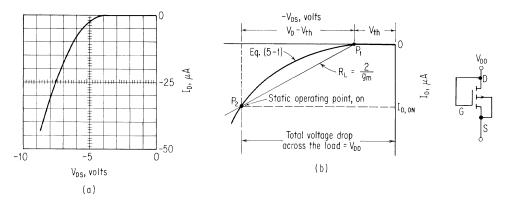

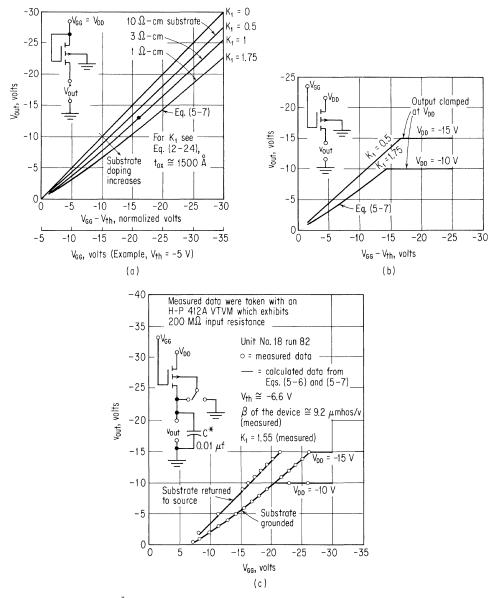

When a constant-drain-voltage line is graphed on the output characteristics, as in Fig. 1-3b, and the output-current-input-voltage relationship along this line is plotted, the resulting figure is known as a *transfer curve*. The transfer curves of Fig. 1-4 illustrate clearly enhancement-depletion-mode operation, threshold voltage, and the square-law behavior of the MOS. Actual data of drain current plotted as a function of input gate voltage are presented in Fig. 1-5. To illustrate

Fig. 1-5. Transfer curve illustrating the square-law characteristic of the MOS.

### 8 MOSFET in Circuit Design

Fig. 1-6. Characteristic breakdown curves showing the control that the gate voltage exerts over the breakdown voltage.

the parabolic nature of the transfer curve (in saturation), the data in Fig. 1-5 are also presented in the form of  $\sqrt{I_D}$  vs.  $V_G$ . The result is a straight-line plot. Extrapolating this plot back to where  $I_D = 0$  gives the threshold or pinchoff voltage\*—the turn-on voltage that is of interest to the circuit designer.

By increasing the magnitude of the drain voltage sufficiently, breakdown characteristics<sup>†</sup> similar to those in Fig. 1-6 can be seen. Observe that breakdown is a function of gate voltage. The magnitude of the breakdown voltage increases as the gate voltage is made more negative and decreases as the gate voltage is made more positive.

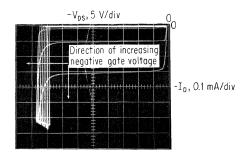

### **1-3 DIGITAL CIRCUITS**

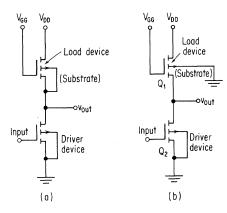

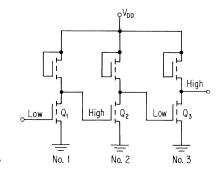

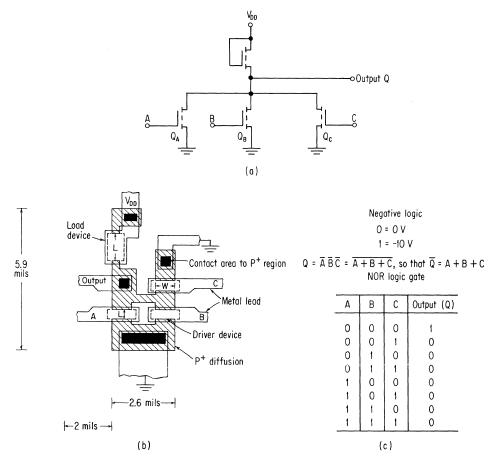

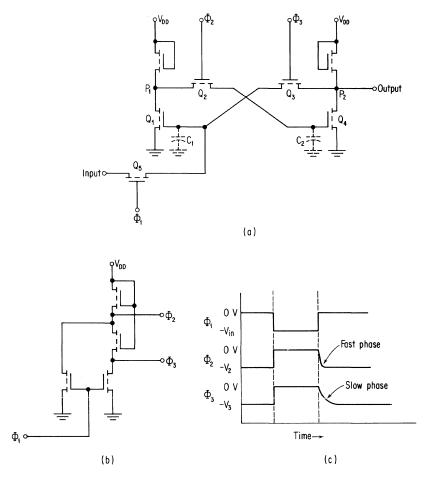

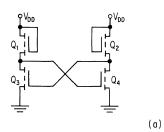

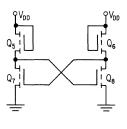

Usually, complex MOS ICs consist only of MOS transistors—no resistors, capacitors, or diodes—as functional elements. The basic building blocks of MOS circuitry are simple NAND and NOR gates such as those shown in Fig. 1-7. These gates, singly and in combination, are used to implement logic-design equa-

\* It has been suggested that the term "pinchoff" be restricted to depletion-mode devices and the term "threshold" be applied to enhancement devices. Pinchoff voltage is reminiscent of the junction FET (a depletion-mode device) and, as such, has some precedent established for its use. In common parlance, the pinchoff voltage of a depletion device is the gate voltage required to suppress the drain current from its initial value of  $I_{DSS}$  to approximately zero. This is shown on the characteristic curves of Fig. 1-3b as approximately +3 V.

With the advent of the P-channel enhancement device, the term "threshold" has become prevalent in field-effect terminology, the threshold being roughly that gate voltage necessary to initiate conduction.

A problem exists in that the origin of the transfer curve is given separate designations, depending upon whether it is to the left or to the right of  $V_{\mathcal{G}} = 0$ . (See Fig. 1-4.)

Since the same set of equations describes either enhancement-mode or depletion-mode operation (with only a change in sign for the turn-on voltage) and since the two types of devices operate in essentially the same way, the author will use  $V_P$  and  $V_{th}$  interchangeably. Because most MOS devices operate in the enhancement mode, the term "threshold" will dominate throughout this book. However, when it clarifies matters to use the term "pinchoff," it will certainly be used.

† Assuming that punchthrough does not exist.

Fig. 1-7. Basic logic gates: (a) NOR, (b) NAND.

tions, create flip-flops and memory elements, implement timing delays, and in general perform all the functions necessary for digital control.

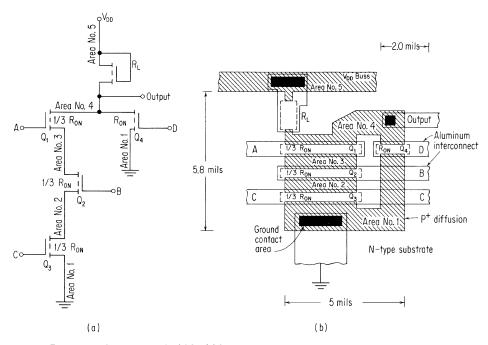

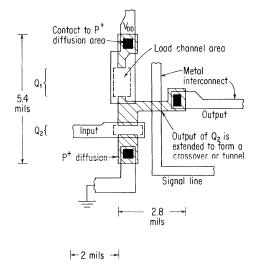

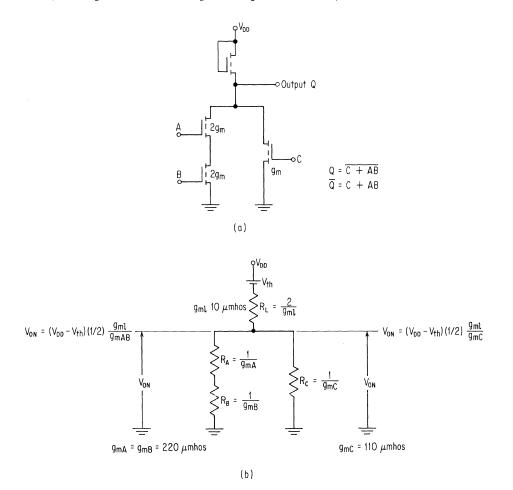

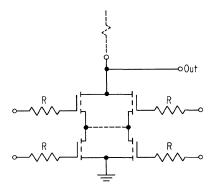

NOR-logic implementation is the best suited to MOS circuit design. More efficient use of space, as compared with NAND logic, can be cited as the reason. Figure 1-8 shows a combination NAND-NOR gate together with a diagrammatic layout. Because of the series arrangement,  $Q_1-Q_3$  must have three times the gain of  $Q_4$  in order to reduce the total ON resistance to the equivalent of a single

Fig. 1-8. Combination NAND-NOR gate with a physical layout (scale drawing).

parallel device. This leads to three times the area per device in the series arrangement shown.

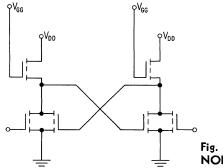

Combining NOR gates, as in Fig. 1-9, results in a cross-coupled flip-flop. Crosscoupling resistors are eliminated because of the extremely high input resistance. Speedup capacitors are also unnecessary. Low-gain MOS transistors are used as load resistors. Values as high as 200 k $\Omega$  are obtainable in this manner. The load gates can be returned either to the drain or to a separate supply. Reducing  $V_{DD}$  and returning the load gates to a separate supply result in lower power and higher-speed operation.

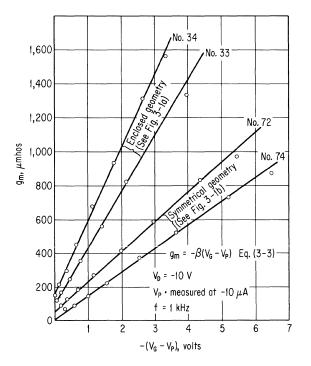

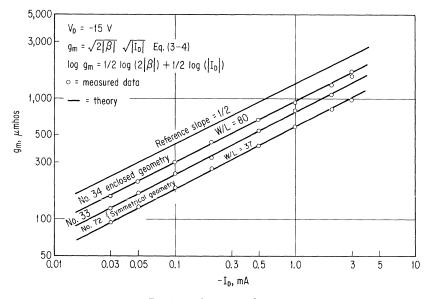

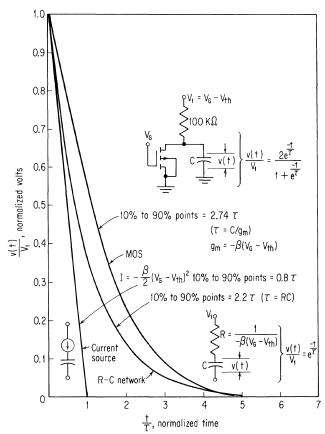

### 1-4 SPEED

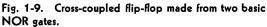

The speed limitation of MOS circuits is due entirely to stray circuit capacitance and the inability of the MOSFET to charge and discharge this capacitance. Intrinsic cutoff frequencies of MOS devices themselves are in the order of 1 GHz or higher. Currently, however, one rarely observes commercial MOS circuits in operation much above 2 MHz. (An exception is four-phase circuitry, which can operate close to 10 MHz.) In contrast, bipolar ICs often operate an order of magnitude or more faster then MOS circuits. The basic reason for the difference in speed is that the bipolar has a higher  $g_m$ , or gain per unit area, than does the MOS. A comparison of bipolar-MOS transconductance as a function of device current dramatically illustrates the gain superiority of the bipolar device (see Fig. 1-10). For typical integrated-device sizes, the bipolar has from 10 to 500 times the  $g_m$  of the MOS, depending upon the current level. The MOS gain can be increased by increasing its width; however, since capacitance as well as  $g_m$  is a linear function of area, capacitance also increases.

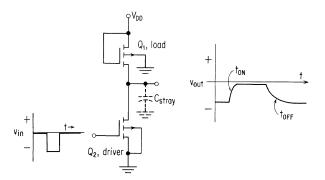

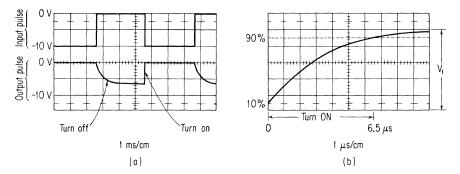

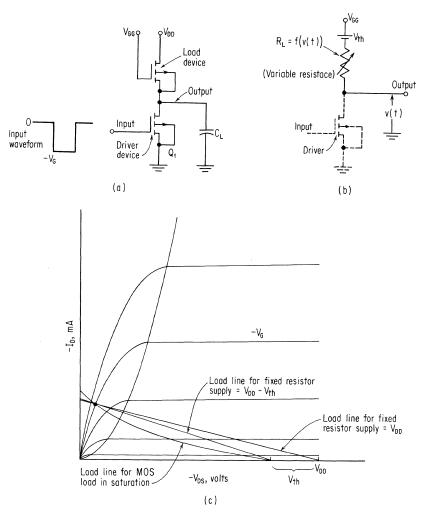

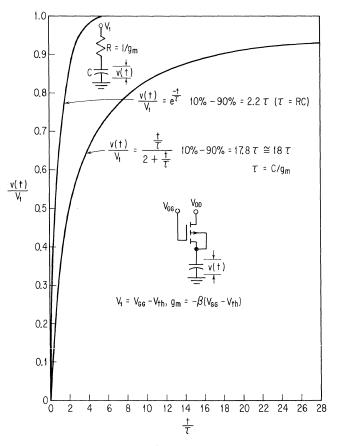

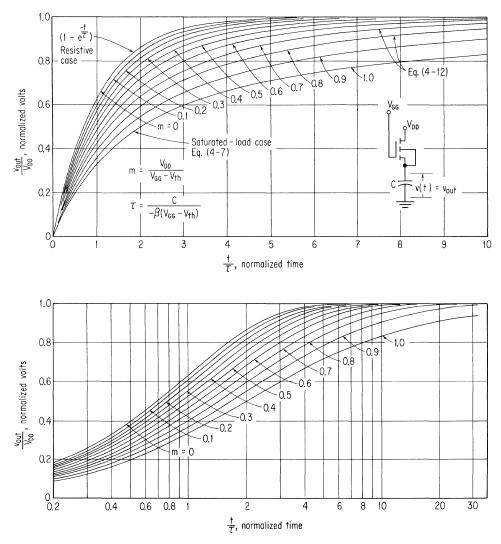

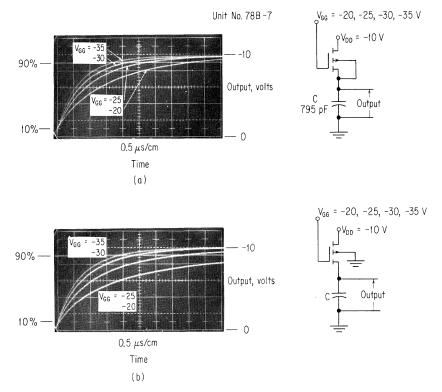

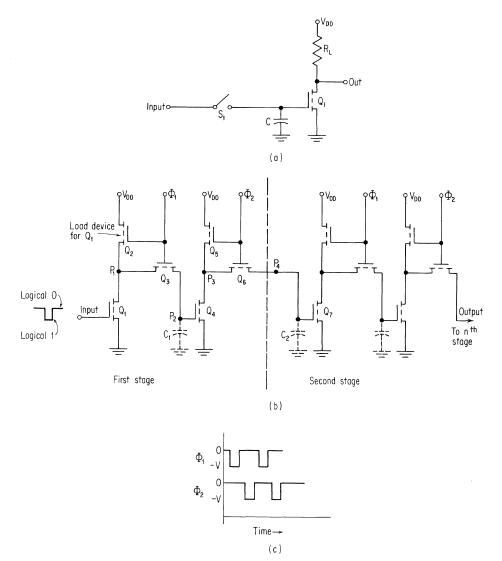

A typical switching waveform of an MOS inverter is shown in Fig. 1-11. The turn-on time, controlled by the driver device, is normally much shorter than the turn-off time of the load. In fact,  $t_{\rm ON}$  can generally be ignored in comparison with  $t_{\rm OFF}$ . Two factors contribute to the fact that  $t_{\rm OFF} \ge t_{\rm ON}$ . First, the resistance of the load device is typically a factor of 10 greater than that of the driver. This implies that for a given stray capacitance, the time constant for the load is 10

### An Introduction to the World of the MOSFET 11

Fig. 1-10. Comparison of bipolar and MOS transconductance.

Fig. 1-11. Basic inverter showing typical switching waveform.

### 12 MOSFET in Circuit Design

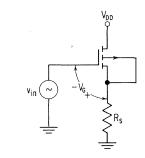

times greater than that for the driver. Second, the gate-to-source controlling bias of the driver remains constant at  $-v_{in}$  during switching. In the load case, the control voltage is modulated by the output (source) voltage in such a way as to reduce the gain of the load as the output increases.  $Q_1$  can be described as a nonlinear resistor whose value increases as the voltage across  $C_{stray}$  increases. These two factors taken together show that the load charging time is responsible for restricting MOS circuits to low-frequency operation. Fortunately, there are a number of things that can be done to reduce the deleterious transient effects of an MOS load.

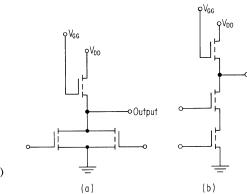

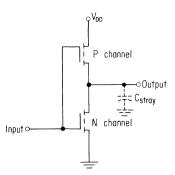

### **1-5 COMPLEMENTARY STRUCTURES**

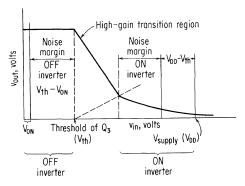

Complementary MOS technology has long been regarded as the ideal solution to many of the difficulties encountered in single-polarity MOS complex ICs. A complementary gate draws approximately zero standby power, making it useful for low-power applications, particularly large, active memories; switching speed is significantly lower than in the case of single polarity; circuit voltages swing the full supply voltage, making two supplies unnecessary; and finally, the output driving impedance is considerably lower than for the single-polarity case. To the circuit designer, these advantages make complementary circuits very attractive. However, complementary technology is not without severe drawbacks.

The major difficulty at the present time is the technology required to fabricate similar complementary devices. N- and P-channel devices inherently have different characteristics when fabricated together; i.e., N-channel devices are depletion mode, while P-channel devices are enhancement mode. The added processing, such as additional diffusions and photomasking steps, necessary to achieve monolithic complementary circuits increases the cost and reduces the yield—undesirable factors in terms of both manufacturer and customer. Additional drawbacks are:

- 1. Because both polarity devices exist side by side, some form of isolation (not necessary in single-polarity circuits) must be used, resulting in a significant increase in area per function.

- 2. The number of devices required to implement a given function is greater than in the single-polarity case.

A complementary inverter is shown in Fig. 1-12. Both devices are of the enhancement type. When the input is low, the N-channel device has its gate returned to the source and is off. The gate of the P-channel device, however, is returned to the most negative potential in the circuit (ground) and is thus turned on. Under these conditions, the output goes high and is inverted with respect to the input. When the input goes high, the N-channel device is turned on and the P-channel device is off, resulting in a low output. Notice that in either case, one device is on (presenting a low driving-point impedance to  $C_{\rm stray}$ ) and the other device is off (limiting the static current drain, and thus the power, to the leakage value).

### Fig. 1-12. Basic complementary inverter.

### 1-6 THE FUTURE OF MOS TECHNOLOGY\*

For the MOS to have a future, it must be able to offer an advantage over existing bipolar ICs. In general, the advantage will not be in performance. Bipolars, because of their low threshold voltage, high transconductance, and low saturation voltage, will outperform MOS circuits when compared on a speedpower figure-of-merit basis. The advantage offered by MOS technology will be lower cost. This will be achieved through the ability of MOS technology to integrate more functions on a given chip and to give consistently higher processing yields than today's technology allows.

1. Discrete Devices and "Discrete Gates." The demand for discrete MOS devices will be small when compared with that for ICs. Discretes will be used in (1) analog switches, because of the theoretically zero offset voltage; (2) high-frequency amplification, where noise is low and the square-law characteristic is desirable; and (3) certain isolated cases, such as the interfacing between MOS-bipolar circuits or where the unique property of the device (i.e., the extremely high input resistance) can be used to advantage.

Along the same line of reasoning, there will be virtually no demand for packaged single-gate functions—the reason being that the performance would be so poor and the cost so close to the cost of present bipolar circuits that no advantage for using MOS would exist.

2. Integrated Circuits. The volume MOS market will be in the area of large, complex ICs operating at slow-to-medium speeds. These ICs will be complete functions representing small systems or subsystems. Integration of a complete function on a chip allows all interconnections to be made on that chip. Thus only the signal and power leads need be brought out of the package. As the number of leads decreases, the package cost decreases. The cost of testing complex ICs, which can make up a very substantial portion of the total cost, is largely dependent upon the number of signal pins in the package. As the number of pins increases, so does the time that is required to test all combinations and permutations. The

\* All comments in this section apply to single-polarity P-channel ICs, except comment No. 6, which applies to the complementary technology.

### 14 MOSFET in Circuit Design

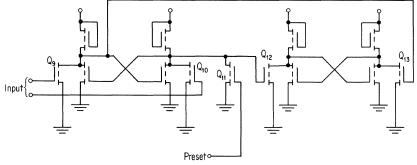

ideal situation is the case of a large, complex IC having one input and one output. Here the signal is fed into the circuit, operated upon in some complex manner, modified, and then presented at the output. The serial shift register (SR) is the classical—and most illustrated—example. Here a pulse is shifted into the register, stored for a predetermined time (milliseconds, minutes, even days), and then, upon command, presented at the output, ready for use. Each bit in the SR string drives an identical bit, so that internal wiring and layout problems, capacitance, large output buffers, and operating tests are kept to a minimum.

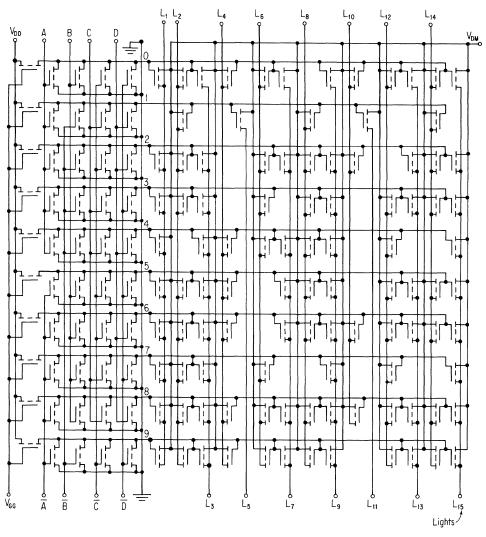

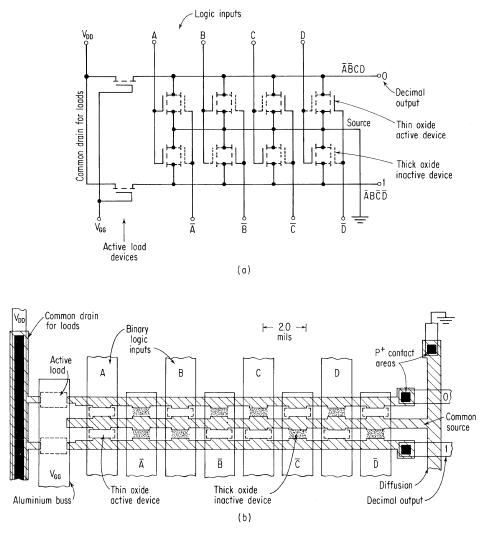

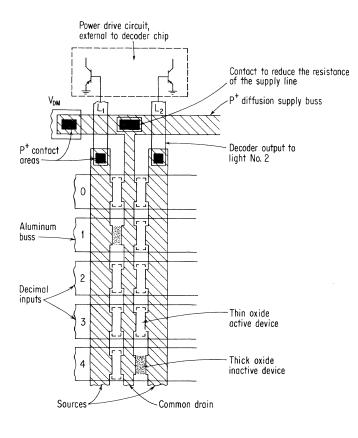

The SR, although an extremely useful function, represents the extreme case for a minimum number of leads. More typically, a complex IC has a number of input and output leads. An example is the binary-to-decimal decoder illustrated in Fig. 5-25. Here the circuit requires 8 input and 15 output signal leads in addition to the power leads.

**3.** Custom Design. As integrated functions on a single chip become larger and more complex, they also become more specialized and therefore more restricted to a given application. Hence custom-designed circuits will dominate the MOS IC market. It seems to the author that it is possible for system companies (both large and small) to do their own MOS IC design. This is definitely *not* the case in bipolar IC design. One major difference between MOS and bipolar complex IC technology is thus emphasized—the ease with which an idea is reduced to practice is more than an order of magnitude greater in the MOS world. The customer will do more of the design himself. A notable exception will be SRs that are sold "by the foot."

The question of who will do MOS design in the future has been given a very colorful answer by Seely and Wanlass in the following quote:<sup>1,\*</sup>

The above considerations have prompted a chemist to remark that he could much more readily design an MOS circuit than he could a conventional transistor circuit to perform the same function. The same sort of thing holds true when it comes to a comparison of MOS and bipolar integrated-circuit design. Given the proper design rules, a good digital designer can learn to engineer his own circuits only after a few hours instruction. This alone almost guarantees the future of MOS, since it puts the burden of design creativity back in the lap of the practicing engineer, where it belongs. In effect, design engineers will be given a new dimension in which to exercise their creativity.

**4.** Complex Integrated-circuit vs. Array Technology.<sup>†</sup> In general, to gain the greatest advantage from MOS technology, the concept of the *complex IC* will be used. A basic tenet of this concept is the design, layout, and fabrication of the complete function in the smallest possible area. The function is specialized to do only one job, which it does efficiently. The unit is handled, tested, and packaged as a

\* Superscript numbers indicate works listed in the Bibliography at the end of the chapter.

† See Ref. 2 for an expanded discussion.

complete function. For the function to work, 100 percent of the components within the function must work. If the function does not work, it is discarded.

On the other side of the fence is *array* technology. Here the idea is to fabricate a large number of basic building blocks (such as simple gates), test each block, catalog the working units, and interconnect these units (bypassing the malfunctioning ones) into complete functional systems or subsystems. Until now, the main effort of array technology has been directed toward bipolar circuits (with a few notable exceptions). Now, this does *not* mean that the MOS will not be used in array technology. It *does* mean that the basic unit cell will be much larger (functionally) than in the present bipolar case. (Here the unit cell might be a simple four-input gate.) Consider an example where a customer requires 500 bits of serial SR. Strings of 50 bits each (300 transistors) might be considered as the basic building block; i.e., compound units of 50 bits are probed as a single unit. Ten working strings would then be connected serially (in a separate masking step) for the required total of 500 bits.

5. Toward Faster Circuits. Because the speed of the MOS is close to 100 times below its theoretical limit, the next few years will show more dramatic improvements in speed in MOS technology than in bipolar technology. This is simply a way of saying that it will be easier to achieve an order-of-magnitude increase in speed in the MOS area than in the bipolar area. Significant speed improvements will come about in the following four areas: (1) circuit innovation, i.e., "tricks" the circuit designer can do to increase performance while not actually changing the process—such as returning the load gates to separate supplies or multiphase clocking schemes; (2) new materials, such as GaAs, which exhibit a higher mobility than silicon; (3) new and improved gate dielectrics that are thinner and have a higher dielectric constant than the currently used silicon oxide; and (4) new technologies, such as dielectric isolation or silicon on sapphire to reduce the stray capacitance or a method to control and increase the surface mobility of currently used materials.

6. Complementary MOS. Complementary ICs will not have the major impact on the market that single-polarity P-channel circuits have had or will have. Because of the sacrifice necessary in the yield (more processing steps), complementary circuits will be higher-cost items than single-polarity circuits. Also, with the increased area that is necessary per function, any size or yield advantage over the bipolar is greatly reduced. Complementary circuitry will thus be forced to compete with bipolars more in the area of performance than in cost. Complementary MOS technology will make inroads into low-power low-duty-cycle digital functions such as large, active memory applications, where power must be conserved. One can predict that the complementary MOS will dominate the highperformance, high-cost MOS market, while the single-polarity P-channel MOS will be sought after by the larger, general-purpose, low-cost market.

7. Advances in MOS-device Technology. So versatile is the MOSFET that numerous new devices, circuits, and techniques will emerge from today's technology. While the MOS is normally thought of as a low-gain, small-signal device,

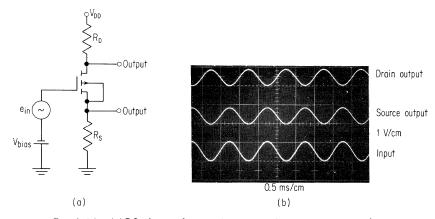

(a)

practical power devices—capable of 50 to 100 W—have already been demonstrated. Exotic devices such as MOS Thyristors (SCR), transducers, negativeresistance elements, and MOS tunneling devices will begin to appear on the scene.

The wide variety of MOS devices and the many combinations that are possible on a single chip certainly indicate the versatility of this new technology. Linear and digital devices fabricated together will enable functions such as analog-todigital conversion to be carried out on single monolithic chips. Small signal and power devices will routinely be fabricated together to form complete amplifiers. Combinations of MOS and bipolar technologies will offer improved performance by utilizing the outstanding features of each type of device. Examples of useful combinations are (1) very high MOS resistance values in bipolar circuits, (2) bipolar output buffers in complex MOS ICs, and (3) M-O-S structures in conjunction with a planar bipolar device for improved gain, stability, and breakdown properties of the bipolar device.

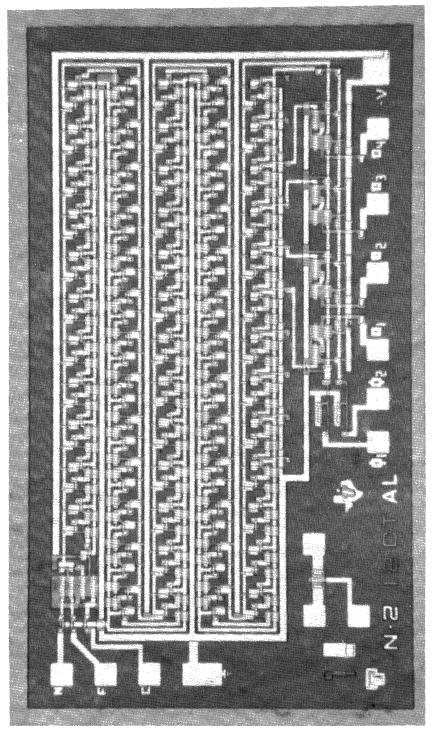

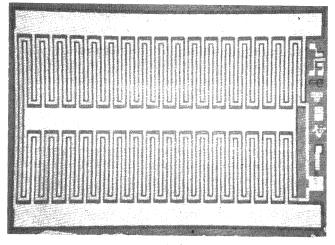

8. Examples of Current MOS Device and Circuit Technology. Figures 1-13 and 1-14 illustrate what is currently available in the area of sophisticated MOS circuitry and devices. Figure 1-13 is a photograph of a complex MOS integrated circuit. This unit is a 64-bit dynamic SR requiring two clocks for operation. The SR, consisting of 413 devices, is a single-input serial register with four separate outputs, all on a silicon bar  $60 \times 100$  mils.

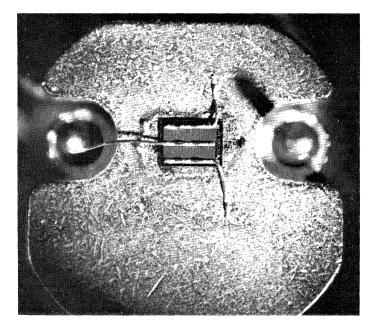

A large-geometry MOS power transistor is shown in Fig. 1-14, both in chip form and mounted on a power header. The device exhibits a typical transconductance of 1,000,000  $\mu$ mhos and requires a chip 90  $\times$  120 mils. Frequency characteristics are excellent as illustrated by the fact that the device switches 1 A < 20 ns. This MOSFET is capable of switching 1 to 3 A at 35 to 45 V.

**9.** In Summary. MOS complex ICs will make up a significant portion of the IC market within the next few years. The MOS will gain in volume not so much by replacing present bipolar ICs but by expanding the market. Areas will open up that have previously been closed to electronics for economic reasons. Applications, such as digital filters and digital differential analyzers, requiring vast quantities of transistors will now become economically feasible. The MOS will be able to make dramatic inroads into areas that have been dominated by mechanical methods; a prime example is the small desk calculator.

#### BIBLIOGRAPHY

- 1. Seely, J. L., and F. M. Wanlass, contributors: *EEE* Specifying Guide: MOS Integrated Circuits, *EEE*, pp. 60–70, May, 1966.

- Petritz, R. L.: Large Scale Integration Technology, Trans. Met. Soc. AIME, vol. 236, pp. 235-249, March, 1966.

### **GENERAL REFERENCES**

Bogert, H. Z.: Metal Oxide Silicon Integrated Circuits, SCP and Solid State Technol., pp. 30-35, March, 1966.

- Christiansen, D.: EEE Specifying Guide: MOS Integrated Circuits, *EEE*, pp. 60–70, May, 1966.

- Editorial Staff: Planning To Use MOS Arrays? *Electron. Design*, pp. 42–45, Jan. 18, 1966.

- Field, R. K.: MOS Arrays Diffuse into Commercial Market, *Electron. Design*, pp. 22–26, Jan. 18, 1966.

- Lohman, R. D.: Applications of MOSFET's in Microelectronics, SCP and Solid State Technol., pp. 23-29, March, 1966.

Seely, J. L.: MOS Arrays Have More on a Chip, *Electron. Design*, pp. 90–93, Jan. 4, 1966.

- Thornton, C. G.: New Trends in Microelectronics Fabrication Technology 1965–1966, Part I, SCP and Solid State Technol., pp. 42–49, March, 1966.

- Warner, R. M.: A Comparison of MOS and Bipolar Integrated Circuits, *NEREM Record*, IEEE Catalog no. F-70, pp. 68-69, November, 1966.

- White, M. H., and J. R. Cricchi: Complementary MOS Transistors, *Solid-state Electron.*, vol. 9, pp. 991–1008, October, 1966.

## 2

### Theory of Operation

Because of the nature of this book, a somewhat simplified, first-order-approximation theory will suffice rather than a long and laborious "complete" analysis. A number of approximations will be made which greatly simplify the model of the MOS field effect. This approach will facilitate the understanding of the basic principles of the MOS device. When additional effects, not predicted by the simple theory, are considered, they are discussed separately in order not to make the analysis too large and unwieldy. One can fast become bogged down in excessive algebraic manipulations and lose sight of the real goal of this chapter—an understanding of the workings of the MOS. For those interested in a more comprehensive study of the MOS structure, the author refers the reader to an excellent paper by Ihantola and Moll.<sup>1,\*</sup>

The following analysis is divided into two sections: The first gives a qualitative description of the internal workings of the MOS; the second concentrates on a quantitative discussion which, in due course, derives the characteristic equations describing the MOS.

Approximations used to describe the MOS model are as follows:

- 1. Mobility of current carriers in the channel is constant.

- 2. The variation of the channel thickness is small along the length of the channel.

- 3. The thickness of the dielectric over the channel region is assumed to be much greater than the channel thickness.

- 4. Parasitic resistances (such as in the source) are assumed to be so small as to be negligible.

- 5. The channel is completely shielded from the drain, so no drain-to-channel feedback exists.

- 6. Doping of the substrate is uniform and nondegenerate.

\* Superscript numbers indicate works listed in the Bibliography at the end of the chapter.

- 7. The drain current consists only of channel current. Leakage currents are neglected.

- 8. The gate dielectric is considered to be a perfect insulator.

- 9. Throughout this book, extrinsic conditions which affect the conduction properties—such as oxide traps, silicon surface states, interface energy states, ionic centers within the oxide, and work-function differences—will be lumped together into a single effective charge term,  $Q_{SS}$ . Furthermore,  $Q_{SS}$  is assumed to be constant and located at the silicon-oxide interface.

#### 2-1 QUALITATIVE ANALYSIS\*

Even though the following analysis refers specifically to a P-channel MOS on an N-type substrate (for convenience), the resulting equations are applicable to both N-channel and P-channel devices. There are three distinct conditions or regions occurring within the semiconductor, at the surface, that are important to MOS operation. They are the accumulation, depletion, and inversion regions and are controlled by the external bias on the gate electrode. Generally, for an oxide-passivated surface, surface states or energy states at the silicon-oxide interface act as ionized donors<sup>3</sup> whose effect is the same as a positive applied gate voltage.

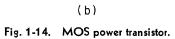

Figure 2-1a shows the MOS structure used in this discussion. Drain-to-source voltage is assumed to be so small as to be negligible. The energy-band diagram of a P-channel device under zero applied gate voltage is shown in Fig. 2-1b. Here and in the following band diagrams, the intrinsic level  $(P = N = n_i)$  is designated as  $E_i$  and is assumed to be halfway between the conduction-band energy  $E_c$  and the valence-band energy  $E_v$ . Because of the positive surface-state charge, negative electrons from within the N-type bulk are attracted to and accumulate at the surface (x = 0). Accumulation results in a downward bending of the conduction and valence bands. The closer  $E_c$  is bent toward the Fermi level, which is set by the substrate doping, the heavier the surface concentration of electrons becomes. Figure 2-1c illustrates the charge-density distribution. The positive charge per unit surface area  $(Q_{SS})$  must be exactly balanced out by the negative charge accumulated near the silicon surface  $(Q_A)$ . (Charge distributions are approximated by  $\delta$  functions.) If a small positive bias is now applied to the gate, additional band bending and accumulation result. Again, the total positive charge must equal the total negative charge so as to maintain charge neutrality  $(Q_G + Q_{SS} + Q_A = 0; \text{ see Fig. 2-1}d).$

If a negative voltage is applied to the gate such that it just counters the effect of  $Q_{SS}$ , then no bending of the bands exists, a condition which is known as the *flat-band case* (Fig. 2-1e and f) ( $\phi_s = 0$ ). Further application of a negative gate voltage repels from the channel region the mobile electrons associated with donor centers, causing a depletion region to form. The band diagram and charge picture

<sup>\*</sup> This discussion follows, in part, that presented by Grove et al.<sup>2</sup>

Fig. 2-1. Energy-band and charge-distribution diagrams describing MOS operation: (a) Structure of the device used in this figure. (b) Energy-band diagram for the accumulation condition due to surface states. (c) Charge-density distribution due to surface states. (d) Charge-density distribution due to surface states in addition to positive applied gate voltage. (e) Energy-band diagram for the flat-band case. (f) Charge-density distribution for the flat-band case. (g) Energy-band diagram for the depletion case. (h) Charge-density distribution for the depletion case. (j) Charge-density distribution for the depletion case. (j) Charge-density distribution for the inversion case. (j) Charge-density distribution for the inversion case.

for this case are shown in Fig. 2-1g and h. When an electron is removed from its donor atom, the ionized atom is left with a net positive charge. Thus the charge in the depletion region is shown as a positive charge,  $Q_D$ , in Fig. 2-1h. When the intrinsic Fermi level  $E_i$  is bent just enough to intersect the Fermi level at x = 0, the surface has gone from its initial N-type concentration to intrinsic (where P = N). ( $\phi_s$  is now equal to  $\phi_F$ .) Additional negative gate bias does not extend the depletion region so much as it induces positive mobile holes at the It is important to note that depletion-region charge and mobile-surface surface. (channel) charge are of the same polarity (positive) and thus their effects add. The sum of these two charge regions must just balance the net charge stored in the oxide  $(Q_{ss})$  and on the gate  $(Q_g)$  so as to maintain an electrically neutral system. As the gate bias is increased in the negative direction, a larger and larger percentage of the charge within the semiconductor is contributed by the mobile holes. (See Fig. 2-1i and j.)

Until  $E_i = E_F$ , mobile electrons still outnumber mobile holes. Beyond this point, electrons are suppressed below the intrinsic level while holes in the channel region are raised above this level. As will be seen later, conduction between the P<sup>+</sup>-type source and drain (by P-type carriers) does not become significant until holes dominate and provide the conducting path. One can label the onset of conduction (or the apparent onset of conduction, as will be discussed later; see Fig. 2-14) as the threshold voltage  $V_{th}$  and define it as where the surface potential goes through intrinsic to a value of  $\phi_s = 2\phi_F$ . The threshold voltage is thus the gate voltage that produces a gate charge which just counterbalances the charge contained in surface states and in a depletion region that supports a voltage of  $2\phi_F$ . Further increases in gate voltage past  $V_{th}$  result in an increase in the number of holes, thus enhancing conduction between the source and drain.

It must be kept in mind that the start of actual conduction is not an abrupt process, in which the channel is completely depleted of carriers at a given gate voltage  $V_G$  and then immediately acquires a finite inversion layer at a small increase in the magnitude of  $V_G$ . The minority and majority carriers within the channel are increasing and decreasing continuously and at a finite rate for changes in the gate voltage. Goldberg described the situation very nicely when he said, "The transition from depletion to inversion is a continuous process, and one must be aware of the fact that the minority carrier concentration increases as the majority carrier concentration decreases and that carriers are always present."\*

Examination of the gate capacitance as a function of the gate voltage can yield additional insight into the physical operation of the MOS. Starting with the accumulation condition, Fig. 2-2a shows that the metal gate and the accumulation layer at the silicon surface form a simple parallel-plate capacitor with a separation distance of  $t_{ox}$  and a normalized value of  $C/C_o = 1$ . Capacitance is measured at the gate, with the source, drain, and substrate grounded. As negative gate bias is applied, the depletion region that forms tends to separate the two plates

\* From Ref. 8, p. 594.

Fig. 2-2. Diagrams illustrating the position of charge under the gate as a function of bias: (a) accumulation case; (b) depletion case; (c) inversion case; (d) C vs.  $V_G$  plot of MOS gate showing the three characteristic regions together with a plot of  $\sqrt{|I_D|}$  vs.  $V_G$ .

of the capacitor and reduce the capacitance (see Fig. 2-2b). (The two plates are now the gate electrode and the bulk silicon at the edge of the depletion region. Separation is  $t_{ox} + x_D$ .) Further application of a negative gate bias attracts holes to the surface (inversion), which in effect decreases the distance separating the two plates, thus increasing capacitance.

A typical C-V plot is shown in Fig. 2-2d. Region I corresponds to the accumulation region, region II to the depletion region, and region III to the inversion region. Notice how the capacitance decreases during the transition from accumulation through depletion as the space-charge region forms. At  $\phi_s > 2\phi_F$ , the

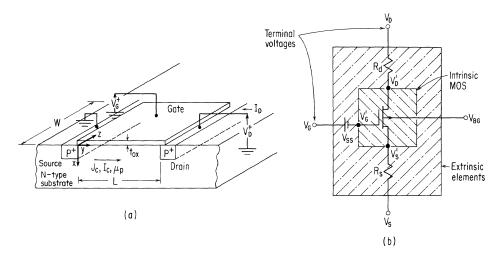

Fig. 2-3. (a) Diagrammatic sketch of an MOS showing dimensions and directions used for analysis. (b) Diagram illustrating the intrinsic and extrinsic elements of an MOS.

charge in the depletion region becomes insignificant compared with the total charge as inversion sets in. The rapid increase in capacitance illustrates how sensitive a function the accumulation layer is to applied gate voltage. Once a significant accumulation layer has formed, the capacitance becomes fixed at approximately  $C/C_o = 1$  and is shown to be independent of further gate voltage increases.\*

In addition to the C vs.  $V_G$  plot, Fig. 2-2d shows the plot of  $\sqrt{|I_D|}$  vs.  $V_G$ . As will be demonstrated later, the MOS is a square-law device that exhibits a straight-line relationship when the square root of current is plotted as a function of the gate voltage. Extrapolation of this straight-line curve to the point where  $I_D = 0$  defines the threshold voltage, or the apparent onset of conduction. In this case,  $V_{th} = -2.97$  V. Projecting upward from  $V_{th}$  to the capacitance plot shows where the surface potential reaches a value of  $2\phi_F$ .

#### 2-2 QUANTITATIVE ANALYSIS†

**1. Triode Region.** Figure 2-3*a* shows an idealized device together with the coordinate system that is used in the analysis. A brief outline of the "plan of attack" used to derive the device equations is as follows:

1. The channel-current density is integrated over a cross section of the channel (W dx) to obtain the current.

\* For a further discussion of C vs. V, see Refs. 2, 5, and 6.

† This discussion follows, in part, that presented by Sah.<sup>3</sup>

- 2. Channel current is now a function of the charge in the channel.

- 3. This charge is found by summing all the system charge to zero.

- 4. Charge is now related to the gate voltage by the use of Gauss' law.

- 5. The expression for channel current can now be integrated over the length L of the channel.

- 6. Channel current can now be equated to the external terminal current.

Channel current can be written as

$$I_C = W \int J_C(x,y) \, dx \tag{2-1}$$

where W indicates channel width in the z direction. W is perpendicular to the direction of current flow.

From Ohm's law,

$$J_C(x,y) = \sigma(x)E_y = q\mu_p p(x)E_y$$

(2-2)

so that  $I_C = W \int q \mu_p E_y p(x) dx$ , or

$$I_C = W q \mu_p E_y \int p(x) \, dx \tag{2-3}$$

$[\mu_p \text{ is constant and independent of } x \text{ (approximation No. 1). } \mu_p \text{ is a positive number, while } \mu_n \text{ is negative.}]$

Now  $E_y = -(dV/dy)$ , so that

$$-I_C = W\mu_p \frac{dV}{dy} q \int p(x) dx \qquad (2-4)$$

where  $q \int p(x) dx$  represents the mobile charge per unit area in the channel. The problem is now reduced to evaluating  $q \int p(x) dx$ . Since the total MOS-system charge must be zero for a neutral system, the sum of all the charge must equal zero:

$$Q_G + Q_{SS} + Q_C + Q_D = 0 (2-5)$$

where  $Q_G + Q_{SS}$  represents all the charge outside of the semiconductor material proper and  $Q_C + Q_D$  represents all the charge within the semiconductor material. The channel charge is thus

$$-Q_C = Q_G + Q_{SS} + Q_D (2-6)$$

The charge induced by the gate can be related to the gate voltage by Gauss' law, which states

$$\oint E_{\rm ox} \, dS = \frac{Q_{\rm total}}{\epsilon_{\rm ox}} \tag{2-7}$$

This says that integrating the E field over a given surface (in this case, the gate or channel area) gives the charge under the area, divided by the dielectric constant (gate material in this case). In Eq. (2-7),  $E_{ox}$  is considered constant at a given distance y (approximation No. 3) and dS integrates to the differential gate area

W dy, so that the relation between E and channel charge is

$$\epsilon_{\rm ox} E_{\rm ox} W \, dy = Q_{\rm total} \tag{2-8}$$

$E_{ox}$  is defined as

$$-\frac{dV_{ox}}{dx}$$

where  $dV_{ox}$  = voltage across the oxide dx = oxide thickness

Now

$$-\frac{dV_{\rm ox}}{dx}\cong-\frac{\Delta V_{\rm ox}}{\Delta x}$$

where  $\Delta x = +t_{ox}$  $\Delta V_{ox} = -[V_G - V(y)]$

So that

$$-\frac{dV_{\text{ox}}}{dx} = +\frac{V_G - V(y)}{t_{\text{ox}}}$$

(2-9)

(The voltage across the oxide is simply the gate voltage minus the voltage on the channel. Channel voltage will be a function of the distance in the y direction, ranging from  $V_D$  at the drain to zero volts at the source.)

Inserting Eq. (2-9) into Eq. (2-8) and letting  $\epsilon_{ox}/t_{ox} = C$  (capacitance per unit area) yield

$$Q_G = [V_G - V(y)]C (2-10)$$

Equation (2-10) relates the product of the gate capacitance per unit area and the voltage across the oxide to the charge per unit area under the gate.

The gate charge found in Eq. (2-10) is substituted into Eq. (2-6):

$$Q_{C} = -[V_{G} - V(y)]C - (Q_{SS} + Q_{D})$$

(2-11)

Equation (2-11) is a mathematical statement of the amount of mobile charge contained in the channel per unit area. Keep in mind that this is the charge that allows conduction between the source and the drain.  $Q_C$  will be enhanced by the gate voltage  $V_G$ , decreased by the channel voltage created by the drain supply, V(y), decreased by the charge stored in the depletion region beneath the channel,  $Q_D$ , and either increased or decreased by  $Q_{SS}$ , depending upon its polarity. Later it will be interesting to investigate the condition required to cause the channel charge to go to zero.

Note that  $Q_c = q \int p(x) dx$ , which is the desired quantity of Eq. (2-4). Substituting Eq. (2-11) into Eq. (2-4) yields

$$-I_{C} = W_{\mu_{p}} \frac{dV}{dy} \left\{ -[V_{G} - V(y)]C - (Q_{SS} + Q_{D}) \right\}$$

(2-12)

Factoring out C,

$$I_C \, dy = W \mu_p C \, dV \left\{ [V_G - V(y)] + \frac{Q_{SS} + Q_D}{C} \right\}$$

(2-13)

Equation (2-13) can now be integrated between 0 and L for the length and between 0 and  $V_D$  for the voltage:

$$I_{C} \int_{0}^{L} dy = W \mu_{p} C \left[ V_{G} \int_{0}^{V_{D}} dV - \int_{0}^{V_{D}} V(y) \, dV + \frac{Q_{SS} + Q_{D}}{C} \int_{0}^{V_{D}} dV \right]$$

$$I_{C} L = W \mu_{p} C \left( V_{G} V_{D} - \frac{1}{2} V_{D}^{2} + \frac{Q_{SS} + Q_{D}}{C} V_{D} \right)$$

Now  $C = C_o/WL$  and

$$I_{C} = -\frac{C_{o}\mu_{p}}{L^{2}} \left[ -(V_{G} - V_{th})V_{D} + \frac{1}{2}V_{D}^{2} \right]$$

(2-14)

where  $V_{th} = -(Q_{SS} + Q_D)/C$ . (The threshold-voltage term will be discussed in more detail in Sec. 2-3.)

Equation (2-14) can also be written as

$$I_{C} = -\beta [-(V_{G} - V_{th})V_{D} + \frac{1}{2}V_{D}^{2}]$$

(2-15)

where  $\beta = \frac{W \epsilon_{ox} \mu_p}{L t_{ox}}$  (Because of the sign convention for  $\mu$ ,  $\beta_p$  is positive and

$\beta_n$  is negative.) Now the channel current of Eq. (2-15) is related to the drain current of Fig. 2-3*a* by the equation  $I_C + I_D = 0$  or  $I_C = -I_D$ . The final form of the equation for the drain current of a device in the triode region can be written as

$$I_D = -\beta [(V_G - V_{th})V_D - \frac{1}{2}V_D^2]$$

(2-16)

(See Table 2-1 for a summary of MOS-device equations.)

\* Equation (2-16) assumes no drain or source resistance (approximation No. 4). At this point, it is easy to include the effects of a given parasitic resistance  $R_d$  and  $R_s$ . These extrinsic elements are illustrated in Fig. 2-3b, where they are shown to be "outside" of the intrinsic MOS device. Equation (2-13) is integrated from 0 to L on the left-hand side and from  $V'_s$  to  $V'_D$  on the right-hand side. This integration yields

$$I_D = -\beta [(V_G - V_{th})(V'_D - V'_S) - \frac{1}{2}(V'_D - V'_S)]$$

(2-16a)

which represents the triode-region drain current. Equation (2-16a) can be related to the terminal voltages by including the two additional equations

$$V'_D = V_D - I_D R_d \qquad V'_S = I_S R_s$$

The saturation drain current can be written as

$$I_D = -\beta \frac{(V_G - V_P)^2}{1 - \beta R_s (V_G - V_P) + \sqrt{1 - 2\beta R_s (V_G - V_P)}}$$

(2-16b)

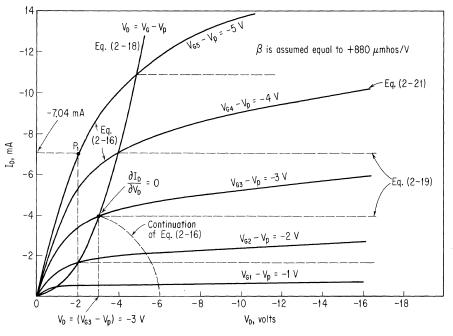

Fig. 2-4. Calculated characteristics of an MOS.

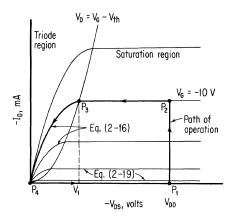

Equation (2-16) was used to generate the triode portion of the characteristic curves for a P-channel device which are shown in Fig. 2-4. A simple numerical example will illustrate the calculation of point  $P_1$  in the figure.

Assuming  $\beta = +880 \ \mu \text{mhos/V}$ ,  $V_G - V_{th} = -5 \text{ V}$ ,  $V_D = -2 \text{ V}$ ,

$$I_D = -8.8 \times 10^{-4} [+(-5)(-2) - \frac{1}{2} \times 2^2]$$

$I_D = -7.04 \text{ mA}$

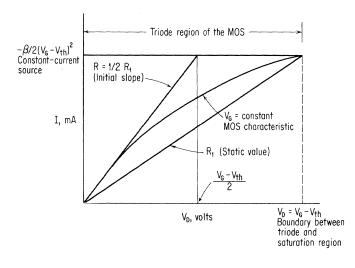

The output current in the triode region depends upon the drain voltage, and hence the drain-source terminals are like a resistor whose value depends upon the gate bias. Using a small-signal approximation, the resistance is linear and adjustable. Close to the origin and when  $|V_D| \ll |V_G - V_{th}|$ , the resistive characteristics are quite linear over a range of voltages and currents. Since the curves pass through the origin, the characteristics suggest that the MOS can be used as a voltage-controlled d-c, as well as a-c, resistor. (See Fig. 3-9.)

Equation (2-16) was derived on the basis of the gradual channel approximation (approximation No. 2) and is valid only for the case where  $|V_D| \ll |V_G - V_{th}|$ .\*

\* A more "exact" analysis by Ihantola<sup>1</sup> points out that, while Eq. (2-16) is valid near the origins, it is only an approximation near the point of saturation. To improve

30

When  $|V_D| \geq |V_G - V_p|$ , the device enters the saturation or pinchoff region and a different device model applies. Equation (2-16) is also not valid in the lowcurrent region when  $V_G \cong V_{th}$ . Here the inversion layer is not yet fully formed, and the gate electric field terminates on comparable quantities of mobile charge (in the channel area) and immobile charge (in the depletion region beneath the channel). Because of this fact, the gate voltage no longer controls the channel conductance in the manner stated by Eq. (2-16). The lower boundary on the gate voltage such that Eq. (2-16) is still valid occurs where the channel carrier concentration is just equal to the bulk doping; that is,  $p_{channel} = N_D$ . This occurs when the intrinsic Fermi level has been bent such that  $\phi_S = 2\phi_F$ . (See Figs. 2-1*i* and 2-2*d*. Also see Refs. 1, 4, and 7 to 9.) This subject will be covered in more detail in Sec. 2-3.

**2.** Saturation Region. For a given gate voltage such that  $|V_G| > |V_{th}|$ , as the drain voltage is increased in magnitude from zero volts, the drain current increases linearly at first, then slows down, and finally tends to level out as  $|V_D|$  is made large. The leveling out of the drain current is associated with the pinching off of the channel near the drain. Once the channel has pinched off, the current is said to have saturated at a given level and is then, to a first approximation, independent of drain voltage. Pinchoff occurs because the voltage across the oxide falls below a critical value. The channel *IR* drop is the factor causing the reduction in electric field. When  $E_{ox}$  is decreased to such a value that it cannot support sufficient mobile charge in a given portion of the channel, then that region decreases to (approximately) zero thickness and is said to have *pinched off*. The general shape of the inversion layer is illustrated in Fig. 1-1.

There are two methods for approximating the mathematical boundary between the triode and saturation regions. The first method involves letting the charge in the channel go to zero. This can be seen mathematically by setting Eq. (2-11) equal to zero. Because the channel voltage

$$[V_G - V(y)]C = Q_{SS} + Q_D (2-17)$$

is highest at the drain, pinchoff will begin at the drain as  $|V_D|$  is increased. V(y) in Eq. (2-17) can thus be replaced by  $V_D$ . Rearranging the terms of Eq. (2-17)

the accuracy near saturation or pinchoff, Ihantola gives a more precise equation:

$$I_{D} = -\beta \{ (V_{G} - V_{\text{th}}) V_{D} - \frac{1}{2} V_{D}^{2} - \frac{2}{3} |K_{1}| [(|V_{D}| + 2|\phi_{F}|)^{\frac{3}{2}} - (2|\phi_{F}|)^{\frac{3}{2}}] \}$$

(2-16c)

When  $|V_D| \gg 2|\phi_F|$ , Eq. (2-16c) reduces to a simpler form:

$$I_D = -\beta [(V_G - V_{th})V_D - \frac{1}{2}V_D^2 + \frac{2}{3}K_1V_D\sqrt{|V_D|}]$$

(2-16d)

† See Eq. (2-18).

gives the relationship

$$V_D = V_G - V_P \tag{2-18}$$

where  $V_P = -(Q_{SS} + Q_D)/C.*$

Equation (2-18) states mathematically the boundary line between the triode and saturation regions which is shown plotted in Fig. 2-4. To the right of this line, the MOS is in saturation and  $|V_D| > |V_G - V_P|$ , while to the left of this line, operation is in the triode region, where  $|V_D| < |V_G - V_P|$ .

The second method for defining the saturation-triode boundary can be found by examining Eq. (2-16). For a given gate and threshold voltage, the magnitude of the drain current increases as  $|V_D|$  is increased from zero volts. Initially, the  $(V_G - V_{th})V_D$  term dominates the expression, resulting in the increase of  $|I_D|$ . Soon, however, the quadratic term becomes significant, with the result that the rate of increase of the current falls off. At some drain voltage,  $|I_D|$  will reach a maximum. Past this point, the equation predicts a decrease. However, at the maximum-current point, the device has reached saturation and the device model and equations change. This is why a decrease in current is not seen. To illustrate this point, Eq. (2-16) is plotted past the point  $V_D = V_G - V_P$  on Fig. 2-4 for the condition  $V_G - V_P = -3$  V. To find the maximum of  $|I_D|$  from Eq. (2-16), the expression can be differentiated with respect to the drain voltage and set equal to zero. Solving the resulting expression yields the result already stated in Eq. (2-18), namely,  $V_D = V_G - V_P$ .

Once saturation has been reached, the voltage drop across the inverted portion of the channel tends to remain fixed at  $V_G - V_P$ , while  $V_D$  varies. To a first approximation, this constant voltage across a constant channel resistance results in a constant drain current. Once saturation has been reached, the output characteristic curves (such as those of Fig. 2-4) can be approximated by horizontal lines. The equation for the current in saturation can be found by placing  $V_D = V_G - V_P$  into Eq. (2-16), which results in

$$I_D = -\frac{\beta}{2} (V_G - V_P)^2$$

<sup>†</sup>

(2-19)

\* Notice that the pinchoff voltage given is exactly the same as the threshold voltage of Eq. (2-14). Refer to the footnote in Sec. 1-2 regarding pinchoff and threshold voltages.

† Equation (2-19) was derived from Eq. (2-16), and as such it does not include any dependence upon the  $\frac{2}{3}|K_{J}|[(|V_{D}| + 2|\phi_{F}|)^{\frac{3}{2}} - (2|\phi_{F}|)^{\frac{3}{2}}]$  term in Eq. (2-16c). An analysis carried out by Greene and Soldano<sup>10</sup> includes the above term and leads to increased accuracy of Eq. (2-19):

$$I_D = -\frac{\beta}{2} (V_G - V'_P)^2$$

(2-19a)

where  $V'_P = |V_P| + \frac{2}{3}|K_1| \sqrt{|V_G - V_P|}$ .

Equation (2-19) is valid for  $|V_D| \ge |V_G - V_P|$ . (See Table 2-1 for a summary of MOS-device equations.)

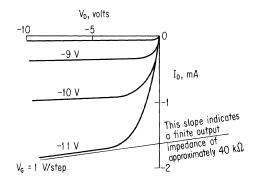

Equation (2-19) shows a square-law dependence of the drain current upon the gate voltage, and it also indicates that the drain current is independent of the drain voltage. (See Fig. 2-5 for the square-law transfer characteristic.) The saturation region, as shown in Fig. 2-4 by dotted lines, is derived from Eq. (2-19). Actual output characteristics of a P-channel MOS device indicate that the drain current is not constant and is, in fact, a function of the drain voltage. Thus a device model must be developed which will take into account the finite output impedance displayed in Fig. 2-6.

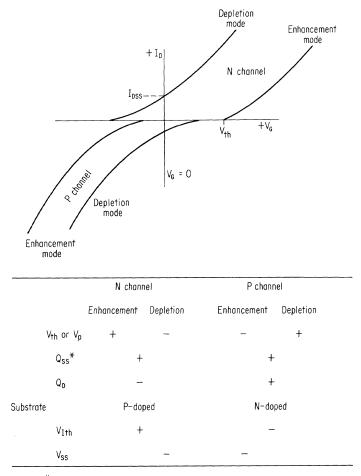

$^{*}Q_{ss}$  is generally an ionized donor and thus acts as a positive charge center. The above table was formed on the basis that there were no "added" effects such as channel doping to modify V<sub>th</sub> and that  $\left|Q_{ss}\right| > \left|Q_{0}\right|$

Figure 2-5

In an MOS transistor operating in current saturation, there are two major feedback components contributing to charge control in the channel . . . region. One is a direct electrostatic coupling between the drain electrode and the [channel] . . . by way of a near insulating substrate. . . The other is a modulation of the length of the [channel] . . . with drain voltage.

These two effects are in "parallel"; which effect dominates will depend upon the particular structure under consideration.\*

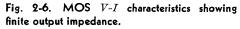

Channel-length Modulation. Figure 2-7 shows a drawing of the channel region used in developing a model for the finite output impedance exhibited by the MOSFET in saturation. Two principal features of the drawing are (1) the depletion width extends into the region of the channel and is a function of the drain voltage, and (2) the channel extending from the source has a voltage developed across it that is independent of the drain potential (to a first approximation).  $L_T$  defines the total channel length, from source to drain. L' is the distance from

\* From Ref. 11, p. 136.

Fig. 2-7. Pictorial model used in the analysis for finite output impedance.

#### Theory of Operation 35

the edge of the channel, at pinchoff, to the drain.  $L_T - L'$  represents the effective channel length.

It was stated earlier that the voltage across the pinched-off channel tends to remain fixed at  $V_G - V_{th}$ , as shown in Fig. 2-7. Any difference in the drain potential and the voltage across the channel must be taken up across a depletion region at the surface, which is designated L'. The voltage supported by this region is  $V_D - (V_G - V_{th})$ . As  $V_D$  increases, L' must also increase to absorb the additional voltage. Thus a modulation of L' by the drain voltage results in a modulation of the effective channel length<sup>1</sup> ( $L = L_T - L'$ ). Increasing the drain voltage decreases the channel length and therefore its resistance. To keep a constant voltage of  $V_G - V_{th}$  across the channel, the drain current must increase to compensate for the decrease in channel resistance. This increase in current with an increase in output voltage is positive feedback which results in the finite output impedance illustrated in Fig. 2-6.

Equation (2-19) can be modified to account for the device's finite output impedance. The distance L representing the effective channel length is now replaced by  $L_T - L'$ , where L' is derived from simple P-N junction theory.

$$L' = \sqrt{\frac{2\epsilon_s [V_D - (V_G - V_{th})]}{qN}}$$

(2-20)

where N is the impurity density of the substrate. Equation (2-19) is rewritten as

$$I_D = I_{DP} \frac{L_T}{L_T - L'}$$

(2-21)

where  $I_{DP} = -(\beta/2)(V_G - V_{th})^2 \Big|_{V_D = V_G - V_{th}}$  (drain current at the point of saturation or pinchoff).

Equations (2-20) and (2-21) show that as the drain voltage is increased, L' increases, causing an increase in the drain current. A set of output characteristics derived from Eqs. (2-16) and (2-21) is shown in Fig. 2-4.

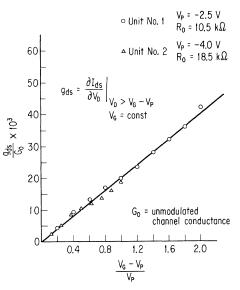

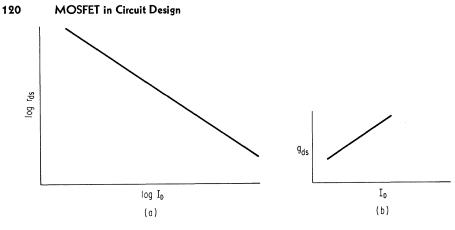

Hofstein and Warfield<sup>11</sup> have shown that for the case of channel-length modulation, the output conductance is directly proportional to the drain current. This conclusion is verified in Fig. 2-8, where  $g_{ds}$  is plotted as a function of  $I_D$ . This graph of measured data shows that the drain conductance is, in fact, a linear function of the drain current. Thus one can conclude that for the two devices shown, the dominant feedback mechanism is the channel-length modulation.

Both Hofstein and Warfield<sup>11</sup> and Reddi and Sah<sup>12</sup> conclude that this type of feedback is analogous to the Early effect that one observes in bipolar devices.\*

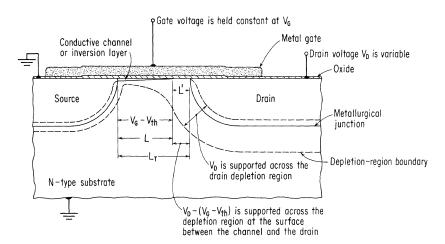

Drain-to-channel Electrostatic Feedback. When the substrate of an MOS device is sufficiently low-doped, the drain field may penetrate into the channel. A model of this situation is shown in Fig. 2-9. Since the charges in the channel cannot tell

\* The Early effect<sup>13</sup> in bipolar transistors is a modulation of the base width with collector voltage which produces a finite output impedance.

Fig. 2-8. Output conductance vs. drain current.

whether the electric field lines terminating upon them come from the negativebiased drain or the negative-biased gate (P-channel device), a modulation of the drain voltage results in a modulation of the channel conductance. In addition to collecting carriers coming from the channel, the drain acts as a gate or a control electrode.

When electrostatic feedback dominates, Hofstein and Heiman<sup>14</sup> have shown that

Fig. 2-9. Model illustrating electrostatic feedback from drain diffusion into the channel. (After Hofstein and Warfield.<sup>11</sup>)

Fig. 2-10. Plot of  $g_{ds}/G_o$  vs.  $(V_G - V_P)/V_P$ . (After Hofstein and Heiman.<sup>14</sup>)

the drain conductance is directly proportional to the effective gate voltage  $(V_G - V_P)$ . Data illustrating this fact are shown in Fig. 2-10.

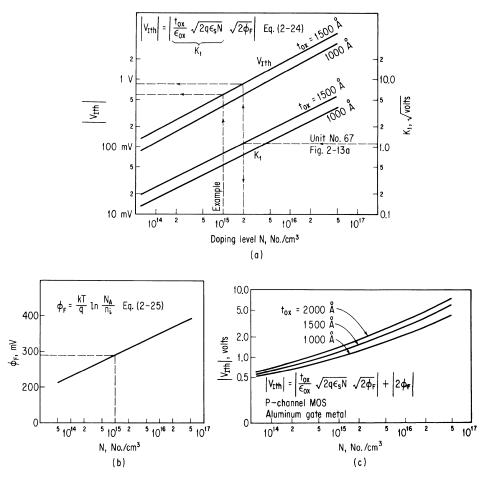

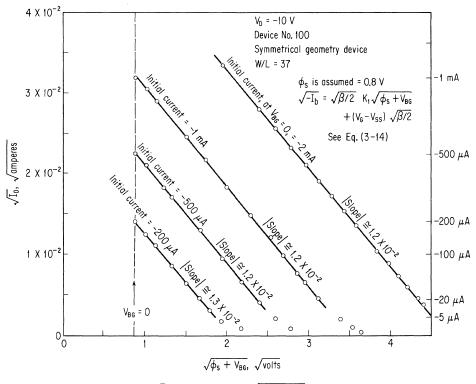

#### 2-3 ADDITIONAL CONSIDERATION OF THE THRESHOLD VOLTAGE

1. Physical Considerations. Threshold voltage was given in Eq. (2-14) as

$$V_{th} = -\frac{Q_{SS} + Q_D}{C} \tag{2-22}$$

where  $Q_{ss}$  = effective surface-state charge density per unit area

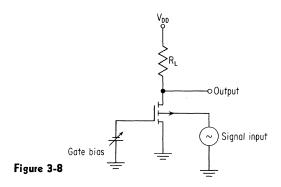

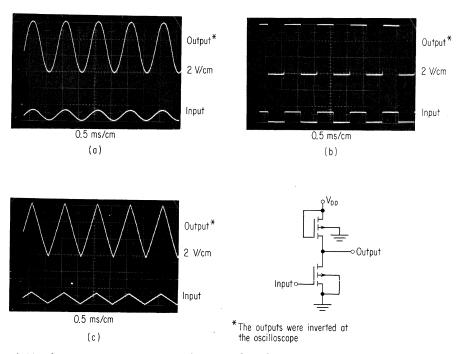

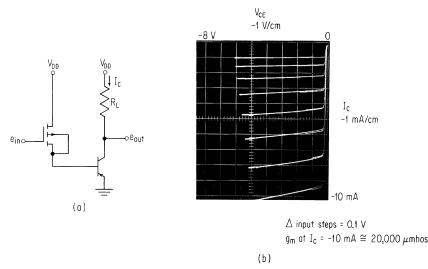

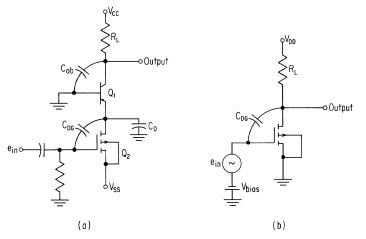

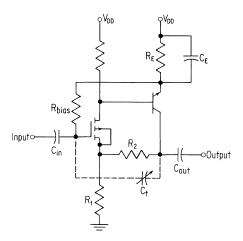

$Q_D$  = bulk charge per unit area associated with the channel depletion region C = capacitance of the gate to channel per unit area,  $\epsilon_{ox}/t_{ox}$