This manual supports the following TEKTRONIX products:

| 8550<br>Options | 8540<br>Options | Products |  |

|-----------------|-----------------|----------|--|

| 2P              | 2P              | 8300E26  |  |

| 3U              | 3U              | 8300P26  |  |

This manual supports a software/firmware module that is compatible with:

DOS/50 Version 2 (8550) OS/40 Version 1 (8540)

# PLEASE CHECK FOR CHANGE INFORMATION AT THE REAR OF THIS MANUAL.

# 8500 MODULAR MDL SERIES 68000 EMULATOR SPECIFICS USERS MANUAL

Tektronix, Inc. P.O. Box 500 Beaverton, Oregon 97077

070-3970-00 Product Group 61 Serial Number \_

Software License No.\_

Contractor: Tektronix, Inc.

Explanation of Limited Rights Data Identification Method Used: Entire document subject to limited rights.

Those portions of this technical data indicated as limited rights data shall not, without the written permission of the above Tektronix, be either (a) used, released or disclosed in whole or in part outside the Customer, (b) used in whole or in part by the Customer for manufacture or, in the case of computer software documentation, for preparing the same or similar computer software, or (c) used by a party other than the Customer, except for: (i) emergency repair or overhaul work only, by or for the Customer, where the item or process concerned is not otherwise reasonably available to enable timely performance of the work, provided that the release or disclosure hereof outside the Customer shall be made subject to a prohibition against further use, release or disclosure; or (ii) release to a foreign government, as the interest of the United States may require, only for information or evaluation within such government or for emergency repair or overhaul work by or for such government under the conditions of (i) above. This legend, together with the indications of the portions of this data which are subject to such limitations shall be included on any reproduction hereof which includes any part of the portions subject to such limitations.

# **RESTRICTED RIGHTS IN SOFTWARE**

The software described in this document is licensed software and subject to **restricted rights**. The software may be used with the computer for which or with which it was acquired. The software may be used with a backup computer if the computer for which or with which it was acquired is inoperative. The software may be copied for archive or backup purposes. The software may be modified or combined with other software, subject to the provision that those portions of the derivative software incorporating restricted rights software are subject to the same restricted rights.

Copyright © 1982 Tektronix, Inc. All rights reserved. Contents of this publication may not be reproduced in any form without the written permission of Tektronix, Inc.

Products of Tektronix, Inc. and its subsidiaries are covered by U.S. and foreign patents and/or pending patents.

TEKTRONIX, TEK, SCOPE-MOBILE, and are registered trademarks of Tektronix, Inc. TELEQUIPMENT is a registered trademark of Tektronix U.K. Limited.

Printed in U.S.A. Specification and price change privileges are reserved.

# Section 7L

# 68000 EMULATOR SPECIFICS

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Page                                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7L-1                                                                                                                            |

| General Information<br>Emulator Hardware Configuration<br>Microprocessors Supported<br>Emulation Modes<br>Clock Rates<br>Symbolic Debug                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7L-1<br>7L-1<br>7L-1<br>7L-1                                                                                                    |

| Emulator-Specific Parameters, Commands, and Displays<br>Byte/Word Parameter<br>Register Designators<br>The 68000 Status Register<br>DOS/50 and OS/40 Commands<br>ALAllocate Memory to Logical Memory Map<br>BKSets or Displays Breakpoint Conditions<br>DDump; Displays Memory Contents<br>DIDisassembles Object Code into Mnemonics<br>DSDisplay Contents of Emulator Processor Registers<br>EXDisplays or Alters Memory Contents<br>FFills Program/Prototype Memory with Data<br>GBegins Program Execution<br>MAPSets or Displays Memory Map Assignments<br>MEMSPDefines Default Memory Space<br>MOVMoves Data Between Program and Prototype Memory<br>PAlters Memory Contents | 7L-2<br>7L-2<br>7L-4<br>7L-5<br>7L-5<br>7L-5<br>7L-6<br>7L-7<br>7L-9<br>7L-9<br>7L-9<br>7L-9<br>7L-9<br>7L-10<br>7L-11<br>7L-11 |

| RDReads from Emulator PortRESETReinitializes EmulatorSAssigns Value to Register or SymbolSEASearches Memory for Value or StringSELSelects the EmulatorTRAControls Display of Executed InstructionsWRTWrites to Emulator I/O PortReal-Time Prototype AnalyzerTrigger Trace Analyzer (TTA) Commands and ParametersEVE and BUS Command ParametersONSSet Consecutive EventsDISPDisplay Contents of Acquisition MemoryTSDisplay Status of TTA Triggers                                                                                                                                                                                                                                | 7L-11<br>7L-13<br>7L-13<br>7L-14<br>7L-14<br>7L-15<br>7L-16<br>7L-16<br>7L-16<br>7L-17<br>7L-17<br>7L-17<br>7L-17               |

| SRB Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7L-21                                                                                                                           |

| Special Considerations           Fetching and the Prefetch Pipeline           Interrupts                                                          | 7L-25                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| Memory Spaces                                                                                                                                     | 7 <b>L-</b> 33          |

| The 68000 STOP Instruction                                                                                                                        | 7L-44                   |

| <u>Jumpers</u><br>EMU 1 Board<br>P1080Emulator Halt Control Selector                                                                              | 7L-45                   |

| EMU 2 Board<br>J2144Break Cycle Control Selector                                                                                                  | 7L-45<br>7L-45          |

| Interface Buffer Board<br>P1Data Transfer ACKnowledge (DTACK) Delay<br>P2 and P3Prototype Bus Arbitration Control                                 |                         |

| P6Address Strobe Control                                                                                                                          | 7L-47<br>7L-47<br>7L-47 |

| P8Internal Generation of DTACK in Mode 1<br>Interface Control Board                                                                               | 7L-48<br>7L-48<br>7L-48 |

| J4011Save Non-Maskable Interrupts<br>J6021Save Prototype Interrupts<br>Mobile Microprocessor Board                                                | 7L-49                   |

| J1045 and J2045Delay of DTACK Assertion                                                                                                           | 7L-49                   |

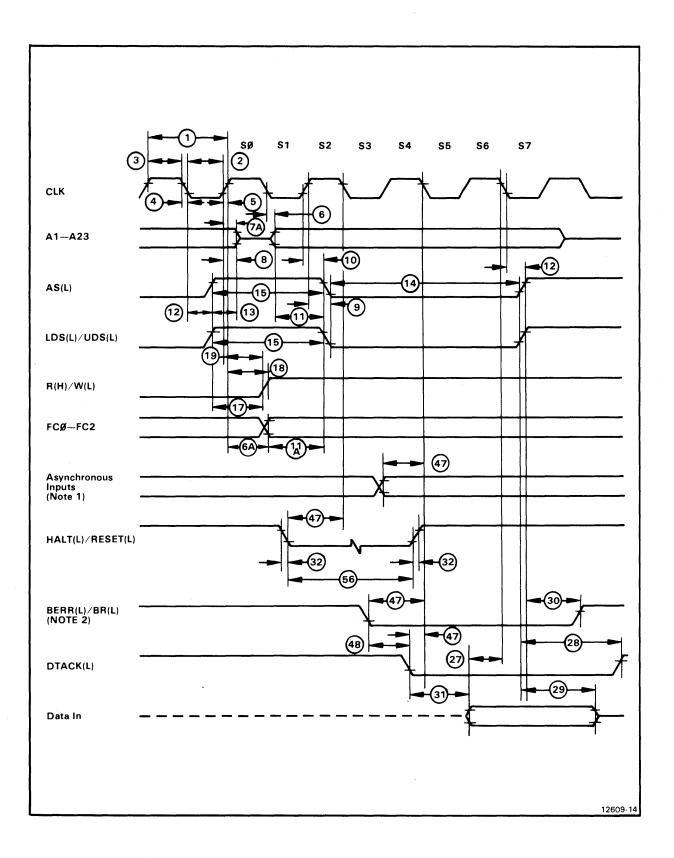

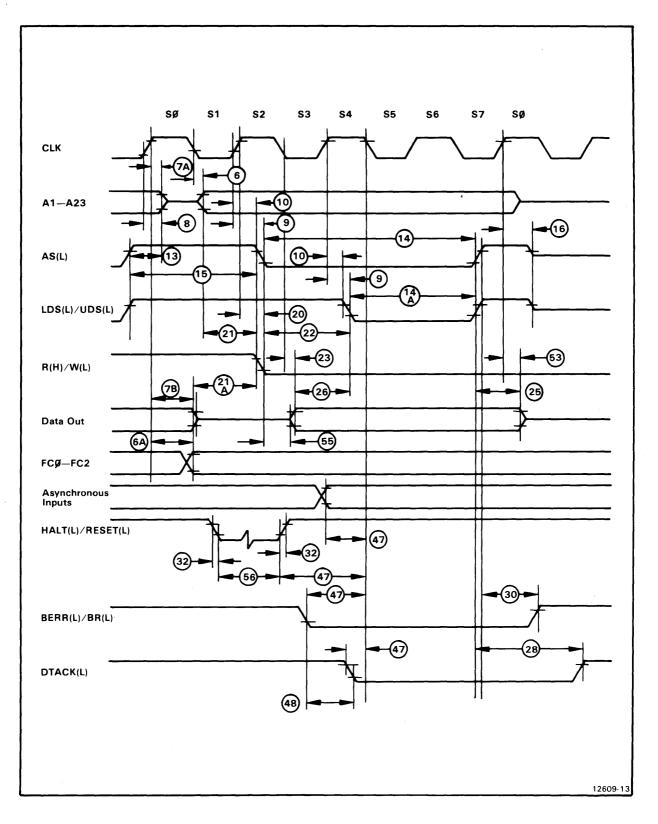

| Emulator Timing                                                                                                                                   |                         |

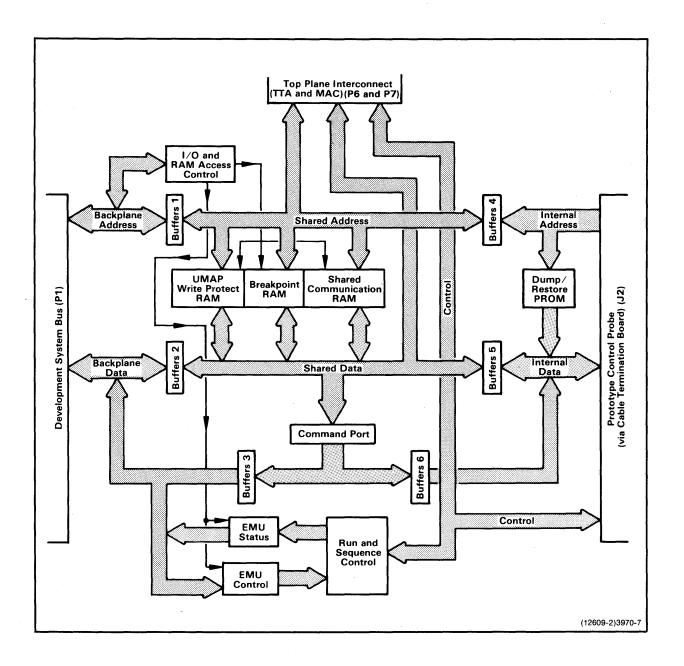

| Probe/Prototype Interface Diagram                                                                                                                 |                         |

| Installing Your 68000 Emulator Software                                                                                                           | 7L <b>-</b> 55          |

| 68000 Demonstration Run<br>Introduction                                                                                                           | 7L-59                   |

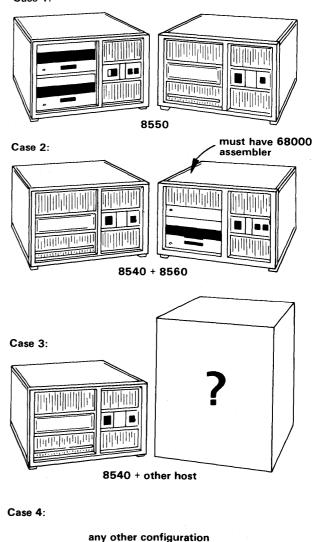

| Examine the Demonstration Program<br>Assemble and Load the Demonstration Program<br>Case 1: Assemble and Load on the 8550                         | 7L-63                   |

| Case 2: Assemble on the 8560; Download to the 8540<br>Case 3: Download from Your Host to the 8540                                                 | 7L-70                   |

| Case 4: Patch the Program into Memory<br>Run the Demonstration Program                                                                            | 7L-83                   |

| Monitor Program Execution<br>Summary of 68000 Emulator Demonstration Run                                                                          |                         |

| Error Messages                                                                                                                                    |                         |

| <u>Reprints</u><br>Microprogrammed Implementation of a Single Chip Microprocessor<br>Design and Implementation of System Features for the MC68000 | 7L-101                  |

| Instruction Prefetch on the MC68000                                                                                                               |                         |

\_\_\_\_\_

# TABLES

\_\_\_\_\_

| Table<br>No.                                               |    |

|------------------------------------------------------------|----|

| 7L-1 68000 Registers and Flags 7L-                         | -3 |

| 7L-2 Register Symbols Accepted by S Command 7L-            | 13 |

| 7L-3 EVE/BUS Signal Symbols 7L-                            | 16 |

| 7L-4 68000 Service Calls 7L-2                              | 20 |

| 7L-5 Encoding of the Memory Space Byte 7L-2                | 21 |

| 7L-6 Classification of Memory Space References             | 33 |

| 7L-7 68000 Exception Vector Assignment 7L-1                | 40 |

| 7L-8 J1045 and J2045 Configurations 7L-8                   | 50 |

| 7L-9 68000 Emulator/Microprocessor Timing Differences 7L-9 | 51 |

| 7L-10 Basic 8560 Editing Commands 7L-                      | 72 |

# ILLUSTRATIONS

| - <b>L</b> | ٦. | ~  |   |

|------------|----|----|---|

| L.         | 1  | Σ. |   |

| _          | _  | 0  | - |

| No.                                                                 |               |

|---------------------------------------------------------------------|---------------|

| 7L-1 Status Register                                                | 7L-4          |

| 7L-2 Sample disassembly                                             | 7L-8          |

| 7L-3 Sample DISP display 71                                         | L-17          |

| 7L-4 A 68000 SRB pointer located at COC3 71                         |               |

| 7L-5 68000 SVC demonstration program listing                        |               |

| 7L-6 Alternate executable code for SVC demonstration program 71     |               |

| 7L-7 68000 instruction pipeline block diagram                       |               |

| 7L-8 Program example                                                |               |

| 7L-9 Example program run with TRA OFF 71                            |               |

| 7L-10 Example program run with TRA ON 71                            |               |

| 7L-11 Memory partitioning example program 7                         |               |

| 7L-12 68000 timing diagram, read cycle 71                           |               |

| 7L-13 68000 timing diagram, write cycle                             |               |

| 7L-14 68000 Prototype Control Probe interface                       |               |

| 7L-15 68000 demonstration run program                               |               |

| 7L-16 68000 demonstration program: Extended Tekhex format 71        |               |

| 7L-17 Symbol table listing                                          |               |

| 7L-18 Host computer commands for preparing demonstration program 71 | L <b>-</b> 76 |

.

•

## Section 7L

#### 68000 EMULATOR SPECIFICS

#### INTRODUCTION

This supplement is designed to be inserted into Section 7 of the 8550 System Users Manual (DOS/50 Version 2) or the 8540 System Users Manual. This Emulator Specifics section explains the features of the 8550 and 8540 that are unique to the 68000 emulator. Throughout this section, "your System Users Manual" refers to the 8550 System Users Manual or 8540 System Users Manual.

The 68000 demonstration run is designed to be used with Section 1, the Learning Guide of your System Users Manual; the rest of this section contains reference material.

As a user of the 68000 emulator, you should be familiar with the material in the MC68000 16-Bit Microprocessor User's Manual, by Motorola. In addition, you should be familiar with the internal operation of the 68000. Information is available in the booklet <u>MC68000 Article Reprints</u>, by Motorola. Three of the more pertinent articles from that booklet have been reprinted here in the subsection "Reprints". Some of the effects of the 68000's design on the behavior of the emulator are discussed under the topic, "Special Considerations".

GENERAL INFORMATION

### EMULATOR HARDWARE CONFIGURATION

Throughout this Emulator Specifics section, the term "68000 emulator" refers to a 68000 Emulator Processor board configured with a 68000 Prototype Control Probe. In emulation mode 0, the prototype control probe must be connected to the main emulator boards. In modes 1 and 2, the prototype control probe must be connected to both the emulator and your prototype. For instructions on installing your emulator boards and probe, refer to your 68000 Emulator Processor and Prototype Control Probe Installation Service Manual.

# MICROPROCESSORS SUPPORTED

The 68000 emulator emulates the Motorola MC68000 microprocessor.

#### EMULATION MODES

The 68000 supports emulation modes 0, 1, and 2, as described in the Emulation section of your System Users Manual.

General Information

CLOCK RATES

In emulation mode 0, the emulator clock rate is 8MHz. In emulation modes 1 and 2, the prototype clock rate may range from 2MHz to 8MHz.

SYMBOLIC DEBUG

The 68000 emulator supports the use of symbolic debug. Most of the displays in this manual include symbolic debug information.

# EMULATOR-SPECIFIC PARAMETERS, COMMANDS, AND DISPLAYS

# BYTE/WORD PARAMETER

Several commands allow you to operate on memory on a byte-oriented or word-oriented basis. This choice is represented by the -B or -W parameter. For the 68000 emulator, the default setting is -W, except for the MOV, RD and WRT commands, where the default is -B.

# REGISTER DESIGNATORS

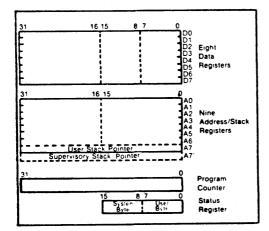

Table 7L-1 alphabetically lists the symbols used by DOS/50 and OS/40 to designate the registers and flags used by the 68000. The table provides the following information for each symbol:

- a description of the register or flag that the symbol represents

- the size of the register or flag

- the value assigned to the register or flag by the RESET command

- whether the register or flag can be assigned a value by the S (Set) command.

7L-2

\_\_\_\_

Table 7L-1 68000 Registers and Flags

\_\_\_\_\_

|        |           | د هه نوی که این که این که این که نود جو که که که که جم که بود بود که این که این این که این که نود که دو وی مع که بود وی د |           |        |            |                            |      |                                       |

|--------|-----------|---------------------------------------------------------------------------------------------------------------------------|-----------|--------|------------|----------------------------|------|---------------------------------------|

|        | 1         |                                                                                                                           |           |        |            | Value After                |      |                                       |

| Symbol | ;<br>;=:: | Description                                                                                                               | ;;<br>=== | (Bits) | ' i<br>:=: | RESET                      | <br> | S Command?                            |

| A0A6   |           | seven address registers                                                                                                   | 1         | 32     |            | unchanged                  |      | yes                                   |

| С      |           | Carry bit of CCR                                                                                                          | 1         | 1      | !          | unchanged                  | ¦    | yes                                   |

| CCR    | ł         | Condition Code portion of SR                                                                                              | 1         | 5      | 1          | unchanged                  | 1    | yes                                   |

| D0D7   | ł         | eight data registers                                                                                                      | 1         | 32     | ł          | unchanged                  | 1    | yes                                   |

| I      | 1         | Interrupt mask of SR                                                                                                      | ł         | 3      |            | 7                          | ł    | yes                                   |

| N      | 1         | Negative bit of CCR                                                                                                       |           | 1      |            | unchanged                  | 1    | yes                                   |

| PC     | <br>      | Program Counter                                                                                                           |           | 24     | <br>       | contents of<br>SP:000004 * | 1    | no                                    |

| S      | !         | Supervisor/User bit of SR                                                                                                 |           | 1      | 1          | 1 (on)                     |      | yes                                   |

| SR     | 1         | Status Register                                                                                                           | 1         | 16     | 1          | 27XX                       |      | yes                                   |

| SSP    |           | Supervisor Stack Pointer (A7)                                                                                             |           | 32     |            | contents of<br>SP:000000 * |      | yes                                   |

| T      | ł         | Trace bit of SR                                                                                                           | 1         | 1      |            | 0 (off)                    | !    | yes                                   |

| USP    |           | User Stack Pointer (A7)                                                                                                   | 1         | 32     | 1          | unchanged                  |      | yes                                   |

| V      |           | oVerflow bit of CCR                                                                                                       |           | 1      |            | unchanged                  | 1    | yes                                   |

| X      |           | eXtend bit of CCR                                                                                                         |           | 1      |            | unchanged                  | ł    | yes                                   |

| Z      |           | Zero bit of CCR                                                                                                           |           | 1      |            | unchanged                  |      | yes                                   |

|        |           |                                                                                                                           |           |        |            |                            | -    | · · · · · · · · · · · · · · · · · · · |

\* SP: is Supervisor Program space.

7L-3

Parameters, Commands, Displays

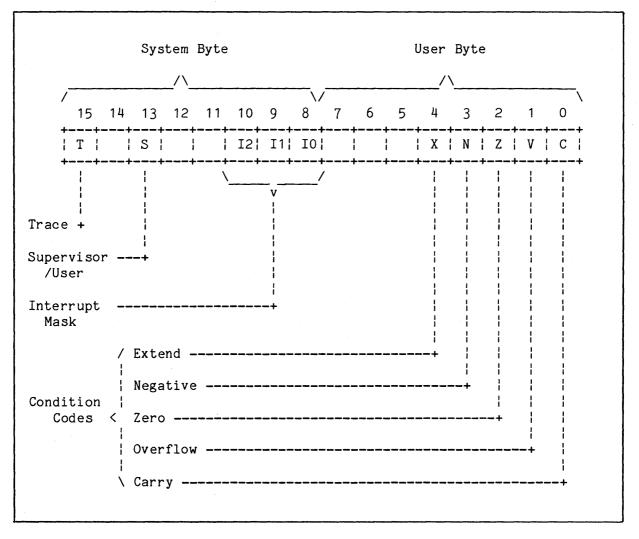

### THE 68000 STATUS REGISTER (SR)

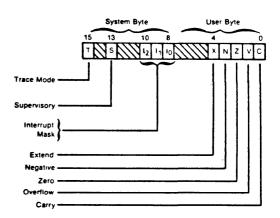

The 16-bit Status Register (SR) has a system byte (high order) and a user byte (low order). The system byte contains the Trace Mode and Supervisor State bits, and contains the three bits used as the Interrupt Mask. The user byte contains five status flag bits, which are used primarily for branch control within a program, and for error detection. Figure 7L-1 shows the Status Register.

ین هم خب جه عد باب بند بینا که ها جو که به هم هم این به هم با هم هم هم باب این ها جه ای هر باب هم

# Fig. 7L-1. Status Register.

DOS/50 AND OS/40 COMMANDS

### AL---Allocate Memory to Logical Memory Map

The AL command allocates 4K-bytes blocks of program memory to the processor's logical memory space. The MAC (Memory Allocation Controller) option must be installed. For example, the command <u>AL SP:UP:0</u> allocates one block of program memory for location 0--OFFF of the two memory spaces SP and UP. Thus, for the range 0--OFFF, these two memory spaces will be in the same physical memory. References to either of those two memory spaces in that range will access the same physical location. For example, the address OA40 in the supervisor program space (SP) will be at the same physical location as the address OA40 in the user program space (UP).

With the 68000 emulator, the AL command may be used only if the Memory Allocation Controller (MAC) option is installed. The use of the AL command does not follow that described by the Command Dictionary of your System Users Manual. Refer to the Emulation section of your System Users Manual for a detailed description of the AL command when the MAC option is installed.

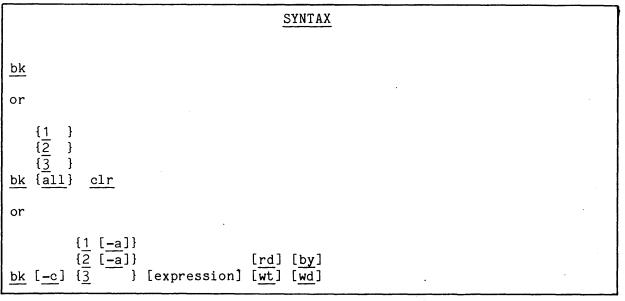

# BK---Sets or Displays Breakpoint Conditions

With the 68000 emulator, the BK command syntax and parameters are not as described in the Command Dictionary of your System Users Manual. Use the following information instead.

#### PARAMETERS

1, 2, and 3. The number specifies the desired breakpoint.

ALL. This specifies all breakpoints.

CLR. This parameter clears the specified breakpoint(s).

Parameters, Commands, Displays

68000 Emulator Specifics Users

<u>-C</u>. This parameter causes execution to continue after each breakpoint occurs. If -C is not specified (the default), the BK command stops execution after a breakpoint occurs. To resume program execution, enter the G command without parameters.

\_\_\_\_\_

<u>-A</u>. This mode sets breakpoint 1 to arm breakpoint 2. When the mode is set, breakpoint 2 will not occur unless breakpoint 1 has already happened. Arming mode may be set when entering either breakpoint 1 or breakpoint 2, but one of these two breakpoints must already be defined. When you redefine either breakpoint 1 or 2 this setting is cancelled.

<u>expression</u>. This parameter is an expression that represents the address where program execution is to be interrupted. The expression may include don't-care bits and/or a memory space designator. The address expression may also be omitted. For example, BK 1,,BY WT will cause a break on the first byte write.

$\overline{\text{RD}}$  and  $\overline{\text{WT}}$ . These parameters designate that a breakpoint occurs when a memory read (or write) occurs at the specified address. The default is any access (read or write).

<u>BY and WD</u>. These parameters designates that a breakpoint occurs when a byte (or word) operation occurs at the specified address. The default is any access (byte or word).

#### NOTE

When you use TRA, and breakpoints are set, the break may occur before the address where the breakpoint is set. This occurs because the address has been identified going into the 68000 prefetch pipeline. Be sure to check the display to see if the last instruction executed was the one on which you wanted to break. If it is not, enter G again, and the next instruction will be executed. Check the display again, and repeat the G command, if necessary. It is recommended that you put NOP statements in your program around the statements where you want to break.

#### D---Dump; Displays Memory Contents

The D command allows memory space designators in the address expressions.

Parameters, Commands, Displays

# DI---Disassembles Object Code into Mnemonics

ہے ہے ہے بہے بنے بین سے بنے بنے بنی بنی بنی جب سے جب بنے جن سے ان اب ان بنی سے بہ ان ان ان اس جب آن بنی سے جب سے غبر ان بن

The DI command translates object code in memory into assembly language instructions. It displays addresses, object code, assembly language mnemonics, and operands.

DI Display Format. In general, the format of the disassembly follows the conventions of both the Motorola cross-assembler and the TEKTRONIX 8500 Series B 68000 Assembler. An example of a disassembled instruction is:

000712 13C0 MOVE.B DO,F00007H

In this example:

6

- 000712 is the memory location of the instruction being disassembled.

- 13C0 is the opcode.

- MOVE is the opcode mnemonic.

- .B is the size extension. In the DI display, the size extension may be shown on some instructions where it may not be required or allowed for assembly.

- DO is the source operand.

- F00007H is the destination operand.

Exceptions from the Assembler Format. The opcode variations ADDA, ADDI, ANDI, CMPA, CMPI, EORI, MOVEA, ORI, SUBA, and SUBI do not appear in the disassembly. The assembler chooses the correct A or I opcode variation by examining the operands in the instruction, rather than by the opcode suffix. Thus, ADDI #035FH,DO and ADD #035FH,DO would both generate the same opcode, and their disassembly will be displayed as ADD.W #035FH,DO.

The opcodes for BT and DBF are disassembled as the equivalent mnemonics, BRA and DBRA, respectively.

The mnemonics EMT\_A and EMT\_F are displayed whenever an attempt is made to disassemble opcodes in the ranges A000--AFFF and F000--FFFF. These opcode ranges are reserved by Motorola for future enhancements.

A line of asterisks (\*\*\*\*\*\*\*) is displayed in the instruction field if an attempt is made to disassemble an illegal opcode.

A sample disassembly is shown in Fig. 7L-2.

|     | كي جيد بعد الشائلة التاريب في منه النائلة المستحد الشائلة ال |                        |         | ويوساد المالي ومستعملة فالقائب وفرجه ومست التلفات فمستعده فاستكار التوريق مستقدا التهيو |

|-----|--------------------------------------------------------------|------------------------|---------|-----------------------------------------------------------------------------------------|

|     | > <u>DI 3000 30</u><br>ADDRESS                               | 22 <cr<br>DATA</cr<br> |         | C                                                                                       |

|     | DEMO+00000                                                   |                        |         |                                                                                         |

|     | 003000                                                       | 4280                   | CLR.L   | DO                                                                                      |

|     | DEMO+00000                                                   |                        |         |                                                                                         |

|     | 003002                                                       | 323C                   | MOVE.W  | #3H,D1                                                                                  |

|     | DEMO+00000                                                   | -                      |         |                                                                                         |

|     | 003006                                                       | 207C                   | MOVE.L  | #1000H,A0                                                                               |

|     | DEMO+00000                                                   |                        | MOVE    | #2000U A1                                                                               |

|     | 00300C                                                       | 227C                   | MOVE.L  | #2000H,A1                                                                               |

|     | LOOP                                                         | 2151                   | MOVE W  | 3024H,3026H                                                                             |

|     | -                                                            |                        | MOVE.W  | 5024II, 5020II                                                                          |

|     | DEMO+00001<br>003018                                         | •                      | MOVE.I. | (AO)+,(A1)+                                                                             |

|     | -                                                            |                        |         | (110) + ; (11) + ;                                                                      |

|     | DEMO+00001<br>00301A                                         |                        | DBF     | D1,3012H                                                                                |

|     | DEMO+00001                                                   |                        |         |                                                                                         |

|     | 00301E                                                       | 4E71                   | NOP     |                                                                                         |

| · . | DEMO+00002<br>003020                                         | 20<br>4E71             | NOP     |                                                                                         |

|     | SELF                                                         |                        |         |                                                                                         |

|     | 003022                                                       | 60FE                   | BT      | 3022H                                                                                   |

|     |                                                              |                        |         |                                                                                         |

Fig. 7L-2. Sample disassembly.

This display was generated when SYMD was ON.

DS---Display Contents of Emulator Processor Registers

The DS command displays the 68000 registers. The display contains PC(next), the fifteen 32-bit general registers, the system and user stack pointers, and the system status register. The status register is displayed in hexadecimal, and in binary with each bit labelled. Refer to the following example:

> DS

PC=00132C D0=000000F D1=0001FF00 D2=0000000 D3=0000000 D4=00BC48FF D5=0000000 D6=0000000 D7=0000000 A0=00F00000 A1=0000000 A2=0000000 A3=00001000 A4=0000004 A5=0000008 A6=0000000 SSP=00DC1000 USP=00100000 T.S. .III ...X NZVC SR=850A ---> 1.0. .101 ...0 1010

The long and short forms of the DS display are the same: the -L modifier has no effect.

# EX---Displays or Alters Memory Contents

The EX (EXamine) command allows memory space designators in the address expression.

An error will occur if you attempt to examine memory that is not on a word boundary while in word mode (-W).

## F---Fills Program/Prototype Memory with Data

The F command allows memory space designators in the address expression.

An error will occur if you attempt to fill memory that is not on a word boundary while in word mode (-W).

#### G---Begins Program Execution

The G (Go) command starts the emulator at the 24-bit address specified. The processor examines the S bit of the 68000 status register to determine whether to start in supervisor or user program space. Memory space designators are not allowed; however, you may select the program space with the Set command.

If breakpoints have been set, it may be necessary to invoke G more than once to actually execute the instruction on which you wish the break to occur. This is because the 68000 performs prefetching and does not have a fetch signal. Refer to the discussions under "Special Considerations" later in this section. Also, refer to the BK command discussion.

# MAP---Sets or Displays Memory Map Assignments

\_\_\_\_\_

The MAP command enables you to assign blocks of memory to either program or prototype memory, and to designate blocks of memory as read-only. The 68000 MAP command differs from the description given in the Command Dictionary as follows:

- The -M modifier is not allowed. Displays are in tabular form only.

- Entering <u>MAP</u> with no parameters causes the display of the current memory map assignments for the default memory spaces (MEMSP M).

- Entering <u>MAP -A</u> displays the current memory map assignments for all valid memory spaces.

- Entering <u>MAP</u> followed by one or more memory space designators displays the current mapping for the indicated memory space(s).

- The block size default is 4K bytes.

- Unlike most other emulators, the 68000 emulator supports write protection for prototype memory through use of the URO parameter.

- Multiple memory space designators are allowed as part of the <u>loaddr</u> parameter. They are not allowed in the <u>hiaddr</u> parameter. The <u>hiaddr</u> parameter defaults to the same memory space(s) as <u>loaddr</u>.

If you attempt to change the program/prototype map assignments and are not currently in emulation mode 1, a warning message is displayed indicating that you are not in mode 1. The mapping of read-only and read/write is valid in any emulation mode.

Here is a sample 68000 MAP assignment and display:

> MAP PRW 000000 70FFFF <CR>

> MAP URW SD:710000 7FFFFF <CR>

> MAP \_A <CR>

UD 000000-FFFFFF PRW

UP 000000-FFFFFF PRW

SD 000000-70FFFF PRW

SD 710000-7FFFFF URW

SD 800000-FFFFFF PRW

SP 000000-FFFFFF PRW

#### MEMSP---Defines Default Memory Space

The 68000 emulator's default MEMSP settings are as follows:

> MEMSP <CR>

Default single memory space.....SP

Default multiple memory spaces...UD UP SD SP

# MOV---Moves Data Between Program and Prototype Memory

The MOV command allows memory space designators in the address expressions.

For example, the command:

> MOV UD:3640 4340 SD:2000 <CR>

moves User Data space 3640--4340 to Supervisor Data space beginning at address 2000.

An error occurs if you attempt to move data that is not on a word boundary while in word mode (-W). The default mode for the MOV command is -B.

#### P---Alters Memory Contents

The P (Patch) command allows a memory space designator in the address expression.

# RD---Reads from Emulator Port

Because the 68000's I/O is memory-mapped, the 68000 RD command works like the D command, except that prototype memory is referenced, and only one word is displayed.

#### RESET---Reinitializes Emulator

0

The RESET command simulates a hardware reset by modifying the registers of the 68000 as follows:

- The Trace bit is turned off (0).

- The Supervisor bit is turned on (1).

- The interrupt level is set to 7.

- The stack pointer is loaded from Supervisor Program memory location 000000.

- PC(next) is set to the value in Supervisor Program memory location 000004.

Parameters, Commands, Displays

.

Here is an example of register contents before invoking RESET:

> DS <CR>

PC=00132C D0=000000F D1=0001FF00 D2=0000000 D3=0000000 D4=00BC48FF D5=0000000 D6=0000000 D7=0000000 A0=00F00000 A1=0000000 A2=0000000 A3=0001000 A4=0000004 A5=0000008 A6=0000000 SSP=00DC1000 USP=00100000 T.S. .III ...X NZVC SR=850A ---> 1.0. .101 ...0 1010

After RESET, the display changes. Assume for this example that the contents of SP:000000 is 000000, and that the contents of SP:000004 is 020000. The arrows show the altered registers and bits:

| > <u>RESET</u> <cr><br/>&gt; <u>DS</u> <cr></cr></cr> |                                                   |

|-------------------------------------------------------|---------------------------------------------------|

|                                                       |                                                   |

| 1                                                     |                                                   |

| V                                                     |                                                   |

|                                                       |                                                   |

| PC=020000                                             |                                                   |

| D0=000000F                                            | D1=0001FF00 D2=00000000 D3=00000000               |

| D4=00BC48FF                                           | D5=00000000 D6=00000000 D7=00000000               |

| A0=00F00000                                           | A1=00000000 A2=00000000 A3=00001000               |

| A4=00000004                                           | A5=00000008 A6=00000000 SSP=00000000 USP=00100000 |

|                                                       | =======                                           |

|                                                       | T.SIIIX NZVC                                      |

| SR=270A>                                              | 0.11110 1010                                      |

| ==                                                    | = = ===                                           |

| <b>^</b>                                              | ^ ^                                               |

| !                                                     |                                                   |

| 1                                                     |                                                   |

| E<br>I                                                |                                                   |

| 1                                                     |                                                   |

S---Assigns Value to Register or Symbol

The S (Set) command changes the values of the 68000's registers. The symbols allowed and the registers they represent are shown in Table 7L-2.

------

|          | Tab     | ole 7L-2 |    |   |         |

|----------|---------|----------|----|---|---------|

| Register | Symbols | Accepted | by | S | Command |

| Symbol      | Register                                                                                                                                                                     |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D0D7        | the eight 32-bit data registers                                                                                                                                              |

| A0A6        | the seven 32-bit address registers                                                                                                                                           |

| T<br>S<br>I | the 16-bit Status Register<br>the Trace bit of the SR<br>the Supervisor bit of the SR<br>the three Interrupt level bits of the SR<br>the 5-bit Condition Code part of the SR |

| N<br>Z<br>V | the eXtend bit of the CCR<br>the Negative bit of the CCR<br>the Zero bit of the CCR<br>the oVerflow bit of the CCR<br>the Carry bit of the CCR                               |

\*a---The emulator does not check whether you have specified values for the unused bits in the Status Register.

# SEA---Searches Memory for Value or String

Try to limit your value and string searches to the smallest portion of memory necessary. The <u>hiaddr</u> parameter of the SEA command defaults to the end of memory. Therefore, it is <u>strongly</u> recommended that you specify the <u>hiaddr</u> parameter of the SEA command. Otherwise, you may experience extremely lengthy search times, due to the 68000's large memory capability.

7L-13

Parameters, Commands, Displays

# SEL---Selects the Emulator

The following command selects the 68000 emulator:

#### > SEL 68000 <CR>

The system responds with the software version number and version date. The emulator hardware need not be in the system when you SELect it.

#### NOTE

The 68000 emulator cannot be selected while you are programming a PROM.

# TRA---Controls Display of Executed Instructions

The TRA command sets the conditions for displaying trace lines during program execution. Memory space designators may be used when defining the <u>loaddr</u> parameter. However, they may not be used in <u>hiaddr</u>. If a memory space is not designated, the default is to all memory spaces. Here is a sample 68000 TRA display:

> <u>SYMD</u> -SL ON <CR>

> TRA ALL <CR>

> <u>G MAIN</u> <CR>

MAIN

UP:001000 227C MOVE.L #F00000H,A1

| PC=001006    |              |             |             |

|--------------|--------------|-------------|-------------|

| D0=000000F   | D1=0000FFFF  | D2=00000000 | D3=00000000 |

| D4=00000000  | D5=00000000  | D6=00000000 | D7=00000000 |

| A0=00000505  | A1=00F00000  | A2=00000000 | A3=00000000 |

| A4=00000000  | A5=00000000  | A6=00000000 |             |

| SSP=00000000 | USP=00000000 | SR=0000     |             |

PROG+000006

UP:001006 207C MOVE.L #500H,A0 PC=00100C D0=0000000F D1=0000FFFF D2=00000000

| D0=000000F   | D1=0000FFFF  | D2=00000000 | D3=00000000 |

|--------------|--------------|-------------|-------------|

| D4=00000000  | D5=00000000  | D6=00000000 | D7=00000000 |

| A0=00000500  | A1=00F00000  | A2=00000000 | A3=00000000 |

| A4=00000000  | A5=00000000  | A6=00000000 |             |

| SSP=00000000 | USP=00000000 | SR=0000     |             |

|              |              |             |             |

PROG+00000C

| UP:00100C | 323C   | MOVE.W  | #4H,D1 |             |             |

|-----------|--------|---------|--------|-------------|-------------|

| PC=001    | 010    |         |        |             |             |

| D0=000    | 0000F  | D1=0000 | 00004  | D2=00000000 | D3=00000000 |

| D4=000    | 00000  | D5=0000 | 00000  | D6=00000000 | D7=00000000 |

| A0=000    | 00500  | A1=00F0 | 00000  | A2=00000000 | A3=00000000 |

| A4=000    | 00000  | A5=0000 | 00000  | A6=00000000 |             |

| SSP=00    | 000000 | USP=000 | 000000 | SR=0000     |             |

| PROG+000010<br>UP:001010 4280              | CLR.L DO     |             |             |

|--------------------------------------------|--------------|-------------|-------------|

| PC=001012                                  |              |             |             |

| D0=00000000                                | D1=00000004  | D2=00000000 | D3=00000000 |

| D4=00000000                                | D5=00000000  | D6=00000000 | D7=00000000 |

| A0=00000500                                | A1=00F00000  | A2=00000000 | A3=00000000 |

| A4=00000000                                | A5=00000000  | A6=00000000 | -           |

| SSP=00000000                               | USP=00000000 | SR=0004     | ×           |

| PROG+000012<br>UP:001012 D018<br>PC=001014 | ADD.B (A0)+, | DO          |             |

| D0=0000001                                 | D1=00000004  | D2=00000000 | D3=00000000 |

| D4=00000000                                | D5=00000000  | D6=00000000 | D7=0000000  |

| A0=00000501                                | A1=00F00000  | A2=00000000 | A3=00000000 |

| A4=00000000                                | A5=00000000  | A6=00000000 |             |

| SSP=00000000                               | USP=00000000 | SR=0000     |             |

| <br>SREAK TRAC                             | CE,ESC>      |             |             |

The lines below each assembly language instruction show the program counter, the data and address registers, the stack pointers and the status register. The line above the instruction shows the program label or "section + offset."

Notes and Exceptions. When any TRA selections are in effect, your program executes at much less than normal speed, even in those parts of the program that are not traced. If execution speed is important, but you want to step through part of a program, you can use the following TTA command:

# > EVE 1 A=loaddr hiaddr -C <CR>

This makes the 68000 emulator pause and print the register contents after executing each instruction in the specified range. Instructions outside the range will be executed at full speed if TRA is OFF.

When TRA ALL is set and execution of the user program comes within 10 bytes of a non-allocated or NOMEMed section of memory, instruction disassembly is no longer performed. This occurs because the disassembler tries to read enough words to disassemble the longest possible instruction. Instruction execution proceeds normally and breaks if the memory boundary is reached.

The emulator does not use the 68000 status register trace bit (T). The user has full use of this bit.

If your program contains only absolute sections, the trace display will not show the "section + offset" line, even if SYMD -SL is ON. However, labels are still displayed.

# WRT---Writes to Emulator I/O Port

The WRT command allows you to write to a memory location as an I/O port. It has the same function as the P command, except that WRT always writes to prototype memory, and does not do a read-back check. A word write to an odd boundary causes an error.

Parameters, Commands, Displays

# REAL-TIME PROTOTYPE ANALYZER

You may not use the Real-Time Prototype Analyzer (RPTA) with the 68000 emulator. An error message is issued if you attempt to use the RTPA while you are using the 68000 emulator.

# TRIGGER TRACE ANALYZER (TTA) COMMANDS AND PARAMETERS

The Trigger Trace Analyzer provides real-time tracing and break conditions for the 68000 emulator running at up to 8MHz.

Memory space designators are allowed as part of the address expression, but are ignored in the actual programming of the TTA. To reference a particular memory space, you must use the BUS command.

The Trigger Trace Analyzer Users Manual describes the TTA and its commands.

# EVE and BUS Command Parameters

Table 7L-3 shows the bus signal symbols which may be used as parameters for the BUS command, and for the B parameter of the EVE command. The DISP command also uses these symbol in its display.

| Symbol      | Description                                            |  |  |  |  |

|-------------|--------------------------------------------------------|--|--|--|--|

| UP (*a)     | User Program                                           |  |  |  |  |

| UD (*a)     | User Data                                              |  |  |  |  |

| SP (*a)     | Supervisor Program                                     |  |  |  |  |

| SD (*a)     | Supervisor Data                                        |  |  |  |  |

| U (*a)      | any operation occurring in User mode                   |  |  |  |  |

| S (*a)      | any operation occurring in Supervisor mode             |  |  |  |  |

| P (*a)      | any operation occurring in Program memory              |  |  |  |  |

| D (*a)      | any Data operation                                     |  |  |  |  |

| INTA        | INTerrupt Acknowledge                                  |  |  |  |  |

| IPLO - IPL7 | InterruPt Levels                                       |  |  |  |  |

| BY          | BYte operation                                         |  |  |  |  |

| WD          | WorD operation                                         |  |  |  |  |

| RD          | ReaD operation                                         |  |  |  |  |

| WT          | WriTe operation                                        |  |  |  |  |

| VPA         | Valid Peripheral Address                               |  |  |  |  |

| BERR        | Bus ERRor                                              |  |  |  |  |

| HLT         | Halt                                                   |  |  |  |  |

| (*a)The DI  | (*a)The DISP command displays these symbols as part of |  |  |  |  |

# Table 7L-3 EVE/BUS Signal Symbols

the address field instead of the bus signal field.

CONS---Set Consecutive Events

The EMU and FET parameters are not supported.

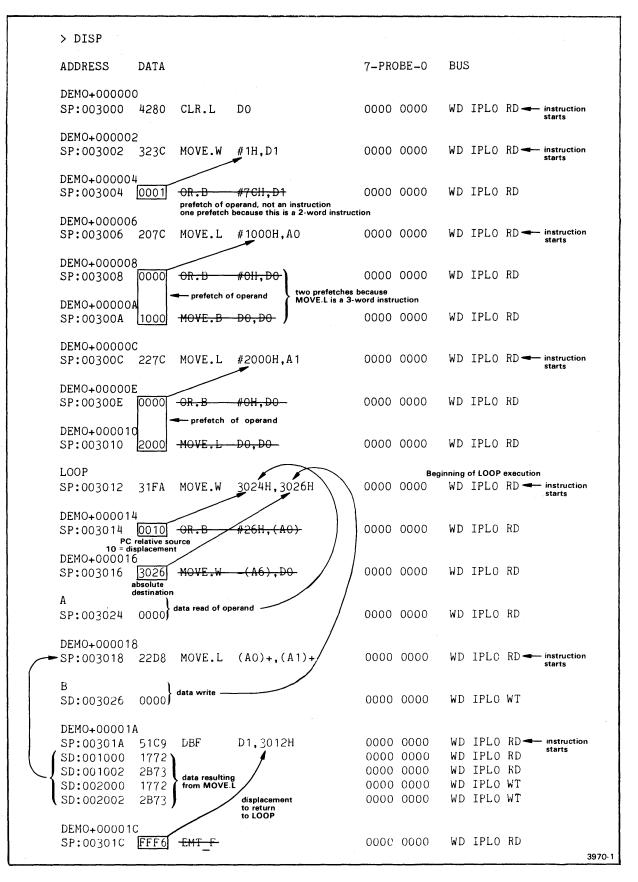

#### DISP---Display Contents of Acquisition Memory

The DISP command displays the contents of the TTA Acquisition Memory. This memory acquires a record of bus activity that occurred while your program was running.

Because the 68000 has a prefetch pipeline, and no fetch signal as discussed under "Special Considerations", the DISP command attempts to disassemble every word as an instruction, unless it is obviously not code. This ensures that every word that really is an instruction is disassembled. However, it also generates superfluous disassembly lines, which should be ignored.

The DISP command also displays the signal symbols shown in Table 7L-3 as part of its ADDRESS and BUS fields. When an INTA (interrupt acknowledge) cycle occurs, the notation **\*\***: will be displayed in place of an memory space designator, since the function code lines (FCx) do not show a valid memory space.

Figure 7L-3 shows a sample display of the following program lines when the program was run with TRA OFF:

CLR.L DO MOVE.W #1H,D1 MOVE.L #1000H,A0

| > <u>DISP</u> <cr:< th=""><th>&gt;</th><th></th><th></th><th></th><th></th></cr:<> | >    |        |           |           |            |

|------------------------------------------------------------------------------------|------|--------|-----------|-----------|------------|

| ADDRESS                                                                            | DATA |        |           | 7-PROBE-0 | BUS        |

| PROG+000000<br>SP:003000                                                           |      | CLR.L  | DO        | 0000 0000 | WD IPLO RD |

| PROG+000002<br>SP:003002                                                           |      | MOVE.W | #1H,D1    | 0000 0000 | WD IPLO RD |

| PROG+000004<br>SP:003004                                                           |      | OR.B   | #7CH,D1   | 0000 0000 | WD IPLO RD |

| PROG+000006<br>SP:003006                                                           | -    | MOVE.L | #1000H,A0 | 0000 0000 | WD IPLO RD |

| PROG+000008<br>SP:003008                                                           | -    | OR.B   | #OH,DO    | 0000 0000 | WD IPLO RD |

| PROG+000004<br>SP:00300A                                                           |      | MOVE.B | D0,D0     | 0000 0000 | WD IPLO RD |

Fig. 7L-3. Sample DISP display.

Note that the third, fifth, and sixth lines are superfluous. They result from disassembly on the operands of the other instructions.

Parameters, Commands, Displays

# TS---Display Status of TTA Triggers

In a TS display, the "bus" signals may not be identical to the parameters you enter with a BUS command or the B parameter of the EVE command. However, the signals displayed are functionally equivalent to the parameters you specified. The format of the display is as described in the 8500 Trigger Trace Analyzer Users Manual.

When an INTA (interrupt acknowledge) cycle occurs, the notation **\*\***: will be displayed in place of a memory space designator, since the function code lines (FCx) do not show a valid memory space.

Supervisor mode (S) will be indicated any time interrupt acknowledge (INTA) is shown.

#### SERVICE CALLS

Service calls (SVCs) allow your program to use many system capabilities of your 8540, 8550, or 8560. The 68000 emulator supports service calls in all three modes.

An SVC is invoked with any byte instruction which writes to the address range specified by the SVC command. The operand of the instruction directs the system to a specified memory address called the SRB pointer. (The pointer points to the SRB, the Service Request Block.) The SRB pointer tells the system where to find the data (stored in the SRB) that informs the system which service to perform. The SRB pointer and the SRB may be located in any of the four memory spaces.

Table 7L-4 shows the default addresses for the eight SRB pointers. You can use the SVC command to alter these addresses and their associated port values to suit your program requirements.

The memory space of the SRB vector can be specified with a memory space designator in the <u>address</u> parameter of the SVC command. The default memory space is the value of MEMSP S. If you do not use the SVC command to specify the SRB vector, the vector defaults to supervisor data space (SD).

Refer to the Command Dictionary of your System Users Manual for syntax and use of the SVC command.

#### SVC Address Range

The 68000 uses memory-mapped I/O. In order for a byte-write instruction to invoke a Service Call, its address operand (the "port") must be in the proper SVC address range. This range may be anywhere in memory; however, it is recommended that the range used be above address 400H. The default address range is F00000--F00007. You can change this range with the SVC command.

Multiple memory spaces are allowed for the "port" parameter in the SVC command. If memory space designators are omitted, the value of MEMSP M at the time the SVC command is executed is used. In the SVC command, the least significant digit of the "port" range will be set to 0 (i.e., OFFF7 will be rounded to OFFF0).

Example. The following command changes the SVC address range to 1000--1007 and causes the SRB vector to start at location F00 in Supervisor Data space.

# > SVC,,SD:F00 1000 <CR>

Then, to invoke SVC1, include the following instructions in your program:

MOVE.B D0,1007H NOP NOP

Table 7L-4 68000 Service Calls

| SVC ·   | Service Call (*a)                          |                                  | ¦ Default<br>⊦ Location of |

|---------|--------------------------------------------|----------------------------------|----------------------------|

| Number  | Mnemonic (*b) (*c)                         | Hexadecimal                      | SRB Pointer                |

| 1       | MOVE.B DO,(GEN.L)F00007H<br>  NOP<br>  NOP | 13C000F00007<br>  4E71<br>  4E71 | c0,C1,C2,C3                |

| 2       | MOVE.B DO,(GEN.L)F00006H<br>  NOP<br>  NOP | 13C000F00006<br>4E71<br>4E71     | C4,C5,C6,C7                |

| 3       | MOVE.B DO,(GEN.L)F00005H<br>NOP<br>NOP     | 13C000F00005<br>4E71<br>4E71     | C8,C9,CA,CB                |

| 4       | MOVE.B DO,(GEN.L)F00004H<br>NOP<br>NOP     | 13C000F00005<br>4E71<br>4E71     | CC,CD,CE,CF                |

| 5       | MOVE.B DO,(GEN.L)F00003H<br>  NOP<br>  NOP | 13C000F00004<br>4E71<br>4E71     | D0,D1,D2,D3                |

| 6       | MOVE.B DO,(GEN.L)F00002H<br>NOP<br>NOP     | 13C000F00002<br>4E71<br>4E71     | D4,D5,D6,D7                |

| 7       | MOVE.B DO,(GEN.L)F00001H<br>NOP<br>NOP     | 13C000F00001<br>4E71<br>4E71     | D8,D9,DA,DB                |

| . 8     | MOVE.B DO,(GEN.L)F00000H<br>  NOP<br>  NOP | 13C000F00000<br>4E71<br>4E71     | DC,DD,DE,DF                |

| (*a) Th | •                                          | 4E71                             | <br> <br>+<br>7)           |

(\*a) The default SVC address range (F00000--F00007) is assumed.(\*b) The MOVE.B instruction is used in this table. However,

any byte-write instruction can be used to invoke an SVC. (\*c) The 68000-specific assembler directive, GEN.L, generates

a long word address.

# NOTE

Include two NOP instructions immediately following the byte-write instruction. The NOPs fill the 68000 prefetch pipeline so that other instructions following the SVC will not be lost.

When SVCs are enabled, the addresses used by the SVCs should not be used in any write instruction except to invoke an SVC. A read instruction will not invoke an SVC.

7L-20

#### SRB Format

The 68000 emulator uses the LAS (Large Address Space) format for SRBs and SRB pointers. This format is described in the Service Calls section of your System Users Manual. Fig. 7L-4 illustrates the format of a 68000 SRB pointer for SVC1.

| + + + |

|-------|

|-------|

Fig. 7L-4. A 68000 SRB pointer located at CO--C3.

Table 7L-5 list the value of the Memory Space byte that corresponds to each memory space. For more information on memory spaces, refer to the heading "Memory Spaces" under "Special Considerations" later in this section.

|                                         | -+- |       |

|-----------------------------------------|-----|-------|

| Memory Space                            | ł   | Code  |

| ======================================= | :=: | ===== |

| current default                         | ł   | 0000  |

| UD:                                     | ł   | 0001  |

| UP:                                     | 1   | 0010  |

| SD:                                     | ł   | 0100  |

| SP:                                     | ł   | 1000  |

|                                         | •+• |       |

Table 7L-5 Encoding of the Memory Space Byte

#### SVC Demonstration

Figure 7L-5 lists a 68000 program that uses four SVC functions: Assign Channel, Read ASCII, Write ASCII, and Abort. The program's algorithm is explained in the Service Calls section of your System Users Manual, which also demonstrates a version of the program written in 8080A/8085A assembly language. Using the program in Fig. 7L-5, you can perform a parallel demonstration with the 68000 B Series Assembler and 68000 emulator.

68000 Service Calls

----

ے نہ ہونے ہو اور سے نے کا پر بنا کا پر کا کرنے کا تو کا ہے کا کا پر بنا کا پر بنا کا اور کا نے کا اور کا کا ت

| ; SSSSS | v v            | ссссс            |                                                         |

|---------|----------------|------------------|---------------------------------------------------------|

| ; S     | V V            |                  |                                                         |

| · ·     | V V<br>V V     |                  | DEMONSTRATION: 68000 EMULATOR                           |

| ; SSSSS |                | ccccc            |                                                         |

| ;       | ORG            | ОСОН             | ;Beginning of SRB vector.                               |

|         | LONG           | SRB1FN           | ;SRB1 LAS specification.                                |

|         | LONG<br>LONG   | SRB2FN<br>SRB3FN |                                                         |

|         | LONG           | SRB3FN<br>SRB4FN |                                                         |

|         | LONG           | SRB5FN           | •                                                       |

| ;       |                |                  | ;End of SRB vector.                                     |

|         | ORG            | 400H             | ;Set up SRB areas.                                      |

| ;       |                |                  | ;SRB1 = Assign 'CONI' to Channel 0.                     |

| SRB1FN  | BYTE           | 10H              | ;Assign                                                 |

| SRB1ST  | BYTE<br>BLOCK  | 00H<br>01H       | ; to Channel O.<br>;Status returned here.               |

|         | BLOCK          | 01H              | Reserved.                                               |

|         | BLOCK<br>WORD  | 02H<br>05H       | ;Reserved.<br>;Length of 'CONI' + <cr>.</cr>            |

|         | LONG           | CONI             | ;LAS pointer to 'CONI' + <cr>.</cr>                     |

|         |                |                  | ;End of SRB1.                                           |

| ;       |                |                  | ;SRB2 = Assign 'LPT' to Channel 1.                      |

| SRB2FN  | BYTE           | 10H              | Assign                                                  |

| SRB2ST  | BYTE<br>BLOCK  | 01H<br>01H       | ; to Channel 1.<br>;Status reserved here.               |

|         | BLOCK          | 01H              | Reserved.                                               |

|         | BLOCK<br>WORD  | 02H<br>04H       | ;Reserved.<br>;Length of 'LPT' + <cr>.</cr>             |

|         | LONG           | LPT              | ;LAS pointer to 'LPT' + <cr>.</cr>                      |

|         |                |                  | ;End of SRB2.                                           |

| ;       |                |                  | ;SRB3 = Read ASCII line from CONI (Channel 0).          |

| SRB3FN  | BYTE           | 01H<br>00H       | ;Read ASCII                                             |

| SRB3ST  | BYTE<br>BLOCK  | 00H<br>01H       | ; from Channel O.<br>;Status returned here.             |

|         | BLOCK          | 01H              | ;Reserved.                                              |

|         | BLOCK<br>WORD  | 02H<br>100H      | ;Byte count returned here.<br>;256 bytes in our buffer. |

|         | LONG           | BUFFER           | ;LAS pointer to our buffer.                             |

| ;       |                |                  | ;End of SRB3.                                           |

|         | -              | 0.001            | ;SRB4 = Write ASCII line to LPT (Channel 1).            |

| SRB4FN  | BYTE<br>BYTE   | 02H<br>01H       | ;Write ASCII<br>; to Channel 1.                         |

| SRB4ST  | BLOCK          | 01H              | ;Status returned here.                                  |

|         | BLOCK<br>BLOCK | 01H<br>02H       | ;Reserved.<br>;Byte count returned here.                |

|         | WORD           | 100H             | ;256 bytes in our buffer.                               |

|         | LONG           | BUFFER           | ;LAS pointer to our buffer.<br>;End of SRB4.            |

|         |                |                  |                                                         |

Fig. 7L-5. 68000 SVC demonstration program listing (part 1 of 2).

:SRB5 = Abort (Close all channels and terminate). SRB5FN BYTE 1FH :Abort. BLOCK OBH ;Reserved. ;End of SRB5. BUFFER BLOCK 100H :Our I/O area. 'CONI' ;ASCII of 'CONI' CONI ASCII BYTE ODH ; + <CR>. ;ASCII of 'LPT' LPT ASCII 'LPT' ODH ; + <CR>. BYTE :End of data definitions. Beginning of executable code. ; START 1000H ORG ;Entry point into program. MOVE.B DO. (GEN.L) OF 00007H ; Call SVC1 to NOP assign 'CONI' NOP to Channel 0. SRB1ST ;Check status to see if all went well. TST.B ;No? Stop everything. BNE ABORT DO,(GEN.L)OF00006H ;Call SVC2 to MOVE.B assign 'LPT' NOP NOP to Channel 1. ;Check status to see if all went well. TST.B SRB2ST ;No? Stop everything. BNE ABORT LOOP MOVE.B DO, (GEN.L) OF 00005H ; Call SVC3 to read NOP a line from 'CONI' : NOP into the buffer. TST.B ;Check status to see if all went well. SRB3ST ;No? Stop everything. BNE ABORT DO,(GEN.L)OF00004H ;Call SVC4 to write MOVE.B NOP a line to 'LPT' NOP from the buffer. TST.B ;Check status to see if all went well. SRB4ST BEQ LOOP ;Yes? Go back to read another line. ;No? Fall through to termination. DO,(GEN.L)OF00003H ;Call SVC5 ABORT MOVE.B NOP to do the abort. NOP END START ;End of the program.

Fig. 7L-5. 68000 SVC demonstration program listing (part 2 of 2).

This program shows the use of four service calls. The program's algorithm is explained in the Service Calls section of your System Users Manual. The program accepts a line of ASCII characters from the system terminal. Then, when it receives a RETURN character, the program writes the line to the line printer and accepts another line. (On the 8550, output to the line printer is buffered. No text is printed until the 8550's line printer buffer is full or the program ends.) To terminate the program, enter a CTRL-Z while the program is waiting for input.

# 68000 Service Calls

\_\_\_\_

Figure 7L-6 shows another way to code the executable portion of the program. By inserting the statement MOVE.L #OF00000,A1 at the beginning of the code, and the block of EQU statements at the end, you can save object code space and reference the SVCs symbolically.

| ;         | Beginni | ng of executabl | le code.                               |

|-----------|---------|-----------------|----------------------------------------|

| START     | ORG     | 1000H           | ;Entry point into program.             |

|           | MOVE.L  | #0F00000,A1     | ;Set a register to the SVC             |

|           |         | •               | ; trigger location.                    |

|           | MOVE.B  | DO,SVC1(A1)     | Call SVC1 to                           |

|           | NOP     |                 | ; assign 'CONI'                        |

|           | NOP     |                 | to Channel 0.                          |

|           | TST.B   | SRB1ST          | Check status to see if all went well.  |

|           | BNE     | ABORT           | No? Stop everything.                   |

|           | MOVE.B  | DO,SVC2(A1)     | Call SVC2 to                           |

|           | NOP     |                 | ; assign 'LPT'                         |

|           | NOP     |                 | ; to Channel 1.                        |

|           | TST.B   | SRB2ST          | ;Check status to see if all went well. |

|           | BNE     | ABORT           | ;No? Stop everything.                  |

| LOOP      | MOVE.B  | DO,SVC3(A1)     | ;Call SVC3 to read                     |

|           | NOP     |                 | ; a line from 'CONI'                   |

|           | NOP     |                 | ; into the buffer.                     |

|           | TST.B   | SRB3ST          | ;Check status to see if all went well. |

|           | BNE     | ABORT           | ;No? Stop everything.                  |

|           | MOVE.B  | DO,SVC4(A1)     | ;Call SVC4 to write                    |

|           | NOP     |                 | ; a line to 'LPT'                      |

|           | NOP     |                 | ; from the buffer.                     |

|           | TST.B   | SRB4ST          | ;Check status to see if all went well. |

|           | BEQ     | LOOP            | ;Yes? Go back to read another line.    |

|           |         |                 | ;No? Fall through to termination.      |

| ABORT     | MOVE.B  | DO,SVC5(A1)     | ;Call SVC5                             |

|           | NOP     |                 | ; to do the abort.                     |

|           | NOP     |                 |                                        |

|           |         |                 | ;Define SVC symbols.                   |

| SVC1      | EQU     | 7               |                                        |

| SVC2      | EQU     | 6               |                                        |

| SVC3      | EQU     | 5               |                                        |

| SVC4      | EQU     | 4               |                                        |

| SVC5<br>; | EQU     | 3               |                                        |

| ,         | END     | START           | ;End of the program.                   |

Fig. 7L-6. Alternate executable code for SVC demonstration program.

#### SPECIAL CONSIDERATIONS

Some of the characteristics of the 68000 microprocessor greatly affect the behavior and appearance of several commands; in particular, BK, TRA, and DISP. These characteristics are discussed in the following paragraphs, and in much greater detail in the reprints at the back of this section.

# Fetching and the Prefetch Pipeline

The 68000 microprocessor has a prefetch pipeline which speeds up the instruction fetch-decode-execute process. The processor does not, however, have a fetch signal available. These two factors combine to cause differences in many of the emulator's displays.

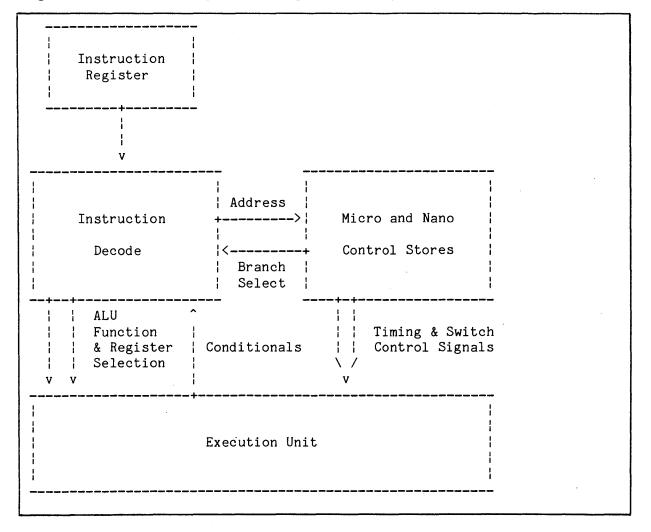

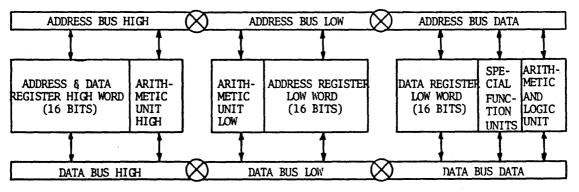

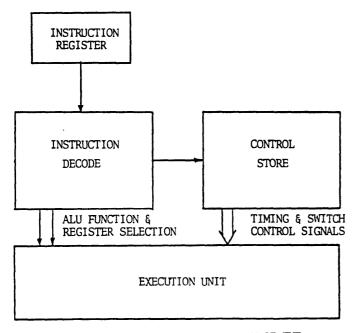

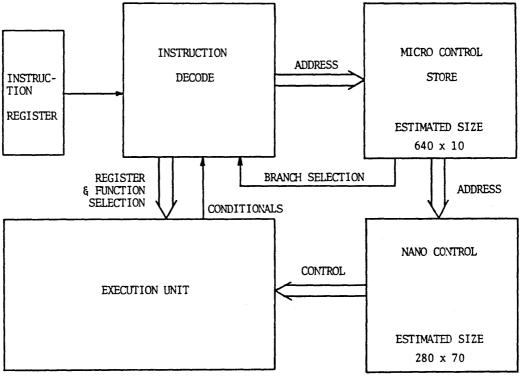

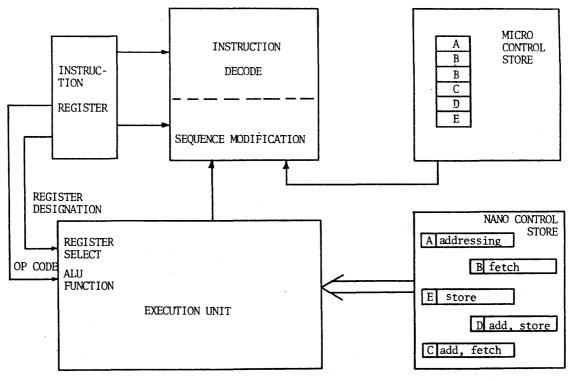

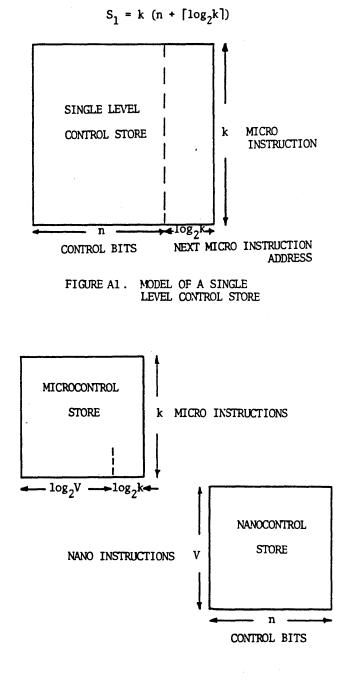

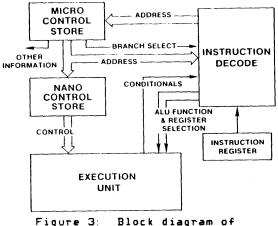

Figure 7L-7 shows a simplified diagram of the pipeline.

Fig. 7L-7. 68000 instruction pipeline block diagram.

The pipeline consists of an Instruction Register, an Instruction Decoder, and an Execution Unit. The Instruction Register holds the most recently fetched instruction word. The Instruction Decoder, using the Micro and Nano Control Stores, decodes the instruction. When the instruction reaches the Execution Unit, it is executed.

It is the responsibility of the instruction that is executing to ensure two things before it finishes its execution:

- 1. that the next instruction word is accessed with sufficient time for complete decoding by the end of the current instruction; and

- 2. that the instruction word following the next instruction is fetched by the end of the current instruction

Since there is no instruction fetch signal, the only time the emulator knows that an instruction has been fetched into the instruction pipeline is when it sees the appropriate values on the bus. The emulator <u>doesn't</u> know whether the instruction is actually executing from this information.

#### Interrupts

The 68000 has seven interrupt levels. Higher-numbered interrupts have higher priority. The level 7 interrupt is a non-maskable interrupt (NMI).

Interrupts are controlled by the three interrupt mask bits (I2-I0) in the Status Register.

When an interrupt request is made, the 68000 compares the level of the interrupt with the interrupt mask. If the new interrupt has a level higher than the mask setting, the interrupt is recognized. When this occurs, the 68000 has to stack its Program Counter and Status Register so that it can return to the interrupted task after the interrupt has been processed.

This stacking is done in the following time sequence: First, PC(L) is stacked, then the interrupt is acknowledged. Next, the status register is stacked, and last, PC(H). Because PC(L) is stacked before the emulator knows that an interrupt has occurred, this Supervisor Data write always appears on a DISP display of your program run.

<u>Program example</u>. The program example in Fig. 7L-8 is used to illustrate the effects of the 68000 characteristics previously described.

\_\_\_\_\_\_

The program was loaded beginning at address 3000H. After moving values into three registers, the program enters the LOOP and executes it twice. The two NOPs are then executed, followed by the branch to SELF. Execution of this instruction would continue indefinitely, but breakpoint 1 was set at SELF before the program was executed.

| LOC<br>SEI | MOVE.L<br>DBF<br>NOP<br>NOP<br>.F BT | DO<br>#1H,D1<br>#1000H,A0<br>#2000H,A1<br>A,B<br>(A0)+,(A1)+<br>D1,LOOP<br>SELF |  |

|------------|--------------------------------------|---------------------------------------------------------------------------------|--|

| A          | BLOCK                                | 02H                                                                             |  |

| В          | BLOCK                                | 02H                                                                             |  |

Fig. 7L-8. Program example.

Figures 7L-9 and 7L-10 use the DISP command to show the contents of the TTA acquisition memory for this program run with TRA OFF and TRA ON, respectively.

Refer to the following comments while examining these two figures:

Each of the superfluous disassembly lines is crossed out. These lines resulted from disassembly of the operand(s) in the preceding instruction. Boxes are drawn around the operands in the object code field, and arrows show where they came from in the preceding instruction.

Data reads and data writes from A, B, and the MOVE.L (A0)+,(A1)+ instruction are interleaved with fetches from the instruction stream.

The effects of prefetching appear in the figures. Notes in each figure indicate where the instructions start, and which ones were actually executed.

At the end of both figures, you can see the next PC(L) stacked in SD space before the interrupt acknowledge to the break interrupt occurred. In Figure 7L-10, where TRA is ON, the display shows that PC(L) was also stacked each time an interrupt to print a trace line occurred.

The run with TRA ON terminated two instructions before the run with TRA OFF, because of the decrease in execution speed with TRA ON. When TRA was OFF, the two additional instructions reached the Execution Unit before the break interrupt occurred. Note that with TRA ON, the instruction on which the breakpoint was set was not executed.

Fig. 7L-9. Example program run with TRA OFF (part 1 of 2).