Xerox 550 Computer

**Reference Manual**

Xerox Corporation 701 South Aviation Boulevard El Segundo, California 90245 213 679-4511

# Xerox 550 Computer

# **Reference Manual**

FIRST EDITION

90 30 77A

February 1974

Price: \$6.50

# **RELATED PUBLICATIONS**

| Title                                      | Publication No. |

|--------------------------------------------|-----------------|

| Xerox Symbol/LN,OPS Reference Manual       | 90 17 90        |

| Xerox Meta-Symbol/LN,OPS Reference Manual  | 90 09 52        |

| Xerox Macro-Symbol/LN,OPS Reference Manual | 90 15 78        |

<u>Manual Content Codes:</u> BP – batch processing, LN – language, OPS – operations, RP – remote processing, RT – real-time, SM – system management, TS – time-sharing, UT – utilities.

ALL SPECIFICATIONS SUBJECT TO CHANGE WITHOUT NOTICE

# CONTENTS

### 1. XEROX 550 COMPUTER SYSTEM

| Introduction                    | 1 |

|---------------------------------|---|

| General Characteristics         | 1 |

| Standard and Optional Features  | 3 |

| General-Purpose Features        | 3 |

| Time-Sharing Features           | 4 |

| Real-Time Features              | 5 |

| Multiuse Features               | 6 |

| Multiprocessor Features         | 6 |

| Multiprocessor Interlock        | 6 |

| Multiport Memory System         | 7 |

| Manual Partitioning Capability  | 7 |

| Multiprocessor Control Function | 7 |

| Shared Input/Output             | 7 |

|                                 |   |

## 2. SYSTEM ORGANIZATION

| Processor Clusters                        | _ 8  |

|-------------------------------------------|------|

| System Control Processor                  | _ 8  |

| Basic Processor                           |      |

| General Registers                         |      |

| Memory Control Storage                    |      |

| Computer Modes                            | _ 11 |

| Information Format                        |      |

| Information Boundaries                    |      |

| Instruction Register                      |      |

| Main Memory                               | 14   |

| Memory Unit                               | 14   |

| Maintainability and Performance           | _ 16 |

| Virtual and Real Memory                   |      |

| Types of Addressing                       | _ 19 |

| Memory Address Control                    | _ 26 |

| Program Status Words                      | 28   |

| Centralized Interrupts                    | _ 30 |

| States of an Interrupt Level              | _ 30 |

| Dialogue Between the Basic Processor and  |      |

| the Interrupt System During an Interrupt- |      |

| Entering Sequence                         | _ 32 |

| Dialogue During an Interrupt-Exiting      |      |

| Sequence                                  | _ 32 |

| Physical Organization                     |      |

| Interrupt Groups                          |      |

| Control of the Interrupt System           |      |

| Single-Instruction Interrupts             | 36   |

| Trap System                               |      |

| Trap Entry Sequence                       | 36   |

| Trap Addressing                           | _ 36 |

| Trap Condition Code                       | 39   |

| Nonallowed Operation Trap                 |      |

| Push-Down Stack Limit Trap                |      |

| Fixed-Point Overflow Trap                 |      |

| Floating-Point Arithmetic Fault Trap      |      |

| Watchdog Timer Runout Trap                |      |

| Programmed Trap                           |      |

| CALL Instruction Trap                     |      |

| Hardware Error Trap                       |      |

|                                           |      |

| Instruction Exception Trap    | 43 |

|-------------------------------|----|

| Power On Trap                 | 44 |

| Power Off Trap                | 44 |

| Processor Detected Fault Flag | 44 |

| Register Altered Bit          | 45 |

#### 3. INSTRUCTION REPERTOIRE

| Load/Store Instructions                    |          |

|--------------------------------------------|----------|

| LI                                         |          |

| LB                                         |          |

| LH                                         |          |

| LW                                         |          |

| LD                                         |          |

| LCH                                        |          |

|                                            |          |

| LCW                                        |          |

|                                            |          |

| LCD                                        |          |

| LAD                                        |          |

| LAS                                        |          |

| LS                                         |          |

| LM                                         |          |

|                                            |          |

|                                            |          |

|                                            |          |

| XW                                         |          |

| STB                                        |          |

| STH                                        |          |

| STW                                        |          |

| STD                                        |          |

| STS                                        |          |

| STM                                        | 55       |

| STCF                                       |          |

| Analyze/Interpret Instructions             |          |

|                                            |          |

| INT<br>Fixed-Point Arithmetic Instructions |          |

| AI                                         |          |

|                                            |          |

| AH<br>AW                                   |          |

| AW<br>AD                                   |          |

|                                            |          |

| SH                                         |          |

| SW                                         |          |

| SD                                         |          |

| MI                                         |          |

| MH<br>MW                                   |          |

|                                            |          |

| DH                                         | 63<br>63 |

| DW<br>AWM                                  |          |

|                                            |          |

| MTB                                        | 64<br>64 |

|                                            |          |

| MTW                                        |          |

| Comparison Instructions                    |          |

| СІ                                         |          |

| Св                                         | 66       |

| СН                                             | 66        |

|------------------------------------------------|-----------|

| CW                                             | 67        |

| CD                                             |           |

| CS                                             | 67        |

| CLR                                            |           |

| CLM                                            |           |

| Logical Instructions                           |           |

| OR                                             |           |

| EOR                                            |           |

| AND                                            |           |

| Shift Instructions                             |           |

| S                                              |           |

| Floating-Point Shift                           |           |

| SF                                             |           |

| Conversion Instructions                        |           |

| CVA                                            |           |

| CVS                                            |           |

| Floating-Point Arithmetic Instructions         |           |

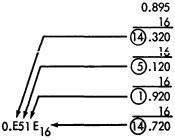

| Floating-Point Numbers                         | /4        |

| Floating-Point Add and Subtract                |           |

| Floating-Point Multiply and Divide             | //        |

| Condition Codes for Floating–Point             |           |

| Instructions                                   |           |

| FAS                                            |           |

| FAL                                            |           |

| FSS                                            |           |

| FSL                                            |           |

| FMS                                            |           |

| FML                                            |           |

| FDS<br>FDL                                     |           |

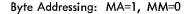

| FDL<br>Push-Down Instructions (Non-Privileged) |           |

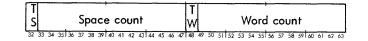

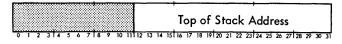

| Stack Pointer Doubleword (SPD)                 |           |

| Push-Down Condition Code Settings              | / 7<br>00 |

| PSW                                            |           |

| PLW                                            |           |

| PSM                                            |           |

| PLM                                            |           |

| MSP                                            |           |

| Push-Down Instructions (Privileged)            |           |

| Status Stack Pointer Doubleword                |           |

| PSS                                            |           |

| PLS                                            |           |

| Execute/Branch Instructions                    |           |

| Nonallowed Operation Trap During               |           |

| Execution of Branch Instruction                | 90        |

| EXU                                            |           |

| BCS                                            |           |

| BCR                                            |           |

| BIR                                            | 91        |

| BDR                                            | 91        |

| BAL                                            | 92        |

| CALL Instructions                              |           |

| CAL1                                           | 92        |

| CAL2                                           | 92        |

| CAL3                                           | 92        |

| CAL4                                           | 93        |

| Control Instructions                           | 93        |

| Program Status Words                           | 93        |

| LPSD                                           |           |

| XPSD                                           | 94        |

| LRP                                            | 96        |

| MMC                                            |           |

| Loading the Memory Map                   | 98  |

|------------------------------------------|-----|

| LMAP                                     |     |

| LMAPRE                                   | 98  |

| Loading the Access Protection Controls   | 98  |

| Memory Write Protection Locks            | 99  |

| LLÓCKS                                   | 99  |

|                                          | 99  |

| Interruption of MMC                      | 100 |

| Memory Access Traps by MMC Instruction   | 100 |

| LRA                                      |     |

| LMS                                      | 101 |

| WAIT                                     | 103 |

| RD                                       | 103 |

| Read Direct, Internal Basic Processor    |     |

| Control (Mode 0)                         | 104 |

| Read Direct, Interrupt Control (Mode 1)  | 105 |

| Read Direct (Mode 9)                     | 105 |

| WD                                       | 107 |

| Write Direct, Internal Basic Processor   |     |

| Control (Mode 0)                         |     |

| Write Direct, Interrupt Control (Mode 1) | 109 |

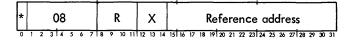

| Input/Output Instructions                | 110 |

| Overall Characteristics                  | 110 |

| I/O Status Information                   | 110 |

| SIO                                      | 118 |

| TIO                                      | 119 |

| TDV                                      | 120 |

| HIO                                      | 121 |

| RIO                                      |     |

| POLP                                     | 122 |

| POLR                                     | 122 |

| AIO                                      | 123 |

# 4. INPUT/OUTPUT OPERATIONS

125

| External DIO Interface                    | 125 |

|-------------------------------------------|-----|

| Multiplexor Input/Output Processor (MIOP) |     |

| Device Controllers                        | 125 |

| Input/Output Processor (IOP) Fundamentals | 126 |

| Command List                              | 126 |

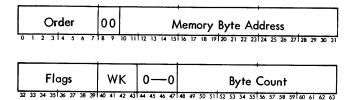

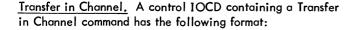

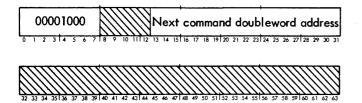

| Operational IOCD                          | 126 |

| I/O Operation Phases                      | 131 |

| Preparation Phase                         | 131 |

| Initiation Phase                          | 131 |

| Fetching Phase                            | 131 |

| Execution Phase                           | 132 |

| Termination Phase                         | 134 |

|                                           |     |

# 5. OPERATIONAL CONTROL

135

| External Control Subsystem         | 135 |

|------------------------------------|-----|

| Centralized System Control         |     |

| Control Console Devices            | 135 |

| Control Commands                   | 136 |

| Operator Control Commands          |     |

| Z <sup>c</sup> I                   | 137 |

| Z <sup>c</sup> SSW                 |     |

| Z <sup>c</sup> SS <sup>#</sup>     | 137 |

| Z <sup>c</sup> LDN <sup>####</sup> | 137 |

| Z <sup>c</sup> RSY                   | 138 |

|--------------------------------------|-----|

| Z <sup>C</sup> RBP                   |     |

| Z <sup>c</sup> RIO                   | 138 |

| Z <sup>c</sup> HLT                   |     |

| Z <sup>c</sup> RUN                   | 139 |

| Diagnostic Control Commands          | 139 |

| P <sup>°C</sup>                      | 139 |

| /                                    |     |

| +                                    | 139 |

|                                      | 139 |

| Μ                                    |     |

| L                                    |     |

| R                                    | 140 |

| I                                    |     |

| RUB OUT                              | 140 |

| S                                    | 140 |

| G                                    |     |

| Х                                    |     |

| Maintenance Control Commands         | 141 |

| Z <sup>c</sup> CLK                   |     |

| k                                    |     |

| Z°C##                                |     |

| Z°E##                                | 142 |

| Z <sup>c</sup> KIL                   | 142 |

| Z <sup>c</sup> MM0                   |     |

| Z <sup>c</sup> MM1                   |     |

| Z <sup>c</sup> MM2                   |     |

| Z <sup>c</sup> MM3                   |     |

| Z <sup>c</sup> MM4                   |     |

| Z <sup>c</sup> MM5                   |     |

| Z <sup>c</sup> MM6                   |     |

| Z <sup>c</sup> MM7                   |     |

| Z <sup>c</sup> MM8                   |     |

| Z <sup>c</sup> MM9                   |     |

| ∠°MMA                                |     |

| Z <sup>c</sup> LDS####               |     |

| Z <sup>c</sup> LDT                   |     |

| Z <sup>c</sup> T                     |     |

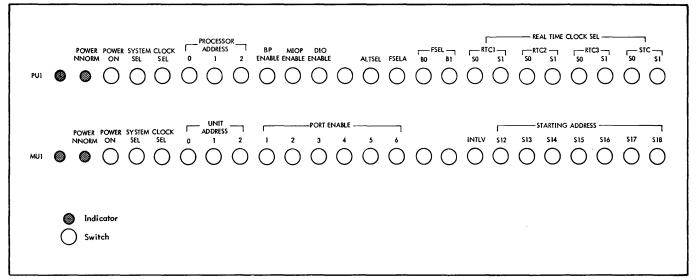

| System Control Panel                 | 144 |

| Operating Procedures and Information |     |

| operating recederes and internation  |     |

| 6. | System Configuration Control | 150 |

|----|------------------------------|-----|

|    |                              |     |

Configuration Control Panel (CCP) \_\_\_\_\_\_ 150

# APPENDIXES

| Α. | REFERENCE TABLES | 155 |

|----|------------------|-----|

| А. | REFERENCE TABLES | 100 |

| Standard Symbols and Codes             | 155 |

|----------------------------------------|-----|

| Standard Character Sets                | 155 |

| Control Codes                          | 155 |

| Special Code Properties                | 155 |

| Standard 8-Bit Computer Codes (EBCDIC) | 156 |

|    | Standard 7-Bit Communication Codes (ANSCII) | _ 156 |

|----|---------------------------------------------|-------|

|    | Standard Symbol-Code Correspondences        | 157   |

|    | Hexadecimal Arithmetic                      | 161   |

|    | Addition Table                              | . 161 |

|    | Multiplication Table                        | . 161 |

|    | Table of Powers of Sixteen <sub>10</sub>    |       |

|    | Table of Powers of Ten <sub>16</sub>        | 162   |

|    | Hexadecimal–Decimal Integer Conversion      |       |

|    | Table                                       | 163   |

|    | Hexadecimal-Decimal Fraction Conversion     |       |

|    | Table                                       | 169   |

|    | Table of Powers of Two                      | 173   |

|    | Mathematical Constants                      | 173   |

| Β. | GLOSSARY OF SYMBOLIC TERMS                  | 174   |

| с. | FAULT STATUS REGISTERS                      | 177   |

# FIGURES

| ١.  | A Xerox 550 Computer System                                                    | _ 9   |

|-----|--------------------------------------------------------------------------------|-------|

| 2.  | The Basic Processor                                                            | _ 10  |

| 3.  | Information Boundaries                                                         | _ 13  |

| 4.  | Main Memory                                                                    | _ 15  |

| 5.  | Addressing Logic                                                               | 18    |

| 6.  | Index Displacement Alignment (Real and<br>Virtual Addressing Modes)            | _ 21  |

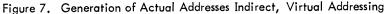

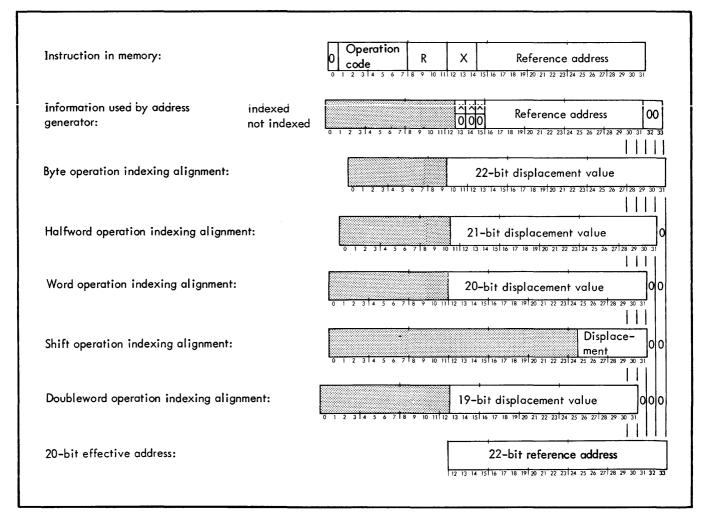

| 7.  | Generation of Actual Addresses Indirect,<br>Virtual Addressing                 | _ 22  |

| 8.  | Index Displacement Alignment (Real–<br>Extended Addressing)                    | _ 23  |

| 9.  | Generation of Effective Virtual Address<br>(Indirect Real-Extended Addressing) | _ 24  |

| 10. | Operational States of an Interrupt Level                                       | . 31  |

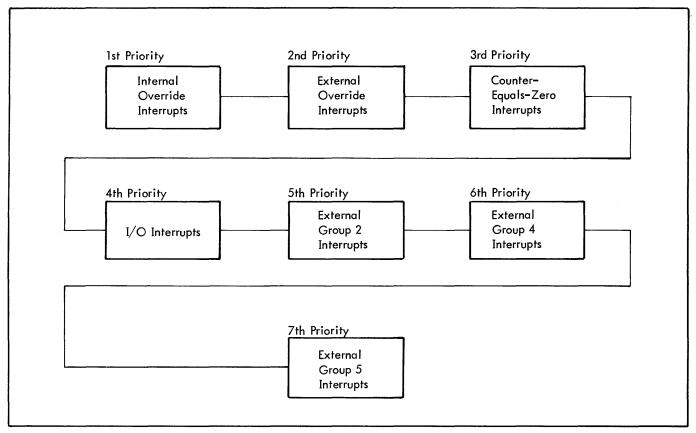

| 11. | Interrupt Priority Chain                                                       | . 34  |

| 12. | Typical 28–Word Portion of Memory Stack<br>for PSS and PLS                     | . 86  |

| 13. | Formats of I/O Instructions                                                    | . 111 |

| 14. | Bootstrap Loader                                                               | 138   |

| 15. | System Control Panel                                                           | . 145 |

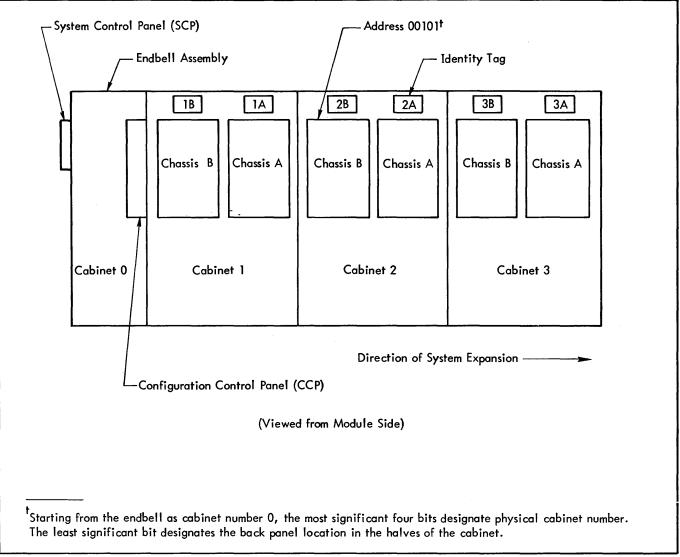

| 16. | Chassis Physical Configuration                                                 | . 151 |

| 17. | Sample Rows of CCP Switches                                                    | 151   |

# **TABLES**

| 1.  | Basic Processor Operating Modes and<br>Addressing Cases         | . 25 |

|-----|-----------------------------------------------------------------|------|

| 2.  | Interrupt Locations                                             | . 33 |

| 3.  | Summary of Trap Locations                                       | . 37 |

| 4.  | TCC Setting for Instruction Exception Trap X'4D'                | . 44 |

| 5.  | Registers Changed at Time of a Trap Due to an<br>Operand Access | 45   |

| 6.  | ANALYZE Table for Operation Codes                               | . 56 |

| 7.  | Floating-Point Number Representation                            | 75   |

| 8.  | Condition Code Settings for Floating–Point<br>Instructions      | 78   |

| 9.  | Status Word 0                                                   | 102  |

| 10. | Status Word 1                                                   | 103  |

| 11. | Read Direct Mode 9 Status Word                                  | 105  |

| 12. | Chassis Type Assignments                                        | 106  |

| 13. | Description of I/O Instructions                                 | 111  |

| 14. | I/O Status Information (Register R)                             | 113  |

| 15.  | Device Status Byte (Register R or Ru1)<br>(SIO, TIO, and HIO only)               | _114  |

|------|----------------------------------------------------------------------------------|-------|

| 16.  | Operational Status Byte (Register Ru1)                                           | _115  |

| 17.  | Status Response Bits for I/O Instructions                                        | _116  |

| 18.  | IOP Status Byte                                                                  | _117  |

| 19.  | Status Response Bits for AIO Instruction                                         | _ 118 |

| 20.  | I/O Address (AIO Response)                                                       | _ 118 |

| 21.  | Event Messages                                                                   | _ 136 |

| 22.  | Diagnostic Control (P-Mode) Commands                                             | _ 140 |

| 23.  | Bit Assignments and Description, Processor<br>Control Word, Register Q30 (X'1E') | _ 148 |

| 24.  | Bit Assignments, Address Compare Register<br>Q31 (X1'F')                         | _ 149 |

| 25.  | Functions of Processor Cluster Configuration<br>Control Panel Row                | _ 152 |

| 26.  | Functions of Memory Unit Configuration<br>Control Panel Row                      | _ 153 |

| C-1. | Fault Status Registers                                                           | _ 177 |

| C-2. | Memory Unit Status Register                                                      | _ 178 |

# 1. XEROX 550 COMPUTER SYSTEM

#### INTRODUCTION

The Xerox 550 general-purpose, digital, computer system accommodates a variety of scientific, business, real-time, and time-sharing applications. A system includes system control, basic processor, I/O processor, and main memory (up to 256K words) with two ports. Each major system element performs asynchronously with respect to other elements.

The basic system can be readily expanded. Memory access paths can be increased from the basic two ports to a maximum of six ports. Input/output capability can be increased by adding more input/output processors (IOPs), device controllers, and peripheral devices.

The basic processor (BP) has an extensive instruction set that includes floating-point instructions.

The multiaccess memory units, with interleaving, afford a high level of system performance. Main memory can be expanded in 16K word increments to a maximum of 256K words. Address interleaving may be performed between memory units of like size. The number of ports to each memory unit can be expanded to allow independent access to memory by up to six "processor clusters" (i.e., functional groups).

Processor clusters are the grouping of two or more functions (such as a basic processor, an I/O processor, and interfaces) on a common bus. Clustering permits processors to share common facilities, e.g., buses and memory interfaces. Therefore, the hardware is less redundant, hence less complex, resulting in more reliability at a lower cost. There are multiple combinations of functional groups from which to select.

Existing Sigma 5-9 programs may be run on the system. The upward compatibility of the comprehensive, modular software (assemblers, compilers, mathematical and utility routines, and application packages) eliminates reprogramming.

Features have been incorporated in this design to enhance overall system reliability, maintainability, and availability. Centralized switches for system repartitioning may permit faulty units, or an entire subsystem, to be isolated for diagnosis or repair while the primary system continues operation. Parity checking is performed on each byte of information for most system interfaces and internal control signals. Most failed instructions are automatically retried, and uninterrupted processing continues. The only apparent effect may be an entry in the error log. In the event an error is irrecoverable, there are error storage registers that return complete data on the fault and the status of the system at that point.

## **GENERAL CHARACTERISTICS**

The following system features and characteristics permit efficient operation in general-purpose, multiprocessor, time-sharing, real-time, and multiuse environments:

- Word-oriented memory (32-bit word plus parity bit per byte) that can be addressed and altered as byte (8-bit), halfword (2-byte), word (4-byte), and doubleword (8-byte) quantities.

- Memory expandable to 256K words (K = 1024) in modular units of 16K words each.

- Indirect addressing with or without postindexing.

- Displacement index registers, automatically selfadjusting for all data sizes.

- Immediate operand instructions for greater storage efficiency and increased speed.

- Four blocks of 16 general-purpose registers for addressing, indexing, and accumulating. Multiple registers permit rapid context switching.

- Hardware memory mapping, which virtually eliminates memory fragmentation and provides dynamic program relocation.

- Memory access protection for system and information security and protection.

- Memory write protection within memory units to prevent inadvertent destruction of critical areas of memory from any processor cluster.

- Watchdog timer to assure nonstop operation.

- Real-time priority interrupt system with automatic identification and priority assignment, fast response time, and 14 internal and up to 48 external levels that can be individually armed, enabled, and triggered by program control.

- Instructions with long execution times can be interrupted.

- Automatic traps for error or fault conditions, with masking capability and maximum recoverability, under program control.

- Power fail-safe for automatic shutdown and resumption of processing in event of power failure.

- Multiple interval timers with a choice of resolutions for independent time bases.

- Privileged instruction logic for program integrity in multiuse environments.

- Extensive instruction set that includes:

- Byte, halfword, word, and doubleword operations.

- Use of all memory-referencing instructions for register-to-register operations, with or without indirect addressing and postindexing, and within normal instruction format.

- Multiple register operations.

- Fixed-point integer arithmetic operations in halfword, word, and doubleword modes.

- Immediate operand instructions.

- Floating-point hardware operations in short and long formats with significance, zero, and normalization control and checking, all under full program control.

- Full complement of logical operations (AND, OR, exclusive OR).

- Comparison operations, including compare between limits (with limits in memory or in registers).

- Call instructions that permit up to 64 dynamically variable, user-defined instructions, and allow a program access to operating system functions without operating system intervention.

- Push-down stack operations (hardware implemented) of single or multiple words, with automatic limit checking, for dynamic space allocation, subroutine communication, and recursive routine capability.

- Automatic conversion operations, including binary/ BCD and any other weighted-number systems.

- Analyze instruction that facilitates effective address computation.

- Interpret instruction that increases speed of interpretive programs.

- Shift operations (left and right) of word or doubleword, including logical, circular, arithmetic, searching shift, and floating-point modes.

- Built-in reliability and maintainability features that include:

- Extensive error logging. When a fault is detected, system status and fault information are available for program retrieval and logging for subsequent analysis.

- Full parity checking on all data and addresses communicated in either direction on buses between memory units and processors, providing fault

detection and location capability to permit the operating system or diagnostic program to quickly determine a faulty unit.

Address stop feature that permits operator or maintenance personnel to:

Stop on any instruction address.

Stop on any memory reference address.

Stop when any word in a selected page of memory is referenced.

- Traps that provide for detection of a variety of fault conditions, designed to enable a high degree of system recoverability.

- Partitioning features that enable system reconfiguration via a centralized Configuration Control Panel. Units may be partitioned from the system by selectively disabling them from buses (assuming other system facilities can handle the additional load). Thus, faulty units, processors, devices, or an alternate system can be isolated from the operational system to enable diagnosis or repair while the primary system continues operation.

- Independently operating I/O system with the following features:

- Direct input/output (READ DIRECT, WRITE DIRECT instructions) for transfer of 32-bit words between the specified general register and an external device; a 16-bit address is transferred for selection and control purposes; and each transfer is under direct program control.

- Up to five independent I/O processor clusters (restricted only by the maximum number of 6 ports).

- Multiplexor I/O processors (MIOPs) (up to 3 per I/O cluster), each providing for simultaneous operation of up to 16 devices per processor.

- Data chaining for gather-read and scatter-write operations.

- Command chaining for multiple record operations.

- Write lock protect feature within memory unit for positive protection from all processors storing into memory.

- Comprehensive modular software that is program compatible with Sigma 5-9 computers:

- Expands in capability and speed as system grows.

- Operating system: Control Program Real-Time (CP-R).

- Language processors and utilities and applications software for both commercial and scientific users.

- Peripheral equipment includes:

- Card equipment: Reading speeds up to 1500 cards per minute; punching speed of 100 cards per minute; intermixed binary and EBCDIC card codes.

- Line printers: Fully buffered with speeds up to 1250 lines per minute; 132 print positions with character sets containing 64 or 95 characters.

- Magnetic tape units: 9-track systems, single or dual density (1600 or 800/1600 BPI), industrycompatible; high-speed, automatic loading units operating at 125 inches per second with transfer rates up to 200,000 bytes per second; and at 75 inches per second with transfer rates up to 120,000 bytes per second.

- Rapid Access Data (RAD) and disk files: RAD capacity of 2.9 million bytes, with a transfer rate of 750,000 bytes per second; disk capacities in increments of 49 million bytes per unit with a transfer rate of 312,500 bytes per second.

- Keyboard printers: 10 characters per second.

- Data communications equipment: Complete line of character-oriented, message-oriented, and procedure-oriented equipment to connect remote user terminals (including remote batch) to the computer center via common carrier lines and local terminals directly.

## STANDARD AND OPTIONAL FEATURES

A basic system has the following standard features:

- A basic processor (BP) that includes:

- Full instruction set

- Memory map with access protection

- Register blocks (4)

- Multiplexor Input/Output Processor (MIOP) with:

- 16 subchannels

- 1- or 4-byte interface

- Input/Output Adapter

- Memory unit that includes:

- Dual port access

- Memory write lock protection

- A system control processor that includes:

- Real-time clocks (4)

- Internal interrupts (14)

- Power fail-safe detection

- External Control Subsystem (ECS)

- System Control Panel (SCP)

- Configuration Control Panel (CCP)

- Local and remote assist facility

- Error detection facilities

- Diagnostics

A system may have the following optional features:

- System Control Processor options:

- Up to 48 external priority interrupts (in groups of 12)

- External Direct Input/Output interface (DIO)

- Memory options:

- Memory expansion up to 256K words

- Up to 4 additional access ports (in sets of 2).

- Input/Output options:

- Multiple I/O clusters<sup>T</sup>.

- Up to 3 additional MIOPs, each with 16 subchannels, per cluster.

- One Input/Output Adapter (for one MIOP) per cluster.

# **GENERAL-PURPOSE FEATURES**

General-purpose computing applications are characterized by emphasis on computation and internal data handling.

<sup>&</sup>lt;sup>t</sup>The aggregate of processor clusters is restricted by the maximum memory port limitation of 6.

Many operations are performed in floating-point format. Other typical characteristics include high system input/ output transfer rates.

General-purpose features are described in the following paragraphs.

Floating-Point Hardware. Both short (32-bit) and long (64-bit) formats are available in the floating-point instructions. Under program control, the user may select optional zero checking, normalization, floating-point rounding and significance checking. Significance checking permits use of short floating-point format for high processing speed and storage economy and of long floatingpoint format when loss of significance is detected.

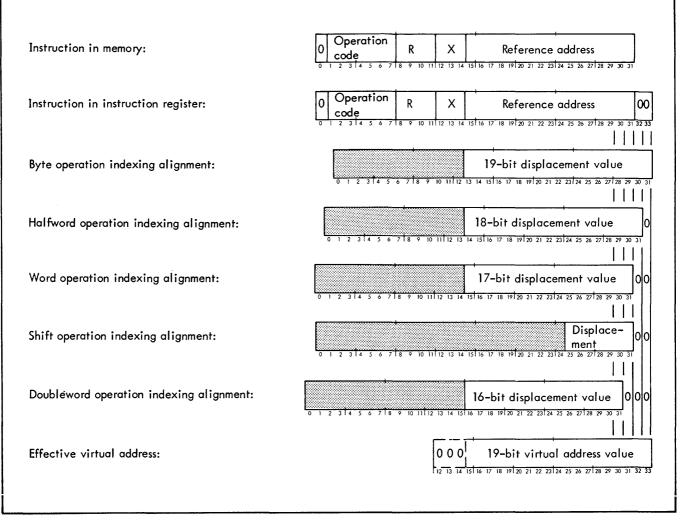

Indirect Addressing. Indirect addressing facilitates table linkages and permits keeping data sections of a program separate from procedure sections for ease of maintenance.

Displacement Indexing. Indexing by means of a "floating" displacement permits accessing a desired unit of data without considering its size. The index registers automatically align themselves appropriately; thus, the same index register may be used on arrays with different data sizes. For example, in a matrix multiplication of any array of full word, single-precision, fixed-point numbers, the results may be stored in a second array as double-precision numbers, using the same index quantity for both arrays. If an index register contains the value of k, then the user always accesses the kth element, whether it is a byte, halfword, word, or doubleword. Incrementing by various quantities according to data size is not required; instead, incrementing is always by units in a continuous array table regardless of the size of data element used.

<u>Instruction Set.</u> The instructions permit short, highly optimized programs to be written. These are rapidly assembled and minimize both program space and execution time.

<u>Conversion Instructions.</u> Two generalized conversion instructions provide for bidirectional conversions between internal binary and any other weighted number system, including BCD.

<u>Call Instructions.</u> These four instructions permit handling up to 64 user-defined subroutines, as if they were built-in machine instructions. Call instructions also gain access to specified operating system services without requiring its intervention. Interpret Instruction. The Interpret instruction simplifies and speeds interpretive operations such as compilation, thus reducing space and time requirements for compilers and other interpretive systems.

<u>Four-Bit Condition Code</u>. Checking results is simplified by automatically providing information on almost every instruction execution, including indicators for overflow, underflow, zero, minus, and plus, as appropriate, without requiring an extra instruction execution.

Direct Input/Output (DIO). Direct input/output facilitates in-line program control of asynchronous or specialpurpose devices. This feature permits information to be transmitted directly to or from general-purpose registers.

Multiplexor Input/Output Processor (MIOP). Once initialized, I/O processors operate independently of the basic processor, freeing it to provide faster response to system needs. An MIOP requires minimal interaction with the basic processor. I/O command doublewords permit both command chaining and data chaining without intervening basic processor control. I/O equipment speeds range from slow rates involving human interaction (teletypewriter, for example) to transfer rates of rotating memory devices of over 750,000 bytes per second. Peripheral controllers attached to an MIOP may be operated simultaneously.

### **TIME-SHARING FEATURES**

Time-sharing is the ability of a system to share its total resources among many users at the same time. Each user may be performing a different task, requiring a different share of the available resources. Some users may be online in an interactive, "conversational" mode with the basic processor while other users may be entering work to be processed that requires only final output.

Time-sharing features are described in the following paragraphs.

Rapid Context Saving. When changing from one user to another, the operating environment can be switched quickly and easily. Stack-manipulating instructions permit storing in a push-down stack of 1 to 16 general-purpose registers by a single instruction. Stack status is updated automatically and information in the stack can be retrieved when needed (also, by a single instruction). The current program status words, which contain the entire description of the current user's environment and mode of operation, may be stored anywhere in memory, and new program status words may be loaded, all with a single instruction. <u>Multiple Register Blocks.</u> The availability of four blocks of 16 general-purpose registers improves response time by reducing the need to store and load register blocks. A distinct block may be assigned for different functions as needed; the program status words automatically select the applicable register block.

<u>User Protection.</u> The slave mode feature restricts each user to his own set of instructions while reserving to the operating system certain "privileged" (master mode) instructions that could destroy another user's program if used incorrectly. Also, a memory access – protection feature prevents a user from accessing any storage areas other than those assigned to him. It permits him to access certain areas for reading only, such as those containing public subroutines, while preventing him from reading, writing, or accessing instructions in areas set aside for other users.

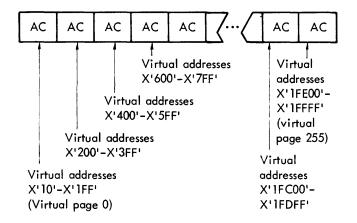

Storage Management. Main memory is expandable to 256K (K = 1024) words. To make efficient use of available memory, the memory map hardware permits storing a user's program in fragments as small as a page of 512 words, wherever space is available; yet all fragments appear as a single, contiguously addressable block of storage at execution time. The memory map also automatically handles dynamic program relocation so that the program appears to be stored in a standard way at execution time, even though it may actually be stored in a different set of locations each time it is brought into memory. The memory map provides the ability to locate any 128K-word virtual program in the basic processor's logical addressing space. Thus, the system can always address a virtual memory of 128K words regardless of physical memory size.

<u>Input/Output Capability</u>. Time-sharing input/output requirements are handled by the same general-purpose input/ output capabilities described under "General-Purpose Features".

Nonstop operation. A "watchdog" timer assures that the system continues to operate even in case of halts or delays due to failure of special I/O devices. Multiple real-time clocks with varying resolutions permit independent time bases for flexible allocation of time slices to each user.

Reliability, Maintainability, Availability. Since timesharing systems have many on-line users needing immediate system response, "downtime" defeats time sharing's primary purpose. Pooling of resources along with flexible reconfiguration control ensures a high level of continuous availability. Configuration controls are provided to switch the load from one unit to another in the event of a failure with no loss of functional capability, only capacity. In addition, a nonworking subset of the total system may be logically isolated (partitioned) so that maintenance may proceed on the subset while the remainder of the system continues to operate. To minimize the effect of transient errors, automatic retry of failed instructions is performed.

### **REAL-TIME FEATURES**

Real-time applications are characterized by a need for: (1) hardware that provides quick response to an external environment; (2) speed that is sufficient to keep up with the real-time process itself; (3) input/output flexibility to handle a wide variety of data types at different speeds; and (4) reliability features to minimize irreplaceable lost time.

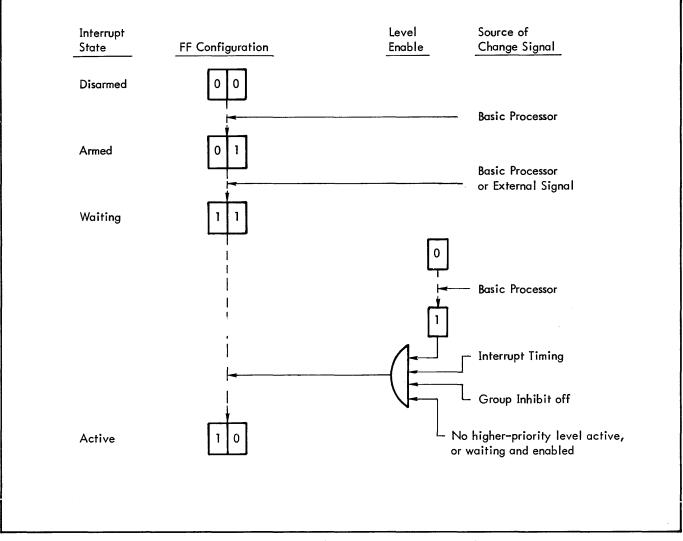

<u>Multilevel</u>, <u>Priority Interrupt System</u>. The real-timeoriented system provides rapid response to external interrupt levels. Each interrupt is automatically identified and responded to according to its priority. For further flexibility, each level can be individually disarmed (to discontinue input acceptance) and disabled (to defer responses). Use of the disarm/disable feature makes programmed dynamic reassignment of priorities quick and easy, even while a realtime process is in progress.

Programs involving interrupts from specially designed equipment often require checkout before the equipment is actually available. To permit simulating this special equipment, any external interrupt level can be "triggered" by the basic processor through execution of a single instruction. This capability is also useful in establishing a modified hierarchy of responses. For example, in responding to a high-priority interrupt, after the urgent processing is completed, it may be desirable to assign a lower priority to the remaining portion so that the interrupt routine is free to respond to other critical stimuli. The interrupt routine can accomplish this by triggering a lower-priority level, which processes the remaining data only after other interrupts have been handled.

READ DIRECT and WRITE DIRECT instructions (described in Chapter 3) allow the program to completely interrogate, preserve, and alter the condition of the interrupt system at any time and to restore that system at a later time.

Nonstop Operation. When connected to special devices (on a ready/resume basis), the basic processor may be excessively delayed if the specific device does not respond quickly. As in the time-sharing environment, the built-in watchdog timer assures that the basic processor cannot be delayed for an excessive length of time.

<u>Real-Time Clocks</u>. Many real-time functions must be timed to occur at specific instants. Other timing information is also needed – for example, elapsed time since a given event, or the current time of day. The computer system can contain up to four real-time clocks with varying degrees of resolution to meet these needs. These clocks also allow easy handling of separate time bases and relative time priorities.

Rapid Context Switching. When responding to a new set of interrupt-initiated circumstances, a computer system must preserve the current operating environment, for continuance later, while setting up the new environment. This changing of environments must be done quickly, with a minimum of "overhead" time costs. Any one of the four blocks of general-purpose arithmetic registers can, if desired, be assigned to a specific environment. All relevant information about the current environment (instruction address, current general register block, memory-protection key, etc.) is kept in the program status words. A single instruction stores the current program status words anywhere in memory and loads new ones from memory to establish a new environment, which includes information identifying a new block of general-purpose registers. Thus, the system's operating environment can be preserved and changed completely through the execution of a single instruction.

<u>Memory Protection</u>. Both foreground (real-time) and background can run concurrently in the system because a foreground program is protected against destruction by an unchecked background program. Under operating system control, the memory access-protection feature prevents accessing memory for specified combinations of reading, writing, and instruction acquisition.

Variable Precision Arithmetic. Much of the data encountered in real-time systems are 16 bits or less. To process this data efficiently, both halfword and fullword arithmetic operations are provided. For extended precision, doubleword arithmetic operations are also included.

<u>Direct Input/Output.</u> For handling asynchronous I/O, a 32-bit word can be transferred directly between any general-purpose register and external devices.

Reliability, Maintainability, Availability. The capabilities described in the section, "Time-Sharing Features" apply equally to the real-time environment. Priority Interrupt System. In a multiuse environment, many elements operate simulatneously and asynchronously. Thus, an efficient priority interrupt system is essential. It allows the computer system to respond quickly, and in proper order, to the many demands made on it, with attendant improvements in resource efficiency.

Quick Response. The many features that combine to produce a quick-response system (multiple register blocks, rapid context saving, multiple push-pull operations) benefit all users because more of the system's resources are readily available at any instant.

Memory Protection. The memory protection features protect each user from every other user and guarantee the integrity of programs essential to critical real-time applications.

<u>Input/Output</u>. Because of the wide range of capacities and speeds, the I/O system simultaneously satisfies the needs of many different application areas economically, both in terms of equipment and programming.

<u>Instruction Set.</u> The comprehensive instruction set provides the computational and data-handling capabilities required for widely differing application areas; therefore, each user's program length and running time is minimized, and the throughput is maximized.

### **MULTIPROCESSOR FEATURES**

System design readily permits expansion to shared memory in a multiprocessor system. The system can contain a combination of functional clusters, each of which in turn may contain multiple processors. The total number of clusters is restricted to the maximum port limitation of six. All processors in a system may share common memory.

The following paragraphs describe the major multiprocessor features of the system.

## MULTIUSE FEATURES

As implemented in this system, "multiuse" combines two or more application areas. The real-time application is the most difficult general computing task because of its severe requirements. Similarly, another difficult multiuse task is a time-sharing application that includes one or more realtime processes. Because the system is designed on a realtime base, it is qualified for a mixture of applications in a multiuse environment. Many hardware features that prove valuable for certain application areas are equally useful in others, although in different ways. This multiple capability makes the system particularly effective in multiuse applications.

The major multiuse features are described in the following paragraphs.

#### **MULTIPROCESSOR INTERLOCK**

In a multiprocessor system, the basic processors often need exclusive control of a system resource. This resource may be a region of memory, a particular peripheral device, or, in some cases, a specific software process. There is a special instruction to provide this required multiprocessor interlock. This special instruction, LOAD AND SET, unconditionally sets a "1" bit in the sign position of the referenced memory location during the restore cycle of the memory operation. If this bit had been previously set by another processor, the interlock is said to be "set" and the testing program proceeds to another task. On the other hand, if the sign bit of the tested location is a zero, the resource is allocated to the testing processor, and simultaneously the interlock is set for any other processor.

#### **MULTIPORT MEMORY SYSTEM**

The system has growth capability of up to 6 ports per memory unit. A memory unit may contain 16K or 32K words. This architecture allows flexibility in growth patterns and provides high memory bandwidth, essential to multiprocessor systems.

#### MANUAL PARTITIONING CAPABILITY

Manual partitioning capability is afforded for all system units. Thus, besides the primary advantage of increased throughput, a secondary advantage of a multiprocessor system is the "fail-soft" ability. Given a duplicate unit, any unit can be partitioned by selectively disabling it from the system buses. Depending on the type of failing unit, the system will be operable, with some degree of degraded performance. An alternate processor bus with dual system capabilities can be provided.

#### **MULTIPROCESSOR CONTROL FUNCTION**

A multiprocessor control function is provided on all multiprocessor systems. This function provides these basic features:

1. Control of the External Direct Input/Output bus (External DIO), used for controlling system maintenance and special purpose units such as analog to digital converters.

- 2. Central control of system partitioning.

- 3. Centralized interrupt system, providing capability for the operating system to use interrupts to schedule tasks independently of the number of basic processors present in a system.

- 4. Processor to processor communication via processor buses.

#### **SHARED INPUT/OUTPUT**

In a multiprocessor system, any basic processor may direct I/O actions to any I/O processor. Specifically, any basic processor can issue an SIO, TIO, TDV, or HIO instruction to begin, test, or stop any I/O process. However, the "end-action" sequence of the I/O process is directed to one of the basic processors in the system by the System Control Processor. This feature (accomplished by setting a pair of configuration control switches) allows dedicating I/O end-action tasks to a single processor and avoids conflict resolution problems.

# 2. SYSTEM ORGANIZATION

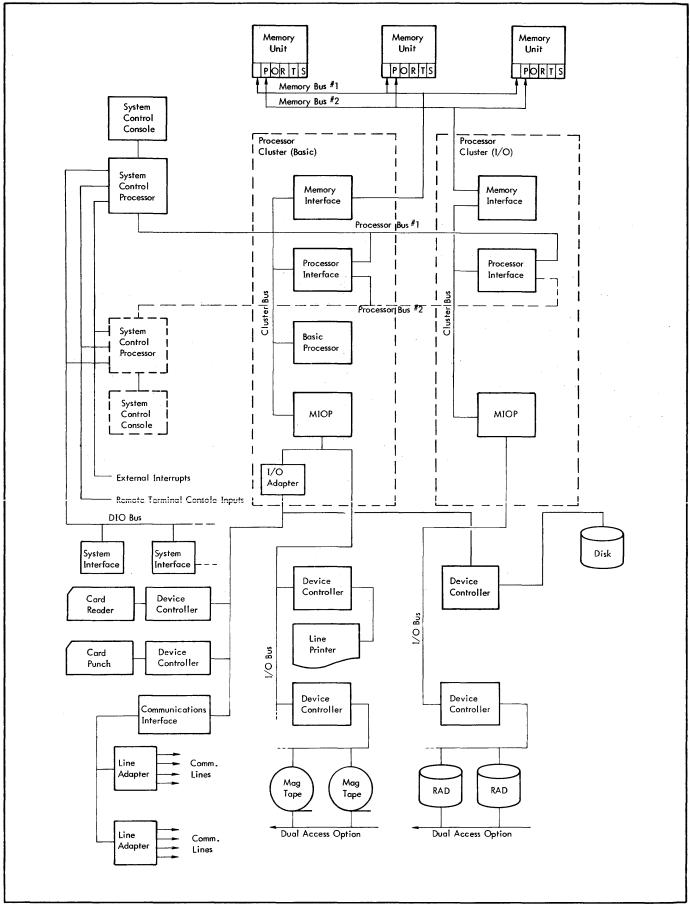

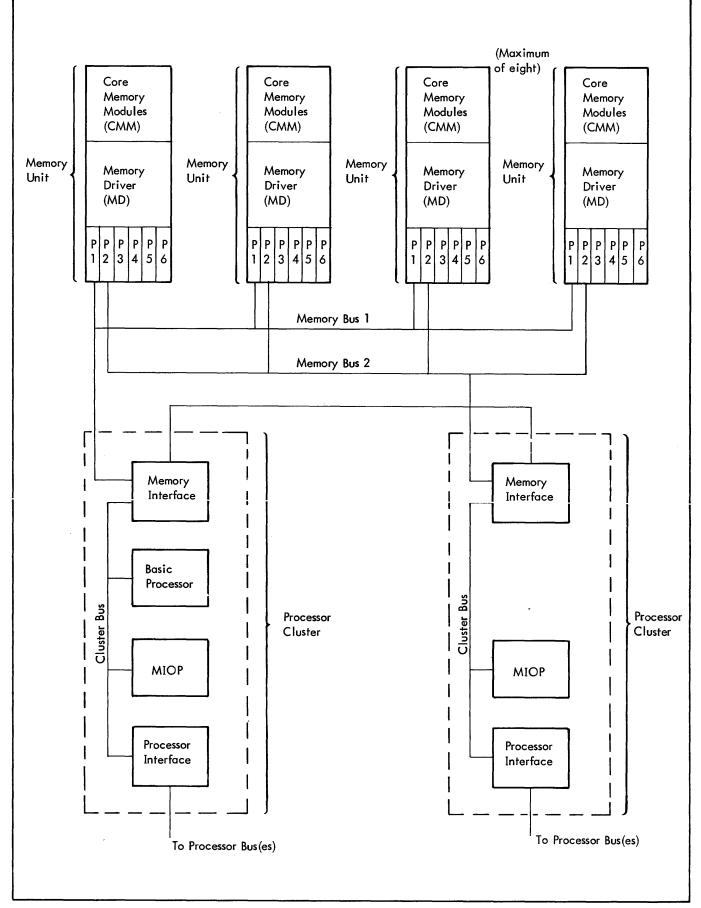

The elements of this computer system include a basic processor (BP), input/output processors (IOPs), memory, I/O device controllers, and devices (see Figure 1). The processors and interfaces clustered into functional groups, interconnected via buses and controlled from a Configuration Control Panel and a System Control Processor. Elements within a processor cluster share an access path for intracluster communications. Thus, the total computer system can be viewed functionally as a group of program-controlled processor clusters communicating with each other and a common memory. Each processor cluster operates asynchronously and semi-independently, automatically overlapping the operation of elements within as well as the operation of other processor clusters for greater speed (when circumstances permit).

### **PROCESSOR CLUSTERS**

Processors (basic processor and MIOP, for example) are grouped functionally along with a Memory Interface (MI) and a Processor Interface (PI) into a processor cluster. Elements within a processor cluster share an access path (the cluster bus) to the Memory Interface, which connects to the memory system via a memory bus. The Memory Interface resolves contention problems and controls use of the cluster bus by the elements in the cluster.

A processor communicates with processors in other processor clusters through the Processor Interface, which connects directly to a processor bus. Via the processor bus, any processor can communicate with or control any other processor anywhere in the system configuration.

Note: Although two processor buses are provided, a Processor Interface can be connected to one or the other of the processor buses, but not to both at the same time.

Within a basic processor-MIOP processor cluster, the basic processor primarily performs overall control and data reduction tasks whereas the MIOP performs the task associated with the exchange of digital information between main memory and selected peripheral devices. The MIOP communicates with device controllers via the I/O bus, which connects to the Controller Interface (CI).

## SYSTEM CONTROL PROCESSOR

The System Control Processor performs these primary functions in the overall system:

- 1. System control.

- 2. External Control Subsystem.

- 8 System Organization

- 3. Internal and external interrupt processing.

- 4. External and certain internal direct I/O (DIO) control.

It provides these major interfaces with other parts of the system:

- 1. System console interface.

- 2. System control bus interface.

- 3. Processor bus interface.

- 4. Internal and external interrupt interfaces.

- 5. External and certain internal DIO interfaces.

- 6. System clock interface.

In addition to these major interfaces it provides paths for other signals including system reset, 1.024 MHz clock, power on/power off trap requests, and external real-time clocks.

Figure 1 shows the interconnection of a System Control Processor to processor clusters via a processor bus as well as interconnection to the system console, external Direct Input/ Output (DIO), and external interrupts.

#### **BASIC PROCESSOR**

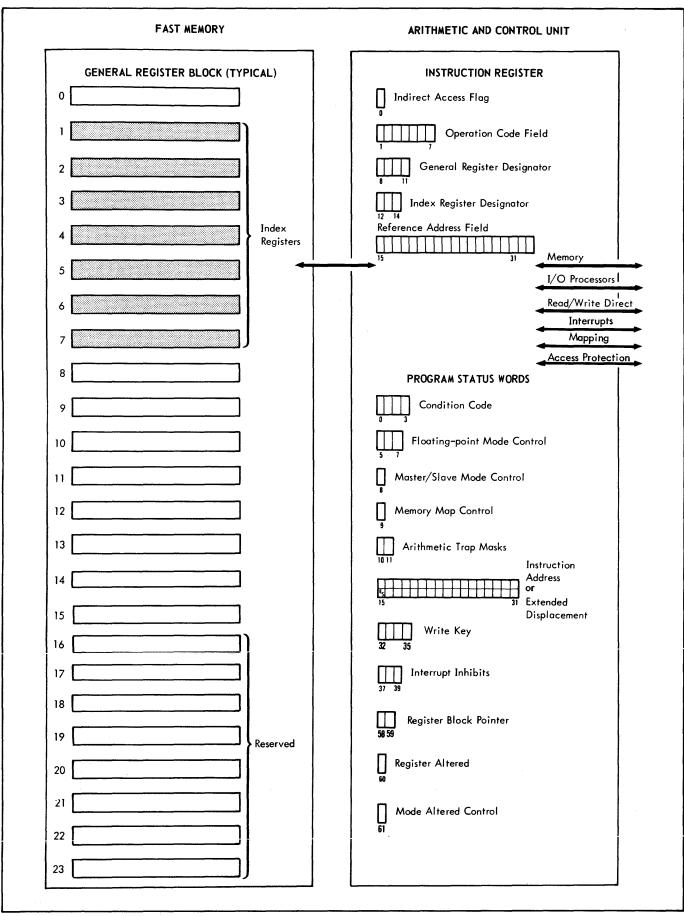

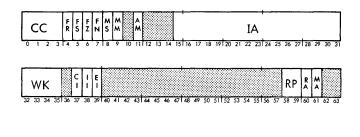

This section describes the organization and operation of the basic processor in terms of instruction and data formats, information processing, and program control. The basic processor comprises a fast memory and an arithmetic and control unit as functionally shown in Figure 2.

Note: Functionally associated with the basic processor but physically located elsewhere are a memory map, memory access protection codes, and memory write protection codes. Memory control storage for the memory map and access codes is located in the Memory Interface, and the memory control storage for the write protection codes (write locks) is located in the memory. These functions are described in "Memory System", later in this chapter.

#### **GENERAL REGISTERS**

A fast (integrated circuit) memory consisting of ninety-six 32-bit registers is used within the basic processor. A group of 24 registers is referred to as a register block; thus, a basic processor contains four register blocks. A 2-bit control field (called a register block pointer) in the program status words (PSWs) selects the register block currently

Figure 1. A Xerox 550 Computer System

Figure 2. The Basic Processor

available to a program. The register block pointer can be changed when the basic processor is in the master mode or the master-protected mode. Only the first 16 general registers of a register block may be used by programs; the last eight are reserved.

Each of the first 16 general registers in a register block is identified by a 4-bit code in the range 0000<sub>2</sub> through 1111<sub>2</sub> (0 through 15 in decimal notation, or X'0' through X'F' in hexadecimal notation). Any of these 16 registers can be used as a fixed-point temporary data storage location, or to contain control information such as a data address, count, pointer, etc. General registers 1 through 7 can be used as index registers.

#### MEMORY CONTROL STORAGE

The memory control storage for the memory map and the associated memory access protection codes are contained in the Memory Interface (MI). Memory control storage for the 4-bit write locks are contained in the memory units. Memory control storage can be modified when the basic processor is in the master mode or the master-protected mode.

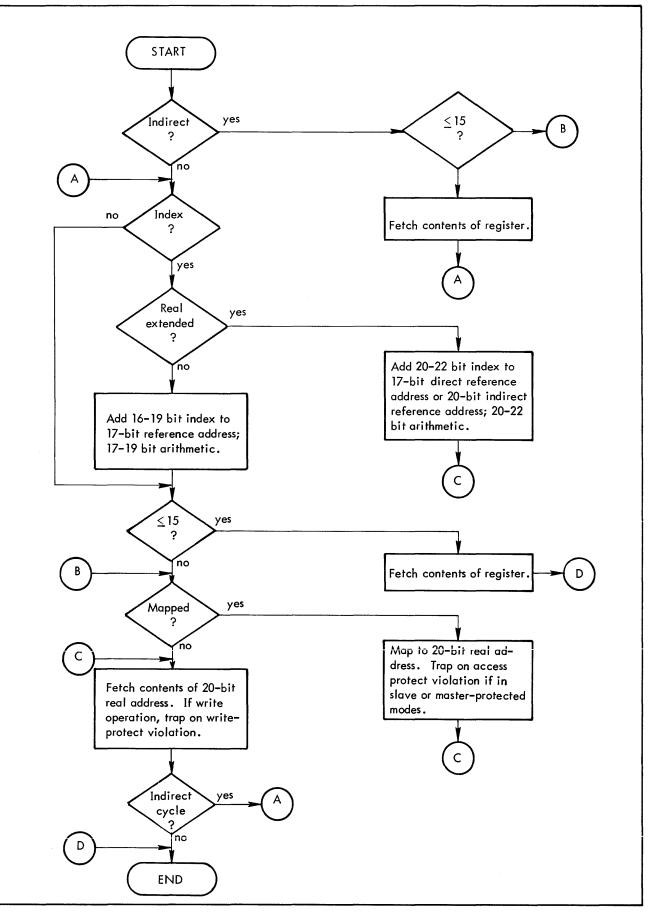

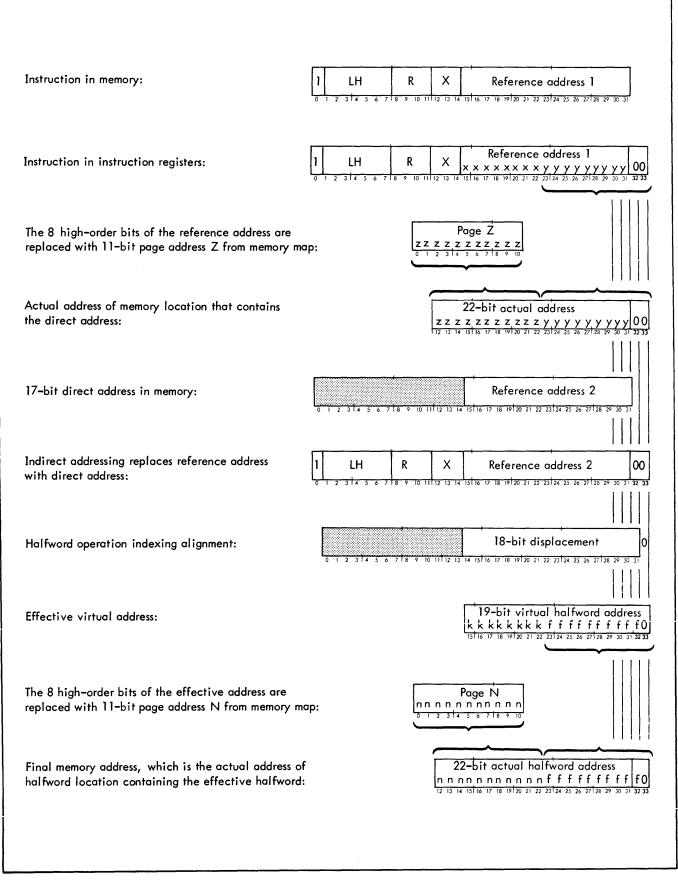

#### MEMORY MAP

Two terms are essential in understanding the memory mapping concept: actual (i.e., absolute or real) address and virtual address.

An actual address is used within the memory unit (memory address registers) to access a specific, physical memory location for storage or retrieval of information as required by the execution sequence of an instruction. Actual addresses are fixed and are dependent on the wired-in hardware.

A virtual address refers to a logical location as required by an individual program. Like an actual address, a virtual address may designate a location that contains a program instruction, an element of data, a data address (indirect address), or it may also be an explicit quantity. Normally, virtual addresses are derived from programmer-supplied labels through an assembly (or compilation) process followed by a loading process. Virtual addresses may also be computed during a program's execution. Virtual addresses include all instruction addresses, indirect addresses, and addresses used as counts within a stored program, as well as those instructions computed by the program. (See "Virtual and Real Memory", later in this chapter.)

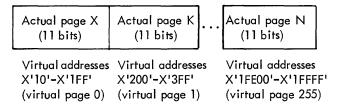

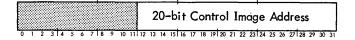

Memory mapping transforms virtual addresses as seen by the individual program into actual addresses as seen by the memory system. Thus, when the memory map is in effect, any program can be broken into 512-word pages and dynamically relocated throughout memory in whatever pages of space are available. When the memory map is not in effect, all virtual address values above 15<sub>10</sub> are used by the memory as actual addresses. Virtual addresses 0 through 15 are always<sup>†</sup> used by the basic processor as general register addresses rather than as memory addresses. For example, if an instruction uses virtual address 5 to address the location where a result is to be stored, the basic processor stores that result in general register 5 in the current register block instead of in memory location 5.

When the basic processor is operating with the memory map in effect, virtual addresses 0 through 15 are still used as general register addresses. Virtual addresses above 15 are transformed into actual addresses by replacing the highorder portion of the virtual address with a value obtained from the memory map. (The memory map address replacement process is described in "Memory Address Control", later in this chapter.)

#### MEMORY ACCESS PROTECTION

When the basic processor is operating with the memory map in the slave mode or the master-protected mode, the access protection codes determine whether the program may access instructions from, read from, or write into specific regions of the virtual address continuum (virtual memory). If the slave mode or master-protected mode program attempts to access a protected region of virtual memory, a trap occurs (see "Memory Address Control", "Virtual and Real Memory", and "Trap System", later in this chapter).

#### MEMORY WRITE PROTECTION

The memory write-protection feature operates independently of access protection and the memory map. The 4-bit write lock operates in conjunction with a 4-bit field, called the write key, in bits 32-35 of the Program Status Words (PSWs). The lock and the key determine whether any program may alter any word of main memory. The write key can be changed when the basic processor is in the master mode or the master-protected mode. (The functions of the write lock and key are described in "Memory Address Control", later in this chapter.)

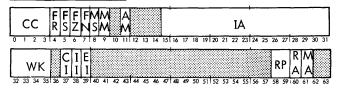

#### **COMPUTER MODES**

The basic processor operates in one of three modes: master, master-protected, or slave. The operation mode is determined by the setting of three bits (bits 8, 9, and 61) of the Program Status Words (PSWs). (See "Program Status Words", later in this chapter.) Additionally, the basic processor operates in a mapped mode or an unmapped mode.

<sup>&</sup>lt;sup>T</sup>Except for the READ DIRECT (RD)/WRITE DIRECT (WD) instructions which can read from and store into these locations.

#### MASTER MODE

The master/slave control bit (bit 8 of the PSWs) must contain a zero for the basic processor to operate in master mode. In this mode the basic processor can perform all of its control functions and can modify any part of the system. The restrictions upon the basic processor's operations in this mode are those imposed by the write locks on certain protected parts of memory. It is assumed that there is a resident operating system (operating in the master mode) that controls and supports the operation of other programs (which may be in the master, master-protected, or slave mode).

#### MASTER-PROTECTED MODE

The master-protected mode of operation provides additional protection for programs that operate in the master mode. The master-protected mode occurs when the basic processor is operating in the master mode with the memory map in effect and the mode altered control bit (bit 61 of the PSWs) is on. In this mode the memory protection violation trap occurs (location X'40', with CC4 = 1), as it does in all mapped slave programs, if a program makes a reference to a virtual page to which access is prohibited by the current setting of the access protection codes.

#### SLAVE MODE

The slave mode of operation is the problem-solving mode of the basic processor. In this mode, access protection codes apply to the slave mode program if mapping is in effect, and all "privileged" operations are prohibited. Privileged operations are those relating to input/output and to changes in the fundamental control state of the basic processor. All privileged operations are performed in the master or master-protected mode by a group of privileged instructions. Any attempt by a program to execute a privileged instruction while the basic processor is in the slave mode results in a trap. The master/slave mode control bit (bit 8 of the PSWs) can be changed when the basic processor is in the master or master-protected mode. Nevertheless, a slave mode program can gain direct access to certain executive program operations by means of CALL instructions. The operations available through CALL instructions are established by the resident operating system.

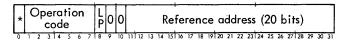

#### MAPPED MODE

Although the memory map is located in the Memory Interface (MI), it functions as part of the basic processor. The basic processor communicates with memory through the MI. Mapping is effective for all the words of real memory, and is invoked when bit 9 (MM) of the PSWs contains a one. Memory mapping generates real page addresses from virtual addresses. The memory map can be loaded with either 11-bit real page addresses or 8-bit real page addresses by means of the MOVE MEMORY CONTROL (MMC) privileged instruction (see Chapter 3, "Control Instructions"). Elevenbit real page addresses are always provided for in the map, thus if 8-bit real page addresses are generated, the three high-order bits contain zeros. The memory map always maps 17-bit virtual addresses into 20-bit real addresses (see "Memory Address Control", later in this chapter for a discussion of how the map is used).

#### UNMAPPED MODE

When the basic processor is operating in the unmapped mode, there is a direct one-to-one relationship between the effective virtual address of each instruction and the actual address used to access main memory. (See "Real Addressing", later in this chapter.)

#### **INFORMATION FORMAT**

Nomenclature associated with digital information within the computer system is based on functional and/or physical attributes. A "word" may be either a 32-bit instruction word or a 32-bit data word.

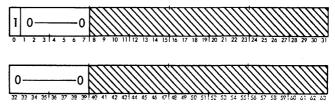

The bit positions of a word are numbered from 0 through 31 as follows:

Word

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

A word can be divided into two 16-bit parts (halfwords) in which the bit positions are numbered from 0 through 15 as follows:

|   |   |   |   |   |   |   |   | or |   | -  |    |    |    |    |    |   |   |   |   | . ' |   |   |   |    | d | 1  |    |    |    |    |    |    |

|---|---|---|---|---|---|---|---|----|---|----|----|----|----|----|----|---|---|---|---|-----|---|---|---|----|---|----|----|----|----|----|----|----|

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 18 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 0 | 1 | 2 | 3 | 4   | 5 | 6 | 7 | 18 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | ۰. |

A word can also be divided into four 8-bit parts (bytes) in which the bit positions are numbered 0 through 7 as follows:

| 1 |          |   |    |    |   |   | - |   |     | T | _        |   |    |     |     |   |     |   | Τ |   |              |    |     |   |   |  |   |   |      |          |    |   |   |       |

|---|----------|---|----|----|---|---|---|---|-----|---|----------|---|----|-----|-----|---|-----|---|---|---|--------------|----|-----|---|---|--|---|---|------|----------|----|---|---|-------|

|   |          |   | B١ | /t | e | ( | ) |   |     |   |          |   | By | te  | e ' | l |     |   |   |   |              | By | /te | е | 2 |  |   |   | В    | y        | te | Э | 3 |       |

|   | <u> </u> | - | 2  | 3  | t | 4 | 5 | 6 | - 7 | + | <u> </u> | 1 |    | - 1 | 14  | 5 | - 6 | 7 | + | _ | <del>.</del> | -  | 3   | 1 |   |  | - | 0 | <br> | <u> </u> | ส  | - | - | <br>7 |

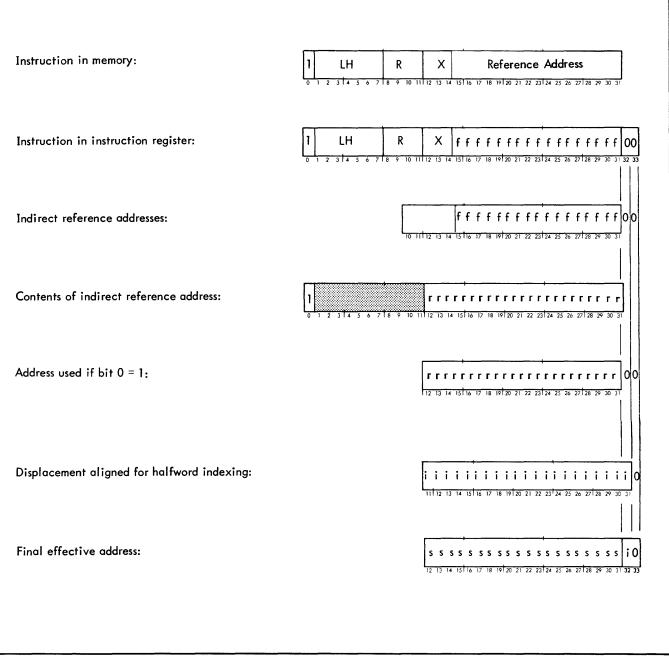

Two words can be combined to form a 64-bit element (a doubleword) in which the bit positions are numbered 0 through 63 as follows:

|   |   |   |   |   |   |   |   |    |   | м  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|---|---|---|---|---|---|---|---|----|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| 0 | 1 | 2 | З | 4 | 5 | 6 | 7 | 18 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 |

Least significant word

32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63

In fixed-point binary arithmetic each element of information represents numerical data as a signed integer (bit 0 represents the sign, remaining bits represent the magnitude, and the binary point is assumed to be just to the right of the least significant or rightmost bit). Negative values are represented in two's complement form. Other formats required for floating-point and decimal instructions are described in Chapter 3.

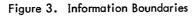

#### **INFORMATION BOUNDARIES**

Basic processor instructions assume that bytes, halfwords, and doublewords are located in main memory according to the following boundary conventions:

1. A byte is located in bit positions 0 through 7, 8 through 15, 16 through 23, and 24 through 31 of a word.

ſ

- 2. A halfword is located in bit positions 0 through 15 and 16 through 31 of a word.

- A doubleword is located such that bit positions 0 through 31 are contained within an even-numbered word, and bit positions 32 through 63 are contained within the next consecutive word (which is odd-numbered).

Figure 3 illustrates these boundaries.

|        |          |         | Doubl  | eword  |          |         |        |        |         |        | Doubl       | eword  |          |          |       |

|--------|----------|---------|--------|--------|----------|---------|--------|--------|---------|--------|-------------|--------|----------|----------|-------|

| Wo     | ord (eve | n addre | ess)   | Wo     | ord (odd | d addre | ss)    | Wo     | rd (eve | n addr | ess)        | Wo     | ord (odd | l addres | ss)   |

| Half   | word 0   | Halfv   | word 1 | Hal fv | vord 0   | Halfv   | vord 1 | Halfw  | ord 0   | Halfv  | word 1      | Halfw  | vord 0   | Halfw    | ord 1 |

| Byte ( | ) Byte 1 | Byte 2  | Byte 3 | Byte O | Byte 1   | Byte 2  | Byte 3 | Byte O | Byte 1  | Byte 2 | 2<br>Byte 3 | Byte 0 | Byte 1   | Byte 2   | Byte  |

#### **INSTRUCTION REGISTER**

The instruction register contains the instruction the basic processor is currently executing. The format and fields of the two general types of instructions (memory reference and immediate operand) are described below. Specific formats for each instruction are given in Chapter 3.

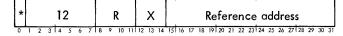

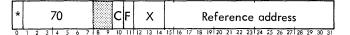

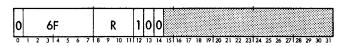

#### MEMORY REFERENCE INSTRUCTIONS

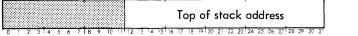

Instructions that make reference to an operand in main memory may have the following format:

|   | * |   |   | C | 0  | ati<br>de |   |   |    | R | 2  |    |     | Х  |    |    |    |    |    |    | fe |    |    |    |    |    |    |    |    |    |    |    |

|---|---|---|---|---|----|-----------|---|---|----|---|----|----|-----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| 0 | ) | 1 | 2 | 3 | 14 | 5         | 6 | 7 | 18 | 9 | 10 | 11 | 112 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 |

#### Bits Description

- 0 <u>Indirect addressing</u>. One level of indirect addressing is performed only if this bit position contains a one.

- 1-7 Operation code. This 7-bit field contains the code that designates the operation to be performed. See the inside front and back covers for complete list-ings of operation codes.

- 8-11 <u>R field.</u> For most instructions this 4-bit field designates one of the first 16 general registers of the

- Bits Description

- 8–11 current register block as an operand source, result (cont.) destination, or both.

- 12-14 <u>X field.</u> This 3-bit field designates one of general registers 1-7 of the current register block as an index register. If X contains zero, indexing will not be performed; hence register 0 cannot be used as an index register. (See "Address Modification Example: Indexing (Real and Virtual Addressing)", later in this chapter for a description of the indexing process.)

- 15-31 Reference address. This 17-bit field normally contains the reference address of the instruction operand. The reference address is translated into an effective virtual address in accordance with the addressing type (real, real extended, or virtual) and the address modification requied (direct/ indirect or indexing). (See "Memory Reference Addresses" later in this chapter.)

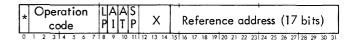

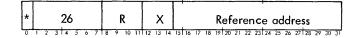

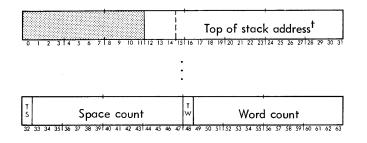

#### IMMEDIATE OPERAND INSTRUCTIONS

Immediate operand type instructions are particularly efficient because the required operand is contained within the instruction word. Hence, memory reference, indirect addressing, and indexing are not required.

| 0 | ( | 0 | 5 | ero<br>oc | ati<br>le | or | ſ |    | R |    |    |    | х  |    |    |    |    |    |    | fe |    |    |    |    |    |    |    |    |    |    |    |

|---|---|---|---|-----------|-----------|----|---|----|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| 0 | ĩ | 2 | 3 | Τ4        | 5         | 6  | 7 | 18 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 |

Bits Description

- 0 Bit position 0 must be coded with a zero. If it contains a one, the instruction is interpreted as being nonexistent. (See "Trap System", later in this chapter.)

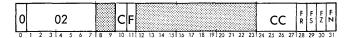

- 1-7 Operation code. This 7-bit field contains the code that designates the operation to be performed. When the basic processor encounters any immediate operand operation, it interprets bits 12-31 of the instruction word as an operand. These are the immediate operand operation codes:

| Operation<br>Code | Instruction<br>Name                                                | Mnemonic |

|-------------------|--------------------------------------------------------------------|----------|

| X'02'             | Load Conditions<br>and Floating Con <del>-</del><br>trol Immediate | LCFI     |

| X'20'             | Add Immediate                                                      | AI       |

| X'21'             | Compare Immediate                                                  | CI       |

| X'22'             | Load Immediate                                                     | LI       |

| X'23'             | Multiply Immediate                                                 | MI       |

- 8-11 <u>R field</u>. This 4-bit field designates one of the first 16 general registers in the current general register block. The register may contain another operand and/or be designated as the register in which the results of the operation are to be stored or accumulated.

- 12-31 Operand. This 20-bit field contains the immediate operand. Negative numbers are represented in two's complement form. For arithmetic operations bit 12 (the sign bit) is extended by duplication to the left through bit position 0 to form a 32-bit operand.

#### MAIN MEMORY

The memory system comprises memory units, memory interfaces (MIs), and memory buses. Figure 4 illustrates the relationships among these components.

The primary technology for main memory is magnetic core. The maximum physical storage is 256K words. Memory units can be interleaved on a two-way interleave basis. Each memory unit is provided with a set of starting address switches on the Configuration Control Panel (see Chapter 6) together with a two-position switch that selects one of two possible clock and power sources. Memory units may contain two, four, or six ports, which have a fixed priority order for the resolution of contention problems.

The following sections describe the organization and operation of the memory system. Also described are the various modes and types of addressing, including indexing.

#### **MEMORY UNIT**

Main memory is divided physically and logically into one to eight module assemblies called memory units. Because the memory unit is a logical component that contains all the functions available in the entire memory, the minimum memory is one memory unit. The minimum storage capacity per memory unit is 16K words; the maximum is 32K words. A memory location stores a word of 36 bits; the first 32 bits are information and the last 4 are byte parity bits (the latter being unavailable to the program). Each memory unit comprises a specific storage capacity, drive and sense circuits, a set of operational registers (address, data, and status), a set of write lock control registers for 32K words of memory, and a timing and control unit.

#### CORE MEMORY MODULES

Core memory modules (CMMs) provide a storage facility of standard modules (see Figure 4).

#### MEMORY DRIVER

The memory driver in each memory unit performs all memory operations except storage (provided for by the CMMs) and the few operations performed by the ports. The major functions of the memory driver are:

- 1. Store address word.

- Store data-in and data-out words during memory cycles.

- 3. Store write locks in special memory (other than CMMs).

- Perform parity generation and checking on address and memory bus data words, and on core memory module words.

- 5. Generate and store status words.

- 6. Control and time all transfers of address words, data words, status words, write locks, and write key among the ports, CMM, and the storage registers.

- 7. Control and time all data, parity, and control signals issued to the memory bus.

- Accept one of two or more simultaneous memory requests on the basis of port positional priority and other priority status information such as "high priority" and "memory reserved".

Figure 4. Main Memory

#### PORTS AND MEMORY BUSES

A memory unit may contain two, four, or six ports, which have a fixed priority order for the resolution of access contention. Each port allows the memory unit to communicate via a memory bus with a different external system (i.e., a processor cluster), which communicates with the memory bus via the Memory Interface (MI) (see Figure 4). Ports are numbered from 1 (top priority) to 6 (lowest priority). The selection logic is biased to select port 1 (the fast port) whenever the memory is quiescent. Thus performance is improved for the Memory Interface (MI) connected to that port, and hence to the processors connected to that MI.

A memory reserve function insures proper execution of instructions that require guaranteed re-access to a memory location before a second processor can access it.

Each port is equipped with an inhibit function that can be activated from the Configuration Control Panel (see Chapter 6).

Other major functions performed by the ports are:

- 1. Address recognition.

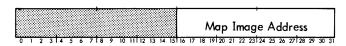

- 2. Address interleaving.