Reference Manual

NNARXO9HX NNARXO9HXXNARXO9HXX BANIK XEROXBANIK XEROX BANIK XERC

# 530 Computer

## **Reference Manual**

90 19 60B

September 1973

Price: \$3.75

## REVISION

This publication, 90 19 60B, is a revision of the Xerox 530 Computer Reference Manual, 90 19 60A. It incorporates Publication Revision Package, 90 19 60A-2(4/73). The major change to the manual is the addition of Appendix B, "Instruction Timing". Other changes are indicated by a vertical line in the margin of the affected page.

## **RELATED PUBLICATIONS**

| <u>Title</u>                                   | Publication No. |

|------------------------------------------------|-----------------|

| Xerox Symbol/Reference Manual                  | 90 10 51        |

| Xerox Extended Symbol/Reference Manual         | 90 10 52        |

| Xerox Computer Systems/Interface Design Manual | 90 09 73        |

Manual Content Codes: BP - batch processing, LN - language, OPS - operations, RP - remote processing, RT - real-time, SM - system management, TS - time-sharing, UT - utilities.

## **CONTENTS**

|    | VED OV 500 COVERNETED SVSTEV         | ,  | 0.4.4.0                                         | 0-         |

|----|--------------------------------------|----|-------------------------------------------------|------------|

| 1. | XEROX 530 COMPUTER SYSTEM            | !  | RAND                                            |            |

|    |                                      |    | RCPYI                                           |            |

|    | Introduction                         |    | RADDI                                           |            |

|    | General Characteristics              |    | RORI                                            |            |

|    | Real-Time and Multiusage Features    |    | REORI                                           |            |

|    | Standard and Optional Features       |    | randi                                           |            |

|    | Information Nomenclature and Formats | 4  | RCPYC                                           |            |

|    |                                      |    | RADDC                                           |            |

|    |                                      |    | RORC                                            |            |

| 2. | system organization                  | 6  | REORC                                           |            |

|    |                                      |    | randc                                           | 28         |

|    | Buses                                |    | RCLA                                            | 28         |

|    | Main Memory                          | 6  | RCLAI                                           | 28         |

|    | Central Processing Unit              |    | RCLAC                                           | 28         |

|    | General Registers                    |    | MUL                                             | 2          |

|    | Protection System Registers          |    | DIV                                             |            |

|    | Arithmetic and Control Unit          |    | WD                                              |            |

|    | Program Status Doubleword            |    | RD                                              |            |

|    | Interrupt System                     |    | General Register Instructions                   |            |

|    | Fault System                         |    | LW                                              |            |

|    | Effective Address Computation        |    | STW                                             |            |

|    | Effective Instructions               |    | AW                                              |            |

|    | Lifective Histipctions               | 1/ | SW                                              |            |

|    |                                      |    | AND                                             |            |

| ^  | TALICATE LICAL DE DEDA CADE          | 20 |                                                 |            |

| 3. | INSTRUCTION REPERTOIRE               | 20 | CW                                              |            |

|    |                                      | 00 | Multiple-Register Instructions                  |            |

|    | Memory Reference Instructions        |    | LDM                                             |            |

|    | LDA                                  |    | LDD                                             |            |

|    | STA                                  |    | STM                                             |            |

|    | LDX                                  |    | STD                                             |            |

|    | ADD                                  |    | DAD                                             |            |

|    | SUB                                  |    | DSB                                             |            |

|    | AND                                  |    | CPD                                             |            |

|    | IM                                   |    | Floating-Point Instructions                     |            |

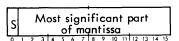

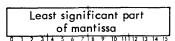

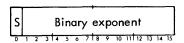

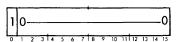

|    | \$                                   | 22 | Floating-Point Numbers                          | 39         |

|    | SARS                                 |    | Floating-Point Mode Control                     | 40         |

|    | SARD                                 | 22 | Scratchpad Floating Accumulator                 | 4          |

|    | SALS                                 | 23 | FLD                                             | 4:         |

|    | SALD                                 |    | FST                                             | 4:         |

|    | SCRS                                 | 23 | FAD                                             | 4          |

|    | SCRD                                 |    | F SB                                            | 42         |

|    | SCLS                                 | 24 | FMP                                             | 43         |

|    | SCLD                                 |    | FDV                                             | 4          |

|    | CP                                   |    | FCP                                             | 43         |

|    | В                                    | 24 | Field Addressing Instructions                   | 4          |

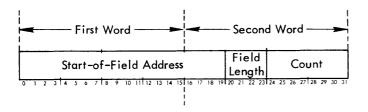

|    | Conditional Branch Instructions      |    | Field Descriptor                                | 4.         |

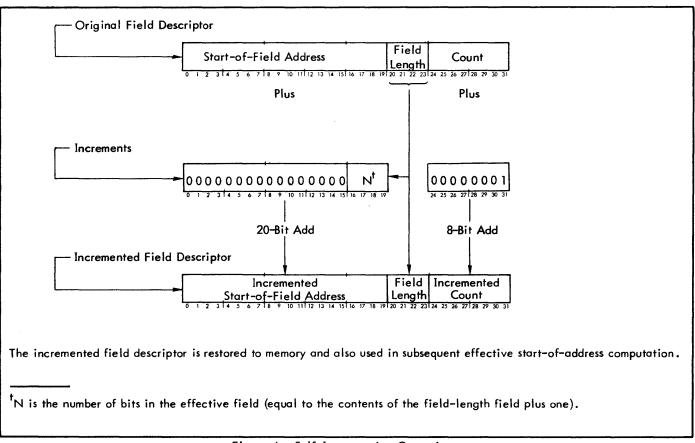

|    | BAN                                  |    | Self-Incrementing of the Start-of-Field         |            |

|    | BAZ                                  |    |                                                 | 4          |

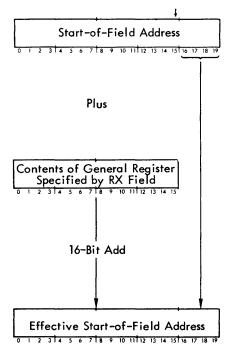

|    | BEN                                  |    | Register Indexing of the Start-of-Field         |            |

|    | BNO                                  |    | Address                                         | 40         |

|    | BNC                                  |    | Other Characteristics of Field Addressing       | ~          |

|    | BIX                                  |    | Instructions                                    | 4          |

|    | BXNO                                 |    |                                                 | +          |

|    |                                      |    | Self-Decrementing of the Start-of-Field Address |            |

|    | BXNC                                 |    |                                                 |            |

|    | Copy Instructions                    |    | LLF                                             |            |

|    | RCPY                                 | 26 | LAF                                             | 4          |

|    | RADD                                 | 26 | STF                                             | — <u>4</u> |

|    | ROR                                  |    | SZF                                             |            |

|    | RF OR                                | 27 | SOF                                             | 50         |

|    | CLF                                       | 50         |            | Hexadecimal-Decimal Integer                                                            |      |

|----|-------------------------------------------|------------|------------|----------------------------------------------------------------------------------------|------|

|    | CAF                                       |            |            | Conversion Table                                                                       | 75   |

|    | SLF                                       | 51         |            | Hexadecimal-Decimal Fraction                                                           |      |

|    |                                           |            |            | Conversion Table                                                                       | 81   |

|    |                                           |            |            | Table of Powers of Two                                                                 | 85   |

| 4. | INPUT/OUTPUT SYSTEMS                      | 52         |            | Mathematical Constants                                                                 | 85   |

|    | IOP Systems                               | 52         | В.         | instruction timing                                                                     | 86   |

|    | Device Number                             |            |            | Instruction Times                                                                      | 86   |

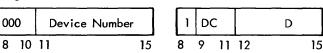

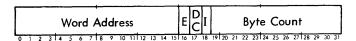

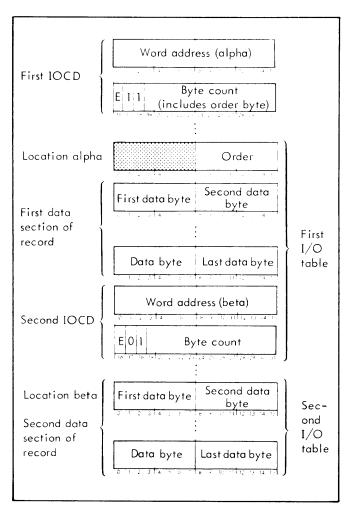

|    | I/O Control Doubleword (IOCD)             | 53         |            | marroen interest                                                                       | 00   |

|    | Operational Status Byte                   |            | C.         | read/write (mode 0) instructions                                                       | 92   |

|    | I/O Tables                                |            | С.         | READ/ WRITE (MODE O) 11431ROCTIO143                                                    | 12   |

|    | Device Orders                             | 56         |            |                                                                                        |      |

|    | Device Interrupts                         |            |            | FIGURES                                                                                |      |

|    | I/O Instructions                          |            |            |                                                                                        |      |

|    | \$IO                                      |            |            | Xerox 530 Computer System                                                              |      |

|    | TIO                                       |            | 1.         | Xerox 530 Central System Block Diagram                                                 |      |

|    | TDV                                       |            | 2.         | Central Processing Unit                                                                |      |

|    | HIO                                       |            | 3.         | Interrupt Level Operation                                                              |      |

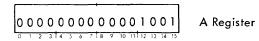

|    | AIO                                       |            | 4.         | Self-Incrementing Operation                                                            | 46   |

|    | Device Status Byte                        |            | 5.         | Self-Decrementing Operation                                                            |      |

|    | External DIO                              | 60         | 6.         | I/O Control Doublewords and I/O Tables                                                 |      |

|    |                                           |            | 7.         | Processor Control Panel                                                                | 61   |

| 5. | OPERATOR CONTROLS                         | 61         |            |                                                                                        |      |

|    |                                           | . 1        |            | TABLES                                                                                 |      |

|    | Processor Control Panel                   |            | 1          | T-1 (C)                                                                                | 11   |

|    | Basic Operating Procedures                | 01         | l.         | Interrupt System                                                                       |      |

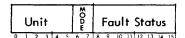

|    | Initialization (Power On and Normal Load) | <b>4</b> 1 | 2.<br>3.   | Unit Field (Fault Information)                                                         |      |

|    | Register Modification                     | O I        | 3.<br>4.   | Mode and Fault Status Values (CPU Faults)<br>Mode and Fault Status Values (IOP Faults) |      |

|    | Enter Loop                                |            | 4.<br>5.   | Mode and Fault Status Values (IOF Faults)  Mode and Fault Status Values (IM and        | 18   |

|    | Memory Display                            |            | ٦.         | DIO Faults)                                                                            | 10   |

|    | Memory Modification (Single)              |            | 6.         | Effective Address Computation                                                          |      |

|    | Memory Modification (Multiple             | 00         | 7.         | WRITE DIRECT Mode Values and General                                                   | 19   |

|    | Sequential Locations)                     | 4.4        | <i>/</i> • | Functions Performed                                                                    | 20   |

|    | Address Halt                              |            | 8.         | READ DIRECT Mode Values and General                                                    | 27   |

|    | Memory Scan                               |            | 0.         | Functions Performed                                                                    | 32   |

|    | Without y Scall                           |            | 9.         | Floating-Point Numbers                                                                 | 40   |

|    |                                           |            | 10.        | IOP Channel Register and Channel-Device-                                               | _ +0 |

|    |                                           |            |            | Controller Numbers (Hexadecimal)                                                       | 52   |

|    |                                           |            | 11.        | I/O Tables                                                                             | 55   |

|    |                                           |            | 12.        | Device Status Byte                                                                     |      |

|    |                                           |            | 13.        | PCP Switches                                                                           |      |

|    | APPENDIXES                                |            | 14.        | PCP Indicators                                                                         |      |

|    | <del></del>                               |            | B-1.       | Instruction Preparation and Execution Times                                            |      |

| Α. | REFERENCE TABLES                          | 67         |            | (in µsecs.)                                                                            | 86   |

|    |                                           |            | C-1.       | READ DIRECT (Mode 0) Instruction, Function                                             |      |

|    | Standard Symbols and Codes                | _ 67       |            | Values X'00'-X'3F'                                                                     | 92   |

|    | Standard Character Sets                   | 67         | C-2.       | READ DIRECT (Mode 0) Instruction, Function                                             |      |

|    | Control Codes                             | 67         |            | Values X'40'-X'7F'                                                                     | 92   |

|    | Special Code Properties                   | 67         | C-3.       | READ DIRECT (Mode 0) Instruction, Function                                             |      |

|    | Standard 8-Bit Computer Codes             |            |            | Values X'80'-X'BF'                                                                     | _ 93 |

|    | (EBCDIC)                                  | 68         | C-4.       | READ DIRECT (Mode 0) Instruction, Function                                             |      |

|    | Standard 7-Bit Communication Codes        |            |            | Values X'C0'-X'FF'                                                                     | _ 94 |

|    | (ANSCII)                                  | 68         | C-5.       | WRITE DIRECT (Mode 0) Instruction, Function                                            |      |

|    | Standard Symbol-Code                      |            |            | Values X'00'-X'3F'                                                                     | _ 94 |

|    | Correspondences                           | 69         | C-6.       | WRITE DIRECT (Mode 0) Instruction, Function                                            |      |

|    | Hexadecimal Arithmetic                    |            |            | Values X'40'-X'7F'                                                                     | 95   |

|    | Addition Table                            |            | C-7.       | WRITE DIRECT (Mode 0) Instruction, Function                                            |      |

|    | Multiplication Table                      | 73         |            | Values X'80' - X'BF'                                                                   | 95   |

|    | Table of Powers of Sixteen <sub>10</sub>  | 74         | C-8.       | WRITE DIRECT (Mode 0) Instruction, Function                                            |      |

|    | Table of Powers of Ten <sub>16</sub>      | 74         |            | Values X'C0'-X'FF'_                                                                    | 95   |

Xerox 530 Computer System

## 1. XEROX 530 COMPUTER SYSTEM

#### INTRODUCTION

This high-speed low-cost system is an integrated combination of sophisticated hardware technology (i.e., large- and medium-scale integrated circuits), advanced microprogramming techniques, and field-proven existing software. The Xerox 530 has advantages that are usually found only in large computing systems. It is well suited for a multiusage environment, both real-time and general-purpose applications.

A basic system includes a central processor, main memory, and an independent input output processor. The basic system may be expanded easily to accommodate the user's requirements (see "Standard and Optional Features"). The CPU's basic instruction repertoire may be increased to include the optional floating-point and field-addressing instructions. Main memory may be expanded by adding more memory modules. Input/output capability may be increased by adding a second input/output processor and additional device controllers and peripheral devices. A large complement of peripheral devices is available for cost effective input/output.

Concurrent multiprogramming capability permits the user to operate one or more fully protected, real-time programs in the foreground while concurrently operating a general-purpose program in the background. Overhead in switching from one task to another is minimized because both hardware and software are specifically designed for rapid context switching. A hardware register permits the software to generate reentrant code efficiently. Therefore, routines common to several programs, whether in foreground or background, need to be stored in memory only once.

The comprehensive field-proven programming package (assemblers, compilers, mathematical and utility routines, and applications) utilizes advanced features in the hardware. These programming systems are easy-to-use programming tools that increase productivity and allow user programs to be written more quickly at lower cost.

Existing Sigma 2 or 3 computer programs may be run on a Xerox 530 computer system. The compatibility of the modular software eliminates reprogramming or requires only minimal upgrading.

Optional field addressing instructions enable efficient operation upon any group of from 1 to 16 contiguous bits in memory without regard to word boundaries. Effectively used, the system provides a bit and byte manipulating capability, a general pushdown stack facility, and the ability to effectively operate on logical structures such as tables and strings.

General register instruction capability puts the result of executing one of a prescribed set of arithmetic and logical instructions (see Chapter 3) into a designated general register rather than into the accumulator. This mode of operation permits efficiencies in both code generation and execution times.

To enhance computations using scientific notations, optional floating-point hardware is available.

Xerox 530 systems provide significant reliability, maintainability, and availability improvements over other small- or medium-size computer systems. A remote assistance terminal connection with special software permits remote assistance as an integral part of maintenance.

#### **GENERAL CHARACTERISTICS**

The Xerox 530 computer system functions efficiently in a variety of computing environments and applications. Its operating characteristics and features are outlined below:

- Both word and byte organization of memory.

- Memory expandable from 8K words to 64K words in increments of 8K words.

- General-purpose registers to control program operations (all are available to the program). They provide

- Hardware index registers for preindexing (base address), postindexing, or both (double indexing).

- Hardware register for subroutine linkages.

- Double precision accumulator.

- Program address register.

- Temporary storage register.

- Rapid context switching to preserve computer environment when switching from one program to another, including automatic status preservation at interrupt.

- Up to two independent Input/Output Processors (IOPs) for high-volume data I/O operations.

- Up to 28 fully automatic I/O channels operating concurrently with one another.

- I/O data chaining, for scatter-read and gatherwrite operations.

- Up to two direct memory adapters (optional), each having a maximum information transfer rate of approximately 625,000 words per second.

- Direct input/output of a full word (in parallel) without the use of an I/O channel (optional).

- A real-time priority interrupt system that features

- Ten internal interrupt levels and up to 30 external interrupt levels. All external and most internal levels can be individually armed, enabled, and triggered by program control.

- Automatic identification and fast response time.

- Machine fault register which collects fault status enabling program retrieval.

- Power Monitor for automatic shutdown in event of power failure and resumption of processing when power returns.

- System protection that includes both memory write protection and operation protection for foreground programs.

- Two real-time clocks (one with a choice of resolution) for independent time bases.

- An extensive repertoire that includes these classes of instructions:

- Memory reference.

- Conditional branch.

- Copy (register-to-register).

- Direct control.

- Multiply/Divide.

- Double precision, operations on 32-bit operands.

- General register capability, which places the result of executing one of a prescribed set of arithmetic and logical instructions into a designated general register rather than in the accumulator.

- Floating-point (optional).

- Field addressing (optional), which permits operation on any group of from 1 to 16 contiguous bits in memory without regard to word boundaries, providing bit and byte manipulation, general pushdown stack capability, and ability to operate on logical structures such as tables and strings.

- Instruction characteristics include

- Only one word of storage required for most instructions.

- Two levels of indexing and one level of indirect addressing may be invoked individually or simultaneously.

- Relative addressing (forward and backward).

- Use of index register 2(B) as a base address register.

- Direct reference of up to 1024 addresses; 256 addresses beginning with location zero, 256 addresses beginning with the base address, 256 addresses beginning with the current instruction location (relative forward), and 256 addresses backward from the current instruction (relative backward).

- Comprehensive, modular software that expands in capability and speed as the system grows, with no reprogramming required. Existing, field-proven Sigma 2 or 3 computer programs may be run on a Xerox 530 system.

- Basic Control Monitor (BCM) Operating System for smaller systems including Symbol and Basic FORTRAN.

- Real-Time Batch Monitor (RBM) Operating System including Extended Symbol, Basic FORTRAN IV, ANS FORTRAN IV, RPG, and SORT.

- General loading programs.

- Utility routines.

- Mathematical routines.

- General Debug for symbolic program troubleshooting.

- Concordance program for documentation.

- System Generation program for creating installation master.

- Standard and special-purpose peripheral equipment including

- Rapid Access Data (RAD) files: capacities of .75, 1.5, or 3.0 million bytes per storage unit; transfer rate of 188,000 bytes per second; average access time of 17 milliseconds.

- Magnetic tape units: IBM compatible; 7-track

units operating at 37.5 inches per second with

transfer rates up to 20,800 bytes per second; 9-track

units operating at 75 inches per second with transfer rates up to 60,000 bytes per second.

- Card equipment: reading speeds up to 200 or 400 cards per minute; punching speeds up to 100 cards per minute.

- Line printers: fully buffered with speeds from 310 to 1100 lines per minute; up to 132 print positions and up to 91 characters.

- Keyboard/printers: ten characters per second; also available with paper tape reader (20 characters per second) and punch (10 characters per second).

- Paper tape equipment: readers with speeds up to 300 characters per second; punches with speeds up to 120 characters per second.

- Graph plotters: digital incremental, providing drift-free plotting in two axes in up to 300 steps per second at speeds from 30 millimeters to three inches per second.

- Data communications equipment: complete line

of character-oriented and message-oriented equipment to connect remote user terminals to the computer system via common carrier lines and local

terminals directly.

- Removable disk storage: capacities from 24.5 million to 196.6 million bytes; transfer rate of 312,000 bytes per second; average access time of 87.5 milliseconds; one- or two-byte data paths; device pooling.

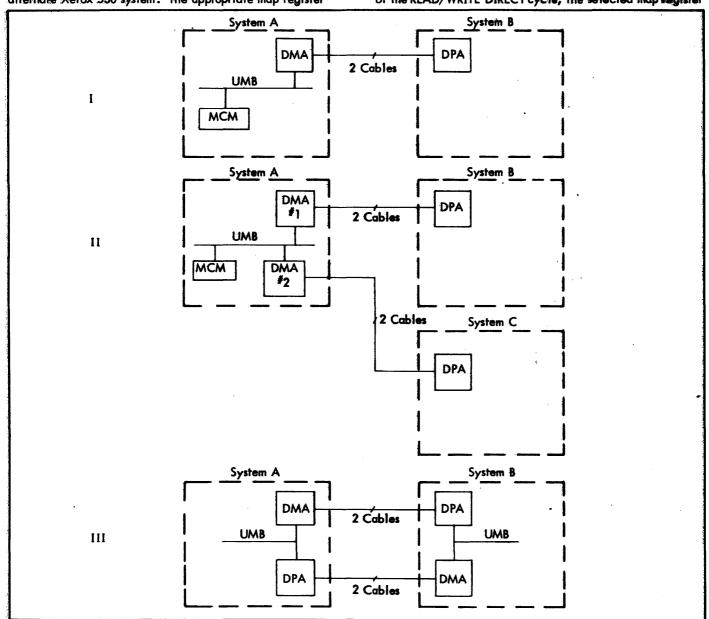

- Multiprocessing equipment: exchange of critical control and data signals between CPUs and between IOPs on a real-time basis; sharing of I/O devices attached to IOPs; concurrent control of external (DIO) devices.

#### **REAL-TIME AND MULTIUSAGE FEATURES**

Real-time applications are characterized by a need for (1) hardware that provides quick response to an external environment, (2) sufficient speed to keep up with the real-time process itself, and (3) input output flexibility to handle a wide variety of data types at varying speeds.

Multiusage applications, in the context of this computer system, are defined as the combination of foreground (real-time) and background processing techniques into one system. One of the most difficult general computing problems is the real-time application with its severe requirements for extreme speed and capacity. Since the computer system design is on a real-time base, it is well qualified for a mixture of applications in a multiusage environment. Many hardware features that are valuable for real-time applications are equally useful in background processing, but in different ways. The major features that make this system suitable for multiusage applications are described in the following paragraphs.

Multilevel, Priority Interrupt System. In a multiusage environment, many elements operate simultaneously and asynchronously. Thus, an efficient priority interrupt system is essential. The source of each interrupt is automatically identified and responded to according to its priority. For further flexibility, each level can be individually disarmed (to discontinue input acceptance) and disabled (to defer responses). Use of the disarm/disable feature makes programmed dynamic reassignment of priorities quick and easy, even while a real-time process is in progress.

Programs that deal with interrupt signals from special equipment often require checkout before the equipment is actually available. To permit simulating this special equipment, any external interrupt level can be "triggered" by the CPU through execution of a single instruction. This capability is also useful in establishing a modified hierarchy of responses. For example, in responding to a high priority interrupt after the urgent processing is completed, it may be desirable to assign a lower priority to the remaining portion so that the interrupt system is free to respond to other critical stimuli. The interrupt routine can accomplish this by "triggering" a lower priority level, which processes the remaining data only after other interrupts have been handled.

READ DIRECT and WRITE DIRECT instructions (described in Chapter 3) allow the program to acknowledge an I/O interrupt condition, read the status of interrupts, and control the individual levels of the priority interrupt system.

Nonstop Operation. When connected to special devices (on a ready/resume basis), the computer may be excessively delayed if the specific device does not respond quickly. A built-in watchdog timer assures that the computer cannot be delayed for an excessive length of time.

Real-Time Clocks. Many real-time functions must be timed to occur at specific instants. Other timing information is also needed; for example, elapsed time since a given event, or the current time of day. The computer system provides two real-time clocks, one with varying degrees of resolution, to meet these needs. These clocks also facilitate handling separate time bases and relative time priorities.

Rapid Context Switching. When responding to a new set of interrupt-initiated circumstances, a computer system must preserve the current operating environment for continuance later, while setting up the new environment. This changing of environments must be done quickly, with a minimum of "overhead" time costs. In this computer system, relevant information about the current environment (instruction address, status indicators, etc.) is retained in a 32-bit program status doubleword (PSD). When an interrupt occurs, the current PSD is automatically stored at an arbitrary location in memory; and the interrupt-servicing routine begins, following the location into which the PSD is stored. At the end of the interrupt-servicing routine, the PSD is restored and the interrupt level cleared.

Memory Protection. Both foreground (real-time) and background programs can be run concurrently in this computer system, since a real-time program is protected against destruction or alteration by an unchecked background program. The protect feature prevents accessing protected areas of memory for specified combinations of reading, writing, and instruction acquisition. The feature guarantees that protected memory cannot be written into by a program residing in unprotected memory. This feature also prevents background programs from executing instructions that could change the I/O system or the protection system. The protection pattern can be changed very quickly.

<u>Input/Output</u>. Because of the wide range of capacities and speeds, the computer system simultaneously satisfies the needs of many different application areas economically, both in terms of equipment and programming.

#### STANDARD AND OPTIONAL FEATURES

The basic Xerox 530 system has the following standard features:

- A CPU that includes

- Main memory of 8K words.

- Extended arithmetic unit (including multiply/ divide).

- Processor control panel.

- Two real-time clocks.

- Memory protection feature.

- Interrupt master including 16 levels of interrupt priority.

- Power Monitor.

- Input/Output Processor (IOP) with 16 channels.

- Remote assistance terminal connection.

The system may also include the following optional features:

- Memory in 8K increments to a maximum of 64K.

- Floating-point arithmetic instructions.

- Field addressing instructions.

- Up to 24 external interrupt levels (two optional groups of 12).

- External interface (Direct I/O).

- An additional input/output processor with 12 channels.

- Four ASR, KSR Teletype models available (keyboard/printer required as operator's console).

- Up to two Direct Memory Attachments.

#### **INFORMATION NOMENCLATURE AND FORMATS**

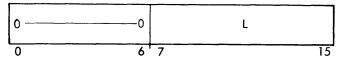

The binary digit, or bit, is the most basic unit of digital information. Depending upon the context, a bit may be described by its binary value (0 or 1), status (off or on), condition (false or true), or other dichotomous attributes. A group of bits that are functionally related is commonly referred to as a "field". Except for fields that are used as operands for field addressing instructions, all fields have fixed formats and parameters (length, boundaries, and positional notations). The parameters of operands (containing from 1 to 16 bits) for field address instructions, described in Chapter 3, are defined by the software. Common "fixed" fields are bits, bytes, words, and doublewords.

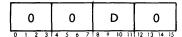

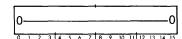

The parameters of a fixed word, as illustrated, are 16 contiguous bits, a unique position (0 through 15) for each bit, and word boundaries that occur between bit 15 of one word and bit 0 of the next word.

The format of a data word for fixed point arithmetic operation is

Bit position 0 contains a sign bit which is 0 if the integer is positive or a 1 if the integer is negative. Bit positions 1-15 represent the value of the integer. Bit position 1 is the most significant bit; bit position 15 is the least significant bit. The binary point is assumed to be on the right boundary.

Negative numbers are expressed in the two's complement.

For logical operations, a word is considered to be 16 bits without sign.

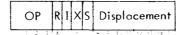

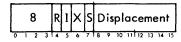

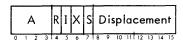

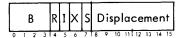

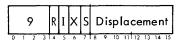

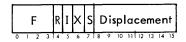

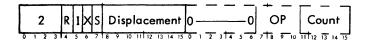

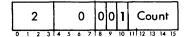

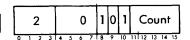

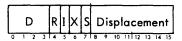

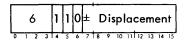

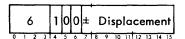

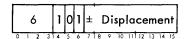

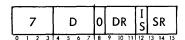

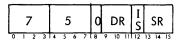

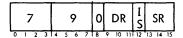

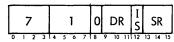

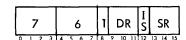

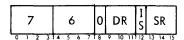

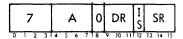

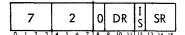

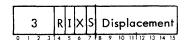

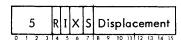

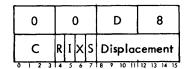

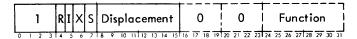

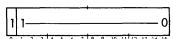

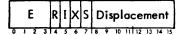

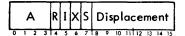

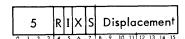

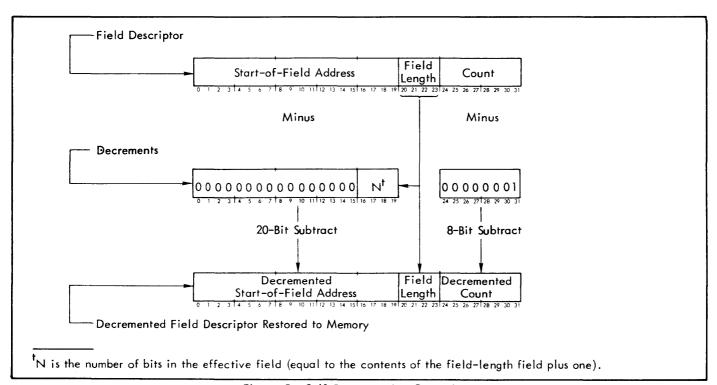

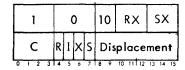

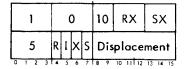

The format for a typical one-word instruction is

Bit positions 0-3 contain the operation code (OP). The operation code and format for each instruction are described in Chapters 3 or 4.

Bit positions 4-7 (R, I, X, S) comprise an address-control field. Refer to "Effective Address Computation" for further details.

Bit positions 8–15 contain a displacement value. Refer to "Effective Address Computation" and Chapters 3 or 4 for further details.

When the parameters of a byte (eight contiguous bits) are fixed, a byte is either the most significant half of a word (byte 0) or the least significant half of a word (byte 1). Bit positions within a byte are designated as 0 through 7. Byte boundaries occur between bit 7 of one byte and bit 0 of the next byte. Byte boundaries between bytes of different words coincide with the word boundaries.

|   |   | В | yte  | 0    |     |   | В | yt  | е | 1 |   |  |

|---|---|---|------|------|-----|---|---|-----|---|---|---|--|

| 0 | 1 | 2 | . 14 | 5. 1 | 1,3 | į |   | - 3 | 4 | 2 | ā |  |

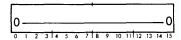

The parameters of a doubleword are always fixed. The individual bits are numbered 0 through 31.

The first 16 bits (0-15) comprise the most significant word and the second 16 bits (16-31) comprise the least significant word. Doubleword boundaries occur between bit 31 of one doubleword and bit 0 of the next doubleword. The general format of a doubleword is

| Most Significant Word          | Least Significant Word                     |

|--------------------------------|--------------------------------------------|

| र १४ अ.च. च राहर स्थाप माध्याप | 3 17 18 19 20 21 22 20 14 21 26 2 1.6 29 5 |

A doubleword is always referred to by the address of the most significant word. As part of a Program Status Doubleword, an I/O Control Doubleword, a Field Descriptor required for field addressing instructions, or as part of doubleword operands, the most significant word of a doubleword may have either an even or odd address.

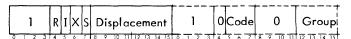

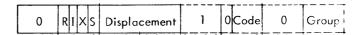

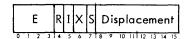

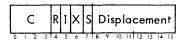

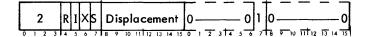

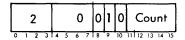

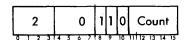

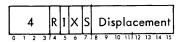

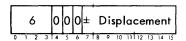

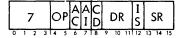

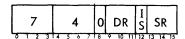

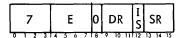

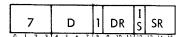

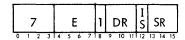

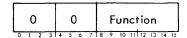

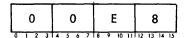

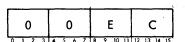

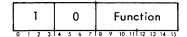

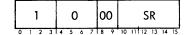

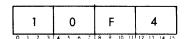

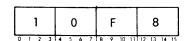

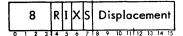

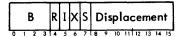

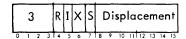

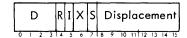

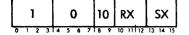

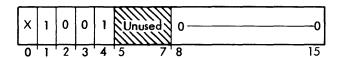

Field Addressing, General Register, and Multiple Register instructions, as described in Chapter 3, are two-word instruction sequences which have the following format:

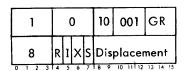

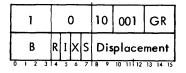

| 1       | 0 |   |   |   | Function              |  |  |  |  |

|---------|---|---|---|---|-----------------------|--|--|--|--|

| ОР      | R | I | Х | S | Displacement          |  |  |  |  |

| 0 1 2 3 | 4 |   |   | , | 8 9 10 11 12 17 14 1- |  |  |  |  |

For these instructions, the first word is always a READ DIRECT (Mode 0) instruction. As such, the recommended coding for the first word is as illustrated. The format and coding of the second word is similar to that described above for the typical one-word instruction.

A two-word instruction sequence is also used to exit from an interrupt-servicing routine. The format is similar to that illustrated above, except the first word is coded as a WRITE DIRECT (Mode 0).

The specific format (and recommended coding, when applicable) for each instruction is shown in Chapter 3.

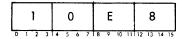

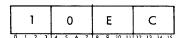

Hexadecimal digits (each equivalent to four bits) are commonly used when referring to binary information. Thus, a

four-bit field (e.g., operation code) may be expressed as one hexadecimal character, a byte may be expressed as a string of two hexadecimal digits, a word as a string of four hexadecimal digits, and a doubleword as a string of eight hexadecimal digits. The 16 configurations of four bits and corresponding decimal and hexadecimal digits are shown below.

| Binary | Decimal | Hexadecimal |

|--------|---------|-------------|

| 0000   | 0       | 0           |

| 0001   | 1       | 1           |

| C010   | 2       | 2           |

| 0011   | 3       | 3           |

| 0100   |         |             |

| 0100   | 4       | 4           |

| 0101   | 5       | 5           |

| 0110   | 6       | 6           |

| 0111   | 7       | 7           |

|        |         |             |

| 1000   | 8       | 8           |

| 1001   | 9       | 9           |

| 1010   | 10      | Α           |

| 1011   | 11      | <b>B</b>    |

| 1100   | 12      | С           |

| 1101   | 13      | D           |

| 1110   | 14      | E           |

| 1111   | 15      | F           |

|        |         |             |

Note that within this manual (except for format diagrams) a hexadecimal number is displayed as a string of hexadecimal digits enclosed by single quotes and preceded by the letter "X". For example, the binary number 01011010 is expressed in hexadecimal notation as X'5A'.

Although hexadecimal notation is generally used to denote address and data values, decimal notation (where it is more meaningful or customary) may be used. Decimal/hexadecimal conversions are performed by assembler systems.

## 2. SYSTEM ORGANIZATION

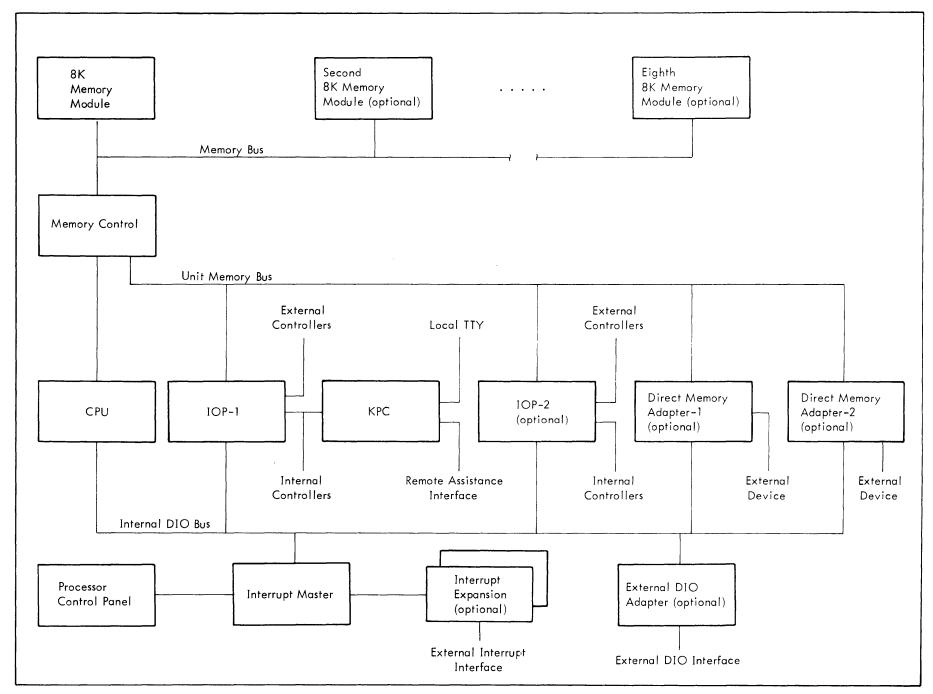

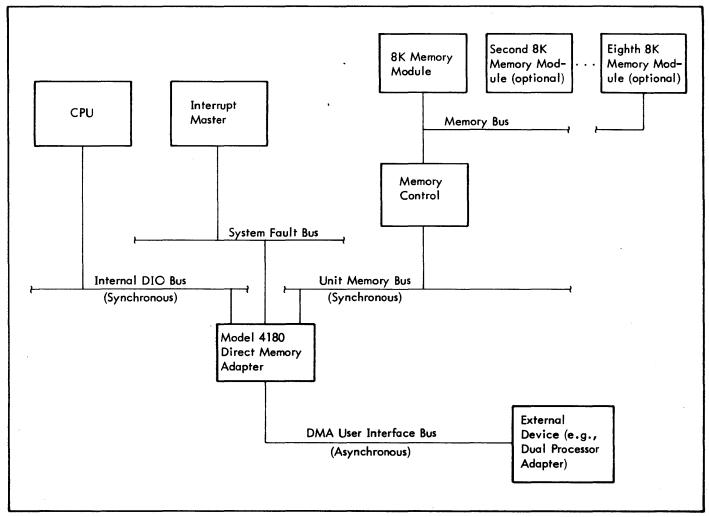

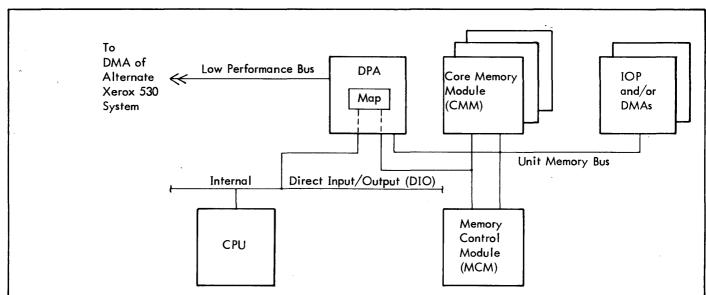

A Xerox 530 computer system, as illustrated in Figure 1, may be comprised of standard and optional units. A functional description of the main memory, central processor unit (CPU), interrupt system, fault system, and interconnecting buses is given in this chapter. The input/output processors (IOPs) and related input/output instructions are described in Chapter 4. The processor control panel (PCP) and related operating procedures are described in Chapter 5.

#### **BUSES**

The various units of the computer system are interconnected by three buses. The "memory" bus connects the Memory Control to all memory modules. The "unit memory" bus is used by all units that require direct access to memory with the exception of the CPU, which connects directly to memory control logic. The "internal Direct I/O (DIO)" bus provides control interconnections between the CPU, interrupt system, external DIO Interface, IOPs, and Direct Memory Adaptors.

#### **MAIN MEMORY**

The memory system, which operates synchronously with the other central system components, is composed of magnetic core memory modules (CMM). The storage capacity of each memory module is 8K words, with each word consisting of 16 data bits plus two parity bits (one parity bit for each byte of the word). The memory capacity ranges from a minimum of 8K words to a maximum of 64K words, in 8K word increments.

When the memory system is 64K words, the memory is "wraparound" or circular, where the next location after 64K-1 is location 0. If a system has less than 64K words, any attempt to address a nonexistent location for either a fetch or store operation results in a machine fault interrupt.

The main memory may be accessed via one of four (maximum) access paths to the unit memory bus and by the CPU. Each access path of the unit memory bus is used by an IOP or a Direct Memory Adapter. Memory is addressed identically by all units (including the CPU) and only one memory access may take place during any instant of time. If two or more accesses to memory are attempted simultaneously, the conflict is resolved in accordance with the following priority: Direct Memory Adapter-2 (highest priority), IOP-2, IOP-1, Direct Memory Adapter-1, CPU (lowest priority).

#### CENTRAL PROCESSING UNIT

The central processing unit (CPU) is the primary controlling element for most system functions. Control intercommunications between the CPU, the interrupt system, external DIO adapter, IOPs, and Direct Memory Adapters are accomplished via the internal DIO bus.

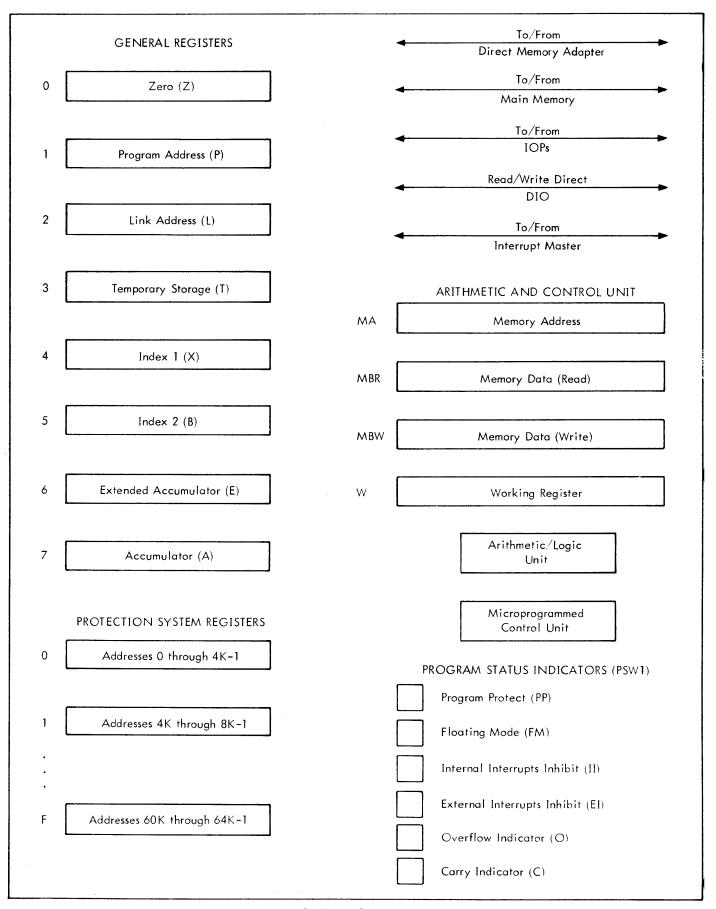

Basically, the CPU consists of registers, an arithmetic logic unit, and a microprogrammed control unit (see Figure 2).

#### **GENERAL REGISTERS**

These eight registers are used for various purposes by a program. The address, designation, and function of each general register are as follows:

| Address | Designation | Function                    |  |  |

|---------|-------------|-----------------------------|--|--|

| 0       | Z           | Zero-Source                 |  |  |

| 1       | P           | Program Address             |  |  |

| 2       | L           | Link Address                |  |  |

| 3       | T           | Temporary storage           |  |  |

| 4       | X           | Index 1 (post-index)        |  |  |

| 5       | В           | Index 2 (pre-index or base) |  |  |

| 6       | E           | Extended accumulator        |  |  |

| 7       | А           | Accumulator                 |  |  |

The general registers are addressable by General Register instructions, COPY instructions, READ DIRECT (Mode 0) instructions, and WRITE DIRECT (Mode 0) instructions, as described in Chapter 3.

#### PROTECTION SYSTEM REGISTERS

These 16 registers and a protect violation interrupt level comprise a protection system that guarantees the integrity of a master- or executive-mode (foreground) program while another (background) program is concurrently being executed. The protection system provides both operation protection and memory write protection. Each bit in these 16 registers (or words) is associated with a specific block of 256 consecutive locations in main memory. Bit 0 of protection register 0 is associated with main memory locations X'0000' through X'00FF', bit 1 of protection register 0 is

Figure 1. Xerox 530 Central System Block Diagram

Figure 2. Central Processing Unit

associated with main memory locations X'0100' through X'01FF', and bit 15 of protection register X'F' is associated with main memory locations X'FF00' through X'FFFF'. A protect bit of "0" designates an unprotected memory block and a protect bit of "1" designates a protected block.

Each of the protection system registers can be loaded individually by executing a WRITE DIRECT (Mode 0) instruction having a function value of X'8r', where r is a hexadecimal digit that designates the protection register that is to be loaded with the contents of the accumulator (A register). Thus, the protect bits for 16 memory blocks (4096 words of main memory) can be set up by executing a single instruction.

Operation of the protection system is under control of the key-operated switch on the processor control panel (see Chapter 5). If the protection system is enabled, the following rules apply:

- 1. Privileged READ DIRECT and WRITE DIRECT instructions can be executed only if they are accessed from protected memory. If a privileged instruction is accessed from unprotected memory, the instruction is not executed; instead, the protect violation interrupt level is triggered. Note that two-word instruction sequences for Field Addressing, General Register, and Multiple Register instructions, as well as the SET FLOATING MODE instruction, are not privileged.

- 2. An instruction accessed from unprotected memory can be immediately followed by an instruction accessed from protected memory only in response to an interrupt condition. If an instruction is accessed from protected memory and the immediately preceding instruction was accessed from unprotected memory, the instruction is not executed (unless it is in response to an interrupt condition); instead, the protect violation interrupt level is triggered. This rule applies to branching from unprotected memory to protected memory as well as to executing an instruction in protected memory as the next instruction in normal sequence after an instruction in unprotected memory.

- 3. A STORE ACCUMULATOR (STA) or an INCREMENT MEMORY (IM) instruction can be used to alter protected memory only if the instruction is accessed from protected memory. If an attempt is made to alter protected memory with an instruction accessed from unprotected memory, the operation is not performed; instead, the protect violation interrupt level is triggered.

#### ARITHMETIC AND CONTROL UNIT

The arithmetic and control unit contains the necessary registers and control logic to access general registers or main memory, to modify instruction addresses, to perform arithmetic and logical operations, to provide indications of computational results, and to preserve interrupt status information. Basically, the arithmetic and control unit consists

of registers, program status indicators, and a bussed arithmetic/logic unit with control provided by a microprogrammed control unit built around a read-only memory.

The MA (Memory Address), MBR (Memory Buffer Read), and MBW (Memory Buffer Write) registers are used to access main memory and provide temporary storage for information read out or written into main memory. The W (Working) register is an internal register and is not programmable; however, its contents may be displayed by the indicators on the processor control panel. The contents of the W register are used when generating effective addresses or effective instructions.

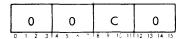

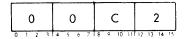

#### PROGRAM STATUS DOUBLEWORD

Critical control conditions of the CPU are defined by the Program Status Doubleword (PSD). When stored in main memory, the first (most significant) word of a PSD may occupy a location with an even address or an odd address and the second word must occupy the next contiguous location. The format of a PSD, as stored in memory, is as follows:

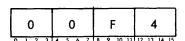

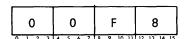

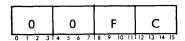

| 0       | 0       | F     E                                     | Address                 |

|---------|---------|---------------------------------------------|-------------------------|

| 0 1 2 3 | 4 5 6 7 | 9 10 11112 13 14 15 16 17 16 19 20 21 22 23 | 24 25 25 27 28 29 30 31 |

The first word of a PSD contains the following six status bits:

| Bit<br>Position | Status Bit<br>Designation | Function                   |

|-----------------|---------------------------|----------------------------|

| 8               | PP                        | Protected Program          |

| 9               | FM                        | Floating Mode              |

| 10              | II                        | Internal Interrupt Inhibit |

| 11              | EI                        | External Interrupt Inhibit |

| 14              | 0                         | Overflow                   |

| 15              | С                         | Carry                      |

Other bit positions are unassigned and must contain a zero. The second word of a PSD contains a program address. The first word of the current PSD is contained within an internal register (PSW); the second word of the current PSD is contained within general register 1 (P). The contents of the first word of the current PSD may be displayed by indicators on the Processor Control Panel.

If the Protected Program (PP) bit is a 1, the current program is located in an area of main memory that is protected; otherwise, the PP bit is a 0.

If the Floating Mode (FM) bit is a 1, the CPU is conditioned to perform Floating Point instructions (optional).

The Internal and External Interrupt inhibit bits determine whether a program interruption can occur. If an interrupt inhibit bit is a 0, the respective set of interrupt levels are allowed to interrupt the program being executed. Conversely; if an interrupt inhibit bit is a 1, the respective set of interrupt levels are inhibited from interrupting the program. Inhibiting interrupt levels also removes them from the interrupt system priority chain, allowing a lower-priority interrupt level to interrupt the program. Note, however, that the first six standard interrupt levels cannot be inhibited; and, that the six integral (external) interrupt levels within the standard group may be controlled with the Internal Interrupt inhibit bit.

The Overflow and Carry bits reflect the results of various operations. For arithmetic operations, the Overflow bit is set to a 1 if an overflow occurred and the Carry bit is set to a 1 if a carry occurred from the most significant (sign) position of the adder. Also, on a subtract operation, the Carry bit is set to a 1 if a "borrow" occurred from the sign position of the adder. For nonarithmetic operations (i.e., I/O operations), the Overflow and Carry bits may reflect status information relevant to the operation. When applicable, the significance of the Overflow and Carry bits are described under each instruction.

When an interrupt occurs, the current PSD is automatically stored in main memory and another PSD is loaded into the PSW and P registers to become the active PSD. The first PSD remains inactive in main memory until it is restored into the PSW and P registers (normally, when exiting from an interrupt-servicing routine).

#### INTERRUPT SYSTEM

Physically, the modular interrupt system is composed of one standard group of 16 interrupt levels and one or two optional groups, each with 12 external interrupt levels (see Table 1). Thus, a minimum interrupt system has 16 interrupt levels, an intermediate system has 28 levels, and a maximum system has 40 interrupt levels.

Each interrupt level has a unique priority, as listed in column 2, Table 1; a unique memory location, as listed in column 1; and, an assignment, as listed in column 6. Other operational and control characteristics are described in subsequent paragraphs.

#### STANDARD GROUP

The 16 interrupt levels that comprise the standard group are divided into two functional groups: internal and integral (or external). The functional assignments of each interrupt level is described below.

Power-On/Power-Off. These two interrupt levels (memory locations X'100' and X'101') are essential to the power monitor feature. Whenever an imminent power failure is sensed, the power-off interrupt level is triggered and a "power-off" routine is entered that typically stores (saves) volatile information (e.g., registers, program status doublewords, etc.) in main memory, halts all I/O operations, and ends with the CPU in a waiting state. When the power returns to a safe limit, the power-on interrupt level is triggered and a "power-on" routine is entered that typically restores information from main memory and prepares the system to resume processing.

These two interrupt levels operate automatically and continuously. They cannot be inhibited by the Internal Interrupt (II) bit of the Program Status Doubleword. Also, they are not addressable; hence, they cannot be controlled by a WRITE DIRECT instruction or interrogated with a READ DIRECT instruction.

If the power-on and power-off routines are both executed within two milliseconds, the power monitor feature is able to preserve the system, even under the most adverse condition (i.e., a power failure occurs immediately after the power assumed a normal value). This time constraint is imposed because of the following reasons:

- 1. The relative priority of the two interrupt levels precludes the power-off routine from becoming active until the power-on routine is completed (system is restored to a predictable state).

- The primary power will remain at a safe limit for two milliseconds after an imminent power failure has been detected.

Note that when the power-on interrupt is active, the program protect feature is disabled (status of PSD 8, the PP bit, is ignored); and the program may execute instructions from any portion of memory.

Counter 2/Counter 1 (Real-Time Clocks). These two standard interrupt levels may be triggered by pulses from internal or external sources. Counter 1 has a constant frequency of 500 Hz; counter 2 may be set, at installation time, to any of four frequencies - the commerical line frequency, 2kHz, 8kHz, or a user-supplied external signal. When a clock pulse is received by one of the counter interrupt levels (and the level is armed and enabled), the value in the dedicated interrupt location is incremented by 1, and the level is cleared and re-armed. If the value in the dedicated interrupt location is zero after being incremented, the corresponding counter-equals-zero interrupt level is then triggered. All other interrupt levels (including the counterequals-zero interrupt levels) are processed by interruptservicing routines and are designated as "normal" interrupt levels. The counter interrupt levels are addressable (group code X'0') and their status can be read with a READ DIRECT (Mode 1) instruction. They can be armed, disarmed, enabled, disabled, or triggered. Since a counter interrupt level never goes to the active state in normal operations,

Table 1. Interrupt System

| Dedi<br>Inter<br>Loca<br>Dec.                                                    |                                                                                  | Priority<br>Level                                                    | Read<br>Status<br>Register<br>Bit                            | Set<br>Active<br>Register<br>Bit                                | Write<br>Direct<br>Register<br>Bit                                                     | Assignment                                                                                                                                                                         | Availability                                                                                                         | PSD<br>Inhibit<br>Bit                                          | Read/Write<br>Group Code                                     |

|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------|--------------------------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------------|

|                                                                                  | 176%                                                                             | Level                                                                | DII                                                          | DII                                                             |                                                                                        | Assignment                                                                                                                                                                         | Availability                                                                                                         | DII                                                            | Group Code                                                   |

| 256<br>257<br>254<br>255<br>258<br>259<br>264<br>265<br>262<br>263<br>266<br>267 | 100<br>101<br>FE<br>FF<br>102<br>103<br>108<br>109<br>106<br>107<br>10A          | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11                | None<br>None<br>2<br>3<br>0<br>1<br>8<br>9<br>6<br>7<br>10   | None <sup>†</sup> None None None None <sup>†</sup> None † 10 11 | None <sup>†</sup> None <sup>†</sup> 2 3 None <sup>†</sup> None <sup>†</sup> 8 9 6 7 10 | Power on Power off Counter 2 Counter 1 Machine Fault Protection Violation Integral 5 <sup>t†</sup> Integral 6 <sup>t†</sup> Input/Output Control Panel Counter 2 = 0 Counter 1 = 0 | Standard | None None None None None II II II II                           | None None X'0' X'0' X'0' X'0' X'0' X'0' X'0' X'0             |

| 268                                                                              | 10C                                                                              | 13                                                                   | 12                                                           | 12                                                              | 12                                                                                     | Integral 1 <sup>tt</sup>                                                                                                                                                           | Standard                                                                                                             | II                                                             | X'0'                                                         |

| 269                                                                              | 10D                                                                              | 14                                                                   | 13                                                           | 13                                                              | 13                                                                                     | Integral 2 <sup>tt</sup>                                                                                                                                                           | Standard                                                                                                             | II                                                             | X'0'                                                         |

| 270<br>271                                                                       | 10E<br>10F                                                                       | 15<br>16                                                             | 14<br>15                                                     | 14<br>15                                                        | 14<br>15                                                                               | Integral 3 <sup>tt</sup><br>Integral 4 <sup>tt</sup>                                                                                                                               | Standard<br>Standard                                                                                                 | II                                                             | X'0'<br>X'0'                                                 |

| 272<br>273<br>274<br>275<br>276<br>277<br>278<br>279<br>280<br>281<br>282<br>283 | 110<br>111<br>112<br>113<br>114<br>115<br>116<br>117<br>118<br>119<br>11A<br>11B | 17<br>18<br>19<br>20<br>21<br>22<br>23<br>24<br>25<br>26<br>27<br>28 | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10         | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10            | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10                                   | Designated by<br>Customer.                                                                                                                                                         | First optional<br>group of<br>12 external<br>interrupts                                                              | EI<br>EI<br>EI<br>EI<br>EI<br>EI<br>EI<br>EI<br>EI             | X'5'<br>X'5'<br>X'5'<br>X'5'<br>X'5'<br>X'5'<br>X'5'<br>X'5' |

| 284<br>285<br>286<br>287<br>288<br>289<br>290<br>291<br>292<br>293<br>294<br>295 | 11C<br>11D<br>11E<br>11F<br>120<br>121<br>122<br>123<br>124<br>125<br>126<br>127 | 29<br>30<br>31<br>32<br>33<br>34<br>35<br>36<br>37<br>38<br>39<br>40 | 12<br>13<br>14<br>15<br>0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | 12<br>13<br>14<br>15<br>0<br>1<br>2<br>3<br>4<br>5<br>6         | 12<br>13<br>14<br>15<br>0<br>1<br>2<br>3<br>4<br>5<br>6                                | Designated by<br>Customer.                                                                                                                                                         | Second<br>optional<br>group of<br>12 external<br>interrupts.                                                         | EI<br>EI<br>EI<br>EI<br>EI<br>EI<br>EI<br>EI<br>EI<br>EI<br>EI | X'5' X'5' X'5' X'6' X'6' X'6' X'6' X'6'                      |

<sup>&</sup>lt;sup>t</sup>These bits need not be set to zero by program (they are ignored by hardware).

the level must not be programmed into that state. These two levels can not be inhibited by the II bit of the Program Status Doubleword. Counter 2 has the third highest priority and counter 1 has the fourth highest priority within the interrupt system.

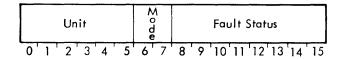

Machine Fault. This interrupt level is triggered whenever the Fault Register is nonzero, signifying that an abnormal condition has been detected and the correct PCP switches are enabled (see "Fault System"). The status of the machine fault interrupt level may be read into bit position 0 of the

tt Connected and used as an external interrupt level.

A register by executing a READ DIRECT (Mode 1) instruction. This interrupt level cannot be controlled with a WRITE DIRECT (Mode 1) instruction nor can it be inhibited by the Internal Interrupt bit of the Program Status Doubleword.

Protection Violation. This sixth highest priority interrupt level is part of the protection system. This interrupt level is triggered if the protection system is enabled when a protection violation is encountered. The status of the interrupt level is read into bit position 1 of the A register whenever a READ DIRECT (Mode 1) instruction is executed. This interrupt level cannot be controlled with a WRITE DIRECT (Mode 1) instruction nor can it be inhibited by the Internal Interrupt control bit of the Program Status Doubleword.

Input/Output. The input/output interrupt level accepts interrupt signals from standard I/O systems. An I/O interrupt-servicing routine must contain an ACKNOWLEDGE I/O INTERRUPT (AIO) instruction, described in Chapter 4, that identifies the source and cause of an I/O interrupt. The I/O interrupt level is addressed with a group code of X'O'. The state of the interrupt level may be read into bit 6 of the A register by executing a READ DIRECT (Mode 1) instruction. The interrupt level may be controlled by a WRITE DIRECT (Mode 1) instruction and bit 6 of the A register. The interrupt level may be inhibited by the Internal Interrupt bit of the Program Status Doubleword.

Control Panel. The control panel interrupt level may be activated by either the INTERRUPT switch on the processor control panel or by a special control sequence on the operator's keyboard (see Chapter 5). The interrupt level can be triggered by the computer operator to initiate a specific routine. The control panel interrupt level is addressed with a group code of X'0'. The state of this interrupt level may be read into bit position 7 of the A register by executing a READ DIRECT (Mode 1) instruction. The interrupt level may be controlled with a WRITE DIRECT (Mode 1) instruction and bit 7 of the A register. The interrupt level may be inhibited by the Internal Interrupt bit of the Program Status Doubleword.

Counter-Equals-Zero. As described under "Counter 2/ Counter 1" above, a counter-equals-zero interrupt level is triggered whenever the corresponding counter (memory location) is incremented to the value of zero as a result of a count pulse. Triggering a counter-equals-zero interrupt level does not affect the counting process. The counter-equals-zero interrupt levels may be addressed with a group code of X'0'. The state of counter two-equals-zero may be read into bit position 10 of the A register and the state of counter one-equals-zero may be read into bit position 11 of the A register when a READ DIRECT (Mode 1) instruction is executed. Both interrupt levels may be

controlled with a WRITE DIRECT (Mode 1) instruction and both interrupt levels may be inhibited by the Internal Interrupt bit of the Program Status Doubleword.

Integral Interrupt Levels. There are six integral interrupt levels within the standard group that may be used by the customer as external interrupts. The interrupt levels are addressed with a group code of X'0'. The state of each interrupt level may be read with a READ DIRECT instruction and controlled with a WRITE DIRECT instruction. The interrupt levels may be inhibited by the Internal Interrupt bit of the Program Status Doubleword.

Note: Care must be exercised in assigning integral five and integral six interrupt levels since foreground tasks connected to these interrupts can not utilize certain RBM or BCM monitor services (e.g., requests for monitor input/output services can not be made from these interrupt levels).

#### OPTIONAL INTERRUPT GROUPS

Each optional interrupt group consists of 12 external interrupt levels. All 24 optional interrupt levels may be inhibited by the External Interrupt bit of the Program Status Doubleword. The first 16 optional interrupt levels are addressed with a group code of X'5' while the last eight optional interrupt levels are addressed with a group code of X'6'. All optional interrupt levels may be read with a READ DIRECT (Mode 1) instruction and controlled with a WRITE DIRECT (Mode 1) instruction.

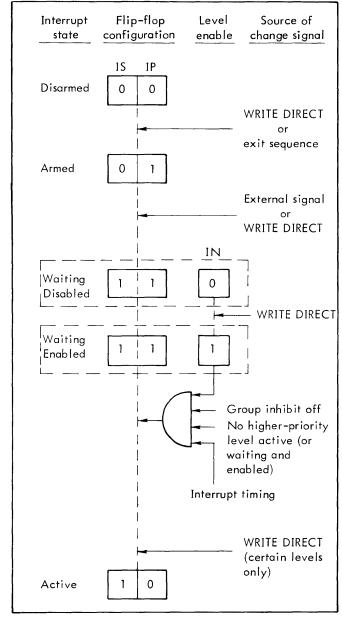

#### INTERRUPT LEVEL STATES

Each interrupt level is controlled on an individual basis by three flip-flops. Two of the flip-flops define four mutually exclusive states: disarmed, armed, waiting, and active. The third flip-flop enables or disables the level. The various states and the condition causing changes in state (see Figure 3) are described in the following paragraphs:

<u>Disarmed.</u> When an interrupt level is in the disarmed state, no signal to that interrupt level is admitted; that is, no record is retained of the signal nor is any program interrupt caused by it at any time.

Armed. When an interrupt level is in the armed state (IP flip-flop is on), it is capable of accepting and remembering an interrupt signal. The receipt of such a signal advances the interrupt level to the waiting state (IS flip-flop is turned on).

Figure 3. Interrupt Level Operation

<u>Waiting.</u> When an interrupt level in the armed state receives an interrupt signal, it advances to the waiting state, and remains in the waiting state until it is allowed to advance to the active state. (IP and IS flip-flops are both on in the waiting state.)

If the level-enable flip-flop (IN) is off, the interrupt level can undergo all state changes except that of moving from the waiting to the active state. Furthermore, if this flip-flop is off, the interrupt level is completely removed from the chain that determines the priority of access to the CPU. Thus, an interrupt level in the waiting state with its level-enable in the off condition does not prevent an enabled, uninhibited interrupt level of lower priority from moving to the active state.

When an interrupt level is in the waiting state, the following conditions must all exist simultaneously before the level advances to the active state:

- The level is enabled (i.e., its level enable flip-flop, IN, is a 1).

- The group inhibit (if applicable) is off (i.e., the appropriate inhibit is a 0).

- 3. No higher-priority interrupt level is in the active state (or is in the enabled, waiting state with its inhibit off).

- 4. The CPU is in an interruptible phase of operation.

Active. When a normal interrupt level (any interrupt level except Counter 2 or Counter 1) meets all of the conditions necessary to permit it to move from the waiting state to the active state, it is permitted to do so by being acknowledged by the computer, which then automatically stores the current PSD at the location specified by the contents of the location associated with the level. The first instruction of the interrupt-servicing routine is then taken from the location following the stored PSD. A new interrupt cannot occur until after the execution of this first instruction.

A normal interrupt level remains in the active state until it is removed from the active state by a specific configuration of the WRITE DIRECT (WD) instruction, followed by an LDX instruction (an "exit sequence"), or if the same active level is armed or disarmed via an appropriate WD instruction. An interrupt-servicing routine can itself be interrupted (whenever a higher-priority interrupt level meets all of the conditions for becoming active) and then continued (after the higher-priority interrupt level is removed from the active state). However, an interrupt-servicing routine cannot be interrupted by a lower-priority interrupt level as long as its interrupt level remains in the active state. Normally, the interrupt-servicing routine returns its interrupt level to the armed state and transfers program control back to the point of interrupt by means of an interrupt routine exit sequence (see "Interrupt Routine Entry and Exit").

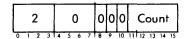

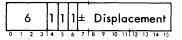

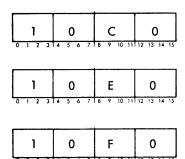

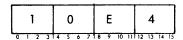

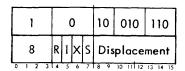

#### READING INTERRUPT LEVELS

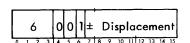

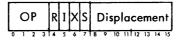

Except for the first two interrupt levels (power on and power off), the state of all interrupt levels may be read into the A register by executing a READ DIRECT (Mode 1) instruction. The format of a typical READ DIRECT (Mode 1) instruction is as follows:

The effective instruction (shown enclosed within broken lines) is generated from the original instruction in the same manner as an effective address; i.e., the displacement value is modified as specified by the "RIXS" bits.

The recommended method for producing the appropriate configuration of the effective instruction is to indirectly address a memory location that contains the appropriate bit configuration.

Bits 0-3 of the effective instruction must be coded as X'1' to specify the interrupt control mode. (See READ DIRECT instruction, Chapter 3, for other control modes.)

Bits 4 and 8-11 must be coded as zeros.

Bits 5, 6, and 7 (the "code" field) may be coded to one of three values to specify a read operation to be performed (read one of the three flip-flops associated with each interrupt level).

| Code Field<br>Bits 5 6 7 | Read Function                                                                                                                         |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| 001                      | Set to a 1 the accumulator bits corresponding to each interrupt level that is in the Armed or Waiting state. Read IP flip-flops.)     |

| 010                      | Set to a 1 the accumulator bits corresponding to each interrupt level that is in the Waiting (or Active) state. (Read IS flip-flops.) |

| 100                      | Set to a 1 the accumulator bits corresponding to each interrupt level that is Enabled. (Read IN flip-flops.)                          |

The A register bit format for the READ DIRECT (Mode 1) instruction is shown in column 3 of Table 1. For READ DIRECT group code X'0', bit 5 is unused and is indeterminate, and bit 4 is set to 1 if the TRACE toggle switch is in the up (on) position or set to 0 if the TRACE switch is in the down (off) position. An uninstalled interrupt level will respond with a 0 to any of the three read operations.

Bits 12-15 specify which group of interrupt levels is to be interrogated.

| Group Field<br>Value | Interrupt Group Interrogated                                                                                                                      |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| X'0'                 | Standard group. Note that the first<br>two interrupt levels (power on and<br>power off) cannot be interrogated<br>with a READ DIRECT instruction. |

| X'5'                 | The first 16 (optional) external interrupt levels.                                                                                                |

| X'6'                 | The last 8 (optional) external inter-<br>rupt levels.                                                                                             |

#### INTERRUPT SYSTEM CONTROL

The interrupt system may be controlled in the following ways:

- If the Internal Interrupt (II) bit of the Program Status Doubleword (PSD) is set to a 1, all interrupt levels within the standard group, except the first six – power on, power off, counter 2, counter 1, machine fault, and protection violation (see Table 1), are inhibited.

- If the External Interrupt (EI) bit of the PSD is set to a 1, all optional interrupt levels are inhibited.

- 3. Except for the first six interrupt levels, each interrupt level (on an individual basis as specified by assigned bits of the A register) may be set to the Active state by executing a WRITE DIRECT (Mode 1) instruction, described below.

- 4. Except for the power on, power off, machine fault, and protection violation interrupt levels, each interrupt level (on an individual basis as specified by assigned bits of the A register) may be armed, disarmed, enabled, disabled, or triggered by executing a WRITE DIRECT (Mode 1) instruction, described below.

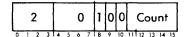

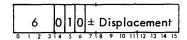

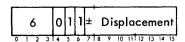

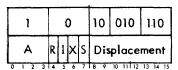

The format of a typical WRITE DIRECT (Mode 1) instruction for controlling the interrupt system is as follows:

The effective instruction (enclosed within broken lines) is generated in the same manner as an effective address; i.e., the displacement value of the original instruction is modified by the "RIXS" bits.

The recommended method for producing the appropriate configuration of the WRITE DIRECT effective instruction is to indirectly address a memory location that contains the appropriate bit configuration.

Bits 0–3 of the effective instruction must be coded as X'1' to specify the interrupt control mode. (See "WRITE DIRECT" instruction, Chapter 3, for other control modes.)

Bits 4 and 8-11 must be coded as zeros.

Bits 5, 6, and 7 (the "code" field) may be coded to any one of eight values to specify a function that is to be performed on a group of interrupt levels which is designated by the value of the "group" field (bits 12–15).

Individual interrupt levels within the designated group are further designated by the contents of the A register. The value of the "code" field and associated functions are as follows: