# Graphic7

# COMPUTER GRAPHICS DISPLAY SYSTEM

MODELS 7709/7710 TERMINAL CONTROLLER MAINTENANCE MANUAL

DANIEL WEBSTER HIGHWAY, SOUTH-NASHUA, NEW HAMPSHIRE 03061

Copyright 1981 Sanders Associates, Inc. GRAPHIC 7 is a registered trademark of Sanders Associates, Inc.

H-80-0055

## COMPUTER GRAPHICS DISPLAY SYSTEM

MODELS 7709/7710 TERMINAL CONTROLLER MAINTENANCE MANUAL

Information Products Division Federal Systems Group

**SANDERS**

DANIEL WEBSTER HIGHWAY, SOUTH-NASHUA, NEW HAMPSHIRE 03061

Copyright 1981 Sanders Associates, Inc. GRAPHIC 7 is a registered trademark of Sanders Associates, Inc. Sanders Associates, Inc., reserves the right to modify the products described in this manual and to make corrections or alterations to this manual at any time without notice.

(

Original - August 1980 Reprint - October 1980 Reprint - February 1981 Reprint - July 1981 Reprint - January 1982

## **RECORD OF CHANGES**

| CHANGE NO. DATE |         | TITLE OR BRIEF<br>DESCRIPTION | ENTERED BY        |

|-----------------|---------|-------------------------------|-------------------|

| 1               | SEPT 81 | Corrects Errors               |                   |

|                 |         |                               |                   |

|                 |         |                               |                   |

|                 | -<br>-  |                               |                   |

|                 |         |                               |                   |

|                 |         |                               |                   |

|                 |         |                               | • • • • • • • • • |

|                 |         |                               |                   |

|                 |         |                               |                   |

|                 |         |                               |                   |

|                 |         |                               |                   |

|                 |         |                               |                   |

|                 |         |                               |                   |

|                 |         |                               |                   |

|                 |         |                               |                   |

|                 |         |                               |                   |

|                 |         |                               |                   |

|                 |         |                               |                   |

|                 |         |                               |                   |

|                 |         |                               |                   |

|                 |         |                               |                   |

|                 |         |                               |                   |

|                 |         |                               |                   |

|                 |         |                               |                   |

|                 |         |                               |                   |

#### SAFETY PRECAUTIONS

The following are general safety precautions not related to any specific procedure and therefore do not appear elsewhere in this manual. These are recommended precautions that must be understood and applied during installation or maintenance of the terminal controller.

#### AVOID LIVE CIRCUITS

Observe all safety regulations at all times. Do not replace components in the terminal controller power panel assembly with power applied.

#### RESUSCITATION

When working with or near high voltages, be familiar with modern resuscitation methods.

Primary power (100 Vac to 240 Vac) is present at the power panel assembly. Line voltage of 115 Vac is present at the power supply.

Always turn off terminal controller and pull power plug before removing any cabinet- or chassis-mounted component.

#### TERMINAL CONTROLLER PROTECTION

Circuit card assemblies in the terminal controller can be damaged by transient surges.

CAUTION

Always turn off terminal controller before removing or installing any circuit card.

Always turn down brightness of display indicator before removing or installing any circuit card in terminal controller.

#### SPECIAL HANDLING FOR MOS DEVICES

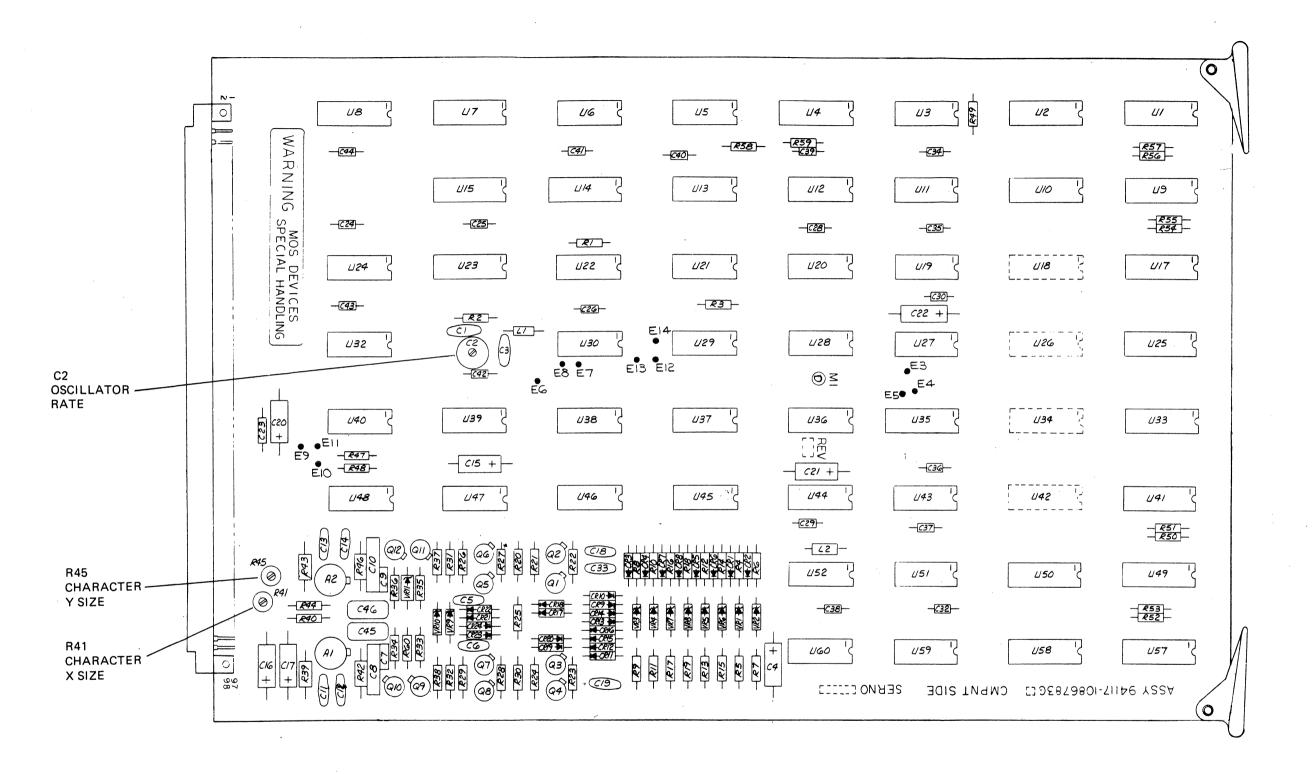

MOS devices are subject to damage caused by static charges. Assemblies that contain MOS devices are the D/A converters and character generator. When not installed in the card cage, these assemblies should be stored in black Velostat bags with the MOS warning statement printed on the outside of the bag.

CAUTION

Always handle these cards only by the card extractors or by the edges of the connector. Avoid touching the card components or the printed circuit.

## TABLE OF CONTENTS

## Section

.,

| 1.1       Introduction       1-1         1.2       Physical Description       1-1         1.3       Functional Description       1-6         1.3.1       Group 1 Circuit Cards       1-6         1.3.1.1       Display Processor       1-6         1.3.1.2       ROM Card Status Logic       1-8         1.3.1.3       Read/Write Memory       1-8         1.3.1.4       Expansion Module       1-8         1.3.1.5       Multiport Serial Interface       1-10         1.3.1.6       Parallel Interface       1-10         1.3.1.7       Graphic Controller       1-11         1.3.1.8       2-D/3-D Coordinate Converter       1-11         1.3.2       Group 2 Circuit Cards       1-11         1.3.2.2       Character Generator       1-12         1.3.2.3       Ramp/Conic Generator       1-13         1.3.2.4       Output Channel       1-13         1.3.2.5       2-D Coordinate Converter       1-13         1.4.1       Display Indicators       1-13         1.4.2       Input Devices       1-14         1.4.2.2       PHOTOPEN       1-15         1.4.2.3       Trackball, Forcestick and Data Tablet       1-15                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.2       Physical Description       1-1         1.3       Functional Description       1-6         1.3.1       Group 1 Circuit Cards       1-6         1.3.1.1       Display Processor       1-6         1.3.1.2       ROM Card Status Logic       1-8         1.3.1.3       Read/Write Memory       1-8         1.3.1.4       Expansion Module       1-8         1.3.1.5       Multiport Serial Interface       1-10         1.3.1.6       Parallel Interface       1-10         1.3.1.7       Graphic Controller       1-10         1.3.1.8       2-D/3-D Coordinate Converter       1-11         1.3.2       Group 2 Circuit Cards       1-11         1.3.2.1       Vector/Position Generator       1-12         1.3.2.2       Character Generator       1-13         1.3.2.3       Ramp/Conic Generator       1-13         1.3.2.4       Output Channel       1-13         1.3.2.5       2-D Coordinate Converter       1-13         1.4       Optional Equipment       1-13         1.4.1       Display Indicators       1-14         1.4.2.1       Keyboards       1-14         1.4.2.2       PHOTOPEN       1-15         1.                            |

| 1.3       Functional Description       1-6         1.3.1       Group 1 Circuit Cards       1-6         1.3.1.1       Display Processor       1-6         1.3.1.2       ROM Card Status Logic       1-8         1.3.1.3       Read/Write Memory       1-8         1.3.1.4       Expansion Module       1-8         1.3.1.5       Multiport Serial Interface       1-10         1.3.1.6       Parallel Interface       1-10         1.3.1.7       Graphic Controller       1-10         1.3.1.8       2-D/3-D Coordinate Converter       1-11         1.3.1.9       Floating Point Converter       1-11         1.3.2.1       Vector/Position Generator       1-11         1.3.2.2       Character Generator       1-12         1.3.2.3       Ramp/Conic Generator       1-13         1.3.2.4       Output Channel       1-13         1.3.2.5       2-D Coordinate Converter       1-13         1.4.1       Display Indicators       1-13         1.4.2       Input Devices       1-14         1.4.2.2       PhotOPEN       1-15         1.4.2.3       Trackball, Forcestick and Data Tablet       1-15         1.4.2.4       Maintenance Data Input Devices     |

| 1.3.1       Group 1 Circuit Cards       1-6         1.3.1.1       Display Processor       1-6         1.3.1.2       ROM Card Status Logic       1-8         1.3.1.3       Read/Write Memory       1-8         1.3.1.4       Expansion Module       1-8         1.3.1.5       Multiport Serial Interface       1-10         1.3.1.6       Parallel Interface       1-10         1.3.1.7       Graphic Controller       1-11         1.3.1.8       2-D/3-D Coordinate Converter       1-11         1.3.1.9       Floating Point Converter       1-11         1.3.2       Group 2 Circuit Cards       1-11         1.3.2.1       Vector/Position Generator       1-11         1.3.2.2       Character Generator       1-12         1.3.2.3       Ramp/Conic Generator       1-13         1.3.2.4       Output Channel       1-13         1.3.2.5       2-D Coordinate Converter       1-13         1.4       Optional Equipment       1-13         1.4.1       Display Indicators       1-14         1.4.2.2       HOTOPEN       1-15         1.4.2.3       Trackball, Forcestick and Data Tablet       1-15         1.4.2.4       Maintenance Data Input Devices |

| 1.3.1.1       Display Processor       1-6         1.3.1.2       ROM Card Status Logic       1-8         1.3.1.3       Read/Write Memory       1-8         1.3.1.4       Expansion Module       1-8         1.3.1.5       Multiport Serial Interface       1-10         1.3.1.6       Parallel Interface       1-10         1.3.1.7       Graphic Controller       1-10         1.3.1.8       2-D/3-D Coordinate Converter       1-11         1.3.1.9       Floating Point Converter       1-11         1.3.2       Group 2 Circuit Cards       1-11         1.3.2.1       Vector/Position Generator       1-11         1.3.2.2       Character Generator       1-12         1.3.2.3       Ramp/Conic Generator       1-13         1.3.2.4       Output Channel       1-13         1.3.2.5       2-D Coordinate Converter       1-13         1.4       Optional Equipment       1-13         1.4.1       Display Indicators       1-14         1.4.2       Input Devices       1-15         1.4.2.3       Trackball, Forcestick and Data Tablet       1-15         1.4.2.4       Maintenance Data Input Devices       1-15         1.4.3       Output Devices   |

| 1.3.1.2       ROM Card Status Logic       1-8         1.3.1.3       Read/Write Memory       1-8         1.3.1.4       Expansion Module       1-8         1.3.1.5       Multiport Serial Interface       1-10         1.3.1.6       Parallel Interface       1-10         1.3.1.7       Graphic Controller       1-10         1.3.1.8       2-D/3-D Coordinate Converter       1-11         1.3.1.9       Floating Point Converter       1-11         1.3.2       Group 2 Circuit Cards       1-11         1.3.2.1       Vector/Position Generator       1-11         1.3.2.2       Character Generator       1-12         1.3.2.3       Ramp/Conic Generator       1-13         1.3.2.4       Output Channel       1-13         1.3.2.5       2-D Coordinate Converter       1-13         1.4       Optional Equipment       1-13         1.4.1       Display Indicators       1-14         1.4.2.2       PHOTOPEN       1-15         1.4.2.3       Trackball, Forcestick and Data Tablet       1-15         1.4.2.4       Maintenance Data Input Devices       1-15         1.4.3       Output Devices       1-15         1.4.3       Output Devices       1  |

| 1.3.1.3       Read/Write Memory       1-8         1.3.1.4       Expansion Module       1-8         1.3.1.5       Multiport Serial Interface       1-10         1.3.1.6       Parallel Interface       1-10         1.3.1.7       Graphic Controller       1-10         1.3.1.8       2-D/3-D Coordinate Converter       1-11         1.3.1.9       Floating Point Converter       1-11         1.3.2       Group 2 Circuit Cards       1-11         1.3.2.1       Vector/Position Generator       1-11         1.3.2.2       Character Generator       1-12         1.3.2.3       Ramp/Conic Generator       1-13         1.3.2.4       Output Channel       1-13         1.3.2.5       2-D Coordinate Converter       1-13         1.4       Optional Equipment       1-13         1.4.1       Display Indicators       1-14         1.4.2.1       Keyboards       1-14         1.4.2.2       PHOTOPEN       1-15         1.4.2.3       Trackball, Forcestick and Data Tablet       1-15         1.4.2.4       Maintenance Data Input Devices       1-15         1.4.3       Output Devices       1-15         1.4.3       Output Devices       1-15          |

| 1.3.1.4Expansion Module1-81.3.1.5Multiport Serial Interface1-101.3.1.6Parallel Interface1-101.3.1.7Graphic Controller1-101.3.1.82-D/3-D Coordinate Converter1-111.3.1.9Floating Point Converter1-111.3.2Group 2 Circuit Cards1-111.3.2.1Vector/Position Generator1-111.3.2.2Character Generator1-121.3.2.3Ramp/Conic Generator1-131.3.2.4Output Channel1-131.3.2.52-D Coordinate Converter1-131.4Optional Equipment1-131.4.1Display Indicators1-141.4.2Input Devices1-141.4.2.3Trackball, Forcestick and Data Tablet1-151.4.3Output Devices1-151.4.3Output Devices1-151.4.3Output Devices1-161.7Equipment Supplied1-16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1.3.1.5Multiport Serial Interface1-101.3.1.6Parallel Interface1-101.3.1.7Graphic Controller1-101.3.1.82-D/3-D Coordinate Converter1-111.3.1.9Floating Point Converter1-111.3.2Group 2 Circuit Cards1-111.3.2.1Vector/Position Generator1-111.3.2.2Character Generator1-121.3.2.3Ramp/Conic Generator1-131.3.2.4Output Channel1-131.3.2.52-D Coordinate Converter1-131.4Optional Equipment1-131.4.1Display Indicators1-141.4.2Input Devices1-141.4.2.3Trackball, Forcestick and Data Tablet1-151.4.2.4Maintenance Data Input Devices1-151.4.3Output Devices1-151.4.3Output Devices1-151.4.3Output Devices1-151.4.3Output Devices1-151.4.3Duput Devices1-151.4.3Duput Devices1-151.4.3Output Devices1-151.4.3Duput Devices1-151.4.3Duput Devices1-151.4.3Duput Devices1-151.4.3Duput Devices1-151.4.3Duput Devices1-151.4.3Duput Devices1-151.4.4Informance Specification1-161.7Equipment Supplied1-16                                                                                                                                                                                                                                                           |

| 1.3.1.6Parallel Interface1-101.3.1.7Graphic Controller1-101.3.1.82-D/3-D Coordinate Converter1-111.3.1.82-D/3-D Coordinate Converter1-111.3.1.9Floating Point Converter1-111.3.2.0Group 2 Circuit Cards1-111.3.2.1Vector/Position Generator1-111.3.2.2Character Generator1-121.3.2.3Ramp/Conic Generator1-131.3.2.4Output Channel1-131.3.2.52-D Coordinate Converter1-131.4Optional Equipment1-131.4.1Display Indicators1-141.4.2Input Devices1-141.4.2.1Keyboards1-151.4.2.3Trackball, Forcestick and Data Tablet1-151.4.3Output Devices1-151.4.3Output Devices1-151.4.3Output Devices1-151.4.3Output Devices1-151.4.3Output Devices1-151.4.3Output Devices1-151.4.3Output Devices1-151.4.3Output Devices1-151.4.3Output Devices1-151.4.4Formance Specification1-161.7Equipment Supplied1-16                                                                                                                                                                                                                                                                                                                                                                  |

| 1.3.1.7Graphic Controller1-101.3.1.82-D/3-D Coordinate Converter1-111.3.1.9Floating Point Converter1-111.3.2Group 2 Circuit Cards1-111.3.2.1Vector/Position Generator1-111.3.2.2Character Generator1-121.3.2.3Ramp/Conic Generator1-131.3.2.4Output Channel1-131.3.2.52-D Coordinate Converter1-131.4Optional Equipment1-131.4.1Display Indicators1-141.4.2Input Devices1-141.4.2.3Trackball, Forcestick and Data Tablet1-151.4.2.4Maintenance Data Input Devices1-151.4.3Output Devices1-151.4.3Output Devices1-151.4.3Output Devices1-151.4.4Devices1-151.4.5Power and Environmental Requirements1-161.7Equipment Supplied1-16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1.3.1.82-D/3-D Coordinate Converter1-111.3.1.9Floating Point Converter1-111.3.2.9Group 2 Circuit Cards1-111.3.2.1Vector/Position Generator1-111.3.2.2Character Generator1-121.3.2.3Ramp/Conic Generator1-131.3.2.4Output Channel1-131.3.2.52-D Coordinate Converter1-131.4Optional Equipment1-131.4.1Display Indicators1-141.4.2Input Devices1-141.4.2.3Trackball, Forcestick and Data Tablet1-151.4.2.4Maintenance Data Input Devices1-151.4.3Output Devices1-151.4.4Output Devices1-151.4.5Power and Environmental Requirements1-161.7Equipment Supplied1-16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1.3.1.9Floating Point Converter1-111.3.2Group 2 Circuit Cards1-111.3.2.1Vector/Position Generator1-111.3.2.2Character Generator1-121.3.2.3Ramp/Conic Generator1-131.3.2.4Output Channel1-131.3.2.52-D Coordinate Converter1-131.4Optional Equipment1-131.4.1Display Indicators1-141.4.2Input Devices1-141.4.2.1Keyboards1-151.4.2.3Trackball, Forcestick and Data Tablet1-151.4.3Output Devices1-151.4.3Output Devices1-151.4.3Output Devices1-151.4.3Output Devices1-151.4.3Output Devices1-151.4.3Output Devices1-151.4.3Output Devices1-161.7Equipment Supplied1-16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1.3.2Group 2 Circuit Cards1-111.3.2.1Vector/Position Generator1-111.3.2.1Vector/Position Generator1-121.3.2.2Character Generator1-131.3.2.3Ramp/Conic Generator1-131.3.2.4Output Channel1-131.3.2.52-D Coordinate Converter1-131.4Optional Equipment1-131.4.1Display Indicators1-141.4.2Input Devices1-141.4.2.1Keyboards1-141.4.2.2PHOTOPEN1-151.4.2.3Trackball, Forcestick and Data Tablet1-151.4.3Output Devices1-151.4.3Output Devices1-151.5Power and Environmental Requirements1-161.7Equipment Supplied1-16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1.3.2.1Vector/Position Generator1-111.3.2.1Character Generator1-121.3.2.2Character Generator1-131.3.2.3Ramp/Conic Generator1-131.3.2.4Output Channel1-131.3.2.52-D Coordinate Converter1-131.4Optional Equipment1-131.4.1Display Indicators1-131.4.2Input Devices1-141.4.2.1Keyboards1-141.4.2.2PHOTOPEN1-151.4.2.3Trackball, Forcestick and Data Tablet1-151.4.2.4Maintenance Data Input Devices1-151.4.3Output Devices1-151.5Power and Environmental Requirements1-151.6Performance Specification1-161.7Equipment Supplied1-16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1.3.2.2Character Generator1-121.3.2.3Ramp/Conic Generator1-131.3.2.4Output Channel1-131.3.2.52-D Coordinate Converter1-131.4Optional Equipment1-131.4.1Display Indicators1-131.4.2Input Devices1-141.4.2.1Keyboards1-141.4.2.2PHOTOPEN1-151.4.2.3Trackball, Forcestick and Data Tablet1-151.4.2.4Maintenance Data Input Devices1-151.4.3Output Devices1-151.5Power and Environmental Requirements1-151.6Performance Specification1-161.7Equipment Supplied1-16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1.3.2.3Ramp/Conic Generator1-131.3.2.4Output Channel1-131.3.2.52-D Coordinate Converter1-131.4Optional Equipment1-131.4.1Display Indicators1-131.4.2Input Devices1-141.4.2.1Keyboards1-141.4.2.2PHOTOPEN1-151.4.2.3Trackball, Forcestick and Data Tablet1-151.4.2.4Maintenance Data Input Devices1-151.4.3Output Devices1-151.5Power and Environmental Requirements1-151.6Performance Specification1-161.7Equipment Supplied1-16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1.3.2.4Output Channel1-131.3.2.52-D Coordinate Converter1-131.4Optional Equipment1-131.4.1Display Indicators1-131.4.2Input Devices1-141.4.2.1Keyboards1-141.4.2.2PHOTOPEN1-151.4.2.3Trackball, Forcestick and Data Tablet1-151.4.2.4Maintenance Data Input Devices1-151.4.3Output Devices1-151.5Power and Environmental Requirements1-151.6Performance Specification1-161.7Equipment Supplied1-16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1.3.2.52-D Coordinate Converter1-131.4Optional Equipment1-131.4.1Display Indicators1-131.4.2Input Devices1-141.4.2.1Keyboards1-141.4.2.2PHOTOPEN1-151.4.2.3Trackball, Forcestick and Data Tablet1-151.4.2.4Maintenance Data Input Devices1-151.4.3Output Devices1-151.5Power and Environmental Requirements1-151.6Performance Specification1-161.7Equipment Supplied1-16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1.4Optional Equipment1-131.4.1Display Indicators1-131.4.2Input Devices1-141.4.2.1Keyboards1-141.4.2.2PHOTOPEN1-151.4.2.3Trackball, Forcestick and Data Tablet1-151.4.2.4Maintenance Data Input Devices1-151.4.3Output Devices1-151.5Power and Environmental Requirements1-151.6Performance Specification1-161.7Equipment Supplied1-16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1.4.1Display Indicators1-131.4.2Input Devices1-141.4.2.1Keyboards1-141.4.2.2PHOTOPEN1-151.4.2.3Trackball, Forcestick and Data Tablet1-151.4.2.4Maintenance Data Input Devices1-151.4.3Output Devices1-151.5Power and Environmental Requirements1-151.6Performance Specification1-161.7Equipment Supplied1-16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 1.4.2Input Devices1-141.4.2.1Keyboards1-141.4.2.2PHOTOPEN1-151.4.2.3Trackball, Forcestick and Data Tablet1-151.4.2.4Maintenance Data Input Devices1-151.4.3Output Devices1-151.5Power and Environmental Requirements1-151.6Performance Specification1-161.7Equipment Supplied1-16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1.4.2.1Keyboards1-141.4.2.2PHOTOPEN1-151.4.2.3Trackball, Forcestick and Data Tablet1-151.4.2.4Maintenance Data Input Devices1-151.4.3Output Devices1-151.5Power and Environmental Requirements1-151.6Performance Specification1-161.7Equipment Supplied1-16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1.4.2.2PHOTOPEN1-151.4.2.3Trackball, Forcestick and Data Tablet1-151.4.2.4Maintenance Data Input Devices1-151.4.3Output Devices1-151.5Power and Environmental Requirements1-151.6Performance Specification1-161.7Equipment Supplied1-16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1.4.2.3Trackball, Forcestick and Data Tablet1-151.4.2.4Maintenance Data Input Devices1-151.4.3Output Devices1-151.5Power and Environmental Requirements1-151.6Performance Specification1-161.7Equipment Supplied1-16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1.4.2.4Maintenance Data Input Devices1-151.4.3Output Devices1-151.5Power and Environmental Requirements1-151.6Performance Specification1-161.7Equipment Supplied1-16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1.4.3Output Devices1-151.5Power and Environmental Requirements1-151.6Performance Specification1-161.7Equipment Supplied1-16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1.5Power and Environmental Requirements1-151.6Performance Specification1-161.7Equipment Supplied1-16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1.6Performance Specification1-161.7Equipment Supplied1-16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1.7 Equipment Supplied 1-16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| I.8 Equipment Identification I-ID                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1.9 Related Publications 1-16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1.10Test Equipment Required1-16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2 OPERATION 2-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2.1 General 2-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2.2 Controls and Indicators 2–1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2.3 Turn-On Procedure 2-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.31011 Introductor2.12.4Operating Procedures2-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.4.1 Normal Operating Procedures 2-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.4.1.1 System Mode Operation 2-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

i

## TABLE OF CONTENTS (Cont)

C 1

(

C

## Section

3

|           |                                           | Page |

|-----------|-------------------------------------------|------|

| 2.4.1.2   | Local Mode Operation                      | 2-4  |

| 2.4.1.3   | Verification Test Pattern and Diagnostics | 2-5  |

| 2.4.1.4   | Hardcopy Generation                       | 2-10 |

| 2.4.1.5   | Data Tablet Testing                       | 2-11 |

| 2.4.2     | Local Mode Commands                       | 2-11 |

| 2.4.2.1   | Memory Commands                           | 2-13 |

| 2.4.2.2   | Displaying a Refresh File                 | 2-13 |

| 2.4.2.3   | Transfer of Program Control               | 2-14 |

| 2.4.2.4   | Transfer to System Mode                   | 2-14 |

| 2.4.2.5   | Teletypewriter Emulation                  | 2-14 |

| 2.4.2.6   | Additional Local Mode Commands            | 2-14 |

| 2.4.3     | Standard Transfer Table                   | 2-16 |

| 2.4.4     | Operator Performance Checks               | 2-16 |

| 2.5       | Turn-Off Procedure                        | 2–19 |

| THEORY OF | OPERATION                                 | 3-1  |

|           |                                           |      |

| 3.1       | General                                   | 3-1  |

| 3.2       | Signal/Bus Structure                      | 3-1  |

| 3.2.1     | Processor Bus                             | 3-1  |

| 3.2.2     | Graphic Bus                               | 3-4  |

| 3.2.3     | Power Bus                                 | 3-5  |

| 3.3       | Processor Bus Control and Timing          | 3-6  |

| 3.3.1     | Bus Control Logic                         | 3-6  |

| 3.3.2     | Bus Control Timing                        | 3-8  |

| 3.3.3     | Interrupt Logic                           | 3-10 |

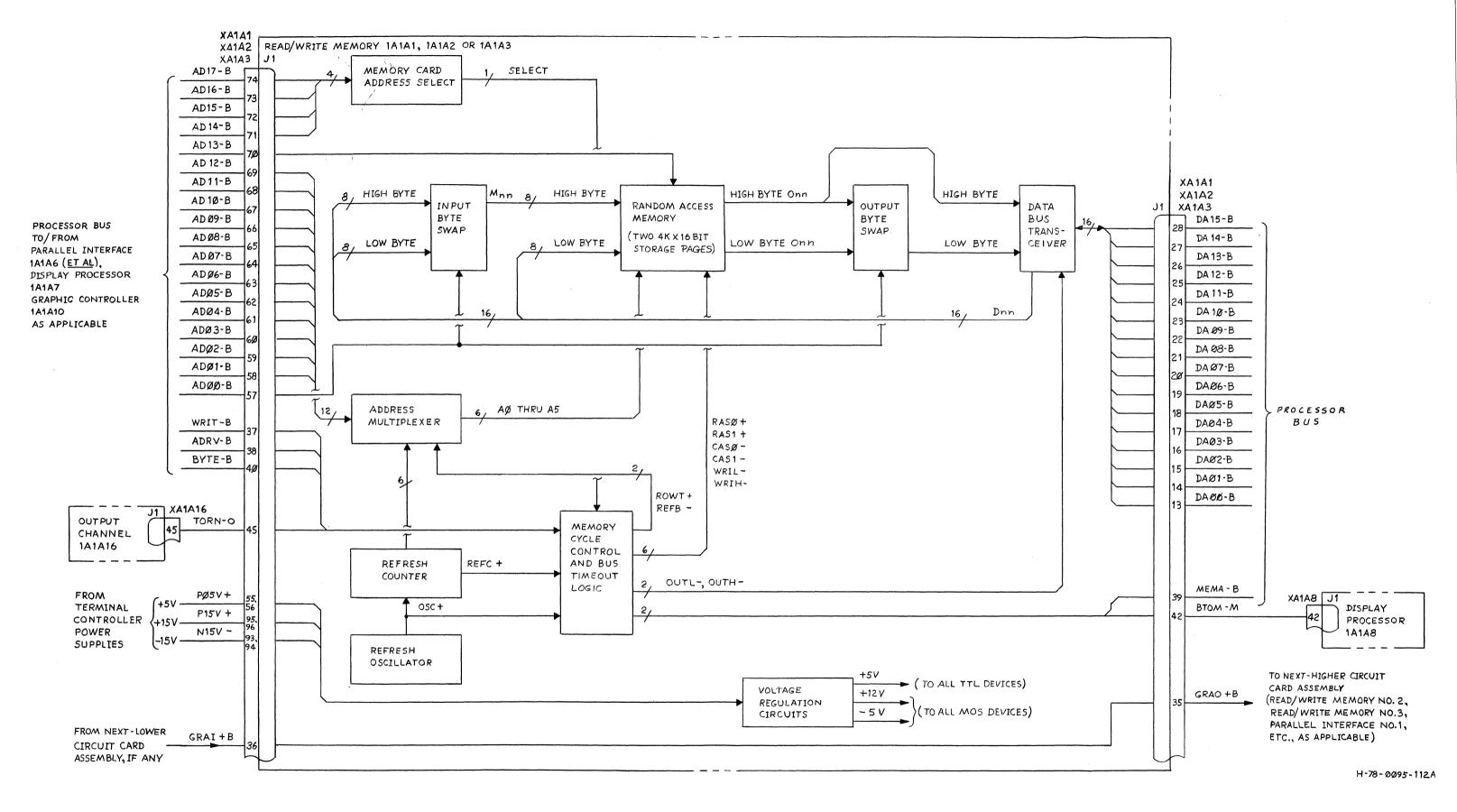

| 3.4       | Read/Write Memory                         | 3-13 |

| 3.4.1     | Major Circuits                            | 3-13 |

| 3.4.2     | Operation                                 | 3-16 |

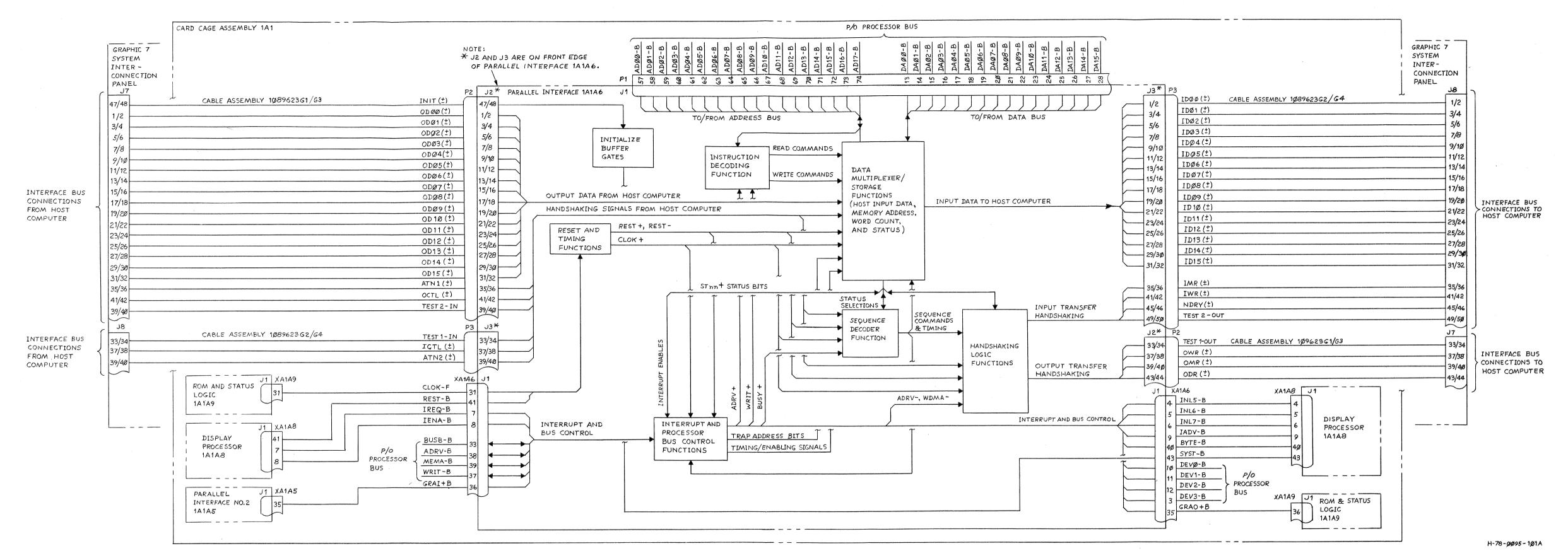

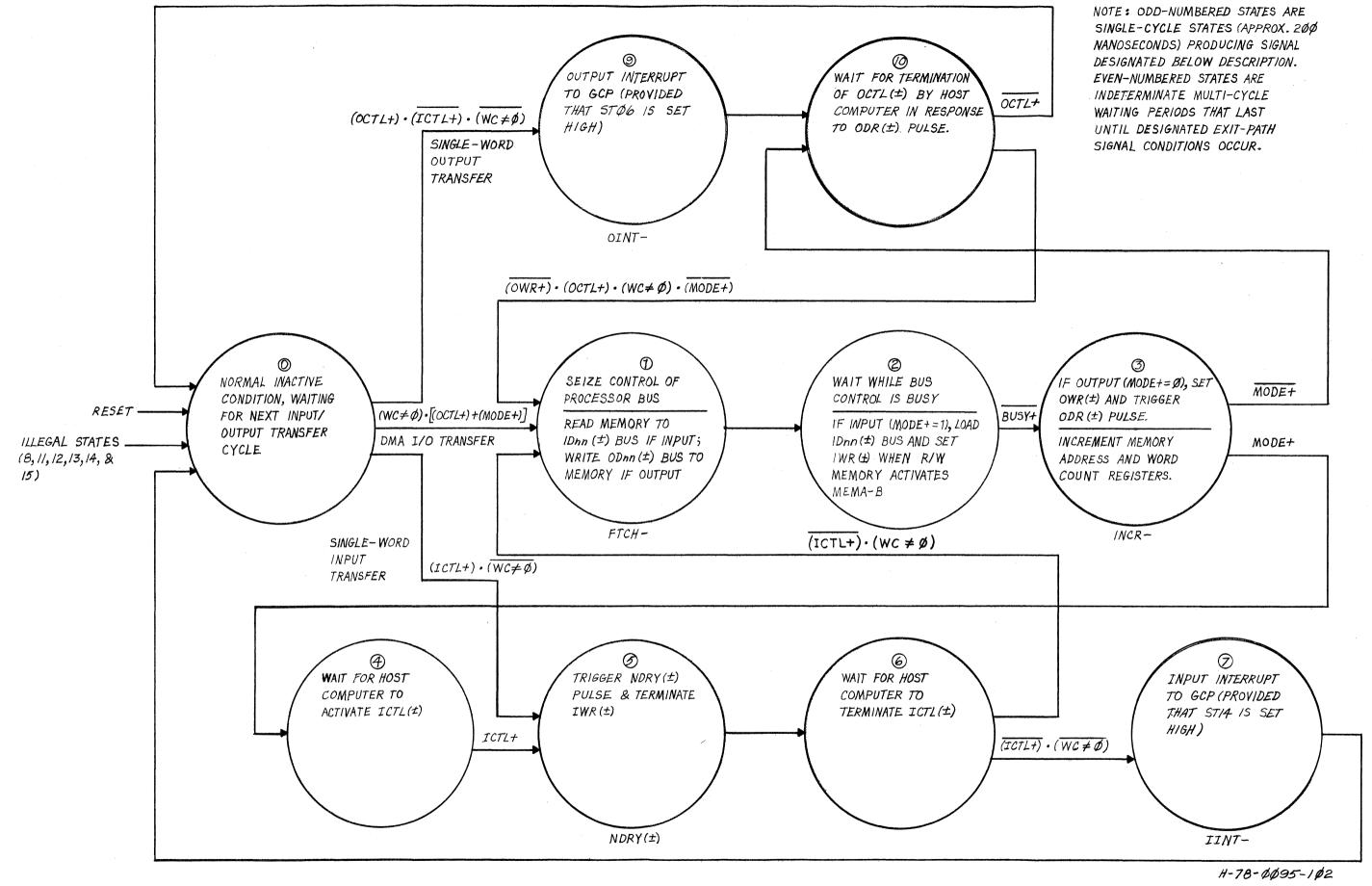

| 3,5       | Parallel Interface                        | 3-23 |

| 3.5.1     | Signal Connections                        | 3-23 |

| 3.5.2     | Parallel Interface Internal Buses         | 3-24 |

| 3.5.3     | Major Circuits                            | 3-24 |

| 3.5.4     | Operation                                 | 3-28 |

| 3.5.4.1   | Initialization                            | 3–28 |

| 3.5.4.2   | Status Setup                              | 3–28 |

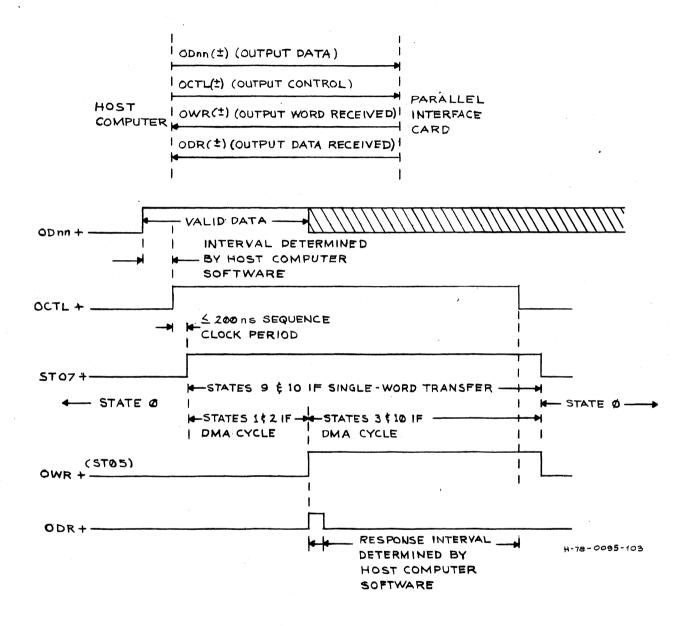

| 3.5.4.3   | Single Word Output Transfers              | 3-32 |

| 3.5.4.4   | DMA Output Transfers                      | 3-34 |

| 3.5.4.5   | Single Word Input Transfer                | 3-35 |

| 3.5.4.6   | DMA Input Transfers                       | 3-36 |

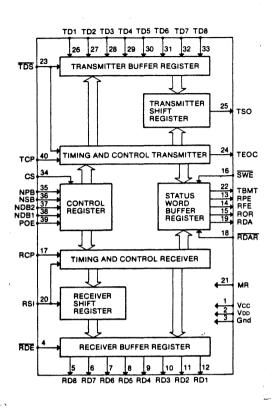

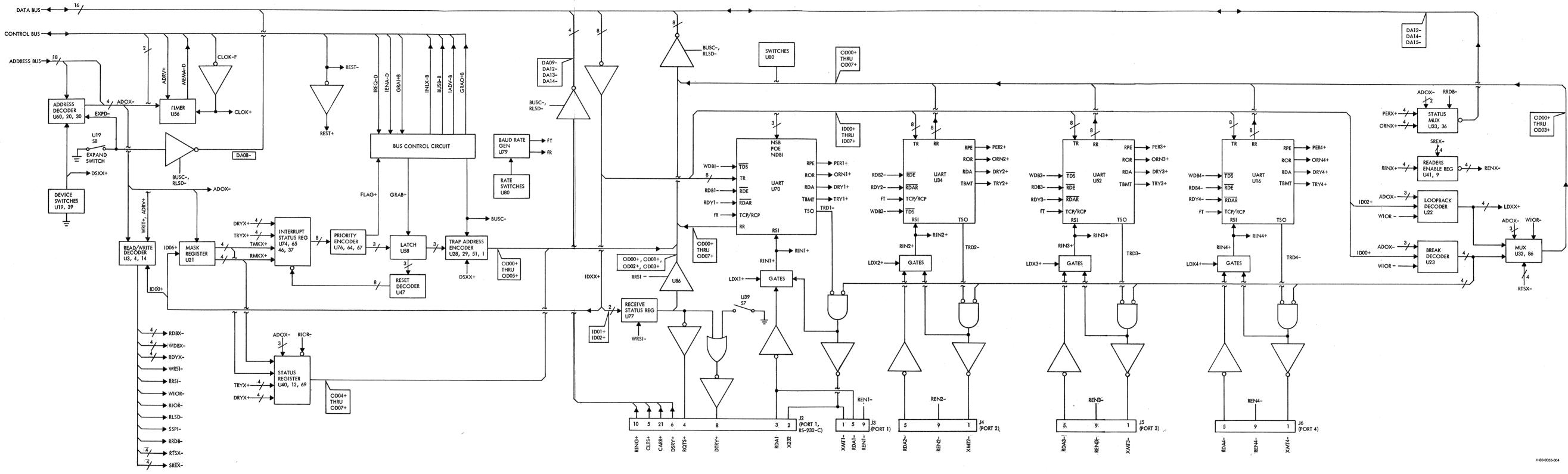

| 3.6       | Multiport Serial Interface                | 3-45 |

| 3.6.1     | Major Circuits                            | 3-47 |

| 3.6.2     | Operation                                 | 3-53 |

| 3.6.2.1   | Definitions of Bits                       | 3-53 |

| 3.6.2.2   | Typical Receive Sequence                  | 3-55 |

| 3.6.2.3   | Typical Transmit Sequence                 | 3-55 |

#### Section

4

4.6.8

Character Generator

|           |                                                  | Page         |

|-----------|--------------------------------------------------|--------------|

| 3.6.2.4   | Modem Operation                                  | 3–56         |

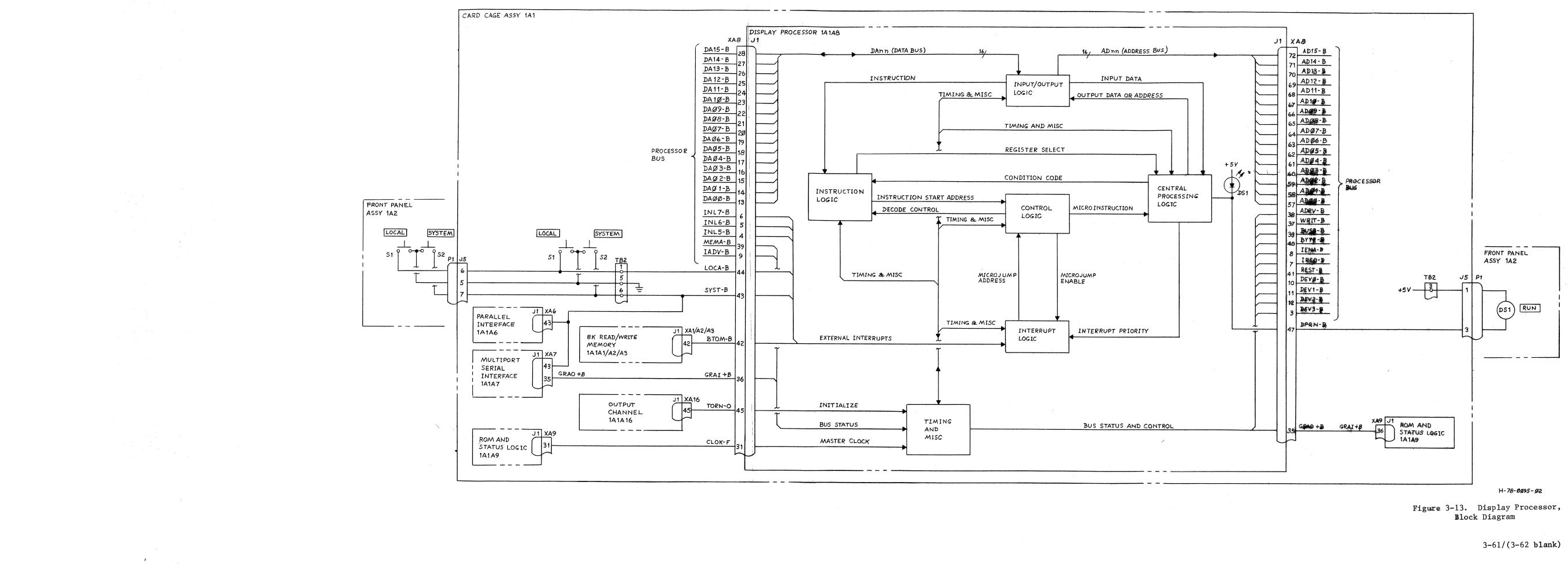

| 3.7       | Display Processor                                | 3–59         |

| 3.8       | ROM and Status Card                              | 3–67         |

| 3.9       | Graphic Controller                               | 3–83         |

| 3.9.1     | Major Circuits                                   | 3–83         |

| 3.9.2     | Operation                                        | 3–89         |

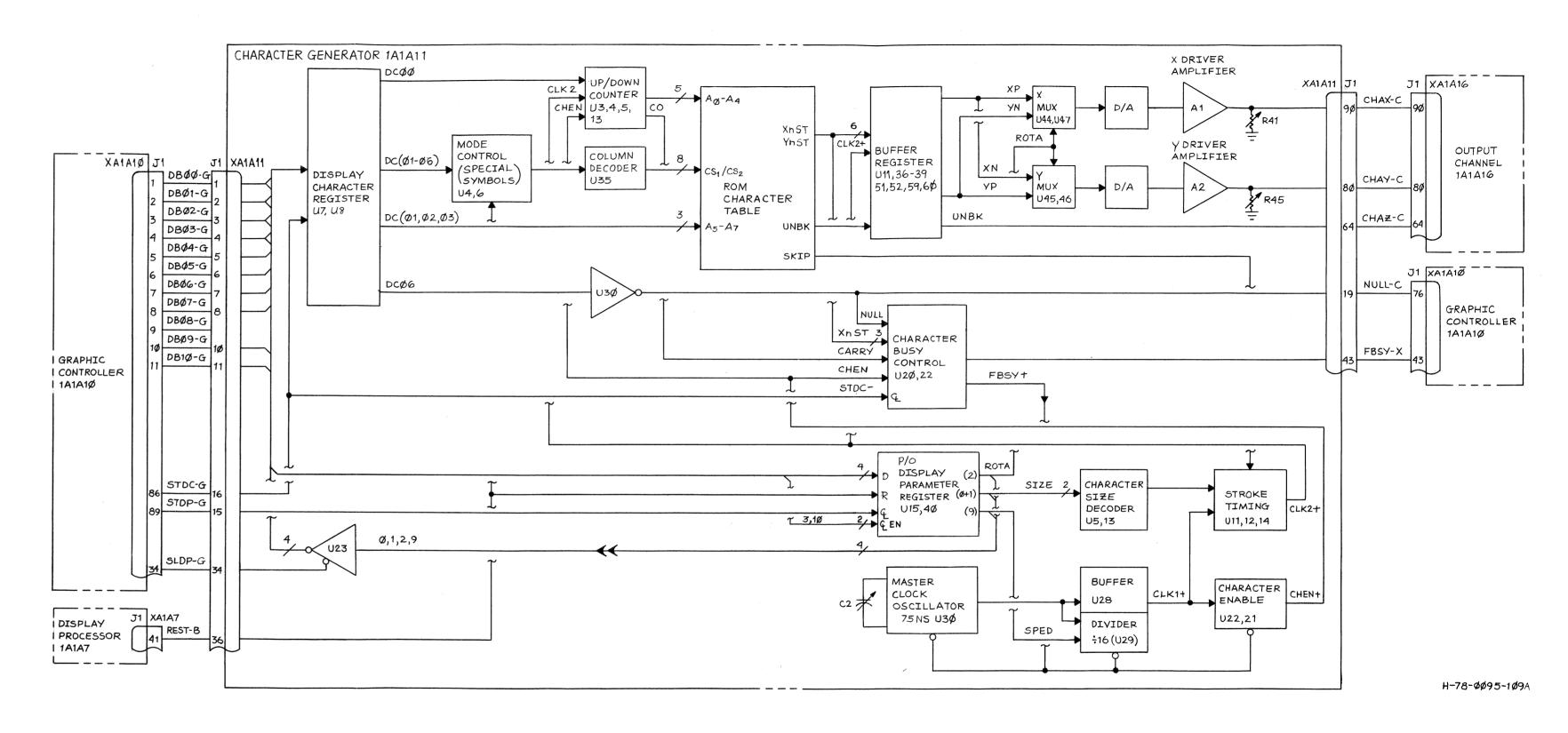

| 3.10      | Character Generator                              | 3–95         |

| 3.10.1    | Major Circuits                                   | 3–95         |

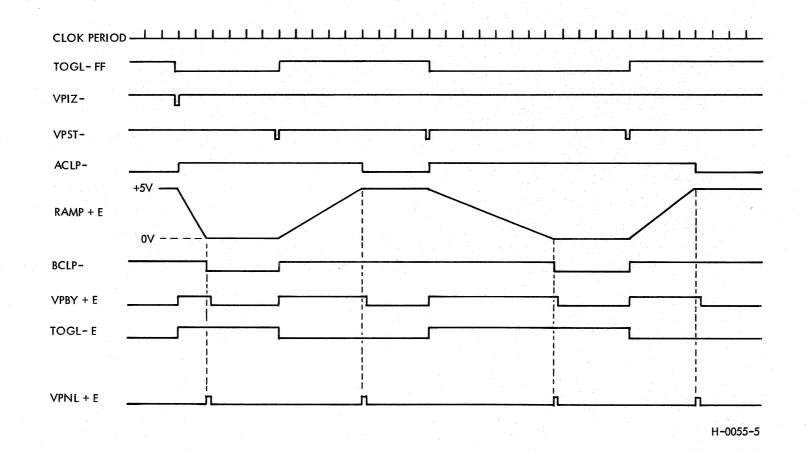

| 3.11      | RAMP Generator                                   | 3–105        |

| 3.11.1    | Major Circuits                                   | 3-106        |

| 3.11.2    | Operation                                        | 3-110        |

| 3.11.2.1  | Setup                                            | 3-110        |

|           | Operation                                        | 3-111        |

| 3.12      | D/A Converters                                   | 3-121        |

| 3.12.1    | Major Circuits                                   | 3-121        |

| 3.12.2    |                                                  | 3-122        |

| 3.12.2.1  | •                                                | 3-123        |

| 3.12.2.2  |                                                  | 3-123        |

| 3.12.2.3  | Beam Drive Signal Development                    | 3-124        |

| 3.12.2.4  | Drive Output Signal on Up-Ramp                   | 3-124        |

| 3.12.2.5  |                                                  | 3-125        |

| 3.12.2.6  |                                                  | 3-125        |

| 3.12.2.7  | ,                                                | 3-126        |

| 3.12.2.8  |                                                  | 3-126        |

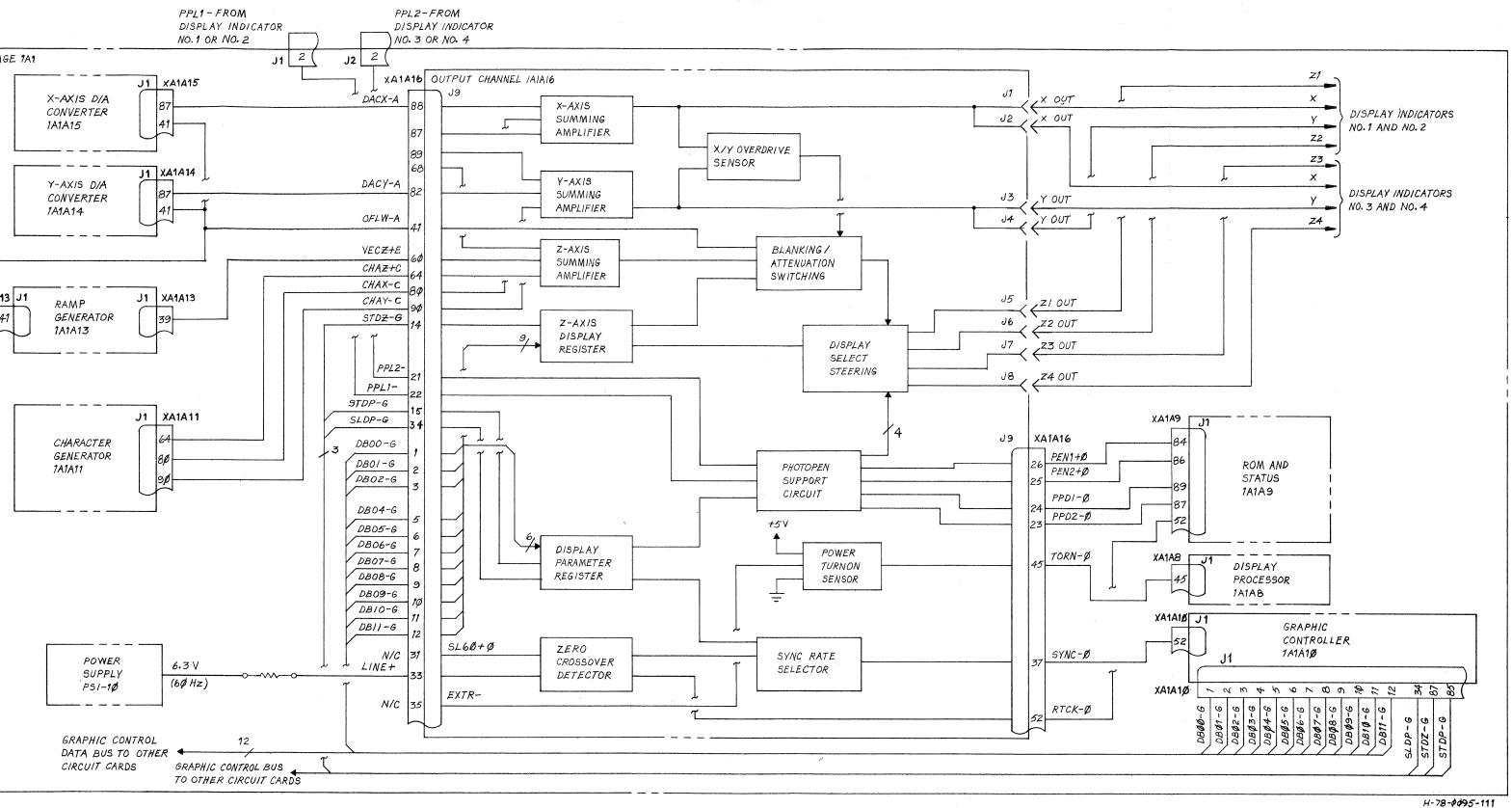

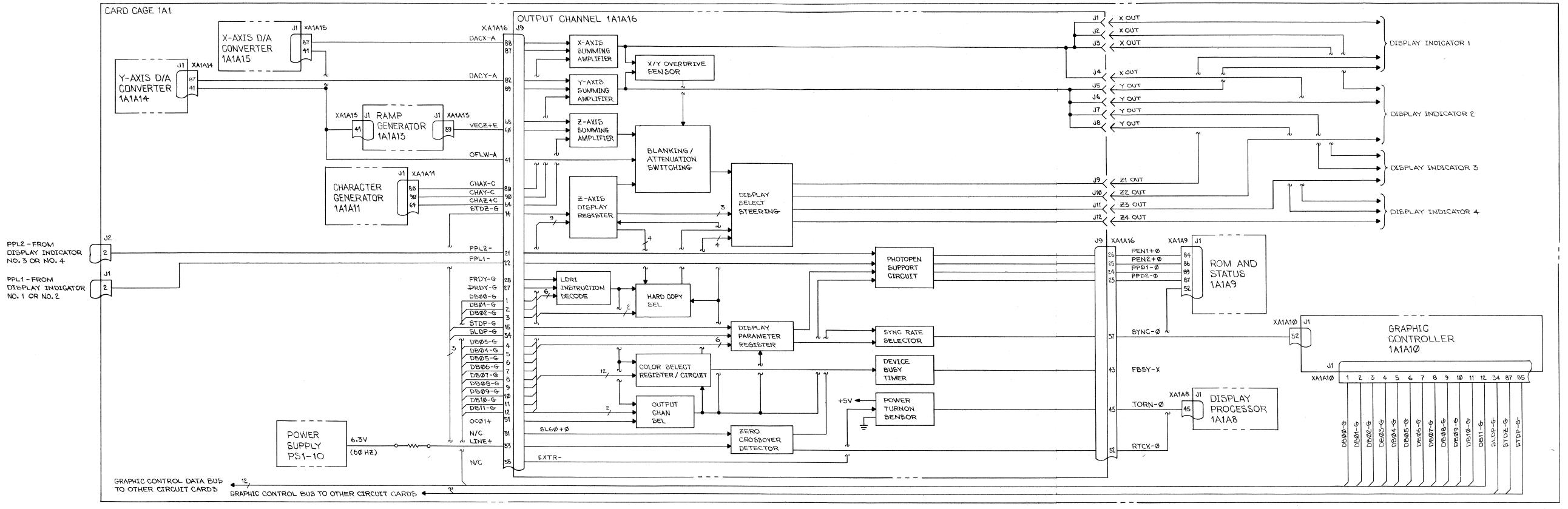

| 3.13      | Output Channel Card                              | 3-133        |

| 3.13.1    | -                                                | 3-133        |

| 3.13.2    | Unique Circuits of Color Output Channel Card     | 3-136        |

| INSTALLAT | TON                                              | 4-1          |

| 4.1       | Environmental Considerations                     | 4-1          |

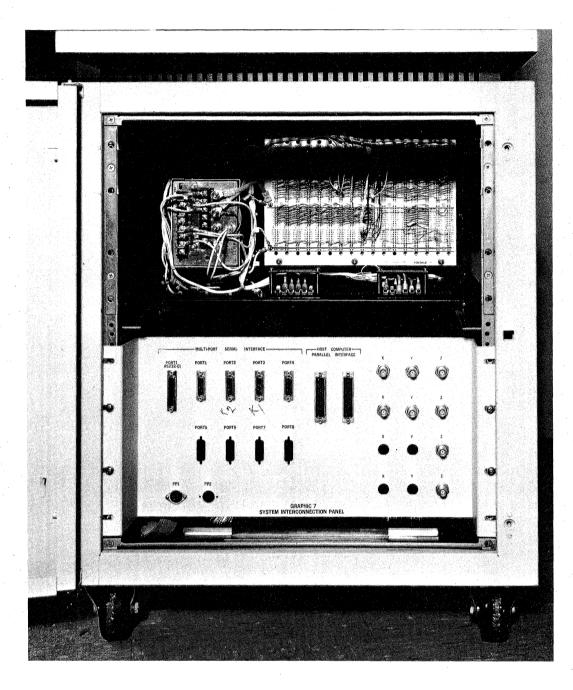

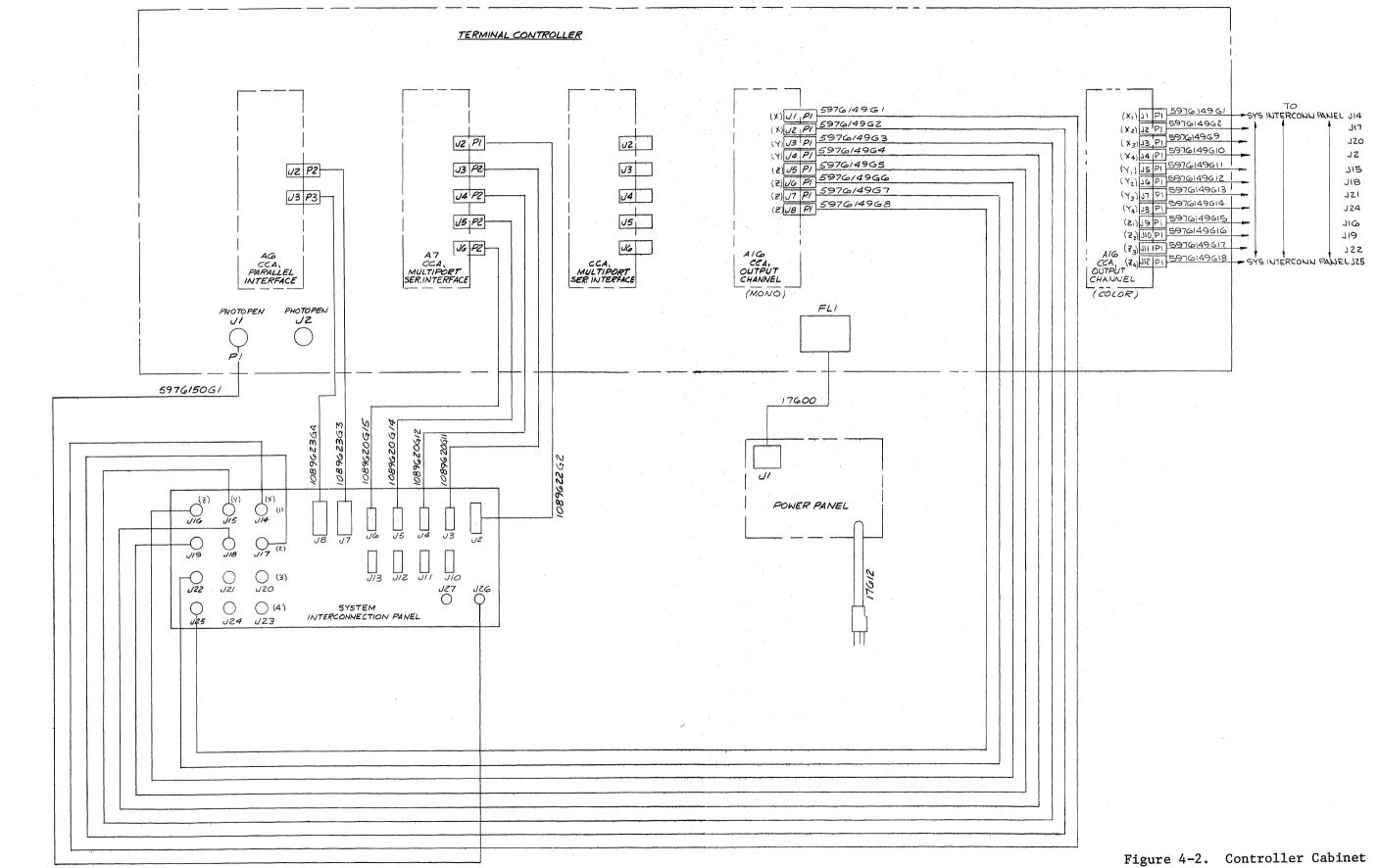

| 4.2       | Equipment Cabinet                                | 4-1          |

| 4.3       | Power Panel Assembly                             | 4-2          |

| 4.3.1     | Alternative Power Panel Assembly                 | 4-3          |

| 4.4       | System Interconnect Panel Assembly               | 4-3          |

| 4.5       | Connections to be Made at Installation           | 4-5          |

| 4.5.1     | Terminal Controller Mounted in Equipment Cabinet | 4-5          |

| 4.5.2     | Terminal Controller without Equipment Cabinet    | 4-6          |

| 4.6       | Switch and Jumper Selections                     | 4-11         |

| 4.6.1     | Display Processor                                | 4-11         |

| 4.6.2     | 8K Read/Write Memory Card                        | 4-11         |

|           | 8K ROM and Status Card                           | 4-11         |

| 4.6.3     | Multiport Serial Interface                       | 4-14         |

| 4.6.4     | •                                                | 4-14<br>4-18 |

| 4.6.5     | Parallel Interface                               | 4-18         |

| 4.6.6     | Graphic Controller                               | 4-21         |

| 4.6.7     | Ramp Generator                                   | 4-21         |

4-21

#### TABLE OF CONTENTS (Cont)

## Section

5

А

В

С

Page

| 5.1       | General                                      | -<br>-   |

|-----------|----------------------------------------------|----------|

| 5.2       | Maintenance Philosophy                       | 5        |

| 5.3       | Test Equipment Required                      | 5        |

| 5.4       | Troubleshooting Instructions                 | 5        |

| 5.4.1     | Built-In Diagnostics                         | <u> </u> |

| 5.4.2     | Terminal Verification Pattern                | <u> </u> |

| 5.4.2.1   | Vector/Position Generator Verification       | 5        |

| 5.4.2.2   | Character Generator Verification             | 5        |

| 5.4.2.3   | Character Rotate and Gray Level Verification | -        |

| 5.4.3     | Additional Hints                             | 5        |

| 5.5       | Adjustment Procedures                        | -        |

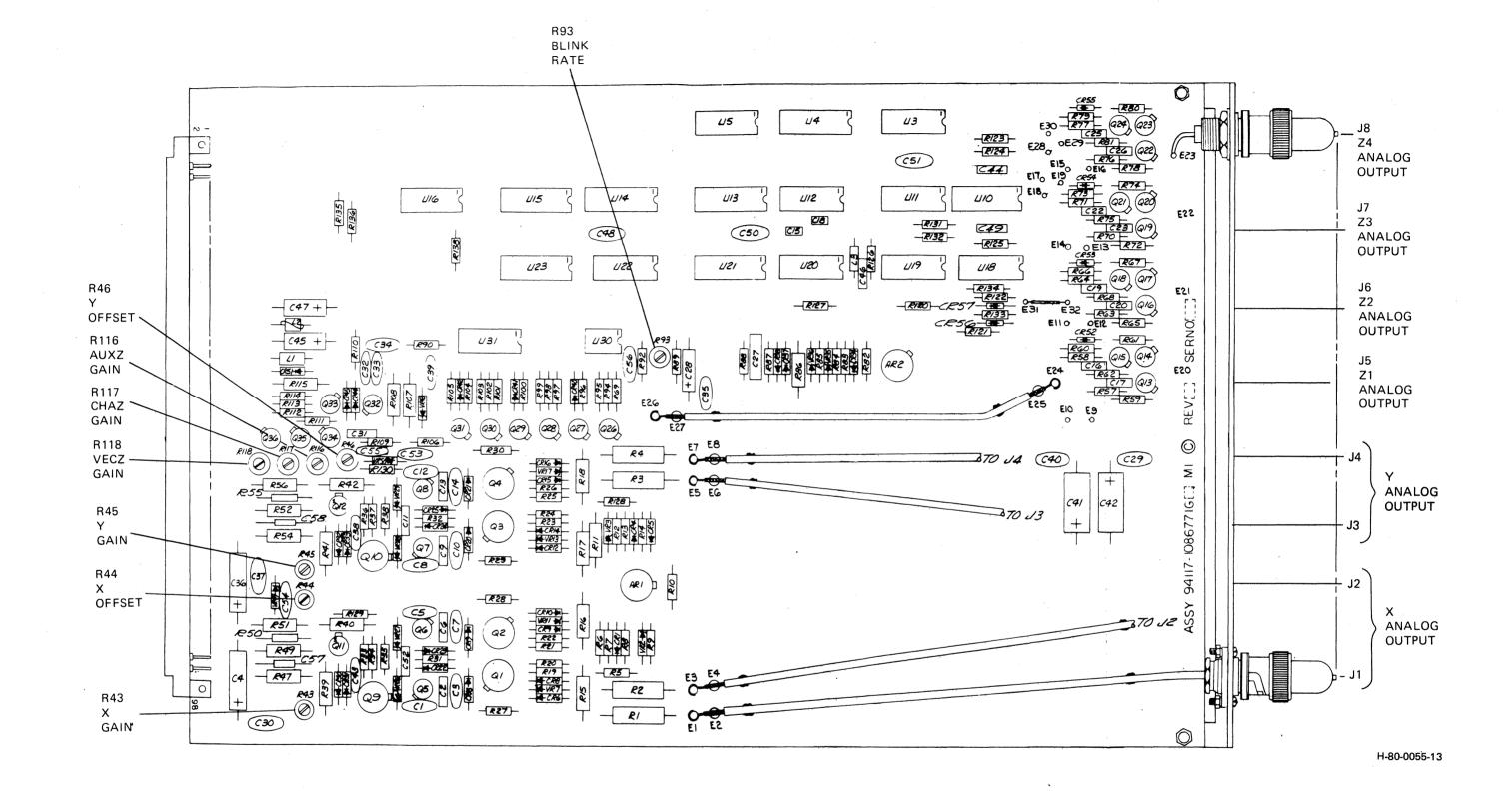

| 5.5.1     | Ramp Generator Adjustments                   | 4        |

| 5.5.2     | D/A Converter Adjustments                    |          |

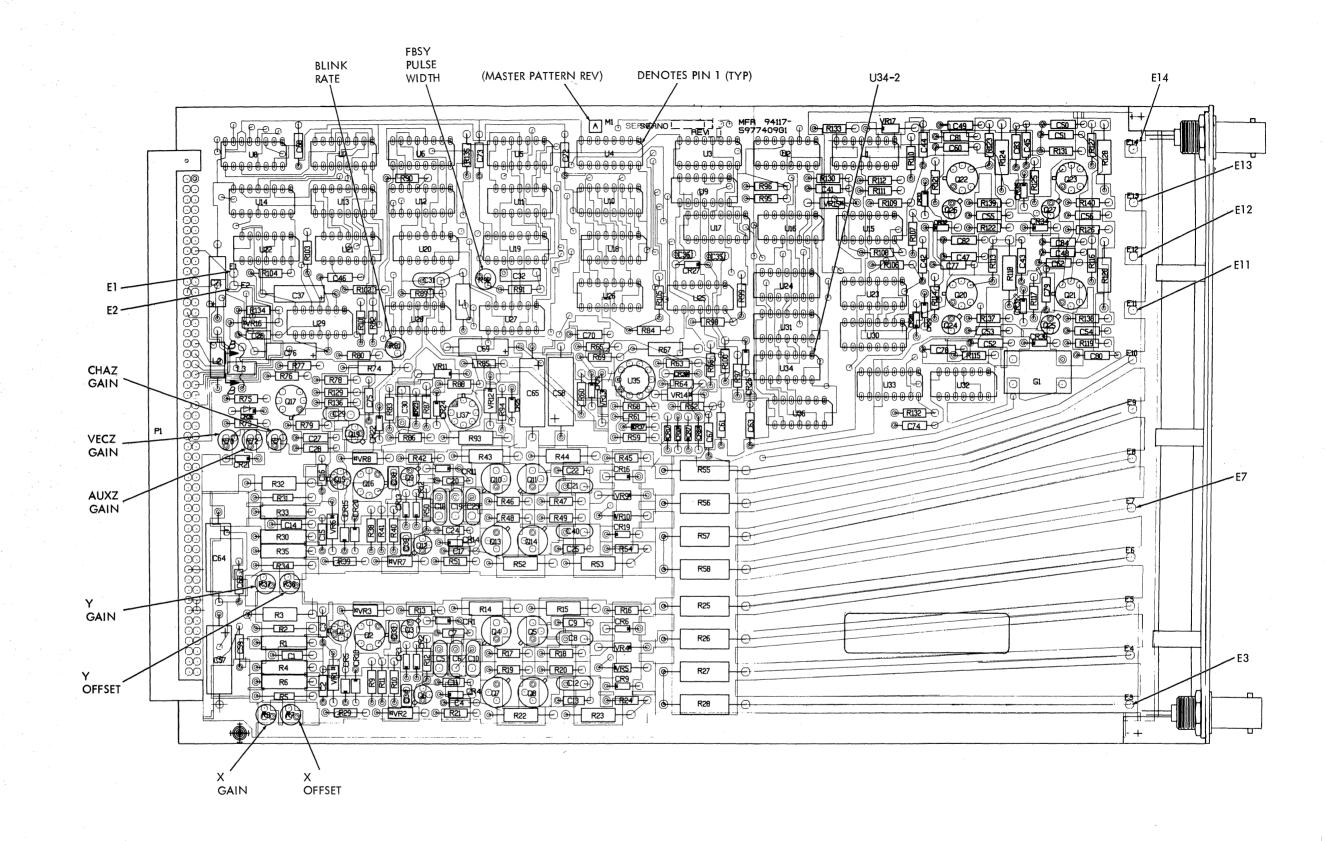

| 5.5.3     | Character Generator Adjustments              | -        |

| 5.5.4     | Output Channel Adjustments                   | <u> </u> |

| 5.5.4.1   | Monochrome Output Channel 1086771            |          |

| 5.5.4.2   | Color Output Channel 5977409                 | -        |

| 5.6       | Repair                                       | -        |

| 5.6.1     | Circuit Card Replacement                     | 1        |

| 5.6.2     | Chassis-Mounted Components                   |          |

| 5.6.3     | Special Handling for MOS Devices             | -        |

| MNEMONICS |                                              | l        |

| A-1       | General                                      |          |

| A-2       | Mnemonics Dictionary                         | 1        |

| A-3       | Register and Bus Bit Mnemonics               | I        |

| A-4       | Power Supply Mnemonics                       | I        |

| A–5       | Card Slot Pin Signals                        |          |

| CONNECTIO | ONS TO HOST COMPUTER                         | ]        |

| RELATED F | PUBLICATIONS                                 | (        |

#### LIST OF ILLUSTRATIONS

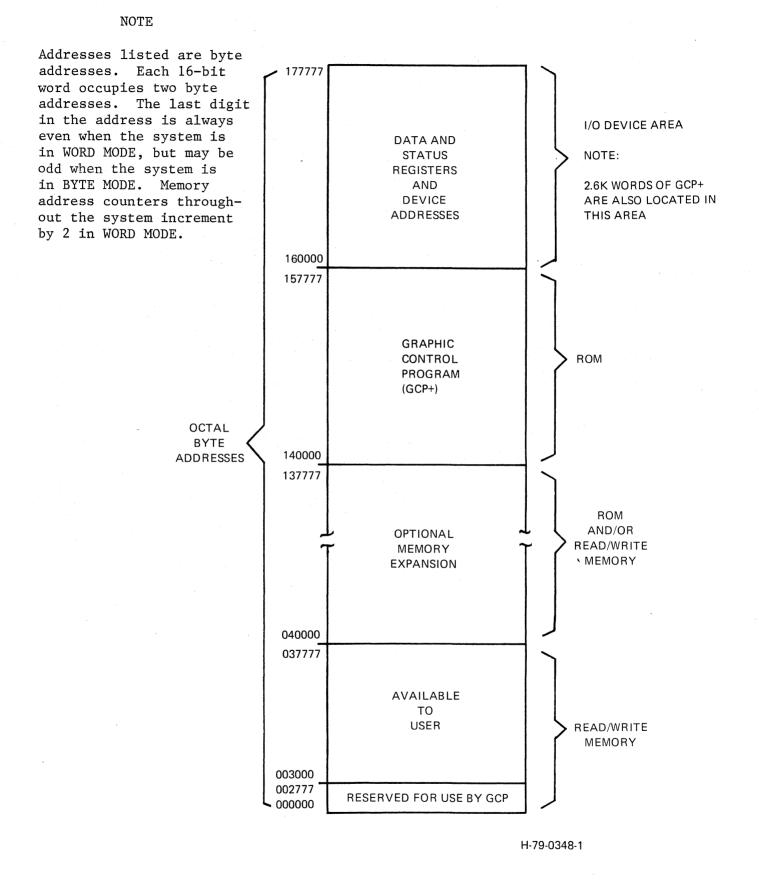

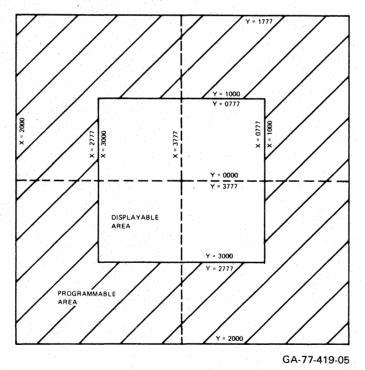

#### Number Page GRAPHIC 7 Terminal Controller 1-0 1 - 1Typical GRAPHIC 7 System Configuration 1-2 1 - 21-3 1-3 Terminal Controller Interior Card Cage 1-3 1--4 1-5 Terminal Controller Card Locations 1-5 Terminal Controller Block Diagram 1 - 71-6 GRAPHIC 7 System Memory Map 1-9 1-7

#### LIST OF ILLUSTRATIONS (Cont)

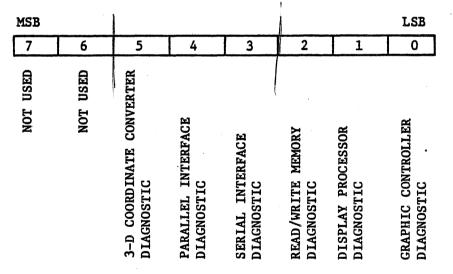

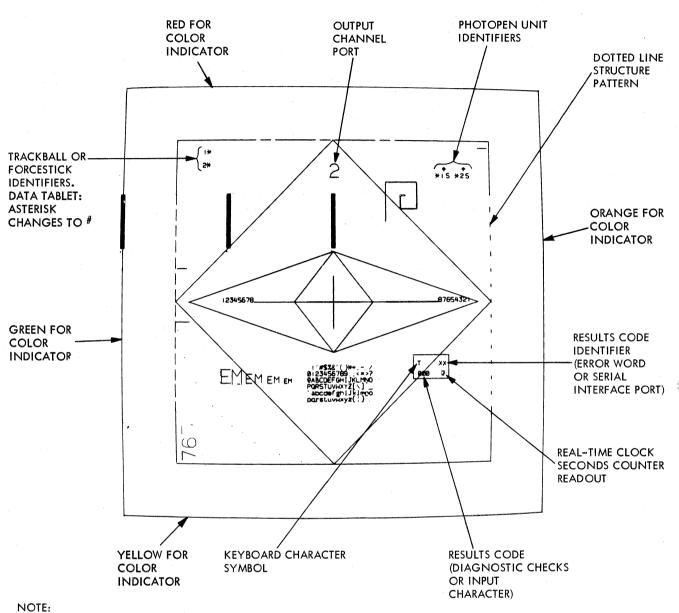

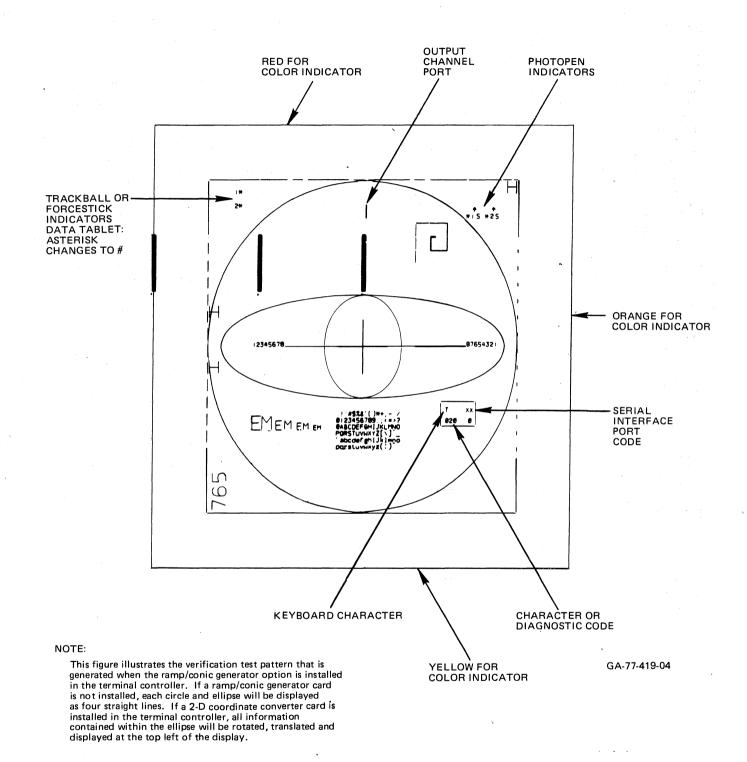

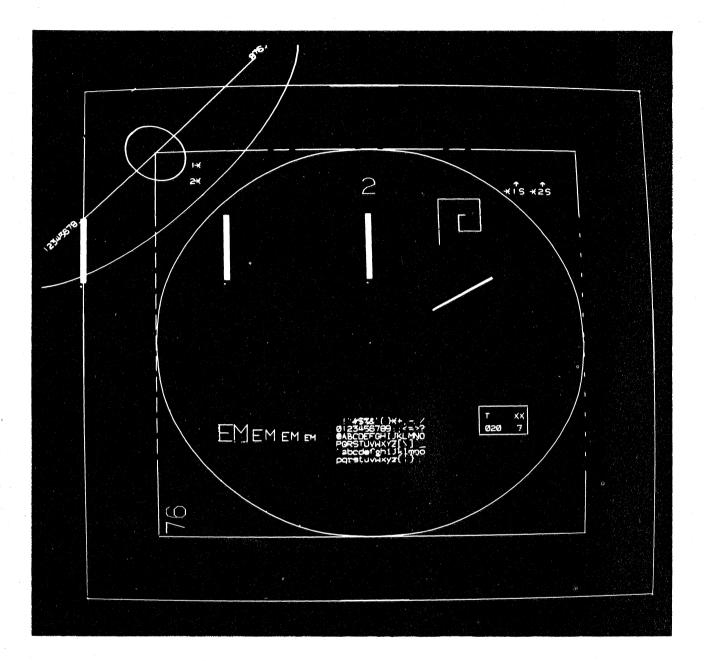

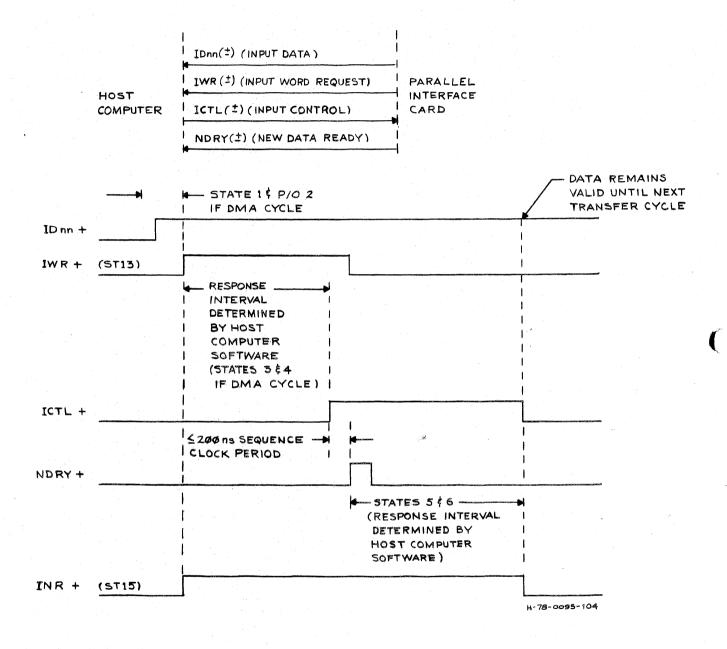

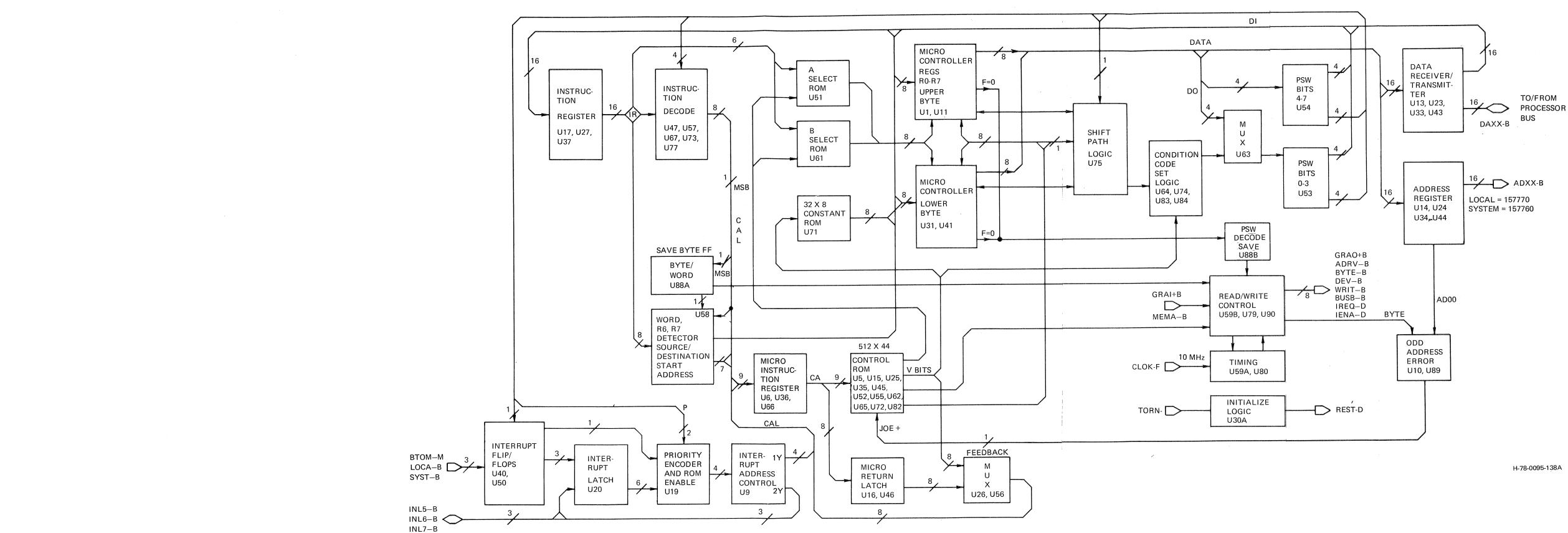

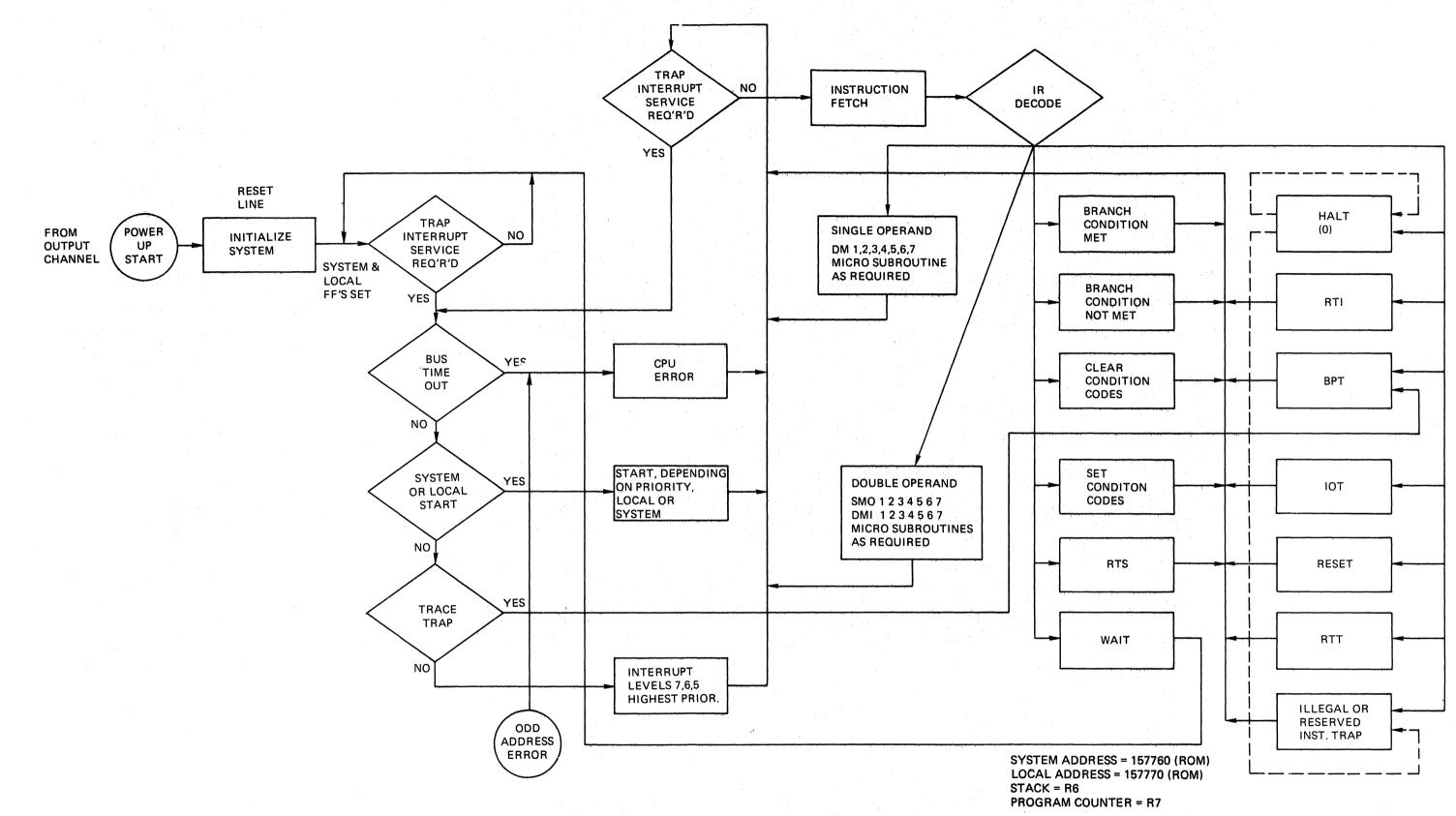

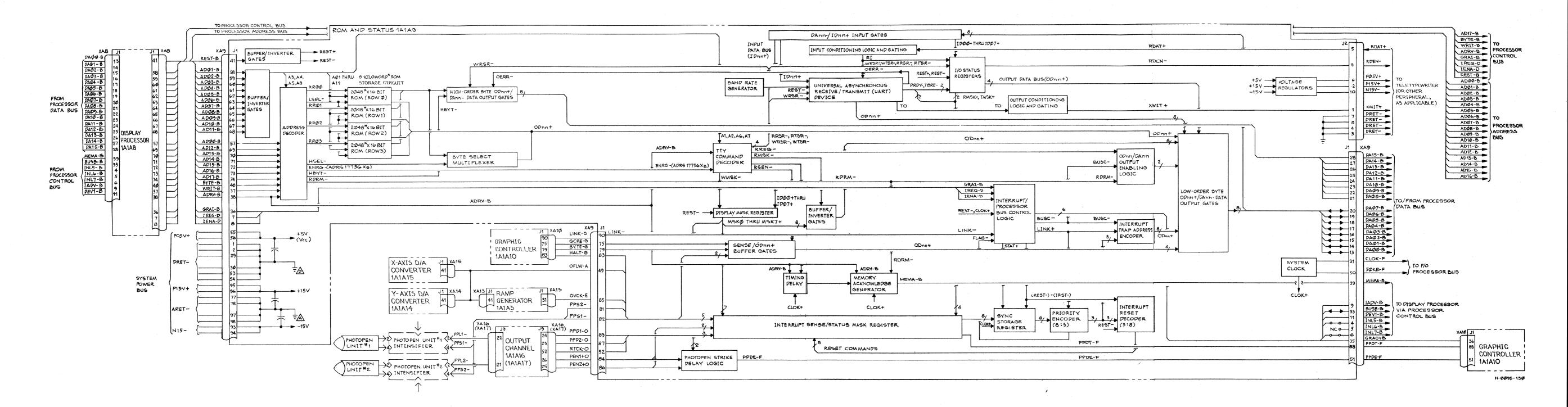

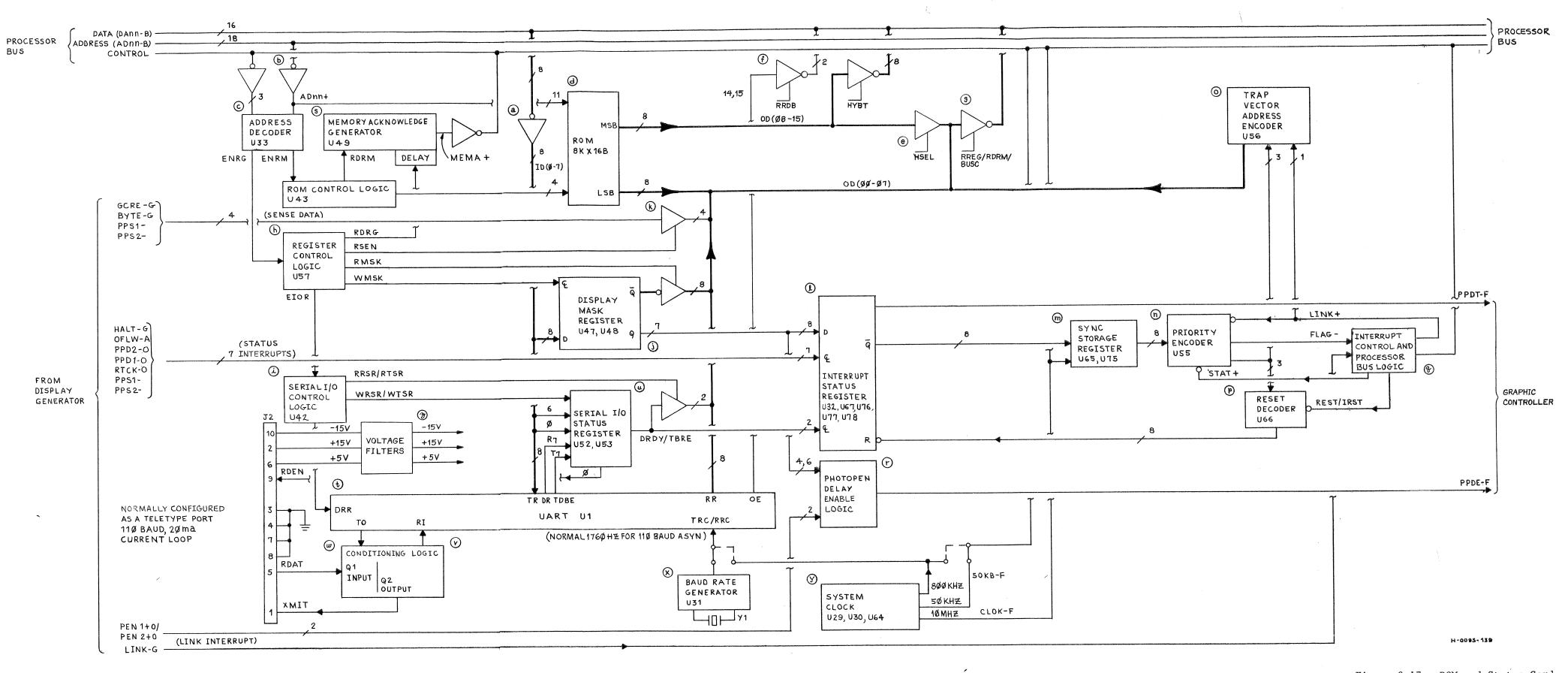

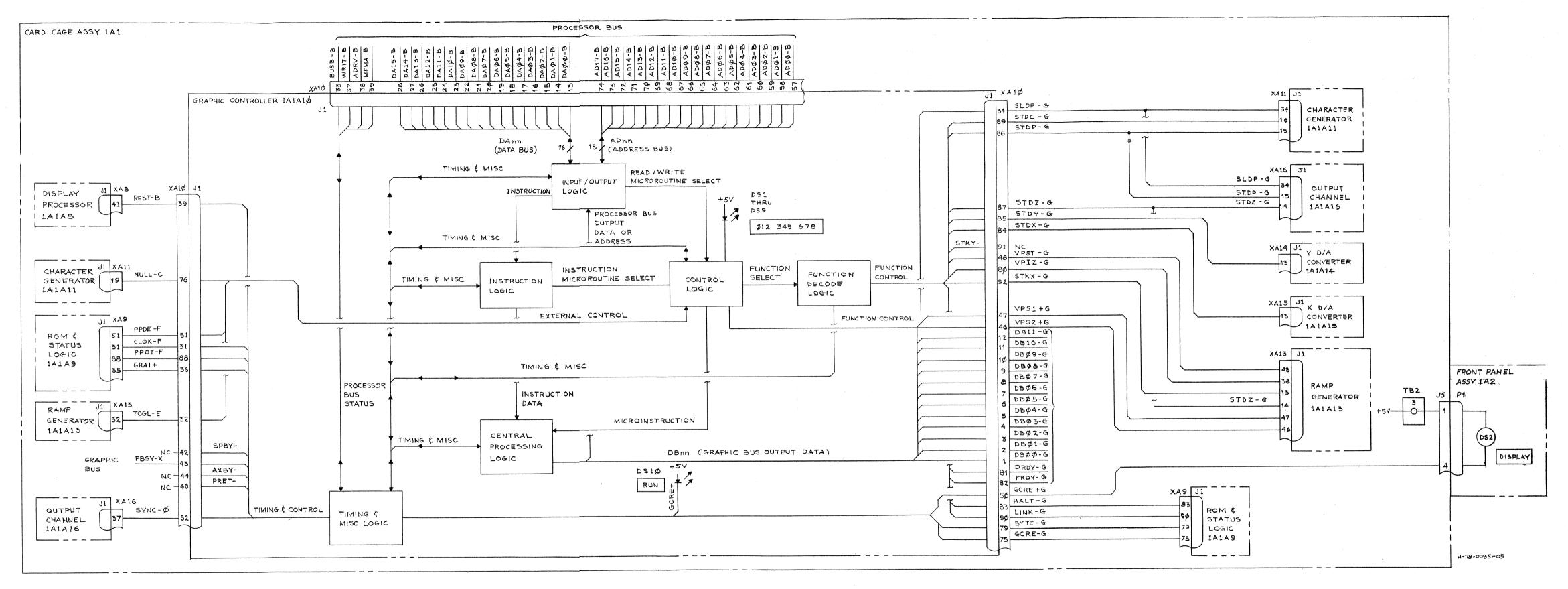

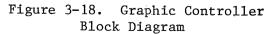

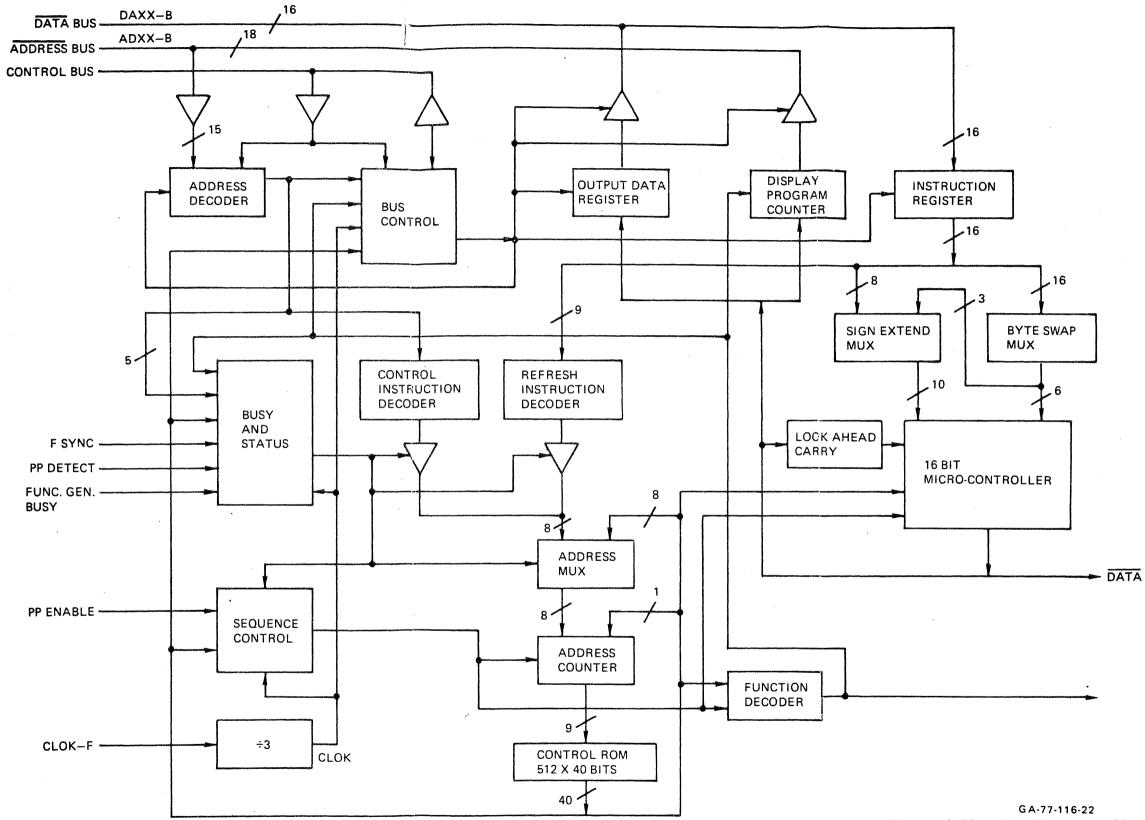

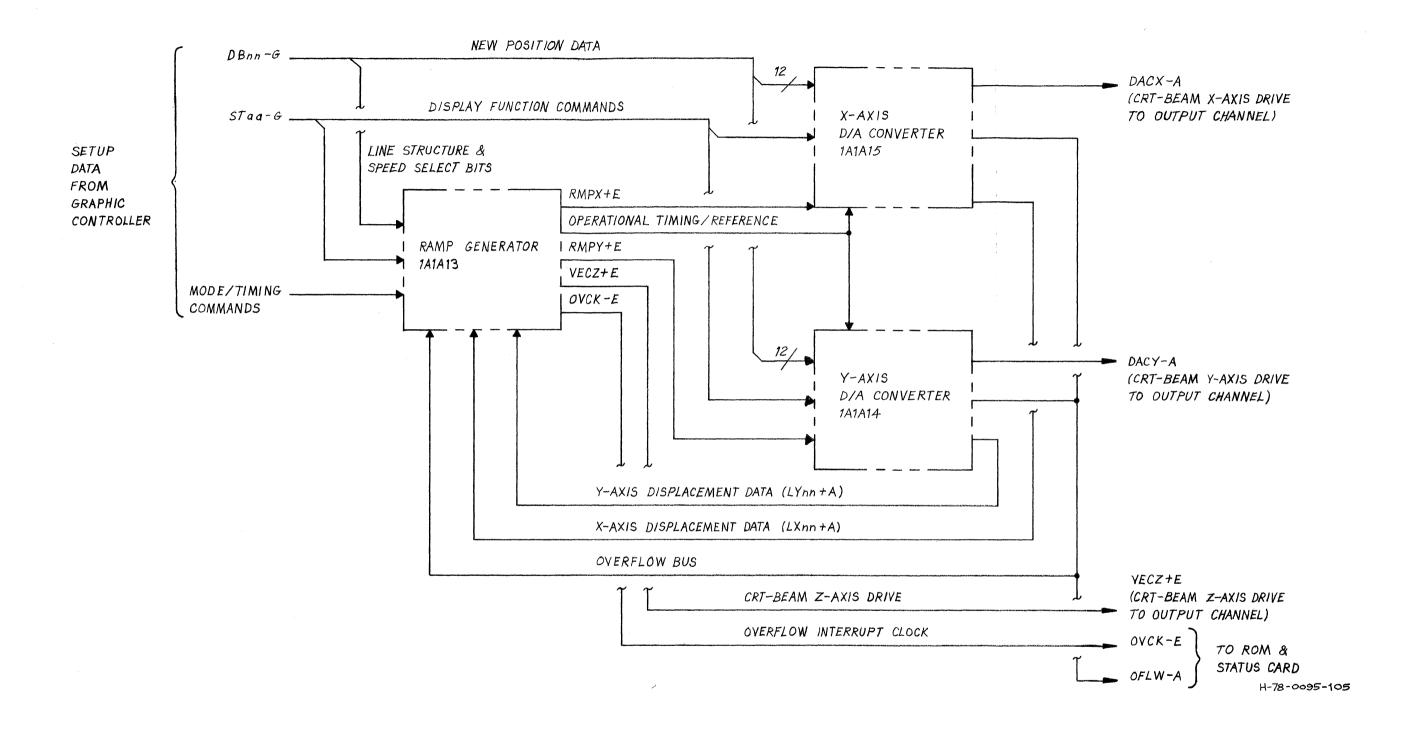

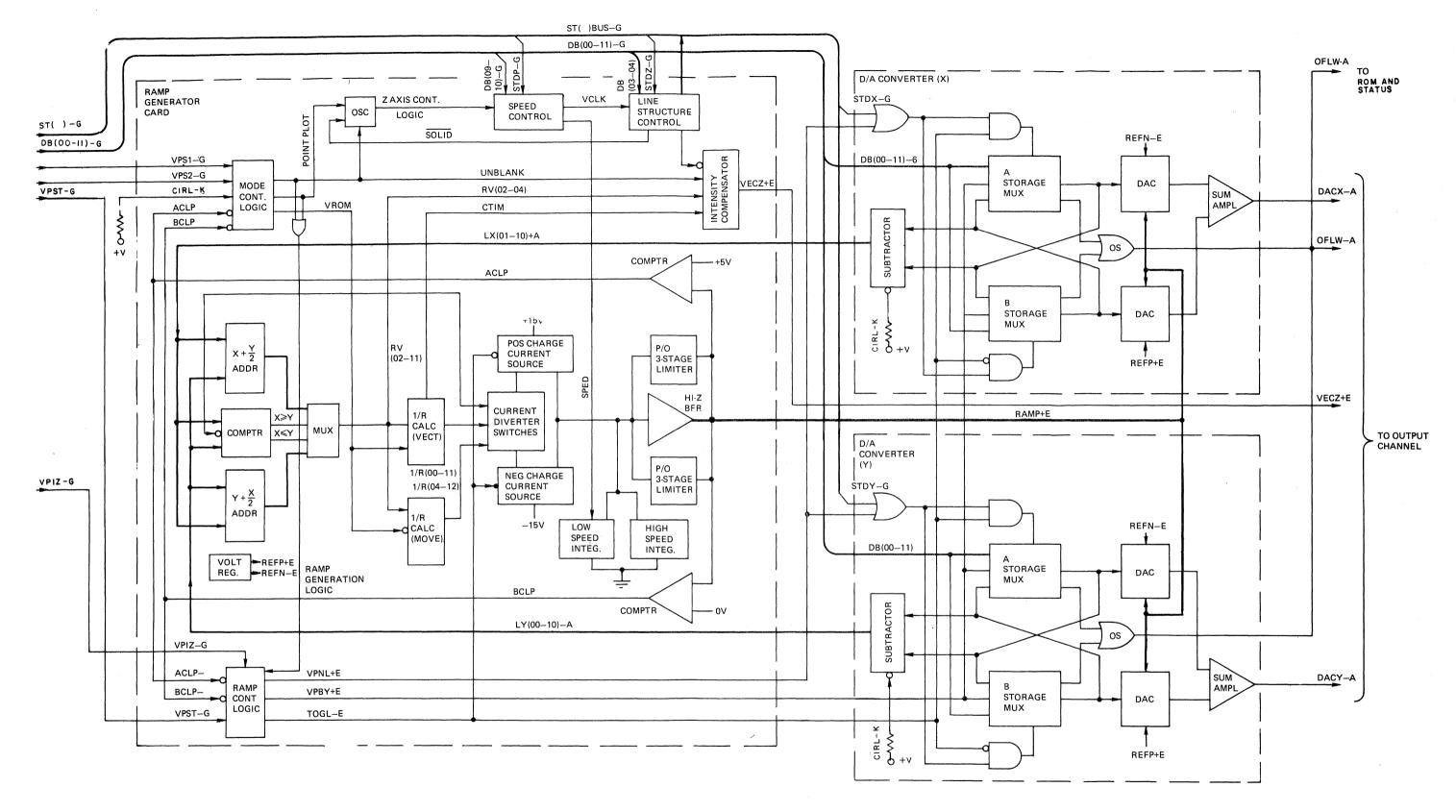

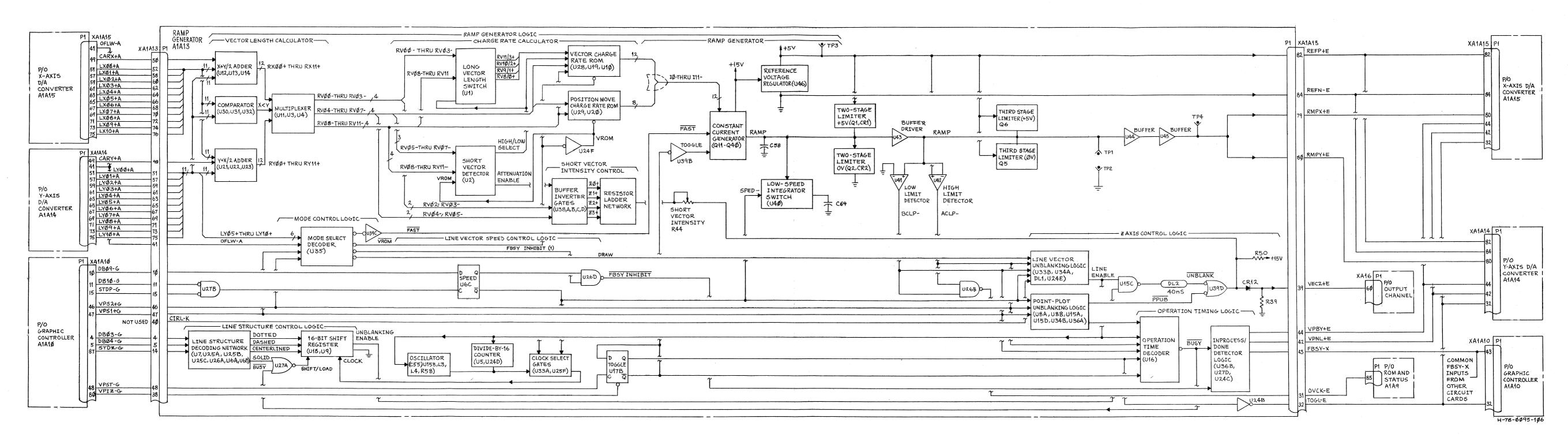

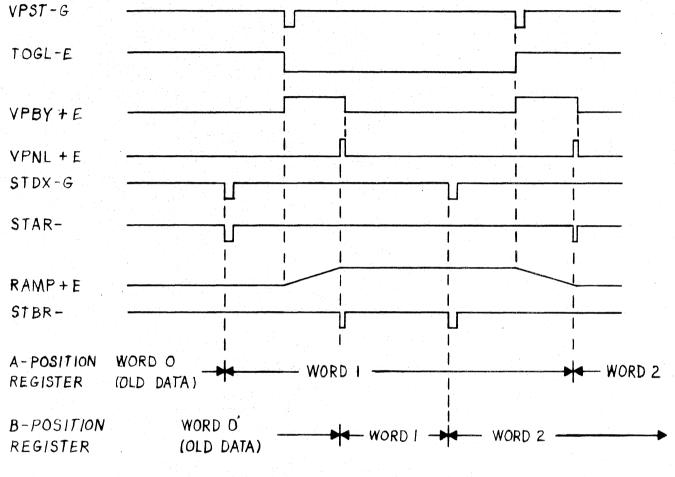

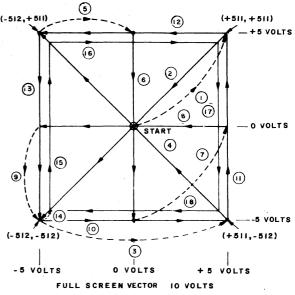

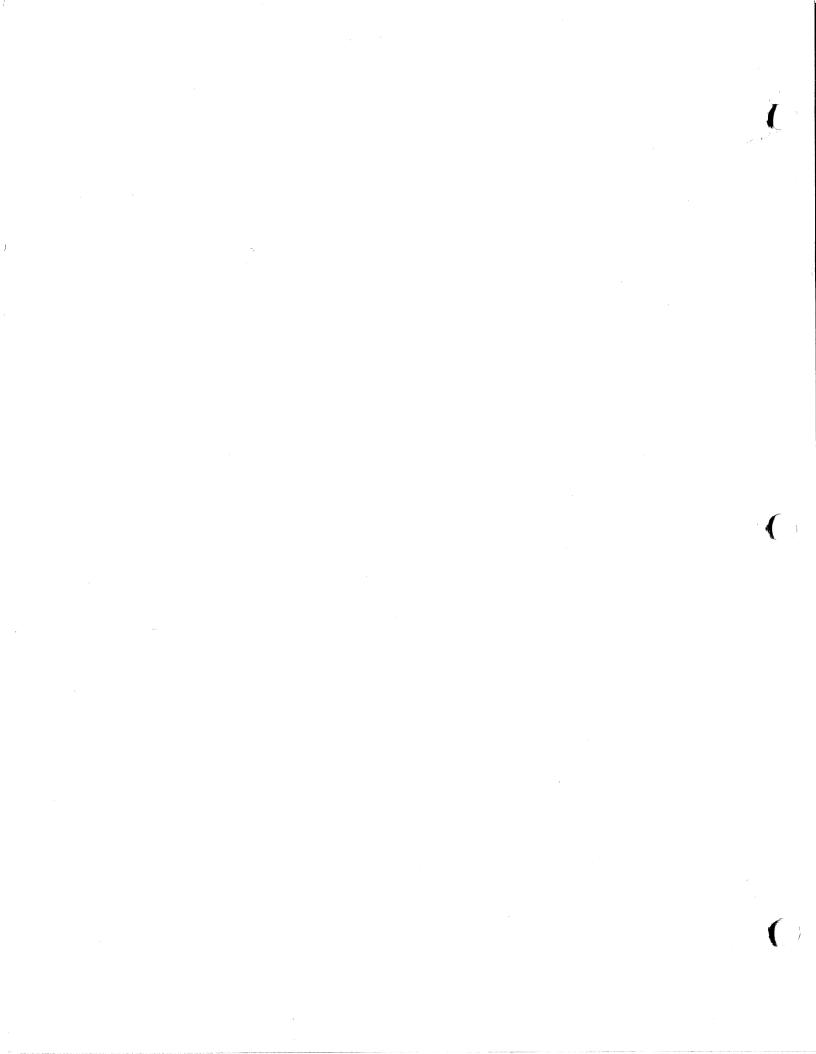

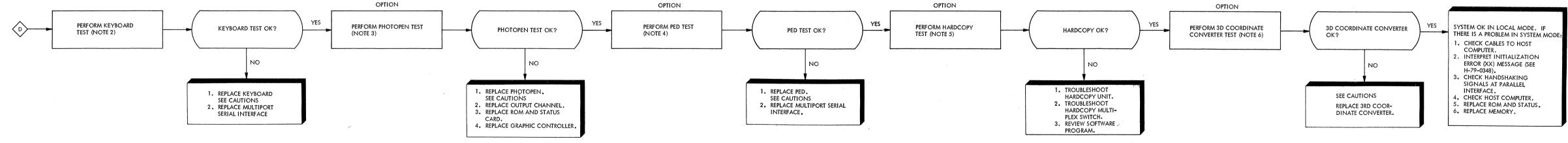

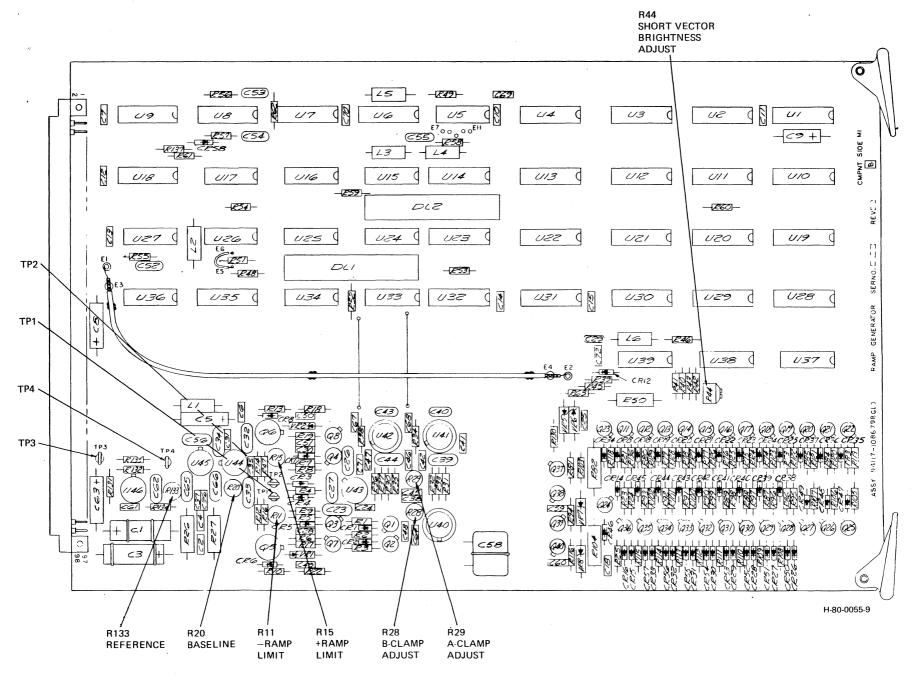

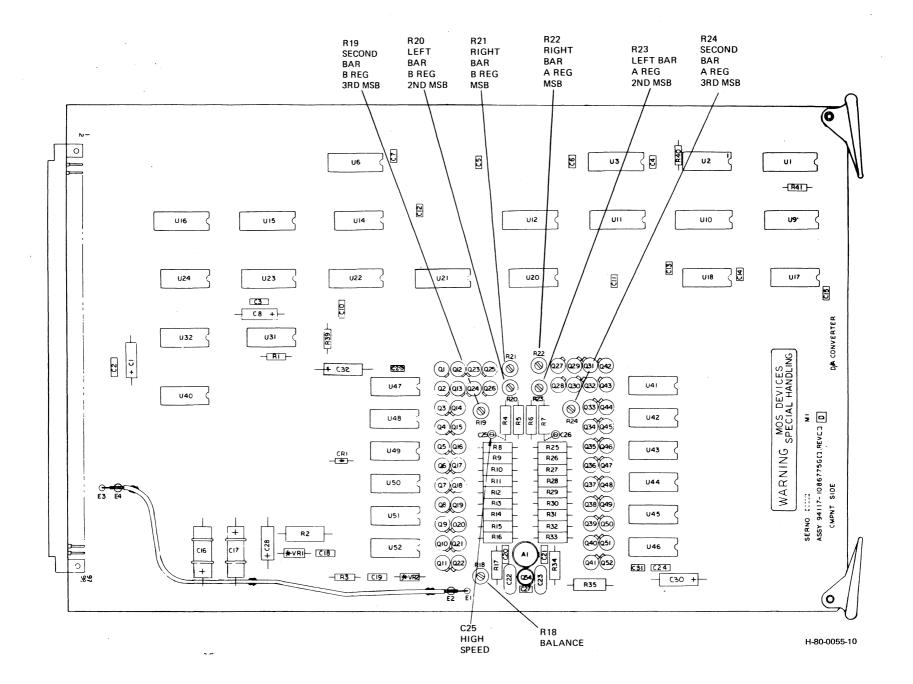

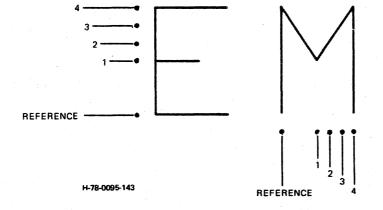

#### Number Page 1 - 8CRT Programmable vs Displayable Areas 1 - 122 - 1Terminal Controller Controls and Indicators 2 - 22-2 Verification Test Pattern 2-6 3 - 1Bus Grant Circuit, Simplified Diagram 3-7 3 - 2Processor Bus Timing 3-9 3-3 Interrupt Logic and Timing 3-11 3-4 Memory Organization 3-14 3-5 Read/Write Memory Card, Block Diagram 3-21 3-6 Parallel Interface LED Indicators 3-26 3-7 Parallel Interface Block Diagram 3-39 3-8 Parallel Interface State Diagram 3-41 3-9 Parallel Interface Output Transfer, Timing Diagram 3 - 433 - 10Parallel Interface Input Transfer, Timing Diagram 3-44 3-11 UART Functional Block Diagram 3-47 3 - 12Serial Interface, Block Diagram 3-57 3 - 13Display Processor, Block Diagram 3-61 Display Processor, Functional Block Diagram 3-14 3-63 3-15 Display Processor, Flow Diagram 3-65 3-16 ROM and Status Card, Block Diagram 3-79 3 - 17ROM and Status Card, Functional Block Diagram 3-81 Graphic Controller, Block Diagram 3-18 3-91 Graphic Controller, Functional Block Diagram 3-19 3-93 3-20 Character Generator for Typical Character Table 3-96 Character Generator Card, Block Diagram 3 - 213-103 3-22 Ramp Generator Timing 3 - 1123-23 Vector/Position Generator Block Diagram 3 - 1153-24 Ramp Generator Card, Block Diagram 3-119 3-25 D/A Converter Timing Diagram 3 - 1283-26 Vector Position Generator Pattern Development 3 - 1293-27 D/A Converter Card, Block Diagram 3-131 3-28 Output Channel Card P/N 1086771 Block Diagram 3 - 1393-29 Color Output Channel Card P/N 5977409 Block Diagram 3 - 141System Interconnect Panel 4-1 4-4 Controller Cabinet Interconnect Diagram 4-2 4-9 Serial Interface, Normal Switch Positions 4-18 4–3 Terminal Controller Troubleshooting Diagrams 5-5 5-1 5-2 Ramp Generator Card Adjustments 5 - 155-3 D/A Converter Card Adjustments 5 - 17Terminal Verification Pattern, Character Height and Width 5-4 5-18 Adjustment Gauges Character Generator Card Adjustments 5 - 195-5 1 5-20 5-6 Oscilloscope Display 5-21 5-7 Monochrome Output Channel Adjustments Color Output Channel Adjustments 5-25 5-8 A-1 Illustrative Signal Mnemonic A-1

v

## LIST OF TABLES

(

(

Ci

}

| Number       |                                                                                                                               | Page         |

|--------------|-------------------------------------------------------------------------------------------------------------------------------|--------------|

| 1-1          | Physical Characteristics                                                                                                      | 1-4          |

| 1-2          | GRAPHIC 7 Terminal Controller Specifications                                                                                  | 1-17         |

| 1-3          | Basic Components of the Model 7709 Terminal Controller                                                                        | 1-18         |

| 2-1          | Terminal Controller Controls and Indicators                                                                                   | 2-1          |

| 2-2          | Serial Interface Port Codes                                                                                                   | 2-9          |

| 2-3          | Local Mode Command Summary                                                                                                    | 2-12         |

|              | Standard Transfer Table                                                                                                       | 2-17         |

|              | Processor Subsystem Cards, Preferred Priority Arrangement                                                                     | 3-2          |

|              | Processor Bus Signals                                                                                                         | 3-2          |

|              | Standard Graphic Subsystem Cards                                                                                              | 3-5          |

|              | Power Bus (Common to All Cards)                                                                                               | 3-5          |

|              | Read/Write Memory Card Addressing                                                                                             | 3-15         |

|              | Parallel Interface Interrupt Trap Addresses                                                                                   | 3-27         |

|              | Parallel Interface Register Addresses                                                                                         | 3-29         |

|              | Parallel Interface Status Register Bit Descriptions                                                                           | 3-29         |

|              | Single-Word Output Transfer Sequence                                                                                          | 3-33         |

|              | DMA Output Transfer Sequence                                                                                                  | 3-34         |

|              | Single-Word Input Transfer Sequence                                                                                           | 3-36         |

|              | DMA Input Transfer Sequence                                                                                                   | 3-37         |

|              | Multiport Serial Interface Devices                                                                                            | 3-48         |

|              | Serial Interface Port Device Assignments                                                                                      | 3-49         |

| 3-15         | Program Address/Hardware Relationships for Different PN 1086746                                                               | 0 (0         |

| <b>A A A</b> | 4K ROM Configurations                                                                                                         | 3-69         |

| 3-16         | Program Address/Hardware Relationships for Different PN 1088682                                                               | 0 70         |

| 0 17         | 8K ROM Configuration                                                                                                          | 3-70         |

|              | Display Mask Register Bits                                                                                                    | 3-71         |

|              | DAnn-B Processor Bus Data Word                                                                                                | 3-72         |

|              | Interrupt Status Register Input Signals                                                                                       | 3–72<br>3–73 |

|              | Priority Encoder Trap Address Values                                                                                          | 3-77         |

|              | TTY Receive Status Register (Address 1775608) Bit Descriptions                                                                | 3-77         |

|              | TTY Transmit Status Register (Address 1775648) Bit Descriptions<br>TTY Receive Data Buffer (Address 1775628) Bit Descriptions | 3-78         |

|              | TTY Transmit Data Buffer (Address 1775628) Bit Descriptions                                                                   | 3-78         |

|              | Graphic Controller Control ROM Bit Assignments                                                                                | 3-85         |

|              | Graphic Controller Microcontroller Register Addresses and                                                                     | 5.02         |

| 5-20         | Function Control Signal Selection Codes                                                                                       | 3-88         |

| 3-27         | Display Parameter Setup Data Codes                                                                                            | 3-99         |

|              | Stroke Times vs. Character Size                                                                                               | 3-101        |

|              | Mode Control Logic Input/Output Relationships                                                                                 | 3-108        |

|              | Line Structure Select Bits                                                                                                    | 3-109        |

|              | Line Vector Speed Select Bits                                                                                                 | 3-109        |

|              | Programmable Divider Bit Codes                                                                                                | 3-135        |

|              | Connector P3 Configurations                                                                                                   | 4-2          |

|              | Parallel Interface I/O Connectors, Pin Assignments                                                                            | 4-7          |

|              | Multiport Serial Interface I/O Connectors, Pin Assignments                                                                    | 4-8          |

|              | ROM and Status Card Jumper Configurations                                                                                     | 4-11         |

|              |                                                                                                                               |              |

## LIST OF TABLES (Cont)

|        | ·                                                    |      |

|--------|------------------------------------------------------|------|

| Number |                                                      | Page |

| 4-5    | Multiport Serial Interface Parameter Selections      | 4-14 |

| 4-6    | Parallel Interface Parameter Selections              | 4-18 |

| 4-7    | Ramp Generator Parameter Selections                  | 4-21 |

| 5-1    | Ramp Generator Adjustments                           | 5-14 |

| 5-2    | D/A Converter Adjustments                            | 5-16 |

| 5-3    | Character Generator Adjustments                      | 5-18 |

| 5-4    | Monochrome Output Channel Adjustments                | 5-20 |

| 5-5    | Color Output Channel Adjustments                     | 5-23 |

| A-1    | Signal Source Codes                                  | A-2  |

| A-2    | Mnemonics Dictionary                                 | A-3  |

| A-3    | Power Supply Mnemonics                               | A-8  |

| A-4    | Card Slots XAl to XA8, Common Controller Bus Signals | A-10 |

| A-5    | ROM and Status Card Slot XA9 Signals                 | A-12 |

| A-6    | Graphic Controller Card Slot XAlO Signals            | A-14 |

| A-7    | Character Generator Card Slot XAll Signals           | A-16 |

| A-8    | Ramp Generator Card Slot XA13 Signals                | A-18 |

| A-9    | D/A Converters Card Slots XA14, XA15 Signals         | A-20 |

| A-10   | Output Channel Card Slot XA16 Signals                | A-22 |

| B-1    | Connector J2, Inputs to Host Computer                | B-1  |

| в-2    | Connector J2, Outputs from Host Computer             | B-1  |

| в-3    | Connector J3, Inputs to Host Computer                | В-2  |

| в-4    | Connector J3, Outputs from Host Computer             | в-3  |

79-580-009

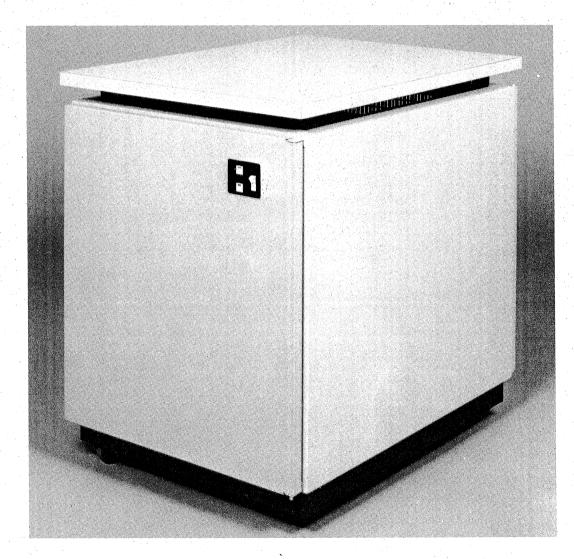

Figure 1-1. GRAPHIC 7 Terminal Controller

1-0

#### SECTION 1

#### GENERAL INFORMATION

#### 1.1 INTRODUCTION

The GRAPHIC  $7^{(R)}$  system is an intelligent interactive graphic display system that is compatible with most computers. System output is a display image on a CRT indicator.

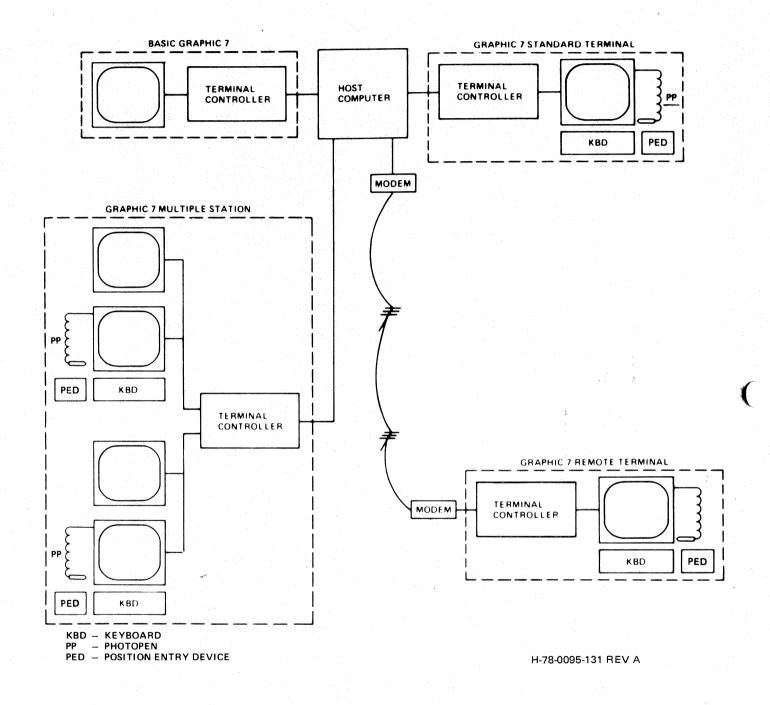

The GRAPHIC 7 terminal controller (figure 1-1) is a fundamental component of the GRAPHIC 7 system (figure 1-2).

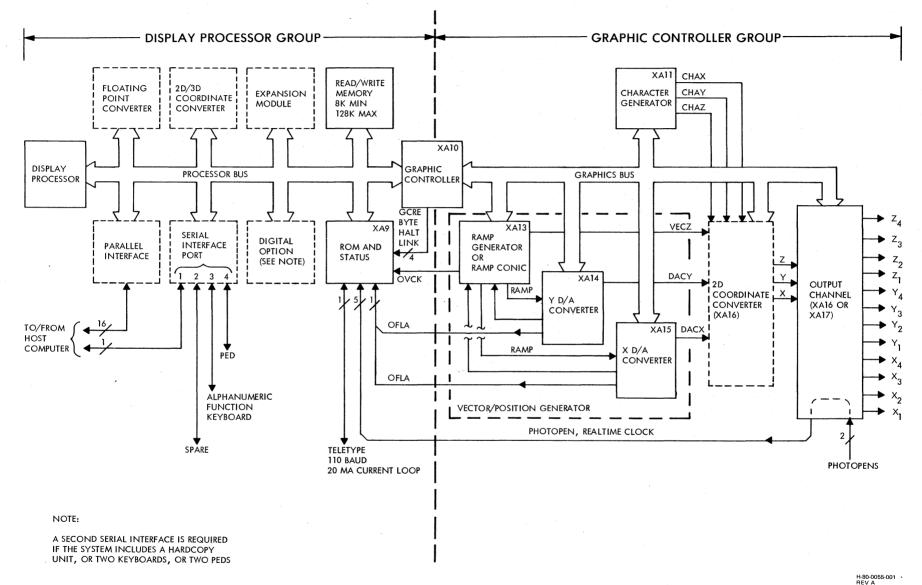

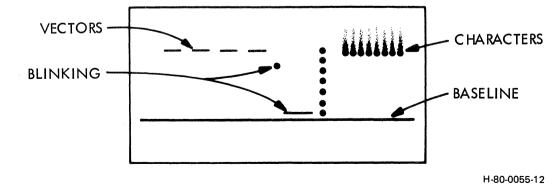

The terminal controller is that component of the GRAPHIC 7 system that receives instructions from the host computer and converts those instructions to X, Y, Z drive signals that produce graphic displays on up to four display indicators. The displays may consist of combinations of lines (vectors), conics, alphanumerics, and special symbols. Displays may have a wide variety of formats: tabular, maps, diagrams, or pictorial. The terminal controller determines the form of the display, the position of the data, its intensity, size, orientation, and color.

When suitable options are provided, the terminal controller can impart motion to displayed data in two or three dimensions.

The terminal controller is controlled either by a host computer or by the terminal operator. The computer may be located near the terminal controller or remote from it; in the latter case, modems may be required for communication.

Major assemblies of the terminal controller include two microprocessors, readonly memory, random access read/write memory, vector and character generators, and an output channel.

Various ancillary devices such as tape readers, position entry devices, alphanumeric/function keyboards, PHOTOPEN<sup>(B)</sup>, and hardcopy units are available as options.

#### 1.2 PHYSICAL DESCRIPTION

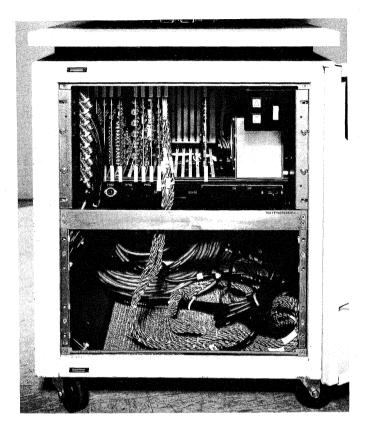

The terminal controller comprises a card cage containing 17 circuit card slots, a power supply, and two blower fans (figure 1-3). A control panel covers the front of the unit; a protective cover is mounted on the back.

The terminal controller is mounted either in a standard 19-inch equipment rack or in an optional cabinet (figure 1-4). In either case, the control panel is removed for access into the terminal controller.

® GRAPHIC 7 and PHOTOPEN are registered trademarks of Sanders Associates, Inc.

C

i. T

0

Figure 1-2. Typical GRAPHIC 7 System Configurations

1-2

80-346-010

Figure 1-3. Terminal Controller Interior

79-580-011

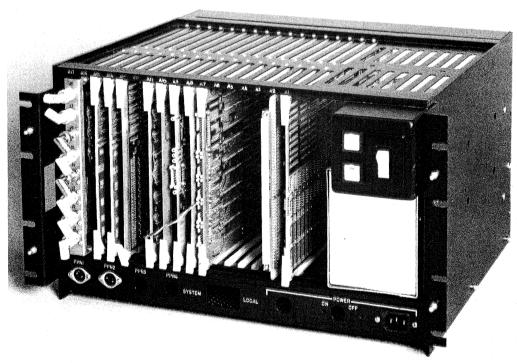

Figure 1-4. Card Cage

As shown in figure 1-3, the circuit cards are inserted into the card cage from the front of the terminal controller, and plug into a wire-wrapped backplane. The blower fans, located beneath the card cage and power supply, draw air from the bottom of the unit and discharge the air through the top.

The basic terminal controller contains nine standard circuit cards. Optional cards are inserted as required. Most applications use both the multiport serial interface and the parallel interface cards. Other cards are available to expand the read/write memory or provide special display functions.

Figure 1-5 shows the circuit card order assumed for this manual. The figure indicates the normal locations for a full complement of circuit cards, including the optional interface cards and read/write memory expansion cards. The figure also shows the optional circuit card extender located in the normally unused IAIXA12 position.

Table 1-1 lists the physical characteristics of the terminal controller and circuit cards.

Table 1-1. Physical Characteristics

| TTDMTNAT | CONTROLLER |  |

|----------|------------|--|

| LEKMINAL | CONTROLLER |  |

| Height | 10.5 inches (26.8 cm)                            |

|--------|--------------------------------------------------|

| Width  | 19.0 inches (48.2 cm) including mounting flanges |

| Depth  | 16.0 inches (40.6 cm)                            |

| Weight | 55 pounds (25 kg) including circuit cards        |

CIRCUIT CARDS

| Height | 12-3/8 inches (31.4 cm) |

|--------|-------------------------|

| Width  | 7-3/4 inches (19.7 cm)  |

The terminal controller can operate with 100V - 120V or 220V - 240V ac input power. An input power control panel (located in the lower front of the equipment cabinet) contains a fuse, a power receptacle, and a removable configuration plug. The configuration plug must be wired for the proper voltages.

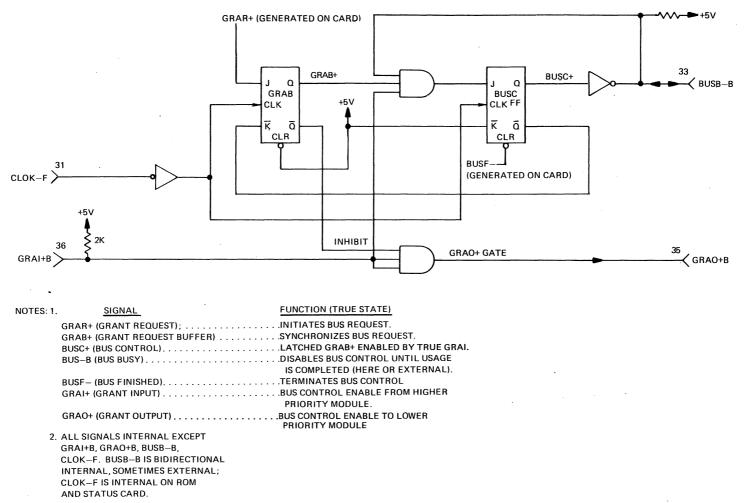

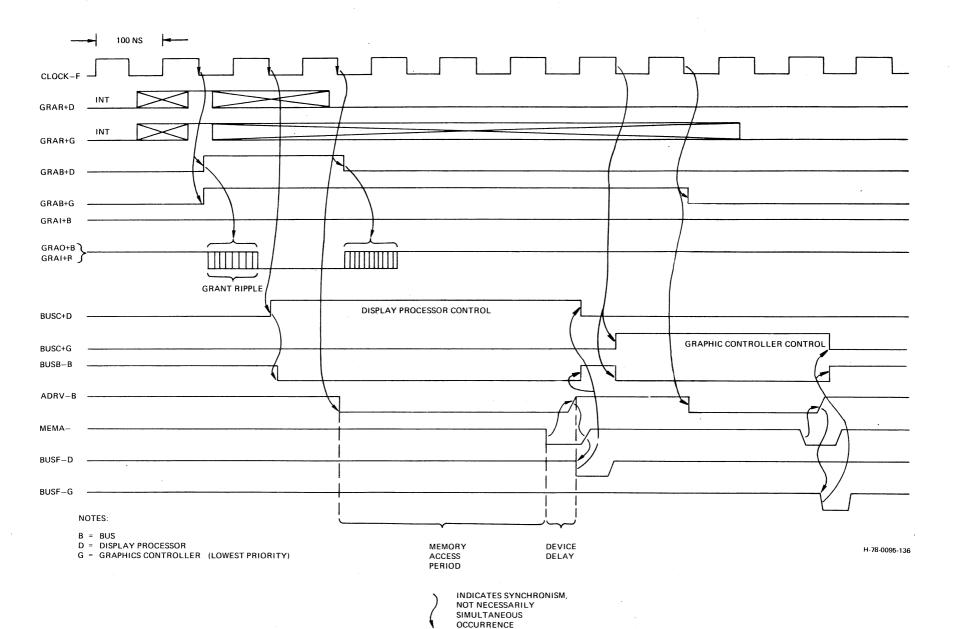

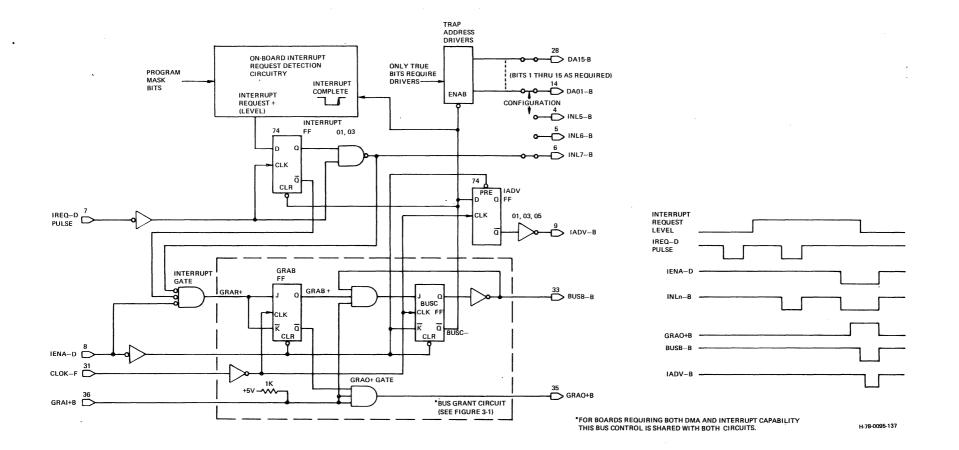

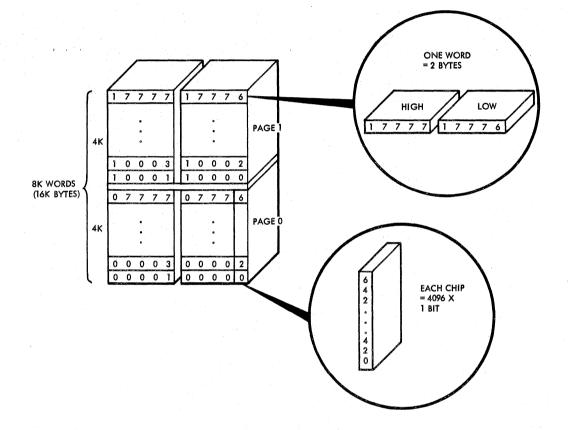

## USER'S OPTION SLOT ASSIGNMENTS (SEE NOTE)