# **TRAINING GUIDE**

6

# SYSTEMS 70 북동 TRAINING GUIDE

RADIO CORPORATION OF AMERICA

70 - 45 - 801

The information contained herein is subject to change without notice. Revisions may be issued to advise of such changes and/or additions.

First Printing: December, 1964 Second Printing: January, 1965

# CONTENTS

# Page

| FUNCTIONAL DESCRIPTION OF RCA 70/45-55 SYSTEMS | 1            |

|------------------------------------------------|--------------|

| Introduction                                   | 1            |

| System Characteristics                         | 1            |

| Scratch Pad Memory                             |              |

| Data Formats                                   |              |

| Instruction Formats                            |              |

| Address Generation                             |              |

| Program Interrupt                              |              |

| Input/Output                                   |              |

| Symbology                                      |              |

|                                                |              |

| DECIMAL ARITHMETIC                             |              |

| Instruction Format                             |              |

| Data Format                                    |              |

| Packing, Unpacking Data                        | , 11         |

| Decimal Operations                             | , 11         |

| RCA 70/45-55 ASSEMBLY SYSTEM                   | . 15         |

| Program Format                                 |              |

|                                                |              |

| Symbols                                        |              |

| Expressions                                    |              |

| Defining Storage                               |              |

| Defining Constants                             |              |

| Attributes                                     |              |

| Statement Fields                               | . 17         |

| DATA MANIPULATION                              | . 22         |

| Bit Manipulation                               |              |

| Instructions                                   |              |

| Assembly System Hexadecimal Constants          |              |

| Decimal Data Shifting                          |              |

| Logical Data Shifting                          |              |

| Character Movement                             |              |

| Logical Testing                                |              |

| Editing Data                                   |              |

|                                                | , 20         |

| FIXED-POINT ARITHMETIC                         |              |

| Fixed-Point Numbers                            |              |

| Assembly System Constants                      | . 27         |

| Assembly Storage Definition                    |              |

| Instructions                                   | . 28         |

| PROGRAMMING TECHNIQUES                         | . 32         |

| Address Manipulation                           |              |

| Expression Constant                            | . 32         |

| Using, Drop Instructions                       | . 32         |

| Data Translation                               |              |

|                                                | ,            |

| Subroutines                                    | 25           |

| Subroutines                                    |              |

| P-counter                                      | . 35         |

|                                                | . 35<br>. 36 |

# CONTENTS (Continued)

| FLOATING-POINT ARITHMETIC                      | 40 |

|------------------------------------------------|----|

| Introduction                                   | 40 |

| Data Format                                    | 40 |

| Conversion                                     | 40 |

| Normalization                                  | 41 |

| Assembly System Constants                      | 42 |

| Load and Store Instructions                    | 43 |

| Arithmetic Instructions                        | 45 |

| Compare and Halve Instructions                 | 47 |

| Condition Code                                 | 47 |

|                                                |    |

| INPUT/OUTPUT                                   | 49 |

| Basic Components                               | 49 |

| Input/Output Operations                        | 50 |

| Assembly System Instructions                   | 55 |

| Data Flow                                      | 55 |

| Multiprocessor Connections                     | 56 |

| r                                              |    |

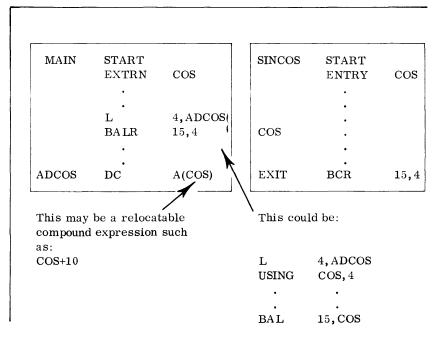

| PROGRAM CONTROL AND LINKING                    | 57 |

| Program Control Instructions                   | 57 |

| Program Linking                                | 58 |

|                                                |    |

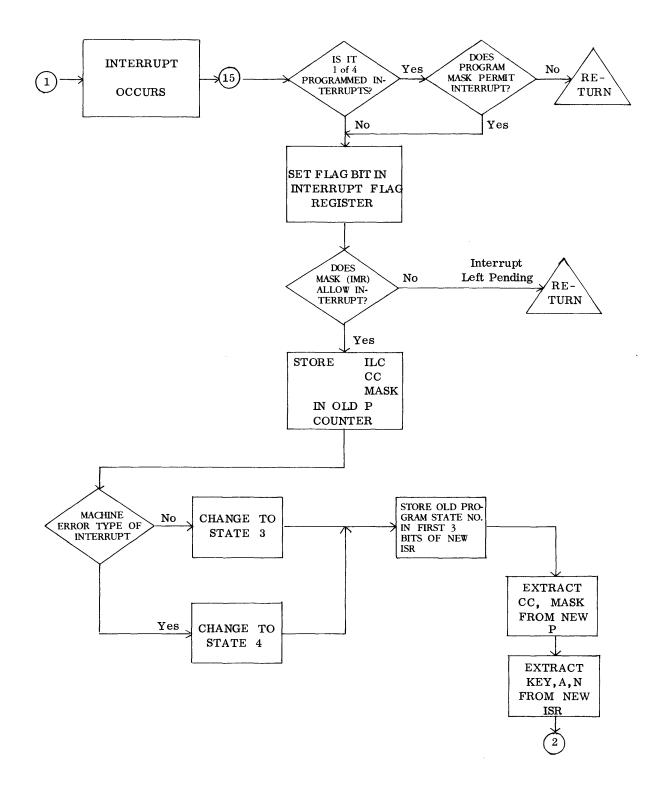

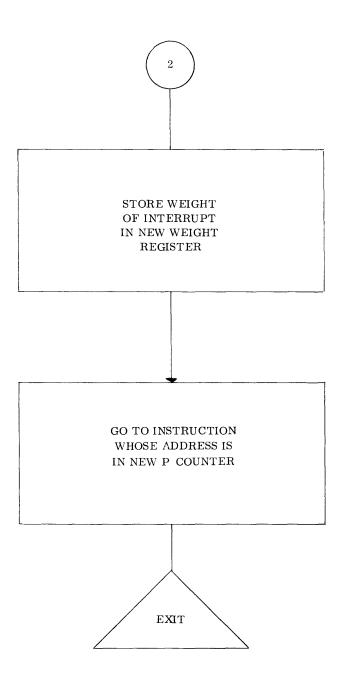

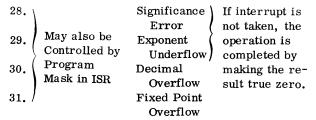

| INTERRUPT SYSTEM                               | 59 |

| Concepts of Interrupt System                   | 59 |

| Processor States                               | 59 |

| Scan                                           | 59 |

| P and ISR                                      | 60 |

| Interrupt Condition Summary                    | 63 |

| Privileged Instructions                        | 64 |

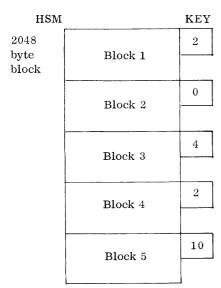

| Memory Protection                              | 65 |

| Clock                                          | 66 |

|                                                |    |

| APPENDIX A - INSTRUCTIONS IN ORDER BY MNEMONIC | 67 |

|                                                |    |

| APPENDIX B - CONDITION CODE                    | 68 |

# FOREWORD

# 70/45-55 TRAINING GUIDE

This manual is designed as an instructor/student guide to the Spectra 70/45-55 Systems. Emphasis is placed on programming techniques and on the application of the more powerful elements of the systems. Many programming illustrations and exercises are supplied. While the manual is organized from a pedagogical point of view, it depends heavily on the 70/45-55 Assembly and System Reference Manuals and should not be considered without access to these documents.

On the matter of content, the basic processor functions and instructions are described. Input/Output operations and programming are described as they relate to the basic processors. Programming is illustrated in the basic assembly language and the features of the basic assembly system are described.

Inexperienced programmers might find it helpful to study either the 70/15 or 70/25 Training Manual before studying this document.

# FUNCTIONAL DESCRIPTION OF RCA 70/45-55 SYSTEMS

# INTRODUCTION

This section of the manual describes the functional characteristics and the principal features of the 70/45-55 processors. The intent is to give the reader a coherent and meaningful summary of the capabilities of the processor, primarily from a system viewpoint.

This introductory section is not excessively concerned with detail, for each of the topics discussed here will be amplified in the succeeding sections. Appended to this section is a definition of the symbols used throughout the manual.

# SYSTEM CHARACTERISTICS

The RCA 70/45-55 are medium- to large-scale processors within the Spectra 70 family.

Some of their salient features are summarized in Charts 1 and 2.

An extremely important feature of the processors is the compatibility that they possess with the other processors in the Spectra 70 family, and with the IBM 360 System. The following charts summarize these compatibility features.

# SCRATCH-PAD MEMORY

The Scratch-Pad Memory contains the processor working registers. Each location is addressable and may be manipulated by several of the privileged instructions.

- 4 Processor States for efficient interrupt control

- Unique sets of general-purpose registers for each state

- Privileged instructions (those which can be executed only when specified by a program switch)

- Variable length instructions

- EBCDIC or ASCII Code

- Fixed and variable length data formats

- Memory protection

- Elapsed time clock

- 32 individually maskable interrupt conditions

- Multiplexor channel to simultaneously control up to 8 slow-speed I/O devices

- High-speed selector channels

- Multiplexor and each selector can control up to 256 I/O devices

- Wide variety of I/O devices, mass storage and communication equipment

- 11-way simultaneity on 70/45

- 14-way simultaneity on 70/55

- Up to 256 communications devices can operate simultaneously

- Read/write direct control for multiprocessor systems

- Scratch-Pad Memory of 512 bytes with 300ns 32-bit access cycle time

- DXC (Data Exchange Control) memory-tomemory transfer between 2 processors

- SHARING of memory by processors (70/55 only)

- Floating point arithmetic for scientific applications (optional in 70/45)

- Chart 2 -

|                   | $\frac{70/45}{100}$        | 70/55          |

|-------------------|----------------------------|----------------|

| Scope             | Medium                     | Medium - Large |

| Maximum Data Rate | 465K bytes                 | 640K bytes     |

| Storage           | 16-262K bytes              | 65–524K bytes  |

| Access Time       | 1.44us                     | .84us          |

| Data Path         | 2 bytes                    | 4 bytes        |

| Implementation    | Logic controlled           | Order code     |

|                   | by EO's contained          | implemented    |

|                   | in 2 read only<br>memories | by Hardware    |

- Chart 1 -

# Compatibility (within the Spectra family)

- A. Data Compatible 1. Same internal data code used by all

- processors.

- 2. Any peripheral device controller and its associated devices can be operated by any processor.

# B. Program Compatible

- 1. 70/25 programs executable on

- 70/45-55 with

- a. Minor editing

- b. Reassembly to link into 70/45-55 Operating System

- 2. Two-way compatibility between 70/45

- and 70/55.

# - Chart 3 -

# Compatibility with System 360

- A. Machine language compatible with 360 series systems having similar complements for all programs limited to 360's "Problem State".

- B. 360 series assembly language programs may be assembled and run on 70/45-55 provided the following are redefined:

- 1. Linkage to and descriptive information for 360 I/O and executive control routines.

- 2. User defined macro-instructions.

- 3. Privileged operations within user's own code.

- 4. References to standard locations (first 128 bytes of storage).

- C. External control parameters to the operating system must be defined in accordance with 70/45-55 requirements.

- Chart 4 -

# Scratch Pad contains:

- 1. General-purpose registers for each processor state.

- 2. Floating-point registers.

- 3. Interrupt masks.

- 4. Program control information.

- 5. Control words for I/O operations.

- 6. Buffer area for I/O operations.

- 7. Various hardware utility registers.

- Chart 5 -

# Scratch Pad Characteristics:

- 128 Words

- 32 bits per word

- 300 nanosecond cycle time

- Locations are uniquely addressed

- Not part of main memory

- Chart 6 -

# **GENERAL-PURPOSE REGISTERS**

Each program state has its own set of generalpurpose registers. These registers can be used:

- 1. as index registers

- 2. in address arithmetic and indexing

- 3. as accumulators for fixed point and logical operations.

Each register has a 32-bit capacity and is designated by number, 0-15. For some operations, two adjacent registers can be coupled, providing a twoword capacity.

# FLOATING-POINT REGISTERS (optional in 70/45)

Four floating-point registers are provided having a 64-bit capacity. They are designated by the numbers 0, 2, 4, and 6.

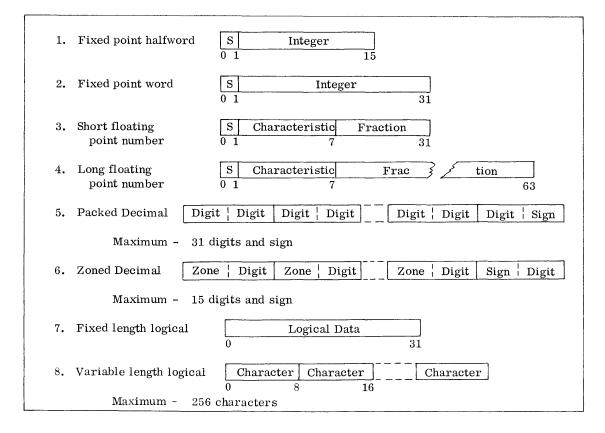

# DATA FORMATS

The basic building block of the various data (and instruction) formats is the byte. A <u>byte</u> contains 9 bits--8 bits of information plus a parity bit, which is used for accuracy control.

Bytes may be grouped to form:

- 1. Halfwords 2 consecutive bytes

- 2. Words 4 consecutive bytes

- 3. Double Words 8 consecutive bytes

Each byte is binarily addressable starting with location 0. Fixed length fields such as halfwords or words must begin on integral boundaries as shown in the following chart. Binary Address

| 0000 | 0001        | 0010 | 0011 | 0100 | 0101 | 0110 | 0111 | 1000  | 1001   |   |  |

|------|-------------|------|------|------|------|------|------|-------|--------|---|--|

| Byte | Byte        | Byte | Byte | Byte | Byte | Byte | Byte | Byte  | Byte   |   |  |

| Half | word        | Half | word | Half | word | Half | word | Half  | word   |   |  |

|      | Word Word   |      |      |      |      |      |      | W     | ord    |   |  |

|      | Double Word |      |      |      |      |      |      | Doubl | e Word | c |  |

- Chart 7 -

Note, therefore, that the addresses for the various units of information are related in the following way:

| Address Must Be a Multiple Of |

|-------------------------------|

| 1                             |

| 2                             |

| 4                             |

| 8                             |

|                               |

- Chart 8 -

# CHARACTER CODE

Characters(8-bit bytes)may be represented in either EBCDIC or ASCII code with equal facility. The user specifies the code by setting a program switch.

# Illustration

The characters 'RCA' are shown in both codes:

Fixed length data of 8, 16, 32, or 64 bits and variable length data of up to 256 characters may be processed. The eight data formats are summarized below.

| ASCII  | 1011 | 0010 | 1010 | 0011 | 1010 | 0001 |  |

|--------|------|------|------|------|------|------|--|

|        | R    |      | (    | 2    | A    |      |  |

|        |      |      |      |      |      |      |  |

| EBCDIC | 1101 | 1001 | 1100 | 0011 | 1100 | 0001 |  |

# Illustration

The number +1234 is expressed in the 4 possible decimal formats.

| 1. | Zoned-Decimal, EBCDIC                 | 1111 0001 | 1111 0010 | 1111 0011 | 1100 0100 |

|----|---------------------------------------|-----------|-----------|-----------|-----------|

|    |                                       | 1         | 2         | 3         | + 4       |

| 2. | Packed-Decimal, EBCDIC                | 0000 0001 | 0010 0011 | 0100 1100 | }         |

| 4. | Packed-Decimal, EDCDIC                | 1         | 2  3      | 4 +       |           |

|    |                                       |           |           |           | ,         |

| 3. | Zoned-Decimal, ASCII                  | 0101 0001 | 0101 0010 | 0101 0011 | 1010 0100 |

|    |                                       | 1         | 2         | 3         | + 4       |

| 4. | Packed-Decimal, ASCII                 | 0000 0001 | 0010 0011 | 0100 1010 | ]         |

|    |                                       |           |           |           |           |

|    | · · · · · · · · · · · · · · · · · · · | 1         | 23        | 4 +       |           |

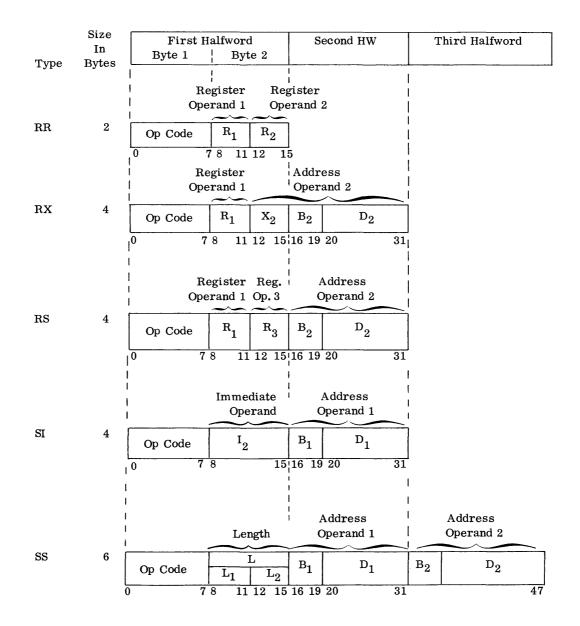

# INSTRUCTION FORMATS

There are five basic instruction formats. The instruction format expresses, in general terms, the operation to be performed as shown in the following chart:

- RR register-to-register operation

- RX register-to-indexed storage operation

- RS register-to-storage operation

- SI storage-and-immediate operand operation

- SS storage-to-storage operation

- Chart 9 -

The detailed format of each instruction is shown in Chart 10. (See following page.)

The instruction sub-fields are defined as follows:

| $R_1, R_2, R_3$                 | 4 bit operand register specification |

|---------------------------------|--------------------------------------|

| $\mathbf{x}_2$                  | 4 bit index register specification   |

| в <sub>1</sub> , в <sub>2</sub> | 4 bit base register designator       |

| $D_1$ , $D_2$                   | 12 bit displacement                  |

| $I_2$                           | 8 bit immediate operand              |

| L <sub>1</sub> , L <sub>2</sub> | 4 bit operand length specification   |

| L                               | 8 bit operand length specification   |

|                                 |                                      |

- Chart 11 -

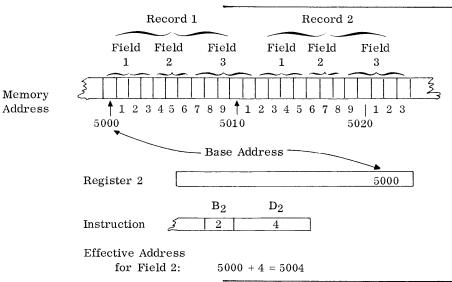

# ADDRESS GENERATION

The effective storage address is computed from the following binary components:

- 1. Base (contents of the designated base register,  $B_1$  or  $B_2$ )

- 2. Displacement  $(D_1, D_2)$ , and

- Index (contents of the designated index register, X<sub>2</sub>) for RX instructions

In computing the address, the base and index are treated as unsigned 24-bit positive binary integers in bits 8-31 of the designated register. The displacement is treated as a 12-bit positive binary integer. The effective address is computed by adding the components as binary numbers, ignoring overflow.

NOTE: If register 0 is specified as the base register and/or the index register, then a zero quantity is to be added, <u>regardless</u> of the contents of register 0.

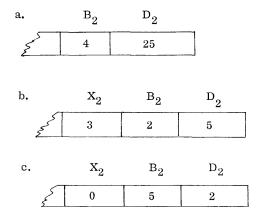

The following illustrations use decimal addresses for convenience.

Illustration

| Assume    | Reg.<br>Reg. |          |                |   |                | 20<br>04 |         |  |

|-----------|--------------|----------|----------------|---|----------------|----------|---------|--|

| Instructi | on           |          | <sup>B</sup> 1 | ] | D <sub>1</sub> | I        | $3_{2}$ |  |

|           | /            | <u>ک</u> | 12             |   | 0              | : 1      | 13      |  |

D<sub>2</sub> 20

The effective address of  $B_1, D_1$  is 00 00 20 00.

The effective address of  $B_2$ ,  $D_2$  is 00 00 05 00.

- Chart 10 -

Illustration

| Assume    | Reg.<br>Reg. |   |                | <br>$\begin{array}{c} 00\\ 02 \end{array}$ |       |

|-----------|--------------|---|----------------|--------------------------------------------|-------|

| Instructi | on           |   | $\mathbf{x}_2$ | $B_2$                                      | $D_2$ |

|           |              | ž | 3              | <br>2                                      | 1000  |

The effective address, composed of  $X_2$ ,  $B_2$ ,  $D_2$ , is 00 03 00 10 + 00 00 02 00 + 1000 = 00 03 12 10.

Illustration

# PROGRAMMING NOTE ON ADDRESSING

Because overflow is ignored, "wrap-around" can occur. The RCA 70/45 System allows addressing of a maximum of 262,144 bytes beyond which "wraparound" occurs. The 70/55 allows for addressing of a maximum of 524,288 bytes before "wrap-around" occurs.

# Illustration

Assume  $\begin{array}{ccc} B_{2} & 262 & 143 \\ D_{2}^{2} & 000 & 003, \text{ then the} \end{array}$

70/45 effective address is 000 002 and the 70/55 effective address is 262 146.

To process Record 2, the contents of Register 2 are increased by 12, the size of Record 1. The instruction field illustrated would then refer to Field 2 of Record 2.

If the instruction is an index-type instruction, a second general-purpose register, called an index register, also generates the address. In the above illustration, the index register (Register 3, for example) would initially be cleared to zero. After the first record is processed, the contents of Register 3 is increased by the record size. Then the instructions using Registers 2 and 3 for addressing would refer to Record 2. An illustration of this follows:

Effective Address for Field 2, Record 2: 5000 + 12 + 4 = 5016 The address wrap-around property provides negative indexing.

#### Illustration

It is desired to decrement the storage address by 1.

Thus, the rightmost 24 bits of the register specified by  $X_2$  should be all 1 bits; i.e., 524,287.

In forming constants to get deliberate wrap-around, say for decrementation, the situation should be viewed as if both processors wrapped at 524,288 to maintain compatibility. Thus, in the preceding example, although decrementation could be achieved on the 70/45 with X<sub>2</sub> = 262,143, such would not be the case in the 70/55.

# INSTRUCTION EXECUTION

Instructions are performed by the basic processing unit primarily in the sequential order of their locations. This sequence is altered by branching instructions and program interrupts. The detailed operation of the various branching instructions is determined by the Condition Code (CC). The two bits of the Condition Code provide for four possible settings--0, 1, 2, and 3. The Condition Code reflects such conditions as first operand high, equal, overflow, channel busy, etc.

# PROGRAM INTERRUPT

The interrupt system is designed to respond to asynchronously occurring external and I/O signals and to monitor exceptional conditions generated by the program Processor. The interrupt is facilitated in that the processor has four program states, each with its own set of registers.

# Processor States

- 1. Processing (User's program(s))

- 2. Interrupt response (interrupt conditions serviced)

- 3. Interrupt control (interrupt conditions analyzed)

- 4. Machine condition (machine error interrupts)

- Chart 12 -

There are thirty-two possible interrupt conditions such as Op-code trap, decimal overflow, selector trunk 1 terminate, etc., each individually maskable. Except for machine error conditions, if an interrupt condition is effected and is not masked out, control is given to state 3.

Other important features facilitating the interrupt system are outlined in Chart 13.

# Interrupt Features

- A. Read/Write Direct Control

- B. Privileged instructions.

- C. 32 interrupt conditions, each individually maskable.

- D. Priority scheme for interrupt conditions.

- E. Weight register allows cause of interrupt to be detected efficiently.

- F. Elapsed time clock with maximum cycle of 15.5 hours.

- G. Memory protection in blocks of 2048 bytes.

- Chart 13 -

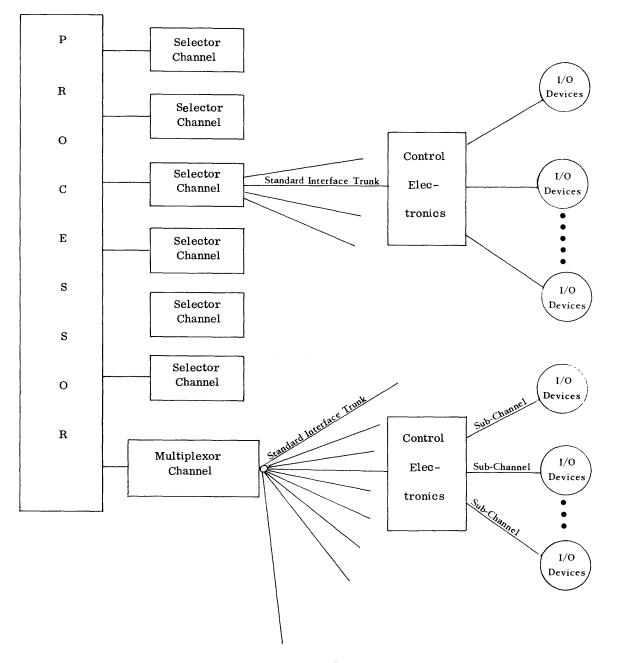

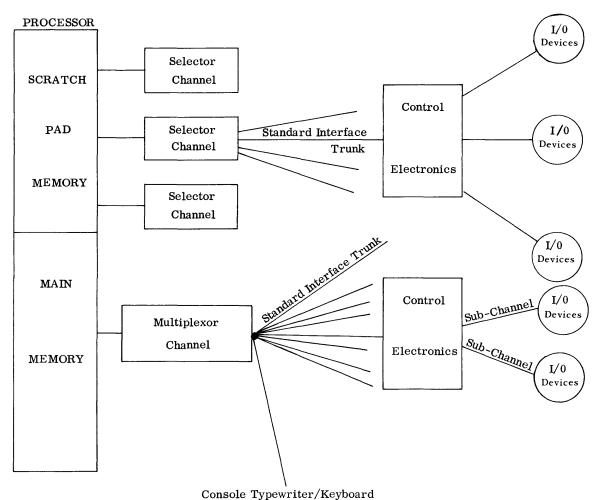

### INPUT/OUTPUT

A wide variety of input/output devices may be connected to the 70/45-55 processors. The processors contain I/O channels so that these devices can run off line, independent of program operation.

There are two types of I/O channels: Selectors and Multiplexors. A selector channel may have up to 256 devices connected, but only one may be operating at a time. Each of these devices is connected to a Control Electronics which, in turn, connects to the Selector via the RCA Standard I/O Interface. In general, several devices may be connected to a Control Electronics.

A Multiplexor channel may have connected up to 256 devices, and it is possible for all the devices to be operating at one time. The Multiplexor may be operated in a burst mode so that the Multiplexor in effect functions as a Selector.

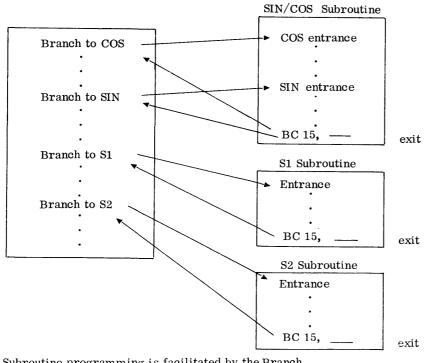

Diagram 1 depicts the logical connection of the I/O channels and I/O devices. (See following page.)

The following chart summarizes the  $I\!/O$  characteristics of the two processors.

| I/O Characteristics                 | 70/45      | 70/55      |

|-------------------------------------|------------|------------|

| Maximum data rate                   | 465K bytes | 640K bytes |

| Number of selectors                 | 0-3        | 0-6        |

| Control Electronics/selector        | 1 - 2      | 1-4        |

| Devices/selector (maximum)          | 256        | 256        |

| Multiplexor (standard)              | 1          | 1          |

| Control Electronics for Multiplexor | 8          | 8          |

| Devices attached to Multiplexor     | 256        | 256        |

| Maximum total Control Electronics   | 14         | 20         |

- Chart 14 -

# - Diagram 1 -

70/45-55 Input/Output Flow

Console Typewriter/Keyboard

Some possible I/O connections are shown below.

| 50/45       | # Control Electronics Attache<br>Per Channel |   |   |   |

|-------------|----------------------------------------------|---|---|---|

| 70/45       | Α                                            | В | С | D |

| Selector 1  |                                              |   | 2 | 2 |

| 2           |                                              |   | 2 | 2 |

| 3           |                                              |   |   | 1 |

| Multiplexor | 1                                            | 8 | 1 | 8 |

I/O Connections

Thus, in configuration D, Chart 15, 11-way simultaneity is possible because each of the 3 selectors can control an I/O device while the Multiplexor can control 8 devices at the same time.

| 70/55                               | # Conti | # Control Electronics Attached<br>Per Channel |                  |                       |  |  |

|-------------------------------------|---------|-----------------------------------------------|------------------|-----------------------|--|--|

| 10/00                               | A       | В                                             | С                | D                     |  |  |

| Selector 1<br>2<br>3<br>4<br>5<br>6 |         | 2                                             | 4<br>2<br>1<br>1 | 4<br>2<br>2<br>1<br>1 |  |  |

| Multiplexor                         | 1       | 8                                             | 4                | 8                     |  |  |

- Chart 16 -

Because devices operating in the multiplex mode require more processor time to service each byte than selector or burst mode, the peak data rates must be weighted. The weights for the various modes of operation are shown below.

|             | 70/45<br>Weight | 70/55<br>Weight |

|-------------|-----------------|-----------------|

| Multiplexor | 7.5             | 4.0             |

| Burst Mode  | 1.0             | 1.0             |

| Selector    | 1.0             | 1.0             |

Thus, two 120KC tapes could not operate simultaneously via the Multiplexor because their combined data rate, 960KC, exceeds the maximum data rate of the processor.

# SYMBOLOGY

The following symbols are used throughout this manual to define and describe instructions.

- Bn Instruction base register number field n  $(B_1 \text{ or } B_2)$

- Dn Instruction displacement field n ( $D_1$  or  $D_2$ )

- I2 Immediate data byte of an instruction(operand 2)

- Ln Instruction length-of-operand field n (L,  $L_1$ , or  $L_2$ )

- M Instruction mask field (replaces an R field)

- Rn Instruction general-purpose register field n ( $R_1$ ,  $R_2$ , or  $R_3$ )

- (Rn) The contents of the general-purpose register specified

- Rn The absolute value of the contents of Rn

- ${f R}_n^{+1}$  The next sequential register following the one specified

- RN General-purpose register N; N=0, 1, 2,..., 15

- RN<sup>+1</sup> The next sequential register following RN

- S Storage field of an assembly instruction (S,  $S_1$ , or  $S_2$ )

- Sbn Storage location whose address is (Bn)+Dn

- Srn Storage location whose address is contained in Rn

- Sxn Storage location whose address is (xn)+(Bn) + Dn

- X<sub>2</sub> Instruction index register field (operand 2)

- \_\_\_\_\_ Is transferred to

- = Is equal to

- Is greater than

- Is less than

- < Is less than or equal to

- > Is greater than or equal to

- $\neq$  Is not equal to

>

<

Note that symbols such as Bn represent some base (general-purpose) register and/or its address as an instruction field. Also, while Sbn, for example, is the address of one byte in memory, it also refers to the entire field starting at that byte.

# Questions

- 1. How many general-purpose registers are there in the Processing State? What are their uses?

- 2. To what do ASCII and EBCDIC refer?

- 3. Match the following:

| ASCII  |          | a. | 32 bits      |

|--------|----------|----|--------------|

| Packed |          | b. | Zoned data   |

| Word   | <u> </u> | c. | 8 bits       |

| Byte   | ····     | d. | Decimal data |

4. What is the result of packing the following field? Is it plus or minus?

| 11111001 | 11110000 | 11 <b>11</b> 0101 | 11010110 |

|----------|----------|-------------------|----------|

|          |          |                   |          |

- 5. What are the sizes of the following numeric fields?

- a. fixed-point number

- b. floating-point number

- c. decimal arithmetic field

- 6. What is integral storage alignment?

- 7. What is the Processing State?

- 8. What is the Condition Code?

- 9. What is immediate data?

- 10. General-purpose registers 2, 3, 4, and 5 contain the following addresses:

| <b>2</b> | 3000 |

|----------|------|

| 3        | 25   |

| 4        | 4000 |

| 5        | 142  |

What are the effective addresses generated for the following instruction fields?

11. What are the major differences between selector and multiplexor channels?

# DECIMAL ARITHMETIC

This section describes the instructions and data format associated with decimal arithmetic. Instruction formats, in machine and written form, are illustrated. Overflow and the condition codes set by the instructions are illustrated.

# INSTRUCTION FORMAT

| Bytes    | 1  | 2     |       | 3  |  | 4              | 5     |  | 6     |  |

|----------|----|-------|-------|----|--|----------------|-------|--|-------|--|

| SS form: | OP | $L_1$ | $L_2$ | в1 |  | D <sub>1</sub> | $B_2$ |  | $D_2$ |  |

Written form: OP  $D_1(L_1, B_1), D_2(L_2, B_2)$ .

Note that the written L's are one unit greater than the machine L's; i.e., the written L is the actual field length, the machine L is one byte less.

RX form:

| Bytes | 1  | 2                             | 3  | 4     |  |

|-------|----|-------------------------------|----|-------|--|

|       | OP | $\mathbf{R}_1   \mathbf{X}_2$ | в2 | $D_2$ |  |

Written form: OP  $R_1, D_2(X_2, B_2)$

# DATA FORMAT

Decimal operations use the packed format for data. Z means zone in the following example.

Unpacked: Z1 Z2 Z3 +4

Packed: 01 23 4+

# PACKING, UNPACKING DATA

$(Sb_2)$  is extended with leading zeros, if necessary, to fill  $Sb_1$ . (The R indicates that the operation is performed right to left.) The fields may overlap.

# DECIMAL OPERATIONS

When CC appears following an instruction definition, it indicates that the Condition Code is set. The L indicates a left to right operation. (See table below.)

Note that the MVC instruction specifies only one L field. Thus, L can have a maximum value of 256 (255 in machine form).

Programming note: Because the move operation is performed from left to right, one character at a time, it is possible to propagate a character through a field by having the  $Sb_1$  field start one byte to the right of the  $Sb_2$  field. The two fields must overlap.

# CONDITION CODES

| OPERATION            | 0 | 1 | 2 | 3        |

|----------------------|---|---|---|----------|

| Arithmetic result is | 0 | Θ | + | overflow |

| Operand 1 compares   | = | < | > |          |

Note that overflow only applies to AP, SP, and ZAP. Also, plus zero compares as equal to minus zero.

| PACK(SS): | Delete zones, pack $(Sb_2) \longrightarrow Sb_1$                      | $D_1(L_1, B_1), D_2(L_2, B_2)$ R |

|-----------|-----------------------------------------------------------------------|----------------------------------|

| UNPK(SS): | Insert zones, unpack (Sb <sub>2</sub> ) $\rightarrow$ Sb <sub>1</sub> | $D_1(L_1, B_1), D_2(L_2, B_2)$ R |

| Name (Form)                                                                                                                                                                        | Mnemonic                                       | Operation                                                       | Written Operand Form                                 |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|-----------------------------------------------------------------|------------------------------------------------------|--|--|

| Add Decimal (SS)<br>Subtract Decimal (SS)<br>Zero and Add (SS)<br>Divide Decimal (SS)<br>Multiply Decimal (SS)<br>Compare Decimal (SS)<br>Move (SS)<br>Branch on Condition<br>(RX) | AP<br>SP<br>ZAP<br>DP<br>MP<br>CP<br>MVC<br>BC | $\begin{array}{rrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrr$            | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |  |  |

|                                                                                                                                                                                    |                                                | Branch to $Sx_2$ if a mask bit corresponds to a condition code. |                                                      |  |  |

# Illustrations

The relation of the Condition Code and several masks of a BC instruction is shown below:

| CC   | 0 | 1 | 2 | 3 |               |

|------|---|---|---|---|---------------|

| M=4  | 0 | 1 | 0 | 0 | test CC1      |

| M=12 | 1 | 1 | 0 | 0 | test CC0 or 1 |

| M=15 | 1 | 1 | 1 | 1 | test all      |

When M = 15 the instruction acts as an Unconditional Branch instruction.

# MULTIPLICATION

(Sb<sub>1</sub>)

$$\underbrace{\begin{array}{c} 00 & 00 & 42 & 34 & 1+ \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\$$

Product 00 05 08 09 2-

|    |           |                   | Inv      | alid Operati       | ons                                                 |

|----|-----------|-------------------|----------|--------------------|-----------------------------------------------------|

|    | (         | Sb <sub>1</sub> ) | OP       | (Sb <sub>2</sub> ) | Reason                                              |

|    | 42        | 3 +               | +        | 62 1+              | Sum too large                                       |

|    | 42        | 3 +               | +        | 24 00 0 -          | - (Sb <sub>2</sub> ) too long                       |

|    | 02        | 5 +               | x        | 00 6 -             |                                                     |

|    | 63        | 4 +               | x        | 4 -                |                                                     |

|    |           |                   |          |                    | leading zeros                                       |

| 41 | <b>24</b> | 0 +               | ÷        | 523-               | - (Sb <sub>1</sub> ) lacks                          |

|    |           |                   |          |                    | leading zero                                        |

| 00 | 41        | 0 +               | ÷        | 03 2 -             | - 0320 < 0410                                       |

|    |           |                   |          |                    | the quotient                                        |

|    |           |                   |          |                    | would be too                                        |

|    |           |                   |          |                    | large                                               |

| 00 | 41        | 2 +               | ÷        | 05 23 0 -          | $L_2 = L_1$                                         |

|    |           |                   | stration |                    |                                                     |

| Lo | catio     | ons               | 4004     | 4-4007: 00         | 1                                                   |

| Lo | cati      | ons               | 4008     | 8-4009:            | 92 5+ $Sb_2^-$                                      |

| Re | gist      | er 4:             |          |                    | 40 00 -                                             |

| Wr | itte      | n form            | : OP     | $D_1 (L_1, B_1)$   | , D <sub>2</sub> (L <sub>2</sub> , B <sub>2</sub> ) |

|    |           |                   |          |                    |                                                     |

MP 4(4, 4), 8(2, 4)

Result 4004-4007: 02 24 77 5+

Example 1: (Z represents the four-bit zone)

| Item               | <u>Data Form</u> |               | Va            | lue           |               | Locations |

|--------------------|------------------|---------------|---------------|---------------|---------------|-----------|

| Part Number        | Zoned            |               | $\mathbf{Z2}$ | $\mathbf{Z3}$ | $\mathbf{Z4}$ | 4001-4003 |

| Quantity           | Packed           |               | 01            | 24            | 3+            | 4004-4006 |

| Unit Cost (\$9.25) | Packed           |               |               | 92            | 5+            | 4007-4008 |

| Discount factor    | Packed           |               |               | 09            | 0+            | 4009-4010 |

| Test constant      | Zoned            | $\mathbf{Z5}$ | Z0            | $\mathbf{Z0}$ | + 0           | 4011-4014 |

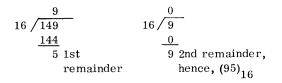

DIVISION

(Sb<sub>1</sub>) 04 12 4+

$$\div$$

(Sb<sub>2</sub>) 52 3-

L<sub>1</sub>=3 L<sub>2</sub>=2

$\overbrace{7-463+}^{7-463+}$

Quotient Remainder

L<sub>1</sub>-L<sub>2</sub> bytes L<sub>2</sub> bytes

Examples of valid and invalid arithmetic operations follows:

# Valid Operations

|    | (         | (Sb <sub>1</sub> ) | OP | (Sb <sub>2</sub> ) | Result: (Sb <sub>1</sub> ) |

|----|-----------|--------------------|----|--------------------|----------------------------|

|    | <b>42</b> | 3+                 | +  | 00 02 4-           | 39 9+                      |

| 00 | 08        | 9+                 | ×  | 0 -                | 00 00 0-                   |

|    | 00        | 4+                 | ×  | 4 -                | 01 6-                      |

| 04 | <b>12</b> | 4+                 | ÷  | 52 3-              | 7 - 46 3+ (rem.)           |

| 00 | <b>41</b> | 2-                 | ÷  | 32 3+              | 1 - 08 9- (rem.)           |

Prepare an output item, in zoned form, containing the part number and total cost, starting at location 5000. If the quantity equals or exceeds 5000, apply a 10% discount to the total cost. Assume that General-Purpose Registers 1, 4, and 5 contain 1000, 4000, and 5000 respectively.

| Storage<br>Location                                                  | Inst.<br>Bytes                                      | ОР                                                        | Operand                                                                                                                                                                                         | Remarks                                                                                                                                                                                                                                    |

|----------------------------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1000<br>1006<br>1012<br>1018<br>1022<br>1028<br>1034<br>1040<br>1044 | 6<br>6<br>6<br>4<br>6<br>6<br>6<br>6<br>4<br>6<br>6 | MVC<br>PACK<br>CP<br>BC<br>ZAP<br>MP<br>UNPK<br>BC<br>ZAP | $0(3,5), 1(4) \\ 15(3,4), 11(4,4) \\ 4(3,4), 15(3,4) \\ 10, 44(0,1) \\ 15 (5,5), 4(3,4) \\ 15 (5,5), 7(2,4) \\ 3(7,5), 15(5,5) \\ 15, 40(0,1) \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ $ | Part number $\rightarrow$ output<br>Pack the test constant<br>Quantity: 5000<br>If Qty $\geq$ 5000, go to 1044<br>Extend quantity field<br>Quantity x cost = total cost<br>Unpack total cost<br>Go to 1040 (wait)<br>Extend quantity field |

| 1050<br>1056<br>1062                                                 | 6<br>6<br>6                                         | MP<br>MP<br>UNPK                                          | 15(7,5), 4(3,4)<br>15(7,5), 7(2,4)<br>15(7,5), 9(2,4)<br>3(9,5), 15(7,5)                                                                                                                        | Quantity x unit cost<br>Apply discount<br>Unpack total cost                                                                                                                                                                                |

(SS operand form:  $D_1(L_1,B_1),D_2(L_2,B_2)$  )

# ANALYSIS OF CODING

# Instruction

Location

| 1000   | (4001-4003) transferred to 5000-5002   |    |

|--------|----------------------------------------|----|

| 1006   | (4011-4014) packed and transferred to  |    |

|        | 4015-4017                              |    |

| 1012   | (4004-4006) compared to (4015-4017)    |    |

| 1018*  | Mask of 1010 compared to Condition     |    |

|        | Code. Instruction branches if code is  |    |

|        | 0 or 2, equal or greater.              |    |

| 1022   | Four leading zeros are added to the    |    |

|        | number from 4004-4006 so that it is    |    |

|        | large enough to contain the product.   | Ex |

| 1028   | (5015-5019) multiplied by (4007-4008)  | Ex |

| 1034   | Zones inserted in number in 5015-      |    |

|        | 5019, expanding it to 5003-5009        |    |

| 1040*  | An unconditional branch to the loca-   |    |

|        | tion containing the branch instruc-    |    |

|        | tions has the effect of stopping the   |    |

|        | computer                               |    |

| 1044 - | These instructions are executed when   |    |

| 1062   | the quantity equals or exceeds 5000.   |    |

|        | Note that 90% of the total cost pro-   |    |

|        | duces a 10% discount and a result with |    |

|        | four decimal places.                   |    |

|        |                                        |    |

Example 2:

| Locations   |       | Contents   |       |

|-------------|-------|------------|-------|

| 1000-1001   | N1    | (          | 02 5- |

| 1002 - 1007 | N2 00 | 0 00 05 73 | 42 7+ |

| 1008-1010   | N3    | 24 3       | 32 6+ |

| 1011        | N4    |            | 5+    |

| 1012-1013   | N5    | 1          | 01 2+ |

| Register 2  |       |            | 5 00  |

| Register 3  |       |            | 10 00 |

| Calculate | Ð |   | N1 | (N | 2- | N3) |

|-----------|---|---|----|----|----|-----|

|           | n | _ | ]  | N4 | +  | N5  |

| *When zero  | is used for an X or B field, the field |

|-------------|----------------------------------------|

| is ignored. | Register zero is not specified.        |

| Storage<br>Location | OP | Operand            | Results                                                                                  |

|---------------------|----|--------------------|------------------------------------------------------------------------------------------|

| 0500                | SP | 2(6, 3), 8(3, 3)   | (1002-1007):00000549101+(1002-1007):00013727525-(1012-1013):017+(1002-1007):0807501-008- |

| 0506                | MP | 2(6, 3), 0(2, 3)   |                                                                                          |

| 0512                | AP | 12(2, 3), 11(1, 3) |                                                                                          |

| 0518                | DP | 2(6, 3), 12(2, 3)  |                                                                                          |

# Exercise 1

Write the instructions to propagate the byte in location 5000 through the field in location 4000-4055. Assume that register three contains 3000.

# Exercise 2

| Input data (Zoned)    | Locations              |                        |    |     | For  | mat   |             |                    |       |

|-----------------------|------------------------|------------------------|----|-----|------|-------|-------------|--------------------|-------|

| Part number           | 4000-4007              | $\mathbf{Z}\mathbf{X}$ | ZX | ZX  | zx   |       | ZX          |                    |       |

| Quantity<br>Unit cost | 4008-4011<br>4012-4015 |                        |    |     |      |       | $_{\rm ZX}$ |                    |       |

|                       |                        |                        |    | ass | sume | ed de | ecim        | al p               | oint  |

| Constants (Packed)    | Locations              |                        |    |     | For  | mat   | <u>t</u>    |                    |       |

| 95%                   | 5000-5001              |                        |    |     | 09   | 5+    |             |                    |       |

| 90%                   | 5002-5003              |                        |    |     | 09   | 0+    |             |                    |       |

| +1000                 | 5004-5006              |                        |    | 0   | 1 00 | 0+    |             |                    |       |

| +5000                 | 5008-5010              |                        |    | 0   | 5 00 | 0+    |             |                    |       |

| +100                  | 5012-5013              |                        |    |     | 10   | 0+    |             |                    |       |

| +2                    | 5014                   |                        |    |     |      | 2+    |             |                    |       |

| Register              | <u>Conte</u>           | nts                    |    |     |      |       |             |                    |       |

| 2                     | 200                    | 0                      |    |     |      |       |             |                    |       |

| 4                     | 400                    | 0                      |    |     |      |       |             |                    |       |

| 5                     | 500                    | 0                      |    |     |      |       | Thi         | s ex               | ampl  |

| 6                     | 600                    | 0                      |    |     |      |       |             |                    |       |

|                       |                        |                        |    |     |      |       | If G        | <mark>)</mark> >50 | 00, 1 |

Prepare an output item in packed form starting at location 6000 and consisting of the part number and total cost. The total cost is computed as follows: if quantity exceeds 5000, the first 1000 units receive a 10% discount, half of the remainder receives a 5% discount, and the remaining half are billed at the unit cost. (Assume that the quantity is an even number.) If the quantity does not exceed 5000, it is billed at the unit cost. Locate the assumed decimal point in both possible results. This example may be shown symbolically as:

If Q>5000, total cost =

$$1000 \times U \times 90\% + \underline{Q-1000}_{2} \times U \times 95\% + \underline{Q-1000}_{2} \times U$$

If  $Q \le 5000$ , total cost =  $Q \times U$

(Note: Keep track of the position of the assumed decimal point throughout. The factor of 100 will be required to adjust the number of decimal places in at least one partial result.)

# RCA 70/45-55 ASSEMBLY SYSTEM

This section introduces the basic features of the RCA 70/45-55 Assembly System. The use of symbols and expressions is illustrated. The method of defining storage and constants is explained, and the details of writing instructions are described.

# **EXPRESSIONS**

Expressions specify operand fields of machine and assembly instructions. They may be simple or compound as shown below:

# PROGRAM FORMAT

The elements of a program are illustrated by the following chart.

|                        | NAME                  | OPERATION                       | OPERAND                    | COMMENTS                                            |

|------------------------|-----------------------|---------------------------------|----------------------------|-----------------------------------------------------|

|                        | Symbol                | Mnemonic<br>Instruction<br>Code | Symbols,<br>Expressions    |                                                     |

| MACHINE<br>STATEMENTS  | START                 | AP<br>BC                        | ABLE(3), BAKER<br>15, *+14 | ABLE+BAKER<br>LOCATION COUNTER                      |

|                        | Symbol                | Assembly<br>Instruction         | Defining Fields            |                                                     |

| ASSEMBLY<br>STATEMENTS | ABLE<br>CONST<br>REGL | DS<br>DC<br>EQU                 | 2C24<br>2L3C'123'<br>10    | DEFINE STORAGE<br>DEFINE CONSTANT<br>EQUATE SYMBOLS |

# SYMBOLS

Symbols are prepared by the user to identify statements (names), work areas, and I/O units. Examples of valid and invalid symbols follow.

| Valid              | Invalid                                                                                                                                  |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| A<br>A12<br>ABLE2A | 1A (begins with a decimal digit)<br>A <sup>+</sup> 23 (contains a special symbol)<br>ABLEABLEABLE (too long)<br>A BLE (contains a blank) |

Symbols are either <u>absolute</u> or <u>relocatable</u>.

The EQU instruction can define a symbol and make it absolute or equate one symbol with another. Examples of absolute and relocatable symbols follow. It is assumed that all of the EQU instructions below are executed in order in the same program.

NAME | OPERATION | OPERAND

| RECI         | EQU | 1        | Abgoluto         |

|--------------|-----|----------|------------------|

| <b>REGL</b>  | ЕQU | 1 1      | Absolute         |

| REGL<br>OPND | EQU | REGL     | Both absolute    |

| BEGIN        | BC  | 2,3(4,5) | Relocatable      |

| START        | EQU | BEGIN    | Both Relocatable |

# SIMPLE EXPRESSIONS

ABLE(symbol)  $\mathbf{2}$  $\left. \begin{array}{c} 2 \\ C'B' \end{array} \right\}$  self-defining values \*(Location counter)

#### COMPOUND EXPRESSIONS

\*+23 **ABLE** +10 ABLE-BAKER + ALPHA A + B \* Y = (A + (B \* Y))

(Self-defining values may be decimal or hexadecimal numbers up to six digits in length, or a single character.)

# INVALID COMPOUND EXPRESSIONS

|           |                                     | Correct Form |

|-----------|-------------------------------------|--------------|

| ABLEX'02' | (arithmetic operator missing)       | ABLE*X'02'   |

| A + -10   | (two arithmetic operators together) | A – 10       |

| -ALPHA+10 | (begins with arithmetic operator)   | ALPHA + 10   |

| A-B+C+10  | (too many terms)                    | A - B + C    |

| **5       | (multiply follows location counter) | *+5          |

Expressions are either relocatable or absolute depending on the nature and relation of the included symbols. A relocatable expression must be positive. An absolute expression may be negative.

In the illustrations below, the symbols have the following values:

| А   | 2000 | )           |

|-----|------|-------------|

| В   | 1000 | relocatable |

| С   | 4000 | )           |

| FOX | 500  | absolute    |

# ABSOLUTE EXPRESSIONS VALUE

| A-B+10            | 1010                                     |

|-------------------|------------------------------------------|

| FOX*10            | 5000                                     |

| FOX+25<br>A-B+FOX | $\begin{array}{c} 525\\ 1500\end{array}$ |

# RELOCATABLE EXPRESSIONS

| A-FOX        | 1500                        |

|--------------|-----------------------------|

| <b>*</b> +10 | Depends on location counter |

| A+10         | 2010                        |

| A-B+C        | 5000                        |

VALUE

Note that the value of a relocatable symbol or expression depends on where the program is loaded. The maximum value of an expression is 131,071.

# INVALID EXPRESSIONS

| A*FOX<br>A+B+C       | (two relocatable symbols added)<br>(relocatable symbol multiplied)<br>(no minus)<br>(can plue) | $\frac{\text{Correct Form}}{A-B+10}$ FOX*5 $A-B+C$ $A-B+C$ |

|----------------------|------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| A – B – C<br>FOX – A | (no plus)<br>(relocatable subtracted from                                                      | FOX + A                                                    |

| B-2000               | absolute)<br>(relocatable expression cannot be<br>negative)                                    | B-FOX                                                      |

# DEFINING STORAGE

Input/Output areas and work areas are reserved by the Define Storage instruction, DS. The form of its operand is dCLn. (d is the duplication factor and n is the number of bytes in the length of storage before duplication.) In the following example, 10 bytes (characters) of storage will be reserved starting at ALPHA, ten starting at BETA, and ten at GAMMA.

| NAME  | OPERATION | OPERAND |

|-------|-----------|---------|

| ALPHA | DS        | 2CL5    |

| BETA  | DS        | CL10    |

| GAMMA | DS        | 10C     |

Note that the storage area reserved is not cleared. Ln has a maximum value of 256.

# Exercise 1

| NAME | OPERATION | OPERAND   |

|------|-----------|-----------|

| COST | DS        | 10CL2     |

| FILE | DS        | 80C       |

| WORK | DS        | 10CL10    |

| CON  | EQU       | 125       |

| MAST | EQU       | FILE-COST |

Assume that the above instructions are executed. Indicate which of the following symbols and expressions are valid, invalid, absolute, or relocatable.

MAST+CON a.

b. COST\*CON

COST-CON+FILE c.

d. MAST\*CON

WORK+CON-COST e.

# DEFINING CONSTANTS

Constants are defined by the Define Constant instruction: DC. Its form is dCLn 'characters'. The following instructions cause the constant 123bb123bb to be created (b = blank) in zoned form. 1

| NAME OPERATION OPERAN |  | OPERAND                    |

|-----------------------|--|----------------------------|

| CON1<br>CON2          |  | 2CL5'123'<br>C'123bb123bb' |

1

Note that if Ln is too small, the rightmost characters of the constant within the quotation marks are truncated. The maximum length of a character constant is 16 bytes, before the duplication factor is applied.

# ATTRIBUTES

Symbols and expressions generally have two attributes: a value and a length. The value may be a storage address, a register number, or a numerical value. The length attribute is used by the assembly system to provide L fields for SS instructions. The following illustration assumes that the coding is assembled according to the storage locations shown on the left. The attributes apply to the expressions or symbols on the same line. (See example on following page.)

Note that the length attribute of a compound expression is the implied length of its first simple expression (e.g. ABLE in ABLE+10 above). If the first simple expression is a self-defining value, the length attribute of the expression is one (10+ABLE above).

| Value | Length                                         |

|-------|------------------------------------------------|

|       |                                                |

|       |                                                |

| 1000  | 3                                              |

| 1060  | 1                                              |

| 1066  | 3                                              |

| 1072  | 10                                             |

| 2     | 1                                              |

| 1112  | 2                                              |

| 1010  | 3                                              |

| 1010  | 1                                              |

|       | 1060     1066     1072     2     1112     1010 |

# STATEMENT FIELDS

An assembly program consists of a sequence of statements. A statement is composed of four fields, each separated by at least one blank: Name field, Operation field, Operand field, and Comment field.

# NAME FIELD

The Name field is blank unless it is necessary to reference the statement, in which case a symbol is written. A comment may also begin in the Name field as illustrated on page 19.

# OPERATION FIELD

1

The Operation field contains a mnemonic machine or assembly system instruction.

| NAME        | OPERATION         |                                                                     |

|-------------|-------------------|---------------------------------------------------------------------|

| ADD<br>ABLE | START<br>AP<br>DS | assembly instruction<br>machine instruction<br>assembly instruction |

| <b>VDTF</b> | 100               | assembly matricelon                                                 |

|             |                   | ADD AP                                                              |

# OPERAND FIELD

The Operand field contains information to complete the instruction begun in the Operation field.

# MACHINE INSTRUCTION OPERANDS

| Instruction            | Explicit                                 |                      |

|------------------------|------------------------------------------|----------------------|

| Type                   | Form                                     | Examples             |

| RR                     | R <sub>1</sub> , R <sub>2</sub>          | 2, REG3              |

| $\mathbf{R}\mathbf{X}$ | $R_1, D_2(X_2, B_2)$                     | TEN, 25(2, 3)        |

| RS                     |                                          | 1, 2, 125(3)         |

| SI                     | ${f R_1, R_3, D_2(B_2) \ D_1(B_1), I_2}$ | 40(9) <b>,</b> C'\$' |

| SS                     | $D_1(L_1, B_1), D_2(L_2, B_2)$           | 10(3,1),5(4,2)       |

|                        | Implied                                  | Implied              |

| Instruction            | Base Register                            | Base Register        |

| Туре                   | Form                                     | Examples             |

| RX                     | $R_{1}, S_{2}(X_{2})$                    | REG2, ABLE(3)        |

| RS                     | $R_{1}, R_{3}, S_{2}$                    | 3, 4, ABLE           |

| SI                     | $1 S_{1}, I_{2}$                         | ABLE, C'B'           |

| SS                     | $S_1(L_1), S_2(L_2)$                     | ABLE(5), BAKER       |

Note that storage fields  $(S_1, S_2)$  are relocatable expressions. All other fields must be absolute. The Assembly System determines the B and D fields for ABLE, and the  $B_1, D_1$ , and <u>L</u> fields for BAKER. BAKER must have a suitable length attribute, which would have been assigned by a Define Storage instruction, for example; note also that the Assembly L is one byte longer than the machine L. (The Chart on the following page shows all possible combinations for operand fields.)

In order to write machine instructions with implied base registers, a procedure utilizing the USING assembly instruction must be employed. The method will be explained in a later section. The programmer must keep in mind that general purpose registers must be loaded with addresses bracketing the entire area of memory required. For example, assume that the programmer loaded registers 2 and 3 with the addresses 1000 and 5096 (1000 + 4096), respectively. The assembly system will treat the following instruction operands on the left, as if they were written as shown on the right.

| Storage<br>Location | NAME  | OPERATION | OPERAND        | Converted<br>Operand |

|---------------------|-------|-----------|----------------|----------------------|

| 1046                | BEGIN | AP        | ABLE(5), BAKER | 904(5,3),1304(5,3)   |

| •                   |       | •         |                |                      |

| •                   |       | •         |                |                      |

| •                   |       | •         |                |                      |

| •                   |       | •         |                |                      |

| 2000                |       | BC        | 15, BEGIN      | 15,46(0,2)           |

| •                   |       | •         |                |                      |

| •                   |       | •         |                |                      |

|                     |       | •         |                |                      |

| 6000                | ABLE  | DS        | 100CIA         |                      |

| 6400                | BAKER | DS        | 14CL5          |                      |

.

|                                                                                                                                                 | ASSEMBLER                                         | OPERAND FIELD CHARACTERISTICS                      |                                                                                                          |                             |                            |                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|----------------------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------------|----------------------------|---------------------------------------|

| OPERAN<br>FIELD<br>MACHINE FORMAT FORMA                                                                                                         |                                                   | FIE LD                                             | BIT<br>SIZE                                                                                              | SIMPLE<br>COM-<br>POUND     | ABS.<br>REL.               | MAX.<br>VALUE                         |

| $RR \qquad \begin{array}{c c} 8 & 4 & 4 \\ \hline O & P & R_1 & R_2 \\ \hline \hline & 8 & 4 & 4 \\ \hline & O & P & R_1 \\ \hline \end{array}$ | R <sub>1</sub> , R <sub>2</sub><br>R <sub>1</sub> |                                                    | $     \begin{array}{c}       4 \\       12 \\       4 \\       4 \\       4 \\       8     \end{array} $ | S<br>SC<br>S<br>S<br>S<br>S | A<br>A<br>A<br>A<br>A<br>A | $15 \\ 4095 \\ 15 \\ 15 \\ 16 \\ 256$ |

| 8 8<br>O P I                                                                                                                                    | I                                                 | I,I <sub>2</sub><br>S <sub>1</sub> ,S <sub>2</sub> | 8<br>16                                                                                                  | s<br>sc                     | A<br>R                     | 255                                   |

# MACHINE FORMAT

# OPERAND FORMAT

|    |                                                                              | EXPLICIT<br>BASE,<br>EXPLICIT<br>LENGTH                            | EXPLICIT<br>BASE,<br>IMPLIED<br>LENGTH                                   | IMPLIED<br>BASE,<br>EXPLICIT<br>LENGTH                                                | IMPLIED<br>BASE,<br>IMPLIED<br>LENGTH   |

|----|------------------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-----------------------------------------|

| RX | $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                      | $R_1, D_2(X_2, B_2)$                                               |                                                                          | $R_1, S_2(X_2)$<br>$R_1, S_2$ (no indexing)<br>$R_1, D_2$ (no X or B)                 |                                         |

| RS |                                                                              | R <sub>1</sub> , R <sub>3</sub> , D <sub>2</sub> (B <sub>2</sub> ) |                                                                          | $R_1, R_3, S_2$                                                                       |                                         |

|    | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                       | $R_1, D_2(B_2)$                                                    |                                                                          | R <sub>1</sub> ,S <sub>2</sub>                                                        |                                         |

| SI | $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                      | $D_1(B_1), I_2$                                                    |                                                                          | s <sub>1</sub> , I <sub>2</sub>                                                       |                                         |

|    | 8         8         4         12           O         P         B1         D1 | D <sub>1</sub> (B <sub>1</sub> )                                   |                                                                          | s <sub>1</sub>                                                                        |                                         |

| SS | $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                      | $D_1(L_1, B_1), D_2(L_2, B_2)$                                     | D <sub>1</sub> (, B <sub>1</sub> )<br>D <sub>2</sub> (, B <sub>2</sub> ) | $\begin{array}{c} \mathrm{S}_1(\mathrm{L}_1)\\ \mathrm{S}_2(\mathrm{L}_2)\end{array}$ | $egin{array}{c} s_1 \\ s_2 \end{array}$ |

|    | $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                      | $D_1(L, B_1)$<br>$D_2(B_2)$                                        | D <sub>1</sub> (, B <sub>1</sub> )                                       | S <sub>1</sub> (L)<br>S <sub>2</sub>                                                  | s <sub>1</sub>                          |

Note that if indexing is not to occur for an RX instruction, zero must be written for the X field if a B field exists. If the field or fields within parentheses are zero, the parentheses and the included field or fields may be omitted. Whenever zero is specified for an Z or B field, the field is ignored.

# Illustrations

| BC                   | 15, START  | No indexing, implied B   |

|----------------------|------------|--------------------------|

| $\operatorname{SLL}$ | 2,15       | B omitted (a shift left) |

| BC                   | 15,25(0,3) | No indexing, B required  |

# Exercise 2

An 80-column card is to be read into storage. It is composed of the following fields:

| Field | Name | Columns |

|-------|------|---------|

| 1     | ID   | 1-10    |

| 2     | COST | 11-20   |

| 3     | QTY  | 21 - 25 |

| 4     | LEAD | 26 - 30 |

| 5     | UNKN | 31-80   |

Define each field, and an 80-byte area called WORK. Write the instructions to transfer all 80 characters to WORK. Multiply COST times QTY a) from the original storage area and b) from their locations in WORK. (Assumes that COST has a sufficient number of leading zeros.)

# Exercise 3

What are the length attributes of the DS symbols and valid expressions in Exercise 1?

#### Comments

The two forms of comments are shown below.

| NAME | OPERA<br>TION | OPERAND                                       | COMMENTS |

|------|---------------|-----------------------------------------------|----------|

|      |               | EQUIRES AN ASTERISK<br>2,A12 THIS FOLLOWS THE | OPERAND  |

# Example

Example 1 of page 12 could be coded as shown below. The test factor, 5000, has been defined by a DC instruction. The following facts are significant and should be noted.

# MVC

OUTPUT has a length attribute of 1. Thus the length of the field moved (3) must be written. If OUTPUT were defined as 4CL3, the length of field could be omitted.

| NAME   | OPERA-<br>TION | OPERAND                  | COMMENTS                        |

|--------|----------------|--------------------------|---------------------------------|

| PART   | DS             | CL3                      |                                 |

| QTY    | DS             | CL3                      |                                 |

| COST   | DS             | CL2                      |                                 |

| FACTOR | DS             | CL2                      |                                 |

| CONST  | DC             | C'5000'                  |                                 |

| OUTPUT | DS             | 120                      |                                 |

| BEGIN  | MVC            | OUTPUT(3), PART          | PART-→OUTPUT                    |

|        | PACK           | CONST, CONST             | Z5Z0Z0S0→0005000·               |

|        | CP             | QTY, CONST               | COMPARE QTY: 5000               |

|        | BC             | 10, DISCNT               | GO TO DISCNT IF $\geq$          |

|        | ZAP            | OUTPUT+3(4),QTY          | EXTEND QTY WITH O               |

|        | MP             | OUTPUT+3(4),COST         | $QTYxCOST \rightarrow OUTPUT +$ |

|        | UNPK           | OUTPUT+3(7), OUTPUT+3(4) | UNPACK RESULT                   |

|        | BC             | 15,*                     | WAIT                            |

| DISCNT | ZAP            | OUTPUT+3(5),QTY          | EXTEND QTY WITH O               |

|        | MP             | OUTPUT+3(5),COST         | QTYxCOST-→OUTPUT+               |

|        | MP             | OUTPUT+3(5), FACTOR      | OUTPUT+3 xFACTOR                |

|        | UNPK           | OUTPUT+3(9), OUTPUT+3(5) | UNPACK RESULT                   |

|        | BC             | 15,*                     |                                 |

# PACK, CP

The length attributes of the operands are adequate: the L fields can be omitted.

# $\mathbf{ZAP}$

OUTPUT + 3 is a relative address: of the first byte following the output part number. Because it is used often, it could be defined as OUT, for example, as follows:

| NAME | OP  | OPERAND  |

|------|-----|----------|

| OUT  | EQU | OUTPUT+3 |

The instruction operand would then be OUT(4), QTY.

Note that the symbols in the expression equated must all have been previously defined.

#### BC

\*, the location counter is the address of the BC instruction.

# Exercise 4

Data in the format shown, is read into the defined storage areas. Z's represent zones, X's represent decimal digits, S represents a sign, and the carat ( $\land$ ) represents an assumed decimal point. Write the instructions to perform the specified operations. If overflow can occur during an operation, provide a branch to OVERFL.

| a. | ABLE plus | BAKI          | ER less | FOX                    | (res                   | sult i                 | n AE                   | BLE)                   |                        |                    |

|----|-----------|---------------|---------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|--------------------|

|    | ABLE      | $\mathbf{DS}$ | CL7     | ZO                     | $\mathbf{ZO}$          | $\mathbf{Z}\mathbf{X}$ | $\mathbf{Z}\mathbf{X}$ | $\mathbf{Z}\mathbf{X}$ | $\mathbf{Z}\mathbf{X}$ | SX                 |

|    | BAKER     | $\mathbf{DS}$ | CIA     | OX                     | XX                     | XX                     | $\mathbf{XS}$          |                        |                        |                    |

|    | FOX       | DS            | CL4     | 00                     | ox                     | XX                     | XS                     |                        |                        |                    |

|    |           |               |         |                        |                        |                        |                        |                        |                        |                    |

| b. | ABLE less | BAKI          | ER plus | FOX                    | (res                   | sult i                 | n FC                   | DX)                    |                        |                    |

|    | ABLE      | DS            | CL5     | $\mathbf{Z}\mathbf{X}$ | zx                     | $\mathbf{Z}\mathbf{X}$ | $\mathbf{Z}\mathbf{X}$ | sx                     |                        |                    |

|    | BAKER     | $\mathbf{DS}$ | CL5     | ZO                     | $\mathbf{Z}\mathbf{X}$ | $\mathbf{Z}\mathbf{X}$ | ΖX                     | $\mathbf{SX}$          |                        |                    |

|    | FOX       | DS            |         |                        | XX                     | XS                     |                        |                        |                        |                    |

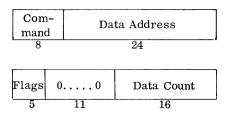

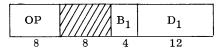

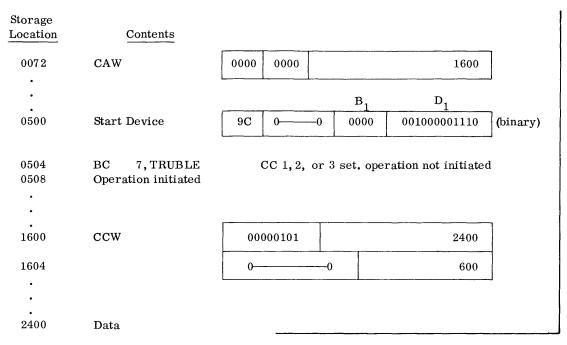

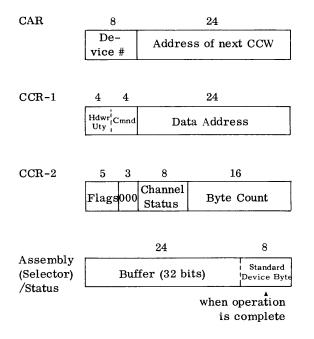

|    |           |               |         |                        |                        |                        |                        |                        |                        |                    |