SYSTEMS INFORMATION MANUAL

#### PORATION OF AMERICA RA OR

70-00-601

The information contained herein is subject to change without notice. Revisions may be issued to advise of such changes and/or additions. First Printing: December, 1964

# CONTENTS

# Page

| SYSTEMS DESCRIPTION 1                                                                                    | -        |

|----------------------------------------------------------------------------------------------------------|----------|

| Introduction 1                                                                                           |          |

| Systems Structure 1                                                                                      | -        |

| RCA Model 70/15 Processor 1                                                                              |          |

| RCA Model 70/25 Processor1RCA Model 70/45 Processor1RCA Model 70/55 Processor2RCA Model 70/55 Processor2 |          |

| RCA Model 70/45 Processor 1                                                                              |          |

| RCA Model 70/55 Processor 2                                                                              | 2        |

| Input-Output Devices                                                                                     | 2        |

| Systems Characteristics 2                                                                                | 2        |

| Design Philosophy 2                                                                                      |          |

| Expandability 3                                                                                          | \$       |

| Compatibility 3                                                                                          | 5        |

| Programming Systems 3                                                                                    |          |

| Code Structure                                                                                           |          |

| Machine Addressing 3                                                                                     |          |

| Instruction Format                                                                                       |          |

| Arithmetic Operations 4                                                                                  |          |

| Interrupt                                                                                                |          |

| Processor States                                                                                         | -        |

| Input-Output Channels 4                                                                                  | •        |

| Communications                                                                                           | -        |

| Memory Protect                                                                                           |          |

| Direct Control                                                                                           |          |

| Elapsed Time Clock                                                                                       |          |

|                                                                                                          |          |

| Multisystem Operation 7                                                                                  |          |

| EQUIPMENT DESCRIPTION                                                                                    | )        |

| RCA Model 70/15 Processor 9                                                                              |          |

| General                                                                                                  |          |

| High-Speed Memory                                                                                        |          |

| Program Control                                                                                          |          |

| Input-Output Control                                                                                     |          |

| Instruction Formats and Timing 10                                                                        |          |

| RCA Model 70/25 Processor 11                                                                             |          |

|                                                                                                          |          |

|                                                                                                          | -        |

|                                                                                                          |          |

| Program Control                                                                                          | -        |

| Input-Output Control12Instruction Formats and Timing12                                                   |          |

| Instruction Formats and Timing 12                                                                        |          |

| RCA Model 70/45 Processor 13                                                                             |          |

| General 13                                                                                               |          |

| Main Memory 13                                                                                           |          |

| Scratch-Pad Memory 13                                                                                    |          |

| Read Only Control Memory 13                                                                              |          |

| Non-Addressable Memory 13                                                                                | ,        |

| Program Control 14                                                                                       | :        |

| Input-Output Control 15                                                                                  | ,        |

| Instruction Formats and Timing 16                                                                        | <b>,</b> |

| RCA Model 70/55 Processor                                                                                |          |

| General                                                                                                  |          |

| Main Memory                                                                                              |          |

|                                                                                                          |          |

| Scratch-Pad Memory 21                                                                                    |          |

| Pa                                       | ıge             |

|------------------------------------------|-----------------|

| Non-Addressable Memory                   | 21              |

| Program Control                          | 21              |

| Input-Output Control                     | $\overline{23}$ |

| Instruction Formats and Timing           | 23              |

| Input-Output Devices                     | 27              |

| Model 70/97 Console and Typewriter       | 27              |

| Model 70/214 Interrogating Typewriter    | <b>27</b>       |

| Model 70/216 Interrogating Typewriter    | <b>27</b>       |

| Model 70/221 Paper Tape Reader/Punch.    | <b>27</b>       |

| Model 70/234 Card Punch                  | 29              |

| Model 70/236 Card Punch                  | 29              |

| Model 70/237 Card Reader                 | 29              |

| Model 70/242 Printer, Medium-Speed       | 31              |

| Model 70/243 Printer, Hi-Speed           | <b>31</b>       |

| Model 70/249 Bill Feed Printer           | 31              |

| Model 70/251 Videoscan Document Reader   | 33              |

| Model 70/432 Magnetic Tape Unit          | 33              |

| Model 70/442 Magnetic Tape Unit          | 34              |

| Model 70/445 Magnetic Tape Station       | 34              |

| Model 70/472-108, -116 Tape Controller   |                 |

| (Single Channel)                         | 35              |

| Model 70/472-208, -216 Tape Controller   |                 |

| (Dual Channel)                           | 35              |

| Model 70/551 Random Access Controller .  | 35              |

| Model 70/564 Disc Storage Unit           | 36              |

| Model 70/565 Drum Memory Unit            | 36              |

| Model 70/568 Mass Storage Unit           | 36              |

| Model 70/627 Data Exchange Control       | 38              |

| Model 70/652 Communication Control       | 38              |

| Model 70/653 Communication Control       | 38              |

| Model 70/664 Communication Buffer        |                 |

| Control                                  | 39              |

| Model 70/672 Communication Multiplexor   | ~ ~             |

| Channel                                  | 39              |

| Model 70/710 Telegraph Buffer            | 40              |

| Model 70/720 Communication Buffer        | 40              |

| Model 70/721 Communication Buffer        | 40              |

| Model 70/722 Communication Buffer        | 41              |

| Model 70/723 Autodin Buffer              | 41              |

| Model 6050 Video Data Terminal           | 41              |

| Model 6051 Video Data Interrogator       | 41              |

| Model 6077 Interrogator Control Terminal | 42              |

| PROGRAMMING SYSTEMS DESCRIPTION          | 43              |

| RCA 70/15 Programming Systems            | 43              |

| System Concept                           | 43              |

| Assembly System                          | 43              |

| Loader Routines                          | $\overline{44}$ |

| Input-Output Control                     | $\overline{44}$ |

| Test Routines                            | 44              |

| Utility Routines                         | 45              |

| Communication Control System             | 45              |

| System Library Maintenance Routines      | 45              |

|                                          | -               |

# CONTENTS (Cont.)

# Page

| Report Program Generator            | 45        |

|-------------------------------------|-----------|

| Sort/Merge                          | 45        |

| RCA 70/25 Programming Systems       | <b>46</b> |

| System Concept                      | 46        |

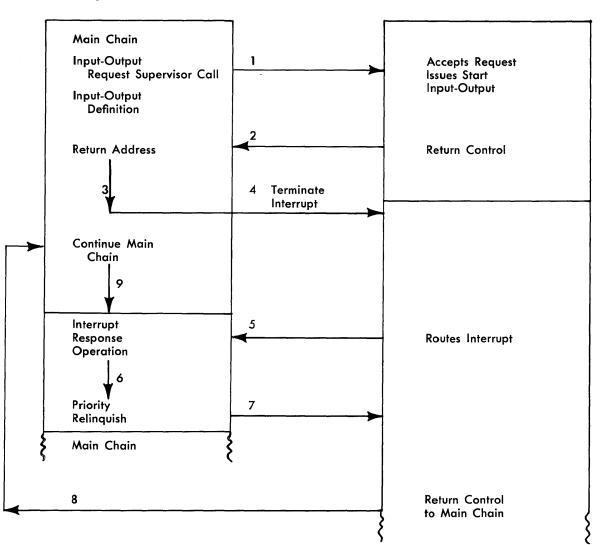

| Tape Operating System 16            | <b>47</b> |

| The Executive                       | 48        |

| The Monitor                         | 48        |

| Assembly System                     | 48        |

| File Control Processor              | 48        |

| Report Program Generator            | <b>49</b> |

| Sort/Merge                          | 49        |

| Peripheral Control System           | 50        |

| Communication Control System        | 50        |

| System Library Maintenance Routines | 50        |

| Tape Operating System 32            | 51        |

| The Executive                       | 51        |

| The Role of the Executive           | 51        |

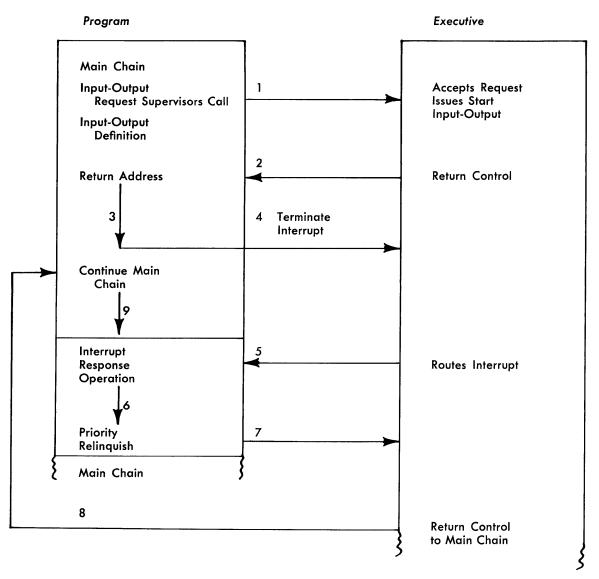

| RCA 70/45-55 Programming Systems    | 54        |

| System Concept                      | 54        |

| Tape Operating System 16            | 56        |

| The Executive                       | 56        |

| The Monitor                         | 56        |

| Basic Assembly System               | 56        |

| File Control Processor              | 56        |

| Report Program Generator            | 57        |

|                                     | •••       |

| COBOL                               | 57        |

| FORTRAN                             | 57        |

| Sort/Merge                          | 58        |

| Peripheral Control System           | 58        |

| Communication Control System        | 58        |

| System Library Maintenance Routines | 59         |

|-------------------------------------|------------|

| Compatibility Support System        | 59         |

| Tape Operating System 32            | 59         |

| The Executive                       | <b>6</b> 0 |

| Extended Assembly System            | <b>6</b> 0 |

| File Control Processor              | <b>6</b> 0 |

| Random Access File Maintenance      |            |

| Routines                            | <b>6</b> 0 |

| Tape Operating System 65            | <b>6</b> 0 |

| COBOL                               | 61         |

| FORTRAN                             | 61         |

| Disc Operating System 65            | 61         |

| Communication Control System        | 61         |

| System Library Maintenance Routines | 62         |

| Disc Operating System 262           | 62         |

| The Role of the Executive           | 62         |

| DDENDIGEG                           |            |

#### APPENDICES

| A. | Input-Output Timing Summary   | 66         |

|----|-------------------------------|------------|

| В. | Extended Binary-Coded-Decimal |            |

|    | Interchange Code (EBCDIC)     | <b>6</b> 8 |

| С. | American Standard Code for    |            |

|    | Information Interchange       | 69         |

| D. | Optical Character Code        | <b>70</b>  |

| Ε. | Paper Tape Codes              | 71         |

| F. | Console Typewriter Code       | 72         |

| G. | Character Code Table          | <b>7</b> 3 |

| Η. | Hexadecimal Table             | 78         |

| I. | Powers of Two Table           | 79         |

| J. | Hexadecimal-Decimal Number    |            |

|    | Conversion Table              | 80         |

# LIST OF ILLUSTRATIONS

Page

#### Figure No.

1.

2.

3.

4.

5.

6.

7.

Title

Model 70/221 Paper Tape

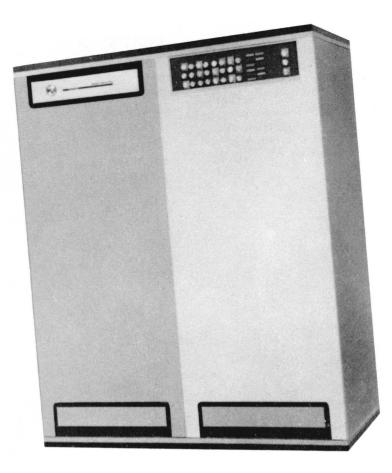

RCA 70/15 System

8

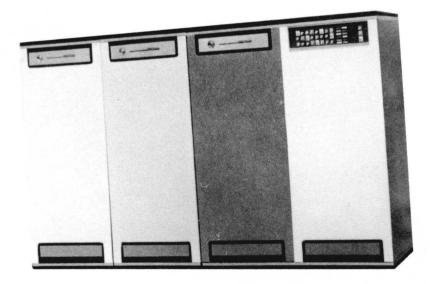

RCA 70/25 System

8

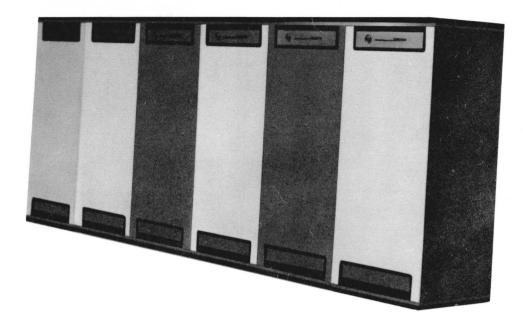

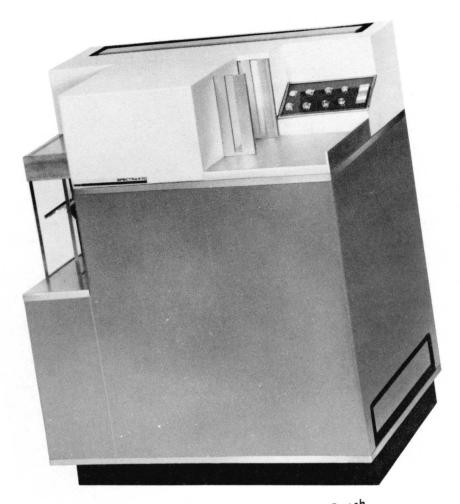

RCA 70/45 System

20

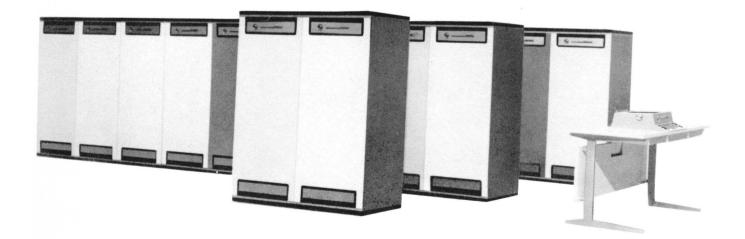

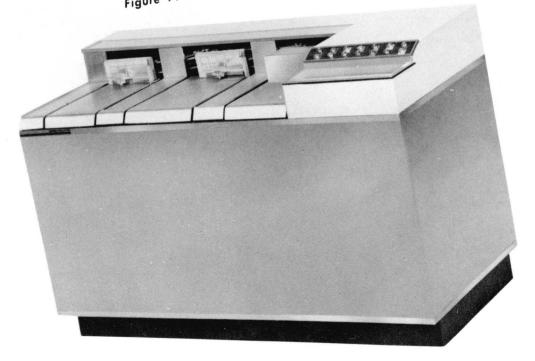

RCA 70/55 System ..... 20

Model 70/97 Console and Typewriter 28

Model 70/236 Card Punch ..... 30

Reader/Punch ..... 28

Figure No.

#### Page

8. Model 70/237 Card Reader ..... 30

Title

- 9. Model 70/243 Printer ..... 32

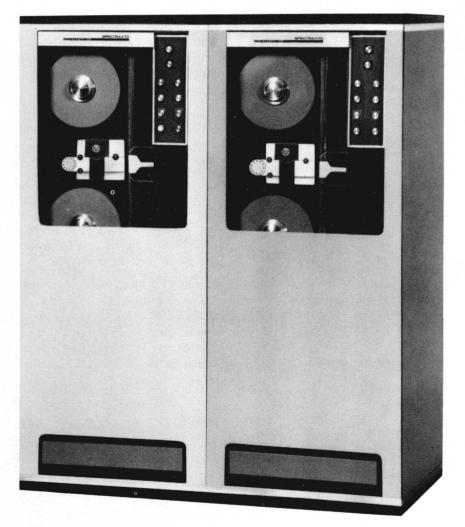

- 10. Model 70/432 Magnetic Tape Unit . . 32

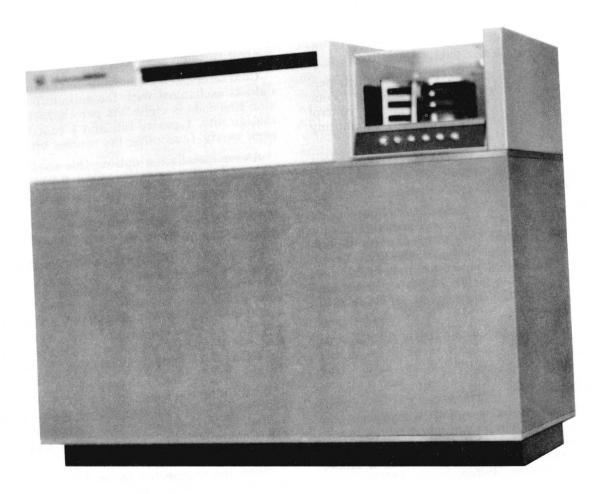

- 11. Model 70/568 Mass Storage Unit ... 37

- 12. Control Flow During an

- Input-Output Operation (70/25) .. 53 13. Control Flow During an Input-Output Operation (70/45-55) 64

# LIST OF TABLES

| Table |       |                           |      | Table |       |                           |      |

|-------|-------|---------------------------|------|-------|-------|---------------------------|------|

| No.   |       | Title                     | Page | No.   |       | Title                     | Page |

| 1.    | 70/15 | Instruction Formats       | . 10 | 7.    | 70/45 | Instruction Formats       | . 16 |

| 2.    | 70/15 | Instruction Timing        | . 10 | 8.    | 70/45 | Instruction Timing        | . 17 |

| 3.    | 70/25 | Instruction Formats       | . 12 | 9.    | 70/55 | Processor State Registers | . 22 |

| 4.    | 70/25 | Instruction Timing        | . 12 | 10.   | 70/55 | Interrupt Conditions      | . 22 |

| 5.    | 70/45 | Processor State Registers | . 14 | 11.   | 70/55 | Instruction Formats       | . 24 |

| 6.    | 70/45 | Interrupt Conditions      | . 14 | 12.   | 70/55 | Instruction Timing        | . 24 |

|       |       |                           |      |       |       | _                         |      |

≤.

# SYSTEMS DESCRIPTION

#### INTRODUCTION

The RCA Spectra 70 Series provides an openended family of compatible data processing systems. Spectra 70 with its wide range of system configurations and all-purpose design meets the requirements of the user in all areas of commercial, scientific, multisystem, control, and communications applications. Through the use of the RCA Standard Interface (standard input-output packaging), new devices for general or special applications can be added without undergoing major redesign costs. In addition, the RCA Standard Interface permits the extension of possible system configurations at an extremely favorable, cost-performance basis.

The RCA Spectra 70 Series is a multilingual system capable of accepting and processing a wide variety of industry accepted codes and programming languages. The high-order models feature micromagnetic memories for nanosecond processing power and extensive instruction complements. Internal circuitry consists of the latest developments in the state of the art. As an example, two models use full third-generation circuitry featuring monolithic integrated circuits that produce the best combination of reliability and physical size yet achieved by the industry. Design has been left open-ended to permit the addition of subsequent advanced concepts as they become available.

#### SYSTEMS STRUCTURE

The RCA Spectra 70 Series consists of a line of extremely fast and powerful processors with the capability to process a variety of diverse applications. An unexcelled throughput rate is ensured by offering a complete range of inputoutput devices that can be applied throughout the series.

Presently there are four processors offered within the Spectra 70 Series; Models 70/15, 70/25, 70/45, and 70/55. The common code structure is based on the Extended Binary Coded Decimal Interchange Code (EBCDIC) of eight bits plus parity. The standard memory unit is termed a byte. Memory access ranges from two microseconds down to 0.84 microsecond. Transfer at these access speeds varies from one to four bytes, depending upon the model processor used.

Memory storage capability starts at 4,096 bytes and extends to 524,288 bytes. The user is provided with extensive memory overlap between models; thus, system growth can be directed towards increased memory requirements and/or increased processing power. In the area of system throughput, simultaneous input-output processing is provided by the use of input-output channels. A selector channel is capable of addressing up to 256 devices, one at a time. The number of selector channels depends upon the processor. In addition, a multiplexor channel capable of simultaneously addressing up to 256 input-output devices is available on Models 70/25, 70/45 and 70/55 Processors. The multiplexor provides simultaneous operation of devices by timesharing the channel.

#### RCA Model 70/15 Processor

The RCA Model 70/15 is a small-scale processor that allows the user to handle varied applications. It can stand alone as a data processor, function as satellite support for larger systems, or operate as a remote communication terminal.

Memory is available in either 4,096 bytes or 8,192 bytes. Memory-cycle time is two microseconds to access one byte of information.

#### RCA Model 70/25 Processor

The RCA Model 70/25 is a small-to-medium size processor that accommodates a wide-range of applications. It may be used as a free standing data processor or as a subsystem of a multisystem complex.

High-throughput rate is facilitated by fast memory cycle time and a high degree of inputoutput simultaneity. The 70/25, equipped with selector channels and a multiplexor channel, concurrently operates up to eight slow-speed devices in addition to eight high-speed devices.

Memory storage is expandable from 16,384 bytes to 32,768 bytes or 65,536 bytes. Memorycycle time is 1.5 microseconds to access four bytes information.

#### RCA Model 70/45 Processor

The Model 70/45 is a medium-scale processor with a high performance capability for business, scientific, communications, and real-time applications. A complete and powerful instruction complement with floating-point operation as an option is available to the 70/45 user.

The 70/45, equipped with a communication multiplexor, addresses up to 256 communications lines in addition to a full range of peripherals. Thus, the 70/45 is an ideal system central for a multisystem operation and/or a powerful communication switching system up to 259-way simultaneity is possible.

Memory storage is expandable from 16,384 bytes to 32,768 bytes to 65,536 bytes to 131,072 bytes to 262,144 bytes. Memory-cycle time is 1.44 microseconds to access two bytes of information.

#### RCA Model 70/55 Processor

The RCA Model 70/55 is a medium-to-large scale processor with excellent performance characteristics. Though capable of the most demanding scientific applications, the 70/55 maintains a high-throughput capability with up to 14-way simultaneity, thereby offering a total solution to all data-processing requirements.

Memory storage is expandable from 65,536 bytes to 131,072 bytes to 262,144 bytes to 524,288 bytes. Memory-cycle time is 0.84 microsecond to access four bytes of information.

#### **Input-Output Devices**

Input-output devices in the Spectra 70 Series are systems-oriented towards the processing task to be performed:

- Card punches are fully buffered and punch at either 100 or 300 cards per minute.

- Three models of printers are offered. A medium-speed printer prints up to a rate of 600 lines per minute, and a high-speed printer prints up to a rate of 1,250 lines per minute, both printers contain a 132 print-position carriage. A bill-feed printer is also available which prints at a speed of 600 lines per minute on continuous forms and a print rate of 800 cards per minute on card documents. A read-compare feature is optional. To ensure maximum system capability, all printers are fully buffered.

- Card reading up to 1,435 cards per minute is performed photoelectrically. Optional mark reading is available.

- Paper-tape capability of 5, 6, 7 or 8-channel operation is offered at a reading rate of 200 characters per second and a punching rate of up to 100 characters per second.

- Three versions of magnetic tape units are available. Tape speeds are 30, 60, or 120 kilobytes per second. In a numeric mode, tape reading and writing are performed up to 240,000 digits per second. All units are industry-compatible and contain extensive accuracy control features. Either 7 or 9channel tape code can be read in either the forward or reverse direction.

- Within the Spectra 70 Series, a complete complement of auxiliary storage devices capa-

ble of use on either a random or serial basis is available including:

- a. High-speed drum with an average access time of 8.6 milliseconds and a capacity of up to one-million bytes.

- b. Interchangeable disc-storage units storing up to 7.25 million bytes with a transfer rate of 156 kilobytes per second.

- c. Mass storage units capable of accessing multi-billion bytes of information in the millisecond range.

- The growing importance of optional-character reading is recognized in the Spectra 70 Series by the inclusion of the Videoscan Document Reader capable of reading up to 1,300 documents per minute on demand. An optional feature allows the Videoscan to function as a slow-speed card reader.

- In addition, a wide range of special-purpose, input-output devices is offered to the Spectra 70 user.

## SYSTEMS CHARACTERISTICS

#### **Design Philosophy**

The prime design criteria of the Spectra 70 Series was to engineer a group of data processing systems utilizing the latest RCA technological developments. This concept produced an advanced series of computing systems which can be effectively and efficiently used to solve present and future problems. The inclusion of highly advanced circuitry in the Spectra 70 Series provides speed, accuracy, and reliability at lower cost.

The use of monolithic integrated circuits in the RCA Models 70/45 and 70/55 safeguards system longevity by producing a series of data processors with the highest order of compactness and reliability. Circuits are produced by advanced photographic and thin-film techniques and are hermetically sealed to ensure optimum efficiency in their operating environment. Circuits that formerly required a full board for construction are now placed on a 4-millimeter square. Coupled with reliability, this compactness illustrates the significance of the monolithic integrated circuit.

The internal speed of the processors in the series is another achievement in the overall advanced-system design. The ability to combine internal processing speeds and potential data throughput rates with the various peripheral devices allows for the creation of a systems series which provides an ideal balance between processing capacity and cost. Scratch-pad memories in the higher range models operating at billionths of a second speed provide intermediate storage for registers and interrupt control.

The accuracy and reliability of data are maintained through the system by continued parity checking. Each memory access embodies a parity check to assure accuracy. If an error occurs, the processor interrupts processing until parity is restored.

#### **Expandability**

The RCA Spectra 70 Series provides memory expansion and peripheral expansion in both throughput capabilities and in the number of input-output devices. Fourteen separate processors are offered within the series, ranging from a 4,096byte memory and expanding to a 524,288-byte memory. This model array allows the user up to a threefold-horizontal increase in processing power within a given memory size, and a vertical increase in memory size within an individual processor model.

Input-output simultaneity is a function of the selector and multiplexor channels in a system. The user can adjust the throughput capability of a Spectra 70 system by the addition of extra channels. Depending upon the series model, up to eight selector channels and one multiplexor channel can be added.

A variety of input-output devices varying in speed and capacity allows for peripheral expansion. This is accomplished by the use of the RCA Standard Interface which permits interchangeability of peripherals between processors without a penalty of increased control costs or abridgement of the device-rated speed.

## Compatibility

The Spectra 70 Series features program compatibility between individual models. Equipment compatibility may be upward as in the 70/15 to 70/25, 70/25 to 70/45 and 70/55, or upward and downward as in the 70/45 and 70/55. Program compatibility requires that the ensuing model have at least the configuration of its predecessor, and that timings, both internal and external, are not adversely effected.

Spectra 70 program compatibility offers the user the advantages of systems back-up, ease in system growth, and reduction in the personnel training between series models.

#### **Programming Systems**

Advanced-programming systems including input-output control systems, operating systems, generative systems, multiprocessing, COBOL, and FORTRAN IV are offered within the Spectra 70 Series.

The level of programming-system support is classified primarily by available memory in addition to the input-output orientation of the particular series model. Provisions are made for the user to elect either a completely programmed operating environment or one where the system is under operator supervision or a combination of both.

#### Code Structure

The Spectra 70 Series coding structure is based on the widely used Extended Binary Coded Decimal Interchange Code (EBCDIC). The series also offers the facilities for generating and using the American Standard Code for Information Interchange (ASCII).

To facilitate efficient manipulation of alphanumeric data, an 8-bit byte is used to represent each character. This allows the Spectra 70 Series to accept most present or future character codes. An 8-bit byte may represent one alphanumeric character, two decimal digits or eight binary digits (bits).

Fixed-length data of 16, 32, or 64 bits may be processed. Variable-length data of up to 256 characters in eight bit bytes may be processed. For purposes of data description the terms character, halfword, word, and double word are used. These are defined as one, two, four, and eight bytes respectively.

#### Machine Addressing

The Spectra 70 Series uses a two-part system of memory addressing consisting of a base address and a displacement address. A standard 12-bit instruction enables the programmer to address up to 4,096 bytes. This part is termed the displacement. A base address, stored in a General Register, consists of a maximum 32 bits and addresses memory beyond the capacity of the displacement address. Thus, the base address, in effect, subdivides memory into 4,096 bytes in that the displacement addresses the individual byte within the 4,096-byte module. The memory capacity of the Model 70/15 Processor obviates the need for a base address in that the displacement has the necessary addressing range by the addition of a high-order bit to permit addressing of up to 8.192 bytes.

#### Instruction Format

The Spectra 70 Series uses a variable-instruction format consisting of 2, 4, or 6-byte instructions. Each instruction contains an operation halfword (two bytes), and one or two register and/or memory addresses as required. Each address may be indexed by any of the General-Purpose registers in combination with the Base Address register.

The smaller processors contain instruction complements which are functional subsets of the larger 70/45 and 70/55 instruction complements. Floating-point operation is standard on the 70/55 and optional on the 70/45. Direct-control and memory-protect are optional features on both the 70/45 and 70/55. There are provisions for expanding the instruction complement to 256 order codes.

#### **Arithmetic Operations**

Complete flexibility in handling arithmetic operations is offered in the Spectra 70 Series. Decimal and binary operations are available throughout the series model. Floating-point operations are available on the 70/45 and 70/55 Processors.

Decimal operations are performed on variable or fixed-signed fields in packed format (two digits per byte). The maximum field size permitted is 31 digits plus sign and the operation is performed storage to storage.

Binary or fixed-point arithmetic operations uses either storage or registers for computation depending on the series model. In the 70/15 and 70/25, a 127-bit field plus sign is permissible. In the 70/45 and 70/55 the limit is a 31-bit field (plus sign) and arithmetic is performed in the registers (registers may be coupled to preserve precision).

Where floating-point arithmetic operations are provided, four additional double-length registers are provided for computation and storage of results. Both short and long precision, four and eight bytes respectively, are provided for either a speed or precision option. Limits of floating-point values are 2.4 x  $10^{-78}$  to approximately 7.2 x  $10^{75}$ .

#### Interrupt

The Spectra 70 Series includes a comprehensive set of system interrupts. These interrupts allow the particular series model to respond to various internal and external conditions affecting systems operation. Processing at the time of the interrupt may be terminated, suppressed, or completed, depending on the cause of the interrupt. Processor interrupts, in general, may be controlled by the program through the use of interrupt masks. Interrupts are divided into the following classifications:

- Program Interrupts program errors such as overflows and illegal operation codes.

- *External Interrupts* servicing remote and operator-controlled devices, such as console intervention and requests from display or analog devices.

- Supervisor Call Interrupts interrupts caused by the user's program to request various functions in the operating system.

- Input-Output Interrupts input-output servicing of devices, such as terminations, transfer errors, and inoperable conditions.

- Machine Interrupts equipment malfunctions such as parity error or power shut-down.

If more than one interrupt occurs simultaneously, the interrupts will be serviced in a fixedorder of priority. After servicing of the interrupt condition, linkage will be provided to the preinterrupt conditions, if desired.

#### **Processor States**

Concurrent with the interrupt mechanism, Spectra 70 Systems may have up to four processor states. These processor states facilitate program control of interrupt conditions and normal processing operations. In effect, processor states reflect the particular status of a system at a given time in relation to the functions being performed.

These processor states deal with normal processing, interrupt mechanism, operating systems, and machine malfunctions. The 70/15 and 70/25contain two processor states while the 70/45 and 70/55 contain four processor states.

In the 70/45 and 70/55 the combinations of interrupt and processor states are carried to their logical extension in that each state contains its own complete interrupt system. The effect of each state having its own masks, registers, and instruction sets facilitates the servicing of the interrupt mechanism with a minimum of program manipulation.

#### **Input-Output Channels**

The control of the transmission of data between the processor and an associated peripheral device is accomplished through channels and the RCA Standard Interface. A channel may be considered as an independent unit controlling data flow to and from the processor, and releasing control to the input or output device. This release allows the processor to function simultaneously with the input-output operation. Each channel utilizes its own set of commands to perform input-output operations. These commands, referenced as channel commands, control the device once a start command has been given by the processor. Chaining of channel commands provides a means by which several operations, such as multiple reads, may be completed independently of the processor.

The RCA Standard Interface functions as a connector between the channel and a device control. The interface establishes an identical relationship with each input-output device in that any device may be connected to the interface regardless of type, size, or speed. The number of channels and interfaces connected varies with the processor model. Within the Spectra 70 Series there are two types of channels: selector channels and multiplexor channels.

#### **Selector Channel**

The selector channel in the Spectra 70 Series controls the transfer of data to and from a peripheral device. These selector channels operate independently of the processor. A selector channel has from one to four trunks, depending upon the processor model. A controller determines the number of devices that can be connected to a trunk. For example, a tape controller controls as many as 16 tape devices. Channels can operate concurrently resulting in the overlap of input-output operations. The transfer rate of the selector channel depends upon the speed of the particular processor.

#### **Multiplexor Channel**

The multiplexor channel provides a unique method through which varying speed peripheral devices may be attached. Speed variances are accommodated by having available two different transmission modes: Multiplex mode and Burst mode.

The Multiplex mode is used when low-speed devices are attached to a processor and the channels data track is time-shared by all of the lowspeed devices connected to the multiplexor. In this instance, every low-speed device may be operated simultaneously by the multiplexor channel sending and receiving the required data. The devices in the slow-speed range are printers, card readers, card punches, paper-tape reader-punch, and display terminals.

The Burst mode must be used when high-speed devices are operated via the multiplexor; however, in the Burst mode, only a single input-output device may use the channel at one time. Tape drive, disc, drum, and mass memory equipment are devices which must operate in the Burst mode. The multiplexor channel normally runs multiple devices on a time-sharing basis. A Burst mode occurs automatically under certain conditions or is specified by a modification of the input-output command. The Burst mode is limited to the Model 70/45 and 70/55 Processors. The multiplexor channel divides the data track into sub-channels over which the data will flow. Each sub-channel may be individually addressed by the program. The multiplexor channel may contain up to eight input-output trunks from which up to 256 devices may be connected.

#### **Communications**

In the normal execution of today's business, data communications is becoming an integral part of the information interchange between operations, administrative, and managerial groups. Efficient operation is a result of using the most current and accurate information available. The integration of communications and processing provides the means for gathering, processing, and disseminating data to the individuals and groups concerned with its use. Message switching, inquiry and response, data collection, and management information systems are indicative of the diversified communications capabilities of the Spectra 70 Series.

To meet the demands of these systems, RCA has designed a comprehensive range of processors and communications equipment in the Spectra 70 Series. The design criteria employed in the series makes it possible for RCA to tailor systems specifically to fit the user's needs.

Each processor in the series has communications capabilities when equipped with the appropriate communication equipment. This equipment provides single and multiple-circuit handling; low and high-speed transmission rates; short and long-distance communications capabilities; and the performance characteristics required to operate with small unsophisticated systems as well as large complex systems.

#### **Communication Control**

The communication control provides singlechannel, long-distance, processor-to-processor communication via telephone lines. Large volumes of data can be transmitted between processors at distant locations making it possible to shorten reporting and data delivery cycles as well as ensuring the delivery of the most current information available. Speed and accuracy are the prime considerations in the design and operation of this device.

#### Data Exchange Control (DXC)

The Data Exchange Control (DXC) enables two RCA processors to communicate with each other. Data transmission may be in either direction, but in only one direction at a time. The DXC facilitates transmission of data at high rates dependent upon the type of channel used and the number of simultaneous active devices attached to the transmitting and receiving processors.

The DXC is a powerful tool for multisystem applications. Large volumes of data can be exchanged between processors for storage, further processing, and/or other peripheral action. In a real-time system, status information, and queue tables are transmitted to the backup processor. This data is used by the backup processor in the event of a change in operational tasks. The utilization of a DXC in a multiprocessor system affords flexibility and an extension of processing capabilities.

#### **Communication Multiplexor Channel**

Multiple-channel communications capabilities are provided by the Communication Multiplexor Channel (CMC). The CMC performs input and output functions in the 70/45 System by exchanging timing, control, and data over the RCA Standard Interface with the appropriate controls and devices. The CMC is completely flexible with respect to the number of lines, the type of lines, the mixture of speeds, and the variety of remote devices it can communicate with.

The 70/45 Processor equipped with a CMC addresses up to 256 devices. These devices are not limited to communications devices but can be standard input-output peripherals. Any combination of peripheral and communication devices may be connected to the CMC up to the maximum capacity. Inclusion of a communication multiplexor channel, replaces the standard multiplexor channel.

Single station and multistation circuit operations are accommodated by the CMC and its associated control and buffering equipment. Depending upon the system characteristics and the operational requirements, a combination of communication equipment and program provide direction, coordination, and the data-handling capacity necessary for the Model 70/45 Processor to function as a powerful communications center.

The CMC operates with a wide range of devices at a variety of speeds. Both high-speed and lowspeed devices may be serviced concurrently. The maximum data rate of the CMC is 62 kilobytes per second.

#### **Communications Buffers**

The Spectra 70 Series includes a wide range of communications buffers capable of interfacing telegraph as well as data-communications devices and systems. The operational and performance characteristics of these buffers are selectable. They are dependent upon the requirements of the particular device or system for which they are designed to interface.

Each buffer in the series operates at a specific range of transmission speeds, code levels, and with specific communications devices and systems. The buffer is the interface between the communication line and the communication buffer control. This control enables the 70/45 Processor, equipped with a communication multiplexor channel, to receive and transmit data.

#### **Memory Protect**

The protection of memory segments from destruction by programming or input devices is provided in the Models 70/45 and 70/55 Processors through the memory-protect feature.

Memory-protect feature can, depending upon availability of memory, protect up to 15 memory segments or programs from address interaction. The basic segment consists of 2,048 bytes and is increased in multiples of 2,048 bytes. Memoryprotect feature is a processor function and does not require memory allocation nor does it increase instruction timing.

Memory-protect feature consists of a set of registers which are constantly scanned during instruction addressing to ascertain that the address falls within preset limits (segments). When an address is detected that exceeds the allowable limitation, an interrupt condition is set and appropriate action is taken.

This feature greatly enhances the capability for multiprogramming in the Spectra 70 Series.

#### **Direct Control**

The optional direct-control feature offered in the Models 70/45 and 70/55 Processors provides control and synchronizing information between the processors and/or special external devices. This direct-control feature provides two instructions that implement the transfer of one byte of information between the memory and an external device. The direct control also provides six external-signal lines effecting an external interrupt.

#### **Elapsed-Time Clock**

An elapsed-time clock for real-time control is available in the Spectra 70 Series. This feature is standard in the 70/25 system and optional in the 70/45 and 70/55 Systems. The timer is maintained on either a 50 or 60 cycle-per-second-rate providing an interrupt capability every 16.67 milliseconds or at the termination of the timer's full cycle. The elapsed-time clock can be reset by the programmer at any time.

## MULTISYSTEM OPERATION

Multisystem operation is available in the Spectra 70 Series. Through the use of shared inputoutput devices and/or data exchange controls (for memory-to-memory transmission), the expansion of a given processor's power for multisystem communication is provided. In addition, multisystem capability is an added advantage for enhancing system reliability in real-time applications.

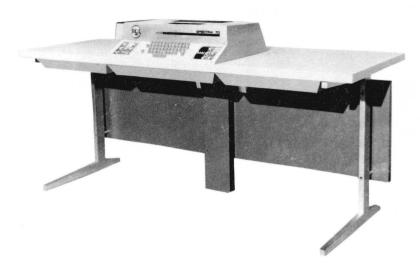

Figure 1. RCA 70/15 System

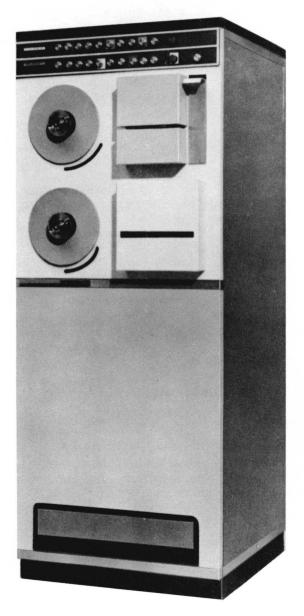

Figure 2. RCA 70/25 System

# EQUIPMENT DESCRIPTION

## RCA MODEL 70/15 PROCESSOR

#### General

The RCA Model 70/15 Processor, smallest member of the Spectra 70 Series, is a powerful data processing system designed specifically for small-scale data applications and low-cost remote and satellite operations. The prime objective of this system is to satisfy the ever-increasing need for low-cost off-line processing. Simultaneity is provided through a read-auxiliary command for card readers and magnetic tapes. Peripheral devices such as the card punch and printer are fully buffered.

To fulfill the growth requirements of the user, the 70/15 is upward compatible within the Spectra 70 Series.

The 70/15 is a byte-organized, two-address serial processor consisting of high-speed memory, program control, and input-output control.

#### **High-Speed Memory**

High-speed memory consists of planes of magnetic cores. These planes are  $64 \times 64$  strings; each string is one byte in depth resulting in a basic block of 4,096 bytes of separately addressable core memory. High-speed memory is field-expandable from the basic 4,096 bytes to 8,192 bytes. The byte is the smallest addressable unit in the Model 70/15 Processor.

The basic memory-cycle time is 2.0 microseconds. This is the time to transfer one byte from the 70/15 memory to the Memory register and to regenerate the byte in storage.

The first 50 bytes of high-speed memory are reserved for use by the processor. They are used as utility registers and intermediate storage media in the handling of input-output operations and interrupt processing.

#### **Program Control**

The function of the program control unit in the Model 70/15 Processor is to interpret and execute the instructions stored in high-speed memory. Necessary registers and indicators are provided by the program control unit to monitor sequence of operations, to perform automatic accuracy checks, and to communicate with the RCA Standard Interface in the control of input-output devices.

Two processor states, each having its own program counter, are present in the Model 70/15 Processor. They provide fast interrupt servicing and facilitate program system control. The processor states and their functions are as follows:

- Processing State  $(P_1)$  executes the user's program and is capable of being interrupted. Once interrupted, the conditions existing at the time of interrupt are automatically stored and control is transferred to the Interrupt State  $(P_2)$ .

- Interrupt State  $(P_2)$  analyzes an interrupt condition and determines the action to be taken. Control is then transferred back to the *Processing State*  $(P_1)$  where the interrupt is serviced. This state may not be interrupted.

Program interruption capabilities are provided in the Model 70/15 Processor as follows:

- 1. Request interrupt for an input-output device interruption of normal processing takes place upon request from the interrogating typewriter, communications control, or data exchange control to process remote inquiries or data transmissions.

- 2. Internal operation code trap an interrupt occurs when an undefined operation code in the 70/15 instruction set is recognized. This provides the facility to simulate operations not included in the standard 70/15 instruction set.

When an interrupt signal is received by the processor, the actual interrupt takes place as soon as the current instruction terminates.

All interrupts (except internal operation code trap) may be inhibited if desired. If, however, the interrupt is not inhibited, control will automatically be transferred to the *Interrupt State*  $(P_z)$ . At this time, conditions existing in the *Proc*essing State  $(P_1)$  are stored by hardware so that an orderly return may be affected once the interrupt has been serviced.

#### Input-Output Control

The Model 70/15 Processor communicates with all input-output devices through the RCA Standard Interface. The input-output channel transmits data to or from a single peripheral device and is capable of handling high-speed input-output devices. Up to six standard interface trunks may be connected to the channel and each trunk can control up to 16 input-output devices.

#### Instruction Formats and Timing

The Model 70/15 Processor includes a standard set of 25 instructions. This instruction repertoire performs arithmetic, data handling, decision, control, and input-output operations.

All instructions must start on halfword boundaries (even-numbered byte location). The basic format of the instruction set is two, four, or six bytes long (see table 1). Twenty instructions have a two-address format and are six bytes in length. Three single-address instructions are in the instruction set and are four bytes long. Halt and Post Status instructions require only two bytes. Direct addressing is used up to the maximum of 8,192 bytes.

| TABLE 1 |  | INSTRUCTION | FORMATS |

|---------|--|-------------|---------|

|---------|--|-------------|---------|

| Halfy        | Halfword |                      | Half   | word                 | Halfword |         |  |

|--------------|----------|----------------------|--------|----------------------|----------|---------|--|

| Byte 1       | Byte     | e 2                  | Byte 3 | Byte 4               | Byte 5   | Byte 6  |  |

| 8<br>Op Code | I        | 8                    | D      | 16<br>1              | D        | 16<br>2 |  |

| 8<br>Op Code | 4<br>L1  | ${4 \atop { m L}_2}$ | D      | 16<br>0 <sub>1</sub> | D        | 16<br>2 |  |

| 8<br>Op Code | 4<br>T   | 4<br>U               | L      | 16<br>),             | D        | 16      |  |

| 8<br>Op Code | N        | 8<br>/I              | L      | 16<br>),             |          |         |  |

| 8<br>Op Code | 4<br>T   | 4<br>U               |        |                      |          |         |  |

| 8<br>Op Code | N        | 8<br>/I              |        |                      |          |         |  |

Numbers in upper right corners of blocks indicate number of bits used.

#### Legend:

- $D_1$  address of leftmost byte of first operand.

- $D_2$  address of leftmost byte of second operand.

- L one less than length of first and/or second operand (0-255).

- $L_{i}$  one less than length of first operand (0-15).

- $L_2$  one less than length of second operand (0-15).

- M mask for Branch On Condition, Test Under Mask, and Halt.

- T input-output trunk referenced.

- U --- input-output device referenced.

A list of the 70/15 standard instruction set and corresponding staticizing and execution timing is tabulated in table 2. For input-output instruction timing, refer to Appendix A.

#### TABLE 2. INSTRUCTION TIMING

| Instruction                                 | Staticizing<br>(µs) | Execution<br>(µs)                                        |

|---------------------------------------------|---------------------|----------------------------------------------------------|

| ARITHMETIC<br>INSTRUCTIONS                  |                     |                                                          |

| Add Decimal                                 | 20                  | $18 + 4N_1 + 2N_2$                                       |

| Add Binary                                  | 20                  | $18+4N_1+2N_2$                                           |

| Subtract Decimal                            | 20                  | $18+4N_1+2N_2$                                           |

| Subtract Binary                             | 20                  | $18+4N_{\scriptscriptstyle 1}+2N_{\scriptscriptstyle 2}$ |

| And                                         | 20                  | 6N                                                       |

| Or                                          | 20                  | 6N                                                       |

| Exclusive Or                                | 20                  | 6N                                                       |

| DATA HANDLING<br>INSTRUCTIONS<br>Move       | 20                  |                                                          |

|                                             | 20                  | 4N                                                       |

| Edit                                        | 20                  | 4I + 4F + 6D                                             |

| Pack                                        | 20                  | $16 + 2N_1 + 2N_2$                                       |

| Unpack                                      | 20                  | $16 + 2N_1 + 2N_2$                                       |

| DECISION AND CONTROL<br>Branch on Condition | 16                  | Branch = 4<br>No Branch = 2                              |

| Compare Decimal                             | 20                  | $16+4N_1+2N_2$                                           |

| Compare Logical                             | 20                  | 6B                                                       |

| Set P <sub>2</sub> Register                 | 16                  | 6                                                        |

| Test Under Mask                             | 16                  | 2                                                        |

| Halt                                        | 12                  | 2                                                        |

| INPUT-OUTPUT<br>Read Forward                | 20                  |                                                          |

| Read Reverse                                | 20                  |                                                          |

| Read Auxiliary                              | 20                  |                                                          |

| Write                                       | 20                  | See                                                      |

| Write Control                               | 20                  | Appendix A                                               |

| Erase                                       | 20                  |                                                          |

| Sense                                       | 20                  |                                                          |

| Post Status                                 | 12                  |                                                          |

#### Legend:

B — number of bytes compared before an inequality occurs.

D - number of digits inserted.

- I -- number of edit characters inserted.

- F number of fill characters inserted.

- N number of bytes.

- $N_i$  number of bytes in first operand.

- $N_2$  number of bytes in second operand.

# RCA MODEL 70/25 PROCESSOR

#### General

The RCA Model 70/25 Processor, the second member of the Spectra 70 Series, is a small-tomedium scale computer designed to satisfy a wide variety of data-processing requirements. The 70/ 25 is organized as a powerful data processor with the capability to concurrently perform up to 16 input-output operations. This input-output simultaneity, coupled with its communications capabilities, makes the 70/25 a highly efficient vehicle for high-speed remote processing. Provision is made for program compatibility between the Model 70/25 Processor and the larger processors in the Spectra 70 Series.

The 70/25 is a word-organized, variable-data format processor consisting of high-speed memory, program control, and input-output control.

#### **High-Speed Memory**

High-speed memory consists of planes of magnetic cores. These planes are  $64 \times 64$  strings; each string is four bytes in depth resulting in a basic block of 16,384 bytes of separately addressable core memory. High-speed memory is field-expandable from 16,384, 32,768, or 65,536 bytes. The byte is the smallest addressable unit in the Model 70/25 Processor. Four 8-bit bytes are accessed in one memory cycle of 1.5 microseconds. Memory time is the time required to transfer a four-byte word from the 70/25 memory to the Memory register and to regenerate the word in storage.

The first 50 bytes of high-speed memory are reserved for use by the processor. They are used as hardware registers and intermediate storage media in the handling of input-output operations and interrupt processing. The last 100 bytes of high-speed memory are reserved for 15 General-Purpose registers, a Timer register, and Utility registers. In addition to these two memory areas, the inclusion of a multiplexor channel in the RCA 70/25 requires that high-speed memory immediately preceding the last 100 bytes be reserved for Multiplexor Channel Device registers. The amount of memory required for this purpose is dependent upon the number of devices associated with the multiplexor channel.

#### **Program Control**

The function of the program control unit in the Model 70/25 Processor is to interpret and execute the instructions stored in high-speed memory. The required registers and indicators are provided by the program control unit to monitor sequence of operations, to perform automatic accuracy checks, and to communicate with the RCA Standard Interface in the control of inputoutput devices.

Two processor states, each having its own program counter, are present in the Model 70/25 Processor. They provide fast interrupt servicing and facilitate program system control. The processor states and their functions are as follows:

- Processing State  $(P_1)$  executes the user's program and is capable of being interrupted. Once interrupted, the conditions existing at the time of interrupt are automatically stored and control is transferred to the Interrupt State  $(P_2)$ .

- Interrupt State  $(P_2)$  analyzes an interrupt condition and determines the action to be taken. Control is then transferred back to the *Processing State*  $(P_1)$  where the interrupt is serviced. This state may not be interrupted.

Program interruption capabilities are provided in the Model 70/25 as follows:

- 1. Request or termination interrupt by an inputoutput device — interruption of normal processing takes place upon request from the interrogating typewriter, communications control, or data exchange control to process remote inquiries or data transmissions. An interrupt also occurs upon termination of an input-output operation.

- 2. Internal operation code trap an interrupt occurs when an undefined operation code in the 70/25 instruction set is recognized. This provides the facility to simulate operations not included in the standard 70/25 instruction set.

- 3. Arithmetic overflow or divide exception an interrupt occurs on all arithmetic-overflow conditions. When a Divide instruction is executed and the quotient is less than one or exceeds 29 digits (plus sign), an interrupt also takes place.

- 4. *Timer interrupt* the timer may be set or altered to provide for interruption of normal processing when a specified amount of time has elapsed.

When an interrupt signal is received by the processor, the actual interrupt takes places as soon as the current instruction terminates.

All interrupts (except internal operation code trap) may be inhibited if desired. If the interrupt is not inhibited, control will automatically be transferred to the *Interrupt State*  $(P_2)$ . At this time, conditions existing in the *Processing State*  $(P_1)$  are stored by hardware so that an orderly return may be affected once the interrupt has been serviced.

#### Input-Output Control

The Model 70/25 Processor communicates with all input-output devices through the RCA Standard Interface. Up to eight selector channels (two of which may be high speed) plus a multiplexor channel may be connected to the system, providing a high degree of simultaneity. Four selector channels (medium-speed) are standard. Each selector channel can control up to 16 devices. A set of registers is provided for each selector channel, making simultaneous operation of all channels possible. Each device (up to 115) on the multiplexor channel has its own sub-channel register. Up to eight of these devices may time-share the channel. It is possible for selector channels and multiplexor channel-connected devices, in any combination, to operate simultaneously with computing.

#### Instruction Formats and Timing

A comprehensive repertoire of instructions is provided with the Model 70/25 Processor. Thirtyone instructions permit a full range of dataprocessing capability including powerful arithmetic, data handling, decision, control, and inputoutput facilities.

All instructions must start on halfword boundaries (even-numbered byte locations). The basic format of the instruction set is two, four, or six bytes in length. Table 3 illustrates these formats and their construction.

| Halfy        | word    |                                      | Half                     | word                                  | Halfword |          |  |

|--------------|---------|--------------------------------------|--------------------------|---------------------------------------|----------|----------|--|

| Byte 1       | Byt     | e 2                                  | Byte 3                   | Byte 4                                | Byte 5   | Byte 6   |  |

| 8<br>Op Code | ]       | 8<br>L                               | 4<br>B1                  | 12<br>D1                              | 4<br>B2  | 12<br>D2 |  |

| 8<br>Op Code | 4<br>L1 | $egin{array}{c} 4 \ L_2 \end{array}$ | 4<br>B1                  | 12<br>D1                              | 4<br>B2  | 12<br>D2 |  |

| 8<br>Op Code | 4<br>T  | 4<br>U                               | 4<br>B1                  | 12<br>D1                              | 4<br>B2  | 12<br>D2 |  |

| 8<br>Op Code | N       | 8<br>/I                              | ${\mathop{\rm B}_{2}}^4$ | $egin{array}{c} 12 \ D_2 \end{array}$ |          |          |  |

| 8<br>Op Code | 4<br>T  | 4<br>U                               |                          |                                       |          |          |  |

| 8<br>Op Code | N       | 8<br>[                               |                          |                                       |          |          |  |

**TABLE 3. INSTRUCTION FORMATS**

Numbers in upper right corners of blocks indicate number of bits used.

Legend:

B<sub>1</sub> — register containing base address of first operand.

$B_2$  — register containing base address of second operand.

$D_1$  — address of leftmost byte of first operand.

#### Legend: (Cont.)

- $D_{\text{\tiny 2}}-\!\!-$  address of leftmost byte of second operand.

- L one less than length of first and/or second operand (0-255).

- $L_1$  one less than length of first operand (0-15).

- $\rm L_2$  one less than length of second operand (0–15).

- M mask for Branch On Condition, Test Under Mask, and Halt.

- T input-output trunk referenced.

- U input-output device referenced.

A list of the 70/25 standard instruction set and corresponding staticizing and execution timing is tabulated in table 4. Staticizing times shown are maximum and can be reduced if instructions are on fullword boundaries. For input-output instruction timing, refer to Appendix A.

TABLE 4. INSTRUCTION TIMING

| Instruction                                                | Staticizing<br>(µs) | Execution<br>(µs)                                                                                                                                              |

|------------------------------------------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ARITHMETIC<br>INSTRUCTIONS<br>Add Binary                   | 13.5                | $8.25 + 2.25 N_1 + 1.5 N_2$                                                                                                                                    |

| Add Decimal                                                | 13.5                | $8.25 + 2.25N_1 + 1.5N_2$                                                                                                                                      |

| Subtract Binary                                            | 13.5                | $8.25 + 2.25N_1 + 1.5N_2$                                                                                                                                      |

| Subtract Decimal                                           | 13.5                | $8.25 + 2.25N_1 + 1.5N_2$                                                                                                                                      |

| Multiply Decimal                                           | 13.5                | $\begin{array}{c} 12.75+9\mathrm{N_1}-1.5\mathrm{N_2}+\\ \mathrm{C}[3.75~(\mathrm{N_1}-\mathrm{N_2})~+\\ 3]~3.75~(\mathrm{N_1}-\mathrm{N_2})~+\\ 3\end{array}$ |

| Divide Decimal                                             | 13.5                | $\frac{9 + 29.25 N_1 - 27 N_2 +}{37.5 N_2 (N_1 - N_2)}$                                                                                                        |

| AND                                                        | 13.5                | 3.75N                                                                                                                                                          |

| OR                                                         | 13.5                | 3.75N                                                                                                                                                          |

| Exclusively OR                                             | 13.5                | 3.75N                                                                                                                                                          |

| DATA HANDLING<br>INSTRUCTIONS<br>Edit                      | 13.5                | 2I + 2F + 3D                                                                                                                                                   |

| Move                                                       | 13.5                | 3W + 3B                                                                                                                                                        |

| Pack                                                       | 13.5                | $6 + 1.5N_1 + 3N_2$                                                                                                                                            |

| Unpack                                                     | 13.5                | $7.5 + 3N_1 + 1.5N_2$                                                                                                                                          |

| Translate                                                  | 13.5                | 6.75N                                                                                                                                                          |

| DECISION AND<br>CONTROL<br>INSTRUCTIONS<br>Branch and Link | 9                   | 3.75                                                                                                                                                           |

| Branch On Condition                                        | 9                   | Branch = 2.25;<br>No Branch = 0.5                                                                                                                              |

| Branch On Count                                            | 9                   | Branch = 6.75;<br>No Branch = 2.25                                                                                                                             |

| Compare Decimal                                            | 13.5                | $6 + 1.5 N_1 + 2.25 N_2$                                                                                                                                       |

| Instruction                                   | Staticizing<br>(µs) | Execution<br>(µs) |

|-----------------------------------------------|---------------------|-------------------|

| DECISION AND<br>CONTROL<br>INSTRUCTIONS Cont. |                     |                   |

| Compare Logical                               | 13.5                | 1.5 + 3B          |

| Halt                                          | 4.5                 | 1.5               |

| Load Multiple                                 | 9                   | 3.75R             |

| Set P <sub>2</sub> Register                   | 9                   | 3                 |

| Store Multiple                                | 9                   | 3.75R             |

| Test Under Mask                               | 9                   | 1.5               |

| INPUT/OUTPUT<br>INSTRUCTIONS                  |                     |                   |

| Erase                                         | 13.5                |                   |

| Post Status                                   | 9                   |                   |

| Read Forward                                  | 13.5                |                   |

| Read Reverse                                  | 13.5                | See Appendix A.   |

| Sense                                         | 13.5                |                   |

| Write                                         | 13.5                |                   |

| Write Control                                 | 13.5                |                   |

Legend:

- B number of bytes processed

- (or number of bytes outside fullword boundaries).

- $\rm C$  sum of multiplier digits.

- D number of digits inserted.

- F number of fill characters inserted.

- I number of edit symbols inserted.

- N total number of bytes.

- $N_1$ —number of bytes in first operand.

- $N_2$  number of bytes in second operand.

- R number of registers.

- W-number of four-byte words.

# RCA MODEL 70/45 PROCESSOR

#### General

The RCA Model 70/45 Processor, the third member of the Spectra 70 Series, is a powerful, solid-state, general-purpose, digital processor. It is the main element of a system handling mediumlarge data processing applications. Because of its large storage capacity, fast data transmission, and computation rates, this processor is highly efficient as both a data processor and a scientificproblem solver. The internal logic is controlled by elementary operations stored in a read only control memory.

All instructions, character codes, interrupt facilities, and programming features are functionally the same as corresponding features on the Model 70/55. Programs may be interchanged between processors provided:

- 1. Systems features are equivalent.

- 2. Programs are written independently of strict timing considerations.

- 3. Programs are restricted to specified functions and 'do not utilize unspecified characteristics peculiar to the hardware of either processor.

The 70/45 is a diad-organized, variable-format processor consisting of main memory, scratch-pad memory, read only control memory, non-addressable memory, program control, and input-output control.

#### **Main Memory**

Main memory consists of expandable magnetic core storage available in sizes of 16,384, 32,768, 65,536, 131,072, or 262,144 bytes. The basic memory-cycle time is 1.44 microseconds. This is the time to transfer two bytes from the main memory to the Memory register and to regenerate the bytes in storage. A byte may consist of a character, two digits, or eight bits. The processor normally operates on two 8-bit bytes at a time although the minimum addressable data unit is one byte and the maximum addressable data unit is 8 bytes.

#### Scratch-Pad Memory

The scratch-pad memory, a fast micromagnetic storage device, contains the General-Purpose, Floating-Point, and various other registers to facilitate processor and program control. This memory consists of 128 four-byte words. Access time is 300 nanoseconds per word. Locations in the scratch-pad memory are uniquely addressed by the Load-Scratch-Pad and Store-Scratch-Pad instructions.

Four double word Floating-Point registers and 16 General-Purpose registers are contained in the scratch-pad memory. The Floating-Point registers are used in floating-point arithmetic operations. The General-Purpose registers are used in base addressing, indexing, and utility operations.

#### **Read Only Control Memory**

The read only control memory contains the internal logic for the elementary operations of the processor. Memory-cycle time is 480 nanoseconds permitting significant reduction in the instruction execution timing.

#### **Non-Addressable Memory**

This memory is a portion of the main memory that cannot be addressed by programming. A set of registers that services the devices attached to a multiplexor channel is contained in the nonaddressable main memory. The size of this memory will vary in accordance with the capacity of the main memory selected by the user. Non-addressable memory is in addition to the main memory capacity of the system.

#### **Program Control**

The Model 70/45 Processor has four distinct processor states to provide extremely fast interrupt servicing. Combined with the program systems control, these processor states provide an extremely efficient interrupt handling. The four processor states are:

- Processing State  $(P_i)$  interprets and executes the user's program. This processing state is the problem-oriented state.

- Interrupt Response State  $(P_z)$  performs specific program tasks as dictated by the Interrupt Control State  $(P_s)$ .

- Interrupt Control State  $(P_s)$  is automatically entered upon recognition of an interrupt other than one caused by a machine check or power failure. This state is responsible for performing a detailed analysis of the cause of interrupt and establishing its priority. Once these functions have been performed, linkage is provided to the proper interrupt processing routine in the Interrupt Response State  $(P_s)$ .

- Machine Condition State  $(P_4)$  is entered whenever a machine check or power failure occurs. This state analyzes the cause of a machine interrupt and establishes its priority. Control is then transferred to the Interrupt Response State  $(P_2)$  so that an indication of the cause of interrupt may be given to the operator.

Table 5 summarizes the type and number of registers uniquely assigned to each processor state.

| TABLE 5. PROCESSOR STATE REGISTER | TABLE | 5. P | ROCESSOR | STATE | REGISTERS |

|-----------------------------------|-------|------|----------|-------|-----------|

|-----------------------------------|-------|------|----------|-------|-----------|

| Desite                    | Processor State |                |    |                |  |  |

|---------------------------|-----------------|----------------|----|----------------|--|--|

| Register                  | P <sub>1</sub>  | P <sub>2</sub> | P3 | P <sub>4</sub> |  |  |

| Program Counter           | 1               | 1              | 1  | 1              |  |  |

| General-Purpose Registers | 16              | 16             | 6  | 5              |  |  |

| Floating-Point Registers  | 8               | *              | *  | *              |  |  |

| Interrupt-Status Register | 1               | 1              | 1  | 1              |  |  |

| Interrupt-Mask Register   | 1               | 1              | 1  | 1              |  |  |

\* Floating-point instructions executed in these states use the floating-point registers of the Processing State (P<sub>i</sub>). Since each processing state has its own General-Purpose registers, Interrupt Status register, and Interrupt Mask register, the need for storing and reloading registers during interrupt processing is virtually eliminated.

Program interrupts occur as a result of errors in data or instruction specifications, input-output operations, external signals, equipment malfunctions, or arithmetic errors. The instruction being executed at the time of interrupt may be completed, suppressed, or terminated depending on the cause of the interrupt.

Any interrupt may be inhibited or permitted in any state through programming. If an interrupt occurs and is permitted, conditions existing in the interrupted state will be automatically stored. Control is then passed to the *Interrupt Control* State  $(P_s)$  or Machine Condition State  $(P_i)$ depending upon the cause of the interrupt. The priority of the interrupt is established and an analysis is made to determine the proper linkage to the *Interrupt Response State*  $(P_z)$  so that the interrupt may be processed. Once interrupt processing has been completed, control is returned to the state which was last interrupted and normal processing is resumed.

If several interrupts occur at the same time, the one having the highest priority will be processed. The remaining interrupts will be processed in turn depending upon their priority.

Table 6 summarizes all of the interrupt conditions, their respective priorities, the interrupt state which each initiates, and a brief description of the cause of interrupt.