### **General Disclaimer**

# One or more of the Following Statements may affect this Document

- This document has been reproduced from the best copy furnished by the organizational source. It is being released in the interest of making available as much information as possible.

- This document may contain data, which exceeds the sheet parameters. It was furnished in this condition by the organizational source and is the best copy available.

- This document may contain tone-on-tone or color graphs, charts and/or pictures, which have been reproduced in black and white.

- This document is paginated as submitted by the original source.

- Portions of this document are not fully legible due to the historical nature of some

of the material. However, it is the best reproduction available from the original

submission.

Produced by the NASA Center for Aerospace Information (CASI)

DOE/JPL/957031--85/1

Distribution Cat. UC-63

DRL No. DRD No. SE-2

> QUARTERLY TECHNICAL REPORT for the period 10/1/84 through 12/30/84

DOE/JPL/957031--85/1 DE85 007127

INK JET PRINTING OF SILVER METALLIZATION FOR PHOTOVOLTAICS

Purdue Research Foundation

Principal Investigator:

R.W. Vest (317/494-7009)

JPL Flat Plate Solar Array Project

January 25, 1985

"The JPL Flat Plate Solar Array Project is sponsored by the U.S. Department of Energy and forms part of the Solar Photovoltaic Conversion Program to initiate a major effort toward the development of flat plate solar arrays. This work was performed by agreement between NASA and DOE."

"This report was prepared as an account of work sponsored by the United States Government. Neither the United States not the United States Department of Energy, nor any of their employees, nor any of their contractors, subcontractors, or their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness or usefulness of any information, apparatus, product or process disclosed, or represents that its use would not infringe privately—owned rights."

#### FOREWORD

The research described in this report represents the effort for the first three months on Contract No. 957031 with the Jet Propulsion Laboratory, Paradena, CA, under the technical cognizance of Paul Alexander. The research was conducted in the Turner Laboratory for Electroceramics, School of Materials Engineering and School of Electrical Engineering, Purdue University, W. Lafayette, IN under the direction of R.W. Vest. The research was carried out by Dr. S. Singaram, D.A. Binford and K.F. Teng.

### TABLE OF CONTENTS

|     |                                              | Page |

|-----|----------------------------------------------|------|

| 1.  | INTRODUCTION AND SUMMARY                     | 4    |

| 2.  | PROGRESS                                     | 7    |

|     | 2.1 Mechanical Modifications                 | 8    |

|     | 2.2 Electronic Modifications and Programming | 10   |

|     | 2.3 Ink Development                          | 14   |

| 3.  | PLANS                                        | 14   |

| 4.  | SCHEDULE                                     | 19   |

| APP | FNDTY A                                      | Δ 1  |

#### 1. INTRODUCTION AND SUMMARY

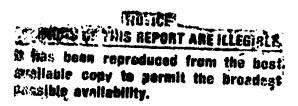

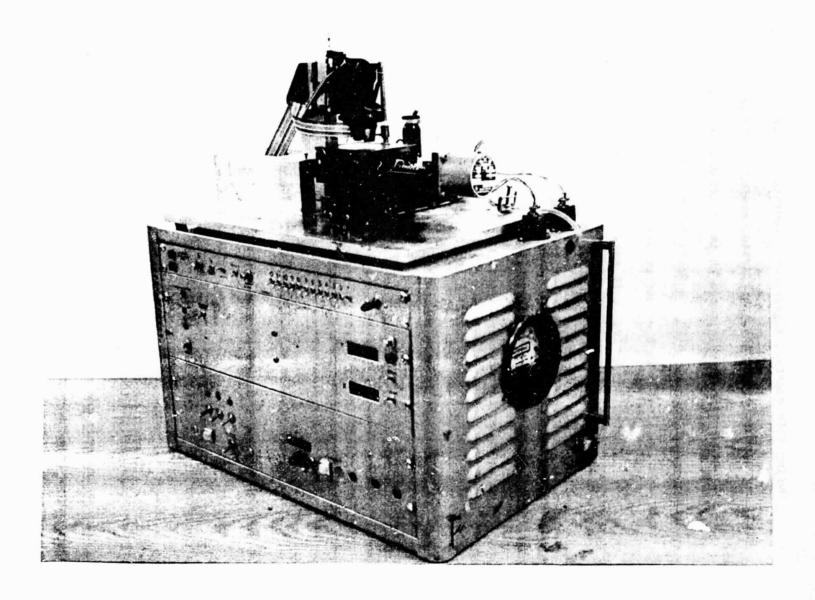

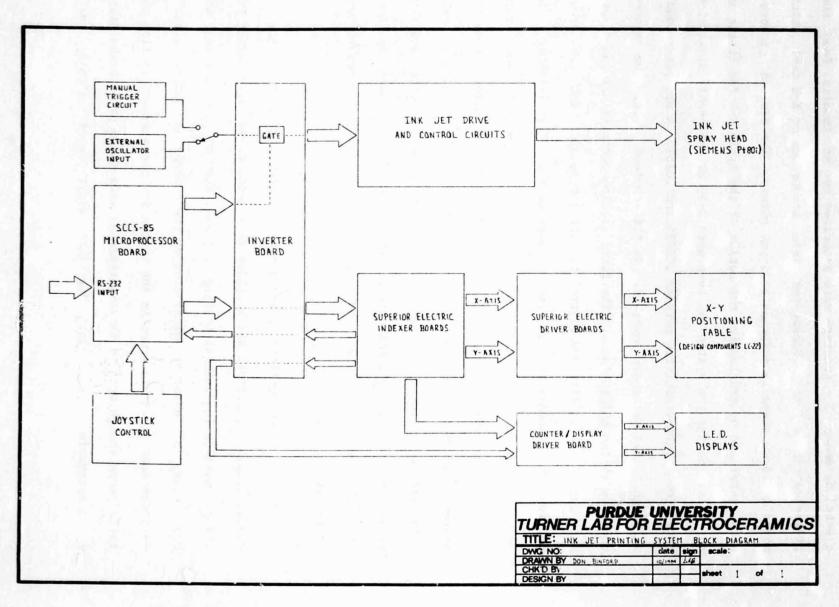

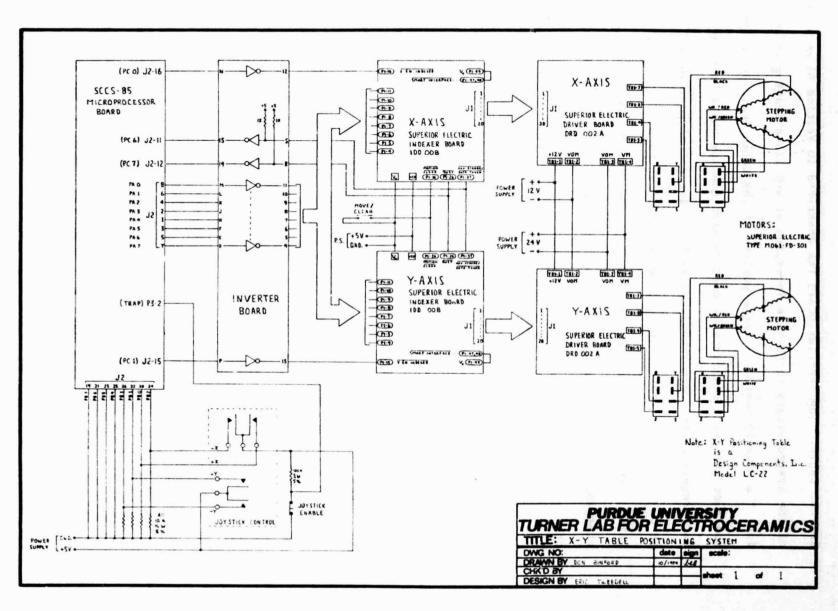

During this quarter, significant progress was made in the continuing development of the ink jet printing system for thick film circuits. The unit being used in this research is a prototype ink jet printer developed on a contract with the Naval Avionics Center. One of the first tasks completed early in the quarter was the complete documentation of this ink jet printing system as it existed. It was determined that this was an essential step in deciding what modifications were needed to the system and how these modifications would be implemented. This printing system documentation has been included as Appendix A to this report, and will be referred to for clarification of changes which have already been completed during this quarter. Figure 1 gives an overall view of the ink jet printer as it existed at the beginning of this contract and Fig. 3 shows more details of the spray heat and X-Y table.

After this initial step was completed, design modification studies were started for electronic, mechanical, and programming aspects of the system. These studies were completed at the end of the second month. The areas needing improvement were discussed and applicable changes decided upon. Some of these improvements were completed during this quarter and others have only been started. It should be noted that, although the general areas needing improvement have been identified and some changes decided upon, the exact details of how other changes will be implemented have not yet been decided. During the next months, these details will be discussed further and the modifications put in place accordingly.

Figure 1. Turner Laboratory Ink Jet Printer.

Figure 2. Spray Head and X-Y Table.

The first section of this report details the modifications which have already been made to the ink jet printing system. These include both mechanical and electronic and programming changes which were decided upon during the design modification studies. In some cases, these changes have been made only on a temporary basis until testing can verify that they work in the manner intended. As testing verifies their applicability, they will be implemented in a more permanent manner. Also, it should be pointed out that these circuit changes themselves may undergo additional modifications as total system packaging considerations and other factors dictate the need.

Other changes which will be made as a result of the design modification studies and those modifications which have been started but not completed are discussed in Section 3. These include not only the mechanical and electronic changes but, also, the programming modifications which often must be made along with the electronic changes and additions. Changes in software are always an ongoing process. For example, if greater print speeds are to be achieved then programming routines to control table acceleration and deceleration must be written to accomplish this. Some of the preliminary study to accomplish this was started early in the quarter and the actual programming is still in the process of being developed. Programming changes which have already been tested and implemented are included in the Section 2.2.

#### 2. PROGRESS

## 2.1 Mechanical Modifications

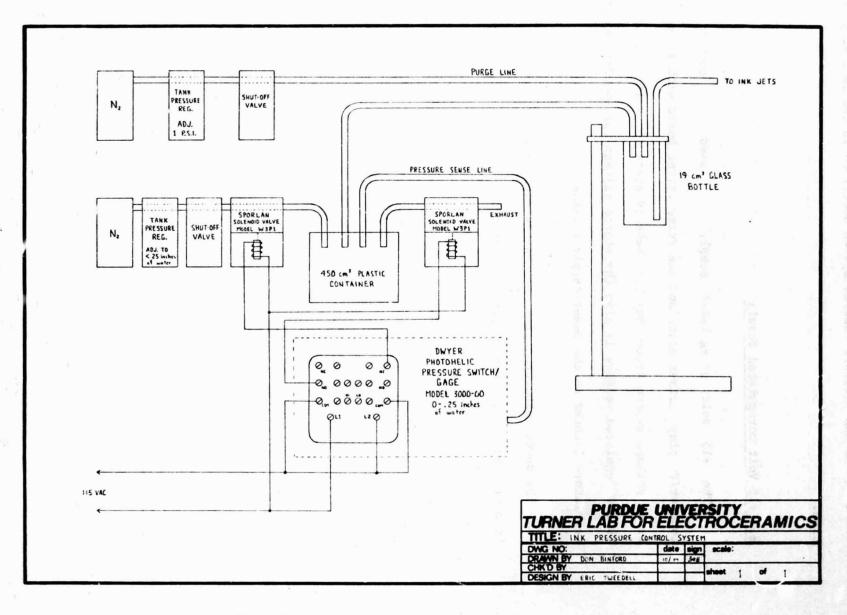

The pressure control system for supplying the ink to the ink jet head assembly is a very critical element for the correct functioning of the ink jet system. This slight pressure (less than 0.25 inches of water) is used to offset the static vacuum present at the ink jet nozzles due to the ink supply being at a level below the nozzles. As additional testing is done to optimize the various parameters associated with the printing process, accuracy in controlling and monitoring this slight pressure will be essential. For this reason, a model 602-1 differential pressure transmitter was purchased from Dwyer Instruments, Inc. It has a minimum range of 0-0.4 inches of water. Power was supplied to the unit by connecting it to a transformer with a 20 volt secondary. A 500 ohm resistor was connected as a receiver for the transmitter and the voltage across the resistor monitored with a digital voltmeter. This assembly was calibrated for the 0 to 0.4 inches of water range which corresponds to 2.0 volts to 10.0 volts on the digital voltmeter.

As a part of this change, the entire pressure control and monitoring system was moved out of the original equipment cabinet (see Fig. 1) and temporarily mounted in a second cabinet to facilitate the changes. The new Dwyer pressure transmitter was connected to the 19 ml glass bottle which contains the MOD ink being printed. This connection was made temporarily by using the purge line as shown on Figure All of Appendix A. This change will permit more accurate evaluation of the existing pressure control system. As additional printing studies are done, other

improvements in the ink supply and pressure control system may have to be made.

Other mechanical modifications to the existing ink jet printing system have been completed. It was decided that a more rigid mounting bracket for the ink jet spray head was needed so that more accurate and repeatable printings could be made. An aluminum wount was machined and attached to the aluminum plate which the positioning table is mounted on. Along with this change, a portion of the Siemens ink jet head not necessary in this application was cut away to make its mounting simpler. The head is attached to a precision adjustment mechanism so that the head to substrate spacing can be changed and this mechanism is attached to the new aluminum mount.

For many of the same reasons, a new brass block was machined for the positioning table. The inner region of chief block has a recessed section where the substrate is placed. The block is machined in such a way that the substrate can be positioned in only one corner of the recessed section. The new block also contains both a vacuum chuck and the original 40 watt cylindrical heating element to keep the block at a temperature between 30 and 35°C.

Finally, two micro switches were mounted on the positioning table so that the table could be positioned to an initial start point prior to each print sequence. These switches are 'debounced' before going to the microcomputer board. The actual initialization is accomplished in the microcomputer programming. This programming and the actual connections into the SCCS-85 board will be described in the next section.

### 2.2 Electronic Modifications and Programming

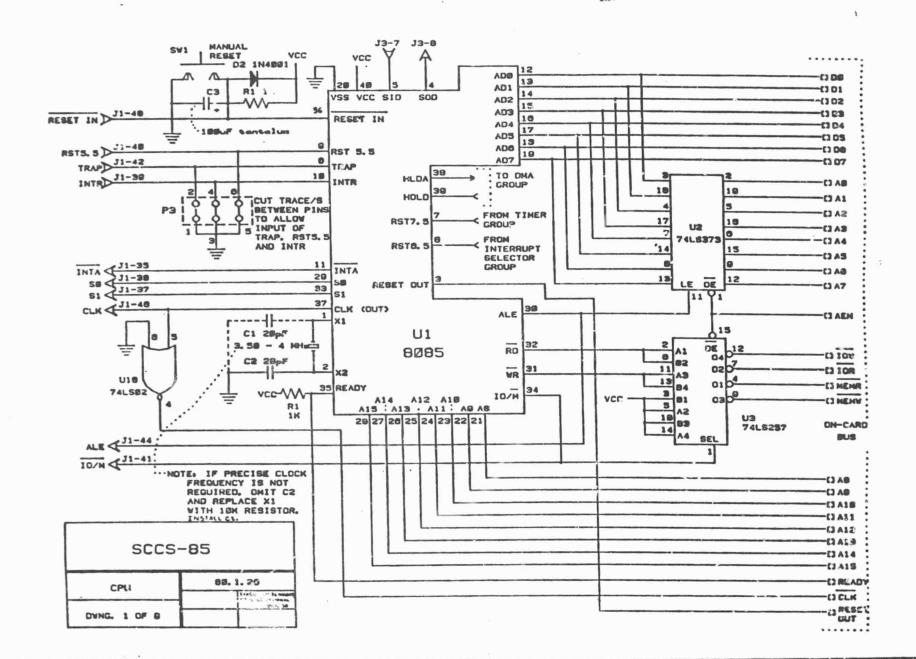

In the existing ink jet printing system, the trigger signal for the pulse driver board circuits either came from a manual trigger circuit or from an external square wave generator (see Fig. A3 of Appendix A). This method did not allow the frequency of the trigger signal to be microprocessor controlled. As additional work is done to determine the optimum ratio between the trigger frequency and the X-Y table stepping frequency, it will be necessary to control these two frequencies carefully. The table stepping frequency is already controlled by the microcomputer board.

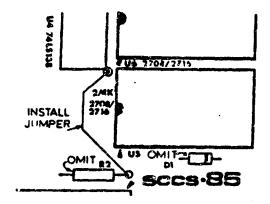

To eliminate the external generator and control the trigger rate from the microprocessor, one of the three programmable timers which are part of the SCCS-85 microcomputer board were utilized. Since these timers are referenced to the on-board crystal controlled clock, the frequency of the trigger signal for the ink jet nozzles could be assured. The timer output selected was OUT 2. It exits the SCCS-85 board at J3 pin 2. This signal was applied directly to the normally open contacts of the twelve ink jet head switches which are tied together. switches still function as before and route the signal on to the selected nozzle channel of the pulse driver board. The two 'AND' gates located on the inverter board which were used to gate the trigger signal on and off were eliminated (see Fig. A3 of Appendix A). The SCCS-85 output port line PC 3 which had controlled these gates was routed to the programmable timer input GATE 2 after the or-board jumper connecting GATE 2 to +5 volts was removed. When GATE 2 is high the OUT 2 signal is enabled. GATE 2's status (either low or high) is controlled through programming. It is taken high only when the table is moving and printing is desired.

In order to utilize the programmable times which is on the SCCS-85 board, a few changes to the main program were recessary. These changes were really just a simple initialization sequence for the times. The times made was established and the frequency of its output signal set. Its mode was set so that it outputs a continuous square wave signal when enabled by the gate. Since the positioning table is currently being used at a base speed only of 400 steps per second, the frequency of the square wave signal from OUT 2 was set at 100 Hz. This frequency can, of course, be easily changed but the one to four ratio between nozzle frequency and table stepping frequency has in the past proven to be a good general rule for obtaining smooth, continuous printed lines. This relationship is something which will be studied further.

Another problem encountered in the past has been the inability to establish an exact starting point for printing on a substrate. The manual 'joystick' controller could be used to position the X-Y table to a general start point under the ink jet head prior to a printing sequence, but it was impossible to go to an exact point time after time. It was decided that the table could be positioned to a start point or origin by using some kind of initialization routine prior to any print sequence. It order to accomplish this some hardware additions were necessary, along with a few programming changes and additions to the main program.

As stated in the previous section, two precision switches having reasonably low differential travel specifications were mounted on the positioning table. These single pole double throw devices were mounted in such a way that their common terminals switched from the normally closed contacts to the normally open contacts when the table was positioned at the desired origin. They have fine adjustment mechanisms so that an exact initial starting point can be set. In order to be interfaced with the SCCS-85 microcomputer board, the switches were first 'debounced' using a circuit similar to the circuit for 'debouncing' the MANUAL TRIGGER switch shown on Fig. A3 of Appendix A. These circuits were built temporarily on the existing inverter board. The output line from the X-axis switch circuit was connected to the RST 5.5 interrupt input on the SCCS-85 board and the line from the Y-axis switch circuit was connected to the RST 6.5 interrupt input on the SCCS-85 board. These two interrupt inputs now make a low to high transition when the table gets to the origin for each respective axis. This completed the necessary hardware additions.

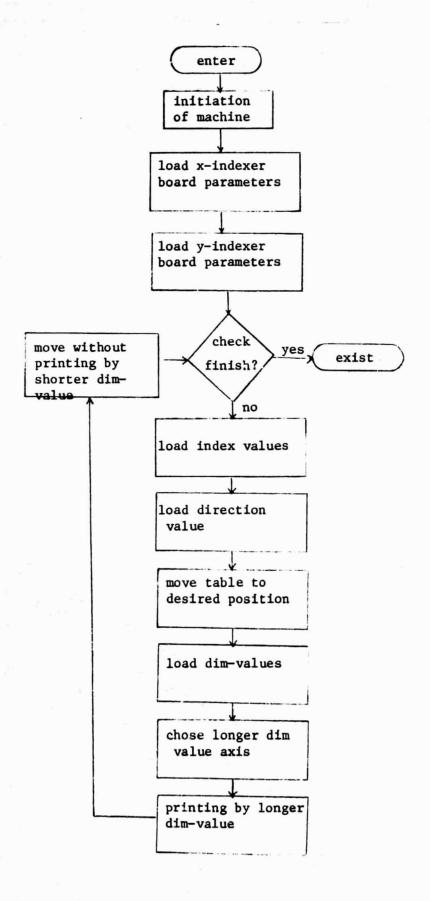

The programming which had to be added to complete this initialization process made use of the Superior Electric indexer board JOG command in order to move the table to the desired start position. The RST 5.5 and RST 6.5 input lines on the SCCS-85 microcomputer board are system interrupts. These two interrupts first had to be enabled and unmasked. The routine to accomplish initialization gives a JOG + command to the X-axis indexer board in an endless loop, moving the table along the X-axis toward the precision switch. When the switch is activated and the RST 5.5 interrupt line goes high, the endless JOG + loop is broken and

the X-axis motor is switched off. The routine called by the interrupt also immediately masks the 5.5 interrupt so that additional switch activations would be ignored. The RST 5.5 interrupt remains masked but the RST 6.5 interrupt must again be enabled because the entire interrupt system is disabled any time any interrupt is received. Similarly, a JOG + command is given repetitively to the Y-axis indexer board, moving the table along the Y-axis until the switch is activated. The RST 6.5 input goes high generating another system interrupt. This switches off the Y-axis stepping motor and, as did the 5.5, masks itself so that additional transitions of the RST 6.5 line are ignored. The positioning table is now set to an origin from which it will begin a print sequence. After receiving the last interrupt, the microprocessor proceeds with the main program.

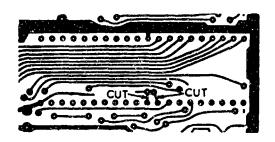

One other electronic modification was completed. There were several features built into the Siemens driver board which could not be used in this application. By eliminating this unneeded circuitry, the power requirements for the system could be reduced and the system further simplified. For these reasons, circuit traces on the board were cut and other modifications made so that power is applied only to the twelve pulse driver channels. The heater, temperature sense, wiper motor, and ink level sense lines to the ink jet head were removed, leaving only thirteen necessary lines to the ink head. Along with this change, the PRINTER READY l.e.d., the LOW INK l.e.d., and the MOTOR switch were discarded. With this change in place, the +5 volt supply is no longer needed on the driver board.

One last modification was made to the Siemens driver board. The original single turn potentiometers R1-R12, which control the amplitude of the output pulses from the 12 driver channels, were replaced with 15 turn potentiometers of the same 5000 ohm value so that more accurate control of the pulse amplitude could be accomplished.

#### 2.3 Ink Development

Lots of silver neodecanoate and bismuth 2-ethylhexanoate were synthesized for use in the first test ink. Further ink development studies must await completion of the initial mechanical and electronic design modifications.

#### PLANS

As described in the preceeding sections, the original prototype ink jet printing system has already undergone several changes. Many other design modifications will be made in the coming months. Most of these will be implemented in order to reduce the number of connections and minimize interwiring (hence improving reliability), improve serviceability, improve system printing accuracy and repeatability, and generally to meet future system goals. Many of the system improvements have been decided upon as a result of the design modification studies. Other changes, however, will be put in place as experience with the system and future plans dictate. Some of these design changes have already been partially implemented or, in some cases, put in place on somewhat of a

temporary basis for testing. Other modifications, particularly software modifications, will require some further investigation and will be made over many months.

During this quarter, some preliminary investigations were initiated to determine how a computer aided design routine might be integrated into the ink jet printing system. The final goal would be to be able to go directly from a circuit design created on a display terminal to the substrate. This would make the ink jet printing system a very valuable tool for circuit prototyping. It was found that there are several programs available within Purdue's Engineering Computer Network for laying out circuits on graphic terminals. Some of these programs may require additional equipment not currently available. This aspect will be looked into further. In any case, programs will have to be written so that the microcomputer board can receive and properly intempret the circuit information that would come from a graphics display terminal. This could require some basic restructuring of the entire main operating pro-Work will continue in order to determine what additional equipment might be needed for this process and what additional programming will be required.

In the area of mechanical modifications, several jobs have either been started or are being planned. It has already been stated that other modifications may have to be made to the ink pressure control and monitoring section after ink printing studies are started. However, along with the changes already made, one other aspect of the system will be changed in the very near future. Two new pinch valves have been ordered to replace the Sporlan solenoid valves currently being used in

the pressure control system. In the past, there had been a periodic problem due to the electrical noise (or line transients) being generated by the valves switching on and off. The new valves operate on 12 volts direct current instead of 115 VAC and operate on much less power. This should alleviate the noise problem encounted in the past. They, also, will avoid the two tubing connections at each valve since they operate by pinching the tube.

Another mechanical aspect of the system which will be improved is in the area of general system packaging. Some preliminary layout work has already been done. This change will involve almost all components of the system. This is being done primarily to minimize connections and interwiring between components, to improve system cooling, to make components more easily accessible, and to generally improve system operation. This change will include redesigning the power supply and relocating it. Additionally, all the components included in the positioning table drive system will be consolidated onto one rack-mountable panel. This panel will also include the two displays indicating table position. The system packaging changes will be an ongoing process ,most of which should be completed in the next several months.

Several electronic modifications are in the planning stages. The pulses to the piezoceramic drivers in the ink jet head must be able to be controlled accurately. The addition of the higher quality potentiometers to the Siemens driver board was a step in this direction. However, the input pulse to the Siemens driver board is largely esponsible for the shape of the output pulse so its pulse width must be precisely controlled. The pulse driver board (Fig. A4 of Appendix A) which is

composed of twelve identical circuits is responsible for generating these pulses. These twelve circuits are 'one-shot' multivibrators which use a simple external resistor-capacitor circuit for controlling their output pulse width. The Siemens Corporation specifies that the pulses to trigger the Siemens driver board have a pulse width of 22.5 µs. A check of the existing circuitry indicated a variation of 20 to 26 µs. To more accurately control this pulse width, the present SN74121N multivibrator I.C.'s will be replaced by dual precision monostable multivibrator I.C.'s. This will, first of all, reduce the chip count from twelve to six since these units have two complete circuits per package. More importantly, these integrated circuits use linear CMOS techniques allowing more precise control of output pulse width. This in combination with the external 15 turn potentiometers for initial calibration will dramatically improve the accuracy of the outputted pulse.

As part of the new packaging for the positioning table drive components, the existing LED displays will be replaced by new liquid crystal displays in order to reduce overall system power requirements. A new up/down counter and LCD display driver integrated circuit has been ordered to provide the correct drive signals to the displays. They will connect to the indexer boards in very much the same way as the displays do currently. Special bezels will be used to mount the new displays into the eighth inch aluminum rack panel.

As a means of planning for the future when an attempt will be made to use all twelve ink jet nozzles for printing, circuitry is being added now so that the nozzles can be turned on and off via the microprocessor. This will be accomplished by adding two octal data latches to the same circuit board which contains the new CMOS multivibrators. Three control lines and the eight data buss lines from the SCCS-85 microcomputer board will control these latches. Twelve manual switches will be included so that the nozzles may still be turned on manually. Light emitting diodes will probably be incorporated to give a visual indication of which nozzles are on. It should be pointed out that before all twelve nozzles can be utilized for printing, much more program development will be necessary.

Program development continues on a regular basis. Even though programs have been written for the nozzle triggering system and for the table initialization process, these programs may require additional work in order that these systems work in the most efficient and concise manner. Other areas requiring programming changes are being investigated. A program addition may be made to pattern data in such a way that the ink jet print head is moved away from the substrate after the print is completed. This will facilitate the removal of the substrate.

More work will be done in achieving the goal of much higher print speeds. This may involve a new degree of programming complexity up until now not needed. Currently the positioning table is being used at a base speed only. The Superior Electric indexer boards are capable of fairly high print speeds, but acceleration and deceleration must also be programmed into the system when higher speeds are used. The acceleration and deceleration parameters are entered into the indexer board in ASCII code as are other instructions. Nonetheless, a large amount of additional software development will be necessary before higher print speeds can be reached. Some preliminary testing routines are currently

being written and work will continue through the next quarter to accomplish this goal.

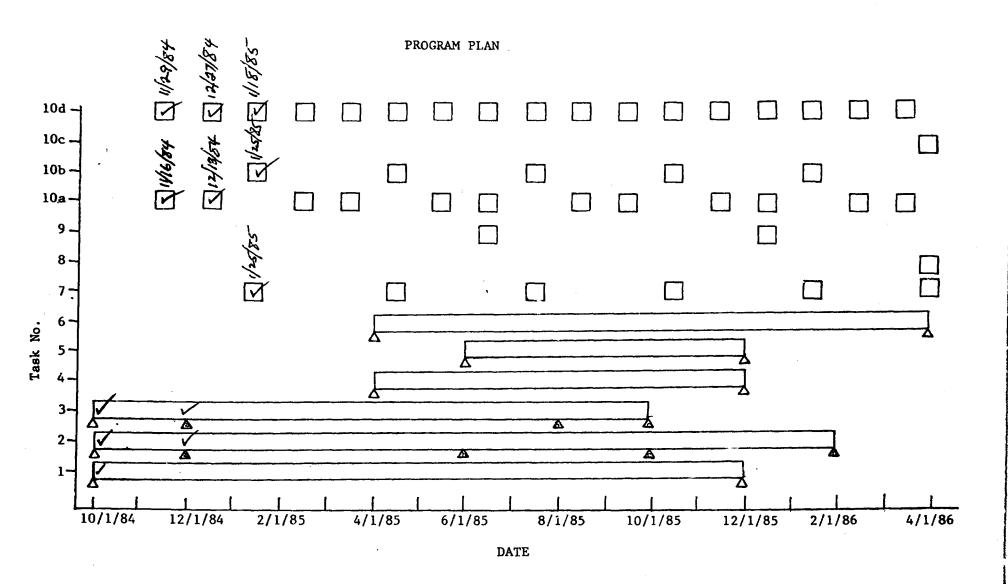

### 4. SCHEDULE

The description of tasks and the updated milestrue chart are attached.

#### LIST OF TASKS

- 1. Ink Development and Processing Studies

- 2. Electronic Modifications and Programming

- a. Design modification studies

- b. Electronic assembly

- c. Operational demonstration

- d. Computer software generation

- 3. Mechanical Modifications

- a. Design modification studies

- b. Mechanical assembly

- c. Operational demonstration

- 4. Film Thickness and Line Width Studies

- 5. Printing Speed Studies

- 6. Fabricating and Characterizing Cells

- Specifications

- 8. Data for Economic Evaluation

- 9. Personnel for Meetings

- 10. Documentation

- a. Monthly technical reports

- b. Quarterly technical reports

- c. Final technical report

- d. Monthly financial reports

### APPENDIX A

Documentation of the Turner Laboratory Ink Jet Printer

as of October 1, 1984

# TABLE OF CONTENTS

|    |                                             | Page |

|----|---------------------------------------------|------|

| 1. | INTRODUCTION                                | A.4  |

| 2. | INK JET PRINTING SYSTEM OVERVIEW            | A.5  |

| 3. | SCCS-85 MICROPROCESSOR SECTION              | A.10 |

|    | 3.1 SCCS-85 Microcomputer Section           | A.10 |

|    | 3.2 Downloading from Host Computer          | A.13 |

|    | 3.3 Joystick Control                        | A.14 |

| 4. | INVERTER BOARD                              | A.14 |

| 5. | INK JET DRIVE SECTION                       | A.17 |

|    | 5.1 Overview                                | A.17 |

|    | 5.2 Triggering and Control Circuits         | A.19 |

|    | 5.3 Pulse Driver Board                      | A.21 |

|    | 5.4 Siemens Driver Board                    | A.23 |

|    | 5.5 Siemens Pt80i Spray Head                | A.25 |

| 6. | X-Y POSITIONING TABLE SYSTEM                | A.27 |

|    | 6.1 Overview                                | A.27 |

|    | 6.2 Superior Electric Indexer Boards        | A.30 |

|    | 6.3 Superior Electric Driver Boards         | A.40 |

|    | 6.4 Design Components X-Y Positioning Table | A.43 |

|    | 6.5 Joystick Control of Table               | A.44 |

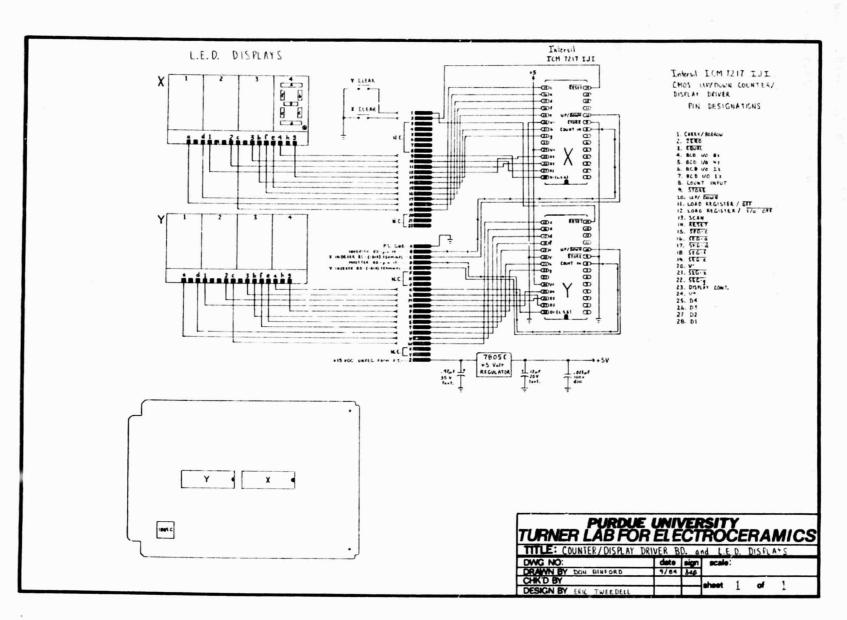

| 7. | L.E.D. DISPLAY SECTION                      | A.46 |

|    | 7.1 Overview                                | A.46 |

|    | 7.2 Counter/Display Driver Board            | A.48 |

|    | 7.3 L.E.D. Displays                         | A.51 |

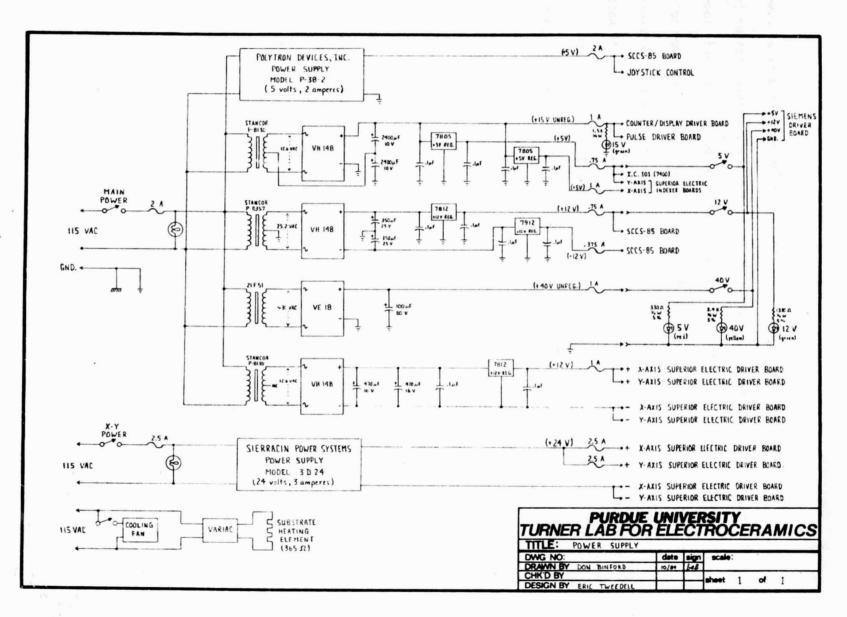

| ٥  | DOLIDA CUDALA CECATAN                       | A 52 |

|    |      |                                                | Page |

|----|------|------------------------------------------------|------|

|    | 8.1  | Overview                                       | A.52 |

|    | 8.2  | +15 Volt Unregulated Supply                    | A.55 |

|    | 8.3  | +40 Volt Unregulated Supply                    | A.55 |

|    | 8.4  | +5 Volt Supplies                               | A.56 |

|    | 8.5  | +12 and -12 Volt Supplies                      | A.57 |

| ,  | 8.6  | +12 Volt Superior Electric Driver Board Supply | A.57 |

|    | 8.7  | +24 Volt Supply                                | A.58 |

| 9. | INK  | SUPPLY AND PRESSURE CONTROL SECTION            | A.58 |

|    | 9.1  | Overview                                       | A.58 |

|    | 9.2  | Siemens Pt80i Head Modifications               | A.60 |

|    | 9.3  | Ink Pressure Control System                    | A.62 |

|    | 9.4  | Purge System                                   | A.63 |

|    | 9.5  | Ink Compositions                               | A.64 |

| 10 | . SO | PTWARE                                         | ۸ 66 |

#### 1. INTRODUCTION

There are many inherent advantages to using ink jet printing techniques on hybrid microcircuits. First of all, this process can easily be completely computer controlled allowing a higher degree of automation than now possible with conventional screening techniques. This would, in turn, yield a potential cost savings, greater repeatability and reliability, and the ability to move rapidly from initial design stages to circuit prototypes. Another major advantage of the ink jet printing process is better uniformity of the thickness of the deposited films since surface topography is no longer a factor in influencing film thickness. If circuit performance can be improved by varying the thickness of the films in various regions of the same circuit then this technique will allow one to accomplish that with relative ease.

There are many potential advantages to ink jet printing, but designing and implementing a workable system requires overcoming some significant problems. First of all, it should be pointed out that consideration of using this technique of printing was made possible by the development of metallo organic decomposition (MOD) inks since this process dictates the use of inks which do not contain particulates. However, for these MOD inks to be used with an ink jet spray head their viscosities had to be much lower than that required for screening and their surface tension was a much more critical parameter in this application. Additionally, the ink jet spray heads presently available were designed primarily for the printing of alphanumeric characters, not for printing the continuous, uniform patterns required for most hybrid

microcircuits. This meant that a commercially available head had to be modified. Other problems also had to be dealt with such as designing an ink supply system for the head which would provide the neccesary meniscus at the ink jet nozzles and also allow the MOD inks to be contained in an inert environment. Another complex task was coordinating the pulsing of the ink jet nozzles with the movement of an X-Y table directly below the ink jet head in order to print the required pattern on a substrate. Some progress has been made in this area but additional work will have to be done, particularly as an attempt is made to increase the printing speed. Some of the mentioned problems have now been resolved, but others will have to be investigated further and solutions found.

The existing system is described in this Appendix, including complete circuit diagrams and explanations, software documentation, and general operational aspects. The system has been described section section with most sections prefixed by a general overview of that portion of the system. There is also a discussion of a few of the problems that require additional investigation and study.

#### 2. INK JET PRINTING SYSTEM OVERVIEW

The ink jet printing system, although having limitations in its current state of development, is capable of printing well defined patterns onto substrates using MOD inks. The ink jet printer used in this study was a Siemens Pt80i head which has 12 nozzles (76 µm diameter) arranged in two staggered rows of six. Each nozzle has its own piezoelectric driver making this head a drop-on-demand type. Ink is

supplied to the head under slight static vacuum so that flow is resisted by the surface tension of the meniscus at the nozzle. A droplet is ejected by means of a pressure wave generated by an impulse from the piezoelectric driver. Substrates were mounted on an X-Y table which moved in 25 µm steps in response to input pulses. The desired patterns were generated by programming the motion of the table and the firing of the jets. So far the system has been used only at reasonably slow print rates (substrate velocities between .00254 and .01016 meters per second) although higher rates are possible. In its simplest form, the system consists of two major blocks. The first section contains all the necessary components to fire and control the ink jet nozzles, and the other section is responsible for the movement of the X-Y positioning table below those nozzles. In actuality, of course, the system is much more A SCCS-85 microcomputer board has been integrated into the complex. system. Its function is basically to take operational and circuit pattern data given to it via its RS-232 input, process that data, and then provide the proper signals to the two above mentioned sections so that they will work together in a manner which will print the desired pattern on the substrate.

All the major sections of the system are indicated in Fig. Al. A manual triggering circuit was provided as a means of manually firing the ink jet nozzles for initial testing purposes. Most of the testing was done using an external oscillator as the triggering source. Also, a joystick control was included in the system for manually controlling the table even though most of the experimental work was done with the table in an automatic control mode. Two four digit 1.e.d. displays were

Figure A.1 Ink Jet Printing System Block Diagram.

incorporated into the system to give a visual indication of table position. Each unit represents one motor step or about 25 µm. Direction and count information for the X and Y channels of the counter/display driver board comes from the X-axis or Y-axis Superior Electric indexer boards respectively. All of these sections mentioned so far, although important, are not an integral part of the main operating system.

At the heart of the operating system is the SCCS-85 microcomputer board. The main operating program and pattern data are downloaded into the microprocessor board via the RS-232 input from a host computer sys-The SCCS-85 then provides signals to the ink jet drive section and the X-Y table positioning section. In the first case, the SCCS-85 provides only a single control line which enables a gate on the inverter board. This allows the external oscillator triggering signals to pass on to the ink jet drive and control circuits. There, one or more tracks of the ink jet spray head are selected and the triggering signals then routed on to the appropriate drive channels. The drive electronics provide the necessary pulses to fire the corresponding piezoelectric elements in the Siemens head. Thus the droplets of ink are ejected onto the substrate. In the case of the table control section, the SCCS-85 provides 10 lines of information, via the inverter board, to the two Superior Electric indexer boards. The 8-bit parallel data bus goes to both boards, then there is a single enable line to each board. Additionally, there are two lines back to the SCCS-85 (again via the inverter board) from the indexer boards to provide proper sequencing of signals. Output signals from the X-axis and Y-axis indexer boards provide the necessary information to the respective X and Y axis Superior Electric driver

boards. These then, in turn, provide the drive signals to the Design Components positioning table. It is also the indexer boards which provide the position information to the l.e.d. displays.

With all these sections working together correctly, a preprogrammed pattern can be printed onto a substrate. The actual operation of the system to accomplish this is fairly simple. A 10 cm square brass block which is mounted on the X-Y table is preheated to somewhere between 30 and 35°C by a heating element mounted in the block and controlled by a variable transformer. The substrate is positioned in a recessed inner region of the block and held in place by a vacuum applied to a hole beneath the substrate. The table is manually positioned to a predetermined start point in respect to the ink jet head. The MOD ink is put in the ink supply system and the supply system checked for proper operation. An oscillator is connected to the external oscillator input and adjusted for the correct triggering signal. All power supply switches are turned on, the MAN/EXT switch is set to EXT, the ENABLE and MOTOR switches are turned on, one of the twelve ink jet track switches is turned on, and the SCCS-85 is reset. The microprocessor is instructed to load and the main operational program is downloaded from the host computer. The micro is again instructed to load and the pattern program is downloaded. A final command to the microprocessor starts the program running and the circuit pattern is printed onto the substrate. program runs the l.e.d. displays track the table movement. Once the printing stops, the vacuum is switched off and the substrate removed and fired as necessary.

It is hoped that the above description has provided the reader with a general understanding of the ink jet printing system that was developed in the Turner Laboratory. The sections which follow describe in more detail the major blocks of the system. There is also a description and listing of the software for the SCCS-85 board.

#### 3. SCCS-85 MICROPROCESSOR SECTION

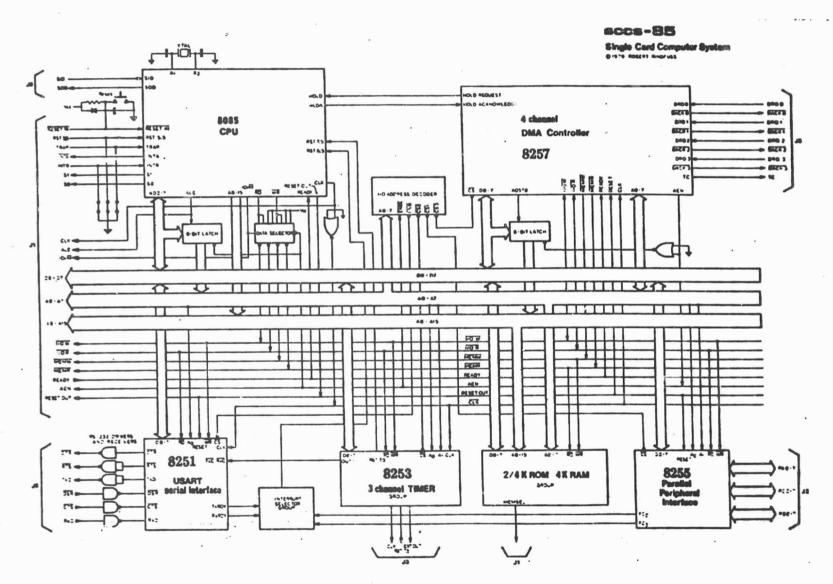

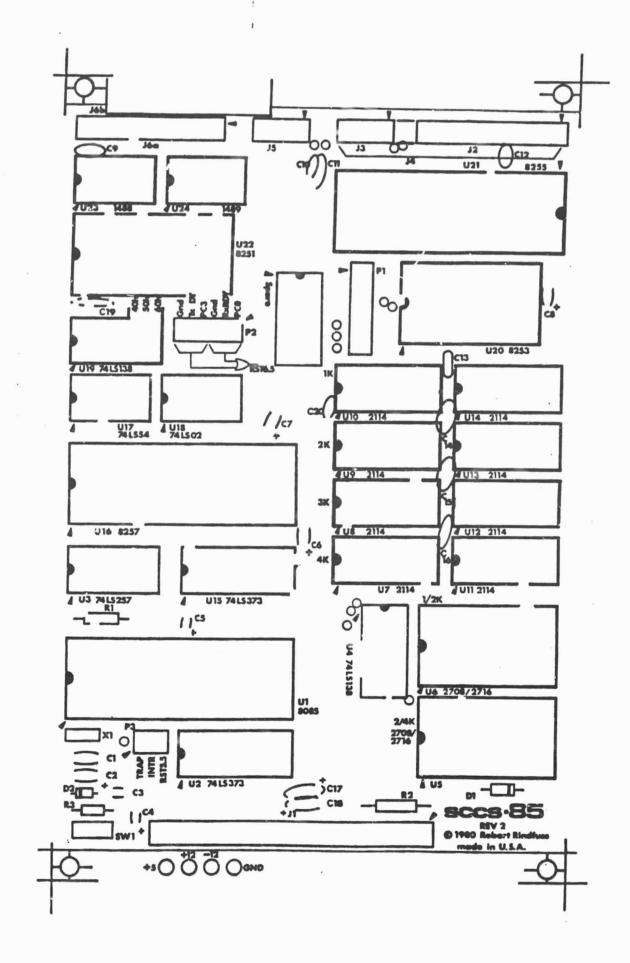

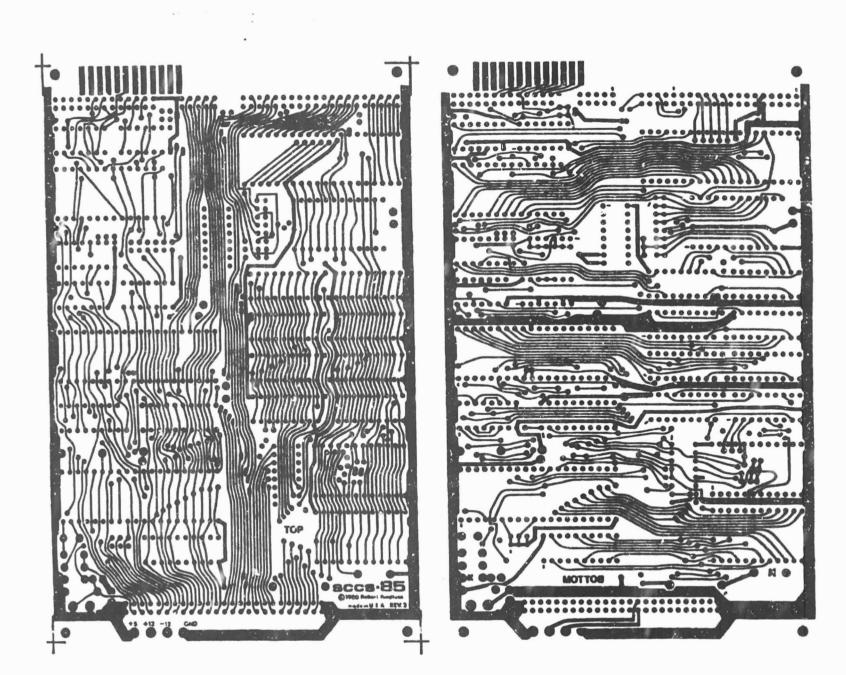

### 3.1 SCCS-85 Microcomputer Board

The SCCS-85 is a very versatile Intel 8085-based microcomputer system contained on a 11.43 cm X 17.78 cm board. Its designed-in flexibility allows it to be used in a wide variety of control applications. With no modifications at all, it is configured to operate as a small computer communicating via RS-232 with a user supplied terminal. Up to four kilobytes of RAM (random access memory) may be installed on the board itself and a memory capacity of up to 65K bytes is possible by extending the SCCS-85 bus to additional cards.

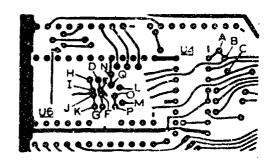

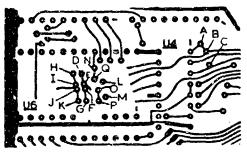

The SCCS-85 circuit board is a unit designed by Robert Rindfuss that was purchased locally. It is revision 2 of the original circuit board design. The integrated circuits, I.C. sockets, connectors, and other miscellaneous electronic components were purchased from various suppliers and mounted on the circuit board according to its included instructions. Specific modifications must be made to the circuit board according to the user's individual needs. Most of these are accomplished by cutting circuit board traces and/ or jumpering pins or specified feed through terminals.

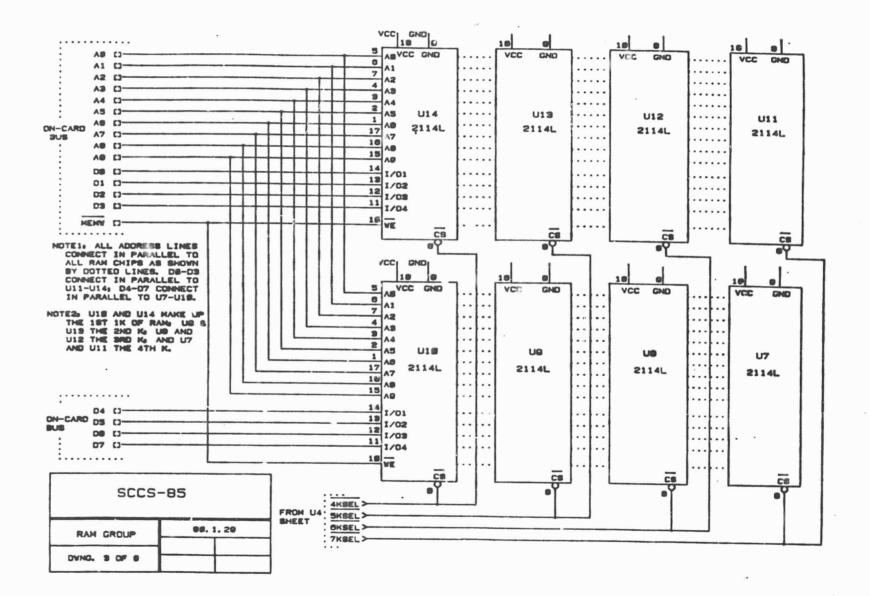

This microcomputer board is divided into seven functional groups.

They are the following:

- 1. CPU (central processing unit) group

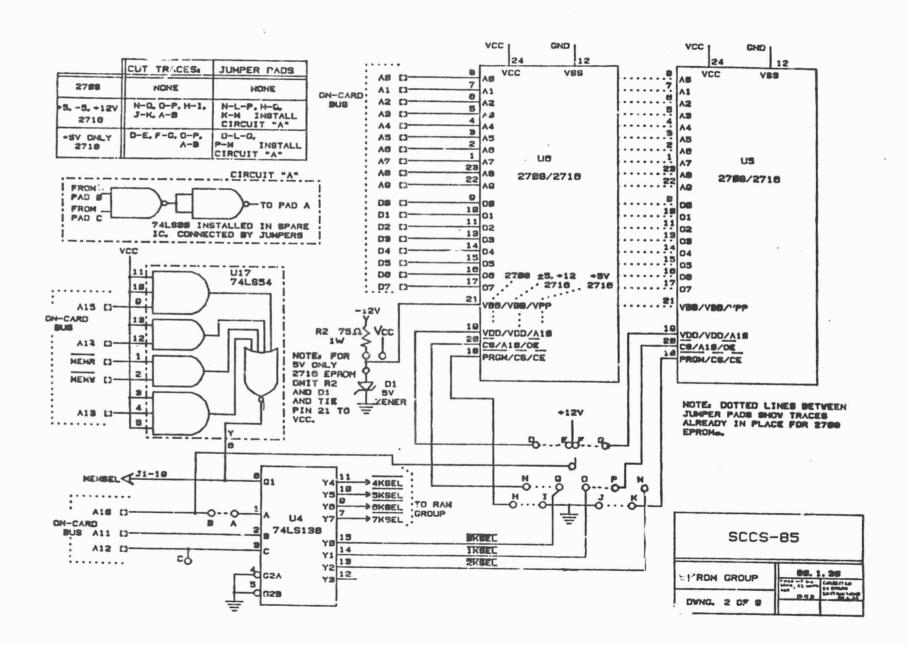

- 2. ROM (read only memory) group

- 3. RAM (random access memory) group

- 4. SERIAL IO (input/output) group

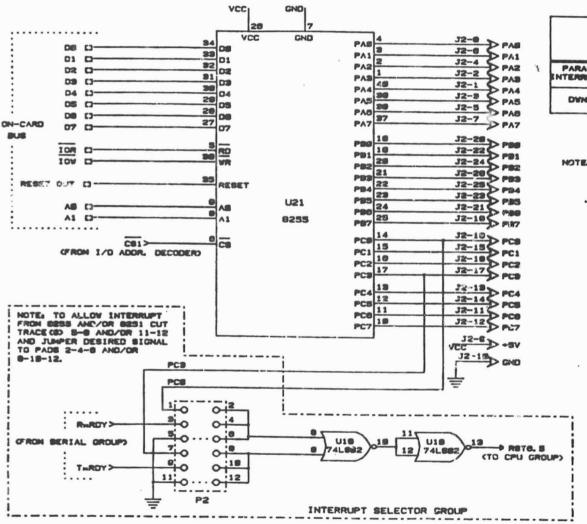

- 5. PARALLEL 10 group

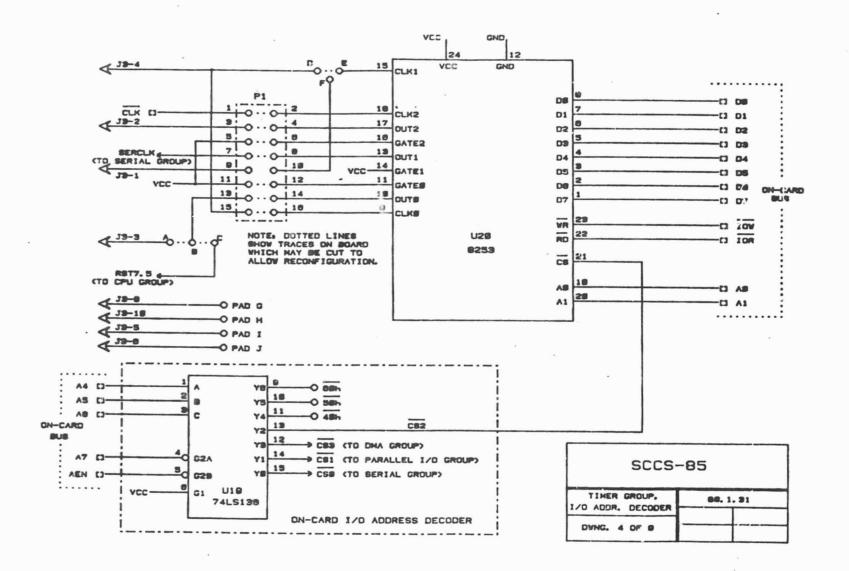

- 6. TIMER group

- 7. DMA (direct memory access) group

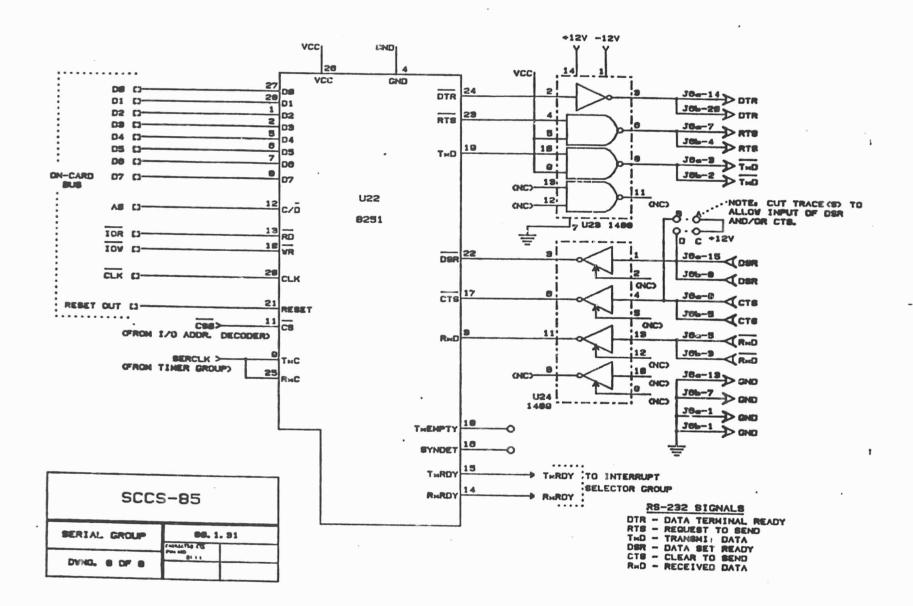

The CPU, RAM, and ROM groups are required for the operation of any system, however the remaining groups are optional and need only be present on the board if the application requires it. For the ink jet printing system, all the above blocks were required except the DMA group. The two integrated circuits necessary for DMA were not purchased and are not present on the ink jet printing system's SCCS-85 board. In the case of the ROM group, a single NEC D2716 EPROM, giving 2K of ROM, is being used, leaving I.C. location U5 free for expansion to 4K as required. The board was reconfigured to accept the 2716 EPROM. The 2K of EPROM (2048 bytes) holds the control and monitor programs. The 4K of RAM short term memory holds graphic data downloaded from the host computer and also provides a scratch pad work space for the monitor and control USART programs. The SERIAL IO group contains the synchronous/asynchronous receiver transmitter) through which all communication and data transfer takes place via a standard RS232 serial link. Outputs to the indexer boards and the ink jet head enable circuitry, and inputs for 'handshaking' lines are sent and received in the PARALLEL I/O

group. The TIMER group is being used to provide the correct timing to the USART and, in the future, may be used to provide the triggering signals to the ink jet head circuitry.

A complete copy of the SCCS-85 (revision 2) User's Manual is included as Appendix Al. Included in it is both a component list for the board and also the instructions for mounting the components. Additionally, necessary modifications as required by the user are described in detail and complete circuit daigrams are provided. As a means of clarification, however, specific modifications and parts used in this application of the microcomputer board are listed below:

- 1. A 4 MHz crystal is used so the 8085's clock frequency is 2 MHz.

- 2. I.C. locations U5, U15, and U16 are not being used.

- 3. A single NEC D2716 EPROM chip is being used in the ROM group section. It is a single voltage (+5V) I.C. so the modification described on pages 12 and 13 of the User's Manual has been performed.

- 4. The TRAP interrupt input (pin 6 of the 8085) is being used for enabling the 'joystick'. On the SCCS-85 the TRAP input is normally pulled low so to use this feature the trace between P3-1 and P3-2 (CPU schematic, User's Manual) had to be cut.

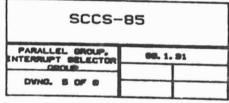

- 5. For proper operation of the RS232 serial data input the following modification was made done (refer to the Serial Group schematic, User's Manual). The trace between C and D was cut so that pin 1 of the 1489 I.C. at location U24 is no longer pulled up to +12 volts.

The connection between pin 3 of the 1489 and pin 22 of the 8251 was broken and pin 3 and pin 22 of the 8251 was jumpered.

6. Two connectors were installed on the circuit board at locations J2 and J6a. Each of these is a 26-pin double row header made by A P Products, Inc. (part # AP 923863-R).

### 3.2 Downloading from Host Computer

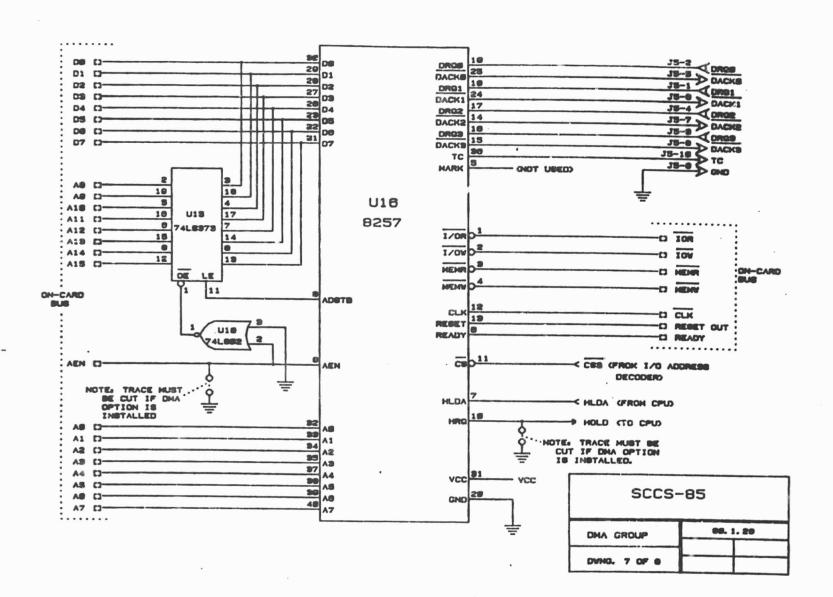

As previously stated, the control and monitor program for the 8085 is contained in the 2716 EPROM on the SCCS-85 circuit board. However, the main operating program and any pattern programs must be downloaded into the SCCS-85 board from a host computer. This is accomplished through the RS232 serial data input which was incorporated into the design of the board. There is a standard 25-pin D connector mounted in the equipment cabinet and it is wired in the following manner to the SCCS-85 board:

Ground J6a-pin 1

Transmit J6a-pin 3

Receive J6a-pin 5

A switch box assembly is used to provide all necessary switching between the host computer, the SCCS-85 board, and a terminal. This makes it possible for the terminal to communicate with either the host computer or with the SCCS-85 board. It also allows the host computer to transmit information directly to the SCCS-85 board, i.e. it allows 'downloading' from the host to the microprocessor. This information is stored in the RAM group on the SCCS-85 board.

### 3.3 Joystick Control

In initial design stages, the X-Y table was only controllable through the use of a manually operated 'joystick'. In its current state of development, the ink jet printing system uses the SCCS-85 microcomputer board to control the positioning table. After this system was implemented, it was still felt that some means of manually positioning the table should be provided so that the table could be positioned to the required start position prior to a print run.

For this reason, a program was written and made a part of the main operating program for the system. Pressing the JOYSTICK ENABLE button takes the TRAP interrupt on the SCCS-85 board momentarily high, vectoring the microprocessor to the joystick program. Once this has been done, the joystick control operates the table in the manner one would expect with this exception. Only movement parallel to the X or Y axis is possible. This, by the way, is also true in the computer controlled mode. All information for manual joystick control enters the Parallel I/O section of the SCCS-85 board via J2 pins 20, 22, 24, and 26.

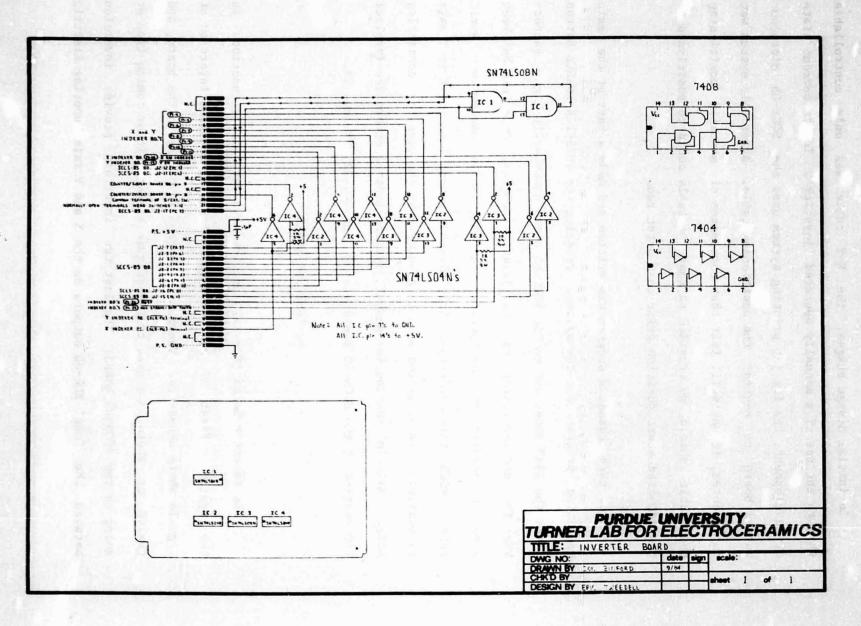

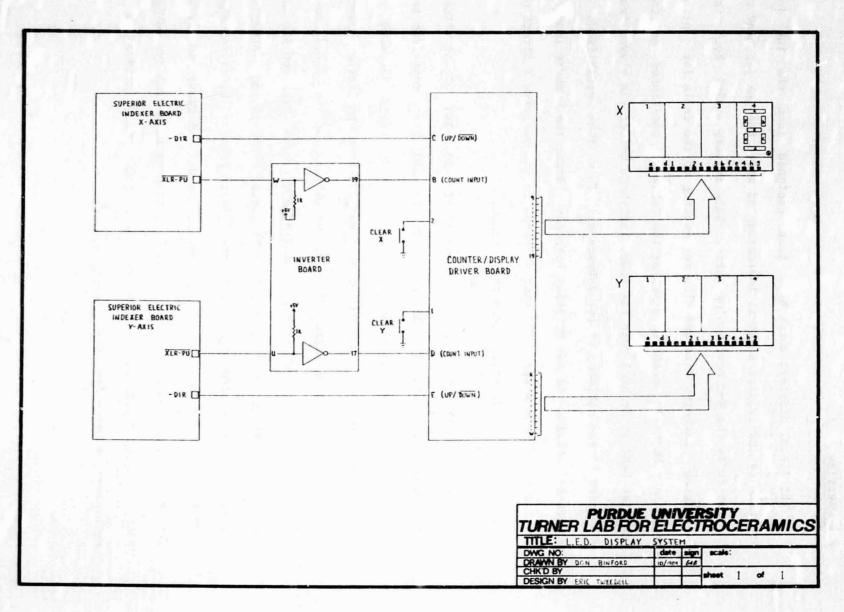

#### 4. INVERTER BOARD

The inverter board (Fig. A2) provides two very simple functions in the system. First of all and most obvious, it provides inversion of signals where necessary. There are fourteen inverters on the board, and twelve of these are used to reconfigure signals either coming from or going to the SCCS-85 board. The last two inverters provide inversion between the 'not' XLR-PU outputs on the X and Y axis Superior Electric

Figure A.2 Inverter Board.

indexer boards and the count inputs on the Counter/Display Driver board. Secondly, the inverter board contains a SN74LSO8N quad-AND integrated circuit. Two sections of this IC are used to provide a gating function for the triggering signal for the ink jet drive and control section. This gate allows the SCCS-85 to enable this trigger.

The inverter board is a 'Vector' #3677-2 circuit board (11.4 cm X 16.5 cm) with a 22-pin edge connector. Mounted on the board is one SN74LSO8N quad-AND IC and three SN74LSO4N hex inverter IC's. Referring to Fig. A2, it is shown that the power supply ground enters the board on pin Z while the +5 volt line is applied at pin A. Pins 20-22 are the input, the output, and the enable lines for the gate IC 1. Two AND gates are used in order to provide proper isolation between input and The trigger signal from the trigger select switch MAN/EXT goes to pin 9 of IC 1. If pins 10 and 13 of IC 1 are high due to an emable signal from the SCCS-85 board, then the trigger signal passes on through from pin 9 to pin 8. Since pin 13 is also high, the signal continues from pin 12 to pin 11 and exits the board at pin 21. Eight inverters are used to invert the data line from the SCCS-85 board to the two indexer boards. The output port (PA 0-7) signals enter the board at pins M-D respectively and exit the board at pins 11-4 respectively. Pins 4-11 connect to Pl-4 through Pl-11 on the Superior Electric indexer boards. Two other signals from PC 0 and PC 1 on the SCCS-85 board are routed to pins N and P. They are inverted and exit at pins 12 and 13 to continue on to P1-16 of the X-axis indexer board and to P1-15 of the Yaxis indexer board respectively. P1-26 ('not' BUSY) lines and P1-37 ('not' AUX STROBE/DATA TAKEN) lines from both indexer boards enter the inverter board at pins R and S. These inverted signals exit at pins 14 and 15 and return information to the SCCS-85 board (PC 7 and PC 6). These two inverters have 1000 ohm pull-up resisters on their inputs. Finally, the 'not' XLR-PU signals from the two indexer boards are input-ted at pins U and W and exit at pins 17 and 19 to provide count information to the corresponding channel of the Counter/Display Driver board. These two inverters also have 1000 ohm resistors from their inputs up to the +5 volt supply.

Even though this board is very simple in its function, its input and output pin number designations can be confusing as described above. For that reason, it is suggested that Figs. A5 and A6 be referred to for clarifying signal flow in and out of the board. On these two figures all fourteen inverters are shown. Figure A3 may also be referred to clarify the function of the gate circuit on this board.

## 5.INK JET DRIVE SECTION

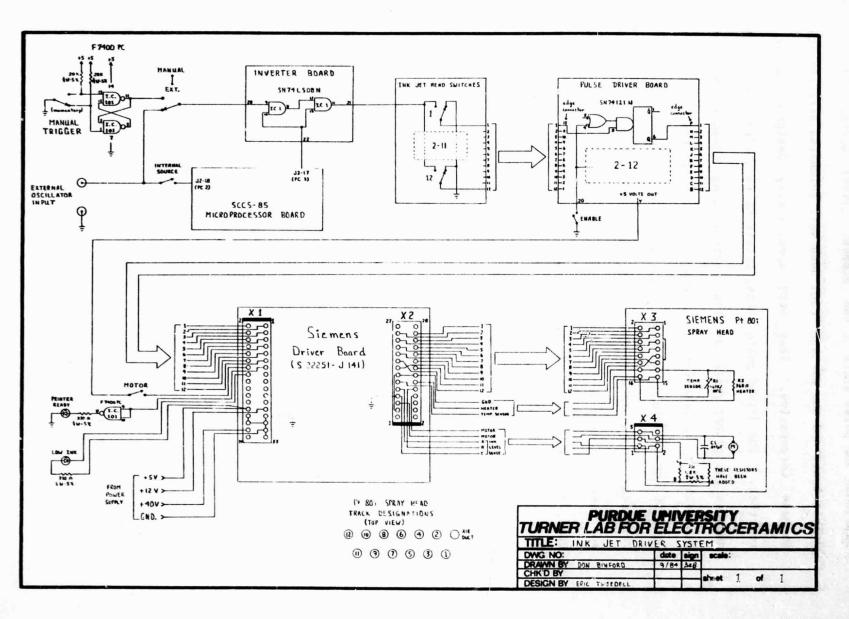

#### 5.1 Overview

The ink jet driver section can be summarized very simply. Figure A3 explains the flow from the triggering source to the Siemens ink jet spray head. The triggering signal, which must be enabled by the SCCS-85 microcomputer board, leaves the inverter board and is routed on to the ink jet head switch assembly. There it is routed to one or more channels of the Pulse Driver board. It should be noted here that most of the testing that has been done was done using only one ink jet nozzle at a time. The Pulse Driver board provides triggering signals of specific

Figure A.3 Ink Jet Driver System.

amplitude and pulse width to the Siemens driver board. The Siemens driver board and the Siemens Pt80i head were purchased directly from the Siemens Corporation. They were specifically designed to be used together. The driver board, after receiving the correct trigger pulse, outputs the proper pulse on the corresponding channel to fire the piezoelectric driver for the corresponding ink jet nozzle. Thus a droplet of ink is ejected onto the substrate. This process continues at a rate equal to the rate of the trigger pulses as long as the microprocessor keeps the gate on the inverter board enabled. Hence, assuming that the X-Y table is moving, a series of ink droplets (forming a line) are printed onto the substrate.

# 5.2 Triggering and Control Circuits

Triggering is possible from either of two sources. IC 101 (F7400PC) is a quad 2-input NAND gate. Two of these gates have been connected as indicated in Figure A3 to form a 'bounceless' switch. The MANUAL TRIGGER switch is a momentary single-pole double-throw device. Pin 11 of IC 1 is normally low. It goes high at the instant the normally open terminal of the MANUAL TRIGGER switch is taken to ground and stays high until the normally open terminal of the switch goes high again (when the button is released). It is the positive-going portion of this signal which is the actual triggering mechanism. Triggering may also come from an external source connected to front panel banana jacks. A Hewlett Packard model 3310A function generator was used for this purpose. Several different waveforms and amplitudes were investigated but it was found that a squarewave with an amplitude of about 5 volts pro-

vided proper triggering. The frequency of the external oscillator had to be adjusted according to the velocity of the positioning table since the relationship of these two variables (and actually several others) affect many characteristics of the line printed. Most tests were conducted using table speeds of .00254, .00508, or .01016 meters per second. These speeds correspond to motor step frequencies of 100, 200, or 400 steps per second respectively. Some experimental work was done concerning the relationship between the trigger frequency and the table velocity. A formula relating the two was found which seemed to produce, in most cases, smooth line patterns on the substrates assuming that a median nozzle to substrate spacing of about 300 µm was maintained. If the table velocity (expressed in meters per second) is divided by .0001 meter per cycle then the value obtained in hertz (cycles per second) is the oscillator frequency which will produce the desired effect. more simply, the table motor step frequency divided by four will yield the required oscillator frequency. The MANUAL/EXT trigger select switch was provided to select between the two above trigger sources.

The trigger leaves the common terminal of the MANUAL/EXT switch and flows through the gate on the inverter board as described in the inverter section. From pin 21 of the inverter board the signal travels on to the normally open terminals of the twelve ink jet head switches. These twelve single-pole double-throw switches either ground the corresponding input on the Pulse Driver board or route the trigger signal on to that channel. These switch numbers indicate the track number on the ink jet spray head as indicated in the lower portion of Fig. A3

The INTERNAL SOURCE switch is not presently being used but has been provided for future development. Eventually, it is hoped that the necessary triggering signals will come from the SCCS-85 board. Additional software development is necessary to provide this feature.

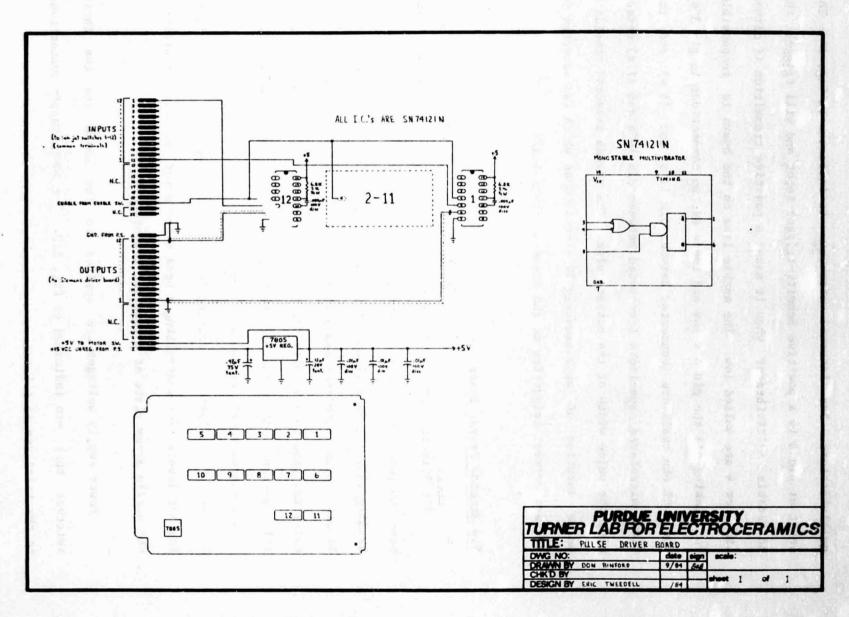

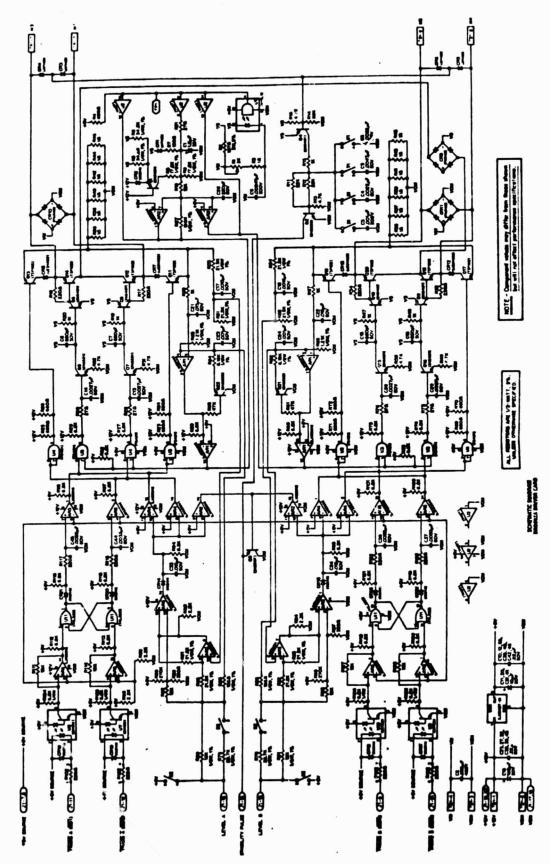

## 5.3 Pulse Driver Board

The pulse driver board's function is to provide the Siemens driver board with triggering pulses of definite pulse duration and amplitude. It assures that the pulses triggering the Siemens board are independent of the amplitude and duration of the triggering pulses coming either from the 'bounceless' switch or the external oscillator.

This board, shown schematically in Fig. A4, is a 12 channel unit built on a 'Vector' #3677-2 circuit board (11.4 cm X 16.5 cm) with a 22-pin edge connector. It is comprised of 12 SN74121N integrated circuits which are monostable multivibrators in 14 pin dual in-line packages. The power supply ground is at pin A and +15 unregulated volts come in at pin Z. There is 7805 +5 volt regulator on the board to provide the necessary supply voltage to the IC's. There is a +5 volt line leaving the board at pin Y which supplies +5 volts to one side of the MOTOR switch. This connection is indicated in Fig. A3. A switched ground (from the front panel ENABLE switch) enters the board at pin 20 to enable the 12 multivibrators. The inputs to the board (from the 12 ink jet head switches) are at pins 1-12 but in an opposite order in terms of track numbers. The pulses exit this board at pins P-B. The output lines from the IC's have been shielded as indicated in Fig. A4 to avoid 'crosstalk' and noise problems.

Figure A.4 Pulse Driver Board.

The SN74121N IC's used on this board are monolithic TTL monostable multivibrators. The internal structure is indicated on Fig. A4. The input at pin 5 is a positive Schmitt-trigger input and will trigger the monostable multivibrator when it makes a positive transition if either pin 3 or 4 are pulled low. The enable line on the board is responsible for taking all the pin 4's low and there are no connections to pin 3's. The 6.8K ohm resistors (connected between pin 11's and 14's) and the 0.005 microfarad capacitors (connected between pin 10's and 11's) determine the pulse width of the output pulse. The values selected provide a pulse duration of approximately 24 microseconds which was selected to achieve correct triggering at the Siemens driver board.

### 5.4 Siemens Driver Board

The Siemens Driver board was purchased directly from the Siemens Corporation. Their identification number for the board is S22251-J141. It is a circuit board approximately 14 cm square with a 34-pin input connector and a 28-pin output connector. It was specifically designed to work with the Siemens Pt80i spray head that is used in this system. Its major purpose is providing the correct drive signals to the piezoelectric elements in the head. Other circuitry has been included on the board for driving led status display lines, for monitoring ink levels, for controlling a head wiper motor, and for maintaining the nozzle array plate at a constant temperature.

Power supply voltages are applied to the board via the three switches that are indicated on Fig. AlO. The power supply connections to the board are as follows:

Ground X1 pins 27-31 and 33

+5 volts X1 pin 26

+12 volts X1 pin 25

+40 volts unreg. X1 pin 32

The inputs to the board are on pins 1-12 of X1 but note (Fig. A3) that track numbers do not correspond to pin numbers. The same holds true in the case of the outputs which are at X2 pins 15-26. Power supply ground is connected to X2 pins 3, 7, 13, and 14. This ground exits the board at X2 pin 14 to provide the ground reference at the ink jet spray head.

The status display lines are being used to drive the PRINTER READY and LOW INK led's. These lines exit the board at Xl pin 15 and 16 respectively. The PRINTER READY led circuit includes one NAND-gate section of IC 101. It serves to invert the pin 15 signal and drive the led. Three 6.8K ohm resistors have been added on the ink level sense terminals of the ink jet head, as shown on Fig. A3, to simulate the presence of ink to the board. This has been done because the board checks for ink presence before operating. Ink level sense lines leave the Siemens driver board at X2 pins 7, 9, and 10. Due to the addition of these resistors, the LOW INK led is never on except momentarily during power up. The motorized head wiping system which is incorporated into the Siemens units is not currently being used in this application. The actual wiping mechanism was removed but, otherwise, the system has been retained. The switched +5 volts from the MOTOR switch enters the board at X1 pin 14. The motor drive lines are at X2 pins 5 and 8. MOTOR switch must be on in order to enable the driver channels of the Siemens board. The nozzle array plate heating system consists of a heater resistor and a temperature sensor in the ink jet head and the necessary control and drive electronics on the Siemens driver board. The temperature sensor and the heater resistor are connected to X2 pins 11 and 12. It was found that the array plate heating system tended to dry the xylene ink solution so it was defeated.

As stated before, the major function of the Siemens driver board !s to provide the necessary signals to fire the ink jet piezoelectric drivers. There are twelve identical channels on the board for that purpose. Each channel includes an amplitude adjustment potentiometer for fine tuning the output pulses. These twelve controls are located in a line along the side of the board opposite to the Xl input connector and are screwdriver adjustable. They provide an output amplitude range from about 125 to 300 volts peak to peak. It was found through experimentation that output pulses need to be somewhere in the range of 150 to 250 volts to properly drive the piezoelectric transducers. The necessary amplitude will be dependent on the pressure in the ink supply bottle, the ink viscosity, and other related parameters. The pulse width of these output pulses is about 30 microseconds. The exact width is difficult to specify due to the non-square nature of the pulse.

#### 5.5 Siemens Pt80i Spray Head

The Siemens Pt80i ink jet spray head is a drop-on-demand type head with 12 nozzles arranged in two vertical rows. The diameter of each nozzle is  $76 \, \mu m$ . Each ink jet channel is concentrically enclosed by a piezoceramic transducer tube. Silver films on the inner and outer surfaces of the tubes serve as electrodes for applying the electric field.

Ink droplets are ejected from the nozzles by momentarily applying an electric field to these transducers. The nozzles that are pulsed are determined by the input signals to the Siemens driver board as described above. The unit, as shipped from Siemens, was designed to print characters using a 12-by-9 dot format. The head in conjunction with its matching driver board was capable of printing up to 300 characters per second.

For th's application specific requirements in an ink jet head had to be met which required that the Siemens head be modified in several ways. The unit was designed, originally, such that ink was ejected from the nozzles in the horizontal plane. Also, a collapsible bladder containing the ink was an integral part of the unit. Along with the ink supply were features to monitor the ink level, wipe the nozzle array plate, and maintain the nozzle array plate at a constant temperature. In this application of the ink jet spray head, most of these features were either not needed or simply could not be used due to other con-Since the substrate needed to be mounted on a positioning table, the ink droplets from the head had to be ejected in the vertical plane. This, alone, would have eliminated using the existing ink supply since the relative position of the ink jet head to the ink supply is responsible for the static vacuum applied to the ink jet nozzles. It is this static vecuum which is critical to the correct operation of this However, using MOD inks in a xylene solution drop-ch-demand system. dictated operating in a closed inert atmosphere which was not possible with the existing head and ink supply system. A new mounting system for the head was devised so that the ink was ejected down onto the substrate. The mounting system includes a means of adjusting the head to substrate distance. Although further studies will be necessary to determine an absolute optimum nozzle to substrate spacing, 300 µm has proven to provide good line definition and so was used for recent testing. A short length of Teflon tubing was attached to the head and connected to a new ink supply arrangement. The specifics of the ink supply system will be discussed in Section 9. The nozzle array plate wiping feature was deemed not necessary and so the actual wiping arm mechanism was removed. The ink level monitoring feature could no longer be used and was overridden. It was also fou d that the array plate heating system tended to dry the xylene ink solution so it was defeated.

The modified head and the Design Components positioning table were mounted on an aluminum plate having dimensions of approximately 1.3 cm X 35.5 cm X 45.5 cm. Connections to the head from the electronics cabinet is via ribbon cable. The table motors, discussed in Section 6, are connected to the cabinet with 'Jones' style 8-pin connectors. A vertical rod is also mounted on this plate for supporting the new ink supply bottle (Section 9).

#### 6. X-Y POSITIONING TABLE SYSTEM

#### 6.1 Overview

The complete X-Y table positioning system is shown in Fig. A5. The basic system consists of two identical channels, one for movement in the X direction and one for movement in the Y direction, both of which are controlled by the SCCS-85 microcomputer board. A 'joystick' control is

Figure A.5 X-Y Table Positioning System.

also connected to the SCCS-85 board to provide a means of manually moving the table. The inverter board (as described in Section 4) is a part of the system simply to provide inversion of any lines leaving or entering the SCCS-85 board. A large portion of the table positioning system has been purchased commercially because high quality units meeting all our requirements were readily available. The actual positioning table is a model LC-22 from Design Components, Inc. It is a X-Y positioning table with a maximum travel in each direction of 5.08 centimeters. The stepping motors which are part of the positioning table are 200 steps per revolution units made by the Superior Electric Co. Each channel consists of two boards, an IDD008 indexer board and a DRD002A driver board. These boards are part of a line of modules for stepping motor control made by the Superior Electric Company which have the trademark name of 'MODULYNX'.

All move information enters the indexer boards on the 8-bit parallel data line in ASCII format from the SCCS-85 board. The number of steps to be taken and the direction is encoded in the data. Four other lines connect the microprocessor board and the two indexer boards as seen in Fig. A5. These four lines are used in a simple 'handshaking' routine to correctly sequence signals.

Manual control of table movement is accomplished by pressing the JOYSTICK ENABLE button and then using the 'joystick' control to move the table as desired. The 'joystick' function is accomplished in a program that has been appended to the main program as discussed in Section 10. When the JOYSTICK ENABLE button is pressed an interrupt vectors the microprocessor to this 'joystick' program.

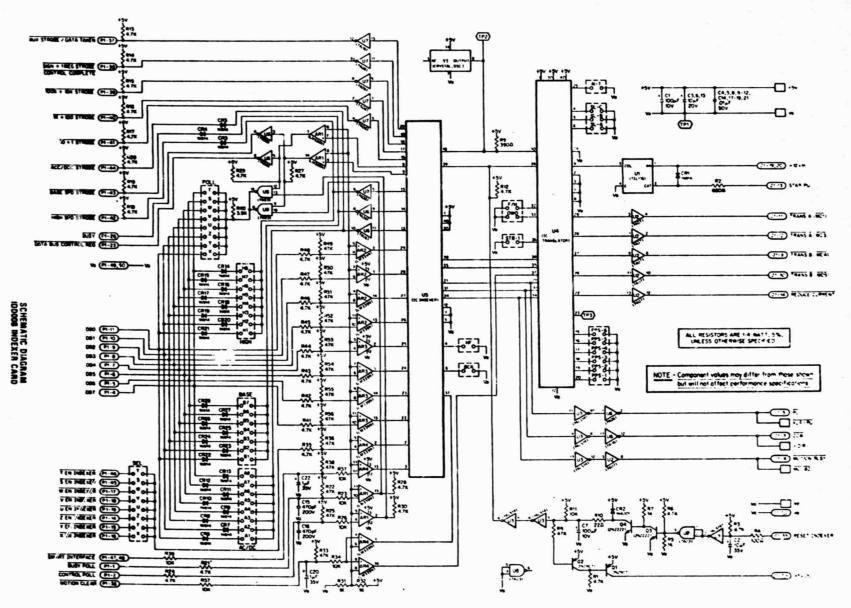

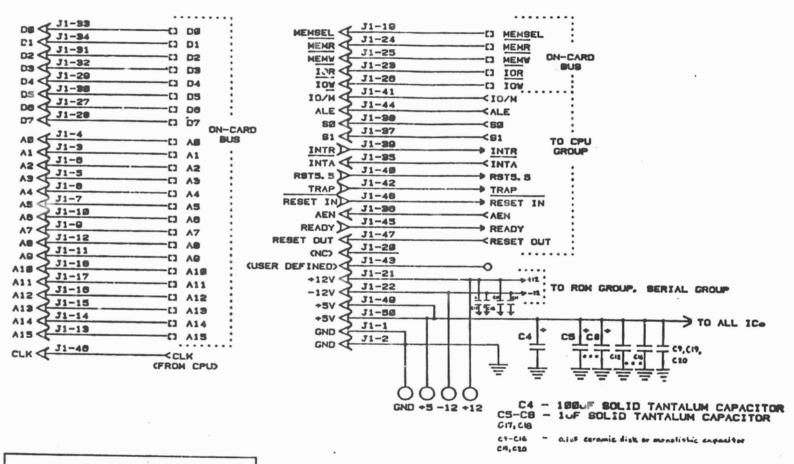

## 6.2 Superior Electric Indexer Boards

The two indexer boards used in this system are IDD008's made by the Superior Electric Co. They have been specifically designed to be used with the DRD002A driver boards. They are 19.6 cm X 22.4 cm circuit boards having 50 pin edge connectors for input signals and 20 pin edge connectors for connections to the DRD002A driver boards. Robinson Nugent, Inc. edge connectors were used for these connections. They were obtained from Digi-Key Corporation and are type R500. In addition to these two edge connectors there are six spade lug terminals along the same edge of the card as J1. Three of these are for grounds and +5 volt power supply connections and the other three are additional output lines. Figure A6 is a complete circuit schematic for the indexer board.

The indexer boards receive input data in digital format which specifies the number of steps to be taken and the direction. When these commands are received, the indexer boards provide the correct number of properly sequenced phase control signals needed to operate the DRD002A two-phase stepping motor drivers. The indexer boards may be used to operate the motors one step at a time in either direction using a Jog command or to run the motors continuously in either direction using the Run command. The indexer boards can be used in two different basic modes in terms of the way in which move information is inputted. In the Switch Interface mode (Pl pins 47 and 48 left floating) move information is entered on the data bus with external switches which are diode isolated. In this application, which required microprocessor control, the indexer boards are being used in the Smart Interface mode accomplished by jumpering Pl-47,48 to Pl-49. This allows all move commands to enter

Figure A.6 Schematic Diagram IDD008 Indexer Card.

the indexer boards on the data bus from the SCCS-85 microcomputer board.

This mode does require a simple 'handshaking' routine in order to function correctly.

Also contained within the circuitry of the indexer boards are provisions for establishing the base speed, the high speed rate, and the rate of acceleration and deceleration. The values for each of these parameters can be fixed using a series of on-board jumpers or may be entered into the IDD008's memories from the data bus in ASCII format. There are several other operational parameters which can be selected with on-board jumpers. The first of these is unique to each of the two indexer boards in that it basically gives each board an address identification. There are two sets of terminal arrays which are responsible They are the SEL and the POL terminals. There are for this address. axis designations of S-Z for each and so it follows that both sets of X terminals should be jumpered on the X-axis board and that both sets of Y terminals should be jumpered on the Y-axis board. The remaining jumper-selected parameters are set the same for both boards. The base speed, the high speed rate, and the rate of acceleration and deceleration, even though jumper-selected on the board, may be overridden in the Smart Interface mode by inputting the data in ASCII format over the data The following is a listing of the other parameters mentioned and an indication of exactly which terminals are jumpered:

| Function      | Terminal Pair | Jumpered? | Result                                |

|---------------|---------------|-----------|---------------------------------------|

| Stepping Mode | F/H<br>OWO    | no<br>no  | Full-step, two<br>windings on<br>mode |

| Reduced       | STB-1         | yes       | Reduced standby                       |

| Standby<br>Current<br>Option                    |                                                      |                                    | current option selected                                                 |

|-------------------------------------------------|------------------------------------------------------|------------------------------------|-------------------------------------------------------------------------|

| Mid-range<br>Stabilization                      | N-T                                                  | no                                 | Mid-range<br>stabilization<br>feature<br>selected                       |

| Mid-range<br>Stability,<br>High Speed<br>Cutout | SL-C<br>SL-B<br>SL-A                                 | yes<br>yes<br>yes                  | Feedback cut-<br>out frequency<br>of 6134 steps/<br>sec. selected       |

| Half<br>Frequency<br>Option                     | HF                                                   | no                                 | Half-frequency<br>option not<br>selected                                |

| Backlash<br>Compensation                        | ВСК                                                  | no                                 | No backlash compensation                                                |

| Resonance<br>Control                            | PPS-1<br>PPS-2<br>PPS-3<br>PPS-4<br>PPS-5<br>PPS-6   | no<br>no<br>yes<br>no<br>yes<br>no | Resonance<br>control time<br>of 2000<br>microseconds<br>selected        |

| Base Speed<br>Programming                       | B-7<br>B-6<br>B-5<br>B-4<br>B-3<br>B-2<br>B-1        | no no no no no no no no            | With HF not jumpered, base speed of 40 pulses/sec. selected             |

| High Speed<br>Limit                             | H-8<br>H-7<br>H-6<br>H-5<br>H-4<br>H-3<br>H-2<br>H-1 | no      | With HF not<br>jumpered,<br>high speed of<br>40 pulses/sec.<br>selected |

| Acceleration/<br>Deceleration                   | A-8<br>A-7<br>A-6<br>A-5<br>A-4<br>A-3<br>A-2<br>A-1 | no      | 500 steps/<br>second/<br>second<br>selected                             |

The state of

In the Smart Interface mode move commands and data are entered into the indexer board through the data bus using a 'handshaking' scheme as mentioned before. Since individual handshaking response is required before any operation takes place, only one axis address enable input (Pl-16 X-axis board or Pl-15 Y-axis board) is allowed at a time. The following sequence of events must occur for ASCII characters to be read from the data buss by an indexer board:

- 1. character put on the data bus.

- 2. In no less than 62 microseconds the indexer will respond by taking 'not' DATA TAKEN low thus reading the character on the data bus.

- 3. The SCCS-85 board sees that 'not' DATA TAKEN has gone low and responds by taking 'not' EN INDEXER back high and removing the ASCII character from the data bus.

- 4. The indexer board senses the low to high transition of This starts the processing of the character read and/or the execution of the move. At the same time that 'not' DATA TAKEN goes high, 'not' BUSY goes low indicating to the SCCS-85 board that the indexer is busy and cannot accept data or commands.

- 5. After the processing and/or execution is completed the indexer board takes 'not' BUSY back high indicating to the SCCS-85 board that it may again enable the board by taking 'not' EN INDEXER low again and repeating the above sequence.

By the use of the above sequence, information is transferred from

the SCCS-85 board to the indexer board. Not only must this specific sequence be used to input characters but also a definite progression of characters must be entered in order for the indexer to carry out the desired move. One of the first things necessary to specify is the data entry format. The two possible formats are hexadecimal and decimal. An 'O' (the letter 0) selects the hexadecimal format and a 'F' selects the decimal format. By default, when power is applied to the indexer board, the hexadecimal format is chosen. It is also chosen whenever the indexer board is given a 'C' command which is a Clear All Registers command. The data entry format remains active until a command specifying the other format is entered.

The indexer card has five registers. Once a register has been selected, data are then entered into the register using a sequence of ASCII characters. Once the data are entered into a register and the register has been closed, another register can be selected by entering the appropriate register select character. The register select characters are as follows:

- A acceleration/deceleration register

- B base speed register

- H high speed register

- M move register

- S delay register

It should be noted that the move register is also selected by power turn-on, a 'not' RESET INDEXER signal, or entry of a 'C' (clear all registers) character. Once a register has been specified by entering one of the five above characters (or by default) then data are entered

into the selected register using the following format:

- 1. Enter the '<' character to clear the previous data and open the addressed register.

- 2. Enter the data characters.

- 3. Enter the '>' character to close the register.

All data entered must be within specified limits for the particular register. Also, it should be noted that that data characters are actually only codes for numbers as specified in tables for each register. The required limits and all tables are listed in the Superior Electric indexer board instruction manual and, due to their length, will not be duplicated in this document. In the case of the move register only, the data characters between the '<' and the '>' may be prefixed with a '-' to indicate movement in the negative direction. If '-' does not preceed the data, then movement in the positive direction is assumed by the indexer.

For clarification, some explanation of 'direction of movement' may be in order at this time. In the operating manual for the indexer board, the Superior Electric Co. defines positive movement as that which occurs when the motor is turning in a clockwise direction as viewed from the label end of the motor. If, however, a point directly below the ink jet head is specified as a origin prior to any table movement, then an indexer positive move command moves the table in such a manner that the head is repositioned at a point either on the X or Y negative axis. For that reason, in order to accomplish movement in the positive X or positive Y direction (that is, of the head in respect to the table), a command for movement in the negative direction must be given to the indexer

board. In the remainder of this section explaining the operation of the indexer boards, reference to the 'positive direction' refers to the positive direction as defined by the manufacturers of the board. Keep in mind that the actual print direction on the substrate will be just the opposite.

In studies to date, the table has been operated only at a constant base speed. For this reason, the acceleration/deceleration register, the high speed register, and the delay register have not been utilized. As increased substrate speeds are investigated, these registers will have to be used.

There are many ASCII character commands that may be used with the indexer board in addition to the commands already mentioned. Many of these utilize special features of the indexer board which are not needed in this application. The following is a listing of motion commands which are used and a brief description of what each command does:

| Command Name | Character | Function                                                      |

|--------------|-----------|---------------------------------------------------------------|

| INDEX        | G         | Initiates a programmed move as specified by previous commands |

| JOG -        | I         | Pulses motor one step in negative direction                   |

| JOG +        | J         | Pulses motor one step in positive direction                   |

In this application the G command is the motion command most often used in that it initiates motion for each individual move. When the JOYSTICK mode of operating the table is selected then the two JOG commands, I and J, are utilized.

Referring to Figure A5, it is seen that an external MOVE/CLEAR switch has been provided for the indexer boards. When Pl pin 36 is taken low by pressing this switch then any motion taking place is terminated, without programmed deceleration (if applicable), and the move register is cleared. If this line is held low then all motion except JOG - and JOG + is inhibited.

The Superior Electric Co. indexer board has many features which are not being utilized presently since all the testing done to date has been at fairly low table speeds. The above description of the board and its command structure for the various registers, etc., may seem somewhat complicated. In the future, as an attempt is made to increase print speed, then many of the additional features built into the board will have to be used. However, it is currently being operated using a very simple process with a minimum of commands. The sequence described above for reading ASCII characters from the data bus must be adhered to, but otherwise the following sequence is all that is needed to accomplish table movement:

- Select the base speed register by inputting a 'B' to the indexer board chosen.

- Open the register and clear it of previous data by inputting an ASCII <<.</li>

- 3. Select the hexadecimal number from the base speed table in the indexer board operating manual which represents the required base speed and input it to the indexer board. This number must be within the range of 00 through FA. (Note: The hexadecimal format

was chosen by default upon application of power to the indexer board.)

- 4. Input a '>' to close the base speed register.

- 5. Select the move register with a 'M'.

- 6. Open the register and clear any previous contents with a < .

- 7. If movement in the negative direction is required then input a '-', otherwise positive direction is assummed.

- 8. Select the hexadecimal number from the move register table in the indexer board operating manual which represents the required number of steps to be moved. This number must be within the range of 000000 through FFFFFF, although leading zeroes need not be entered.

- 9. Close the move register with a '>'.

- 10. Initiate the specified move at the specified base speed by inputting a 'G'.

The two indexer boards in the system, when given the proper commands by the SCCS-85 board, output the proper signals to the associated driver board for each channel in order to accomplish the desired move. A definite format for inputting commands and data to the boards must be followed, but otherwise the process for specifying and accomplishing movement of the X-Y table is fairly simple.

There are three other outputs from the indexer board, two of which are being used. These are buffered translator monitoring signals which

exit the board on both the 20-pin edge connector and also on three spade lug terminals. The 'not' MOTION BUSY line is not being used. The -DIR and the 'not' XLR-PU outputs at the quick disconnect terminals are being employed to provide direction and count information to the Counter/Display Driver board. The details of these signals will be discussed later in the L.E.D. Display section.

# 6.3 Superior Electric Driver Boards