**STD 7000**

7308 Counter/Timer Card USER'S MANUAL

## NOTICE

The information in this document is provided for reference only. Pro-Log does not assume any liability arising out of the application or use of the information or products described herein.

This document may contain or reference information and products protected by copyrights or patents and does not convey any license under the patent rights of Pro-Log, nor the rights of others.

Printed in U.S.A. Copyright<sup>©</sup> 1981 by Pro-Log Corporation, Monterey, CA 93940. All rights reserved. However, any part of this document **may be reproduced** with Pro-Log Corporation cited as the source.

# 7308 Counter/Timer Card USER'S MANUAL

H ()

## FOREWORD

This manual explains how to use Pro-Log's 7308 Counter/Timer Card. It is structured to reflect the answers to basic questions that you, the user, might ask yourself about the 7308. We welcome your suggestions on how we can improve our instructions.

The 7308 is part of Pro-Log's Series 7000 STD BUS hardware. Our products are modular, and they are designed and built with second-sourced parts that are industry standards. They provide the industrial manager with the means of utilizing his own people to control the design, production, and maintenance of the company's products that use STD BUS hardware.

Pro-Log supports its products with thorough and complete documentation. Also, to provide maximum assistance to the user, we teach courses on how to design with, and to use microprocessors and the STD BUS products.

You may find the following Pro-Log documents useful in your work: *Microprocessor User's Guide* and the *Series 7000 STD BUS Technical Manual*. If you would like a copy of these documents, please submit your request on your company letterhead.

$\mathbf{O}$

| Foreward                                                                                                                                                                                                                                                                                     | 111                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| List of Illustrations                                                                                                                                                                                                                                                                        |                                                                                            |

| Section 1 - Purpose and Main Features                                                                                                                                                                                                                                                        | 1-1                                                                                        |

| Section 2 - Installation and Specifications                                                                                                                                                                                                                                                  | 2-1                                                                                        |

| I/O Mapped Card Addressing<br>Address Decoder Operation<br>Changing the 7308's Port Address<br>Electrical Specifications<br>Timing Specifications<br>Signal Input Loading and Output Drive<br>User Vcc Output<br>Mechanical Specifications<br>7308 Environmental Specification               | 2-1<br>2-1<br>2-4<br>2-7<br>2-7<br>2-9<br>2-9<br>2-9<br>2-9<br>2-9                         |

| Section 3 - Operation and Programming                                                                                                                                                                                                                                                        | 3-1                                                                                        |

| Counter/Timer Channels<br>Mode Control Registers: Output Port DB<br>Sequence of Operations in Each Mode<br>Channel Control Ports: Output Ports DC, DD, and DE<br>Port Bit Assignments and Programming Aid                                                                                    | 3-1<br>3-11<br>3-17<br>3-25<br>3-27                                                        |

| Section 4 - Circuits and Signals                                                                                                                                                                                                                                                             | 4-1                                                                                        |

| Signal Glossary                                                                                                                                                                                                                                                                              | 4-1                                                                                        |

| Section 5 - Notes on Typical Applications                                                                                                                                                                                                                                                    | 5-1                                                                                        |

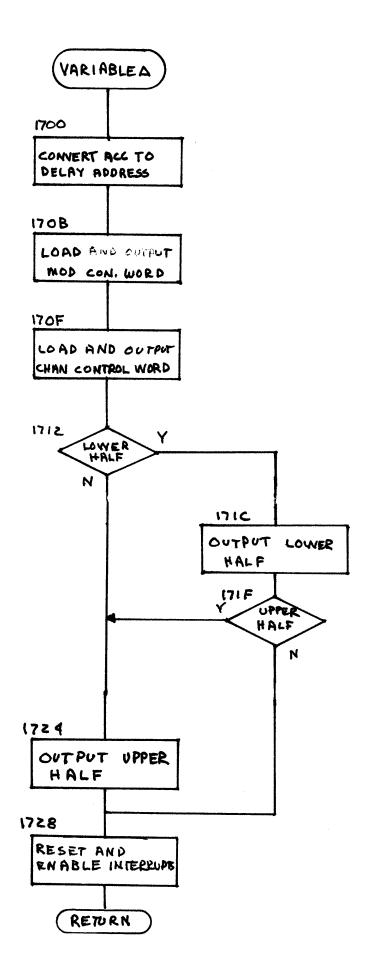

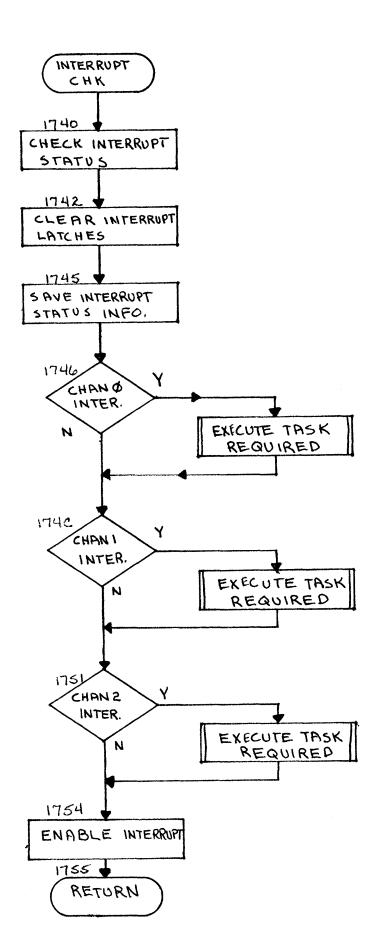

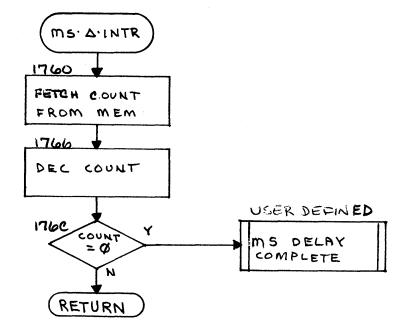

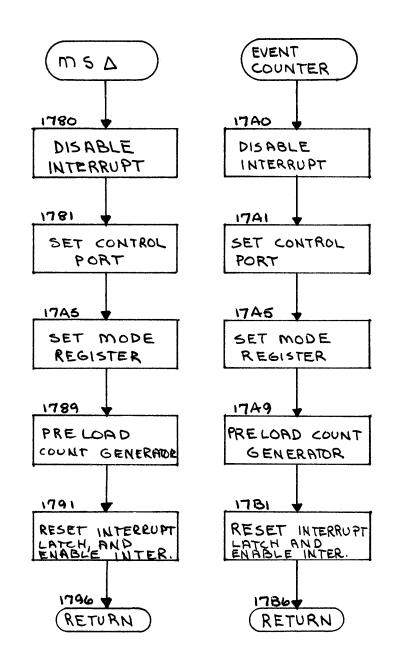

| Loading Each Channel's Load Register<br>Simple One-Time Delays (Mode O)<br>Elapsed Time Measurements<br>Event Counting<br>Extending the Count<br>One-Shot and Delayed Strobe Modes<br>7308 Modules<br>Variable $\Delta$<br>Interrupt Chk<br>MS $\Delta$<br>Event Counter<br>MS $\Delta$ Intr | 5-2<br>5-6<br>5-10<br>5-12<br>5-17<br>5-18<br>5-20<br>5-21<br>5-22<br>5-23<br>2-23<br>2-24 |

| Appendix A - 7308 Strapping Options                                                                                                                                                                                                                                                          | A-1                                                                                        |

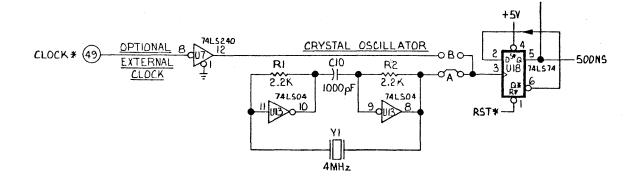

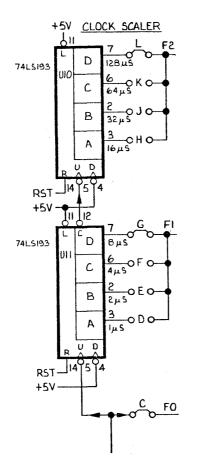

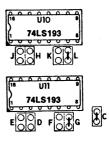

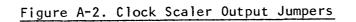

| External Clock Option<br>Clock Scaler Output Changes<br>Nonmaskable Interrupt Request Output<br>Clock Drive STD BUS                                                                                                                                                                          | A-1<br>A-1<br>A-3<br>A-6                                                                   |

| Appendix B - Documentation                                                                                                                                                                                                                                                                   | B-1                                                                                        |

| 7308 Schmatic<br>7308 Assembly Drawing                                                                                                                                                                                                                                                       | B-2<br>B-3                                                                                 |

(iii

## List of Figures

| 1-1  | 7308 Multichannel Counter/Timer Card                                                | 1-2          |

|------|-------------------------------------------------------------------------------------|--------------|

| 1-2  | Block Diagram of 7308 Multichannel Counter/Timer Card                               | 1-2          |

| 2-1  | I/O Mapped Operation in Local Card Rack                                             | 2-2          |

| 2-2  | I/O Port Select Circuit (typical)                                                   | 2-3          |

| 2-3  | Decoder Jumper Pad Numbering (typical)                                              | 2-5          |

| 2-4  | Waveforms at User Interface Connector J2                                            | 2-8          |

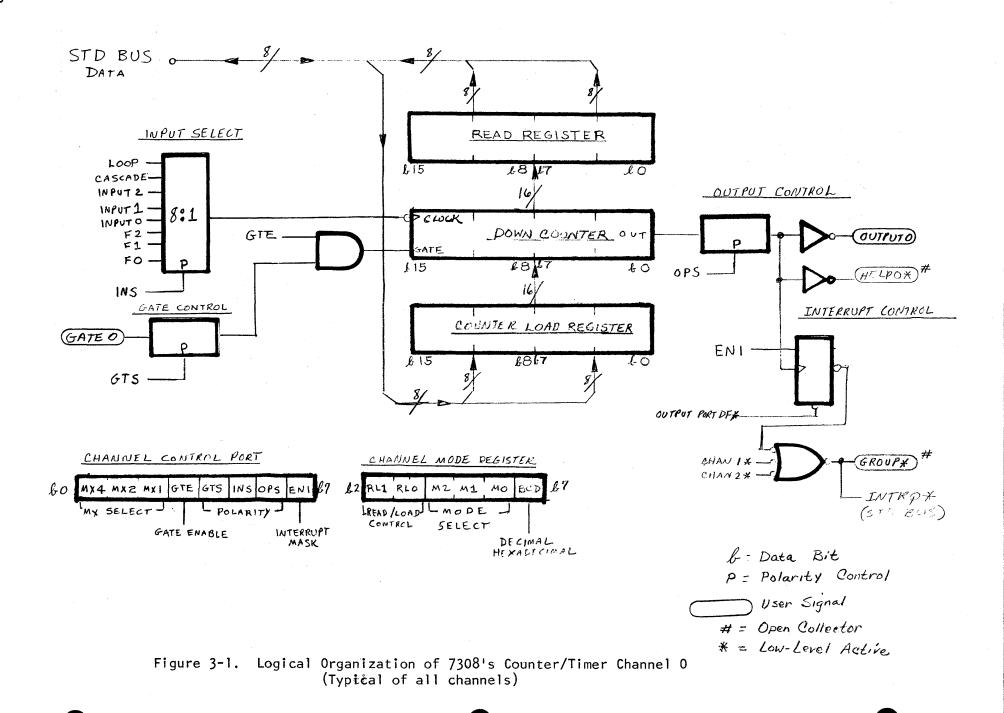

| 3-1  | Logical Organization of 7308's Counter/Timer Channel O<br>(Typical of all channels) | 3-2          |

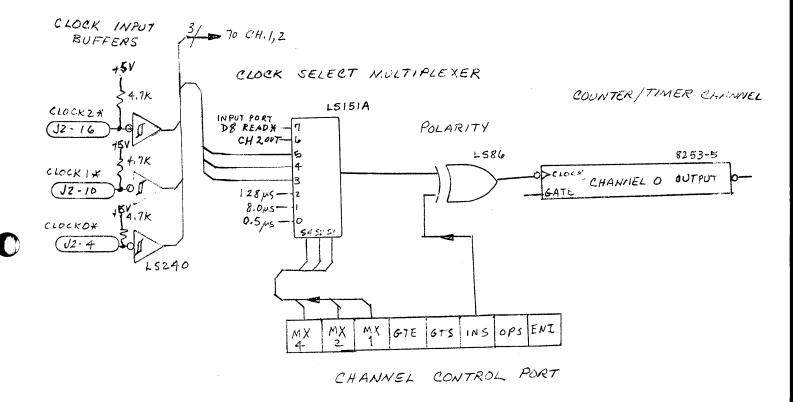

| 3-2A | Clock Control Circuit for Channel O (typical of all channels)                       | 3-8          |

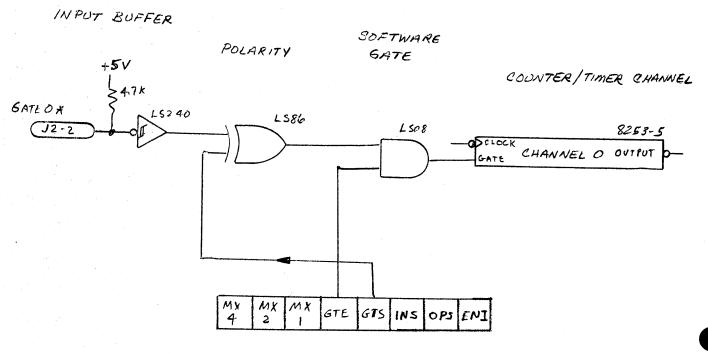

| 3-2B | Gate Control Circuit for Channel O (typical of all channels)                        | 3-8A         |

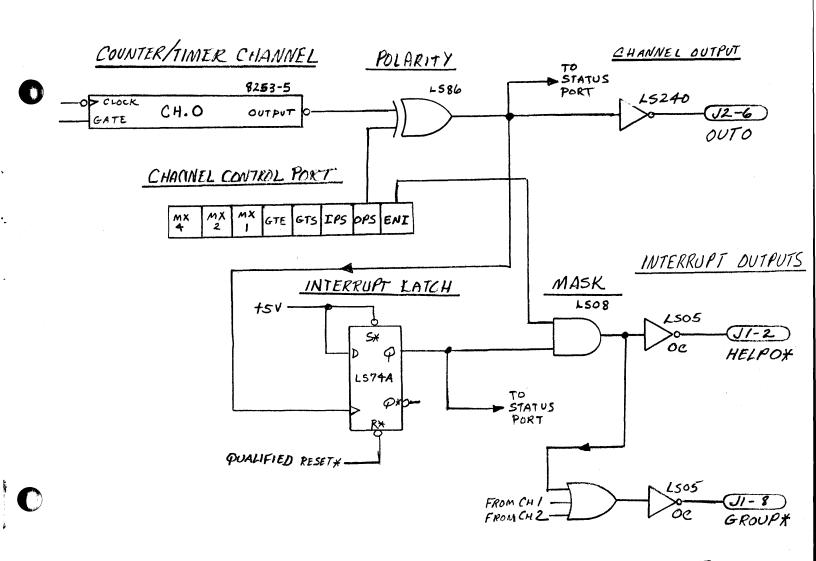

| 3-20 | Channel - Interrupt Circuit for the 7308                                            | 3-8B         |

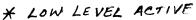

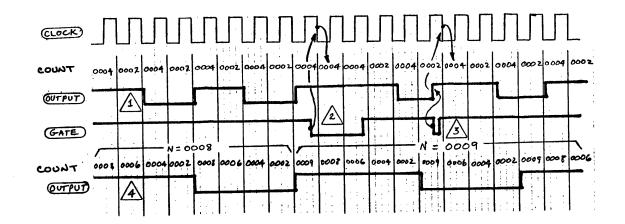

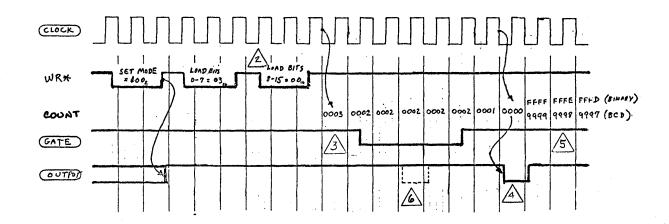

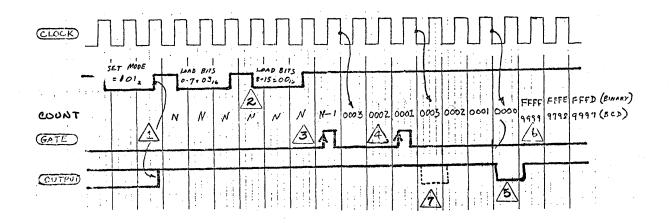

| 3-3  | Mode 0 Waveforms                                                                    | 3-19         |

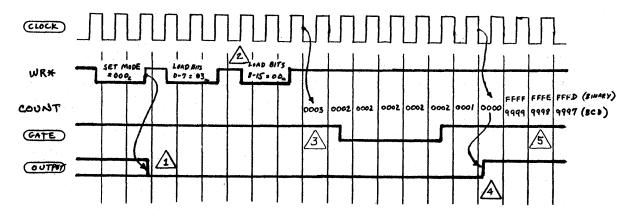

| 3-4  | Mode 1 Waveforms                                                                    | 3-20         |

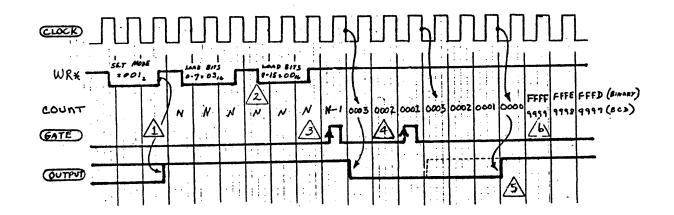

| 3-5  | Mode 2 Waveforms                                                                    | 3-21         |

| 3-6  | Mode 3 Waveforms                                                                    | 3-22         |

| 3-7  | Mode 4 Waveforms                                                                    | 3-24         |

| 3-8  | Mode 5 Waveforms                                                                    | <b>3-</b> 25 |

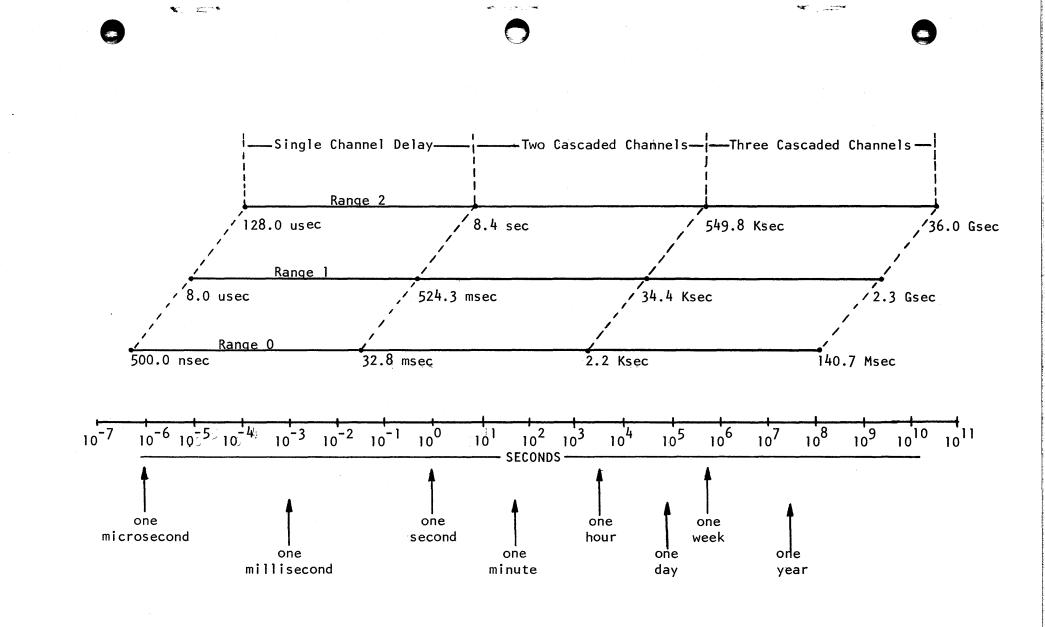

| 3-9  | Single Channel and Cascaded Channel Delay Ranges                                    | 3-30         |

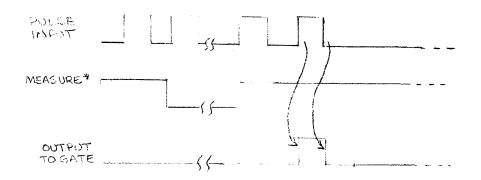

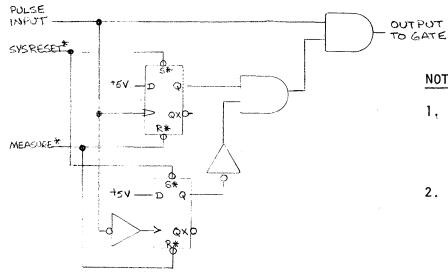

| 5-1  | Circuit Example for Pulse-Width Measurement | 5-13 |

|------|---------------------------------------------|------|

| 5-2  | Decimal and Hexadecimal Totalizing          | 5-15 |

| 5-3  | Limit Counting Example                      | 5-16 |

| A- 1 | External Clock Input Option                 | A-2  |

| A-2  | Clock Scaler Output Jumpers                 | A-4  |

| A-3  | Interrupt Output Jumpers                    | A-5  |

| A-4  | Optional Clock Drive to STD BUS from 7308   | A-7  |

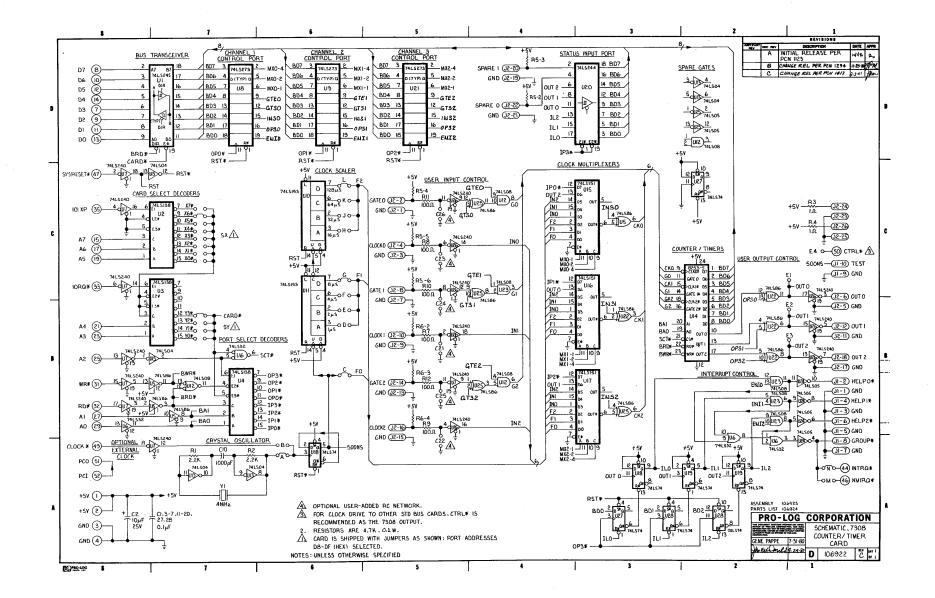

| B-1  | Schematic, 7308 Counter/Timer Card          | B-2  |

| B-2  | Assembly, 7308 Counter/Timer Card           | B-3  |

iv

| LI | ST | 0F | TA | BL | ES |

|----|----|----|----|----|----|

|----|----|----|----|----|----|

(1)

$\mathbf{O}$

| 2-1  | Port Address Jumper Selection                                                                | 2-6  |

|------|----------------------------------------------------------------------------------------------|------|

| 2-2  | User Interface Timing Specification                                                          | 2-8  |

| 2-3  | Edge Connector Pin List                                                                      | 2-10 |

| 2-4  | Connector J1 Pin List for Interrupt Status                                                   | 2-10 |

| 2-5  | Connector J2 Pin List for Counter/Timer Channels                                             | 2-10 |

| 2-6  | 7308 Environmental Specifications                                                            | 2-11 |

| 3-1  | Counter Timer's Read/Load Port                                                               | 3-5  |

| 3-2  | Input Port Clocking of Channels                                                              | 3-7C |

| 3-3  | Mode Control Port Format                                                                     | 3-12 |

| 3-4  | Channel Select Bit                                                                           | 3-12 |

| 3-5  | Read/Load Bit Function                                                                       | 3-12 |

| 3-6  | Channel Operating Mode Codes                                                                 | 3-16 |

| 3-7  | Example of BCD Bit Code Sequence                                                             | 3-18 |

| 3-8  | Decimal/Hexadecimal/Binary Conversion Table                                                  | 3-18 |

| 3-9  | Channel Control Port Bit Format                                                              | 3-27 |

| 3-10 | Clock Multiplexer Programming                                                                | 3-27 |

| 3-11 | Summary of Gate and Clock Input State Control Bits (Channel<br>Control Register Programming) | 3-32 |

| 3-12 | Output Waveform Programming (OPS Bit By Mode)                                                | 3-33 |

| 4-1  | STD BUS Edge Connector Signals Used by the 7308                                              | 4-2  |

| 4-2  | Interrupt Connector Jl Signals                                                               | 4-3  |

| 4-3  | User Interface Connector J2 Signals                                                          | 4-3  |

| 4-4  | Internal 7308 Signals (See Appendix B)                                                       | 4-4  |

| 5-1  | Channel Preload Values for Common Baud Rates                                                 | 5-7  |

| 5-2  | Example of Mode O Programming (Program Segment)                                              | 5-9  |

| 5-3  | Interrupt Polling Program Segment                                                            | 5-11 |

| 5-4  | One Shot and Delayed Strobe Mode Summary                                                     | 5-18 |

v

Section 1

Introducing the 7308 Multichannel Counter/Timer Card (Purpose and Main Features)

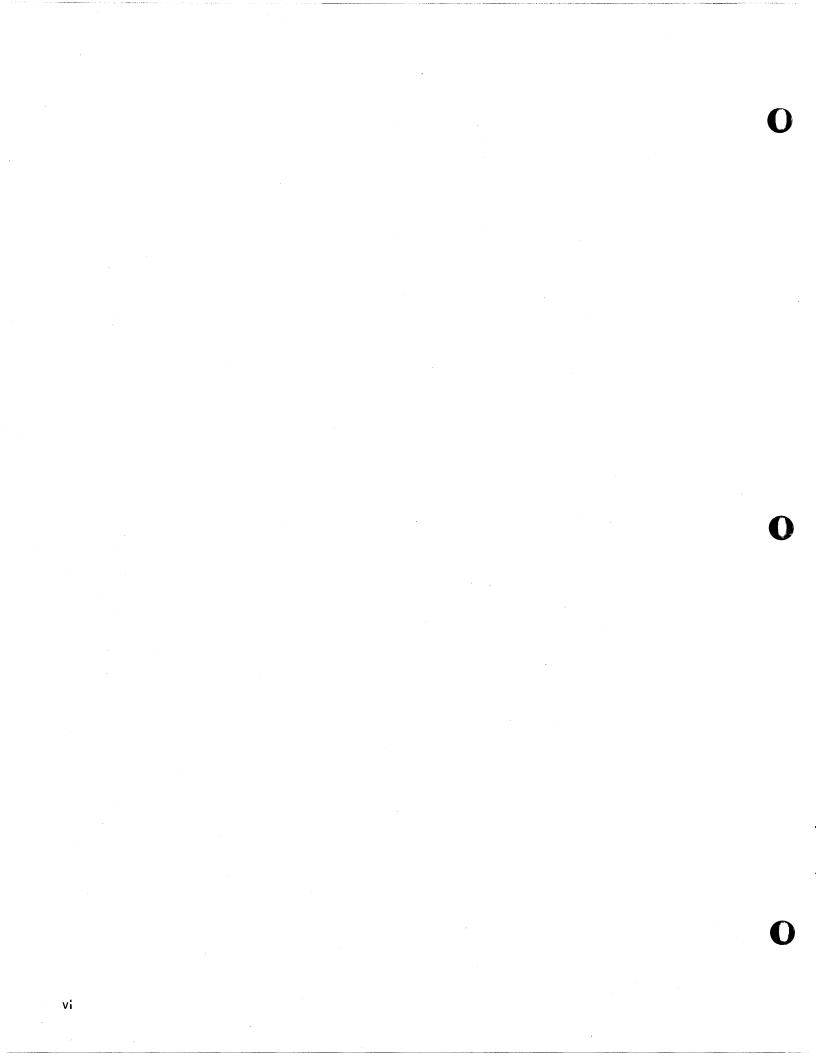

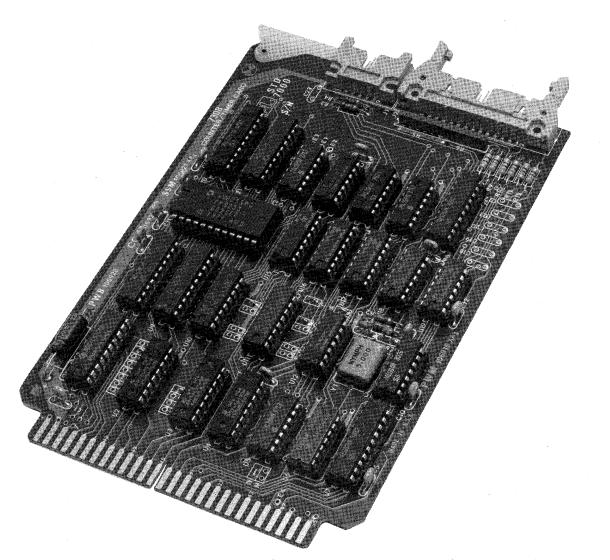

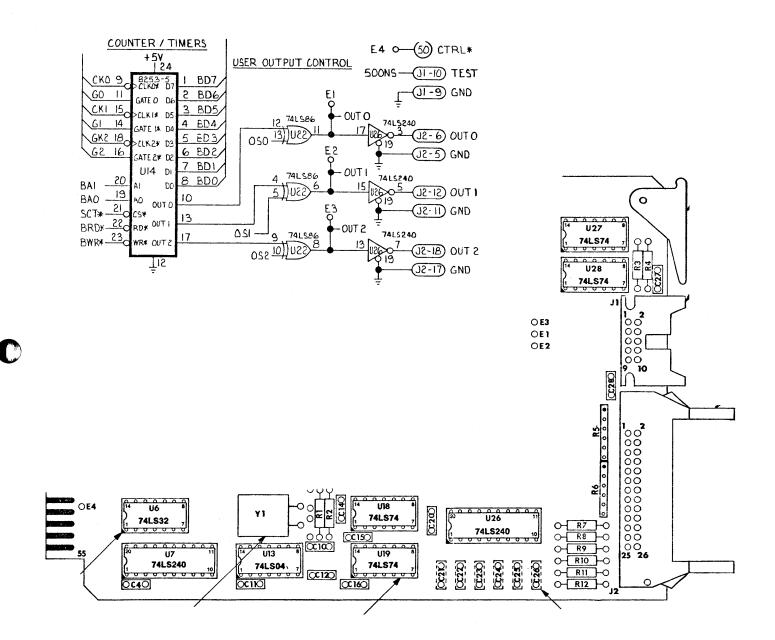

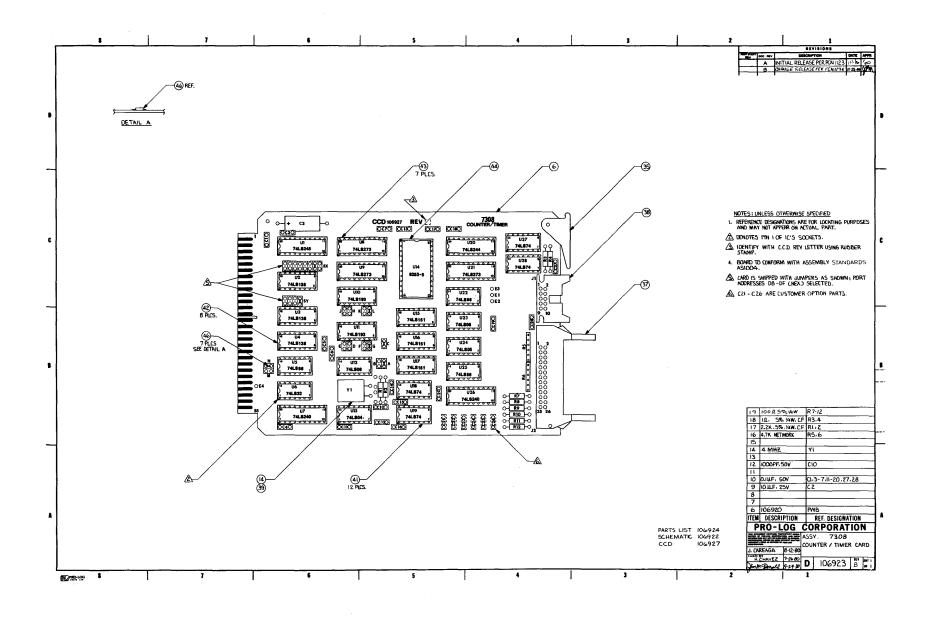

The 7308 is a fully programmable, multichannel counter/timer card (Fig. 1-1). It runs as a stand-alone peripheral after receivingssetup instructions from the system processor card. An onboard interrupt and status polling system identifies completed operations. (See Fig. 1-2 for block diagram).

Based on the 8253-5 counter/timer, the 7308 provides three 16-bit counter/ timer channels. The card has a crystal oscillator and tapped clock divider, an 8-input multiplexer for each channel, and programmable logic states at each clock, gate, and output signal.

The three channels are configured independently by the program. Each is suitable for event counting from DC to 2.5 MHz, for one-shot simulation with hardware and software triggering and retriggering, and for precisely timed interrupts. A special feature allows any channel to interrupt after the nth programmed event or loop iteration.

Main features of the 7308 are:

- . Three independent 16-bit counter/timer channels with six operating modes each.

- . Count source multiplexer, with eight inputs for each channel.

- . Programmable logic polarity at user inputs and outputs.

- . No adjustments minimizes OEM effort and field errors.

- . Onboard interrupt latches and masks for stand-alone operation; STDMG-approved interrupt connector for expansion with 7320 priority interrupt card.

- . Onboard crystal oscillator for accurate programmed timing.

- . Provision for external time-reference signal input, and clock output for other STD BUS cards.

- . Universal processor compatibility: Z80, 8085A, 6800 and others.

- . Multisourced industry-standard components.

- Single +5V operation.

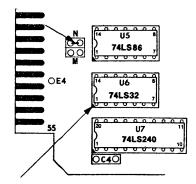

Figure 1-1. 7308 Multichannel Counter/Timer Card.

Figure 1-2. Block Diagram of 7308 Multichannel Counter/Timer Card.

$\square$

Section 2

How to Use the 7308 (Installation and Specifications)

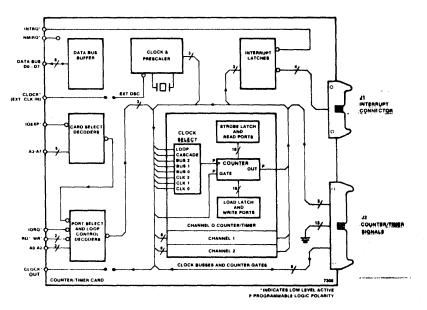

The 7308 operates as part of an STD BUS card rack system. You can plug it directly into the STD BUS backplane (Fig. 2-1) or extend it from the motherboard with a 7901 card extender, or equivalent. In this configuration, the card is mapped at processor I/O port addresses.

## 1/0 Mapped Card Addressing

(Figure 2-1: I/O Mapped Operation in Local Card Rack) In its normal operation, the 7308 is addressed directly by the processor card. The 7308's input and output ports respond to single read and write instructions executed in the processor's operating program. The 7308 is enabled when a jumper-selected combination of address lines AO through A7 is present, and when the following control lines are active: IORQ\*, IOEXP\*, and either RD\* or WR\*.

The 7308 occupies eight consecutive I/O addresses regardless of its mapping assignment. To facilitate testing, we ship the card with hexadecimal addresses D8 through DF connected. You may retain these addresses or change them by moving the installed jumper wires. While the card's port addresses are generally arbitrary, they must differ from all other I/O port addresses in the system. If they do not differ, multiple cards will respond to the same input instruction, resulting in bus contention.

### Address Decoder Operation

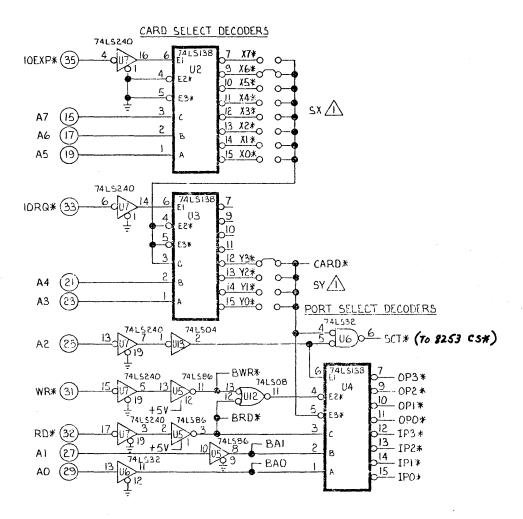

(Figure 2-2: 1/0 Port Select Circuit)

Refer to the 7308 Schematic diagram (Figure B-1) in Appendix B.

Two cascaded 74LS138 decoders (U2 and U3) form the card select circuit which enables the 7308's data bus buffer (U1) and either the 74LS138 port select decoder (U4) or the 8253 device (U14).

## FIGURE 2-1: I/O MAPPED OPERATION IN LOCAL CARD RACK

Ð

FIGURE 2-2: 110 PORT SELECT CIRCUIT (TYPICAL)

The 7308 occupies eight I/O port addresses, with four of the I/O ports internal to the 8253-5 (Ports D8-DB as shipped) and the other four ports. (DC-DF) controlled by the port select decoder (U4).

When address line A2 is low, the 8253-5 ports are selected. The device contains internal circuitry which decodes address lines A0 and A1 with RD\* and WR\* to control read and write operations for ports D8-DB.

When address line A2 is high, port select decoder U4 is enabled with RD\* and WR\* to generate input port strobes IPO\* - IP3\* and output port strobes OPO\*-OP3\*. These strobes control read and write operations for ports DC-DF.

The functions of the eight input and output ports are shown in Table 3-13.

## Changing the 7308's Port Addresses

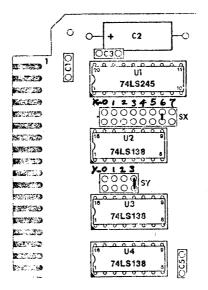

Refering to the 7308 assembly diagram, (Appendix B) locate decoders U2 and U3 (74LS138) next to the STD BUS edge connector. Each decoder has a dual row of pads that form decoder output-select matrices. Make one (and only one) connection to each matrix next to U2 and U3.

Figure 2-3 shows the numbering of the pads next to the decoder chips on the 7308. It also shows the jumpers (at X6 and Y3) that produce hexadecimal port addresses D8-DF (the selections made when the card is shipped).

(Figure 2-3: Decoder Jumper Pad Numbering)

Table 2-1 shows where to place jumper straps to obtain any eight sequential port addresses in the hexadecimal range of 00 through FF. You can change the 7308's address range to occupy any eight ports with the restriction that the least significant digit of the lowest of the eight addresses must be either a zero or an eight (the card can occupy addresses 20-27 or 58-5F, for example).

(Table 2-1: Port Address Decoder Jumper Selection)

Determine which block of addresses you want the card to occupy, then find the most significant digit of the address along the left axis of Table 2-1, then the block of eight least significant digits across the top of the

$\sim$

FIGURE 2-3: DECODER JUMPER PAD NUMBERING (TYPICAL)

| MOST                       |   | LEAST SIGNIFICANT HEX ADDRESS |   |            |    |   |   |   |   |   |   |    |    |   | JUMPER |   |                         |           |

|----------------------------|---|-------------------------------|---|------------|----|---|---|---|---|---|---|----|----|---|--------|---|-------------------------|-----------|

| SIGNIFICANT<br>HEX ADDRESS | 0 | 1                             | 2 | 3          | 4  | 5 | 6 | 7 | 8 | 9 | A | в  | С  | D | E      | F | ] •                     | SELECTION |

| 0                          |   |                               |   | X0         | YO |   |   |   |   |   |   | XO | Y1 |   |        |   | $\overline{\mathbf{N}}$ |           |

| 1                          |   |                               |   | X0         | Y2 |   |   |   |   |   |   | X0 | Y3 |   |        |   | 1                       |           |

| 2                          |   |                               |   | X1         | Y0 |   |   |   |   |   |   | X1 | Y1 |   |        |   | ]                       |           |

| 3                          |   |                               |   | X1         | Y2 |   | · |   |   |   |   | X1 | Y3 |   |        |   | 1                       |           |

| 4                          |   |                               |   | X2         | Y0 |   |   |   |   |   |   | X2 | Y1 |   |        |   | ]                       |           |

| 5                          |   |                               |   | X2         | Y2 |   |   |   |   |   |   | X2 | Y3 |   |        |   | ]                       |           |

| 6                          |   |                               |   | Х3         | Y0 |   |   |   |   |   |   | Х3 | Y1 |   |        |   | ] [                     | x         |

| 7                          |   |                               |   | X3         | Y2 |   |   |   | ŀ |   |   | Х3 | Y3 |   |        |   | ]                       | AND       |

| 8                          |   |                               |   | X4         | Y0 |   |   |   |   |   |   | X4 | Y1 |   |        |   | ]                       | AND       |

| 9                          |   |                               |   | X4         | Y2 |   |   |   |   |   |   | X4 | Y3 |   |        |   | ]                       | Y         |

| Α                          |   |                               |   | X5         | YO |   |   |   |   |   |   | X5 | ¥1 |   |        |   |                         |           |

| В                          |   |                               |   | <b>X</b> 5 | Y2 |   |   |   |   |   |   | X5 | Y3 |   |        |   | ]                       |           |

| С                          |   |                               |   | X6         | Y0 |   |   |   |   |   |   | X6 | Y1 |   |        |   | ]                       |           |

| D                          |   |                               |   | X6         | Y2 |   |   |   |   |   |   | X6 | Y3 |   |        |   | ]                       |           |

| E                          |   |                               |   | <b>X</b> 7 | YO |   |   |   |   |   |   | X7 | Y1 |   |        |   | ]                       |           |

| F                          | Γ |                               |   | <b>X</b> 7 | Y2 |   |   |   |   |   |   | X7 | Y3 |   |        |   | $\mathcal{V}$           |           |

TABLE 2-1: PORT ADDRESS JUMPER SELECTION

table. Read the pair of jumper connections at the intersection of your selections. For example, obtaining addresses 20-27 requires jumpers X1 and Y0; addresses 58-5F require jumpers X2 and Y3. If you change the address jumpers, remember to remove the jumpers that were installed when you received the card (X6 and Y3).

The pad matrices next to U2 and U3 are on 0.10 inch (0.25 cm) centers. If you anticipate changing address selections frequently, you can replace the jumper wires with wire-wrap posts or equivalent.

### Electrical Specifications

$Vcc = +5V \pm 5\%$

lcc = 750mA maximum, 450 mA typical

Address, data, and control busses meet all STD BUS general electrical specifications

User interface inputs are 5 LSTTL loads maximum. Counter/timer outputs

can drive 55 LSTTL loads minimum, and interrupt outputs are open collector with 10 LSTTL load sink capability. Counter/timer inputs and outputs have programmable polarity; interrupt outputs are low level active. See Tables 2-3, 2-4 and 2-5.

#### Timing Specifications

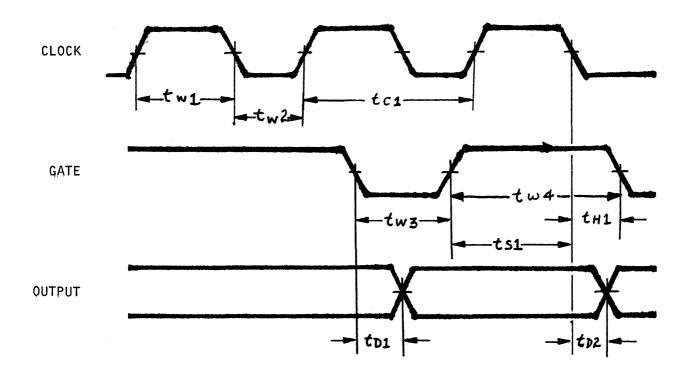

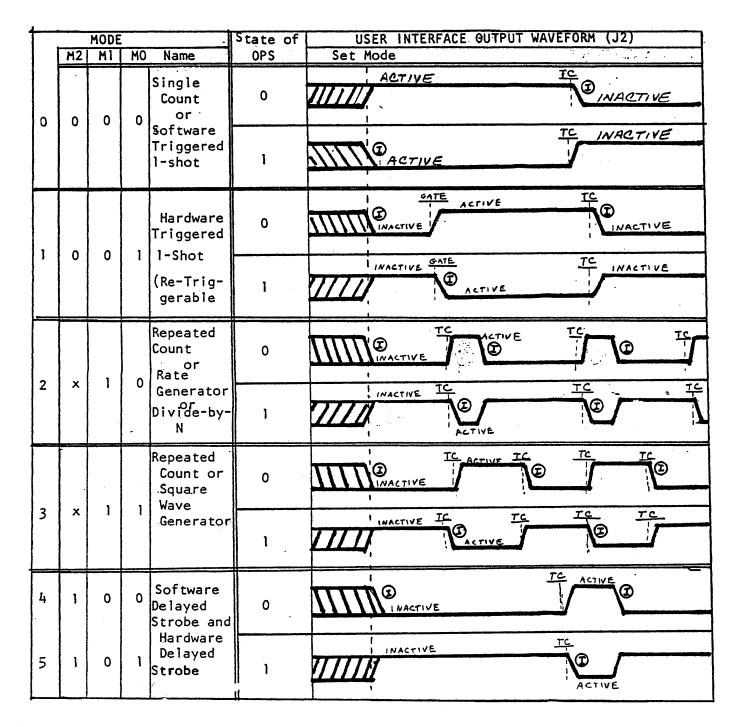

Figure 2-4 shows the relationship of waveforms at the user's counter/timer signal interface connector J2, and Table 2-2 gives min/max timing specifications that apply to the clock, gate, and output signals of any one of the three channels over the specified Vcc and operating temperature ranges.

Note that since the clock and gate input polarities are programmable, Figure 2-4 and Table 2-2 assume that the clock is active on the falling edge and the gate is high level active (IPS=0 and GTS=1; see Table 3-11). This corresponds to the normal logic polarity at the inputs to the 8253-5 device.

(Figure 2-4: Waveforms at User Interface Connector J2) (Table 2-2: User Interface Timing Specification)

n

0

## FIGURE 2-4: WAVEFORMS AT USER INTERFACE CONNECTOR J2

| PARAM           | ETER                                    | MIN | MAX | UNITS       |

|-----------------|-----------------------------------------|-----|-----|-------------|

| tcl             | Clock period asymmetrical waveform      | 400 |     | ns          |

|                 |                                         | 0   | 2.5 | MHz         |

|                 | symmetrical waveform                    | 500 |     | ns          |

|                 |                                         | 0   | 2.0 | MHz         |

| t <sub>W1</sub> | Clock high                              | 250 |     |             |

| t <sub>W2</sub> | Clock low                               | 150 |     |             |

| t <sub>W3</sub> | Gate low                                | 125 |     | ns          |

| t <sub>W4</sub> | Gate high                               | 200 |     |             |

| t <sub>S1</sub> | Gate setup time prior to Clock <b>R</b> | 175 |     | <b>1</b> 10 |

| t <sub>H1</sub> | Gate hold time after to Clock 🔫         | 25  |     | n's ∣       |

| t <sub>D1</sub> | Output delay after Gate 🔫               |     | 525 | ns          |

| t <sub>D2</sub> | Output delay after Clock 🔪              |     | 400 |             |

## TABLE 2-2: USER INTERFACE TIMING SPECIFICATION

## Signal Input Loading and Output Drive

Table 2-3 shows the STD BUS pins that the 7308 uses and the number of LSTTL loads represented by each pin. Pins not used by the card are electrically open. Tables 2-4 and 2-5 show the same information for the interrupt connector J1 and the counter/timer signal connector J2.

For the signal functions and complete electrical specifications of the STD BUS, see Reference 1.

(Table 2-3: STD BUS Edge Connector Pins for the 7308)

(Table 2-4: J1 Connector Pin List for Interrupt Status)

(Table 2-5: J2 Connector Pin List for Counter/Timer Channels)

## User Vcc Output

User interface connector J2 provides system Vcc on pins 24 and 26 for powering user-added signal conditioning circuitry. These output pins are current limited by a one-ohm 1/4 watt resistor each to protect the connector. Output loading on these pins should be restricted to no more than 200 mA each; The output voltage relative to system Vcc will be reduced by 200 mA (typically) with a 200 mA load at each pin.

### Mechanical Specifications

The 7308 meets all general mechanical specifications of the STD BUS, except for J1 and J2 connector protrusion, which is 0.25 inch (0.64 cm) maximum; and J2 mating connector latches, which may protrude up to 0.65 inch (1.65 cm) maximum.

## 7308 Environmental Specifications

(Table 2-6: 7308 Environmental Specifications)

|                     | N NU     | MBER            |    | 1   | PIN N               | UMBE              |           |  |  |  |

|---------------------|----------|-----------------|----|-----|---------------------|-------------------|-----------|--|--|--|

| OUTPUT (LSTTL D     | RIVE     | )               | ור |     | OUTPUT (LSTTL DRIVE |                   |           |  |  |  |

| INPUT (LSTTL LOADS) | <b>`</b> |                 |    |     |                     | NPUT (LSTTL LOADS |           |  |  |  |

| MNEMONIC            | 1        |                 |    |     |                     | [                 | MNEMONIC  |  |  |  |

| +5V                 | IN       | 1               | 2  | 1   |                     | IN                | +5V       |  |  |  |

| GROUND              | IN       | T               | 4  | 3   | 1                   | IN                | GROUND    |  |  |  |

| -5V                 |          | 1               | 6  | 5   |                     |                   | -5V       |  |  |  |

| D7                  | 1        | 55              | 8  | 7   | 55                  | 1                 | D3        |  |  |  |

| D6                  | 1        | 55              | 10 | . 9 | 55                  | 1                 | D2        |  |  |  |

| D5                  | 1        | 55              | 12 | 11  | 55                  | 1                 | D1        |  |  |  |

| D4                  | 1        | 55              | 14 | 13  | 55                  | 1                 | D0        |  |  |  |

| A15                 |          | 1               | 16 | 15  |                     | 1                 | A7        |  |  |  |

| A14                 |          | 1               | 18 | 17  |                     | 1                 | A6        |  |  |  |

| A13                 |          |                 | 20 | 19  |                     | 1                 | A5        |  |  |  |

| A12                 | 1        | 1               | 22 | 21  |                     | 1                 | A4        |  |  |  |

| A11                 | <u> </u> | 1               | 24 | 23  |                     | 1                 | A3        |  |  |  |

| A10                 | 1        | 1               | 26 | 25  |                     | 1                 | . A2      |  |  |  |

| A9                  | 1        |                 | 28 | 27  |                     | 1                 | A1        |  |  |  |

| A8                  |          | 1               | 30 | 29  |                     | 1                 | A0        |  |  |  |

| RD*                 | 1        | 1               | 32 | 31  |                     | 1                 | WR*       |  |  |  |

| MEMRQ*              |          | 1               | 34 | 33  |                     | 1                 | IORC+     |  |  |  |

| MEMEX               |          |                 | 36 | 35  |                     | 1                 | IOEXP     |  |  |  |

| MCSYNC+             |          | 1               | 38 | 37  |                     |                   | REFRESH*  |  |  |  |

| STATUS 0*           |          | 1               | 40 | 39  |                     |                   | STATUS 1* |  |  |  |

| BUSRQ*              |          | 1               | 42 | 41  |                     |                   | BUSAK*    |  |  |  |

| INTRQ*              |          | 10 <sup>8</sup> | 44 | 43  |                     |                   | INTAK+    |  |  |  |

| NMIRQ*              | 1        | 1               | 46 | 45  |                     |                   | WAITRQ*   |  |  |  |

| PBRESET*            | 1        | 1               | 46 | 47  |                     |                   | SYSRESET* |  |  |  |

| CNTRL+              | 1        | 1               | 50 | 49  |                     | 1                 | CLOCK*    |  |  |  |

| PC 1                | IN       | 1               | 52 | 51  |                     | OUT               | PC 0      |  |  |  |

| AUX GND             | 1        | 1               | 54 | 53  |                     |                   | AUX GND   |  |  |  |

| AUX -V              | <b> </b> | +               | 56 | 55  |                     |                   | AUX +V    |  |  |  |

## \* Active Low-level Logic \* Open-Collector Driver Table 2-3 Edge Connector Pin List

| J1 CONN                | ECTO  | R PIN           | LIST  | F    | OR    | INTER       | RUPT     | STATUS          |

|------------------------|-------|-----------------|-------|------|-------|-------------|----------|-----------------|

| P                      | IN NU | MBER            | 1     |      | PIN   | NUMBE       | R        |                 |

| OUTPUT (LST            |       | Ī.              |       | OUTP | UT (L | STTL DRIVE) |          |                 |

| INPUT (LSTTL LO        | ADS)  |                 |       | 11   |       |             | INPU     | T (LSTTL LOADS) |

| SIGNAL                 |       |                 |       |      |       |             |          | SIGNAL          |

| HELP 0*                |       | 10 <sup>a</sup> | 2     | Π    | t     | OUT         |          | GROUND          |

| HELP 1*                |       | 10 <sup>a</sup> | 4     | 1Г   | 3     | OUT         |          | GROUND          |

| HELP 2*                |       | 10 a            | 6     | 11   | 5     | OUT         |          | GROUND          |

| GROUP*                 |       | 10 <sup>a</sup> | 8     | 11   | 7     | OUT         | <u> </u> | GROUND          |

| TEST                   |       | 0               | 10    | 11   | 9     | OUT         |          | GROUND          |

| Active Low-level Logic | * Op  | en-Colle        | ector | Dr   | iver  |             |          |                 |

## Table 2-4: Connector J1 Pin List for Interrupt Status

| J2 CONNECTOR PIN LIST FOR COUNTER/TIMER CHANNELS |     |      |      |        |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |  |  |  |  |  |

|--------------------------------------------------|-----|------|------|--------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|--|--|

|                                                  | PIN | NUMB |      | PIN NU |             | Contraction of the local division of the loc |                 |  |  |  |  |  |

| OUTPUT (LS                                       |     | r    | OUTP | UT (L  | STTL DRIVE) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |  |  |  |  |  |

| INPUT (LSTTL LOADS)                              |     |      | - 1  |        |             | INPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | T (LSTTL LOADS) |  |  |  |  |  |

| SIGNAL                                           |     |      |      |        |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SIGNAL          |  |  |  |  |  |

| GATE 0*                                          | 5   |      | 2    | 1      | OUT         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | GROUND          |  |  |  |  |  |

| CLOCK 0*                                         | 5   |      | 4    | 3      | OUT         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | GROUND          |  |  |  |  |  |

| OUT 0*                                           |     | 55   | 6    | 5      | OUT         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | GROUND          |  |  |  |  |  |

| GATE 1*                                          | 5   |      | 8    | 7      | OUT         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | GROUND          |  |  |  |  |  |

| CLOCK 1.                                         | 5   |      | 10   | 9      | OUT         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | GROUND          |  |  |  |  |  |

| OUT 1*                                           |     | 55   | 12   | 11     | OUT         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | GROUND          |  |  |  |  |  |

| GATE 2*                                          | 5   |      | 14   | 13     | OUT         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | GROUND          |  |  |  |  |  |

| CLOCK 2*                                         | 5   |      | 16   | 15     | OUT         | Τ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | GROUND          |  |  |  |  |  |

| OUT 2*                                           |     | 55   | 18   | 17     | OUT         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | GROUND          |  |  |  |  |  |

| SPARE 1*                                         | 5   |      | 20   | 19     | OUT         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | GROUND          |  |  |  |  |  |

| SPARE 0*                                         | 5   |      | 22   | 21     | OUT         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | GROUND          |  |  |  |  |  |

| +5V                                              |     | OUT  | 24   | 23     | OUT         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | GROUND          |  |  |  |  |  |

| +5V                                              | 1   | OUT  |      | 25     | OUT         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | GROUND          |  |  |  |  |  |

\* Active Low-level Logic

NOTE: +5V outputs each have  $1.0\Omega$ , 4W series resistors for connector protection.

Table 2-5 Connector J2 Pin List for Counter/Timer Channels

| RECOMMENDED OPERATIN | ABSOLUT | E NON-C | PERATING LIM | ITS |     |       |  |

|----------------------|---------|---------|--------------|-----|-----|-------|--|

| PARAMETER            | MIN     | ТҮР     | MAX          | MIN | MAX | UNITS |  |

| Free Air Tempærature | 0       | 25      | 55           | -40 | 75  | °c    |  |

| Humidity *           | 5       |         | 95           | 0   | 100 | %RH·  |  |

\* Non condensing

TABLE 2-6: 7308 ENVIRONMENTAL SPECIFICATIONS

Section 3

How the 7308 Functions (Operation and Programming)

The 7308, in its function as a fully programmable, multichannel counter/timer card, operates as part of the STD BUS card rack system. Uses for the 7308 include:

- Event counting.

- Square-wave and marker pulse waveform generation,

- Time-interval measurements.

- One-shot simulation with hardware and software triggering and retriggering.

- Precisely timed interrupts.

The main elements of the 7308 are three 16-bit counter/timer channels, a crystal oscillator and tapped clock divider, an 8-input multiplexer for each channel, and programmable logic states, for the clock, gate, and output signals.

## Counter/Timer Channels

The three channels of the 7308 are similar in logical organization (see Fig. 3-1 for single channel block diagram).

Each channel consists of the following elements:

- a. 16-bit counter (down counter)

- b. 16-bit channel read and load registers

- c. Mode control register (6 bits)

- d. Channel control port (8 bits)

- e. 8-input multiplexer and clock polarity control

- f. Gate-enable and polarity control

- g. Output-polarity control circuit

- h. Interrupt control circuit

Note in Figure 3-1 that items a, b, and c are part of the 8253-5 counter/timer device.

The 8-bit input and output ports, which the program uses to load data into the counter, read the counter's contents, and read the state of the counter's

outputs and the interrupt system, are implied but not shown in Fig. 3-1.

<u>Down Counter, Load Register, and Read Register</u>. The central element in each channel is the <u>16-bit down counter</u>. The remaining logic elements control and monitor the down counter and set its mode of operation.

You can preset the down counter to any value in the range of 0000-FFFF (hexadecimal) or 0000-9999 (decimal). Once all of the preset input conditions are met, the down counter decrements with each transition at its CLOCK input until terminal count is reached.

Terminal count is defined as the lowest number obtainable when down-counting. Depending on mode, this may be 0000, 0001, or 0002 (decimal or hexadecimal). When terminal count is reached, the OUTPUT circuit responds according to its mode and output-polarity program selections.

You can preload the down counter to any desired value through the <u>load</u> <u>register</u>, which is a 16-bit latch. Note that the program can only write to the load register, not to the down counter itself.

The preload value written to the load register does not enter the down counter immediately. Instead, it is clocked in by the first active transition at the CLOCK input (depending on mode, the GATE may or may not be required to be active to preload the down counter).

The preload value stays in the load register at all times. Depending on mode, this value may be automatically reloaded into the down counter either at terminal count, or at an active GATE transition (when GATE is used as a count trigger, as in the one-shot mode).

The down counter's <u>read register</u> is a transparent latch. It can operate in either the transparent mode, in which case the latch's outputs track exactly with the down counter's outputs and no latching action occurs, or it can synchronously latch and hold a dynamic count upon program command. In latch mode, internal gating synchronizes the read register and the down counter, so that the read register does not latch until the down counter is

stable. Thus, a misread of the down counter from the ripple effect of carry propagation across the 16 bits cannot occur within the clock rate specification of the 7308 (DC to 2.5 MHz.).

IMPORTANT: Unless you are certain that a CLOCK transition cannot occur while the channel's count is being read by the program, we recommend the read register's latched mode for normal operation.

<u>Data Input Ports and Output Ports</u>. The 7308's I/O ports that read and load data to the counter's channels are listed in table 3-1. Note that these addresses reflect the as-shipped mapping of the card. Section 2 shows how the mapping can be changed to any group of eight sequential I/O port addresses. (Table 3-1: Counter/Timer's Read/Load Ports)

<u>Mode Control Register</u>. Each channel has a 6-bit mode control register that selects the following parameters;

- One of six operating modes.

- One of three read/load formats for the data ports.

- Transparent or latched data readback.

- Binary or BCD (hexadecimal or decimal) down-counting.

The data ports described above are 8 bits wide, but each counter/timer channel is 16 bits wide. Consequently, a protocol must be established to handle the most significant or least significant 8 bits in each read or load operation. The mode register performs this function. It also controls the transparent or latched characteristics of the read register and establishes the basic operating mode for the channel (single count, one-shot, marker generator, etc.).

Detailed programming instructions for the mode control register are given in section 4.

| COUNTER/TIMER | READ DATA     | LOAD DATA      |

|---------------|---------------|----------------|

| Channel O     | Input Port D8 | Output port D8 |

| Channel 1     |               | Output port D9 |

| Channel 2     | Input Port DA | Output port DA |