# USACSCS-TF-4-2

# SOFTWARE SUPPORT MANUAL

ASSEMBLY LANGUAGE REFERENCE MANUAL

# PROGRAMMING SUPPORT SYSTEM (PSS-B) (TACFIRE)

(LITTON DATA SYSTEMS) DAAB07-68-C-0154

PREPARED FOR U.S. ARMY COMPUTER SYSTEMS COMMAND FORT BELVOIR, VIRGINIA

Reproduction for non-military use of the information or illustrations contained in this publication is not permitted. The policy for military use reproduction is established for the Army in AR 380-5, for the Navy and Marine Corps in OPNAVIST 5510.18, and for the Air Force in Air Force Regulation 205-1.

## LIST OF EFFECTIVE PAGES

Insert latest changed pages; dispose of superseded pages in accordance with applicable regulations.

NOTE: On a changed page, the portion of the text affected by the latest change is indicated by a vertical line, or other change symbol, in the outer margin of the page. Changes to illustrations are indicated by miniature pointing hands. Changes to wiring diagrams are indicated by shaded areas.

Total number of pages in this manual is 55

consisting of the following:

| Page<br>No. | *Change<br>No. | Page<br>No. |   | *Change<br>No.    | Page<br>No.                           | *Change<br>No. |

|-------------|----------------|-------------|---|-------------------|---------------------------------------|----------------|

| Title       | 0              |             |   |                   |                                       |                |

| Α           | 0              |             |   |                   |                                       |                |

| B Blank     |                |             |   |                   |                                       |                |

| i – iii     |                |             |   |                   |                                       |                |

| 1-1         |                |             |   |                   | · · · · · · · · · · · · · · · · · · · |                |

| 1-2 Blank   | 0              |             |   |                   |                                       |                |

| 2-1 - 2-4   |                |             |   |                   |                                       |                |

| 3-1 - 3-8   |                |             |   |                   |                                       |                |

| 5-1 – 5-5   |                |             | • | tana ara-<br>Ara- |                                       |                |

| 5-6 Blank   |                |             |   |                   |                                       |                |

| 6-1 - 6-2   |                |             |   | •                 |                                       |                |

| 7-1 - 7-8   |                |             |   |                   | ан.<br>2 — 14                         |                |

| 8-6 Blank   |                |             |   |                   | 10.<br>€                              |                |

| 9-1 - 9-4   |                |             |   | la de Sta         |                                       |                |

| 10-1 – 10-2 | 0              |             |   |                   |                                       |                |

## TABLE OF CONTENTS

| Secti | ion                                                                                                                                                          | Page                     | Sec | tion              |                                                                               | Page              |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----|-------------------|-------------------------------------------------------------------------------|-------------------|

|       | OF ILLUSTRATIONS<br>OF TABLES                                                                                                                                | iii<br>                  |     |                   | CHAPTER 4 AN/GYK-12 MACHINE<br>INSTRUCTIONS                                   |                   |

| LISI  | CHAPTER 1 INTRODUCTION                                                                                                                                       | iii                      |     | 4-1               | Introduction                                                                  | 4-1               |

| I     | GENERAL                                                                                                                                                      | 1-1                      |     | 4-2               | Machine Instruction Format                                                    | 4-1               |

| •     | 1-1 Purpose<br>1-2 Applicable Documents                                                                                                                      | 1-1<br>1-1               | . ( | CHAP              | TER 5 AN/GYK-12 COMPUTER EXTEND<br>MNEMONIC INSTRUCTIONS                      | ED                |

|       | 1-3 Description of the Manual                                                                                                                                | 1-1                      |     | <i>с</i> 1        |                                                                               | <b>C</b> 1        |

|       | CHAPTER 2 FUNCTIONS OF THE AN/GYK-<br>ASSEMBLER                                                                                                              | 12                       |     | 5-1<br>5-2        | Introduction<br>Extended Mnemonic Code Instructions                           | 5-1<br>5-1        |

| I     | GENERAL                                                                                                                                                      | 2-1                      |     |                   | CHAPTER 6 COMPOOL SYMBOLS                                                     |                   |

|       | 2-1 Introduction                                                                                                                                             | 2-1                      | I   | GEN               | IERAL                                                                         | 6-1               |

|       | <ul> <li>2-2 Communicating with the AN/GYK-12<br/>Computer</li> <li>2-3 Programming in the AN/GYK-12</li> </ul>                                              | 2-1                      |     | 6-1<br>6-2<br>6-3 | Introduction<br>Compool<br>Compool Symbol Usage                               | 6-1<br>6-1<br>6-1 |

|       | Assembler Language                                                                                                                                           | 2-1                      |     | 6-4               | Converting Compool Symbols                                                    | 6-1               |

| П     | AN/GYK-12 ASSEMBLER<br>2-4 AN/GYK-12 Assembler Basic                                                                                                         | 2-3                      |     |                   | CHAPTER 7 AN/GYK-12 ASSEMBLER<br>INSTRUCTIONS                                 |                   |

|       | Functions                                                                                                                                                    | 2-3                      | I   | GEN               | IERAL                                                                         | 7-1               |

|       | <ul> <li>2-5 Features of the AN/GYK-12<br/>Assembler</li> <li>2-6 Use of Mnemonic Operation Codes</li> </ul>                                                 | 2-3<br>2-3               | •   | 7-1<br>7-2        | Introduction<br>Symbol Definition Instruction (EQU)                           | 7-1<br>7-1        |

|       | 2-7 Variety in Data Representation                                                                                                                           | 2-3                      | П   | DAT               | A DEFINITION INSTRUCTIONS                                                     | 7-2               |

|       | <ul> <li>2-8 Macro Capability</li> <li>2-9 Compool Data Definition Capability</li> <li>2-10 Relocatability</li> <li>2-11 Partitioning and Linking</li> </ul> | 2-4<br>2-4<br>2-4<br>2-4 |     | 7-3<br>7-4<br>7-5 | Generate Data Instruction (GEN)<br>Block Started by Symbol Instruction        | 7-2<br>7-2        |

|       | 2-12 Program Listings<br>2-13 Error Indicators                                                                                                               | 2-4<br>2-4               | 1   | 7-6               | (BSS)<br>Define Length of Local Data<br>Instruction (DATA)                    | 7-3<br>7-4        |

|       | 2-14 Cross Reference and Set/Used Listings                                                                                                                   | 2-4                      | III | PRO               | GRAM LINKING INSTRUCTIONS                                                     | 7-4               |

|       | CHAPTER 3 BASIC COMPONENTS OF THE<br>AN/GYK-12 ASSEMBLER                                                                                                     | 2                        |     | 7-7               | ENT, EXT Instructions                                                         | 7-4               |

|       | LANGUAGE                                                                                                                                                     |                          | IV  | LIST              | ING CONTROL INSTRUCTIONS                                                      | 7-5               |

| I     | SOURCE                                                                                                                                                       | 3-1                      |     | 7-5               | REM, PAGE, OPT Instructions                                                   | 7-5               |

|       | 3-1 Introduction                                                                                                                                             | 3-1                      | V   | PRO               | GRAM CONTROL INSTRUCTIONS                                                     | 7-6               |

|       | <ul> <li>3-2 Assembler Language Source Input<br/>Format</li> <li>3-3 Assembler Language Source Statements</li> </ul>                                         | 3-1<br>3-1               |     | 7-6<br>7-7        | TITLE, ORG, LOC, END Instructions<br>Miscellaneous Instructions: CMP,<br>CNOI | 7-6<br>7-8        |

| II    | GENERAL ASSEMBLER SOURCE                                                                                                                                     |                          |     | 7-8               | Assembly Deck Structure                                                       | 7-8               |

|       | INPUT FORMAT                                                                                                                                                 | 3-2                      |     |                   | CHAPTER 8 MACRO LANGUAGE                                                      |                   |

|       | <ul><li>3-4 General</li><li>3-5 Symbols</li></ul>                                                                                                            | 3-2<br>3-3               | I   | GEN               | ERAL                                                                          | 8-1               |

|       | 3-6 Terms                                                                                                                                                    | 3-4                      |     | 8-1               | Introduction                                                                  | 8-1               |

|       | 3-7 Expressions                                                                                                                                              | 3-7                      |     | 8-2               | The Macro Instruction Statement                                               | 8-1               |

\_1

## **TABLE OF CONTENTS (Continued)**

| Secti | on                                               | Page | Section      |                                                   | Page         |

|-------|--------------------------------------------------|------|--------------|---------------------------------------------------|--------------|

| II    | MACRO DEFINITIONS                                | 8-3  | 9-4          | Prologue Cards (Types 2, 3, 4, 5, 6 and 7)        | 9-2          |

|       | 8-3 Macro Definition and Instruction<br>Examples | 8-3  |              | CHAPTER 10 ASSEMBLY LISTING                       |              |

|       | CHAPTER 9 OBJECT CODE OUTPUT                     |      | 10-1<br>10-2 | Introduction<br>Source Card and AN/GYK-12 Machine | 10-1         |

| I     | INTRODUCTION                                     | 9-1  | 10-3         | Code Listing<br>Prologue                          | 10-1<br>10-1 |

|       | 9-1 Introduction                                 | 9-1  | 10-4         | External Symbol Dictionary                        | 10-1         |

|       | 9-2 Program Identifier Card (Type 1)             | 9-1  | 10-5         | Cross-Reference and Set/Used Listing              | 10-1         |

|       | 9-3 Data Cards (Type 0)                          | 9-1  | 10-6         | Assembly Error Indications                        | 10-1         |

## LIST OF ILLUSTRATIONS

| Num | ber Title                                 | Page | Number                   | Title                                                   | Page |

|-----|-------------------------------------------|------|--------------------------|---------------------------------------------------------|------|

| 2-1 | Programming in the AN/GYK-12              |      | 4-2 Assembler            | Language Machine Instruction                            |      |

|     | Assembler Language                        | 2-1  | Convers                  | ion                                                     | 4-1  |

| 2-2 | AN/GYK-12 Assembler Coding Form           | 2-2  |                          | Language Extended Mnemonic<br>onal Transfer Instruction |      |

| 3-1 | Assembler Language Source Input<br>Format | 3-1  | Convers<br>5-2 Assembler | ion<br>Language Extended Mnemonic                       | 5-1  |

| 3-2 | Example of an Assembler Input Record      | 3-3  |                          | struction Conversion                                    | 5-4  |

| 4-1 | Construction of Assembler Language        |      | 5-3 Assembler            | Language Extended Mnemonic                              |      |

|     | Machine Instruction                       | 4-1  | Format                   | Instruction Conversion                                  | 5-5  |

## LIST OF TABLES

| Nun | nber Title                                                              | Page | Number                                   | Title                                | Page |

|-----|-------------------------------------------------------------------------|------|------------------------------------------|--------------------------------------|------|

| 3-1 | General Assembler Source Input Format                                   | 3-2  | 5-5 Extended                             | Mnemonics for the Shift              |      |

| 4-1 | Addressing Special Symbols                                              | 4-2  | Half Wo                                  | ord Instructions                     | 5-4  |

| 4-2 | Addressing Mode Combinations (Transfer                                  |      | 5-6 Notation L                           | Jsed in Extended Mnemonic            |      |

|     | Instruction Excluded)                                                   | 4-3  | Format                                   | Instruction Codes                    | 5-4  |

| 4-3 | Addressing Mode Combination Examples                                    | 4-4  | 5-7 Extended I                           | Mnemonics for Format                 |      |

| 4-4 | Examples of the Use of Addressing                                       |      | Instruct                                 | ions                                 | 5-5  |

|     | Special Symbols                                                         | 4-6  | 6-1 Examples of                          | of Compool Symbols                   | 6-1  |

| 5-1 | Extended Mnemonics for Conditional                                      |      | 6-2 Bit Instruct                         | tion Examples                        | 6-2  |

|     | Transfer Instructions                                                   | 5-1  | 6-3 Shift and F                          | ormat Instruction Examples           | 6-2  |

| 5-2 | Notation Used in Extended Mnemonic<br>Shift Instruction Codes           | 5-2  |                                          | 2 Assembler Instructions             | 7-2  |

| 5-3 | Extended Mnemonics for the Full Word<br>Shift Options of the SHIFT Full |      | an a | f the Use of the Generate nstruction | 7-3  |

| 5-4 | Word Instruction<br>Extended Mnemonics for the Double                   | 5-3  | 8-1 Macro Defi<br>Operand                | nition Header Statement<br>I Field   | 8-2  |

|     | Word Shift Options of the Shift<br>Full Word Instruction                | 5-3  | 9-1 Program Id                           | entifier Card Format                 | 9-1  |

## LIST OF TABLES (Continued)

| Nun | iber Title                         | Page | Number              | Title                      | Page |

|-----|------------------------------------|------|---------------------|----------------------------|------|

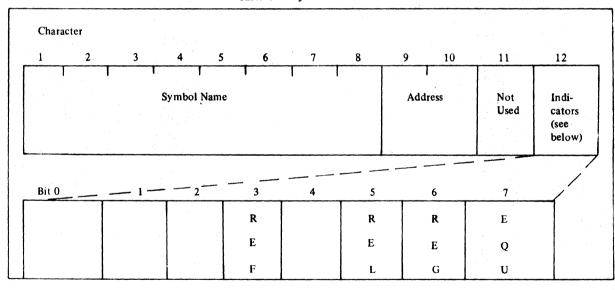

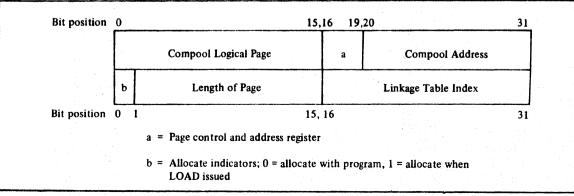

| 9-2 | Data Card Format                   | 9-1  | 9-6 Compool Refe    | rence Linkage Table Format | 9-4  |

| 9-3 | Symbol Table Format                | 9-2  | 9-7 End Card Form   | nat                        | 9-4  |

| 9-4 | Entry Point and External Reference |      | 10-1 Assembly Listi | ing                        | 10-2 |

|     | Tables Format                      | 9-2  | 10-2 External Symb  | ol Dictionary Information  | 10-2 |

| 9-5 | Compool Reference Table Format     | 9-3  | 10-3 Assembly Erro  | or Indication              | 10-2 |

## CHAPTER 1 INTRODUCTION

### Section I. GENERAL

#### 1-1. Purpose

The purpose of this manual is to provide information necessary for programmers to prepare AN/GYK-12 computer assembly programs. Information about the AN/GYK-12 computer assembler language and the assembler itself is presented.

#### 1-2. Applicable Documents

The AN/GYK-12 Principles of Operation Manual USACSCS-TF-4-3 provides information prerequisite to this manual.

#### 1-3. Description of the Manual

Chapter 1 introduces the manual. The purpose and applicable documents are given, and a description of the contents of the manual is provided. Chapter 2 presents general information about the assembler and the assembler language. Information required to construct an input deck to the assembler is presented. In addition, discussions pertaining to communicating with the AN/ GYK-12 computer, programming in the AN/ GYK-12 assembler language, and the AN/GYK-12 assemblier itself are included. Chapter 3 discusses the different types of assembler language source statements, the assembler instruction fields, and the assembler input format. The basic elements of the operand (symbols, terms, and expressions) are also discussed. Chapter 4 presents detailed discussions of the components of the operand field of machine instructions. The con-

tent and format of the different kinds of machine instructions is explained. Addressing modes and indexing are defined and explained. Examples are provided as useful reference material. Chapter 5 presents complete information about the extended mnemonics. Each extended mnemonic instruction is explained in detail and the instruction format used by the assembler is described. Chapter 6 contains detailed descriptions of the use of Compool symbols in an assembler language program. Examples are provided. Chapter 7 discusses the AN/GYK-12 assembler instructions (pseudo operations). The fourteen instructions are organized into groupings, defined, and explained in terms of operand content, format, and usage. Examples are included. Chapter 8 discusses the AN/GYK-12 assembler macro language. Examples are provided to support the detailed definitions and explanations. Chapter 9 explains the assembler object code output. Tables and figures are provided to show the various object code formats. Chapter 10 describes the content and format of the assembly listing. Included are discussions of the program listings, the external symbol dictionary, the cross reference and set/used listing, the assembly error indications, and the error and error symbol counts. Appendix A presents an example of AN/ GYK-12 assembler output. Appendix B is a table of the EBCDIC character codes. Appendix C is a table of the ASCII character codes, and Appendix D consists of a summary table of the AN/GYK-12 machine function codes.

## CHAPTER 2 FUNCTIONS OF THE AN/GYK-12 ASSEMBLER

## Section I. GENERAL

### 2-1. Introduction

This chapter presents general information about the AN/GYK-12 assembler. The structure and function of the assembler are discussed and the various programmer features of the assembler are outlined.

## 2-2. Communicating with the AN/GYK-12 Computer

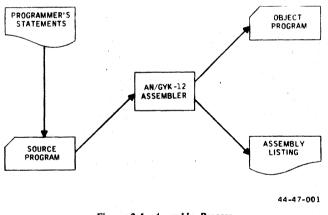

The AN/GYK-12 assembler program instructs the AN/GYK-12 computer to assemble or translate the symbolic assembler language of the source program into AN/GYK-12 machine code instructions to form the object program. The assembly process is illustrated in figure 2-1. The source program consists of a series of instructions. There are several types of instructions in an assembler language, and each type is discussed in a different area in the manual. Machine instructions are discussed in chapters 3 and 4. The assembler instructions (pseudo operations) are discussed in Chapter 7, and the macro instructions are discussed in chapter 8. The actual machine language program will be constructed as indicated by the machine instructions. The assembler instructions control the assembly process by giving directions to the assembler. The assembler will not generate any machine code from these instructions. Macro instructions are used to conveniently generate a desired sequence of instructions many times in one or more programs. A sequence of instructions may be generated as a macro at will by the programmer. This process is called defining a macro. When a macro is referenced by the programmer and used in a program, the process is referred to as macro expansion. The source program is composed of all types of instructions. The source program is written on a special coding form to be keypunched. This form is illustrated in figure 2-2. Any format requirements implied by the form may not hold, as the assembler provides a generally variable field format. The keypunched source program (usually on cards) becomes the

input to the assembly process shown in figure 2-1. There are two outputs from the assembler program. The first is an object program output consisting of actual machine instructions which correspond to the source program instructions presented to the assembler program as input. The object program may be punched on cards, output to magnetic tape, or output to disk. The second output is a program listing or assembly listing. This listing shows the original source program instructions side by side with the object program mer aids such as error indications, a symbol dictionary, and a cross reference listing are provided.

## 2-3. Programming in the AN/GYK-12 Assembler Language

Programming in the AN/GYK-12 assembler language offers a number of important advantages over programming in the actual machine language of the AN/GYK-12 computer.

a. Mnemonic operation codes are provided. For instance, the actual operation code for the add logical full instruction is hexadecimal 0A. In the AN/GYK-12 assembler language the programmer can write the mnemonic operation code ALF. Most programmers never need to learn the actual numeric operation codes.

Figure 2-2. AN/GYK-12 Assembler Coding Form

b. Addresses of data and instructions can be written in symbolic form, and in practice almost all addresses are so written. The programmer is thereby relieved of the task of allocating storage. The use of symbolic addresses reduces the clerical aspects of programming, and the usual resultant errors, and makes the program easier to modify. If the symbols are chosen to be meaningful, the program is also much easier to read and understand than if written with numeric addresses.

c. A macro instruction feature is provided in the assembler language. These instructions are used to simplify the coding of a program, to reduce the change of programming errors, and to provide a standard sequence of instructions for accomplishing a specific task. Whenever a specific sequence of code is needed, the programmer inserts the macro instruction which corresponds to the sequence of code he desires. This macro instruction is recognized by the assembler and a sequence of instructions is generated to represent the macro instruction. The generated instructions are then placed into the code instead of the macro instruction, and are processed like other instructions. Both machine instructions and assembler instructions may be used in a macro definition.

d. Data may be introduced into the program structure, and space reserved for results, by the use of suitable assembler instructions. The communication pool (Compool) feature is an additional data handling feature of the AN/GYK-12 assembler.

e. Many other assembler instructions direct the assembler in the performance of its functions.

## 2-4. AN/GYK-12 Assembler Basic Functions

The AN/GYK-12 assembler is a two pass system encompassing various routines, including a control routine, a macro assembler, and an operand interpreter. The AN/GYK-12 assembler program translates symbolic instructions into machine-language instructions, assigns storage locations, performs tasks initiated by the programmer in the form of machine instructions, makes use of an externally supplied data base description (Compool), generates and resolves macro instructions, provides an assembly listing, and performs various auxiliary functions necessary to produce an efficient, executable machine language program for the AN/GYK-12 computer. The assembly process is accomplished in two passes. The first pass control routines along with the operand interpreter, and the macro assembler, produce a communication file. The operand interpreter is called by pass one to convert and analyze the variable field of certain assembler instructions. The macro assembler is also called by pass one to define and expand macro instructions. The communication file contains the results of the first pass analysis and the original input source language statements in card image format. The second pass uses this communication file as input. The second pass consists of three major processing routines, and a number of input/output routines. The second pass outputs a relocatable binary object deck and a program listing.

a. Pass One Functions. The functions performed by pass one of the AN/GYK-12 assembler are outlined as follows:

(1) Accepts card images of programs in AN/GYK-12 assembler language format.

(2) Verifies and converts operation codes.

(3) Constructs the symbol table.

(4) Evaluates the operands of certain machine instructions. Evaluates portions of the assembly instructions.

(5) Recognizes macro instructions and has macro assembler process macro-instruction definitions or expansions.

(6) Classifies each instruction into one of a number of classes for action by pass two.

(7) Writes the developed information onto a communication device (tape or disk) along with the data from the source code input.

b. Pass Two Functions. The functions performed by pass two of the AN/GYK-12 assembler are outlined as follows:

(1) Accepts the communication file data as input.

(2) Evaluates the several classes of instructions.

(3) Evaluates operands of the assembler instructions and machine instructions not evaluated by the first pass.

(4) Builds the binary object deck, and the ENTRY and EXTERN tables.

(5) Outputs the object program.

(6) Produces a program assembly listing including source and object code listings and error diagnostics, as well as a symbol dictionary, and cross reference listing.

## 2-5. Features of the AN/GYK-12 Assembler

The AN/GYK-12 assembler has a number of features to aid the programmer in the performance of his tasks.

#### 2-6. Use of Mnemonic Operation Codes

The assembler utilizes mnemonic operation codes to provide auxiliary functions that assist the programmer in checking and documenting programs, controlling address assignment, defining data and symbols, generating macro instructions, and controlling the assembly process itself.

#### 2-7. Variety in Data Representation

Decimal, fixed point decimal, hexadecimal, octal, binary, EBCDIC character, or ASCII character representation of machine language binary values may be employed by the programmer in writing source statements. The programmer may select representations best suited to his purpose.

#### 2-8. Macro Capability

The assembler provides an extensive macro capability for the convenience of the programmer. This capability enables the programmer to create, define, and use a macro instruction, wherein a mnemonic symbol, supplied by the programmer, becomes the operation code of the instruction. There are two types of macro instructions: system macro instructions, which provide interface between the object program and the operating system; and programmer-created macro instructions for use in the program at hand, or for incorporation into the macro library for later use. Macro instructions are used to simplify the coding of a program and to provide a standard sequence of instructions for accomplishing a specific task. Whenever the sequence of code is needed, the programmer inserts the macro instruction in the desired place. The assembler program then inserts the sequence of code represented by the macro instruction following the macro instruction mnemonic in the source program.

#### 2-9. Compool Data Definition Capability

An external data definition capability known as communication pool (Compool) is provided. This feature allows the programmer to define symbolic items for use by different program modules. Names of tables, subroutines, and programs may also be included in the Compool. Two types of Compool are provided; the master Compool, and the subset Compool. Both must be generated by a separate program called the Compool Generator and both provide extensive data definition capability.

#### 2-10. Relocatability

The object programs produced by the assembler can be in a format which enables relocation

from the originally assigned storage area to any other suitable area.

#### 2-11. Partitioning and Linking

The AN/GYK-12 assembler allows for partitioning programs into parts called modules. Modules may be added or deleted when loading the object program. Because modules do not have to be loaded contiguously in core, a modularized program may be loaded and executed even though there is not a continuous block of core available that is large enough to accommodate the entire program. The assembler allows symbols to be defined in one program and referred to in another, thus effecting a link between separately assembled programs. This permits references to data and transfer of control between programs.

#### 2-12. Program Listings

A listing of the statements of the source program and the resulting object program may be produced by the assembler for each program that it assembles. The programmer can partially control the content and format of the assembly listing.

#### 2-13. Error Indicators

As a source program is assembled, it is analyzed for actual and potential errors in the programmer's use of the assembly language. Detected errors and irregularities which are potential errors are indicated in the program listing.

## 2-14. Cross Reference and Set/Used Listings

The assembler produces a cross reference and set/used listing incorporating all programmer and Compool defined symbols.

## CHAPTER 3

## BASIC COMPONENTS OF THE AN/GYK-12 ASSEMBLER LANGUAGE

#### Section I. SOURCE

#### 3-1. Introduction

This chapter discusses the basic components of the AN/GYK-12 assembler language. The structure of the assembler input deck is discussed. The different types of assembler language source instructions are introduced. The format of the machine instructions is presented and each field of the general format is discussed. In addition, the various types of symbols, terms, and expressions are discussed.

## 3-2. Assembler Language Source Input Format

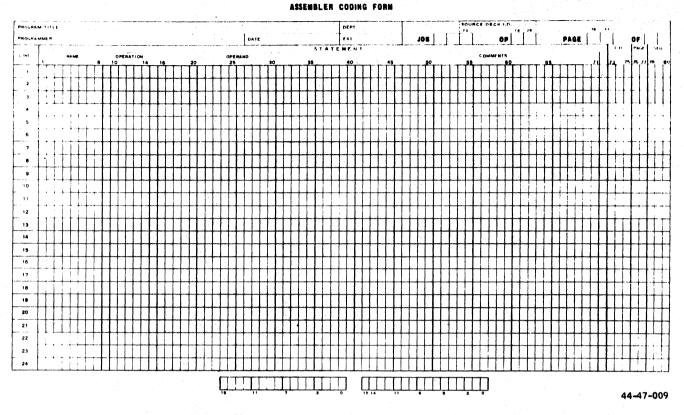

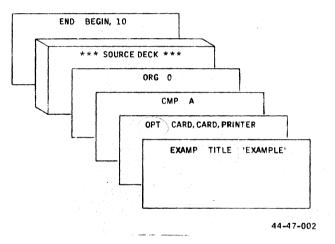

The assembler language source input format is illustrated in figure 3-1. If it is specified, the first card of any assembly deck is the option (OPT) card. Following the OPT card the TITLE card may appear. Then the Compool (CMP) card and then the origin (ORG) or location (LOC) card should be the cards appearing just before the source instructions. Additional origin (ORG) and location (LOC) cards may appear within the source statements themselves as required. The appearance of such a card will cause all of the code following to be made relocatable or nonrelocatable and to start at the location specified. A summary of AN/GYK-12 assembler instructions is illustrated in Chapter 7. These four cards form the introduction to the assembler language program. The OPT card instructs the assembler as to what type of input/output the assembler itself should provide, and what types of outputs are desired by the programmer. The TITLE card identifies the assembly module. The ORG or LOC cards specify where the assembler is to begin assembly of the source program (i.e., at what location should the object code begin), and whether or not the object module will be relocatable from its assembled area at load time. The ORG card identifies the module as reloctable and the LOC card identifies the module as not relocatable. The Compool (CMP) card identifies the Compool to be used with the assembly. Following

these four cards; the OPT, TITLE, CMP, and ORG or LOC, are the source language instructions of the program itself. At the conclusion of the program is the END card which identifies the end of the assembly module and the entry point of the module at load time.

Figure 3-1. Assembler Language Source Input Format

## 3-3. Assembler Language Source Statements

There are four basic types of assembler language source instructions; machine instructions, assembler instructions (pseudo operations), macro reference, and macro definition instructions. The type of instruction is determined by the three to five letter mnemonic operation code which is part of the instruction. Machine instructions directly affect the object program or the actions of the assembler itself.

a. Machine Instructions. Machine instructions are those instructions for which there is a direct equivalent in AN/GYK-12 machine language. All machine instruction mnemonic codes are made up of from three to five letters. Machine instructions have five fields: name, operation, operand, comments, and identification/sequence. The construction of machine instructions corresponds to the

3-1

general assembler source input format described in Section II.

b. Macro Definition Instructions. Each macro definition is a compound instruction consisting of a macro definition header followed by a macro prototype that can be followed by any number of macro model instructions. These macro model instructions may be any AN/GYK-12 assembler language instructions except another macro definition. The macro definition instruction is concluded with a macro definition trailer instruction. The macro model instructions have a format which is identical to the general assembler source input format described in Section II. The macro prototype instruction has a format identical to the macro reference instruction which will correspond to the macro definition instruction in which it appears. Both the macro definition header and the macro definition trailer instructions have special formats.

## Section II. GENERAL ASSEMBLER SOURCE INPUT FORMAT

#### 3-4. General

The AN/GYK-12 assembler language source instructions are input to the assembler from punched cards or punched card images on magnetic tape, disk, paper tape or other suitable input device. The format of each machine instruction consists of an 80 character record divided into five fields as shown in table 3-1.

Table 3-1. General Assembler Source Input Format

| Field               | Maximum length | Starting column |

|---------------------|----------------|-----------------|

| Name                | 8              | 1               |

| Operation           | 5              |                 |

| Operand<br>Comments | 75             |                 |

| ID-Seq.             | . 8            | 73              |

20079-1

a. The format is generally variable field and free format. The only format requirements are:

(1) The name field must begin in column 1. If column 1 contains a blank the assembler assumes that a name has not been entered.

(2) The identification/sequence field must begin in column 73 and end in column 80.

(3) At least one blank must separate each of the fields.

(4) Each record must not exceed 80 characters.

An example of an assembler input is shown in figure 3-2.

b. Name Entry. The name entry contains a symbol created by the programmer to identify or flag an instruction. Any legal symbol may be used as a name. This entry is optional, but if present must consist of not more than eight alphanumeric characters and must contain at least one letter. The first character must be in column 1, and may be a letter or a number. No blanks or special characters may appear within the symbol. If column 1 contains a blank, the assembler assumes that a name has not been entered.

c. Operation Entry. The operation entry contains the mnemonic operation code specifying the machine operation or assembler function desired. The operation entry may begin in any column after column 1, if there is a blank in column 1, or following the first blank after the name entry, if column 1 is not a blank. Valid operation codes consist of groups of alphabetic characters of from three to five letters which are recognizable by the assembler. Invalid operation codes will produce an error diagnostic.

d. Operand Entry. The contents of the operand entry describe data to be acted upon by the instruction. The operand specifies such things as values, storage locations, addressing mode, index register, and accumulator. Depending upon the instruction, one or more operands may be required. Operands are separated by commas with no intervening blanks. The first blank terminates the operand.

e. Comments Entry. The comments entry contains descriptive information about program statements. All valid characters acceptable to the computer, including blanks, may be used in writing the comments entry. This entry cannot extend

44-47-003

COLUMN 1

Figure 3-2. Example of an Assembler Input Record

beyond column 72 and must be separated from the operand entry at least one blank. If there is no operand entry the comments entry must be separated from the operation entry by a blank followed by a comma, followed by another blank. The comments entry will not cause the assembler to generate or modify any executable code resulting from the operation or operand entries of the instruction, in which they appear. If desired entire cards may be used as comments (refer to the REM, Remark Assembly Instruction, Chapter 7).

f. Identification/Sequence Entry. The identification/sequence entry is used to enter program identification and/or instruction sequence characters. Any characters acceptable to the hardware may be used in the identification/sequence entry. The characters in this entry will be checked by the assembler for ascending order according to the standard collating sequence for the computer. An identification/sequence entry with a value less than or equal to that of the preceding entry will be noted on the assembly listing with an asterisk. The identification/sequence entry must begin in column 73 and end in column 80. This entry need not be separated from the operand or comments field by a blank (i.e., column 72 need not be blank).

#### 3-5. Symbols

A symbol is a character or combination of characters used to represent an address or an arbirary value. Symbols, through their use in the name and operand entries, provide the programmer with an efficient way to catagorize and reference a program element.

a. Defining Symbols. The rules which must be followed in defining symbols are as follows:

(1) The symbol must not consist of more than eight characters, at least one of which must be a letter. (2) Only alphanumeric (letter and number) characters may be used. Special characters are not allowed.

(3) Blanks are not allowed in a symbol.

(4) If the symbol is used in the name entry the first character of the symbol must be in the first position of the name entry area (column 1 of the instruction or statement).

(5) The first character of the symbol may be a number or a letter.

The following are valid symbols:

READER 23A46 X4F2 LOOP2 R6 N 01234 L A100

The following are invalid symbols, for the reasons noted:

| 256        | (no letter)                       |

|------------|-----------------------------------|

| RECORDAREA | (more than eight characters)      |

| BCD*34     | (contains a special character, *) |

| IN AREA    | (contains a blank)                |

b. Assignment of Symbols. The assembler assigns a value to each symbol appearing as a name entry in a source instruction. The value assigned represents the address of a storage area, instruction, or constant. Since the addresses of these items may change upon program relocation, the symbols are considered reloctable terms. An exception to this rule is symbols which are within nonrelocatable portions or programs. Symbols used in the name entry of equate (EQU) statements are assigned the value designated in the operand entry of the instruction. Since this value may be relocatable or absolute, depending upon the nature of the operand, the symbol is considered the same as the value to which it is equated.

c. Previously Defined Symbols. Some instructions require that a symbol appearing in the operand entry be previously defined. This means that the symbol, before it is used in the operand entry, must have appeared as a name entry in a previous instruction, or as an identifier in the Compool.

EXAMPLE: DELTA EQU R'8'

## LDF = X'FFF', DELTA

Normally, the second subfield of an instruction contains a number from 0 to 15 which connotes a Process Register number. The above example illustrates a method in which a symbol can be used in place of a Process Register number. In such a case, for the assembler to know that DELTA means Process Register 8, DELTA must be defined prior to its use.

d. General Restrictions on Symbols. A symbol may be defined only once in an assembly. If any symbol is defined more than once in an assembly the assembler will generate an M error (multiple defined symbol) for the instruction in which the subsequent duplicate definition appears. If more than one instruction contains a duplicate name then the error will appear for each such instruction except the first.

#### 3-6. Terms

A term is the basic unit of the operand entry. All terms represent a value. This value may be assigned by the assembler (symbols, or location counter reference) or may be inherent in the term itself. An arithmetic combination of terms is reduced to a single value by the assembler. All terms are unsigned and no blanks are allowed within the term. A term with a sign is considered an expression. Terms are either absolute, relocatable, or special.

a. Absolute Terms. An absolute term represents a self defining value, analogous to a constant in mathematics. The value of an absolute term is inherent in the term itself and is not assigned by the assembler. There are eight types of absolute terms: decimal, hexadecimal, octal, binary, EBCDIC character, ASCII character, process register, and certain symbolic terms. Since the values represented by absolute terms do not change upon program relocation, absolute terms are considered as self defining terms, i.e., their values are defined by the context of the term itself and only once (at assembly time).

(1) Decimal absolute terms. A decimal absolute term is an unsigned decimal number written as a sequence of decimal digits with a decimal point. The decimal point must be placed within or before the number. An integer does not require a decimal point. A scale factor must follow a mixed number or fraction otherwise the fractional portion of the number is lost. In addition a scaling factor and/or a decimal exponent may be used. The decimal number can be an integer, a fraction, or a mixed number (i.e., one with integer and fractional portions). The decimal term is the only term which may use a scaling factor or a decimal exponent. High order ZEROS may be used or omitted for numbers greater than 1 (e.g., 00193 or 193 and 001.67 or 1.67).

(a) A negative decimal term is treated as an expression consisting of a minus sign followed by a decimal constant. At assembly time the decimal term is converted into a binary number of a length sufficient to contain the converted binary number. For example, 37 would be represented as 100101, which is six bits in length. Depending upon the use of the term, the converted binary number must not exceed 31 bits (full word) or 63 bits (double word).

(b) To code a decimal integer all that is needed is the value without any special notation. For fractions or mixed numbers a scale modifier (the letter B) must be used to tell the assembler how many freational bits to reserve for the value. The reason for this is that integer values are always right justified within a computer word.

EXAMPLE: 15 converts to  $1111_2$ 15.25 converts to  $1111_2$

In the above example both numbers converted to the same binary values. The assembler was not told to reserve fractional bits so the fractional part of the value was lost (truncated).

EXAMPLE: 15 converts to 1111<sub>2</sub> 15.25B2 converts to 111101<sub>2</sub>

In the above example a scale modifier is used to correctly position both the integer and the fractional part of the mixed number and the result in binary is different from the result obtained when the scale modifier was not used. To correctly use the scale modifier the letter B immediately follows the fractional part with no intervening blank spaces. Following the letter B is a decimal unsigned number which indicates the number of fractional bits to be reserved. In the second example, two fractional bits were reserved (.25 translates to 01 binary). The entire translation in binary is 1111 for the integer 15 followed by 01 for the fraction. Leading ZEROS would be appended by the assembler (positive value used in the examples). It is also possible to raise or lower a decimal value by powers of 10. This necessitates the use of the term E (for exponent) followed by an optionally signed decimal number.

EXAMPLE: 15 converts to  $1111_2$ 1.5E1 converts to  $1111_2$ 150E-1 converts to  $1111_2$

In the illustrated example the value 1.5 is followed by E1 which is  $10^{1}$  or 10. It could also have been coded E+1. Multiplying 1.5 by 10 results in the value 15. The number following the term E can produce any power of 10 (E2 is  $10^{2}$ , E3 is  $10^{3}$ , etc.). For negative powers of 10 a minus sign must precede the decimal value (E-1 is  $10^{1}$ , E-2 is  $10^{2}$ , etc.). In the illustrated example the number 150 was scaled down by using a negative power of 10 to obtain the value 15. Both the scale factor and the decimal exponent can appear together in the same statement. When this occurs, the decimal exponent must appear first.

## EXAMPLE: 15.25B2 converts to $111101_2$ 1.525E1B2 converts to $111101_2$

In the above example the 1.525 is multiplied by  $10^1$  to produce 15.25. This is then translated to binary with the sacle modifier speciying two fractional bit positions. Any fractional value which requires more than the number of significant bits designated by the scale modifier to fit into the designated binary bit positions of the computer word will be truncated on the right (least significant bits) to fit. Any integer value which is too large to fit into the designated binary bit positions of the computer word will be truncated on the left (most significant bits) to fit. For mixed numbers, if both the integer and the fractional values are too large to fit into the designated binary bit positions of the computer word truncation will occur at both ends.

(2) Hexadecimal absolute terms. A hexadecimal absolute term is written as an unsigned sequence of hexadecimal digits. The digits must be enclosed in single quotation marks preceded by the letter X, for example, X'3A7' or X'AB7'. Each hexadecimal digit is assembled as its four bit binary equivalent. Thus, a hexadecimal term used to represent an eight bit binary number would consist of two hexadecimal digits. Limitations on the value of a hexadecimal term depend upon its use. The hexadecimal digits and their corresponding binary values are as shown in the following chart.

| HEXADECIMAL                               | BINARY VALUE |

|-------------------------------------------|--------------|

| 0                                         | 0000         |

| 1                                         | 0001         |

| 2                                         | 0010         |

| 3                                         | 0011         |

| 4                                         | 0100         |

| 5                                         | 0101         |

| 6                                         | 0110         |

| 7                                         | 0111         |

| 8                                         | 1000         |

| 9                                         | 1001         |

| $\mathbf{A}$ is a product of $\mathbf{A}$ | 1010         |

| B                                         | 1011         |

| <b>C C</b>                                | 1100         |

| D                                         | 1101         |

| E                                         | 1110         |

| F                                         | 1111         |

A negative hexadecimal number is considered an expression consisting of a minus sign followed by an unsigned hexadecimal number. Scale factors and exponents may not be used in hexadecimal terms.

(3) Octal absolute terms. An octal absolute term is written as an unsigned sequence of octal digits. The digits must be enclosed in single quotation marks preceded by the letter 0, for example '743' or '746' (The letter is slashed when used with numbers to distinguish it from the number ZERO.) Each octal digit is assembled as its three bit binary equivalent. Thus, an octal term used to represent a six bit binary number would consist of two octal digits. Limitations on the value of an octal term depend upon its use. The octal digits and their corresponding binary values are as follows:

| OCTAL | BINARY VALUE |

|-------|--------------|

| 0     | 000          |

| 1     | 001          |

| 2     | 010          |

| 3     | 011          |

| 4     | 100          |

| 5     | 101          |

| 6     | 110          |

| 7     | 111          |

A negative octal number is considered an expression consisting of a minus sign followed by an unsigned octal number. Scale factors and exponents may not be used in octal terms.

(4) Binary absolute terms. A binary absolute term is written as an unsigned binary number consisting of a sequence of binary digits. The digits must be enclosed in single quotation marks and preceded by the letter B, for example, B'0101111'. Each binary digit is assembled directly. Thus, a binary term used to represent a six bit mask would consist of six binary digits. Limitations on the value of the binary term depend upon its use.

(5) EBCDIC absolute terms. An EBCDIC absolute term is a sequence of Extended Binary Coded Decimal Interchange Code characters. The characters must be enclosed in single quotation marks and preceded by the letter C, for example, C'TEST(7)'. All letters, decimal digits, and special characters may be used in a character term. Because of the use of single quote marks in the assembler language, two single quote marks must be used to represent a single quote mark or an apostrophe within the character field itself. Examples of EBCDIC absolute terms are: C'/', C'ABC', C' ', C'13', C'''A'''. Each character is assembled as its eight bit EBCDIC code equivalent. A chart of the EBCDIC character codes is provided in Appendix B.

(6) ASCII absolute terms. An ASCII absolute term is a sequence of American Standard Code for Information Interchange characters. The characters must be enclosed in single quotation marks and preceded by the letter A, for example, A'ATEST(7)'. All letters, decimal digits, and special characters may be used in a character term. Because of the use of quote marks in the assembler language, two quote marks must be used to represent a quote mark within the character field itself. Examples of ASCII absolute terms are: A'/ ', A'/ABC', A' ', A'13', A'''A'''. Each character is assembled as its eight bit ASCII code equivalent. A chart of the ASCII character codes is provided in Appendix C.

(7) Process register absolute terms. A process register absolute term is used to reference or indicate a process register, and is written as an unsigned decimal number. The number designation must be enclosed in single quotation marks and preceded by the letter R, for example R'15'. A process register term is assembled as its three or four bit binary equivalent and is placed in the appropriate register containing field indicated by its placement in the operand field. If a process register term appears as the first entry in the operand field it is assembled as the binary equivalent of its special register address in the A field. The hexadecimal addresses generated are as shown in the following chart.

| REGISTER | HEXADECIMAL<br>ADDRESS GENERATED |

|----------|----------------------------------|

| 0        | 0                                |

| 1        | 2                                |

| 2        | 4                                |

| 3        | 6                                |

| 4        | 8                                |

| 5        | Α                                |

| 6        | С                                |

| 7        | E                                |

| 8        | 10                               |

| 9        | 12                               |

| 10       | 14                               |

| 11       | 16                               |

| 12       | 18 •                             |

| 13       | IA IA                            |

| 14       | iC                               |

| 15       | lĔ                               |

| 1.5      |                                  |

Process register terms may be used to specify accumulators, index registers, tally registers, and special registers (as previously shown). Process register terms always designate the set of registers for the currently active program level. Limitations on the value of a process register term depend upon its use.

(8) Symbolic absolute term. A symbolic absolute term is used to specify a non-relocatable address. Any symbols defined within an area governed by a LOC (fixed location counter) card will be non-relocatable. Symbols used in the name field of the equate instruction (EQU) are assigned the value designated in the operand field of the instruction. A symbolic absolute term is one whose equated value is absolute.

EXAMPLE:

|     | LOC | X′5000′      |

|-----|-----|--------------|

| ABA | GEN | F0           |

| ABB | GEN | FX'FFFFFFFF' |

|     |     |              |

In the above example, ABA and ABB are symbolic absolute terms (addresses). They are non-relocatable because they are assembled following a LOC assembler instruction.

b. Relocatable Terms. A relocatable term is a symbolic term whose value is determined by the assembler. The value of a relocatable term is the address of a 16 bit half-word in memory. This address is subject to alteration when the program in which the term appears is loaded for execution. The address will change when the program is relocated. However, portions of a program may be designated relocatable or not relocatable, and terms appearing within a non-relocatable portion of a program will not be relocated. Symbols used in the name field of equate instructions (EQU) are assigned the value designated in the operand field of the instruction. A relocatable symbolic term is one whose equated value is relocatable.

c. Special Designators. There are a number of special designators in the AN/GYK-12 assembly language. The equal sign, =, is used to designate the literal mode of addressing (mode 0). The left and right parentheses, (), are used to designate the indirect mode of addressing (mode 3). The dollar (\$) symbol is used to designate the relative mode of addressing (mode 2), and also represents the instruction location register. The letter R is used to indicate an index register, and the letter D is used to indicate double indexing with the register specified. The asterisk (\*) symbol is used as a means of referencing the location counter without affecting the addressing mode.

(1) Literal addressing designator (=). When the equal sign, =, appears as the first character in subfield one of an instruction the literal mode of addressing (mode 0) is indicated.

(2) Indirect addressing designator ((). When the left parenthesis, (, appears as the first character in subfield one of an instruction the indirect mode of addressing (mode 3) is indicated. The address is enclosed in parentheses.

EXAMPLE: (PC4A)

(3) Relative addressing designator (\$). The programmer may refer to the current value of the instruction location register (ILR) and thereby designate the relative mode of addressing by using a \$ symbol in the operand field of an instruction. The relative mode is used when the programmer wishes to refer to a location relative to the instruction from which the reference is being made. The use of the \$ symbol will designate the relative mode of addressing which is effectively the same as inserting the current value of the instruction location register (the address of the current instruction plus two) into the operand field in place of the \$ symbol.

(4) Location counter designator (\*). A Location Counter is a software counter used to assign addresses to instructions during program assembly as distinguished from the hardware instruction location counter (ILR) which normally contains the instruction location count plus two. The programmer may refer to the current value of the location counter without affecting the mode at any place in the program by using an asterisk (\*) symbol as a term in the operand field. The asterisk (\*) symbol represents the address of the instruction in which it appears. The asterisk (\*) symbol has no effect on the addressing mode and does not indicate relative mode addressing.

(5) Process register indexing designator (R). If the process register absolute term is used following an arithmetic operator in the operand field, the indexing mode of the specified addressing mode will be designated.

(6) Double indexing designator (D). The double indexing designator D is used only with the direct mode of addressing and is used to designate the direct with double indexing mode of addressing. The use of the double indexing designator D implies the use of process register 1 to contain one of the index values. The other index value is designated by the number following the D in the instruction. The double indexing designator is used in place of the R for a normal indexing mode designator may only specify index registers 2 through 7.

## 3-7. Expressions

An expression is an operand entry consisting of either a single term or an arithmetic combination of terms. Up to ten terms can be combined with the following arithmetic operators:

#### USACSCS-TF-4-2

| OPERATION        | EXAMPLE    |

|------------------|------------|

| + Addition       | ALPHA+BETA |

| - Subtraction    | ALPHA-BETA |

| * Multiplication | ALPHA*BETA |

| / Division       | ALPHA/BETA |

An expression may not contain two terms or two operators in succession.

a. Evaluation of Expressions. A single term expression, e.g. BETA, S, X5G, takes on the value of the term involved. A multiterm expression, e.g. BETA + 10, ENTRY-EXIT, 10 + A/B, is reduced to a single value, as follows:

(1) Each term is given its value.

(2) Arithmetic operations are performed left to right. Multiplication and division are performed before addition and subtraction, e.g.  $A + B^*C$  is evaluated as  $A + (B^*C)$ , not  $(A + B)^*C$ . The computed result is the value of the expressions.

(3) Division yields an integer result; any fractional portion of the result will be dropped. For example, the expression 1/2\*10 equals zero but the expression 10\*1/2 equals 5.

b. Absolute Expressions. An absolute expression is a combination of from one to ten terms which may consist of the following:

(1) All absolute terms.

~ ~

(2) An even number of relocatable terms with opposite signs.

(3) An even number of relocatable terms with opposite signs and any number of absolute terms. An even number of relocatable terms with opposite signs cancels the effect of relocation. For example, in the absolute expression A-B+4, A and B are relocatable terms and 4 is an absolute term. If A equals 50 and B equals 40, the values after relocation by +20 would be 70-60+4=14.

An expression is called absolute if its value is unaffected by program relocation. Extreme caution should be used when generating relocatable or absolute expressions with more than one symbolic term.

c. Relocatable Expressions. A relocatable expression is one whose value would change by n if the program in which it appears is relocated n 16 bit words away from its originally assigned area of storage. A relocatable expression may contain relocatable terms, alone or in combination with absolute terms under the following conditions:

(1) There must be an odd number of relocatable terms.

(2) If a relocatable expression contains an odd number of relocatable terms, the extra odd term must not be preceded by a minus (-) sign.

(3) No relocatable term can enter into a multiply or divide operation. An expression is called relocatable if its value at execution time depends upon program relocation. A relocatable expression reduces to a single relocatable value. This value is the value of the odd relocatable term, adjusted by the values represented by the absolute terms and/or paired relocatable terms. For example, in the expression A-B+A, A and B are relocatable terms. If initially A equals 40 and B equals 30, the value of the expression is 50. However, if a relocation factor of 20 is applied, the value of the expression is 70. The value of the pair of terms A-B remains constant, and the value of the expression increases by the relocation factor as a result of its application to the positive odd relocatable term. Note that the intent is to relocate the entire expression by the proper amount, not just one or some of the terms. For example, if the expression A+B-C+D-E is to be relocated by 20, it is the value of the final evaluated expression which should be greater by 20 when the relocation factor of 20 is applied to each of the relocatable terms in the expression. Thus, relocation of expression becomes a question of mathematics and not rules.

## CHAPTER 4 AN/GYK-12 MACHINE INSTRUCTIONS

#### 4-1. Introduction.

This chapter discusses the format and construction of the entries which make up AN/GYK-12 assembler machine language instructions. Brief comments on the name entry, operation entry, comments entry, and identification/sequence entry are presented. A detailed discussion of the operand entry format and the use of Compool symbols in the assembler language machine instructions is presented. The construction of the operand entries for the standard assembler language machine instructions and the extended mnemonic codes is presented. A discussion of the addressing modes is also inccluded. A detailed discussion of the extended mnemonic code instructions is presented in Chapter 5. Appendix D contains a list of the machine instructions acceptable to the assembler. Detail explanations of the

operation of the machine instructions may be found in the USACSCS-TF-4-3 AN/GYK-12 Frinciples of Operation Manual.

### 4-2. Machine Instruction Format

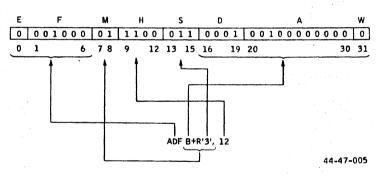

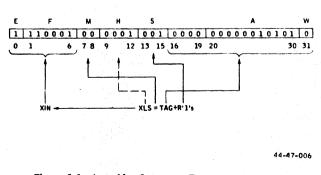

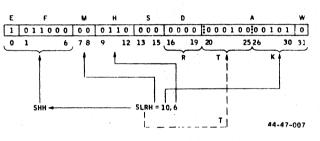

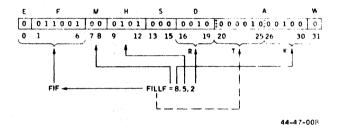

The assembler language machine instruction format follows the general assembler source input format described in Chapter 3. Figure 4-1 illustrates the construction of a machine instruction. Figure 4-2 shows how a sample assembler language machine instruction is assembled.

Figure 4-1. Construction of Assembler Language Machine Instruction

Figure 4-2. Assembler Language Machine Instruction Conversion

a. Name Entry Format. The name entry contains a symbol to be used as a name. The name need not be referenced at any place in the program and is optional.

b. Function Code Entry Format (E and F fields). The function code entry must have a three letter mnemonic operation code, or a three to five letter extended mnemonic operation code.

c. Operand Entry Format. The operand entry specifies the core memory address of data to be accessed, the process register to be used as an accumulator, the process register to be used as an index register, the process register to be used as a tally register, the bit of the field to be considered (in bit manipulation instructions), or the location to which control is to be transferred (for transfer instructions). The extended mnemonic code instructions have a different operand entry format from the assembler language machine instructions and this format is discussed in Chapter 5. The machine instruction operand entry has two subfields. Each subfield is separated by a comma and the first blank terminates the operand entry. If the first subfield were not used then it would be replaced by a comma and the second subfield

#### USACSCS-TF-4-2

would appear directly following the comma with no intervening blank(s). Such an instruction would appear as:

> OPERATION OPERAND ADF .2

All unused subfields are considered to be ZERO.

(1) Operand subfield one. The mode, index, page, word address, and half word address fields of the computer instruction word are provided by this subfield.

(a) Addressing special symbols. Certain special symbols may be used in subfield one for specific purposes. These are discussed in detail in Chapter 3. An explanation is also provided for reference in table 4-1. If none of the special symbols is used in subfield one then the direct mode of addressing (mode 1 or 2) is indicated.

Table 4-1. Addressing Special Symbols

| Special character                                          | Meaning                                                                                                                                                                                                                                                                                         |  |  |

|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| =                                                          | An equal sign as the first character in the subfield indicates the literal mode of addressing (mode 0).                                                                                                                                                                                         |  |  |

| \$                                                         | The dollar sign symbol indicates the relative mode of addressing (mode 2).                                                                                                                                                                                                                      |  |  |

| ()                                                         | If the first subfield is enclosed in parentheses, the indirect mode of addressing (mode 3) is indicated.                                                                                                                                                                                        |  |  |

| and exter<br>tional inf<br>may be u<br>tion. Ref<br>AN/GYK | of these addressing modes with the transfer<br>add mnemonic instructions requires addi-<br>ormation. Only the literal mode (mode 0)<br>sed with the extended mnemonic instruc-<br>er to the USACSCS-TF-4-3<br>-12 Principles of Operation Manual for<br>on regarding the transfer instructions. |  |  |

#### 20079-2

The special symbols are as follows:

(b) The literal mode (mode 0) is indicated by an equal sign (=) appearing as the first character of the operand field.

(c) The relative mode (mode 2) is indicated by a dollar sign (\$) appearing anywhere within subfield one. The dollar sign also denotes the value of the instruction location register (ILR). (d) The direct mode with double indexing (mode 2) is indicated by a double indexing term appearing anywhere within subfield one of the operand.

(e) The indirect mode (mode 3) is indicated by a left parenthesis (() appearing as the first character in the operand field. The mode is contained in the M field of the machine instruction.

Table 4-2 lists the nine possible addressing mode combinations with their corresponding symbolic representations in subfield one.

Examples showing the use of each of the nine possible addressing mode combinations are shown in table 4-3.

#### NOTE

All the instructions in table 4-3 take place as one smooth operation. There are no partial results or distinct steps requiring auxiliary storage, concerning the programmer. In these operations, any partial results or distinct steps indicated in the explanations in the examples are used for the purpose of illustration only. Examples of the use of the special symbols are shown in table 4-4.

(f) Indexing. Indexing is indicated by the appearance of an index register term in subfield one. An index register term is indicated by the special character R followed by the process register number (1-7) enclosed in single quotation marks. If the indexing term is immediately preceded by any other operation indicator but the plus sign (+), the expression will not be correctly evaluated and no error symbol will be placed by the assembler. (The value of the index register will always be added when the addressing mode with indexing is specified.) The S field of the instruction word will be loaded with the indexing register specified and normal indexing execution will take place. If the index register specified is not within the limits 1-7, the assembler will generate an L (limit) error symbol. The indexing register term may appear anywhere within subfield one except as the first term. If mode 2 (relative) is indicated with the presence of the \$ symbol in subfield one and if the S field is ZERO, no indexing will be used. The only acceptable indexing value for the relative mode is register one. Any index register value other than one is

illegal. If the direct mode with double indexing (no special symbols in the operand and the D, double indexing term used), then mode 2 will also be selected but the only acceptable registers for double indexing are registers 2-7. Double indexing may not be used with any mode other than direct addressing (mode 2).

(2) Operand subfield two. The accumulator

(H field) of the machine instruction is specified by this subfield for all instructions, except move into upper byte (MIU) and move into lower byte (MIL), which use two operand subfields. Any term or expression may appear in this subfield with the exception of the double indexing term (D'N'). The limitation on the value of this subfield is 15 for all instructions except MIU and MIL for which the limitation is 255.

| Addressing mode<br>M S |     | ddressing mode              | Symbolic representation (in ranges from 1 through 7) |  |  |

|------------------------|-----|-----------------------------|------------------------------------------------------|--|--|

| 0                      | 0   | literal                     | = Y                                                  |  |  |

| 0                      | 1-7 | literal with indexing       | = Y+R'n'                                             |  |  |

| 1                      | 0   | direct                      | Y                                                    |  |  |

| 1                      | 1-7 | direct with indexing        | Y+R'n'                                               |  |  |

| 2                      | 0   | relative                    | Y -\$ or Y+\$                                        |  |  |

| 2                      | 1   | relative with indexing      | Y-\$+R'1' or Y+\$+R'1'                               |  |  |

| 2                      | 2-7 | direct with double indexing | Y+D'm'(m=2-7)                                        |  |  |

| 3                      | 0   | indirect                    | (Y)                                                  |  |  |

| 3                      | 1-7 | indirect with indexing      | (Y+R'n') or (Y)+R'n' (See note 1)                    |  |  |

Table 4-2. Addressing Mode Combinations (Transfer Instructions Excluded)\*

20079-3

A . A

| Mode with example<br>LITERAL (MODE=0, S=0)<br>ADF = Y, 10<br>Note: If a symbol is used, the address or value<br>(EQU) of the symbol will be placed into the<br>A field of the instruction by the assembler. If<br>the symbol is undefined, an error will be<br>generated. |          | Aode with example         Assumptions                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                     |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                                                                                                                                                                                                           |          | ADF = Y, 10of the instruction contains 200.instruction, whi<br>tents of registerte: If a symbol is used, the address or value<br>QU) of the symbol will be placed into the<br>field of the instruction by the assembler. If<br>symbol is undefined, an error will be2)Register 10 contains 300.Store the result,<br>The previous co<br>have now been to<br>the symbol is undefined, an error will be |                                                                                                                                                                                     |  |