MAGNETIC TAPE WORD PROCESSOR

OPERATION, SERVICE, AND DIAGRAMS MANUAL

UD002441-1

2,197.

SEPT., 1972

This information is current as of September 1972.

Technical Support Operations 10435 North Tantau Avenue Cupertino, California 95014 Tel: (408) 257-6220 TWX 910-338-0280

Printed in U.S.A. September 1972 Copyright © 1972

# CONTENTS

| Chapter |                   |              |         |        |       |   |   |   |   |   |   |     | Page  |

|---------|-------------------|--------------|---------|--------|-------|---|---|---|---|---|---|-----|-------|

| 1       | GENERAL INFOR     | MATION.      |         | • •    |       | • | • | • |   | • |   | •   | 1-1   |

|         | 1.1 Introduction  | •••          | • •     |        |       | • | • |   |   |   |   | •   | 1-1   |

|         | 1.2 Manual Con    | tent         | • •     |        | • •   | • | • | • |   |   |   |     | 1-1   |

|         | 1.2.1 Chapter     | 1, General   | Inform  | ation  | • •   | • | • | • |   | • | • | •   | 1-1   |

|         | 1.2.2 Chapter     | 2, Installat | ion .   |        |       |   | • | • | • |   | • | •   | 1 - 2 |

|         | 1.2.3 Chapter     | 3, Operatio  | n.      |        | • •   | • | • | • | • |   | • | •   | 1 - 2 |

|         | 1.2.4 Chapter     | 4, Theory o  | of Oper | ration |       | • | • | • |   |   | • | •   | 1 - 2 |

|         | 1.2.5 Chapter     | 5, Maintena  | ince    |        |       | • | • |   |   |   |   | •   | 1 - 2 |

|         | 1.2.6 Chapter     | 6, Checks a  | nd Ad   | justm  | ents  | • | • | • |   |   | • | •   | 1 - 2 |

|         | 1.2.7 Chapter     | 7, Error A   | nalysis | ι.     |       |   |   |   | • |   | • | •   | 1 - 2 |

|         | 1.2.8 Chapter     | 8, Replacer  | nent P  | roced  | lures | • | • |   |   |   |   |     | 1 - 2 |

|         |                   | 9, Diagram   |         |        |       |   |   |   |   |   |   |     | 1 - 2 |

|         | 1.3 System Des    |              |         |        |       |   |   |   |   |   | • |     | 1 - 2 |

|         |                   | cessor .     |         |        |       |   |   |   |   |   |   |     | 1-3   |

|         |                   | ι            |         |        |       |   |   |   |   |   |   |     | 1-3   |

|         |                   |              |         |        |       |   |   |   |   |   |   |     | 1-4   |

|         |                   | Tape Tran    |         |        |       |   |   |   | • |   |   |     | 1-4   |

|         | 1.4 Specification |              | -       |        |       |   |   |   |   |   |   | •   | 1-5   |

| 2       | INSTALLATION      |              |         |        |       |   | - |   |   | _ |   |     | 2-1   |

|         | 2.1 Unpacking     |              |         |        |       |   |   |   |   |   |   |     | 2-1   |

|         |                   | g the Typev  |         |        |       |   |   |   |   |   |   |     | 2-1   |

|         | -                 | g the Conso  |         |        |       |   |   |   |   |   |   | •   | 2-1   |

|         | 2.2 System Inter  | -            |         |        |       |   |   |   | • | • | • | •   | 2-3   |

|         | 2.3 Preoperatio   |              |         |        |       |   |   |   |   | • | • | •   | 2-5   |

|         |                   | pply Voltag  |         |        |       |   |   |   |   |   |   | •   | 2-5   |

|         |                   | )iagnostic C | -       |        | •••   |   |   |   |   |   |   | •   | 2 - 7 |

| 3       | OPERATION .       |              |         |        |       |   |   |   |   |   |   |     | 3–1   |

|         | 3.1 Keys, Contr   | rols Indica  | tors a  | nd Als | arms  | • | • | • | • | • | • | •   | 3-1   |

|         | 3.1.1 Basic Op    | •            |         |        |       |   |   | • | • | • | • | •   | 3-1   |

|         |                   | ys           |         |        |       |   |   | • | • | • | • | •   | 3-4   |

|         |                   | ey <b>s</b>  |         |        |       |   |   | • | • | • | • | •   | 3-6   |

|         |                   | Function K   |         |        |       |   |   |   |   |   |   |     | 3-8   |

|         |                   | Controls an  | -       |        |       |   | • |   | • | • | • | •   | 3-11  |

|         |                   |              |         |        |       | • | • | • | • | • | • | •   | 3-11  |

|         | 3.2 Operating Ir  |              |         |        |       | • | • | • | • | • | • | . • | 3-12  |

|         | 5.2 Operating II  | istructions  | •••     | •••    | •••   | • | • | • | • | • | • | •   | 3-13  |

| 4       | THEORY OF OPE     | RATION.      | •••     | •••    |       |   |   | • |   | • | • | •   | 4-1   |

|         | 4.1 Functional I  | Description  |         | • •    |       | • |   | • | • | • | • | •   | 4-1   |

|         | 4.2 Microproces   | ssor         | • •     | •••    | • •   | • |   |   | • | • | • | •   | 4-1   |

|         |                   | y Memory     |         |        |       |   |   |   |   | • | • | •   | 4-1   |

|         |                   | lress Regis  |         |        |       |   |   |   |   |   | • | •   | 4-6   |

# CONTENTS (CONT)

# Chapter

## Page

| 4.2.3 Return Address Register                     | 4-7          |

|---------------------------------------------------|--------------|

| 4.2.4 General Purpose (GP) and Main (M) Registers | 4-8          |

| 4.2.5 Arithmetic Logic Unit (ALU)                 | 4-8          |

| 4.3 Buffer I/O and Buffer Control                 | 4-8          |

| 4.4 Tape Control                                  | 4-9          |

| 4.5 Write Encode                                  | 4-9          |

| 4.6 Read Decode                                   | 4-9          |

| 4.7 Tape Read/Write and Tape Read Only            | 4-10         |

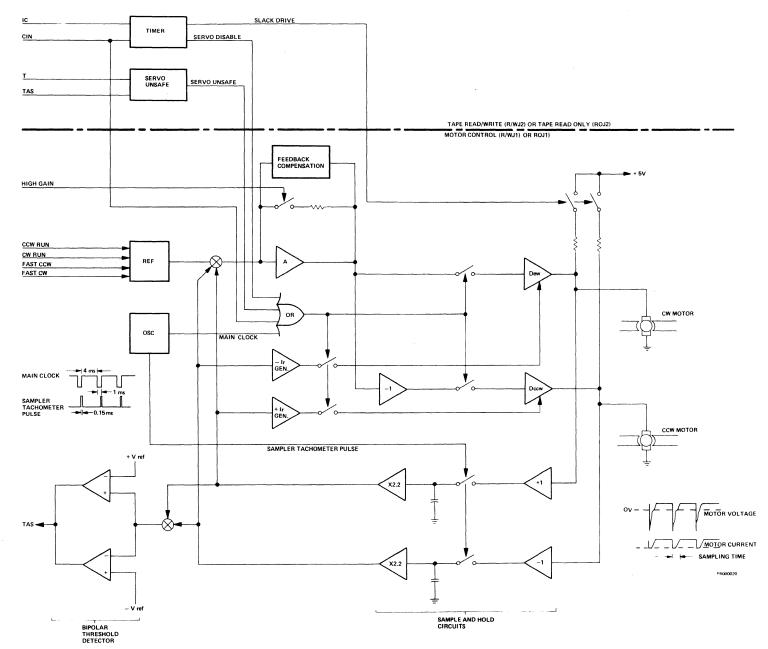

| 4.8 Motor Control                                 | 4-10         |

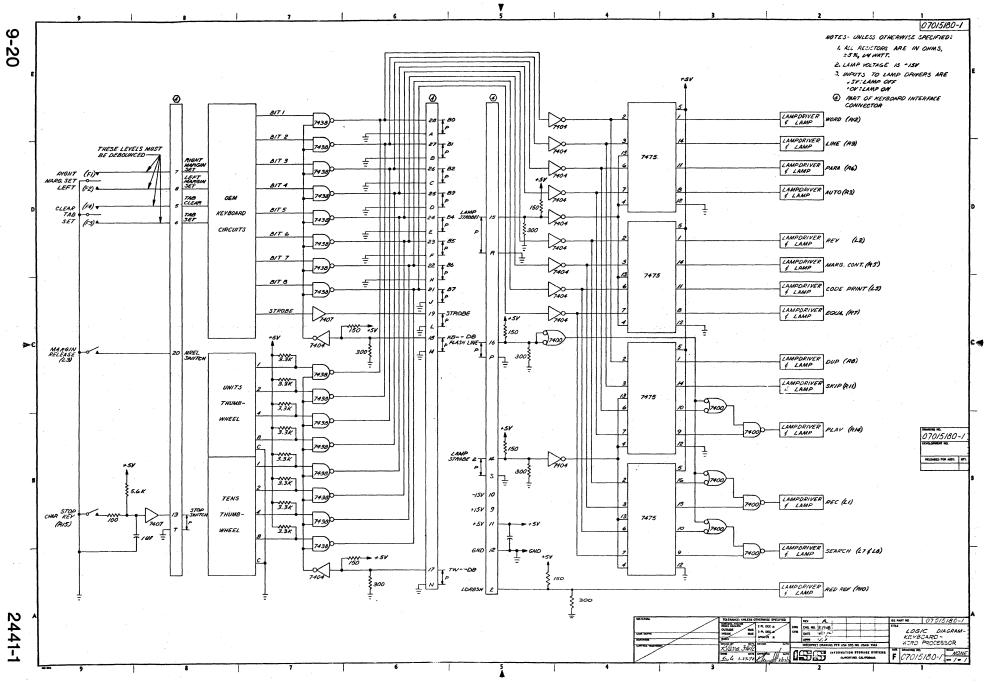

| 4.9 Keyboard Interface                            | 4-12         |

| 4.10 Printer Interface                            | 4-12         |

| 4.11 Miscellaneous, Clock and IC                  | 4-13         |

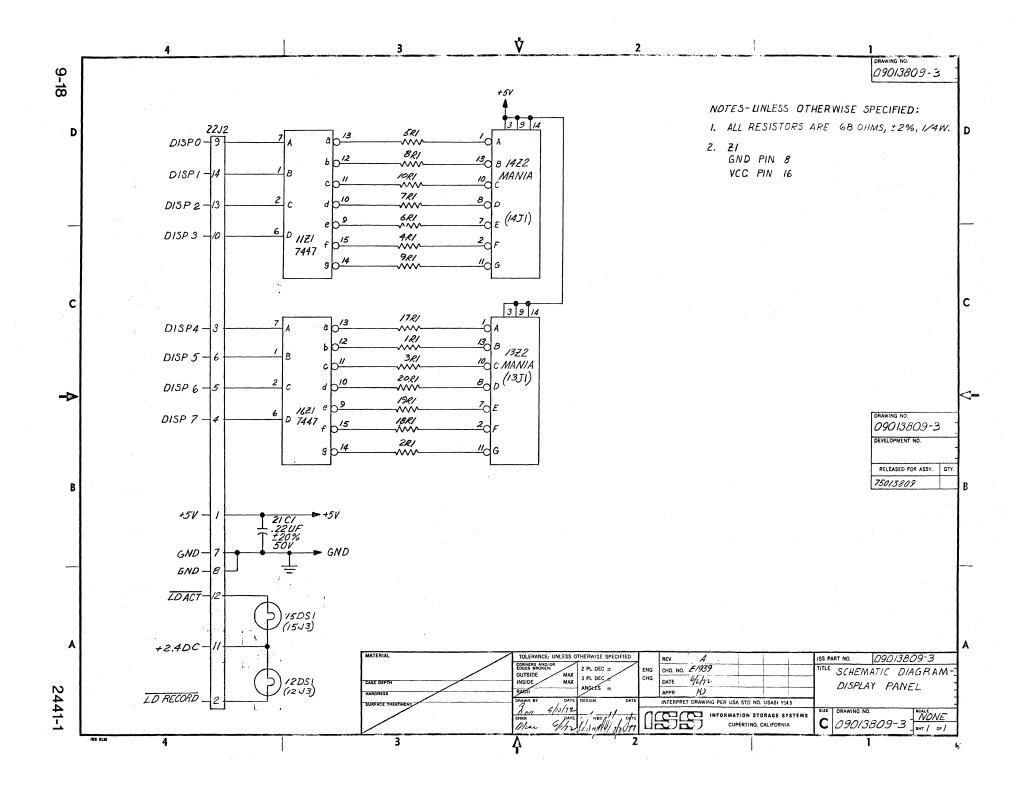

| 4.12 Display Panel                                | 4-13         |

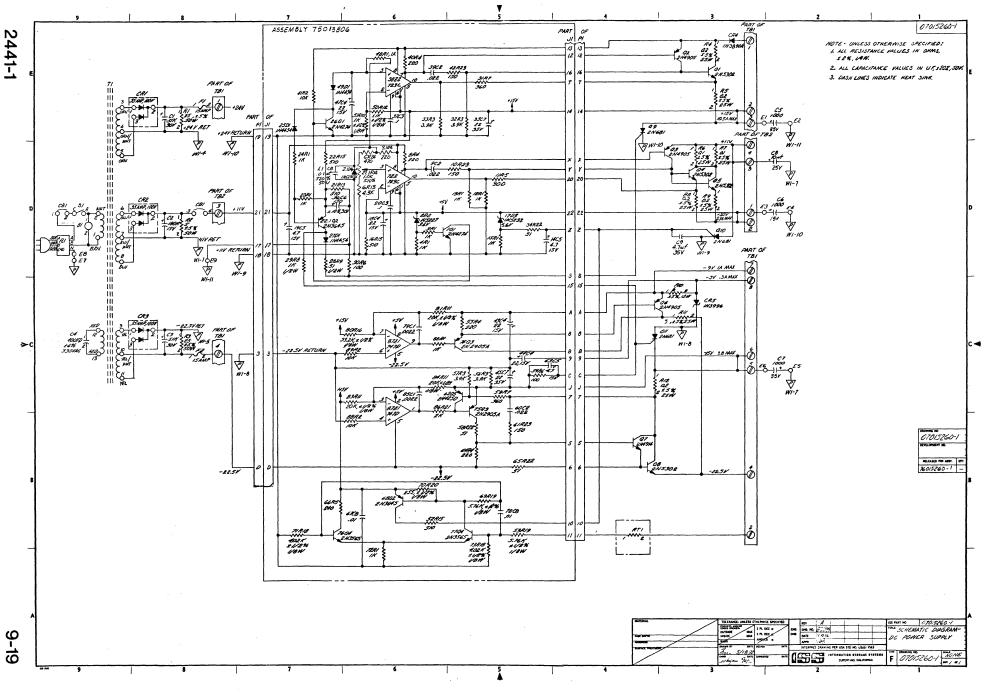

| 4.13 DC Power Supplies                            | 4-13         |

|                                                   |              |

| MAINTENANCE                                       | 5-1          |

| 5.1 Safety Precautions                            | 5-1          |

| 5.2 Maintenance Philosophy                        | 5-1          |

| 5.2.1 Objectives                                  | 5-1          |

| 5.2.2 Basic Considerations                        | 5-1          |

| 5.3 Tools and Servicing Aids                      | 5-2          |

| 5.3.1 Tools                                       | 5-2          |

| 5.3.2 Test Equipment                              | 5-2          |

| 5.4 Power Supply Voltage                          | 5-2<br>5-6   |

| 5.4.1 Voltage Levels                              | 5-6          |

| 5.4.2 Logic Levels $\ldots$                       | 5-6          |

| 5.4.3 Use of Probes                               | 5-7          |

|                                                   | 0-1          |

| CHECKS AND ADJUSTMENTS                            | 6-1          |

| 6.1 General.                                      | 6-1          |

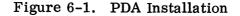

| 6.2 PDA Installation                              | 6-1          |

| 6.3 ROM Test                                      | 6-6          |

| 6.4 Branch Test                                   | 6-7          |

| 6.5 Branch on Data Test                           | 6-9          |

| 6.6 PDA Test                                      | 6-10         |

| 6.7 G-Registers Test                              | 6-10         |

| 6.8 H-Registers Test                              | 6-11         |

| 6.9 ALU Test                                      | 6-12         |

| 6.10 Buffers Test                                 | 6-13         |

| 6.11 Data Bus Out (Lamp) Test.                    | 6-13         |

|                                                   | 6-15         |

| 6.12 Data Bus In (Thumbwheel) Test                | 6-15<br>6-16 |

| 6.13 Keyboard Strobe Test6.14 Printer Test        | 6-10<br>6-17 |

|                                                   | 6-18         |

| 6.15 Transport Tests                              | 6-18<br>6-18 |

| 6.15.1 Run Forward Normal Test                    | 0-19         |

5

6

# CONTENTS (CONT)

| Chapter              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Page       |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|                      | 6.15.2 Run Reverse Normal Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6-20       |

|                      | 6.15.3 Run Forward Fast Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6-21       |

|                      | 6.15.4 Run Reverse Fast Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6-22       |

|                      | 6.15.5 Speed Tests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6 - 23     |

|                      | 6.15.6 Normal Write Forward Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6-26       |

| 7                    | ERROR ANALYSIS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7-1        |

| •                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7-1        |

|                      | 7.1       General       General | 7-1        |

|                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |

| 8                    | REPLACEMENT PROCEDURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8-1        |

|                      | 8.1 General                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 8-1        |

|                      | 8.2 Printer Removal and Installation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8-1        |

|                      | 8.3 Keyboard Removal and Installation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 8-1        |

|                      | 8.4 Transport Removal and Installation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8-2        |

|                      | 8.4.1 Head Assembly Removal and Installation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 8-4        |

|                      | 8.4.2 Motor Removal and Installation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8-6        |

|                      | 8.4.3 Lock Solenoid Removal and Installation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 8-6        |

|                      | 8.4.4 BOT/EOT Sensor Assembly Removal and Installation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 8-7        |

|                      | 8.4.5 Cassette In Place Switch and File Protect Switch Removal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            |

|                      | and Installation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 8-8        |

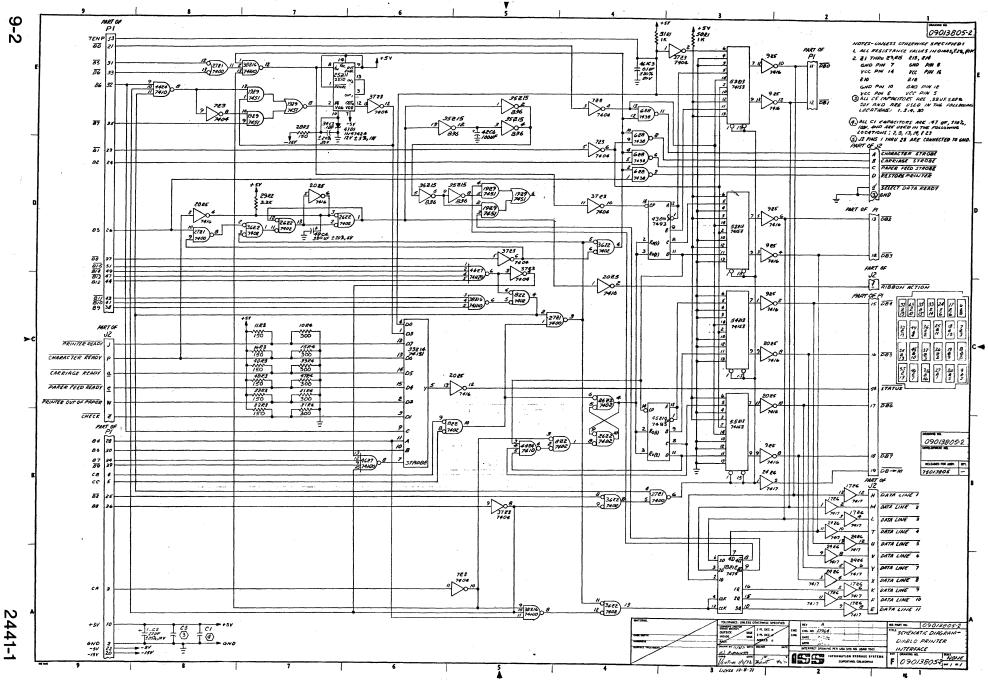

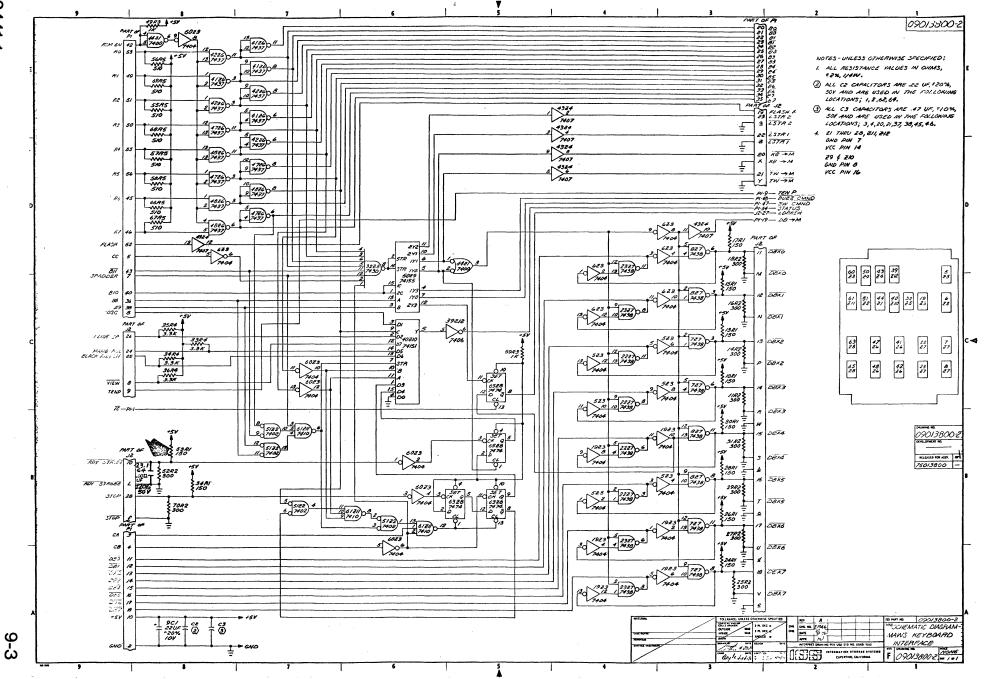

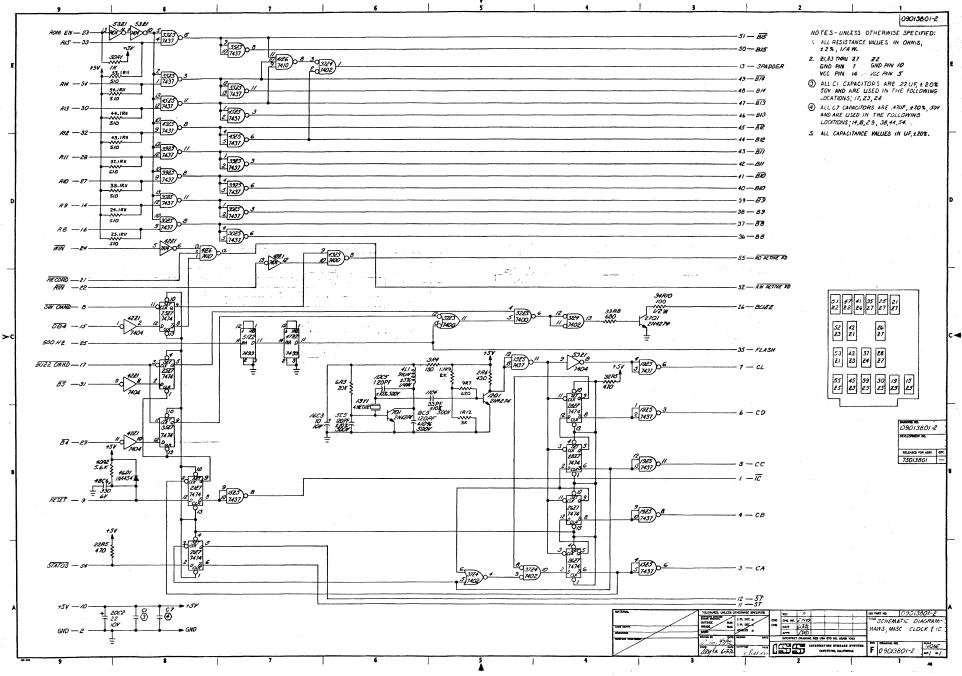

| 9                    | DIAGRAMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 9-1        |

|                      | 9.1 General                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 9-1        |

|                      | 9.2 System Wire List                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 9-24       |

|                      | ILLUSTRATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |

| Fimme                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>D</b>   |

| Figure               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Page       |

| 1-1                  | Magnetic Tape Word Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1-1        |

| 1 - 2                | Simplified System Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1 - 3      |

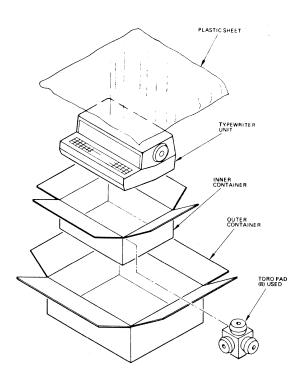

| 2-1                  | Typewriter Unit Packaging                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2-2        |

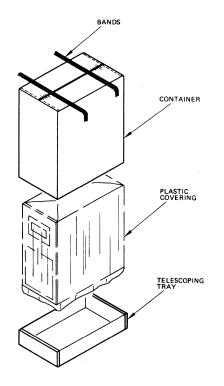

| $2-1^{\circ}$<br>2-2 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-2<br>2-2 |

|                      | Console Unit Packaging                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

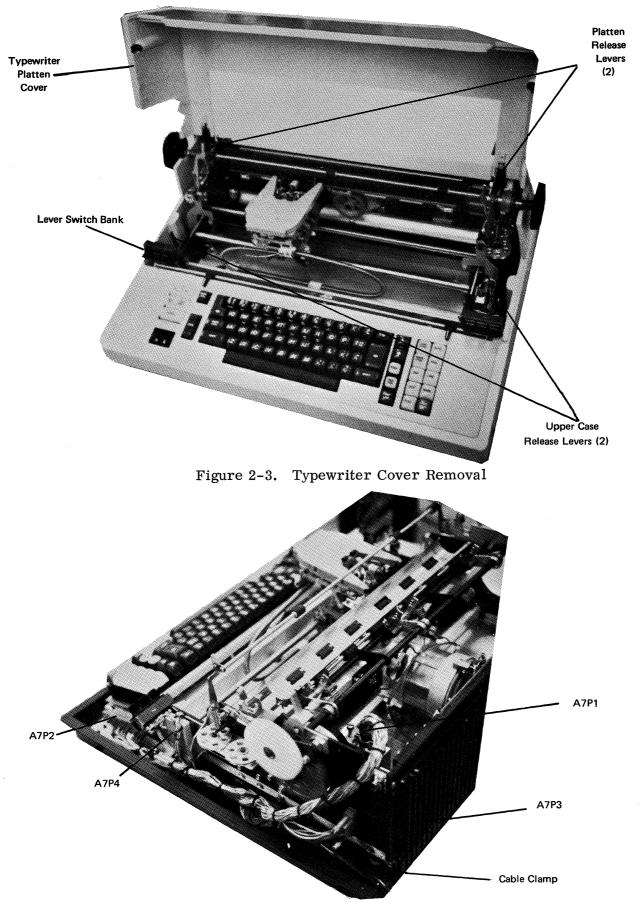

| 2-3                  | Typewriter Cover Removal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2-4        |

| 2-4                  | System Interconnections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2-4        |

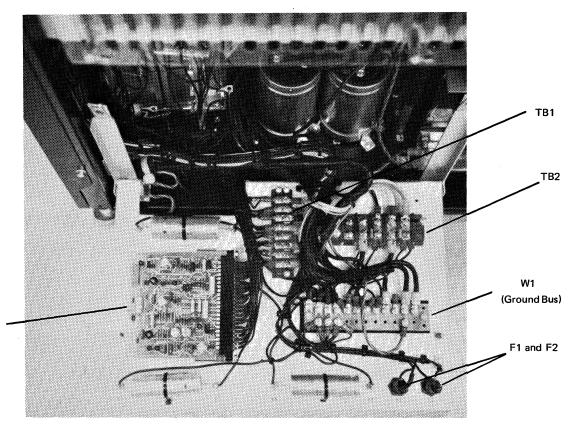

| 2-5                  | Power Supply Interconnect Panel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-6        |

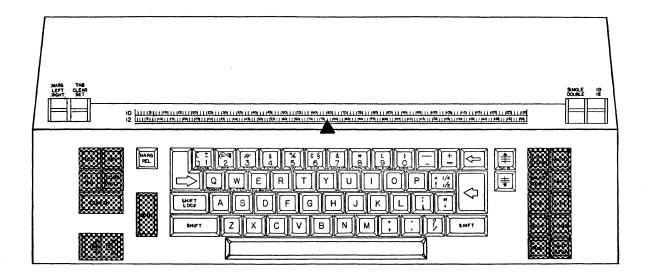

| 3-1                  | Basic Operation Keys                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3-1        |

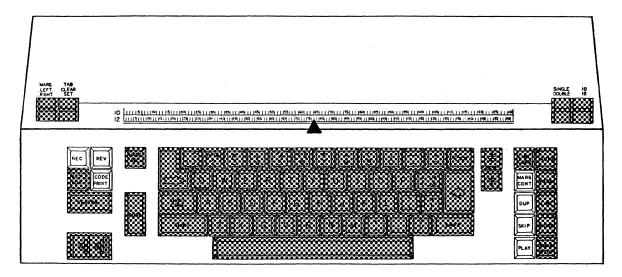

| 3-2                  | Mode Keys                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3-4        |

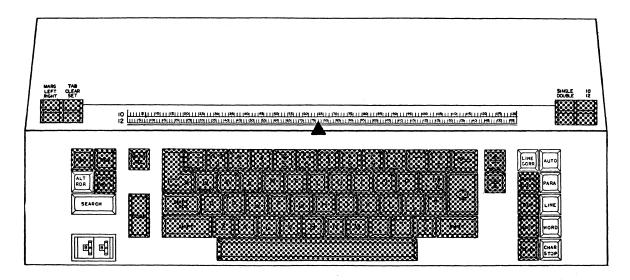

| 3-3                  | Action Keys                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3-6        |

| 3-4                  | Encoded Function Keys.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3-8        |

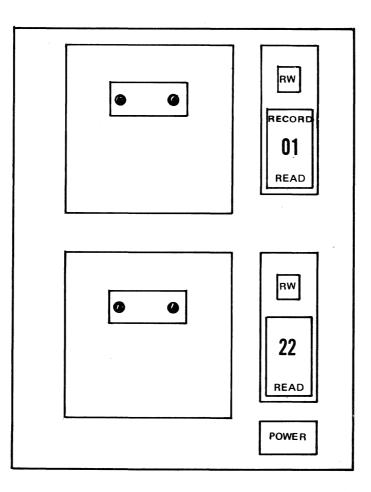

| 3-5                  | Console Controls and Indicators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3-11       |

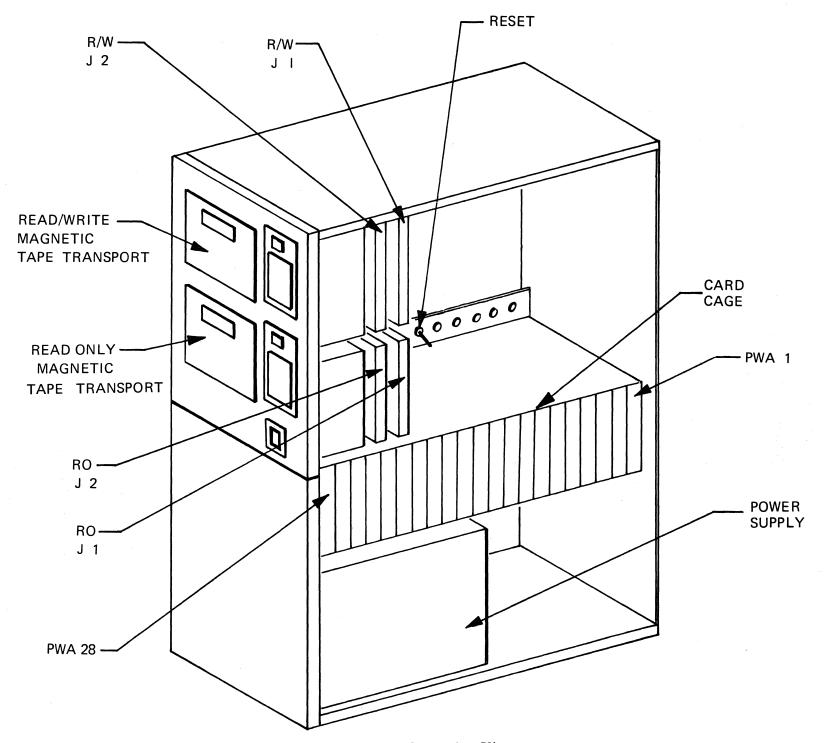

| 4-1                  | Console, Right-Hand Interior View                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4-2        |

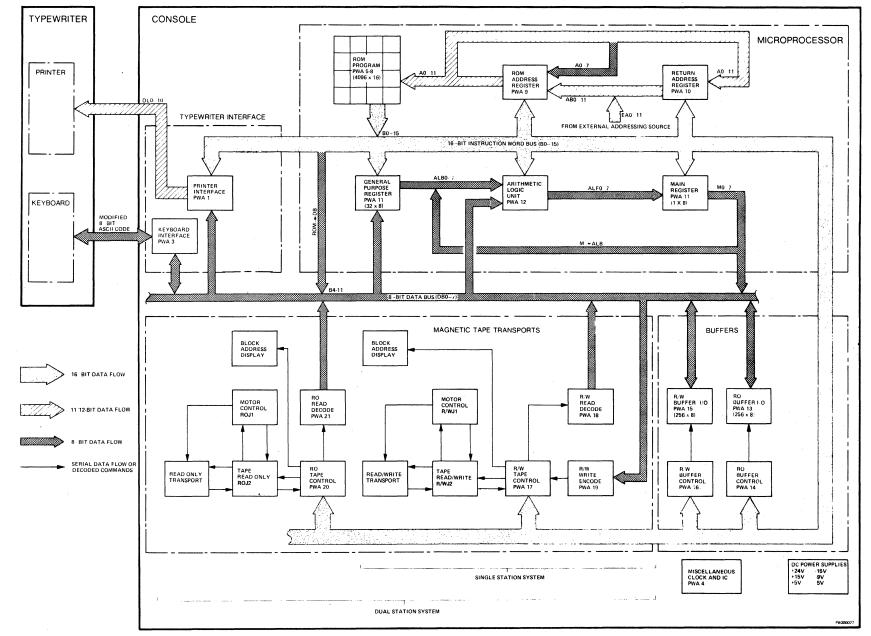

| 4-2                  | Detailed System Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4-4        |

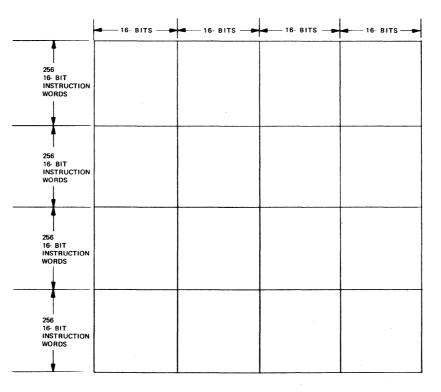

| 4-3                  | K-Page Memory Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4-5        |

.

# ILLUSTRATIONS (CONT)

| Figure                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Page                                                                                                                                                        |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

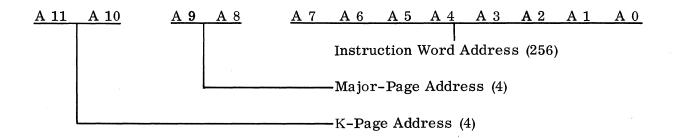

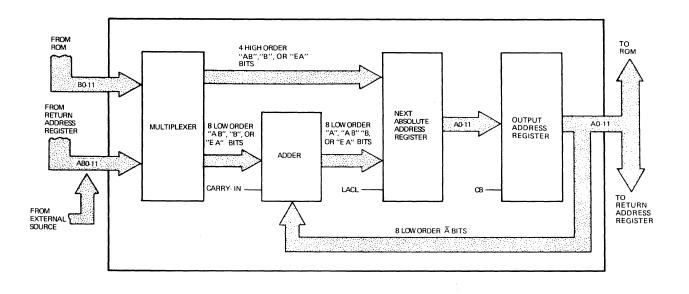

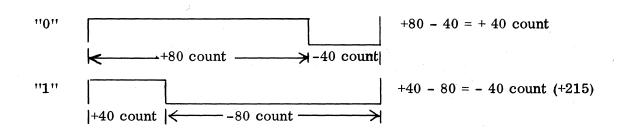

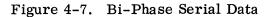

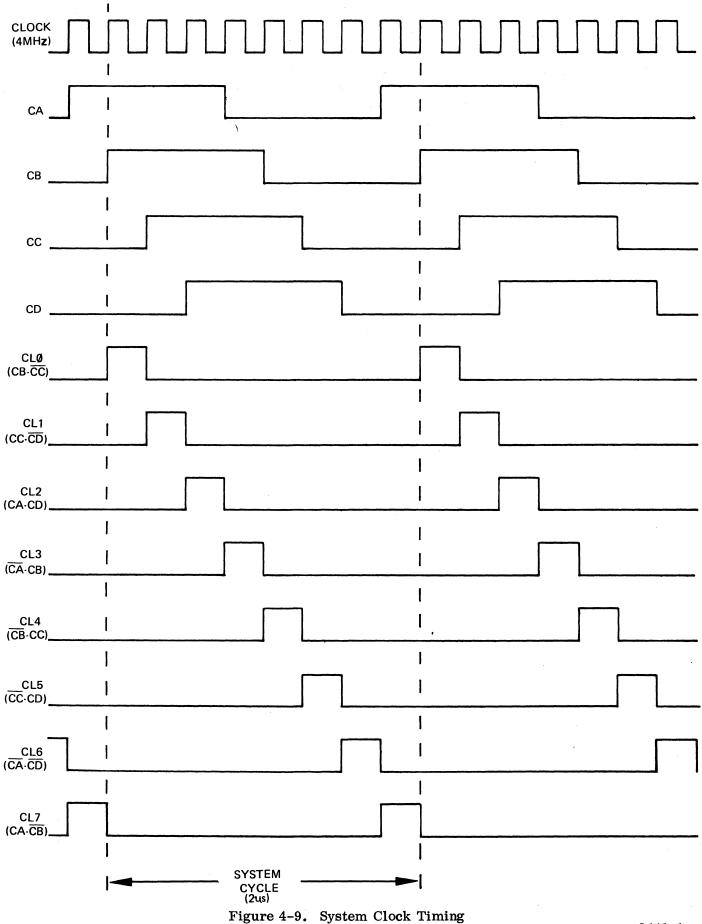

| 4-4<br>4-5<br>4-6<br>4-7<br>4-8<br>4-9 | Major-Page Memory Structure <td>4-5<br/>4-6<br/>4-7<br/>4-10<br/>4-11<br/>4-14</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-5<br>4-6<br>4-7<br>4-10<br>4-11<br>4-14                                                                                                                   |

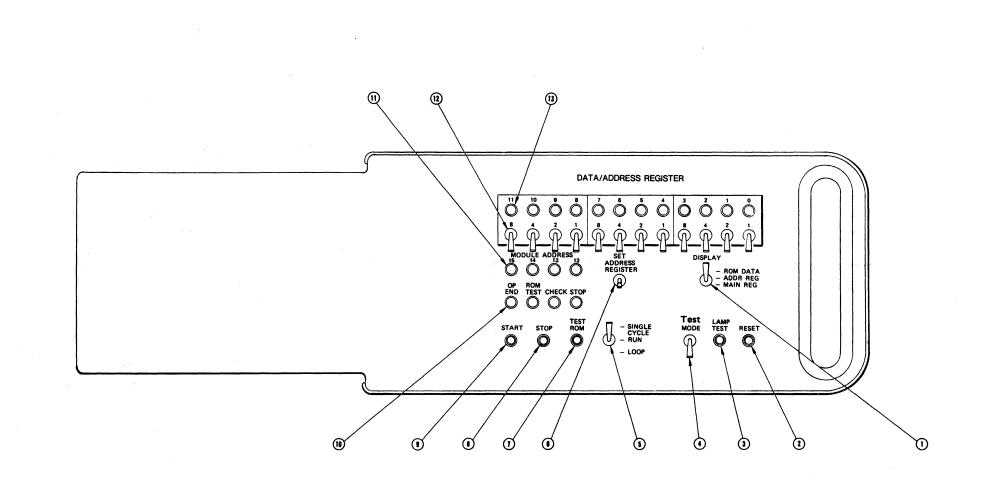

| 5-1                                    | PDA Controls and Indicators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-4                                                                                                                                                         |

| 6 <b>-1</b>                            | PDA Installation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6-1                                                                                                                                                         |

|                                        | Schematics:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                             |

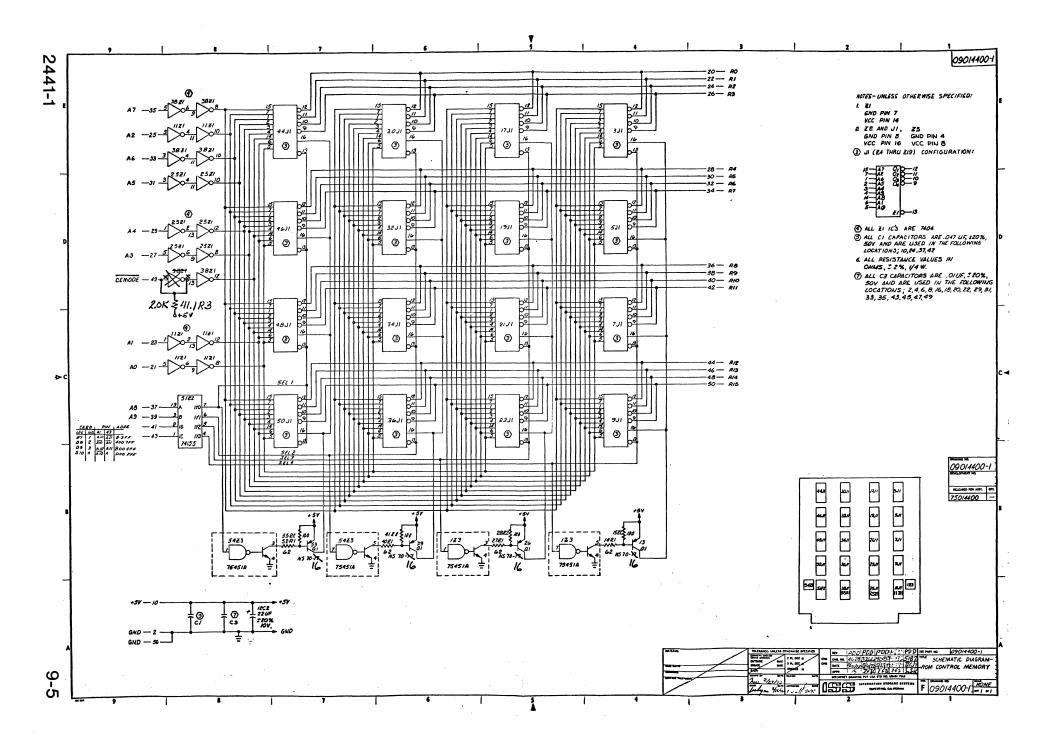

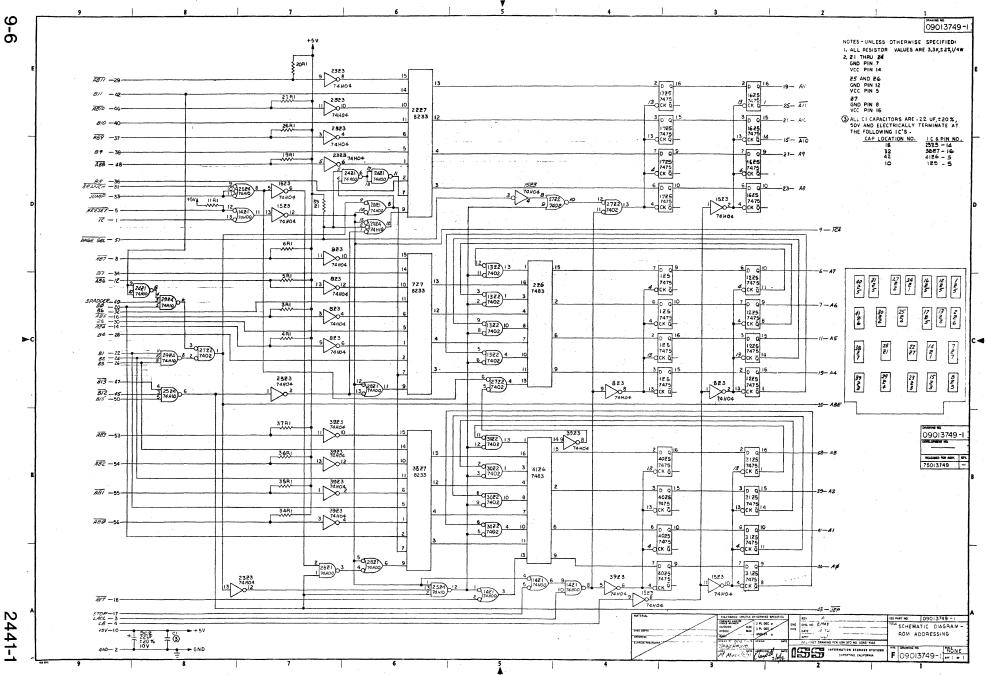

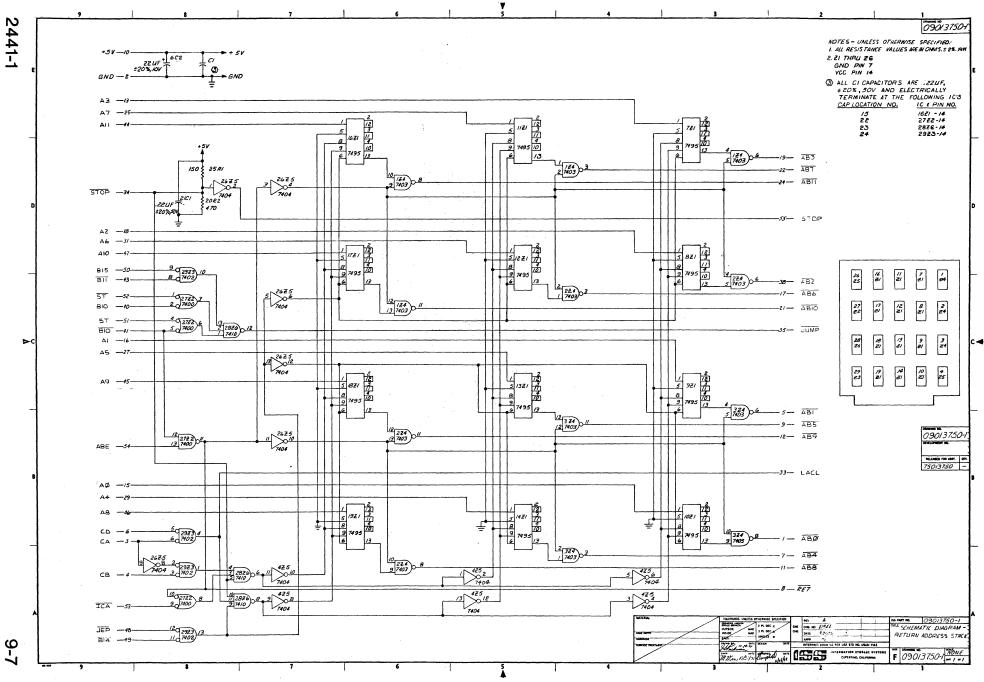

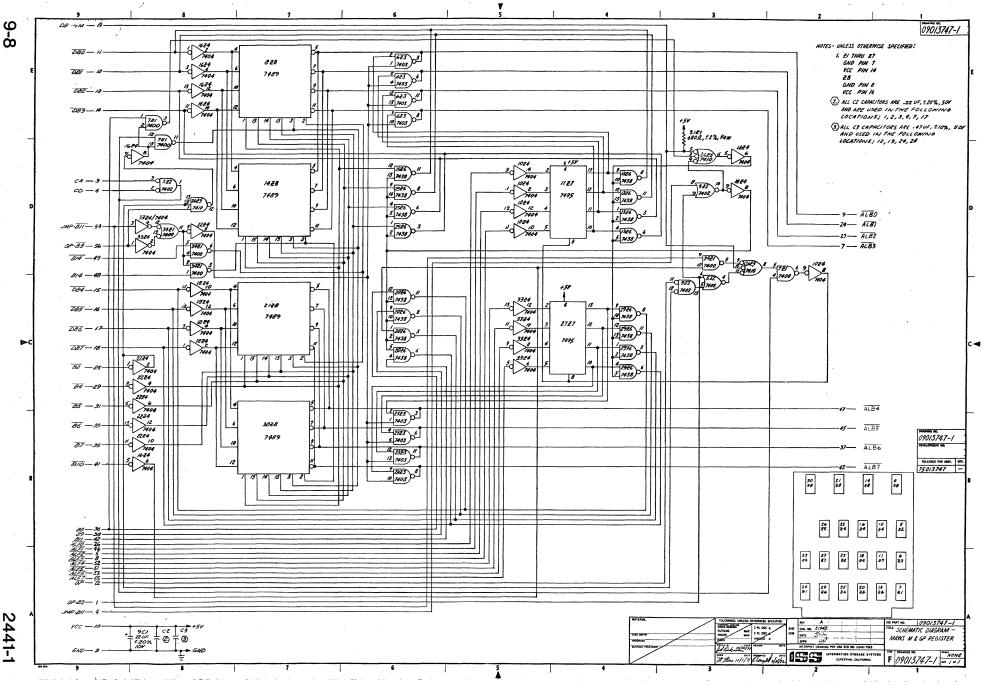

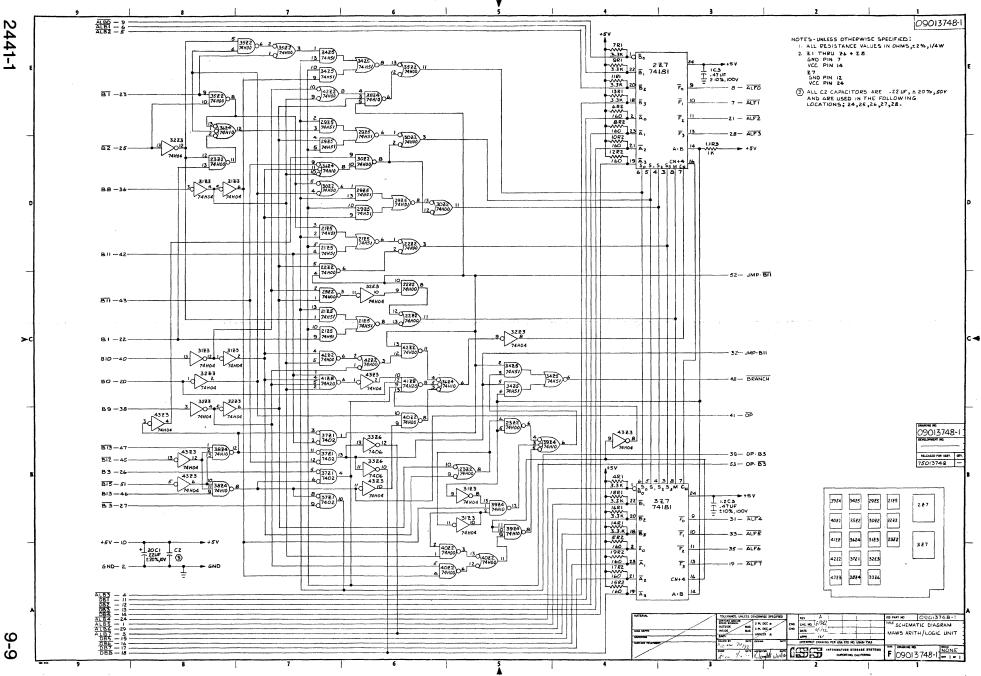

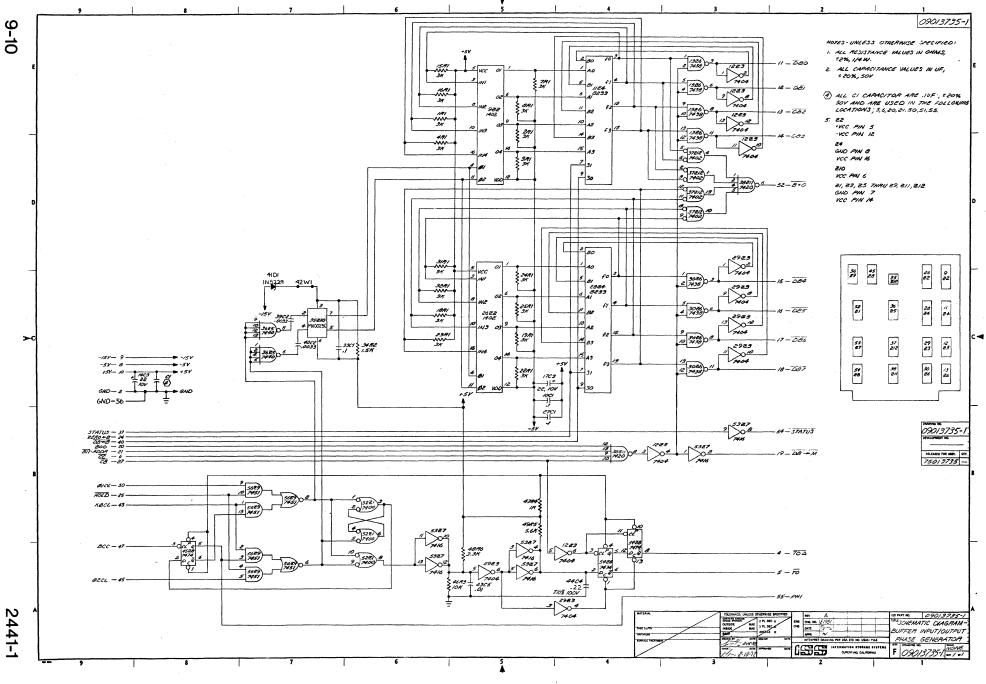

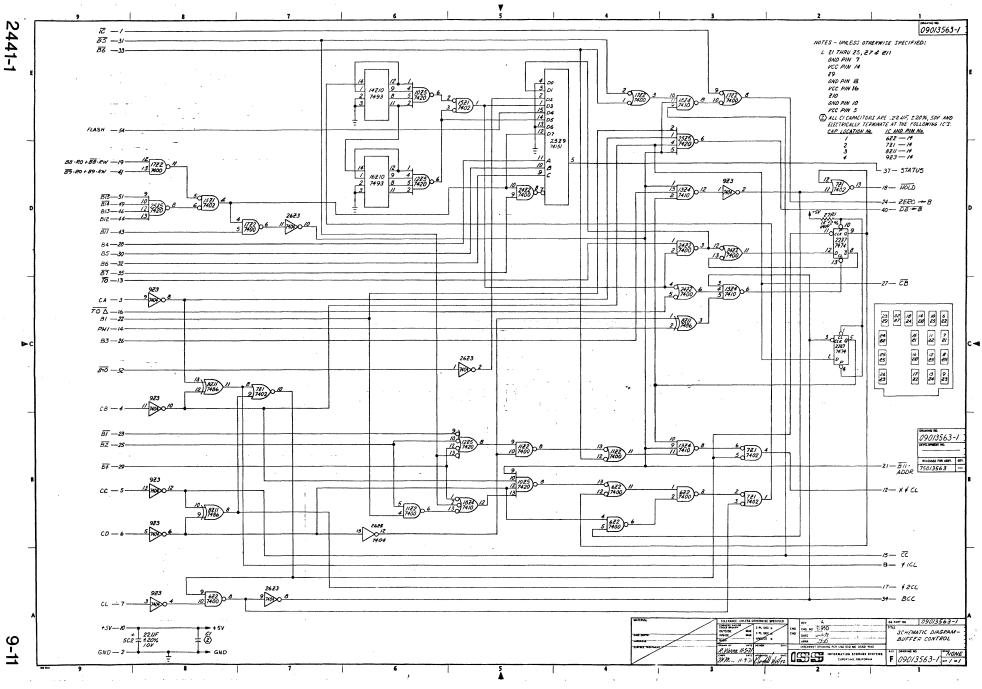

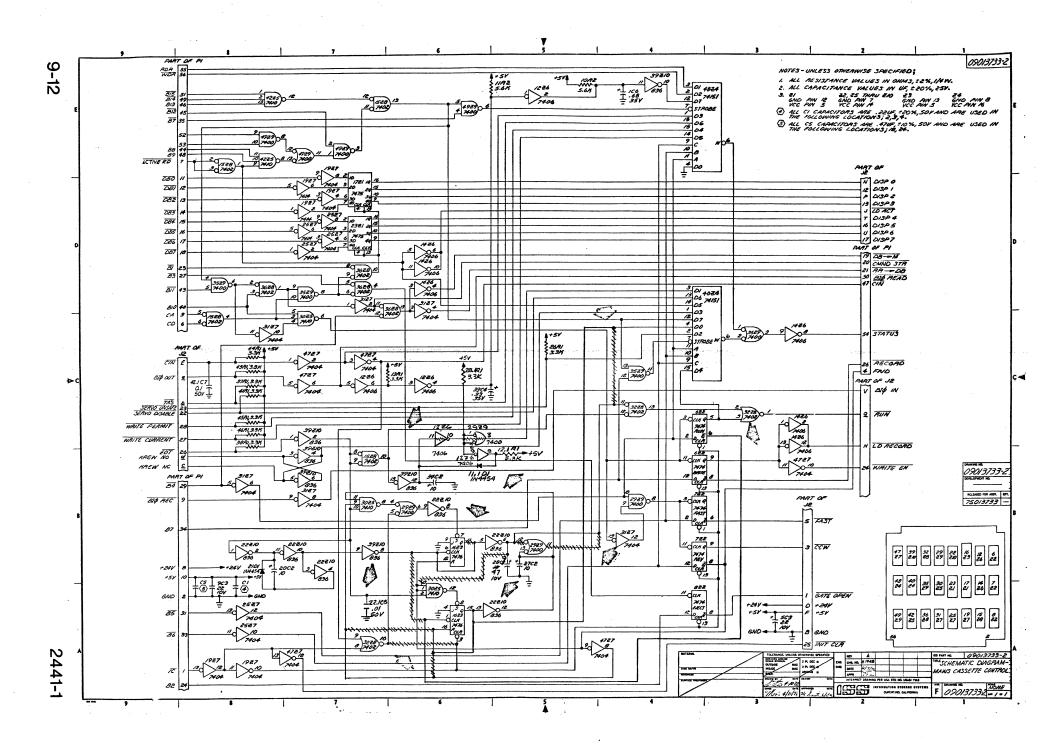

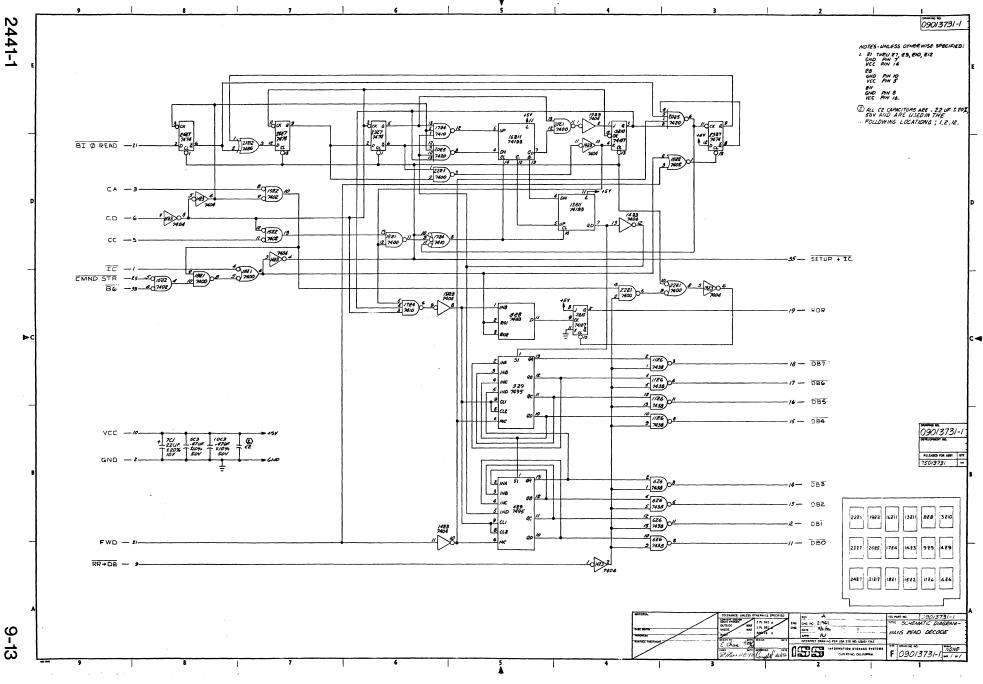

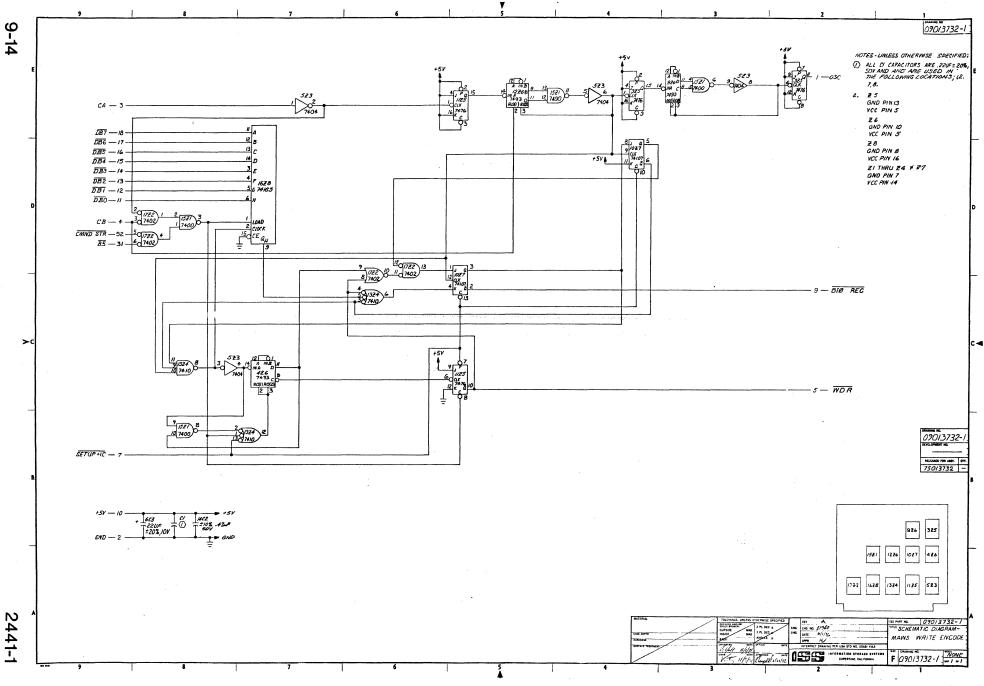

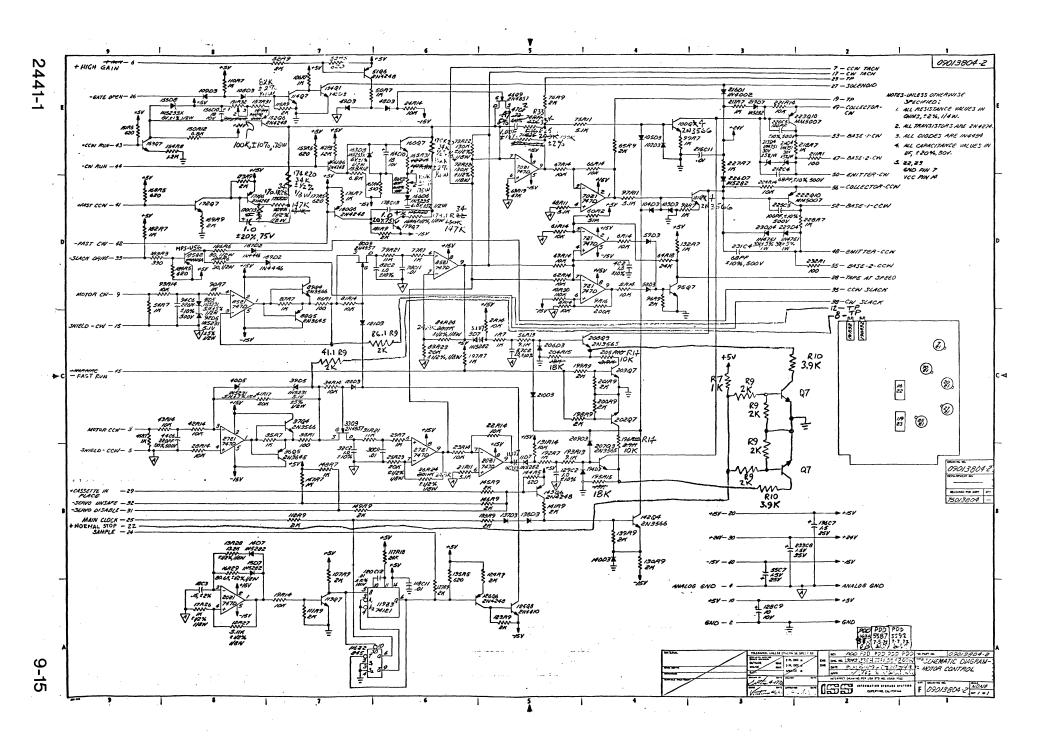

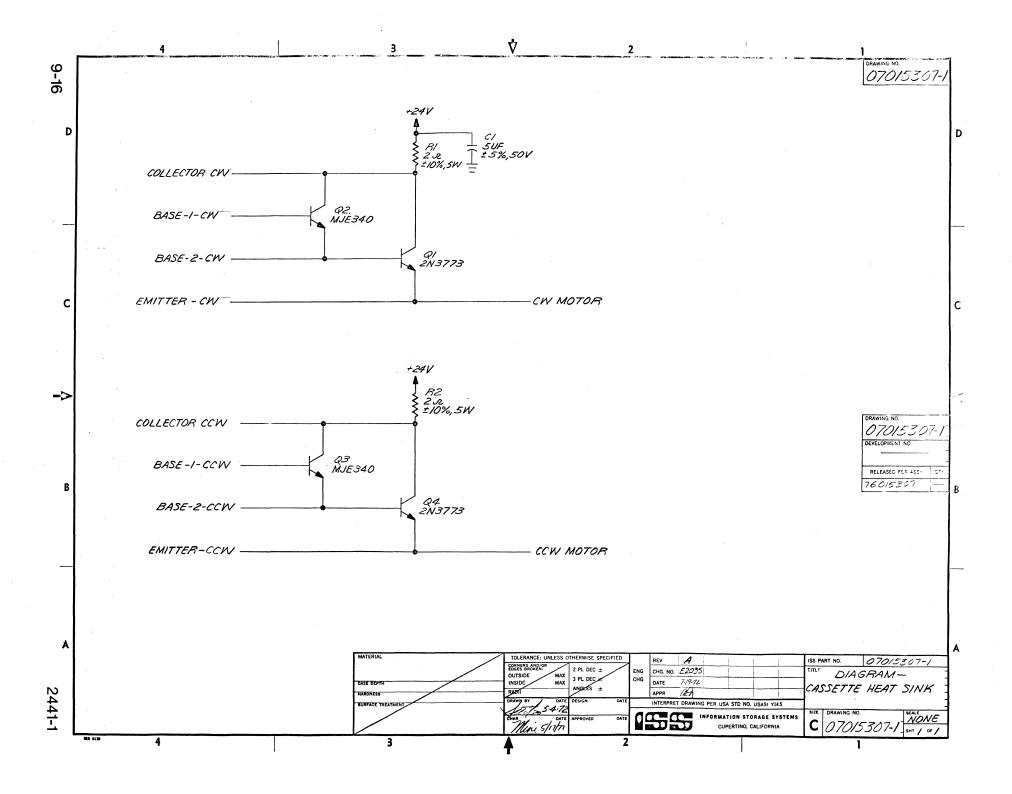

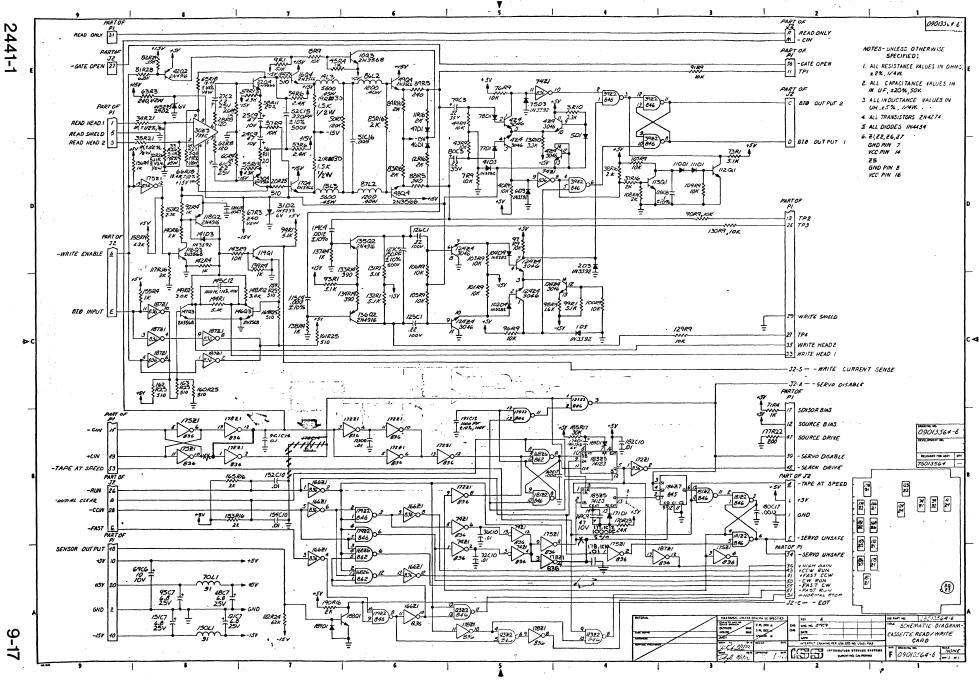

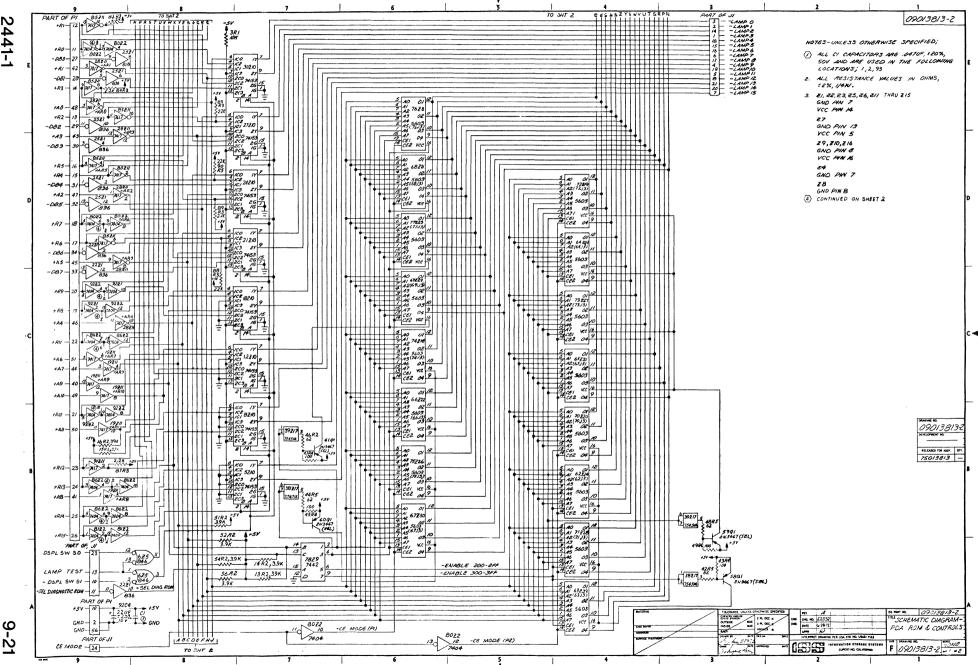

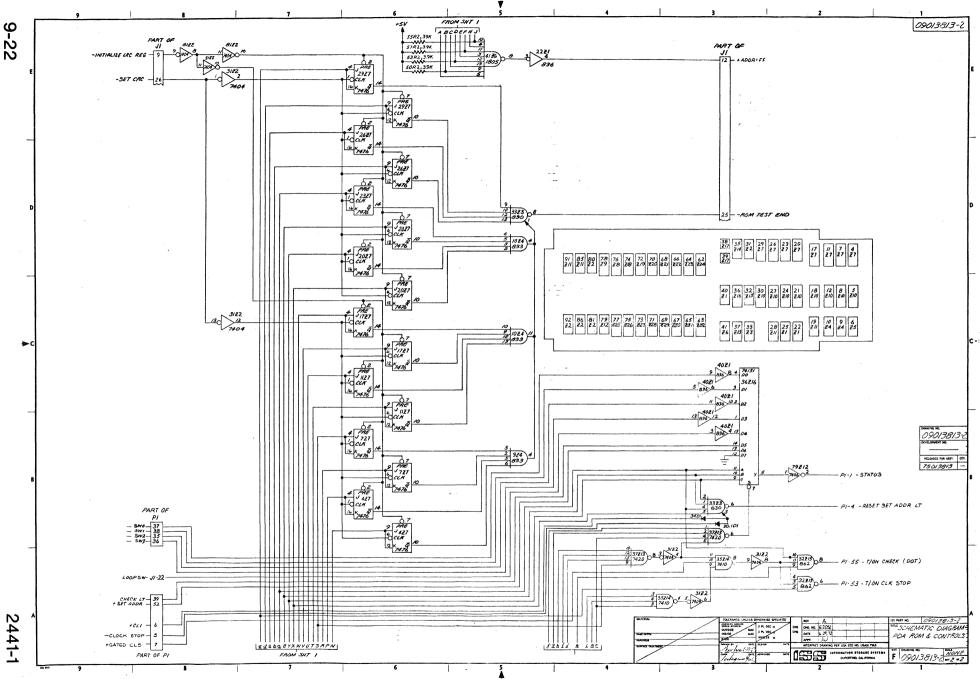

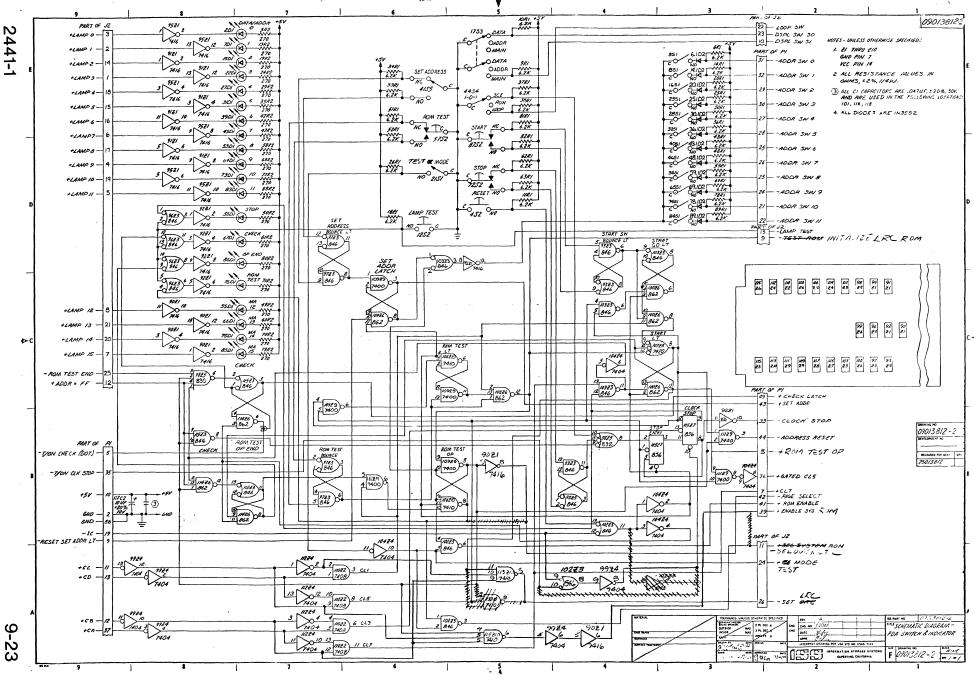

|                                        | Printer Interface (socket 1).Keyboard Interface (socket 3).Miscellaneous, Clock, and IC (socket 4)ROM Program (sockets 5, 6, 7, and 8)ROM Address Register (socket 9)Return Address Register (socket 10)Main and General Purpose Register (socket 11).Arithmetic Logic Unit (socket 12)Buffer I/O (Read Only & Read/Write) (sockets 13 and 15)Buffer Control (Read/Only & Read/Write) (sockets 14 and 16)Tape Control (Read/Write & Read Only) (sockets 17 and 20)Read Decode (Read/Write) (socket 19)Write Encode (Read/Write) (socket 19)Motor Control (sockets R/WJ1 and ROJ1).Cassette Heat SinkTape Read/Write, Tape Read Only (sockets R/WJ2 and ROJ2)Display PanelDC Power SupplyKeyboard LogicPDA ROM and Controls | 9-2<br>9-3<br>9-4<br>9-5<br>9-6<br>9-7<br>9-8<br>9-9<br>9-10<br>9-11<br>9-12<br>9-13<br>9-14<br>9-15<br>9-16<br>9-17<br>9-18<br>9-19<br>9-20<br>2.21 (2.20) |

|                                        | PDA ROM and Controls                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 9-21/9-22<br>9-23                                                                                                                                           |

|                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                             |

# TABLES

| Table      |                                                 |    |   |   |   |   |   |   |   |   |   |   | Page |

|------------|-------------------------------------------------|----|---|---|---|---|---|---|---|---|---|---|------|

| 1-1        | Dual Station MTWP Specification                 | s. | • | • | • | • | • | • | • | • | • | • | 1-5  |

| 2-1        | Power Supply Voltages                           | •  | • | • | • | • | • | • | • | • | • | • | 2-7  |

| 3-1<br>3-2 | Encoded Function Codes<br>Encoded Function Keys |    |   |   |   |   |   |   |   |   |   |   |      |

# TABLES (CONT)

| Table  |                                       |   |   |   |   |   |   |   |   |   | Page          |

|--------|---------------------------------------|---|---|---|---|---|---|---|---|---|---------------|

| 4-1    | Card Cage PWA's                       | • |   | • | • |   |   | • |   | • | 4-3           |

| 4-2    | Other Console PWA's                   | • | • | • | • | • | • | • | • | • | 4-3           |

| 6-1    | PDA Routine Addresses                 | • | • | • |   |   | • | • | • |   | 6-4           |

| 6-2    | Error Addresses                       |   |   |   |   |   |   |   |   |   | 6-5           |

| 6-3    | ROM Tests                             |   |   |   |   |   |   |   |   |   | 6-7           |

| 6-4    | Branch Tests                          |   |   |   |   |   |   |   |   |   | 6-8           |

| 6-5    | Branch on Data Test "Error Addresses" |   |   |   |   |   |   |   |   |   | 6-9           |

| 6-6    | ALU Test "Error Addresses"            |   | • | • |   | • |   |   |   |   | 6-13          |

| 6-7    | Buffers Test "Error Addresses"        |   |   |   |   |   |   |   |   |   | 6 <b>-1</b> 4 |

| 6-8    | Data Bus Out (Lamp) Test Sequence .   |   |   |   |   |   |   |   |   |   | 6-15          |

| 6-9    | Transport Tests Error Analysis        |   |   |   |   |   |   |   |   |   | 6-20          |

| 6 - 10 | Speed Conversions                     |   |   |   |   |   |   |   |   |   | 6-24          |

| 6-11   | Normal Write Forward "Error Addresse  |   |   |   |   |   |   |   |   |   | 6-27          |

| 7-1    | PWA's Affected According to Priority. |   |   |   |   | • | • |   | • |   | 7-2           |

| 7-2    | Troubleshooting Chart                 |   |   |   |   |   |   |   |   |   | 7-3           |

| 8-1    | Transport Power Connections           | • | • | • |   |   | • | • | • | • | 8-3           |

| 8-2    | Head Assembly Connections             |   |   |   |   |   |   |   |   |   | 8-4           |

| 8-3    | BOT/EOT Sensor Assembly Connections   |   |   |   |   |   |   |   |   |   | 8-7           |

| 9-1    | Diagrams                              | • | • | • | • | • | • | • | • | • | 9-1           |

· /

# CHAPTER 1 GENERAL INFORMATION

## **1.1 INTRODUCTION**

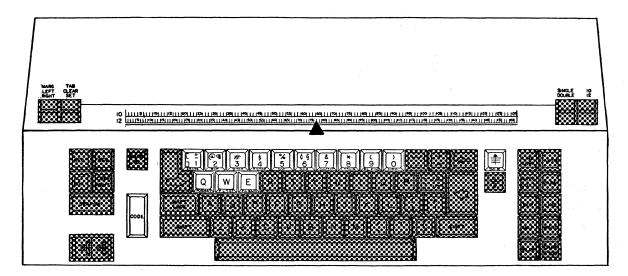

This manual provides installation, operation, and service instructions for both the single and dual station Magnetic Tape Word Processor (MTWP), shown in Figure 1-1. Both systems combine the functions of a Microprocessor, an electronic keyboard and printer, and one (single station) or two (dual station) magnetic tape transports to form an automatic writing system. The Microprocessor and magnetic tape transports are contained in a compact console. The keyboard and printer are housed in an attractive case suitable for secretarial use.

Figure 1-1. Magnetic Tape Word Processor

## **1.2 MANUAL CONTENT**

This Magnetic Tape Word Processor Operation, Service, and Diagrams Manual is divided into nine chapters. The following paragraphs briefly describe the contents of each chapter.

### 1.2.1 Chapter 1, General Information

1

This chapter provides introductory material, a description of manual contents, an equipment description, and the specifications for the system.

#### 1.2.2 Chapter 2, Installation

Chapter 2 discusses unpacking, inspection, and the interconnections required when installing a system. A preoperation checks and adjustments procedure is also provided in this chapter to verify that the system is operating properly.

#### 1.2.3 Chapter 3, Operation

Chapter 3 identifies and describes the function of each key on the keyboard, control and indicator on the console, and system alarm.

#### 1.2.4 Chapter 4, Theory of Operation

The theory of operation is provided in this chapter. Block diagrams, simplified drawings, and timing diagrams are used, where necessary, to support the text.

#### 1.2.5 Chapter 5, Maintenance

Chapter 5 outlines safety precautions, presents maintenance philosophy, and lists required special tools and test equipment.

#### 1.2.6 Chapter 6, Checks and Adjustments

Electrical and mechanical checks and adjustments are contained in Chapter 6.

#### 1.2.7 Chapter 7, Error Analysis

This chapter contains information designed to assist in troubleshooting.

#### 1.2.8 Chapter 8, Replacement Procedures

Chapter 8 presents removal and installation procedures.

#### 1.2.9 Chapter 9, Diagrams

This chapter contains the schematic diagrams for the system as well as those for the Programmed Diagnostic Aid (PDA). The system wire list is also included.

#### **1.3 SYSTEM DESCRIPTION**

The ITEL single or dual station Magnetic Tape Word Processor, (MTWP) is an electronic system for automatic writing. The functions of both are identical; therefore, only the dual station system will be discussed. The dual station does, however, extend the capabilities of the single station system. The major components of the system are:

- A Microprocessor.

- A full duplex electronic keyboard.

- An electronic printer.

- Two magnetic tape transports.

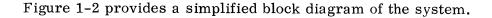

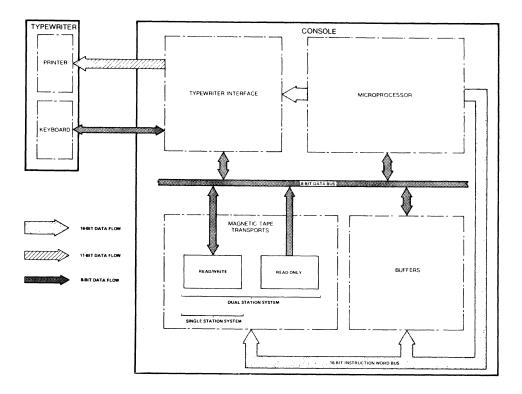

Figure 1-2. Simplified System Block Diagram

### 1.3.1 Microprocessor

The Microprocessor has the capability of storing 4096 sixteen-bit instruction words. These sixteen-bit instruction words are used to control the operation of the system. It also has an eight-bit parallel data bus (DBØ through DB7). Any information which is processed is processed on this data bus. The data bus links the Microprocessor, keyboard, printer, and both magnetic tape transports together into one unit. Information is gated on and off the data bus by the instruction words stored in the Read Only Memory portion of the Microprocessor.

### 1.3.2 Keyboard

The keyboard used in this system is a full duplex electronic keyboard. Through the use of this type of keyboard, signals are routed through the Microprocessor to the printer, rather than directly to the printer. All system functions are controlled by the operator from the keyboard. A standard 44-key typewriter array inputs information into the system during normal typing operations. Certain keys are lighted, when depressed, to indicate the present operation. These lighted keys also monitor the Microprocessor

and flash to display input, output, and system error conditions. The function of each key on the keyboard and each alarm is discussed in detail in Chapter 3 of this manual.

#### 1.3.3 Printer

The printer, used as the output device for the system, is of a serial type (prints a single character at a time). It operates at speeds up to 30 characters per second on general text such as letters, specifications, contracts, etc. The 15-inch long platen indexes at six lines per inch (single space) or three lines per inch (double space).