# VME-68K20 Hardware Reference Manual PRELIMINARY

INTEGRATED SOLUTIONS 1140 Ringwood Court San Jose, California 95131 (408) 943-1902

UNIX is a trademark of AT&T Bell Laboratories.4.2BSD is a trademark of the Board of Regents, University of California, Berkeley.VAX is a trademark of Digital Equipment Corporation.

490103 Rev. A

January 1986 Preliminary

Copyright © 1985, 1986 by Integrated Solutions. All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means (e.g., electronic, mechanical, photocopying, recording) without the prior written permission of Integrated Solutions.

The information in this publication is subject to change without notice.

## PREFACE

This manual describes the Integrated Solutions VME-68K20 processor board. The text provided in this manual includes a product overview, specifications, configuration information, and programming information. The manual is divided into four sections and two appendixes:

SECTION 1: This section describes the general features and architecture of the VME-68K20.

SECTION 2: This section lists the VME-68K20 specifications.

SECTION 3: This section provides the VME-68K20 switch and jumper configuration options.

SECTION 4: This section provides VME-68K20 programming and operations information.

APPENDIX A: This appendix provides VME-68K20 compatibility information.

APPENDIX B: This appendix provides application notes for the Signetic 2681 DUART.

# TABLE OF CONTENTS

| SECTION 1: INT | RODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                | Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                | Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                | 1.3.1 MC68020 Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                | 1.3.2 Bus Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                | 1.3.3 Memory Management Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                | 1.3.4 Serial Ports                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                | 1.3.5 EPROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                | 1.3.6 Floating Point Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1.4            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                | 1.4.1 Off-Board Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| •              | 1.4.2 On-Board Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                | 1.4.3 Interprocessor Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1.5            | Software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1.5            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| SECTION 2: SPE | CIFICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                | Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                | Form Factor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                | System Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                | High-Speed Memory Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                | Bus Arbitration Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.5            | Serial Ports                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2.0            | EPROM Socket                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                | Power Requirements    2-5      Environmental Requirements    2-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2.10           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| SECTION 3: CON | NFIGURATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                | MC68881 Floating Point Co-processor Clock (E5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                | VME Bus Arbitration Jumpers     3-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5.2            | 3.2.1 Request Level (E7–E10 and E12)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                | 3.2.2 Arbitration ( $E1-E4$ and $E6$ )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                | 3.2.3 Bus Master Type (E11)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3.3            | EPROM Socket Configuration (E40–E42)         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         . |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5.0            | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

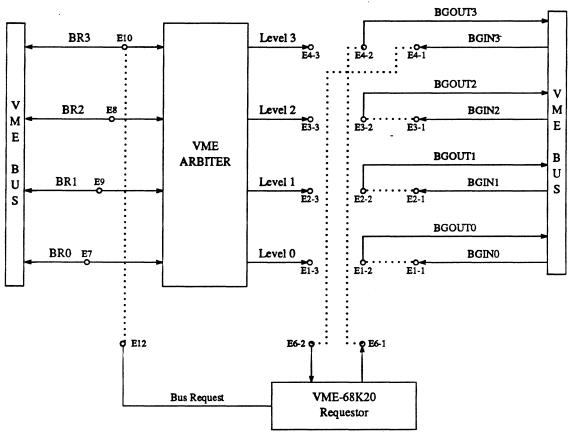

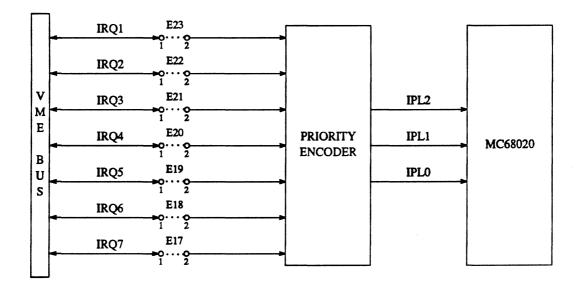

|                | 3.6.1 Off-Board Interrupts (E17–E23)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                | 3.6.2 On-Board Interrupts (E13 and E14)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                | 3.6.3 Interprocessor Interrupts (E15, E16, E33, and E35–E37)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                | Board Status Register (E24–E31)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                | On-Board I/O Cycle Length (E44)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                | VME-68K20 Access to VME Bus Memory (S1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                | VME Bus Access to HSMEM Bus Memory (E38 and E39)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                | Non-Translated Address Boundary (E43)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3.12           | Static VME Bus I/O Sizing (E49)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| SECTION 4. OPF | RATION/PROGRAMMING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4.1           | Translation Buffer          | •  | •    | •   | • | • | • | • | • | • | • | • | • | •   | • | • | • | 4-1        |

|---------------|-----------------------------|----|------|-----|---|---|---|---|---|---|---|---|---|-----|---|---|---|------------|

| 4.2           | Byte I/O Space              | •  | •    | •   | • | • | • | • | • | • | • | • | • | •   | • | • | • | 4-1        |

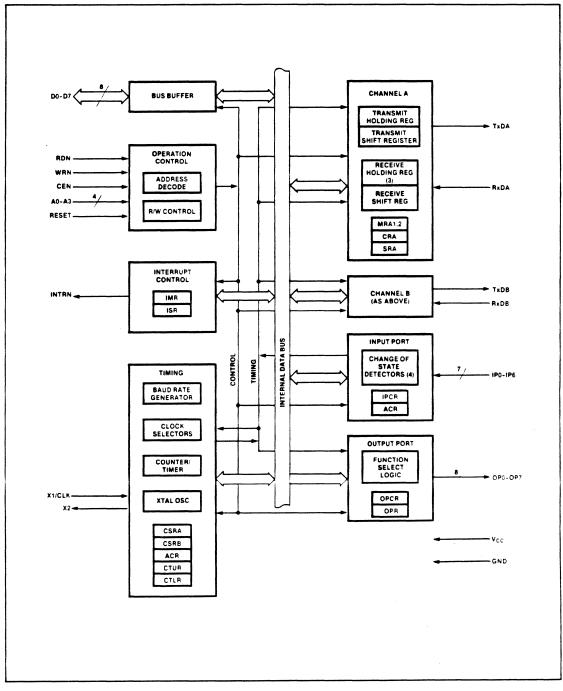

|               | 4.2.1 DUART (Serial Ports)  | •  | •    | •   | • | • | • | • | • | • | ٠ | • | • | •   | • | • | • | 4-2        |

|               | 4.2.2 Error Source Register | •  | •    | •   | • | • | • | • | • | • | • | • | • | •   | • | • | • | 4-3        |

|               | 4.2.3 Board Status Register | •  | •    | •   | • | • | • | • | • | • | • | • | • | •   | ٠ | • | • | 4-4        |

|               | 4.2.4 Context Register .    |    |      |     |   |   |   |   |   |   |   |   |   |     |   |   |   |            |

| 4.3           | Page Table Pointer Buffer . | •  | •    | •   | • | • | • | • | • | • | • | • | • | •   | • | • | • | 4-4        |

| APPENDIX A:   | VME-68K20 BOARD COMPA       | TI | BILI | ITY | • | • | • | • | • | • | • | • | • | • . | • | • | • | <b>A-1</b> |

| APPENDIX B: 1 | DUART APPLICATION NOT       | ES | •    | •   | • | • | • | • | • | • | • | • | • | •   | • | • | • | <b>B-1</b> |

-

.

# LIST OF FIGURES

| Figure 1-1. | VME-68K20 Block Diagram            | •    | •     | •    | •    | •    | •   | •    | •   | • | • | • | • | • | • | • | • | 1-3  |

|-------------|------------------------------------|------|-------|------|------|------|-----|------|-----|---|---|---|---|---|---|---|---|------|

| Figure 1-2. | Memory Management Overview         | •    | •     | •    | •    | •    | •   | •    | •   | • | • | • | • | • | • | • | • | 1-6  |

| Figure 1-3. | PTP Index                          | •    | •     | •    | •    | •    | •   | •    | •   | • | • |   | • | • | • | • | • | 1-6  |

| Figure 1-4. | PTTE Physical Address              | •    | •     | •    | •    | •    | •   | •    | •   | • | • | • | • | • | • | • | • | 1-7  |

| Figure 1-5. | PTTE Format                        | •    | •     | •    | •    | •    | •   | •    | •   | • | • | • | • | • | • | • | • | 1-8  |

| Figure 1-6. | Virtual-to-Physical Address Trans  | lati | on Su | ımı  | nar  | y    | •   | •    | •   | • | • | • | • | • | • | • | • | 1-10 |

| Figure 1-7. | Reading and Writing PTPs           | •    | •     | •    | •    | •    | •   | •    | •   | • | • | • | • | • | • | • | • | 1-11 |

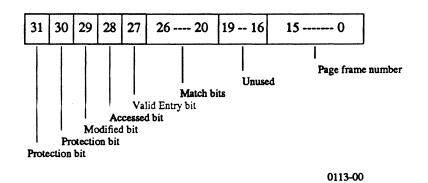

| Figure 1-8. | Translation Buffer Entry Format    | •    | •     | •    | •    | •    | •   | •    | •   | • | • | • | • | • | • | • | • | 1-11 |

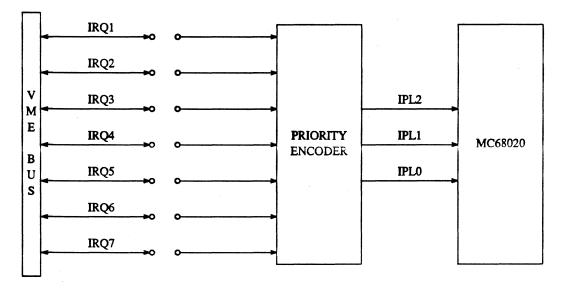

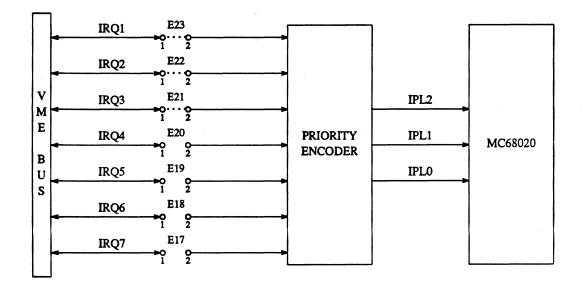

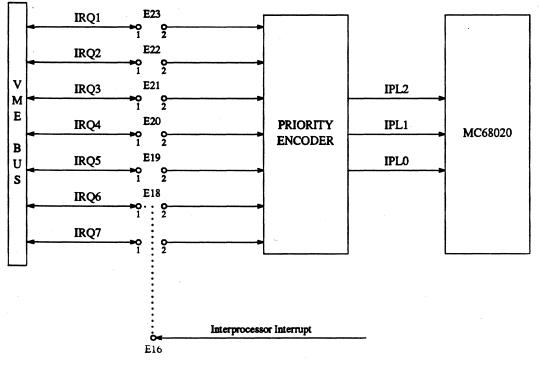

| Figure 1-9. | VME-68K20 Interrupt Handler .      | •    | •     | •    | •    | •    | •   | •    | •   | • | • | • | • | • | • | • | • | 1-12 |

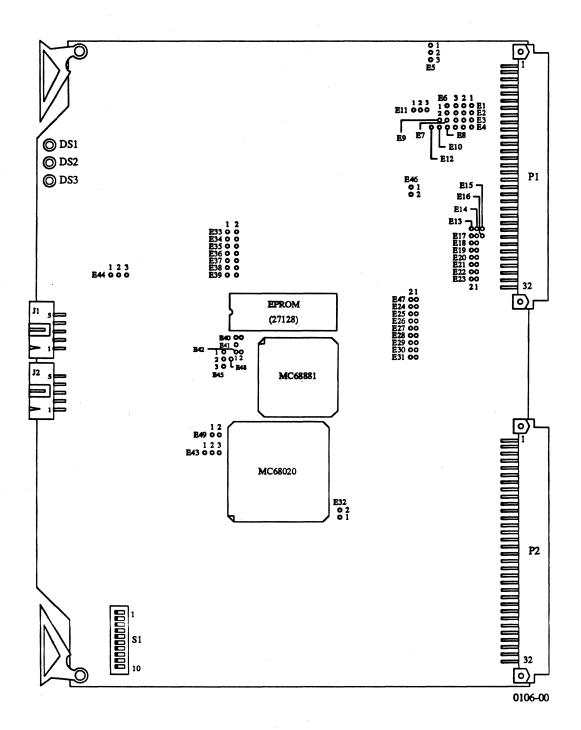

| Figure 3-1. | VME-68K20 Board Layout             | •    | •     | •    | •    | •    | •   | •    | •   | • | • | • | • | • | • | • | • | 3-2  |

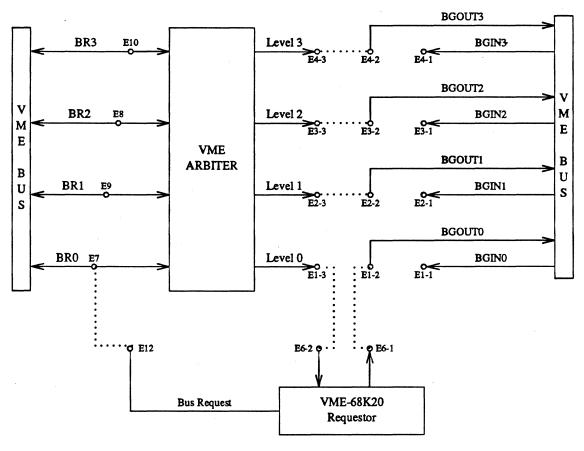

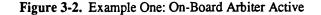

| Figure 3-2. | Example One: On-Board Arbiter A    | Acti | ve.   | •    | •    | •    | •   | •    | •   | • | • | • | • | • | • | • | • | 3-4  |

| Figure 3-3. | Example Two: Off-Board Arbiter     | Act  | ive   | •    | •    | •    | •   | •    | •   | • | • | • | • | • | • | • | • | 3-5  |

| Figure 3-4. | Off-Board Interrupt Jumper Config  | gura | ation | (Si  | ngle | e-pr | OCE | esso | or) | • | • | • | • | • | • | • | • | 3-7  |

| Figure 3-5. | Off-Board Interrupt Jumper Config  | gura | ation | s (N | lult | ipro | ce  | sso  | r)  | • | • | • | • | • | • | • | • | 3-8  |

| Figure 3-6. | Off-Board Interprocessor Interrupt | Ju   | mper  | S    | •    | •    | •   | •    |     | • | • | • | • | • | • | • |   | 3-10 |

# LIST OF TABLES

| Table 1-1.  | HSMEM Bus Signals                                 | 4 |

|-------------|---------------------------------------------------|---|

| Table 1-2.  | PTTE Bit Definitions         1-4                  | 8 |

| Table 2-1.  | VME Bus Connector P1 Pin Assignments              | 2 |

| Table 2-2.  | HSMEM Bus Connector P2 Pin Assignments            | 3 |

| Table 2-3.  | Connector J2 Pin Assignments                      | 4 |

| Table 2-4.  | Serial Port Connector J1 Pin Assignments          | 4 |

| Table 2-5.  | VME-68K20 Indicators                              | 5 |

| Table 3-1.  | MC68881 Clock Frequency                           | 1 |

| Table 3-2.  | VME-68K20 Bus Request Level Jumper Configurations | 1 |

| Table 3-3.  | VME Bus Arbitration Jumper Pin Signals            | 3 |

| Table 3-4.  | EPROM Socket Configuration                        | 6 |

| Table 3-5.  | Auto-Vectored Interprocessor Interrupt Addresses  | 9 |

| Table 3-6.  | Auto-Vectored Interprocessor Interrupt Priority   | 0 |

| Table 3-7.  | Vectored Interprocessor Interrupt Jumpers         | 1 |

| Table 3-8.  | Baud Rate Jumpers                                 | 1 |

| Table 3-9.  | Processor Number Jumpers                          | 1 |

| Table 3-10. | I/O Cycle Length Configuration                    | 2 |

| Table 3-11. | S1 Switch Settings (Regular Addressing)           | 2 |

| Table 3-12. | S1 Switch Settings (Extended Addressing)          | 3 |

| Table 3-13. | Jumper E38 and E39 Configurations                 | 3 |

| Table 3-14. | Non-Translated Address Boundary Jumper            | 1 |

| Table 4-1.  | On-Board I/O Address Space                        | l |

| Table 4-2.  | System and User Translation Buffer Address Ranges | l |

| Table 4-3.  | Byte I/O Space Address Areas                      | 2 |

| Table 4-4. DUART Register Addresses       | •   | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 4-2         |

|-------------------------------------------|-----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|-------------|

| Table 4-5. ESR Bit Definitions            | ٠   | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 4-3         |

| Table 4-6. CTX Bit Definitions            | •   | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 4-4         |

| Table A-1. Compatible Printed Circuit Boa | rds | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | <b>A-</b> 1 |

# **SECTION 1: INTRODUCTION**

The VME-68K20 CPU board is a high-performance systems-oriented CPU on a standard dual-size VME board. Maximizing the performance available from the Motorola MC68020, the VME-68K20 combines the processing speed, large instruction space, and powerful instruction set of the MC68020 processor with the second-generation industry standard VME bus.

Integrated into the VME-68K20 board is the concept of a dual-bus architecture for maximum performance in both single processor and multiprocessor environments. The VME-68K20 also provides the additional features necessary to support multiple processors on a single VME bus.

## **1.1 Features**

Using the latest in VLSI technology, the VME-68K20 offers the following features:

- 16.67 MHz 68020 CPU

- Dual 32-bit buses (VME bus and HSMEM bus)

- VME bus four-level arbiter

- HSMEM bus arbiter

- Support for interprocessor interrupts

- Memory Management Unit featuring an ultra-high-speed translation buffer

- Supports 256-Mbyte virtual address space and 256-Mbyte physical address space

- Support for an MC68881 floating point processor with independent clock

- Two asynchronous serial ports

## **1.2 Performance**

The VME-68K20 maximizes the performance available from the Motorola MC68020 processor. Several architectural features contribute to this optimized performance:

- Use of the HSMEM bus Maximum performance is realized when all memory is present on the\_ HSMEM bus, and the VME bus is used strictly for I/O operations. At 16.67 MHz the 68020 operates with one wait state on reads and no wait states on writes. In addition, no VME bus cycles occur when the 68020 operates over the HSMEM bus, leaving the entire VME bus bandwidth available for peripheral operations.

- Ultra-high-speed translation buffer The 68020 processor board uses a very high-speed single level translation buffer that translates virtual to physical addresses in less than 35 nanoseconds (ns).

- The Motorola MC68020 is a full 32-bit processor with 32-bit registers, data paths, and addressing. The processor's design enables the VME-68K20 to approach maximum performance without exotic hardware. The MC68020 always executes 32-bit instruction fetches resulting in almost a 50 percent decrease in the number of fetches required by 16-bit microprocessors. In addition, the MC68020 has a small internal instruction cache which further reduces the required number of external instruction fetches. The combination of these factors means that the one wait state on reads and no wait states on writes version of the 68020 operating at 16.67 MHz achieves between 90 and 92 percent of the maximum no wait state performance possible.

## **1.3** Architecture

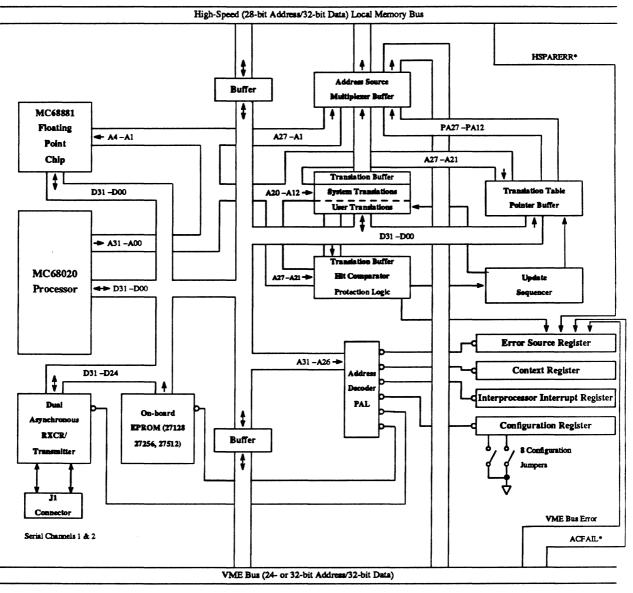

As illustrated in Figure 1-1, the major functional elements that compose the VME-68K20 are

- MC68020 processor

- VME bus and HSMEM bus interface logic

- Memory Management Unit

- Serial ports

- EPROM

- MC68881 Floating point processor

#### 1.3.1 MC68020 Processor

The VME-68K20 uses the Motorola MC68020 processor as the CPU. The MC68020 is a 32-bit processor that offers virtual memory support, 18 addressing modes, a flexible co-processor interface, floating point processor support, memory mapped I/O, internal instruction cache, and pipeline instruction execution. As discussed previously, the processor's advanced design enables the VME-68K20 to approach maximum performance without the need for exotic support hardware.

#### 1.3.2 Bus Interfaces

The VME-68K20 supports two buses, the VME bus and the HSMEM bus. The VME-68K20 dual-busarchitecture provides maximum performance in both single processor and multiprocessor environments.

#### 1.3.2.1 VME Bus

The VME-68K20 has a 32-bit VME interface. The interface supports byte, word, and longword transfers. In 28-bit mode, the VME-68K20 conforms to VME 32-bit addressing with the top four address bits driven to 0. The VME bus interface includes an interrupt handler for all seven interrupt levels and a four-level prioritized bus arbiter.

#### **Interrupt Handler**

The VME-68K20 can receive interrupts at any of the seven VME bus levels. In addition, any level can be independently disabled so that the 68020 does not respond to it. This is useful in multiprocessor environments where each processor handles a portion of the seven interrupt levels.

Support for interprocessor interrupts is required for multiprocessing. The VME-68K20 provides an onboard I/O port into which the 68020 can write to generate an interrupt at any of the seven VME bus levels. A programmable vector will then be driven onto the bus during the VME bus interrupt acknowledge cycle.

#### VME Bus Arbiter

The arbiter can be configured as a Release on Request or a Release When Done arbiter, and the 68020 processor can be configured to request the bus at any one of the four levels. Additionally, in multiprocessor environments where another processor is handling bus arbitration, the arbitre can be completely disabled.

#### 1.3.2.2 HSMEM Bus

The HSMEM bus is a 32-bit bus implemented on the user defined pins of the VME-68K20 P2 connector in conjunction with connector J2, which supports HSMEM bus address Bits 27-24. The HSMEM bus provides access to a maximum of 256 Mbytes of physical memory with one wait state on reads and no wait states on writes at 16.67 MHz. No VME bus cycles occur when the 68020 operates over the HSMEM bus. The HSMEM bus signal lines are provided in Table 1-1.

Figure 1-1. VME-68K20 Block Diagram

#### Table 1-1. HSMEM Bus Signals

| 27 | Address Lines:   | HSADD27-HSADD1                                                                                                   |

|----|------------------|------------------------------------------------------------------------------------------------------------------|

| 32 | Data Lines:      | HSDAT31-HSDAT0                                                                                                   |

| 9  | Control Lines:   |                                                                                                                  |

|    | HSCYC*           | Used to start an HSMEM cycle                                                                                     |

|    | HSUDS*<br>HSLDS* | Used as upper and lower data strobes on the HSMEM bus                                                            |

|    | HSRW*            | The read/write control line                                                                                      |

|    | HSLW*            | Used to signal 32-bit transfers                                                                                  |

|    | HSREF*           | Used to signal the start of a refresh cycle                                                                      |

|    | HSVME*           | Used to signal the start of a VME access cycle                                                                   |

|    | HSPARERR*        | The parity error signal returned by the memory board to the CPU if parity error occurs                           |

|    | HSDTACK*         | Used as a cache hit signal to eliminate the one wait state<br>normally inserted on all high-speed memory cycles. |

#### NOTE

The use of an asterisk (\*) following the signal name indicates that the signal is true when it is low.

#### **HSMEM Bus Arbiter**

The VME-68K20 is designed around the concept of sharing HSMEM bus bandwidth (total bandwidth 16.67 Mbytes/second) among the 68020 processor, the VME bus DMA requests, and the memory refresh circuitry. Few DMA devices can use the entire 16.67 Mbytes/second bandwidth of the HSMEM bus. Therefore, the HSMEM bus arbiter gives DMA devices highest priority, i.e., whatever percentage of the memory cycles they need, and allocates the rest of the cycles to the 68020. The memory refresh circuitry utilizes one memory cycle every 16 microseconds. This is a much more efficient strategy than other bus arbitration schemes where the DMA device retains control of the bus for a period of time, although it cannot perform transfers at a rate even approaching the bus bandwidth. Bus arbitration occurs every 60 ns. In order to avoid synchronizing delays in the 68020 access path, the entire arbiter operates synchronously with the 68020 clock.

#### **1.3.3 Memory Management Unit**

The VME-68K20 has a demand paged Memory Management Unit (MMU) that supports a 256-Mbyte virtual address space and a 256-Mbyte physical address space. The VME-68K20 MMU performs three functions that are necessary for efficient multiprogramming operating systems:

• Translates from the 256-Mbyte virtual address space to the 256-Mbyte physical address space — The VME-68K20 demand paging subsystem is based on four-Kbyte pages. Consequently, 65,536 translations are needed to map the 256-Mbyte virtual address space. These translations are kept in system physical memory in page translation tables (PTTs). The high-speed translation buffer caches the most recently used translations. The hardware sequencer pulls required translations from the PTT area into the translation buffer without software intervention.

- Protects one user program in a multiprogramming environment from corrupting another user program or the operating system itself — The memory management unit has two bits in the PTT entry (PTTE) which are protection bits. These protection bits can be encoded for no access, read only access, or read/write access. If a user program attempts to execute a memory access that is not permitted by the protection bits, the MMU prevents the cycle from occurring and a bus error notifies the processor of the attempted access.

- Provides demand-paged virtual memory support In this role, the MMU supports two additional bits in the PTTE. These bits are the page accessed bit and the page modified bit. The two bits are automatically modified by the hardware under the following conditions:

- Both bits should initially be 0 when the PTTE is created in main memory by the operating system. This indicates that the user program has not modified the page from what was present on the disk. It also indicates that the page has not yet been accessed by the user program.

- When a page is loaded into the translation buffer by the hardware sequencer, the page accessed and page modified bits are checked. If the page accessed bit is 0, it is updated to 1 by the hardware as is the memory-based PTTE. (Central to the design concept of the VME-68K20 MMU is the concept that the memory-based PTTEs are always updated by the hardware in order to remain identical to the translation buffer copy of the PTTEs. Thus, any change in the translation buffer page accessed or page modified bits is immediately followed by an update cycle in which the memory-based PTTE is updated.)

- When a write operation occurs to a page which has a page modified bit value of 0, the page modified bit is updated to 1 both in the translation buffer and in the memory-based PTTE.

The major elements that compose the MMU include a page table pointer buffer, context register, hardware sequencer, and an ultra-high-speed translation buffer.

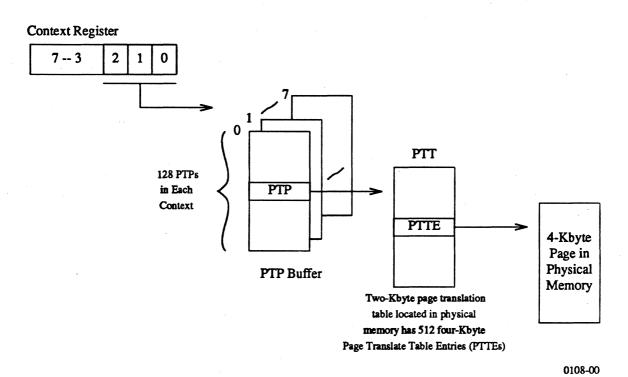

## **1.3.3.1 Page Table Pointer Buffer**

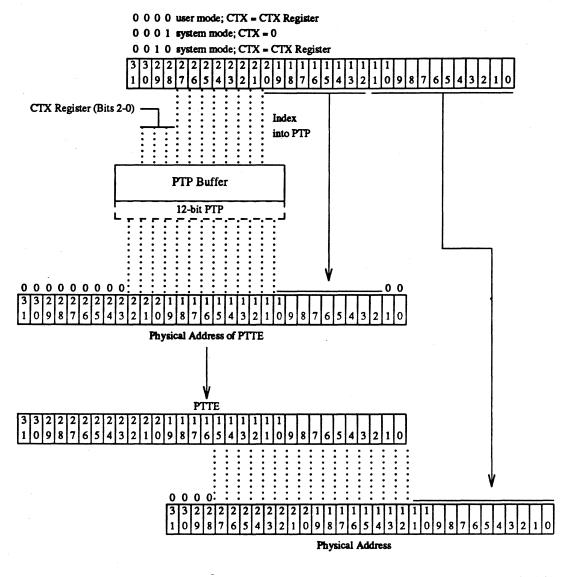

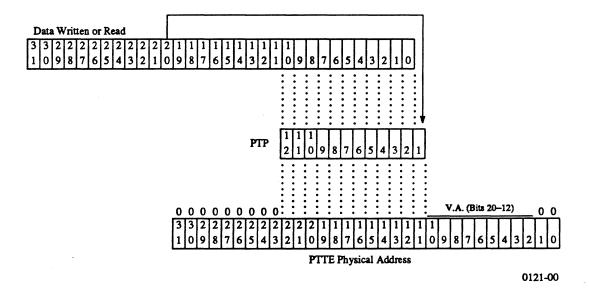

The Page Table Pointer buffer (PTP buffer) contains eight contexts (0-7), each context consisting of 128 twelve-bit Page Table Pointers (PTPs), see Figure 1-2. The PTP buffer can be thought of as an MMU that is used solely by the hardware sequencer. The PTP buffer is programmed by the system software for use by the hardware sequencer and it performs two functions:

- It translates virtual addresses of PTTs into physical addresses.

- It provides an abort mechanism for references to user virtual spaces for which no PTTEs exist. This allows better overall system performance by allowing large sections of virtual address spaces to be disabled very quickly and easily.

#### Virtual Address Translations

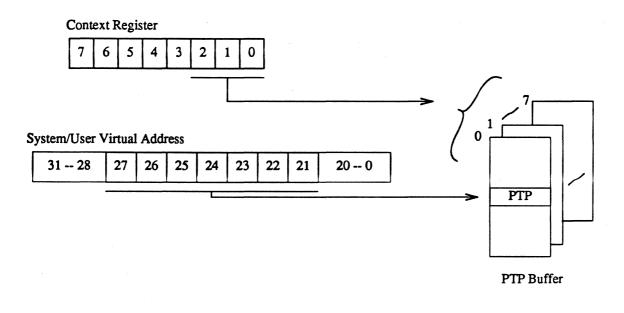

As mentioned previously, the PTP buffer contains eight contexts, the system context (0) and seven user contexts (1-7). As shown in Figure 1-2, it is the function of Bits 2–0 of the Context Register to provide an index into the PTP buffer to select one of the eight contexts.

Within a particular context, one of the 128 PTPs is selected by Bits 27-21 of the system/user virtual address. Context Register Bits 2-0 plus virtual address Bits 27-21 form an index into the PTP buffer (selecting a particular PTP) as illustrated in Figure 1-3.

Figure 1-2. Memory Management Overview

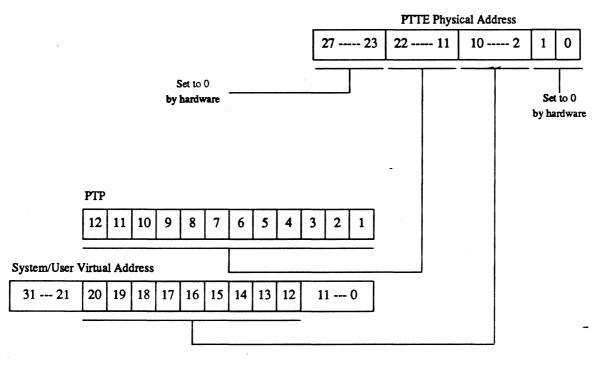

Each 12-bit PTP points to a two-Kbyte block in physical memory called a Page Translation Table (PTT). As shown in Figure 1-2, each PTT contains 512 four-byte Page Table Entries (PTTEs). Virtual address Bits 20-12 form an index into the PTT selecting one of the 512 PTTEs. The 12-bit PTP appended to virtual address Bits 20-12 forms the physical address of a particular PTTE as illustrated in Figure 1-4.

## NOTE

PTTE physical addresses must be in the lower seven Mbytes on the HSMEM bus. The high order nine bits and low order two bits of the 32-bit physical address generated by the PTP are forced to 0 by the hardware.

0110-00

## Figure 1-4. PTTE Physical Address

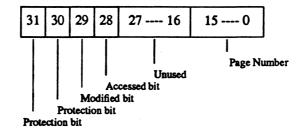

Each PTTE is one longword (32 bits) in length. The PTTE format is shown in Figure 1-5 and Table 1-2 provides bit definitions. PTTE Bits 15–0 specify a page number in physical memory; the complete physical address is formed by appending virtual address Bits 11–0 which provide the offset into the page number specified by PTTE Bits 15–0.

Integrated Solutions

## 0111-00

# Figure 1-5. PTTE Format

| Table 1-2. PTTE Bit Defi | nitions |

|--------------------------|---------|

|--------------------------|---------|

| Bit        | Name              | Description                                                                                                                                                                                                                                                                                                                    |

|------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 31     | Protection Bit    | When 0, this bit indicates that the PTTE is invalid. When 1,<br>the bit indicates a valid entry. When a translation through an<br>invalid entry in the translation buffer is attempted, the cycle<br>is blocked and the cycle is terminated in a bus error as a<br>protection violation.                                       |

| Bit 30     | Protection Bit    | If Bit 30 is a 1, the accessed page is read only. If Bit 30 is 0,<br>the accessed page is read/write. An attempt to write on a<br>read only page results in a protection violation. A protection<br>violation results in the cycle being blocked and terminated<br>with a bus error to notify the processor of the violation.  |

| Bit 29     | Page Modified Bit | This bit is changed from 0 to 1 on the first write access to<br>this page. The hardware sequencer is responsible for<br>keeping the memory PTTE synchronized with the translation<br>buffer entry.                                                                                                                             |

| Bit 28     | Page Accessed Bit | This bit is changed from 0 to 1 on the first access to this<br>page. This first access normally occurs the first time the<br>page is pulled from the PTTs into the translation buffer.<br>Again, the hardware sequencer is responsible for keeping the<br>memory-based PTTE synchronized with the translation<br>buffer entry. |

| Bits 27-16 | —                 | Unused by hardware.                                                                                                                                                                                                                                                                                                            |