# PERKIN ELMER

# **MODEL 3250 PROCESSOR**

User's Manual

50-001 R00

The information in this document is subject to change without notice and should not be construed as a commitment by the Perkin-Elmer Corporation. The Perkin-Elmer Corporation assumes no responsibility for any errors that might appear in this document. The hardware description in this document is intended solely for use in operation, installation, maintenance, or repair of Perkin-Elmer equipment. Use of this document for all other purposes, without prior written approval from Perkin-Elmer, is prohibited. Any approved copy of this manual must include the Perkin-Elmer copyright notice. The Perkin-Elmer Corporation, Computer Systems Division 2 Crescent Place, Oceanport, New Jersey 07757 © 1982 by The Perkin-Elmer Corporation Printed in the United States of America

# TABLE OF CONTENTS

| PREFACE |                                        |                                                                                                                                          | X111                                         |

|---------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| CHA     | PTERS                                  |                                                                                                                                          |                                              |

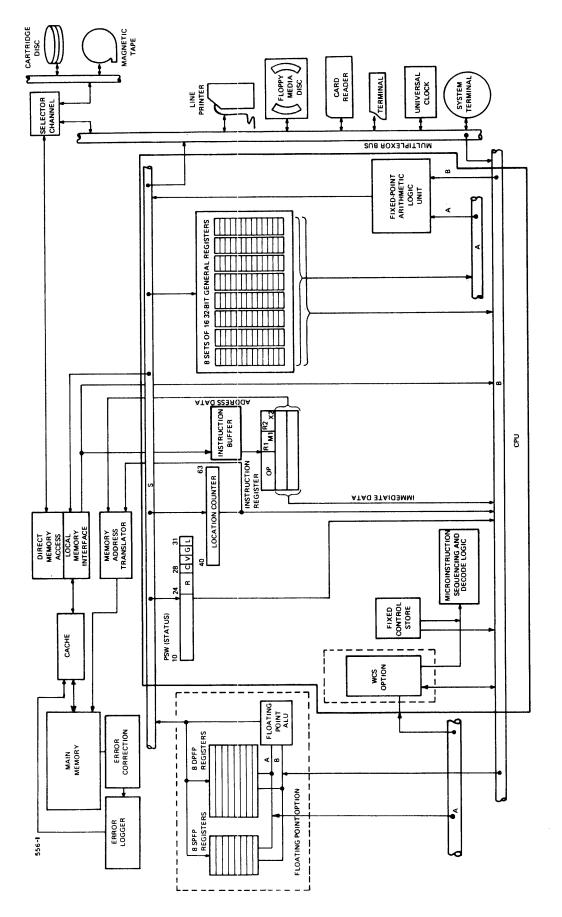

| 1       | SYSTEM D                               | ESCRIPTION                                                                                                                               |                                              |

|         | 1.1                                    | INTRODUCTION                                                                                                                             | 1 – 1                                        |

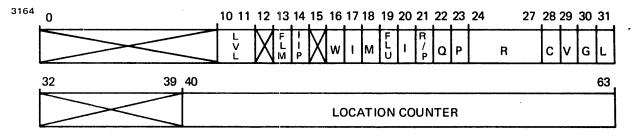

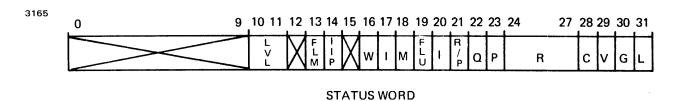

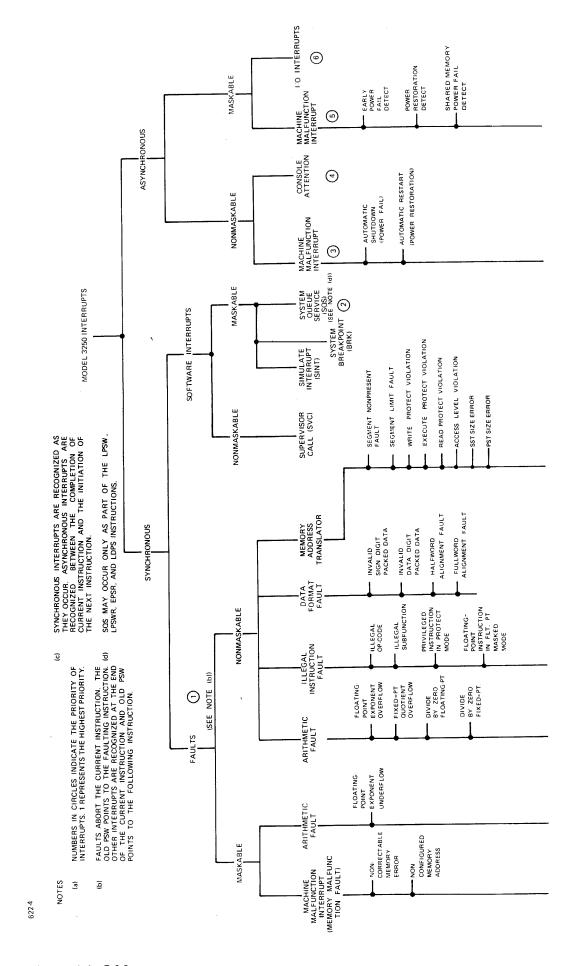

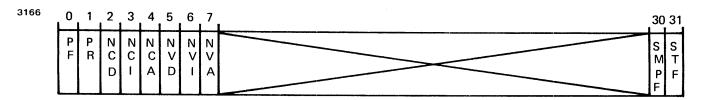

|         | 1.2.1<br>1.2.1.1<br>1.2.1.2<br>1.2.1.3 | PROCESSOR Program Status Word (PSW) Register Set Select (R) Condition Code (C, V, G, L) Location Counter General Registers               | 1-4<br>1-4<br>1-5<br>1-5<br>1-6<br>1-6       |

|         |                                        | Floating-Point Registers                                                                                                                 | 1-6                                          |

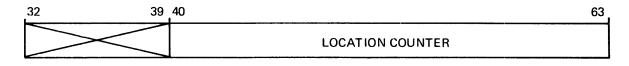

|         | 1.3                                    | PROCESSOR INTERRUPTS                                                                                                                     | <b>1-</b> 5                                  |

|         | 1.4                                    | RESERVED MEMORY LOCATIONS                                                                                                                | 1-7                                          |

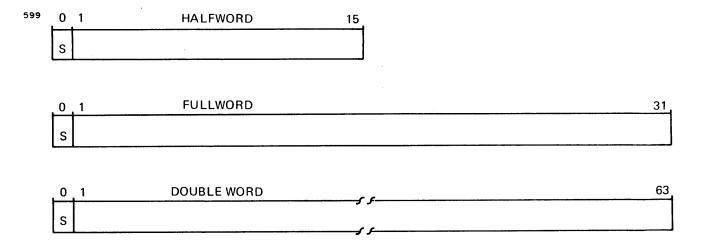

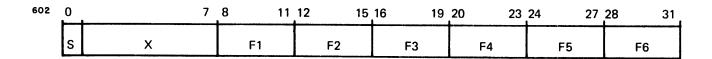

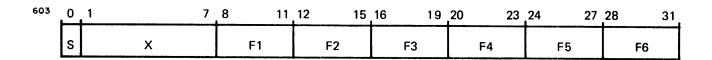

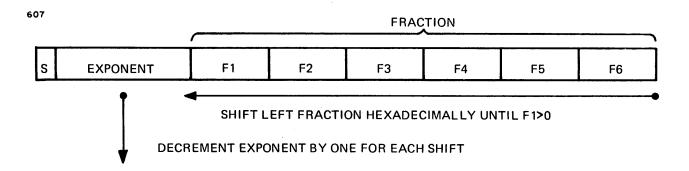

|         | 1.5.2<br>1.5.3                         | DATA FORMATS Fixed-Point Data Floating-Point Data Logical Data Decimal String Data Alphanumeric String Data                              | 1-8<br>1-8<br>1-8<br>1-9<br>1-9              |

|         | 1.6                                    | DATA ALIGNMENT                                                                                                                           | <b>1-</b> 9                                  |

|         | 1.7                                    | INSTRUCTION ALIGNMENT                                                                                                                    | 1-10                                         |

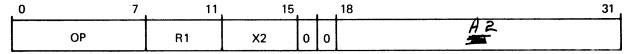

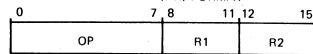

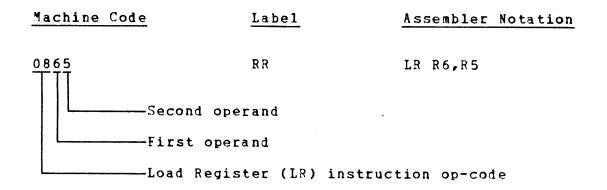

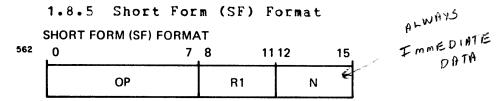

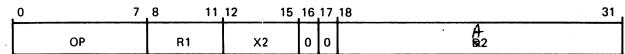

|         | 1.8.4<br>1.8.5                         | INSTRUCTION FORMATS Introduction Branch Instruction Formats Programming Examples Register-to-Register (RR) Format Short Form (SF) Format | 1-10<br>1-10<br>1-12<br>1-12<br>1-13<br>1-13 |

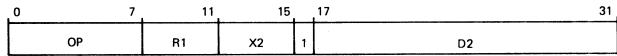

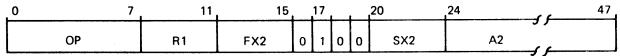

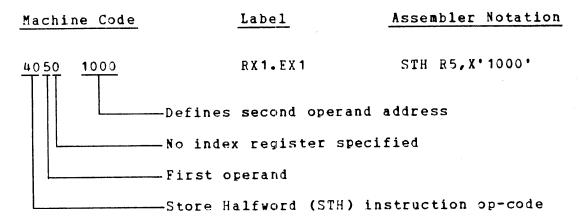

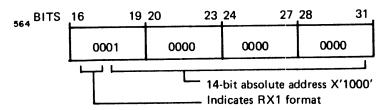

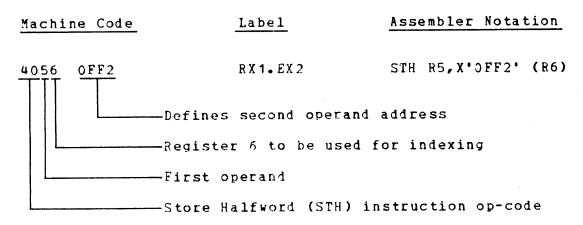

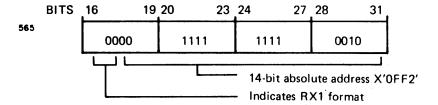

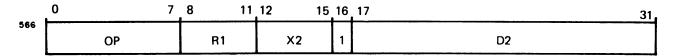

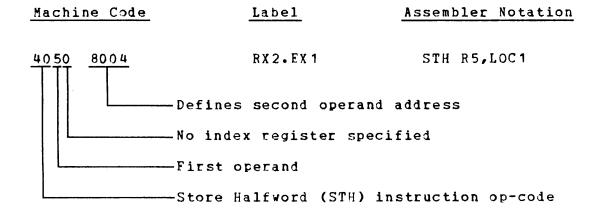

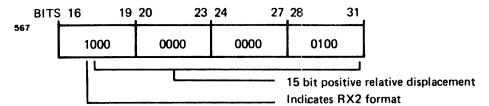

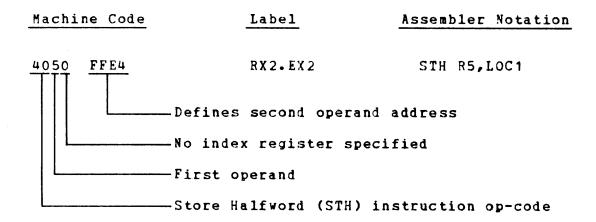

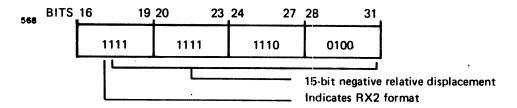

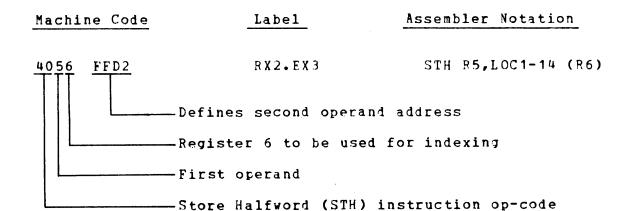

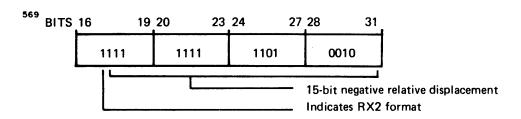

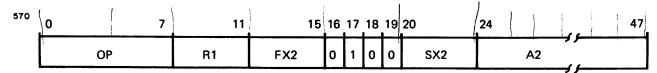

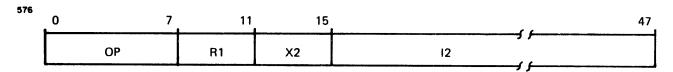

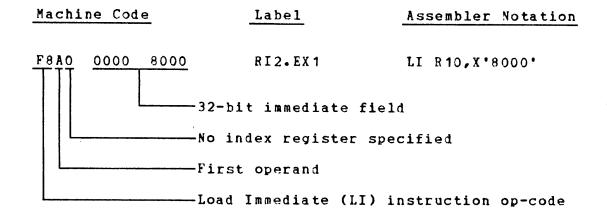

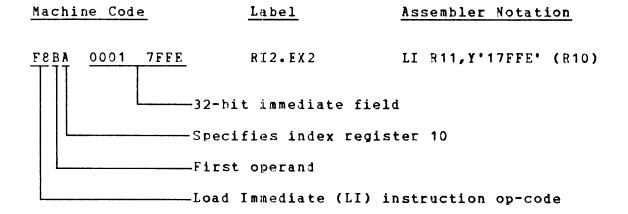

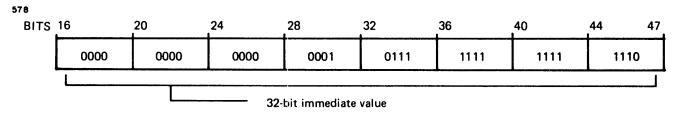

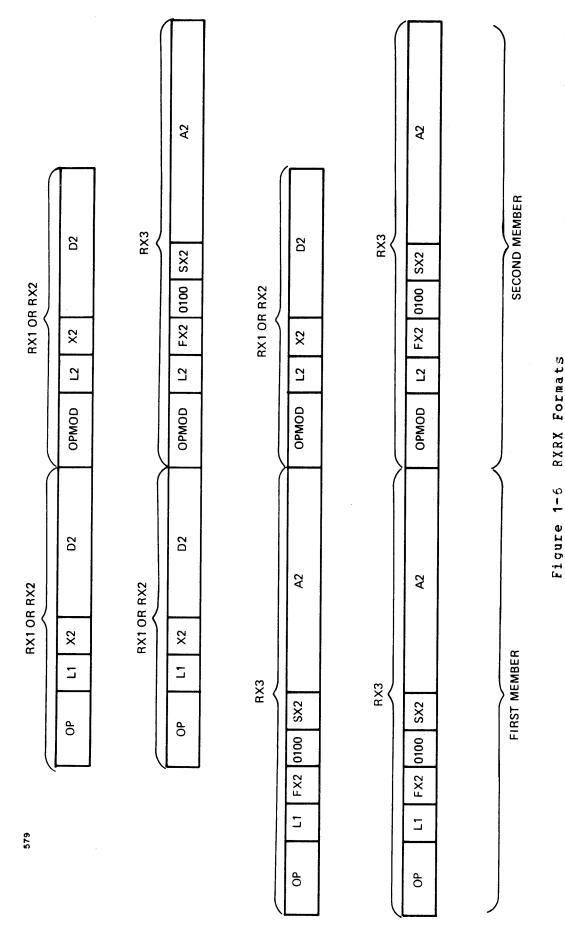

|         | 1.8.6<br>1.8.7                         | Register and Indexed Storage One (RX1) Format Register and Indexed Storage Two (RX2) Format                                              | 1-14                                         |

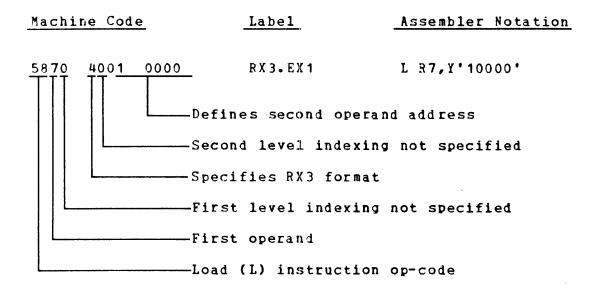

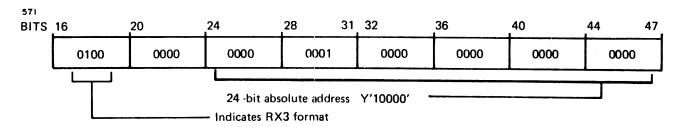

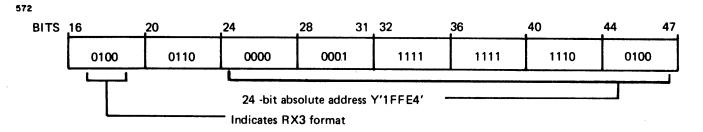

|         | 1.8.8                                  | Register and Indexed Storage Three (RX3) Format                                                                                          | 1-17                                         |

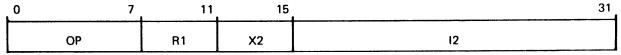

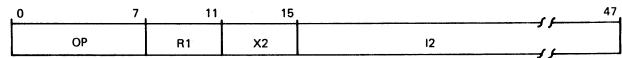

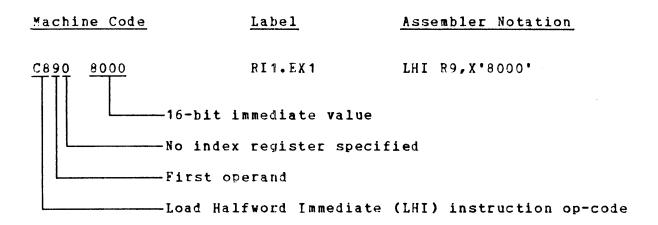

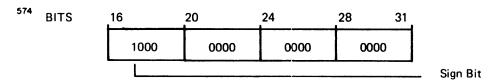

|         | 1.8.9                                  | Register and Immediate Storage One (RI1) Format                                                                                          | 1-19                                         |

i

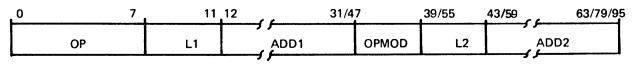

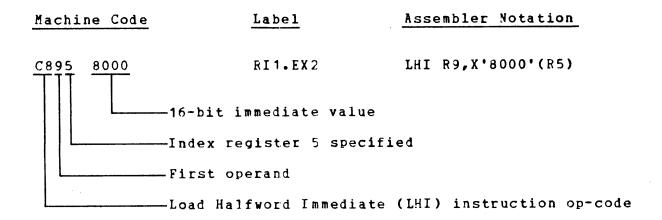

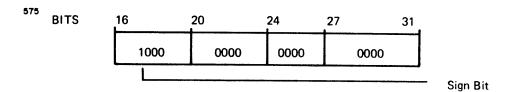

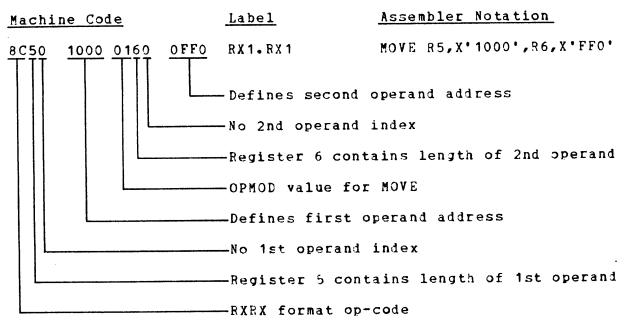

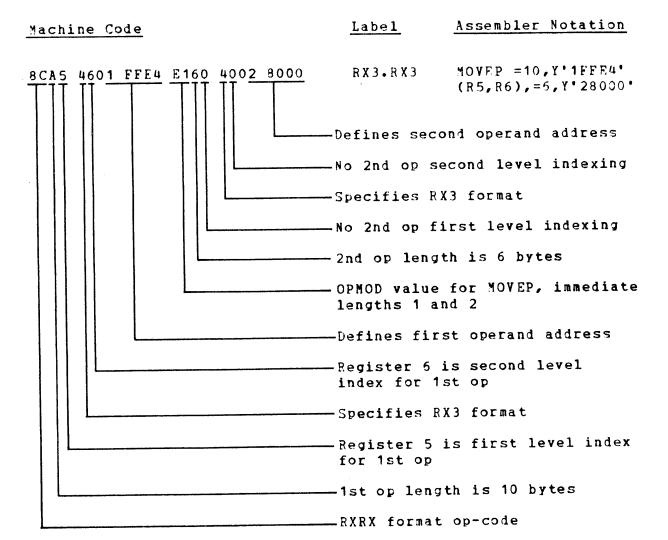

|   | 1.8.10                                                                                                                       | Register and Immediate Storage Two (RI2) Format Register and Indexed Storage/Register and Indexed Storage (RXRX) Format                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1-21<br>1-23                                                                            |

|---|------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| 2 | SYSTEM C                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 2                                                                                     |

| 2 | SISIES C                                                                                                                     | CNIROL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                         |

|   | 2.1                                                                                                                          | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2-1                                                                                     |

|   | 2.2                                                                                                                          | CONFIGURATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-1                                                                                     |

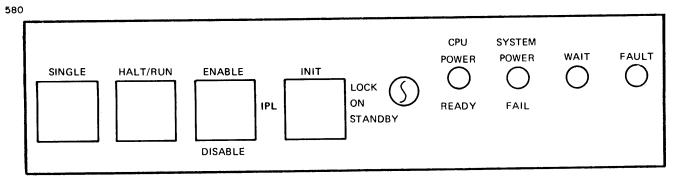

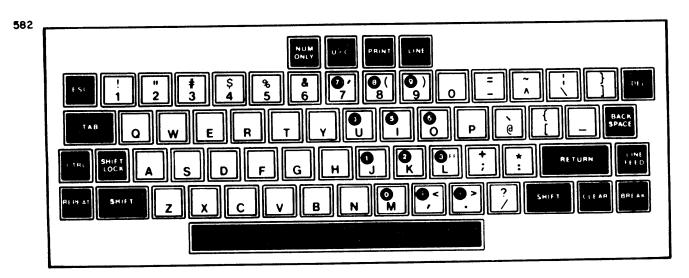

|   | 2.3<br>2.3.1<br>2.3.2                                                                                                        | SYSTEM CONTROL PANEL SWITCHES AND INDICATORS Key-Operated Security Lock Control Switches                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-3<br>2-3<br>2-4                                                                       |

|   | 2.4<br>2.4.1<br>2.4.2<br>2.4.3                                                                                               | CPERATING INSTRUCTIONS Power-up Entering Console Service Initial Program Load (IPL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2-5<br>2-5<br>2-5<br>2-5                                                                |

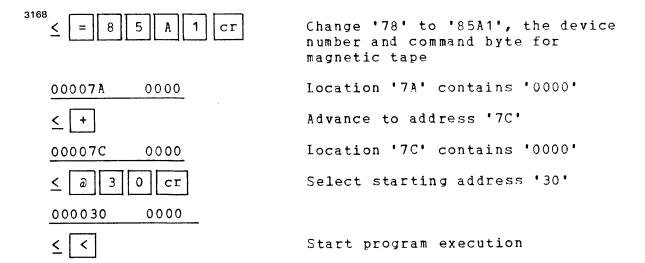

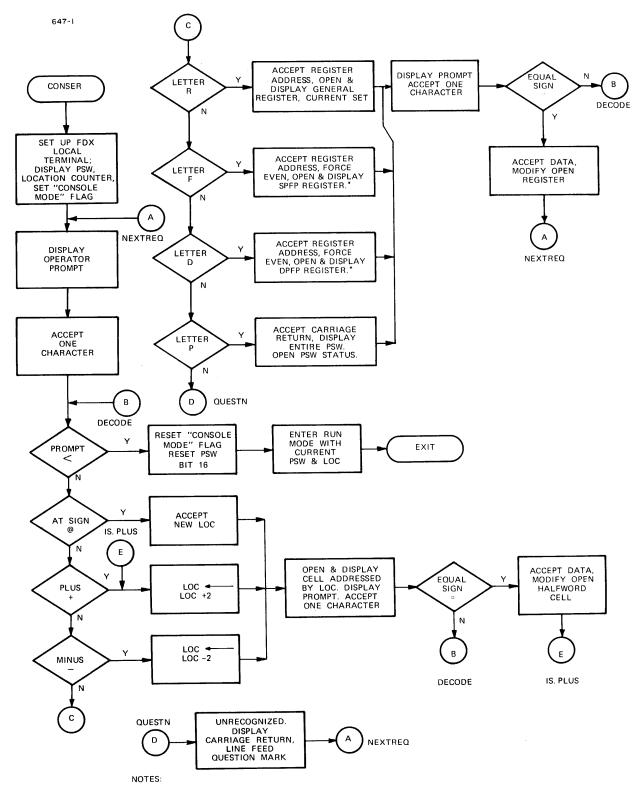

|   | 2.5<br>2.5.1<br>2.5.2<br>2.5.3<br>2.5.4<br>2.5.5<br>2.5.6<br>2.5.7<br>2.5.8<br>2.5.9<br>2.5.10<br>2.5.11<br>2.5.12<br>2.5.13 | SYSTEM TERMINAL COMMANDS Select an Address and Examine "a" Increment and Examine Next Location "+" Decrement and Examine Prior Location "-" Modify Current Location "=" Examine General Register "R" Modify General Register "=" Examine Single-Precision Floating-Point Register "F" Modify Single-Precision Floating-Point Register "=" Examine Double-Precision Floating-Point Register "D" Modify Double-Precision Floating-Point Register "=" Examine Program Status Word "P" Modify Program Status Word "P" Modify Program Status Word "=" Enter Run Mode "<" | 2-6<br>2-6<br>2-5<br>2-7<br>2-7<br>2-7<br>2-7<br>2-8<br>2-8<br>2-8<br>2-9<br>2-9<br>2-9 |

|   | 2.6                                                                                                                          | MEMORY INITIALIZATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2-10                                                                                    |

|   | 2.7                                                                                                                          | PROGRAMMING INSTRUCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-11                                                                                    |

| 3 | LOGICAL                                                                                                                      | CPERATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                         |

|   | 3.1                                                                                                                          | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3-1                                                                                     |

|   | 3.2                                                                                                                          | LOGICAL DATA FCRMATS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3-1                                                                                     |

|   | 3.3<br>3.3.1                                                                                                                 | OPERATIONS Boolean Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3-2<br>3-2                                                                              |

ii 50-001 R00

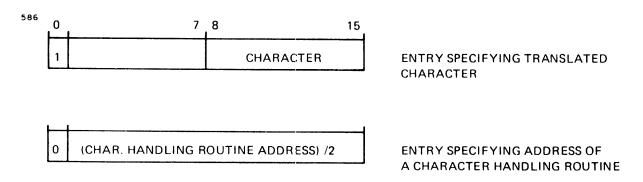

| 3.3.2  | Translation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3-2           |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| 2 2 2  | Timb December                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |               |

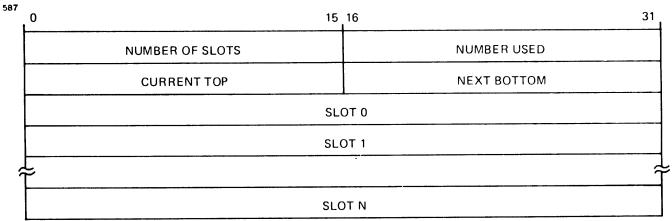

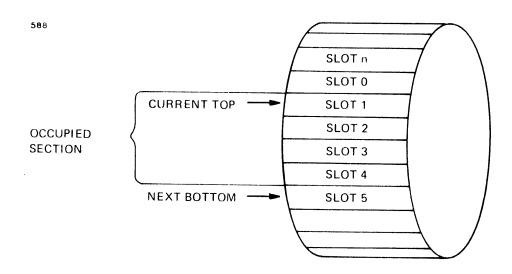

| 3.3.3  | List Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3-3           |

|        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |

| 3.4    | LOGICAL INSTRUCTION FORMATS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>3-</b> 5   |

| J • ¬  | LOGICAL THOTACCTION TOWN ATS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | J )           |

|        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |

| 3.5    | LOGICAL INSTRUCTIONS Load (L, LR, LI) Load Immediate Short (LIS) Load Complement Short (LCS) Load Halfword (LH, LHI) Load Address (IA) Load Real Address (LRA) Load Halfword Logical (LHL) Load Multiple (LM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3-5           |

| 3.5.1  | Load (L, LR, LI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3-7           |

| 3.5.2  | Load Immediate Short (LIS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <b>n</b> 0    |

|        | Load immediate Short (LIS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3-0           |

| 3.5.3  | Load Complement Short (LCS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3-9           |

| 3.5.4  | Load Halfword (LH, LHI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3-10          |

| 3.5.5  | Load Address (IA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3-11          |

|        | Load Addless (IA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3-11          |

| 3.5.6  | Load Real Address (LRA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3-12          |

| 3.5.7  | Load Halfword Logical (LHL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3-16          |

|        | Total Multiple (JM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2 17          |

| 3.5.8  | Load Multiple (LM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3-1/          |

| 3.5.9  | Load Byte (LB, LBR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3-18          |

| 3.5.10 | Exchange Halfword Pegister (EXHR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3-19          |

|        | Enchange Data Datista (TVDD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3-20          |

| 3.5.11 | exchange byte Register (EXBR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3-20          |

| 3.5.12 | Load Byte (LB, LBR) Exchange Halfword Register (EXHR) Exchange Byte Register (EXBR) Store (ST)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3-21          |

| 3.5.13 | Store Halfword (STH)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3 <b>-</b> 22 |

|        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |

| 3.5.14 | Store Multiple (STM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3-23          |

| 3.5.15 | Store Byte (STB, STBR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-24          |

| 3.5.16 | Compare Logical (CL, CLR, CLI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3-25          |