# iSBC® 214 PERIPHERAL CONTROLLER SUBSYSTEM HARDWARE REFERENCE MANUAL

Order Number: 134910-001

Copyright © 1985, Intel Corporation Intel Corporation, 3065 Bowers Avenue, Santa Clara, California 95051 Additional copies of this manual may be obtained from:

Literature Department Intel Corporation 3065 Bowers Avenue Santa Clara, CA 95051

The information in this document is subject to change without notice.

Intel Corporation makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties to merchantability and fitness for a particular purpose. Intel Corporation assumes no responsibility for any errors that may appear in this document. Intel Corporation makes no commitment to update nor to keep current the information contained in this document.

Intel Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in an Intel product. No other circuit patent licenses are implied.

Intel software products are copyrighted by and shall remain the property of Intel Corporation. Use, duplication or disclosure is subject to restrictions stated in Intel's software license, or as defined in ASPR 7-104.9(a)(9).

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of Intel Corporation.

The following are trademarks of Intel Corporation and its affiliates and may be used only to describe Intel products:

| AEDIT              | iDIS                   | iPDS            | OpenNET       |

|--------------------|------------------------|-----------------|---------------|

| BITBUS             | iLBX                   | iRMX            | Plug-A-Bubble |

| BXP                | i <sub>m</sub>         | iSBC            | PROMPT        |

| COMMputer          | iMDDX                  | iSBX            | Promware      |

| CREDIT             | iMMX                   | iSDM            | QueX          |

| Data Pipeline      | Insite                 | iSXM            | QUEST         |

| Genius             | Intel                  | KEPROM          | Ripplemode    |

| i                  | intel                  | Library Manager | RMX/80        |

| $\triangle$        | intelBOS               | MCS             | RUPI          |

| 1                  | Intelevision           | Megachassis     | Seamless      |

| iATC               | inteligent Identifier  | MICROMAINFRAME  | SLD           |

| I <sup>2</sup> ICE | inteligent Programming | MULTIBUS        | SOLO          |

| ICE                | Intellec               | MULTICHANNEL    | SYSTEM 2000   |

| iCS                | Intellink              | MULTIMODULE     | UPI           |

| iDBP               | iOSP                   |                 |               |

and the combination of ICE, iCS, iRMX, iSBC, iSBX, or MCS and a numerical suffix.

| REV. | <b>REVISION HISTORY</b> | DATE  |

|------|-------------------------|-------|

| -001 | Original Issue.         | 07/85 |

|      |                         |       |

|      |                         |       |

|      |                         |       |

|      |                         |       |

|      |                         |       |

|      |                         |       |

|      |                         |       |

|      |                         |       |

|      |                         |       |

|      |                         |       |

|      |                         |       |

|      |                         |       |

|      |                         |       |

|      |                         |       |

|      |                         | -     |

|      |                         |       |

|      |                         |       |

|      |                         |       |

|      |                         |       |

|      |                         |       |

|      | •                       |       |

|      |                         |       |

|      |                         |       |

|      |                         |       |

|      |                         |       |

|      |                         |       |

|      |                         |       |

|      |                         |       |

|      |                         |       |

|      |                         |       |

|      |                         |       |

|      |                         |       |

v

This manual describes the uses and functions of the iSBC 214 multi-peripheral controller board. The information presented in the manual will enable the user to configure and install this controller board for any MULTIBUS-compatible system. The manual assumes that the reader is familiar with the standards for Intel single-board computers and associated peripheral storage devices. It also assumes the reader has a general knowledge of programming which includes specific Intel device programming.

This manual references the information contained in the following technical publication:

• Intel MULTIBUS Handbook, Order Number: 2108833.

This manual uses the asterisk (\*) after signal mnemonics to indicate that the signal is an active-low signal. A signal mnemonic without the trailing asterisk is an active-high signal.

# TABLE OF CONTENTS

PAGE

# Contents

|                               | PAGE |

|-------------------------------|------|

| GENERAL INFORMATION           |      |

| Introduction                  | 1-1  |

| iSBC® 214 Controller Features | 1-1  |

| Documentation                 | 1-3  |

| Specifications                | 1-3  |

# CHAPTER 2 CONTROLLER OPERATION

| Introduction                          | 2-1 |

|---------------------------------------|-----|

| iSBC® 214 Controller Board Functional |     |

| Description                           | 2-1 |

| CPU                                   |     |

| Interfaces                            | 2-1 |

| DMA Controller                        | 2-3 |

| Memory                                | 2-3 |

| Interrupt Controller                  | 2-3 |

| Bus Architecture                      | 2-4 |

#### CHAPTER 3 INSTALLATION

| Introduction                                | 3-1 |

|---------------------------------------------|-----|

| Unpacking and Inspecting the Controller     | 3-1 |

| Installation Considerations                 | 3-1 |

| Power Requirements                          | 3-1 |

| Cooling Requirements                        | 3-2 |

| Physical Characteristics                    | 3-2 |

| iSBC® 214 Controller Jumper Configuration   | 3-2 |

| Wake-Up Port Address Selection              | 3-2 |

| Wake-Up Block Address Selection             | 3-3 |

| System Data Bus Width Selection             | 3-4 |

| Interrupt Priority Number                   | 3-4 |

| Common Bus Request (CBRQ*)/Any              |     |

| Request (ANYRQST) Signal Selection          | 3-4 |

| MULTIBUS <sup>®</sup> Interface ACLO Signal | 3-5 |

| Flexible Disk Drive Configuration           | 3-5 |

| Winchester Drive Configuration              | 3-7 |

| QIC-2 Interface Parity Check                | 3-8 |

| iSBC® 214 Controller Hard Reset             | 3-8 |

|                                             |     |

#### CHAPTER 4 PROGRAMMING INFORMATION

| Introduction              | 4-1 |

|---------------------------|-----|

| Host/Board Communications | 4-1 |

| Wake-Up I/O Port          | 4-1 |

| I/O Communications Blocks |     |

| Wake-Up Block             | 4-4 |

| Channnel Control Block    | 4-5 |

# Controller Invocation Block

| Controller Invocation Block       | 4–6  |

|-----------------------------------|------|

| I/O Parameter Block               | 4–7  |

| Cold-Start Board Initialization   | 4–9  |

| Function Commands                 | 4–9  |

| Initialize (00H)                  | 4-11 |

| Transfer Error Status (01H)       | 4-13 |

| Format (02H)                      | 4-14 |

| Read Sector ID (03H)              | 4-19 |

| Read Data (04H)                   | 4-19 |

| Read to Buffer and Verify (05H)   | 4-22 |

| Write Data (06H)                  | 4-22 |

| Write Buffer Data (07H)           | 4-23 |

| Initiate Track Seek (08H)         | 4-24 |

| Buffer I/O (0EH)                  | 4-25 |

| Diagnostic (0FH)                  | 4-25 |

| Tape Initialize (10H)             | 4-26 |

| Rewind (11H)                      | 4-26 |

| Space Forward One File Mark (12H) | 4-27 |

| Write File Mark (14H)             | 4–27 |

| Erase Tape (17H)                  | 4-28 |

| Load Tape (18H)                   | 4-28 |

| Tape Reset (1CH)                  | 4-29 |

| Retension Tape (1DH)              | 4-29 |

| Read Tape Status (1EH)            | 4-29 |

| Read/Write Terminate (1FH)        | 4-30 |

| Function Modifiers                | 4-30 |

| Extended Status                   | 4-31 |

| Status Operation                  | 4-31 |

| Status Buffer Format              | 4-32 |

| Detailed Error Status             | 4-33 |

| Interrupts                        | 4-38 |

# CHAPTER 5

# **INTERFACING INFORMATION**

| Introduction                                | 5-1 |

|---------------------------------------------|-----|

| MULTIBUS® Interface                         | 5-1 |

| ST506/412 Winchester Disk Drive Interface   | 5–4 |

| SA450/460 5.25-inch Flexible Disk Interface | 5-6 |

| QIC-2 Tape Drive Interface                  | 5-8 |

#### CHAPTER 6 SERVICE INFORMATION

| Introduction                  | 6-1 |

|-------------------------------|-----|

| Service Diagrams              | 6-1 |

| Service and Repair Assistance |     |

# Tables

| TABLE | TITLE PAGE                                          |

|-------|-----------------------------------------------------|

| 1-1   | iSBC <sup>®</sup> 214 Controller Specifications 1-3 |

| 3-1   | Wake-Up Port Address Jumpers 3-3                    |

| 3-2   | Wake-up Block Address Selection                     |

|       | Example 3–3                                         |

| 3-3   | Interrupt Priority Number Selection 3-4             |

| 3-4   | Bus Arbitration Options 3-5                         |

| 3-5   | Flexible Disk Drive Jumper                          |

|       | Configuration 3-6                                   |

| 3-6   | Flexible Disk Media Change Detection                |

|       | Options 3-7                                         |

| 3-7   | Summary of Available Jumpers 3-9                    |

| 4-1   | I/O Channel Commands 4-2                            |

| 4-2   | Wake-Up Block Byte Contents 4-5                     |

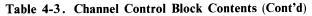

| 4-3   | Channel Control Block Contents 4-5                  |

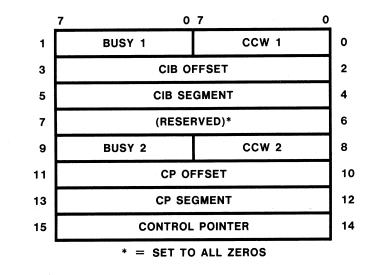

| 4-4   | Controller Invocation Block Contents 4-6            |

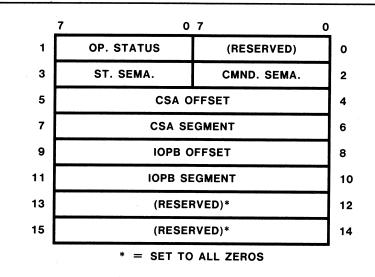

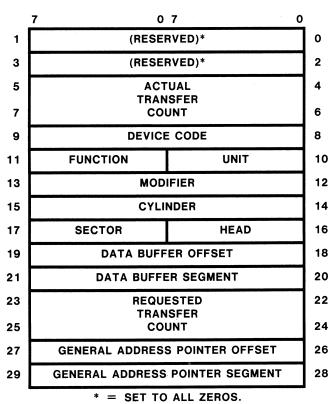

| 4-5   | I/O Parameter Block Contents 4-7                    |

| 4-6   | Function Command Summary 4-10                       |

| 4-7   | Error Status Buffer Format 4-32                     |

| 5-1   | MULTIBUS <sup>®</sup> Connector P1 Pin              |

|       | Assignments 5-1                                     |

# iSBC 214 Hardware Reference

| TABLE | TITLE                                         | PAGE  |

|-------|-----------------------------------------------|-------|

| 5-2   | MULTIBUS <sup>®</sup> Connector P2 Pin        |       |

|       | Assignments                                   | . 5-3 |

| 5-3   | MULTIBUS <sup>®</sup> Connector P1 I/O Signal |       |

|       | Description                                   | . 5-3 |

| 5-4   | MULTIBUS <sup>®</sup> Connector P2 I/O Signal |       |

|       | Description                                   | . 5–4 |

| 5-5   | Winchester Control Interface                  |       |

|       | Connections                                   | . 5–4 |

| 5-6   | Winchester Data Interface Connections         | . 5–5 |

| 5-7   | Winchester Control/Data Signal                |       |

|       | Description                                   | . 5-5 |

| 5-8   | Flexible Disk Interface Connections           | . 5-6 |

| 5-9   | Flexible Disk Interface Signal                |       |

|       | Descriptions                                  | . 5–7 |

| 5-10  | QIC-2 Control Signal Interface                |       |

|       | Connections                                   | . 5-8 |

| 5-11  | QIC-2 Tape Interface Signal                   |       |

|       | Descriptions                                  | . 5–9 |

| 6-1   | iSBC <sup>®</sup> 214 Default Jumper          |       |

|       | Configuration                                 | . 6–2 |

|       | <b>~</b>                                      |       |

# **Figures**

| FIGURE | TITLE                                      | PAGE |

|--------|--------------------------------------------|------|

| 1-1    | iSBC <sup>®</sup> 214 Controller Interface |      |

|        | Connections                                | 1–2  |

| 2-1    | iSBC <sup>®</sup> 214 Controller Logic     |      |

|        | Block Diagram                              | 2–2  |

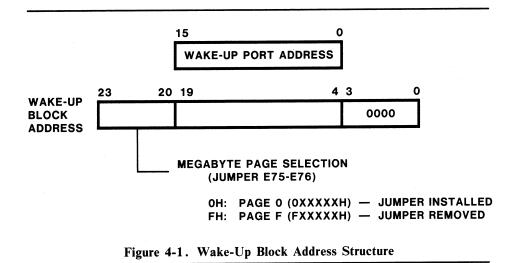

| 4-1    | Wake-Up Block Address Structure            | 4–2  |

| 4-2    | Host CPU/Board Interaction                 | 4–4  |

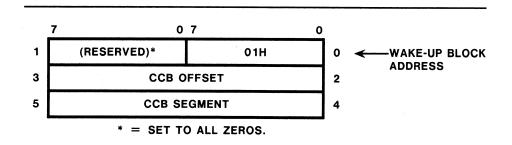

| 4-3    | Wake-Up Block Structure                    | 4–5  |

| 4-4    | Channel Control Block Structure            | 4–6  |

| 4-5    | Controller Invocation Block Structure      | 4–7  |

| 4-6    | I/O Parameter Block Structure              | 4–8  |

| 4-7    | Initialize Function Data Buffer Format     | 4–11 |

| 4-8    | Flexible Disk Drive Initialization         |      |

|        | Byte Structure                             | 4–13 |

| 4-9    | Tape Parameter Byte Structure              | 4–13 |

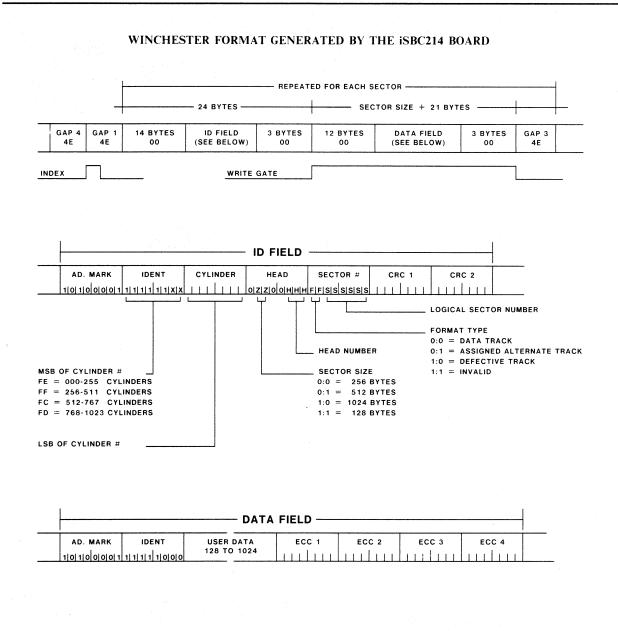

| 4-10   | Winchester Drive Media Format              | 4–15 |

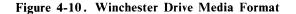

| 4-11   | Flexible Disk Media MFM Format             | 4–16 |

|        |                                            |      |

| FIGURE | TITLE PAGE                                       |

|--------|--------------------------------------------------|

| 4-12   | Flexible Disk Drive FM Format 4-17               |

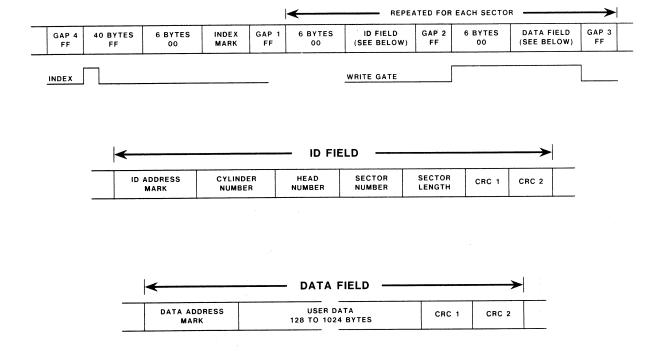

| 4-13   | Track Format Data Buffer Structure 4-18          |

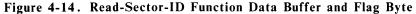

| 4-14   | Read-Sector-ID Function Data Buffer              |

|        | and Flag Byte 4–19                               |

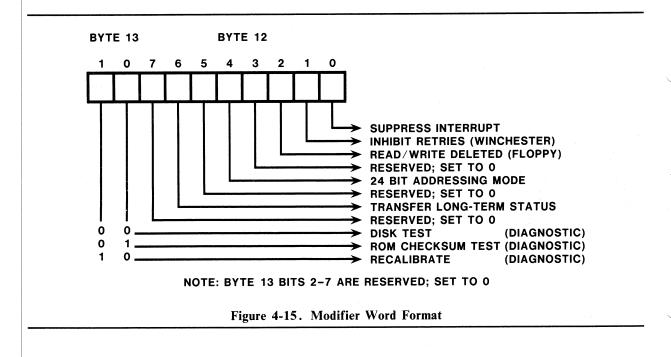

| 4-15   | Modifier Word Format 4-30                        |

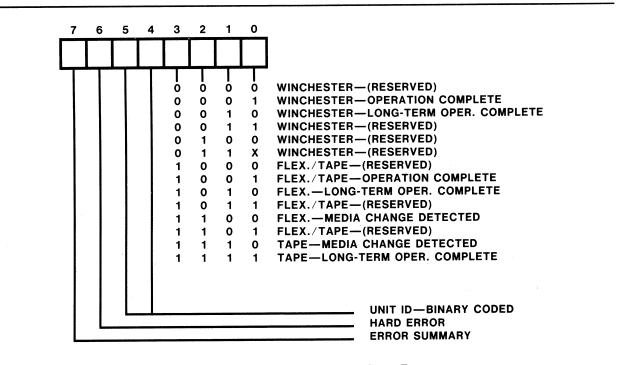

| 4-16   | Operation Status Byte Format 4-32                |

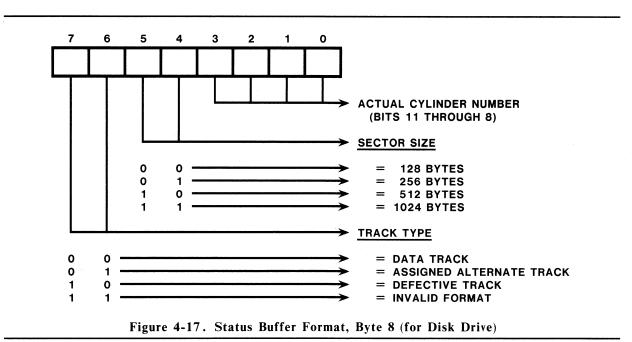

| 4-17   | Status Buffer Format, Byte 8                     |

|        | (for Disk Drive) 4-33                            |

| 4-18   | Status Buffer Format, Byte 0 4-34                |

| 4-19   | Status Buffer Format, Byte 1 4-35                |

| 4-20   | Status Buffer Format, Byte 2 4-37                |

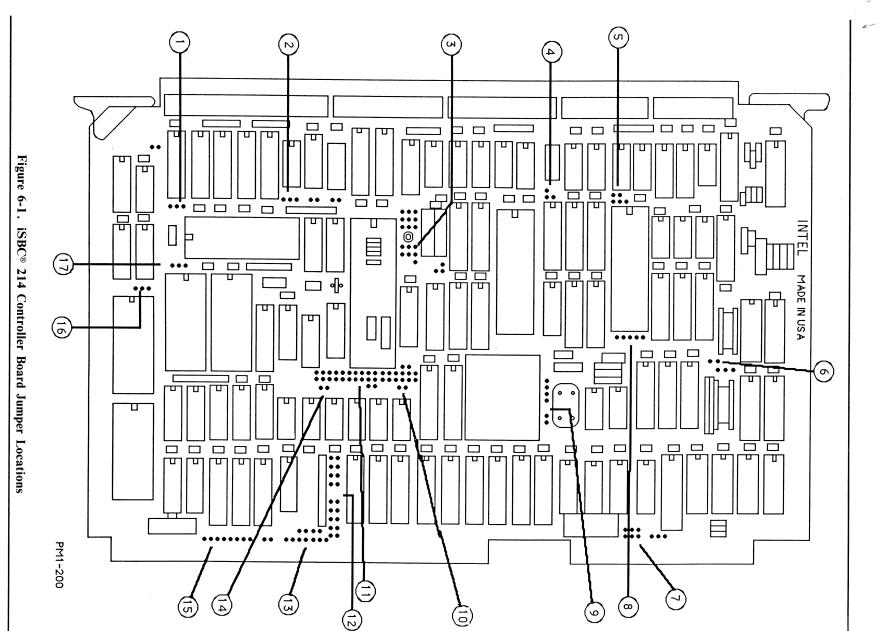

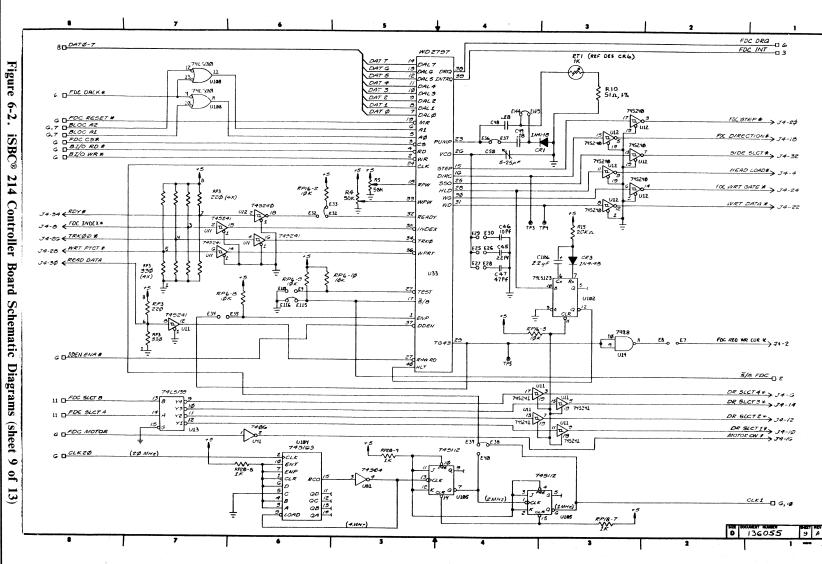

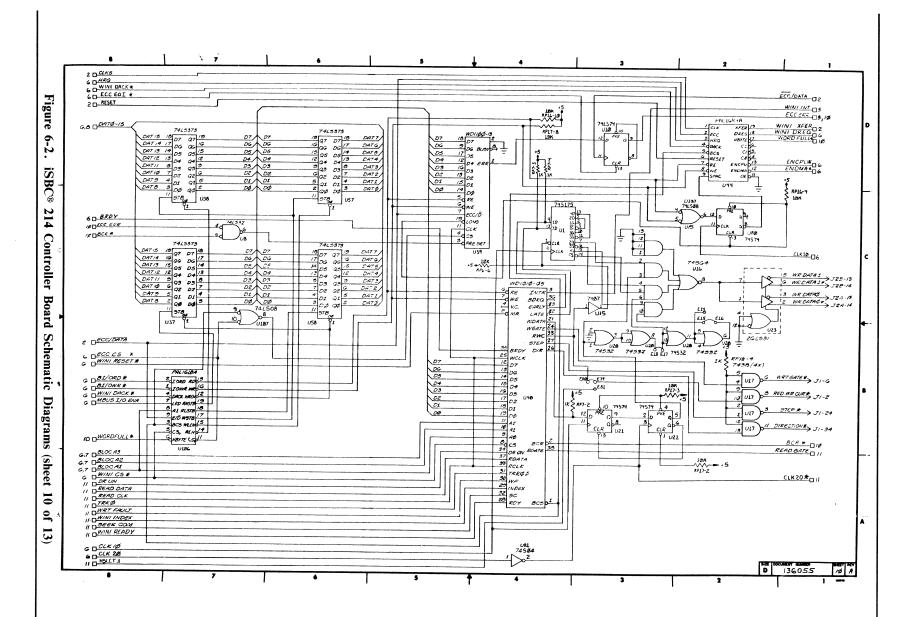

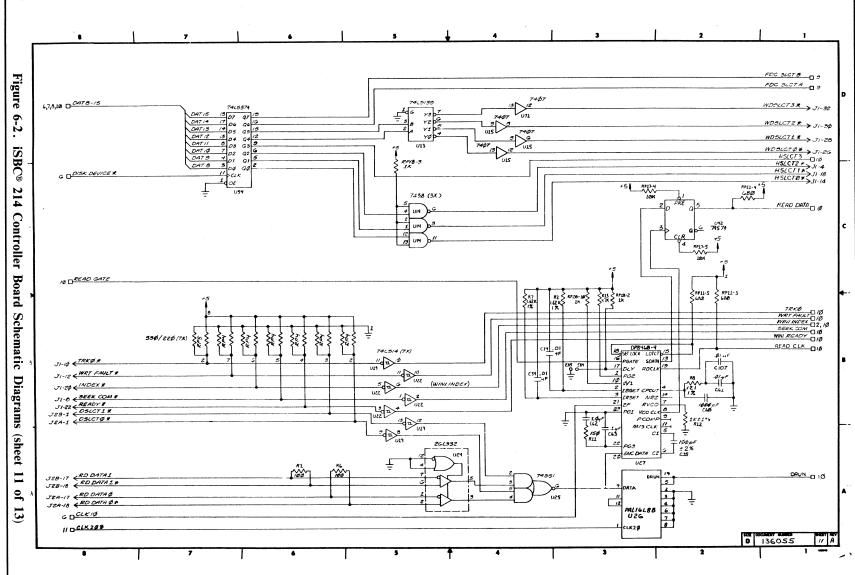

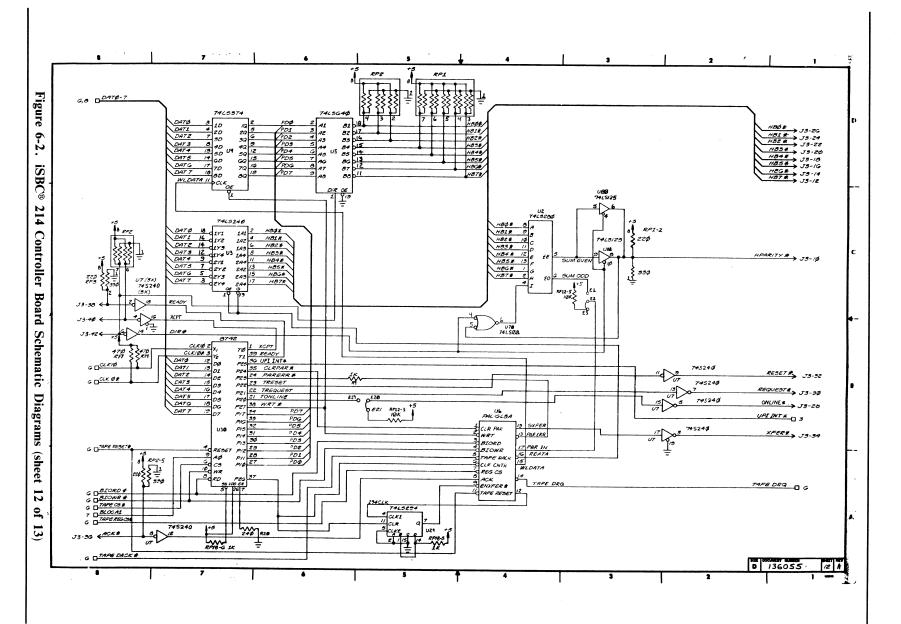

| 6-1    | iSBC <sup>®</sup> 214 Controller Board Jumper    |

|        | Locations                                        |

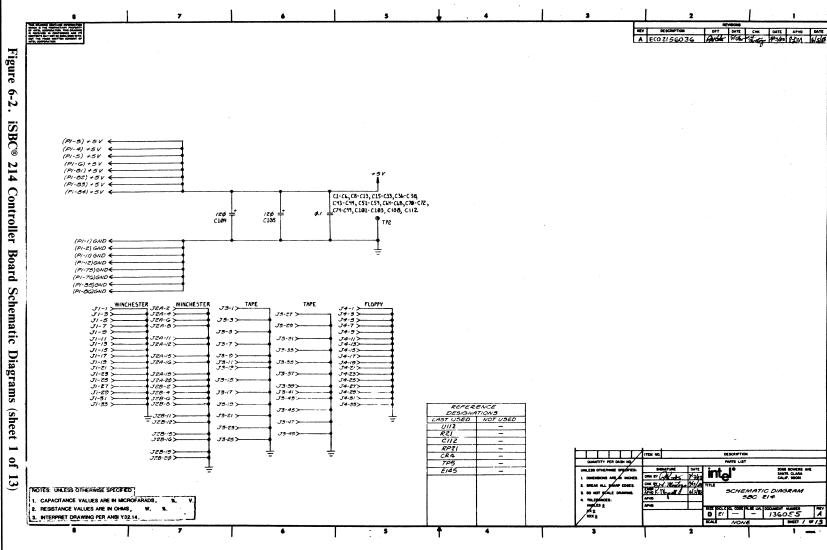

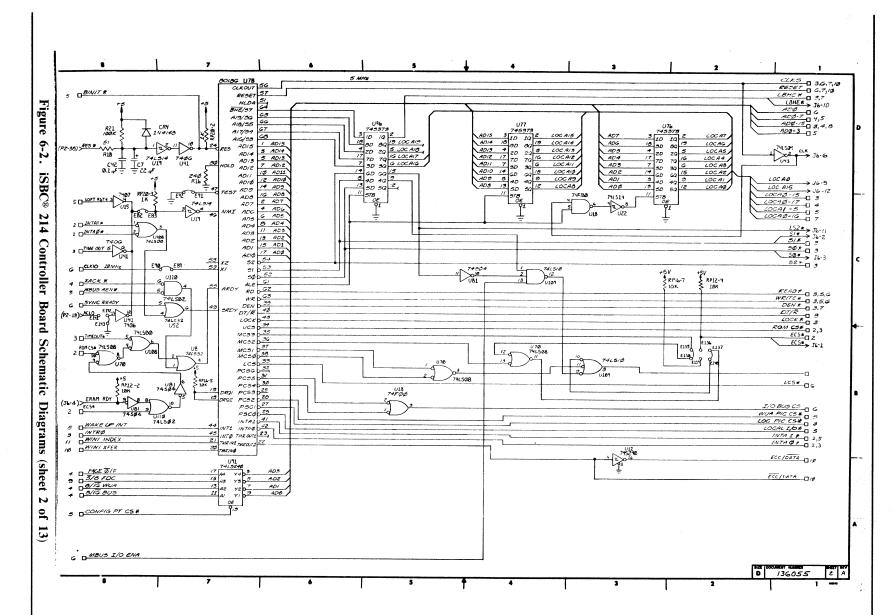

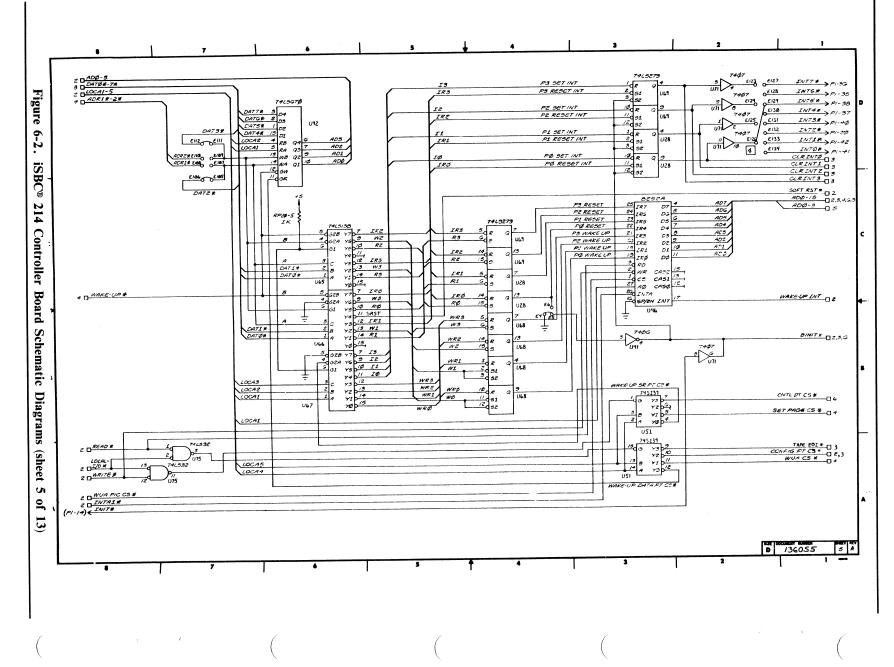

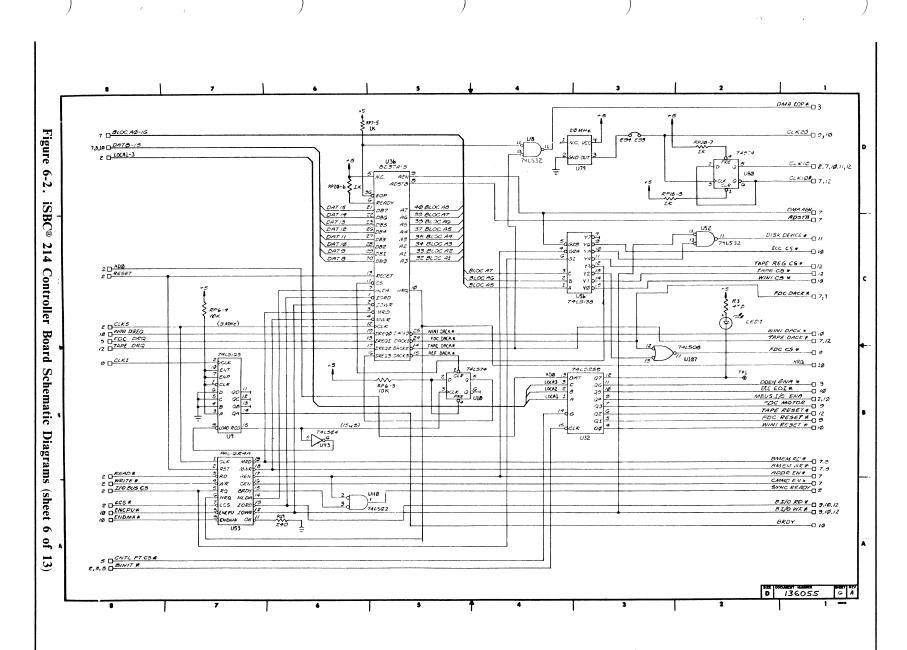

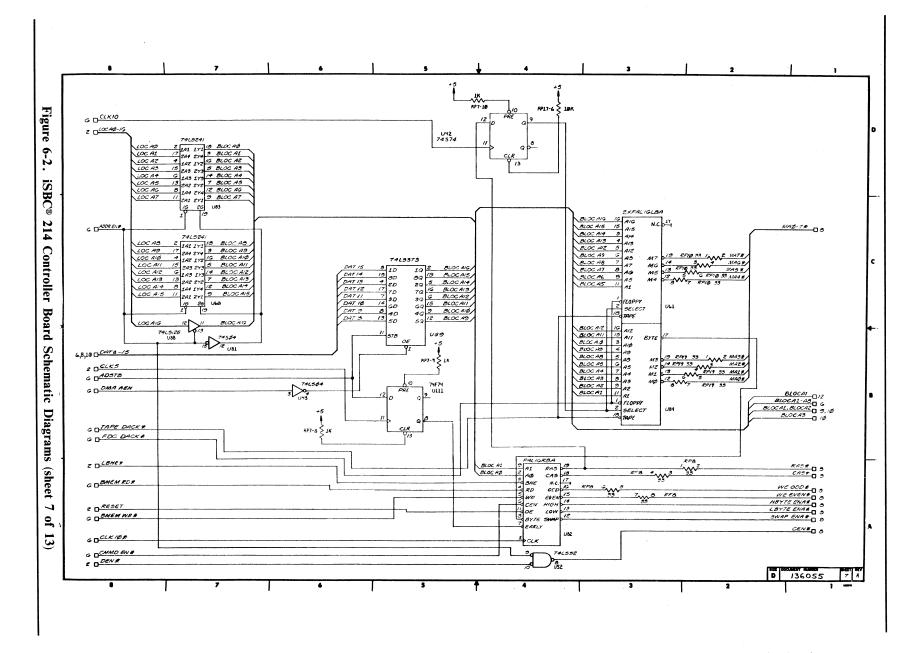

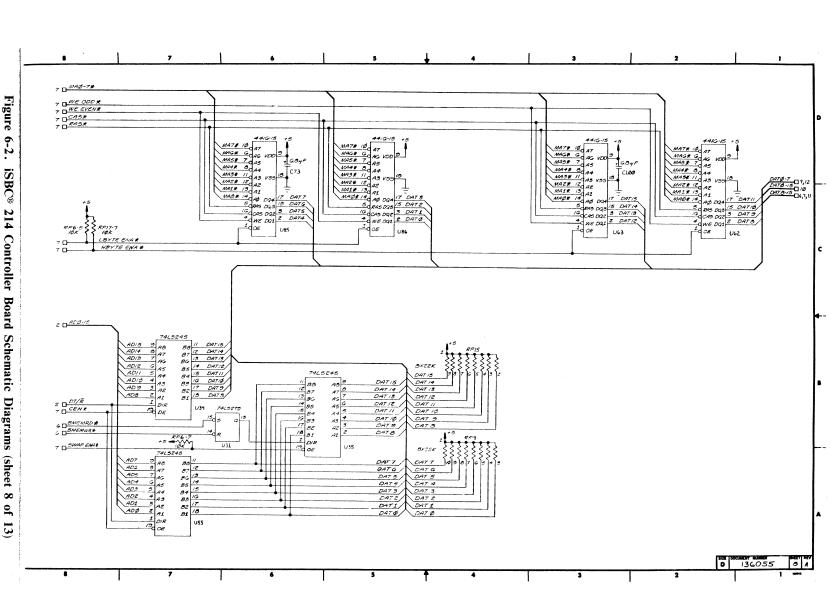

| 6-2    | iSBC <sup>®</sup> 214 Controller Board Schematic |

|        |                                                  |

| iSBC <sup>®</sup> 214 | Controller | Board S | Schematic |     |

|-----------------------|------------|---------|-----------|-----|

| Diagrams              |            |         |           | 6–4 |

viii

# CHAPTER 1 GENERAL INFORMATION

# **1.1 Introduction**

The iSBC 214 multi-peripheral controller provides MULTIBUS systems (8-bit and 16-bit data paths) with an interface for Winchester disk drives, flexible diskette drives, and streaming tape drives. A maximum of ten peripheral devices can interface with one board in the following configuration: two 5.25-inch Winchester disk drives, four 5.25-inch flexible diskette drives, and four <sup>1</sup>/<sub>4</sub>-inch streaming tape drives.

The iSBC 214 controller board emulates the iSBC 215G Winchester controller board communications protocol for interfacing the Winchester drives. The iSBX 217C and iSBX 218A MULTIMODULE® communications protocol is emulated for the tape drive and flexible disk drive interfaces. The Intel 80186 microprocessor serves as the controller's CPU. The Intel 80186 features direct memory access (DMA) and uses a dual-bus architecture to maximize data transfer between the host memory and attached peripheral devices. Each peripheral device interface has a dedicated on-board VLSI controller to perform the data I/O functions requested by the host system.

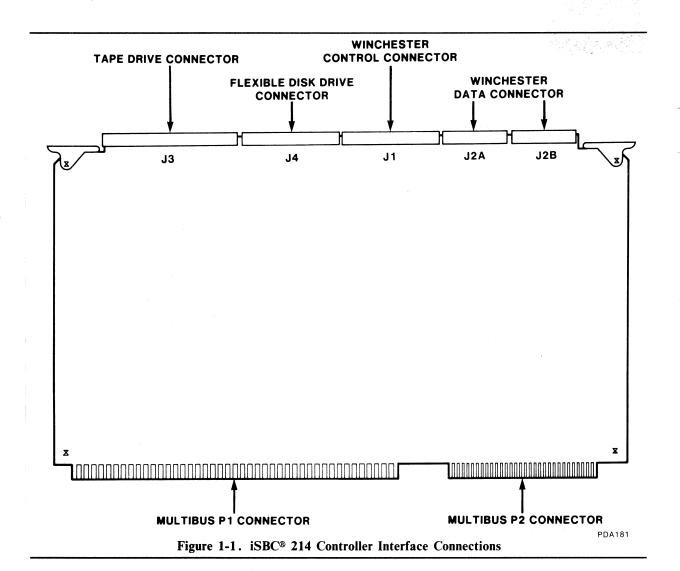

This chapter describes the major features and capabilities of the iSBC 214 controller. Figure 1-1 illustrates the board and identifies the MULTIBUS interface and peripheral device interface connections. The environmental and electrical specifications for the controller are contained in Table 1-1.

# **1.2 iSBC® 214 Controller Features**

The iSBC 214 controller increases the peripheral storage device control capabilities of Intel's micro-systems. It uses VLSI technology for device interface control rather than MULTIMODULES. The following list briefly describes some of the major features of the iSBC 214 controller:

- Supports the ST506/412 interface for one or two 5.25-inch Winchester drives

- Supports the SA450/460 interface for up to four 5.25-inch flexible disk drives

- Supports the QIC-2 interface for up to four <sup>1</sup>/<sub>4</sub>-inch Streaming Tape Drives

- Supports 24-bit MULTIBUS addressing

- Emulates iSBC 215G controller I/O Parameter Block communications protocol (with or without the iSBX 217C and iSBX 218A MULTIMODULES)

- Supports overlapped seek operations

- Performs retry, Error Checking, and Correcting operations on Winchester drive data transfers

- Software selectable bytes per sector, sectors per track, and tracks per surface for Winchester and flexible disk drives

- Provides on-board power-up diagnostics

Track Buffering of the Winchester disk drive is also a standard feature on the iSBC 214 controller. The algorithms and features of track buffering include the following:

- Parts or all of the three most recently used tracks are stored in the track buffers at any one time.

- The requested sector plus the remainder of the track is read from the disk and written to the buffer.

- A rotational position sensor ensures the iSBC 214 controller will read the full track in one rotation time.

- Any read operation that references the data stored in the buffer will access the buffer and not the disk.

- Read operations that reference a track other than those stored in the track buffers will cause replacement of the least recently used track with data from the currently referenced track.

- The requested data is transferred to the host system as soon as it is read into the buffer and ECC checked.

• All write operations are written immediately to the disk and the buffer if applicable. If the write operation is not applicable to the buffer, the buffer data remains unaltered.

Physical connections for the Winchester interface consist of a 34-pin right-angle connector for the control cable and two 20-pin right-angle connectors for the data cables. The QIC-2 interface for tape drives consists of one 50-pin right-angle connector. The interface for the 5.25-inch flexible disk drives is a single 34-pin right-angle connector. Refer to Figure 1-1 for the interface locations on the board. Additional information on the pin assignments and signals for the peripheral device interfaces and the MULTIBUS interface is contained in Chapter 5.

## **1.3 Documentation**

The latest version of board's schematics will be shipped with the iSBC 214 Controller Board.

# **1.4 Specifications**

Table 1-1 lists the environmental and electrical specifications of the iSBC 214 controller.

| Tuble 1-1. ISBC 214 Controller Specifications                                                                       |                                   |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------|-----------------------------------|--|--|--|--|

| Physical Characteristics:                                                                                           |                                   |  |  |  |  |

| Width:                                                                                                              | 6.75″ (17.2 cm)                   |  |  |  |  |

| Length:                                                                                                             | 12.00" (30.5 cm)                  |  |  |  |  |

| Height:                                                                                                             | 0.5″ (1.3 cm)                     |  |  |  |  |

| Power Requirements:                                                                                                 |                                   |  |  |  |  |

| + 5VDC (± 5%) @                                                                                                     | 4.5 Amperes                       |  |  |  |  |

| Environmental Require                                                                                               | ments:                            |  |  |  |  |

| Temperature<br>operating: 0° C to +55° C (+50° F to +131° F)<br>non-operating: -55° C to +85° C (-67° F to +185° F) |                                   |  |  |  |  |

| Humidity: up to 90% non-condensing                                                                                  |                                   |  |  |  |  |

| Memory Capacity:                                                                                                    |                                   |  |  |  |  |

| ROM: 32K bytes<br>RAM: 32K bytes                                                                                    |                                   |  |  |  |  |

| Interface:                                                                                                          |                                   |  |  |  |  |

| MULTIBUS:                                                                                                           | IEEE 796 System Bus Specification |  |  |  |  |

| Winchester Drive:                                                                                                   | ST506/ST412                       |  |  |  |  |

| Flexible Disk Drive:                                                                                                | SA460/450 (5.25 inch drive)       |  |  |  |  |

| Tape Drive:                                                                                                         | QIC-2 Streaming Tape              |  |  |  |  |

Table 1-1. iSBC® 214 Controller Specifications

| Transfer Rates:       |                                                                                                  |                          |  |  |

|-----------------------|--------------------------------------------------------------------------------------------------|--------------------------|--|--|

| Controller to c       | er from:                                                                                         | Transfer Rate            |  |  |

| Host memory (16 bi    | t data path)                                                                                     | 1.6M bytes/sec (max)     |  |  |

| Host memory (8 bit    | data path)                                                                                       | 0.8M bytes/sec (max)     |  |  |

| Winchester drive (ST  | 506)                                                                                             | 0.63M bytes/sec (fixed)  |  |  |

| Flex. drive (D/D 5.2  | 5")                                                                                              | 31.25K bytes/sec (fixed) |  |  |

| Flex. drive (S/D 5.25 | 5")                                                                                              | 15.63K bytes/sec (fixed) |  |  |

| Tape drive (stream.   | 90 ips)                                                                                          | 11.25K bytes/sec (avg)   |  |  |

| Tape drive (stream.   | 30 ips)                                                                                          | 30.00K bytes/sec (avg)   |  |  |

| Address Selection:    |                                                                                                  |                          |  |  |

| User selectable betw  | veen 20-bit and 24-bit ac                                                                        | ldress modes             |  |  |

| MULTIBUS Compliance   | Evels:                                                                                           |                          |  |  |

|                       | D8-bit or D16-bit<br>user defined M20 or M<br>user selectable, 8-bit o<br>V0 (non-bus vectored i | r 16-bit                 |  |  |

# Table 1-1. iSBC<sup>®</sup> 214 Controller Specifications (Cont'd)

# 2.1 Introduction

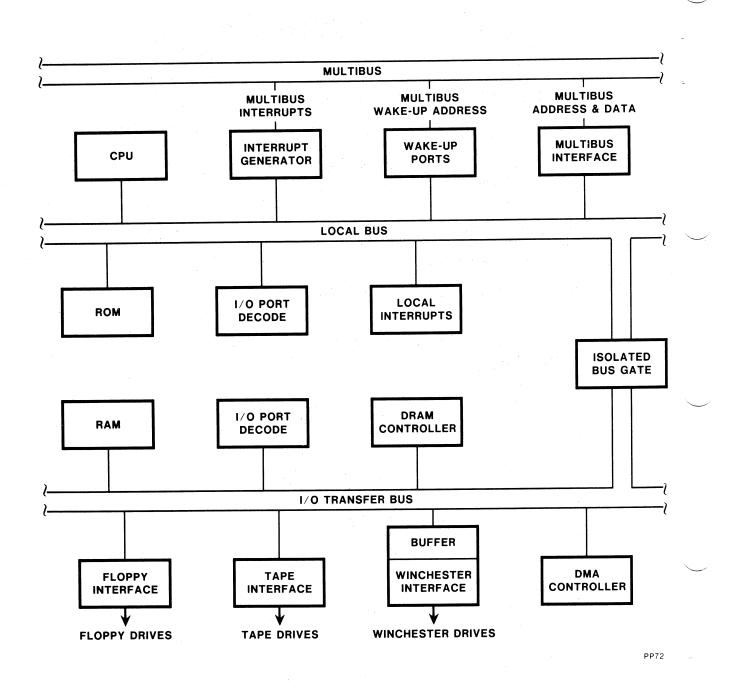

This chapter provides a high-level explanation of the iSBC 214 controller board operation. The information presented is not intended to be a detailed theory of operation, rather a description of the functional operation of the board's major functions as shown in the logical block diagram, Figure 2-1.

## 2.2 iSBC<sup>®</sup> 214 Controller Board Functional Description

The iSBC 214 controller provides MULTIBUS compatible systems with an intelligent interface for 5.25-inch Winchester and flexible disk drives and ¼-inch streaming tape drives in a single board package. The controller performs data I/O operations at the request of the host system. Detailed command information, contained in four blocks of dedicated host memory, is fetched by the controller CPU. The controller CPU then initializes the appropriate on-board VLSI device controller to perform the actual operation. Chapter 3 contains a detailed description of the communications protocol used by the iSBC 214 controller. Figure 2-1 is a logical block diagram of the iSBC 214 controller. The following sections describe the major functions on the board as illustrated in Figure 2-1.

#### 2.2.1 CPU

The iSBC 214 Board uses the Intel 16-bit, 80186 processor. The 80186 operates at 5 MHz and consists of a CPU, an interrupt controller, internal DMA controller, address select logic, wait-state generator, and clock divider circuit. The CPU is responsible for all transfer operations between the host system and the controller; data transfer between the host system and controller memory is handled by the 2-channel internal DMA controller. The CPU fetches I/O command structures from the host system memory and returns operational status to the host. The program store for the 80186 CPU consists of two Intel 27128 EPROMs which provide the controller with 32K bytes of Read-Only memory on the local bus.

#### 2.2.2 Interfaces

The MULTIBUS interface is supported via two standard card edge connectors. The MULTIBUS interface subsystem consists of the MULTIBUS interrupt port, controller Wake-up port, and the address/data interface. The P1 connector is an 86-pin card edge connector which serves as the host system's communication channel to the controller. Power for the iSBC 214 Board is also provided through the P1 connector. The P2 connector is a 60-pin card edge connector which supports the optional 24-bit MULTIBUS addressing scheme and the power-fail ACLO signal.

The ST506/412 Winchester disk drive interface consists of a 34-pin right-angle connector for the control signal cable and two 20-pin right-angle connectors for the data I/O cables. The Winchester controller subsystem consists of three discrete LSI devices and four registered buffers. The Intel 82062 device functions as

#### Figure 2-1. iSBC<sup>®</sup> 214 Controller Logic Block Diagram

the Winchester controller. This device performs read and write operations on Winchester drives. The WD1100-13 device generates the Error Correction Code (ECC).

The SA450/460 flexible disk drive interface uses a single 34-pin right-angle connector. The flexible disk drive controller is the WD2797 device. This device transfers data directly to the I/O transfer bus from the attached flexible disk drive(s).

The QIC-2 <sup>1</sup>/<sub>4</sub>-inch streaming tape drive interface uses a single 50-pin right-angle connector on the board. The tape drive controller subsystem is based on the Intel 8742 Universal Peripheral Interface (UPI). This device controls the tape drive interface and offloads the Intel 80186 CPU of much of the lowlevel hardware control required by the tape interface.

#### 2.2.3 DMA Controller

The DMA controller on the iSBC 214 board is an Intel 8237A-5 DMA controller. This device is driven from the Intel 80186 5 MHz. clock and controls four independent DMA channels. The Intel 8237A-5 controls concurrent data transfer operations between the respective peripheral device controllers and the board's dynamic RAM. The four DMA channels have assigned fixed priorities; the highest priority is the Winchester controller, followed in descending priority by the flexible disk controller, tape controller, and DRAM refresh controller.

#### 2.2.4 Memory

The iSBC 214 controller has 32K bytes of contiguous dynamic RAM, implemented with four 16K x 4, 18-pin devices. The RAM is accessed by the Intel 80186 CPU and the Intel 8237A-5 DMA controller over the I/O transfer bus. It supports I/O data transfer buffering and the Intel 80186 stack and interrupt vectors. The RAM is configured for 16-bit (word) access but also supports byteswapping (occurring on DMA transfers between the controller memory and either the tape or flexible disk controllers) for 8-bit DMA I/O data transfers. The DRAM refresh controller consists of a discrete latch in conjunction with the fourth 8237A-5 DMA controller channel. In addition, a registered PAL serves as the state machine sequencer for all memory cycles while two non-registered PALs perform address multiplexing and shifting operations.

#### 2.2.5 Interrupt Controller

The control firmware for the board is based on a custom real-time peripheral controller operating system and is interrupt driven. The Intel 80186 internal priority interrupt controller and two Intel 8259A Programmable Interrupt Controllers (PIC) are responsible for interrupt support. The Intel 80186 CPU can be interrupted by internally generated interrupts, Wake-Up port 8259A interrupts, I/O system 8259A interrupts, or non-maskable controller error interrupts. From a systems point-ofview, the iSBC 214 controller is configured for MULTIBUS interrupt 5.

#### **2.2.5.1 Intel 80186 Internal Interrupts**

The 80186 CPU acts as the master interrupt controller for the board. Internal interrupts may be generated from the Real-Time clock, the 80186 internal DMA controller, either of the two external (to the CPU) 8259A PICs, or the externally-driven NMI (Non-Maskable Interrupt) error signal.

#### 2.2.5.2 Wake-up Port 8259A PIC

The Wake-Up Port 8259A Programmable Interrupt Controller (PIC) interrupts the on-board CPU whenever the host performs a write operation to the Wake-Up Port address.

#### 2.2.5.3 I/O System 8259A Interrupts

The four remaining internal interrupt inputs to the I/O system 8259A PIC come from the three peripheral device I/O controllers and the Winchester ECC generation/checking circuitry. Interrupts through these input lines signify the completion of an I/O operation or a device error. The Winchester ECC circuit generates interrupts to the Intel 80186 CPU when there is an ECC error in the Winchester data flow.

#### 2.2.5.4 Non-Maskable Interrupts

Three types of non-maskable interrupts (NMI) can occur through the input line to the on-board CPU. For each occurence of an NMI, the iSBC 214 controller requires a host system Wake-up or power-up restart to continue operations. The interrupts are as follows:

- 1. **Special Wake-up port channel 0 attention**—indicates that the host system is trying to issue a hardware reset to the controller and restart the board as if a power-up has just occurred.

- 2. **Bus timeout**—indicates that an 80186 requested access to its local bus, the I/O transfer bus, or the MULTIBUS and was not granted access within the time-out period of seven (7) milliseconds. This type of interrupt also causes the controller to post error status to the host and halt ALL I/O activity.

- 3. A power failure—indicated by the MULTIBUS ACLO signal which signifies that power to the system has dropped below the system's threshold. The Intel 80186 immediately halts ALL I/O operations and goes into a halt state.

#### 2.2.6 Bus Architecture

The iSBC 214 controller uses a dual bus architecture for maximum I/O transfer efficiency. As shown in Figure 2-1, the board has a local bus and an I/O transfer bus. The local bus is a 16-bit data path accessible only by the 80186 CPU. The 80186 processor operates with 0 Wait States on the bus to process function codes and/or DMA data. The I/O transfer bus is also a 16-bit data path, but it is shared by the 80186 DMA processor and the 8237A-5 DMA controller to handle I/O data transfers to and from the peripheral storage devices.

# 3.1 Introduction

This chapter provides the necessary information for preparing the iSBC 214 controller board and installing the board into a MULTIBUS-compatible system. Included in this chapter are instructions for unpacking and inspecting the controller. The remaining sections define the factory-installed jumper configuration of the iSBC 214 board. Table 3-7 at the end of this chapter summarizes the jumper configuration and options on the iSBC 214 board.

## 3.2 Unpacking and Inspecting the Controller

Immediately upon receipt of the controller package, inspect the shipping carton for evidence of damage or mishandling while in transit. If the shipping carton is severely damaged or water-stained, request that the carrier's agent be present when the carton is opened. If the carrier's agent is not present when the carton is opened, and the contents are damaged, keep the carton and all packing materials for a subsequent inspection by the agent.

For repair of the product damaged during shipment, contact the Intel Product Service Center to obtain a Return Authorization Number and receive further instructions. Chapter 6 lists the telephone numbers for the various service centers. Because a purchase order is required to complete the repair, submit a copy of the purchase order to the shipping carrier with your claim.

## **3.3 Installation Considerations**

The iSBC 214 controller board can be installed in any Intel cardcage/backplane or user-designed backplane that complies with the MULTIBUS IEEE-796 interface specification. The board occupies one backplane slot.

The iSBC 214 board operates as a MULTIBUS multi-master interfacing Winchester drives, flexible disk drives and tape drives with the host system. For this reason, the slot where the board is installed must include bus priority arbitration.

#### **3.3.1 Power Requirements**

The iSBC 214 controller board requires a +5VDC ( $\pm 5\%$ ) power at a maximum current of 4.5 A. The power required by the tape drive, flexible disk drive, and Winchester drive is supplied through separate and direct cabling.

#### 3.3.2 Cooling Requirements

The iSBC 214 controller board generates 21.329 kilogram calories of heat per minute (85.32 BTU per hour). (Figures based on a maximum of 25 Watts per hour.) Sufficient circulating, cooling air (about 200 linear feet per minute under normal operating conditions) must be provided to keep the environmental temperature within the required operating range (0° C to 55° C).

#### 3.3.3 Physical Characteristics

The iSBC 214 controller board is a standard iSBC board with the following dimensions: 6.75 in. by 12.0 in. by 0.5 in. Table 1-1 provides a complete list of the controller's specifications.

# 3.4 iSBC<sup>®</sup> 214 Controller Jumper Configuration

The iSBC 214 board contains 138 stake pins which can be jumpered to configure the controller's functions in various system environments. Figure 6-1 illustrates the physical location and the default configuration of jumpered stake pins. Each stake pin on the board is identified by the letter E and a number and includes several hard-wired pads. The following sections explain the functions of each set or array of jumpered stake pins.

#### NOTE

A asterisk (\*) following a signal mnemonic indicates the signal is active when it is in the low state.

#### 3.4.1 Wake-Up Port Address Selection

The host CPU communicates with the iSBC 214 board through an I/O port, called the Wake-up port, and four communication blocks in the host system memory. The wake-up port is a byte wide port in the systems I/O address space whose address is defined by a group of jumpers on the iSBC 214 board.

Sixteen pairs of jumpers on the iSBC 214 board define all sixteen bits of the wake-up port address. These jumpers are located in a logical manner from left to right, corresponding to the MSB (Most Significant Bit) through LSB (Least Significant Bit) of the wake-up port address. Installed jumper plugs define the corresponding address bits to "1". Refer to table 3-1 to find the correlation between the jumper pairs and the bits of the wake-up port address.

For a host CPU which has 8 bit I/O address space (0 through 255) only eight of these sixteen jumpers (the ones corresponding to the least significant eight bits of the wake-up port address) should be configured for the required wake-up port address. The other eight jumpers should also be configured for the Wake-up Block Address calculation. See section 3.4.2 for the details of the wake-up block address.

Jumpers E119–E120 determine the host CPU's I/O address space range. A jumper plug must be installed for the host CPU's with 16-bit I/O address space, such as Intel 8086 (default configuration); not installed for the host CPU's with 8-bit I/O address space, such as Intel 8085.

| Jum  |     |                             |

|------|-----|-----------------------------|

| From | То  | Wake-up Port<br>Address Bit |

| E43  | E44 | F                           |

| E45  | E46 | E                           |

| E47  | E48 | D                           |

| E49  | E50 | С                           |

| E51  | E52 | В                           |

| E53  | E54 | Ā                           |

| E55  | E56 | 9                           |

| E57  | E58 | 8 (*)                       |

| E59  | E60 | 7                           |

| E61  | E62 | 6                           |

| E63  | E64 | 5                           |

| E65  | E66 | 4                           |

| E67  | E68 | 3                           |

| E69  | E70 | 2                           |

| E71  | E72 | 1                           |

| E73  | E74 | 0                           |

Table 3-1. Wake-up Port Address Jumpers

(\*)-Default configuration; jumper installed for the default wake-up port address 0100H.

#### 3.4.2 Wake-up Block Address Selection

Four I/O communication blocks in the host system memory are used as part of the communication protocol between the host CPU and the iSBC 214 board. Refer to Chapter 4-Programming Information-for a detailed discussion of the communication protocol and these I/O communication blocks. The first of these blocks is the Wake-up block, which requires six bytes in the host system memory. The wake-up block address and the wake-up port address together identify the location of the wake-up block. The iSBC 214 board reads the wake-up port address jumpers to calculate the wake-up block address. This gives a 20-bit address to locate the wake-up block anywhere in a 1 Megabyte memory address space. In Multibus systems with up to 16 Megabyte address space (24-bit addressing), the wake-up block can be located in either the first 1 Megabyte page or the last 1 Megabyte page. Installing jumper E75-E76 (default configuration) places the wakeup block in the first Megabyte page (0XXXXXH), and removing the jumper E75-E76 places the wake-up block in the last Megabyte page (FXXXXXH). Jumper E75-E76 must be installed for the systems with up to 1 Megabyte memory address space.

Note that all sixteen bits of the wake-up port address is used for the wake-up block address calculation, therefore the most significant eight bits of the wake-up port jumpers should be configured for the required wake-up block address even if the board is configured for 8-bit I/O address space. Table 3-2 is an example to clarify these options.

| Wake-up Port Address<br>Jumpers = 1234H |                         | Wake-up Port Address<br>(I/O address space) | Wake-up Block Address<br>(Memory address space) |

|-----------------------------------------|-------------------------|---------------------------------------------|-------------------------------------------------|

| 8-bit I/O<br>Address Space              | PAGE-0<br>E75-E76 Inst. | 34H                                         | 012340H                                         |

| Jumper E119-<br>E120<br>Removed         | PAGE-F<br>E75-E76 Open  | 34H                                         | F12340H                                         |

Table 3-2. Wake-up Block Address Selection Example

| Wake-up Port Address<br>Jumpers = 1234H |                         | Wake-up Port Address<br>(I/O address space) | Wake-up Block Address<br>(Memory address space) |  |

|-----------------------------------------|-------------------------|---------------------------------------------|-------------------------------------------------|--|

| 16-bit I/O<br>Address Space             | PAGE-0<br>E75-E76 Inst. | 1234H                                       | 012340H                                         |  |

| Jumper E119-<br>E120<br>Removed         | PAGE-F<br>E75-E76 Open  | 1234H                                       | F12340H                                         |  |

Table 3-2.

Wake-up Block Address Selection Example (Cont'd)

Assume wake-up port address jumpers are configured for 1234H.

#### 3.4.3 System Data Bus Width Selection

System data bus width selection jumper E77-E78 sets the board for the type of system data bus with which the iSBC 214 board is to interface. It is installed for a 16-bit data path, not installed for an 8-bit data path. Installing the jumper allows use of 16-bit data transfer mode to access the system bus (if the system memory supports 16-bit accesses), even though the host CPU supports only 8-bit accesses.

#### 3.4.4 Interrupt Priority Number

The iSBC 214 board internal interrupt request signal can be assigned to any of eight Multibus interrupt priority numbers (INT0\* through INT7\*). The number is selected by wire wrapping two jumper stake pins together as indicated in Table 3-3. The default configuration is INT5\* (wirewrap jumper from E126 to E129).

|                     | Install Wire W | rap Jumper   |

|---------------------|----------------|--------------|

| Interrupt<br>Number | From Stake Pin | To Stake Pin |

| 0                   | E126           | E134         |

| 1                   | E126           | E133         |

| 2                   | E126           | E132         |

| 3                   | E126           | E131         |

| 4                   | E126           | E130         |

| 5                   | E126           | E129         |

| 6                   | E126           | E128         |

| 7                   | E126           | E127         |

Table 3-3. Interrupt Priority Number Selection

#### 3.4.5 Common Bus Request (CBRQ\*)/Any Request (ANYRQST) Signal Selection

The CBRQ\* and ANYRQST signals provide the required mode select inputs to the 8289 arbiter. The arbitration options are shown in Table 3-4.

CBRQ\* is a bidirectional interface signal that improves bus access time by allowing a bus master to retain control of the Multibus interface without contending for it on each transfer cycle, while no other master is requesting control of the bus. The signal is either supplied from the bus via connector P1 or connected to ground, depending on the configuration of the jumper set E100, E101, and E102. This signal operates the same in a parallel or a serial priority resolution scheme.

ANYRQST is a bus arbiter input signal that controls whether the iSBC 214 board will allow a lower-priority device to gain access to the Multibus interface by the CBRQ\* signal. The signal is either high (connected to +5V through a resistor), or low (connected to ground), depending on the configuration of the jumper set E97, E98, and E99. When ANYRQST is high, a lower-priority device may gain control of the bus by activating the CBRQ\* signal. When ANYRQST is low, a lower-priority device cannot gain control of the bus until it gains priority through the BPRN\* signal.

| Signal                  | Jumper                      | Connect To     | Description                                                                                                                                                                                                                                                                                      |

|-------------------------|-----------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CBRQ*<br>and<br>ANYRQST | E101-E102<br>E97-E98        | Bus<br>Ground  | Arbitrate to gain access of Multibus interface.<br>If continued access is required, iSBC 214<br>board retains control until higher-priority de-<br>vice requests bus, at which time board arbi-<br>trates again and surrenders bus control to only<br>that device.                               |

| CBRQ⁺<br>ANYRQST        | E101-E102<br>and<br>E98-E99 | Bus<br>+ 5V    | Arbitrate to gain access to and multibus in-<br>terface. If continued access is required, iSBC<br>214 board retains control until another device<br>requests bus, at which time board arbitrates<br>again and surrenders bus control to request-<br>ing device (either higher or lower priority. |

| CBRQ*<br>ANYRQST        | E100-E101<br>and<br>E98-E99 | Ground<br>+ 5V | Arbitrate for every bus access.                                                                                                                                                                                                                                                                  |

Table 3-4. Bus Arbitration Options

#### **3.4.5.1** Bus Priority Out (BPRO\*) Signal Selection

The BPRO\* signal is used in serial Multibus priority schemes. BPRO\* must be connected to the BPRN\* input of the bus master with the next lower priority. The BPRO\* signal is enabled for serial resolution by installing jumper E95-E96, or disabled for parallel resolution by removing the jumper. The **default configuration** is for parallel resolution with the jumper removed.

#### 3.4.6 MULTIBUS<sup>®</sup> Interface ACLO Signal

A three-way jumper set, E141, E142, and E143, provides the iSBC 214 controller board with a connection to the MULTIBUS interface ACLO signal. This signal, when active, indicates a potential power failure within the host system. This signal is an optional pin on the MULTIBUS system P2 connection and may not be supported by all systems that use the iSBC 214 board. The **default configuration** jumpers E142 to E143 which disables the ACLO input. To enable the ACLO input, jumper pin E141 to pin E142. When ACLO is enabled and active, it generates a Non-Maskable Interrupt (NMI) to the Intel 80186 CPU. See Section 2.2.5.4 for additional information.

#### 3.4.7 Flexible Disk Drive Configuration

The following paragraphs describe the **default configuration** and function of the stake pins that allow the board to interface to the SA450/460 5.25-inch flexible

disk drive standard. Table 3-5 lists the factory default jumper configuration for the iSBC 214 controller.

| Jumper             | Function                   |

|--------------------|----------------------------|

| E7-E8 — open       | Reserved—must be open      |

| E9-E10 — open      | Reserved—must be open      |

| E31-E33 — jumper   | Drive Ready Signal         |

| E34-E35 — open     | Disk Write Precompensation |

| E36-E37 — jumper   | Reserved—must be installed |

| E38-E39 — jumper   | Reserved—must be installed |

| E115-E116 — jumper | Reserved—must be installed |

| E144-E145 — jumper | Pump Filter Circuit        |

Table 3-5. Flexible Disk Drive Jumper Configuration

#### 3.4.7.1 Disk Drive Ready Signal

A three-way jumper set, stake pins E31, E32, and E33 allows the user two options for the Drive Ready signal. The board can be configured to force the signal active (high) constantly (for drives that do not control the Drive Ready signal), or to support drives that generate their own Drive Ready Signal. The **default configuration** jumpers E31 to E33 which causes the board to drive the Drive Ready signal active (high). Jumper pin E31 to pin E32 for those drives that generate their own Drive Ready signal.

#### 3.4.7.2 Disk Drive Write-Precompensation

Stake pins E34 and E35 allow the user two options for the flexible disk drive Write-Precompensation; write precompensation on all drive tracks, or just on tracks greater than 43. The **default configuration** opens pin E34 to pin E35 which causes the WD2797 Flexible Disk Controller to automatically invoke internal Write-Precompensation on tracks greater than 43. This causes EARLY, ON-TIME, and LATE timing delays in the Write Data output from the WD2797 circuit.

#### 3.4.7.3 Media Change Detection and Motor Control Options

Two stake pin pairs, E113/E114 and E117/E118, work in conjunction to allow the user to select one of three valid flexible disk drive media change detection. The **default configuration** jumpers pin E113 to pin E114 and pin E117 to pin E118 which selects Option 1. The three valid options are defined as follows:

Option 1 — This option is used for drives without the Drive Ready signal. A jumper plug must be installed between jumper posts E31 and E33 to supply a ready signal to the flexible disk controller chip. This option can be used with the drives with or without the head load option, but proper Head Load signal is provided to the interface. After four seconds of inactivity, the motor is turned off to protecting the media. Note that flexible disk media changes are not detected with this option.

- Option 2 This option is used for the drives with the limited implementation of the Ready signal, where the Motor-on signal is not a qualifier (i.e. ready = door closed). A jumper plug must be installed between the jumper posts E31 and E32 to pass the Ready signal of the selected flexible disk drive to the flexible disk controller chip. This option can be used with drives with or without the head load/ unload capability, but proper Head Load signal is provided to the interface. Media is protected by turning the motor off after four seconds of inactivity. Media change is detected by the firmware via periodic sampling of the Ready signal. When the iSBC 214 board detects a not ready to ready transition of a flexible disk drive, it recalibrates the drive and sends an interrupt to the host system CPU to report the media change.

- Option 3 This option is used for the drives with the Ready signal and head load/unload capability. A jumper plug must be installed between the jumper posts E31 and E32 to pass the Ready signal of the selected flexible disk drive to the flexible disk controller chip. When this option is used, the Motor-on signal is asserted to the interface all the time and media is protected by unloading the head after three seconds of inactivity. Media change is detected by the firmware via periodic sampling of the Ready signal. When the iSBC 214 board detects a not ready to ready transistion of a flexible disk drive, it recalibrates the drive and sends an interrupt to the host system CPU to report the media change.

| Table 3-6. Flexible Disk Media Change Detection | on Options |

|-------------------------------------------------|------------|

|-------------------------------------------------|------------|

| Option       | E113 | pers<br>E117<br>E118 | Ready<br>Jumpers<br>E31 E32 E33 | Comments                                                                                                                                    |

|--------------|------|----------------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>default | ON   | ON                   | E31-E33                         | For drives without drive ready signal. Media is protected by motor off after 4 seconds of in-<br>activity. No media change detection.       |

| 2            | ON   | OFF                  | E31-E32                         | For the drives with ready = door closed. Me-<br>dia is protected by motor off after 4 seconds<br>of inactivity. Media changes are detected. |

| 3            | OFF  | OFF                  | E31-E32                         | For the drives with Ready signal and head load/unload capability. Media is protected by head unload. Media changes are detected.            |

#### 3.4.8 Winchester Drive Configuration

The following paragraphs describe the stake pins and jumper functions on the controller that pertain to the Winchester disk drives.

#### 3.4.8.1 Read/Write Head Option

A three-way jumper set, stake pins E79, E80, and E81, permits the Winchester Head Select Line 3 (interface connector J1, pin 2) to be selected as a fourth head select line or as a reduced write current control line. The **default configuration** jumpers pin E79 to E81 to support a fourth head select line. This allows interfacing to Winchester drives that have up to sixteen heads. To change the configuration to support the reduced write current control line, the stake pins E79 and E80 must be jumpered together. This configuration allows interfacing to Winchester drives with up to eight heads.

#### NOTE

Jumpered stake pins E79-E80 enables reduced Write Current, E79-E81 enables Head Select (2<sup>3</sup>). For drives with eight or fewer heads that also do not require reduced write current, remove all jumpers.

#### **3.4.8.2** Interface Seek Operations

Stake pins E121 and E122 allow the controller to perform buffered or non-buffered seeks to the Winchester disk drive interface. The **default configuration** jumpers pin E121 to pin E122, enabling buffered seeks. Leave E121 and E122 open to enable non-buffered seeks by the iSBC controller.

#### 3.4.9 QIC-2 Interface Parity Check

A three-way jumper set, E1, E2, and E3, determines if parity checking on the 8-bit parallel QIC-2 tape interface is enabled or disabled. The **default configuration** jumpers pin E2 to pin E3 which disables the parity check. If parity checking is desired, jumper pin E1 to pin E2.

#### 3.4.10 iSBC<sup>®</sup> 214 Controller Hard Reset

A three-way jumper set, stake pins E4, E5, and E6, determines whether the iSBC 214 controller can be hard reset by sending a Reset command to wake-up Port 0. The **default configuration** jumper E4 to E5 disables this feature; the jumper E5 to E6 enables it. Therefore (in the default configuration) the controller can only be hard reset when the MULTIBUS interface signal, INIT, is driven active (low).

#### 3.4.10.1 Time-Out Circuitry

A three-way set, stake pins E11, E12, and E13, determines whether or not the on-board Time-Out circuitry for bus access is enabled. When enabled, the Time-Out signal is active for about 7 milliseconds after the Intel 80186 CPU has initiated a bus cycle without receiving an Acknowledge signal. This causes a non-maskable interrupt (NMI) to the 80186 CPU and subsequently results in a HALT condition for the on-board processor. See Section 2.2.5.4 for additional information. The **default configuration** jumpers pin E12 to pin E13 which enables the Time-Out signal. To disable the Time-Out circuitry, jumper pin E11 to pin E12.

#### 3.4.10.2 iSBC<sup>®</sup> 214 Non-Maskable Interrupt

Stake pins E82 and E83 determine whether several possible error conditions can cause a non-maskable interrupt (NMI) to the controller's on-board CPU. This NMI subsequently results in a HALT condition for the CPU which requires a wake-up from the host system to recover. The **default configuration** jumpers pin E82 to pin E83, which enables all sources of NMI.

| r                    | T                      | . Summary of Avanable Jumpers                  |                      |

|----------------------|------------------------|------------------------------------------------|----------------------|

| Stake<br>Pin         | Jumper or<br>Wire Wrap | Function                                       | Reference<br>Section |

| E1-E2                | Installed              | Enable Tape parity check                       | 3.4.9                |

| *E2-E3               | Installed              | Disable Tape parity check                      | 3.4.9                |

| *E4-E5               | Installed              | Disable Hard Reset                             | 3.4.10               |

| E5-E6                | Installed              | Enable Hard Reset                              | 3.4.10               |

| *E7-E8               | Not Installed          | Reserved-must be open                          | 3.4.7                |

| *E9-E10              | Not Installed          | Reserved-must be open                          | 3.4.7                |

| E11-E12              | Installed              | Disable Time-Out Signal                        | 3.4.10.2             |

| *E12-E13             | Installed              | Enable Time-Out Signal                         | 3.4.10.2             |

| *E15-E16             | Installed              | Reserved                                       |                      |

| *E17-E18             | Installed              | Reserved                                       |                      |

| *E20-E21             | Installed              | Reserved                                       |                      |

| *E22-E23             | Installed              | Reserved                                       |                      |

| E31-E32              | Installed              | Flex. Drive supports own ready signal          | 3.4.7.1              |

| *E31-E33             | Installed              | Flex. Disk Drive Ready Signal                  | 3.4.7.1              |

| *E34-E35             | Not Installed          | Enable Write Precomp                           | 3.4.7                |

| *E36-E37             | Installed              | eserved-must be jumpered                       | 3.4.7                |

| *E37-E39             | Installed              | Reserved-must be jumpered                      | 3.4.7                |

| E43-E44              | Installed              | Wake-up address bit F                          | 3.4.1                |

| E45-E46              | Installed              | Wake-up address bit E                          | 3.4.1                |

| E47-E48              | Installed              | Wake-up address bit D                          | 3.4.1                |

| E49-E50              | Installed<br>Installed | Wake-up address bit C                          | 3.4.1                |

| E51-E52<br>E53-E54   | Installed              | Wake-up address bit B                          | 3.4.1                |

| E55-E56              | Installed              | Wake-up address bit A<br>Wake-up address bit 9 | 3.4.1                |

| *E57-E58             | Installed              | Wake-up address bit 9<br>Wake-up address bit 8 | 3.4.1                |

| E59-E60              | Installed              | Wake-up address bit 7                          | 3.4.1                |

| E61-E62              | Installed              | Wake-up address bit 7                          | 3.4.1                |

| E63-E64              | Installed              | Wake-up address bit 5                          | 3.4.1                |

| E65-E66              | Installed              | Wake-up address bit 4                          | 3.4.1                |

| E67-E68              | Installed              | Wake-up address bit 3                          | 3.4.1                |

| E69-E70              | Installed              | Wake-up address bit 2                          | 3.4.1                |

| E71-E72              | Installed              | Wake-up address bit 1                          | 3.4.1                |

| E73-E74              | Installed              | Wake-up address bit 0                          | 3.4.1                |

| *E75-E76             | Installed              | Select first Megabyte Page                     | 3.4.2                |

| E75-E76              | Not Installed          | Select last Megabyte Page                      | 3.4.2                |

| *E77-E78             | Installed              | 16-bit data bus                                | 3.4.3                |

| E77-E78              | Not Installed          | 8-bit data bus                                 | 3.4.3                |

| E79-E80              | Installed              | 1-8 Wini heads                                 | 3.4.8.1              |

| *E79-E81             | Installed              | 1-16 Wini heads                                | 3.4.8.1              |

| *E82-E83             | Installed              | Enable NMI                                     | 3.4.10.3             |

| E82-E83              | Not Installed          | Disable NMI                                    | 3.4.10.3             |

| *E84-E85             | Installed              | Reserved                                       |                      |

| *E86-E87             | Installed              | Support 27128 EPROMs                           |                      |

| *E89-E90             | Installed              | Reserved                                       |                      |

| *E91-E92<br>*E93-E94 | Installed              | Reserved                                       |                      |

| *E93-E94<br>E95-E96  | Installed<br>Installed | Reserved<br>Serial priority resolution         | 3.4.5.1              |

| *E95-E96             | Not Installed          | Parallel priority resolution                   | 3.4.5.1              |

| *E97-E98             | Installed              | Relinguish bus on ANYRQST                      | 3.4.5                |

| E98-E99              | Installed              | Relinguish bus on CBRQ*                        | 3.4.5                |

| E100-E101            | Installed              | Common bus request I/O                         | 3.4.5                |

| *E101-E102           | Installed              | Relinguish bus after MULTIBUS access           | 3.4.5                |

| *E103-E104           | Installed              | Reserved                                       |                      |

| *E105-E106           | Installed              | Reserved                                       |                      |

| E107-E108            | Not Installed          | Reserved-must be open                          |                      |

| E109-E110            | Not Installed          | Reserved-must be open                          |                      |

| *E111-E112           | Installed              | Reserved                                       |                      |

| *E113-114            | Installed              | Flex. Drive Media Change Select                | 3.4.7.3              |

| *E115-E116           | Installed              | Reserved-must be installed                     | 3.4.7                |

| *E117-E118           | Installed              | Flex drive media change select                 | 3.4.7.3              |

| *E119-E120           | Installed              | Select 16-bit I/O address                      | 3.4.1                |

| E119-E120            | Not Installed          | Select 8-bit I/O address                       | 3.4.1                |

| *E121-E122           | Installed              | Enable Win. buffered seeks                     | 3.4.8.2              |

| E121-E122            | Not Installed          | Enable Win. non-buffered seeks                 | 3.4.8.2              |

|                      |                        |                                                |                      |

| I | able | e 3 | 3-7 | • | Summary | of | A | lvai | la | b | le | Jum | pers |  |

|---|------|-----|-----|---|---------|----|---|------|----|---|----|-----|------|--|

|---|------|-----|-----|---|---------|----|---|------|----|---|----|-----|------|--|

| Stake                                                                                                                                                                       | Jumper or                                                                                                                                                                          | Function                                                                                                                                                                                                                                                                                                        | Reference                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| Pin                                                                                                                                                                         | Wire Wrap                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                 | Section                                                                                                                    |

| E126-E134<br>E126-E133<br>E126-E132<br>E126-E120<br>*E126-E129<br>E126-E128<br>E126-E127<br>*E135-E138<br>*E136-E139<br>*E137-E140<br>*E142-E143<br>E141-E142<br>*E144-E145 | Installed<br>Installed<br>Installed<br>Installed<br>Installed<br>Installed<br>Installed<br>Installed<br>Installed<br>Installed<br>Installed<br>Installed<br>Installed<br>Installed | MULTIBUS Interrupt 0<br>MULTIBUS Interrupt 1<br>MULTIBUS Interrupt 2<br>MULTIBUS Interrupt 3<br>MULTIBUS Interrupt 4<br>MULTIBUS Interrupt 5<br>MULTIBUS Interrupt 6<br>MULTIBUS Interrupt 7<br>Reserved<br>Reserved—must be open<br>Reserved<br>Disable ACLO input<br>Enable ACLO input<br>Pump Filter Circuit | 3.4.4<br>3.4.4<br>3.4.4<br>3.4.4<br>3.4.4<br>3.4.4<br>3.4.4<br>3.4.4<br>3.4.4<br>3.4.4<br>3.4.6<br>3.4.6<br>3.4.6<br>3.4.7 |

| Table 3-7. | Summary | of | Available | Jumners | (Cont'd) |

|------------|---------|----|-----------|---------|----------|

| Table 3-7. | Summary | 01 | Available | Jumpers | (Cont u) |

\*Indicates default configuration

# 4.1 Introduction

This chapter describes the programming conventions necessary to initiate and monitor data transfers between the host system memory and the attached peripheral storage devices (Winchester disk, flexible disk, and streaming tape drives). The iSBC 214 controller firmware emulates the I/O communications protocol of the iSBC 215G disk controller board, the protocols associated with the iSBX 218A Flexible disk controller, and the iSBX 217C tape controller MULTIMODULES mounted on the iSBC 215G board. Hard disk operation of the iSBC 214 board is limited to the ST506/412 compatible Winchester disk drives.

# 4.2 Host/Board Communications

The iSBC 214 board has a DMA controller device that is capable of operating as a bus master for transferring information to and from system memory. However, it cannot operate as the system master (host), and depends upon the system master to provide operation programming. The board responds to any host CPU that provides the necessary operation programming. All mass storage operations are initiated by the output from the host CPU of a command byte to the wake-up port assigned to the iSBC 214 board. Once the operation is initiated by the host CPU, all subsequent communication between the host CPU and the board, until the operation is complete, take place using the I/O communications blocks established in memory by the host CPU prior to initiating the mass-storage operation.

The I/O communication block structure for the board, exclusive of any data buffer, consists of 68 bytes of memory that are arranged into 4 blocks. The format of each of the 4 blocks is specifically defined. However, the blocks can be arranged in any order or in any location within a 1-Mbyte page of memory (dedicated memory locations excluded). Each of the blocks has a defined format, and the memory bytes that make up each block must be contiguous. Each of the blocks also has a defined function related to the overall operation of the iSBC 214 board.

The most important advantage of such a communications block structure is flexibility. Though some of the blocks should be limited in use to only one such block in memory, the system may contain multiple copies of blocks used directly to specify operations. Thus, by merely changing a few pointers, software can specify a different storage operation without structuring an all-new I/O block.

#### 4.2.1 Wake-Up I/O Port

The wake-up port is the I/O address to which the iSBC 214 board responds. The I/O address is user selectable through jumpers on the board and may be either 8 or 16 bits, depending on the host CPU and the applications. The command signal that controls the number of bits in the address to which the board will respond is also jumper selectable.

#### NOTE

The jumpers that select the I/O port address (shifted to the left four places) also select the address of the first byte in the wake-up block. Thus wake-up I/O port address 100H also specifies wake-up block address 1000H. (Refer to section 3.4.2 for more information.)

To invoke iSBC 214 board activity, the host CPU transmits a wakeup command byte to the board through the wake-up I/O port. Three wake-up commands are allowed, as shown in Table 4-1. Note that only the two least significant bits of the command are used to determine which of the three hardware functions to implement. Note that only Multibus I/O write operations are recognized.

#### NOTE

Important timing restrictions exist on the commands listed in Table 4-1 during Cold Start. Refer to section 4.2.7 in for details.

| Command | Function                                                                                                                                                                                                                                                                     |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00H     | CLEAR INTERRUPT—The I/O port to host CPU interrupt is reset, the channel reset is cleared.                                                                                                                                                                                   |

| 01H     | <b>START OPERATION</b> —Instructs the board to start the operation defined by the communication block element.                                                                                                                                                               |

| 02H     | <b>RESET BOARD</b> —Instructions to perform a software reset of the controller board.<br>A Clear Interrupt command must be initiated following this command. Each time the controller is reset, the communication link between the board and the host must be reestablished. |

| 03-FFH  | Reserved                                                                                                                                                                                                                                                                     |

| Table 4-1. I/ | 'O Channe | el Commands |

|---------------|-----------|-------------|

|---------------|-----------|-------------|

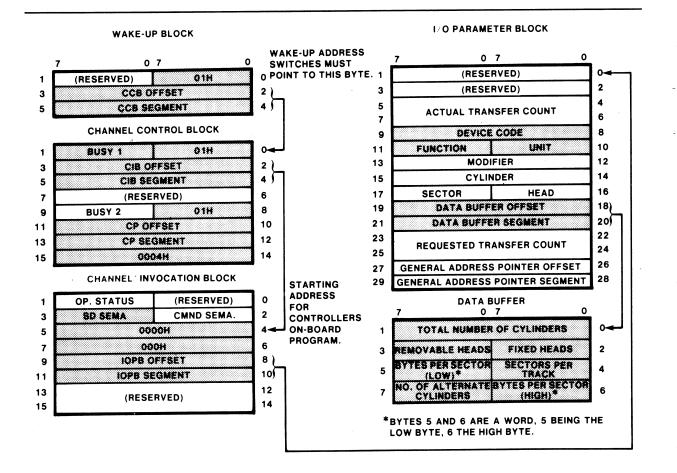

#### 4.2.2 I/O Communications Block

The host CPU and the iSBC 214 board use the four blocks of system memory and one Multibus I/O port to exchange instructions and status. The I/O communications blocks are called the wake-up block, channel control block, controller

invocation block, and I/O parameter block. The iSBC 214 board uses these blocks to perform three basic functions: initialize the board, check and transmit status, and obtain user-selected drive access functions and parameters. In addition to these I/O blocks, certain board functions (such as track formatting) also require data/ parameter buffers in system memory. Dedicated locations, however, are not required.

#### NOTE

Following the iSBC 214 board initialization, the wake-up block, channel control block, and controller invocation block must remain at the assigned locations. The location of the I/O parameter block can be changed only if the I/O parameter block pointer in the controller invocation block is changed to indicate the new location.

One I/O port in the host CPU addressable (Multibus) I/O space is also required. The host CPU uses this port, called the wake-up I/O port, to initiate iSBC 214 board activity. The sequence (see Figure 4-2) in which the board accesses these blocks varies with the type of operation being performed. For a general data read function, the blocks are accessed as follows:

- 1. The host loads the control and data blocks, as required, in system memory with the command and parameters for the function the iSBC 214 board is to perform (for example, read-data).

- 2. The host then transmits a wake-up command (01H) to the wakeup I/O port, signalling the board to read the I/O communication blocks for instructions.

- 3. The board reads the wake-up block and links its way to the channel control block, through the controller invocation block, to the I/O parameter block. (The wake-up block is used once during board initialization. All subsequent wake-up commands cause the iSBC 214 board to read the channel control block.)

- 4. At the I/O parameter block, the iSBC 214 board reads the command and parameter data into local RAM and begins the data transfer function.

- 5. The board reads data from the selected drive into local RAM, then DMAtransfers the data from RAM into system memory.

- 6. When the data transfer is complete, the board posts the status in the controller invocation block, sends an interrupt to the host CPU, and awaits further instructions.

These I/O communication blocks are accessed in a similar manner when performing a write function.

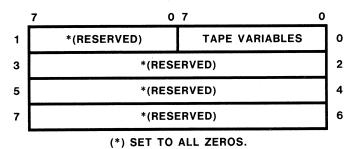

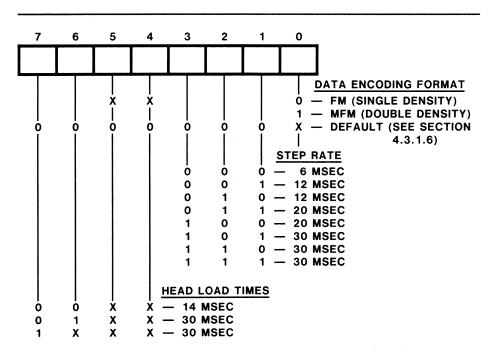

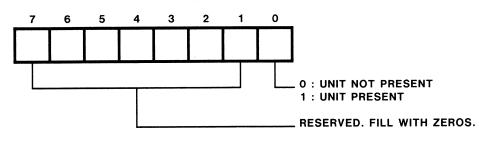

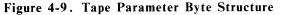

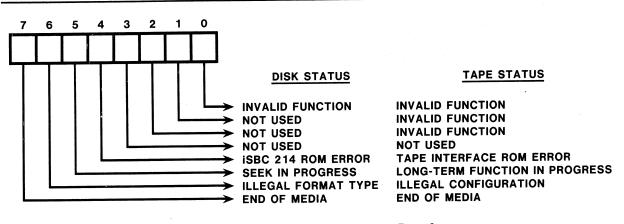

The host CPU initiates board activity through the wake-up I/O port, addressed through the Multibus interface. Once the host has initiated board activity, the 80186 Processor handles all communications between the host CPU, host memory, and disk drive controllers. Board operations software is contained in on-board PROM. Local RAM on the board facilitates intermediate data storage between the host CPU and the disk drive.