#### **Functions Reference Manual**

File Number S36-37

Order Number SA21-9436-5

Sixth Edition (June 1987)

This major revision makes obsolete SA21-9436-4.

References in this publication to IBM products, programs, or services do not imply that IBM intends to make these available in all countries in which IBM operates. Any reference to an IBM licensed program in this publication is not intended to state or imply that only IBM's licensed program may be used. Any functionally equivalent program may be used instead.

Publications are not stocked at the address given below. Requests for IBM publications should be made to your IBM representative or to the IBM branch office serving your locality.

This publication could contain technical inaccuracies or typographical errors. A form for readers' comments is provided at the back of this publication. If the form has been removed, comments may be addressed to IBM Corporation, Information Development, Department 245, Rochester, Minnesota, U.S.A. 55901. IBM may use or distribute whatever information you supply in any way it believes appropriate without incurring any obligation to you.

© Copyright International Business Machines Corporation 1985, 1986, 1987

#### Contents

**About This Manual** xix Who should use this manual ... xix What you should know .... xix If you need more information .... XX How this manual has changed in this edition .... XX **Abbreviations and Acronyms** xxiii Chapter 1. What These Systems Are 1-1 Parts of the System 1-6 Main Storage Processors, Control Storage Processors, and Data Storage Controllers 1-6 **Display Stations** 1-6 Printers 1-9 Disk Storage 1-11 Diskette Drive 1-11 8809 Tape Drive 1-12 6157 Tape Drive 1-12 Magnetic Character Reader 1-12 Data Communications Features 1-12 Data Formats 1-14 Alphanumeric Character Format 1-14 Ideographic Character Format 1-14 **Display Fields** 1-19 **Binary Format (Logical Data)** 1-19 Hexadecimal Digits 1-19 Parity 1-20 Addressing 1-20 Direct Addressing 1-22 **Base Displacement Addressing** 1-22 Instruction Formats 1-23 **Command Instructions** 1-23 **One-Address Instructions** 1-23 Two-Address Instructions 1-24 Modes of System Operation 1-26 Cycle Steal Mode 1-26 Interrupt Mode 1-26 Process Mode 1-26 Instruction Registers 1-26 Instruction Address Register (IAR) 1-26 Address Recall Register (ARR) 1-26 Index Registers 1 and 2 (XR1 and XR2) 1-27 **Op Register** 1-27 Q Register 1-27

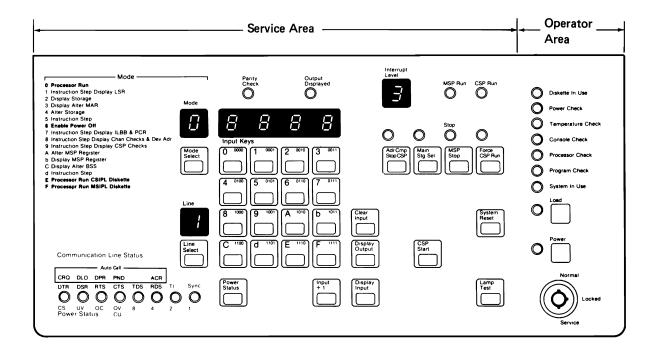

Work Registers 1-27 Program Status Register (PSR) 1-27 Prefix Address Contained Translation Registers (PACT) 1-28 Program Mode Register (PMR) 1-29 Control Mode Register (CMR) 1-30 Address Translation Registers (ATRs) 1-30 Configuration Control Register (CCR) 1-30 Memory Configuration Register (MCR) 1-31 Address Compare Register (ACR) 1-32 Input Output Blocks (IOBs) 1-32 General Input/Output Operations 1-32 Chapter 2. System Control Panel and Unit Emergency Switch 2-1 5360 System Unit Control Panel and Unit Emergency Switch 2-1 Operator Area of the 5360 System Unit Control Panel 2-2 Security Switch 2-2 Power Key 2-2 Power Light 2-3 Load Key and Load Light 2-3 Diskette in Use Light 2 - 3Power Check Light 2-3 **Temperature Check Light** 2-3 Console Check Light 2-3 Processor Check Light 2-4Program Check Light 2-4 System in Use Light 2-45360 System Unit Emergency Switch 2-4 Service Area of the 5360 System Unit Control Panel 2-4CSP Start Key and CSP Run Light 2-5 MSP Run Light 2-5 MSP Stop Key 2-5 MSP Stop Light 2-5 Input Keys 2-5 Mode Select Key and Mode display 2-6 Line Select Key and Line Display 2-6 **Power Status Key and Indicators** 2-6 Hexadecimal Display 2-7 Display Output Key and Output Displayed Light 2-7 Display Input Key 2-7 Input +1 Key 2-7 Clear Input Key 2-7 Parity Check Light 2-7 Interrupt Level Display 2-7 Adr Cmp Stop CSP Key and Light 2-8 Main Stg Sel Key and Light 2-8 Force CSP Run Key and Light 2-8 System Reset Key 2-8 Lamp Test Key 2-9 5362 System Unit Control Panel and Unit Emergency Switch 2-9 Operator Area of the 5362 System Unit Control Panel 2-10 Security Switch 2-10 Power On Key 2-10 Power On Light 2-11 Diskette in Use Light 2-11

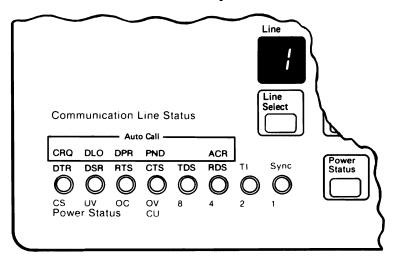

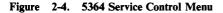

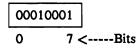

Temperature Light 2-11 Voltage Light 2-11 Current Light 2-11 Console Light 2-11 Program Light 2-11 Processor Light 2-12 5362 System Unit Emergency Switch 2-12 Service Area of the 5362 System Unit Control Panel 2-12 Input Keys 2-12 Select Function Key and Function Display 2-13 Output Display (Hexadecimal) 2-14 Output Display Key and Output Display Light 2-14 5364 System Unit Control Panel 2-14 Operator Area of the 5364 System Unit 2-15 5364 Service Control Menu Screen 2-15 **Chapter 3. Machine Instructions** 3-1 Add Logical Characters (ALC) 3-4 Operation 3-4 Program Note 3-4 Resulting Program Status Byte Settings 3-5 Example 3-6 Add Logical Immediate (ALI) 3-7 Operation 3-7 Program Notes 3-7 **Resulting Program Status Byte Settings** 3-8 Example 3-8 3-9 Add to Register (A) Operation 3-10 Program Notes 3-11 **Resulting Program Status Byte Settings** 3-11 Example 3-12 Add Zoned Decimal (AZ) 3-13 Operation 3-13 Program Notes 3-14 **Resulting Program Status Byte Setting** 3-14 Example 3-15 Branch On Condition (BC) 3-16 Operation 3-16 Program Notes 3-17 **Resulting Program Status Byte Setting** 3-18 Example 3-18 Compare Logical Characters (CLC) 3-19 Operation 3-19 Program Note 3-19 **Resulting Program Status Byte Setting** 3-20 Example 3-20 Compare Logical Immediate (CLI) 3-21 Operation 3-21 Program Note 3-21 Resulting Program Status Byte Setting 3-21 Example 3-21 Edit (ED) 3-23 Operation 3-23 Program Note 3-24

**Resulting Program Status Byte Settings** 3-24 3-25 Example Insert and Test Characters (ITC) 3-26 Operation 3-26 Program Notes 3-27 **Resulting Program Status Byte Settings** 3-27 Example 3-27 Jump On Condition (JC) 3-28 Operation 3-28 Program Notes 3-29 **Resulting Program Status Byte Setting** 3-30 Example 3-30 Load Address (LA) 3-31 Operation 3-31 Program Notes 3-33 **Resulting Program Status Byte Setting** 3-33 Example 3-33 Load Program Mode Register (LPMR) 3-34 Operation 3-34 **Resulting Program Status Byte Setting** 3-35 Load Register (L) 3-35 Operation 3-36 Program Notes 3-36 **Resulting Program Status Byte Setting** 3-37 Example 3-37 Move Characters (MVC) 3-38 Operation 3-38 Program Note 3-38 **Resulting Program Status Byte Setting** 3-39 Example 3-39 Move Hexadecimal Character (MVX) 3-40 Operation 3-40 3-41 Program Notes **Resulting Program Status Byte Setting** 3-41 Example 3-41 Move Logical Immediate (MVI) 3-42 Operation 3-42 Resulting Program Status Byte Setting 3-42 Example 3-42 Set Bits Off Masked (SBF) 3-43 Operation 3-43 **Resulting Program Status Byte Setting** 3-43 Example 3-43 Set Bits On Masked (SBN) 3-44 Operation 3-44 **Resulting Program Status Byte Setting** 3-44 Example 3-44 Shift Right Character (SRC) 3-45 Operation 3-45 **Resulting Program Status Byte Settings** 3-45 Example 3-46 Store Register (ST) 3-46 Operation 3-47 Program Notes 3-48

**Resulting Program Status Byte Setting** 3-48 Example 3-48 Subtract from Register (S) 3-48 Operation 3-49 3-49 Program Notes **Resulting Program Status Byte Settings** 3-50 Example 3-50 Subtract Logical Characters (SLC) 3-51 Operation 3-51 Program Note 3-52 **Resulting Program Status Byte Settings** 3-52 Example 3-53 Subtract Logical Immediate (SLI) 3-54 Operation 3-54 **Resulting Program Status Byte Settings** 3-54 Example 3-54 Subtract Zoned Decimal (SZ) 3-56 Operation 3-56 Program Notes 3-56 **Resulting Program Status Byte Setting** 3-57 Example 3-58 Test Bits Off Masked (TBF) 3-59 Operation 3-59 Program Notes 3-59 **Resulting Program Status Byte Setting** 3-60 Example 3-60 Test Bits On Masked (TBN) 3-61 Operation 3-61 Program Notes 3-61 Resulting Program Status Byte Setting 3-62 Example 3-62 Transfer (XFER) 3-63 Operation 3-63 **Program Notes** 3-63 **Resulting Program Status Byte Setting** 3-64 Zero and Add Zoned (ZAZ) 3-64 **Operation parameters** 3-65 **Program Notes** 3-65 **Resulting Program Status Byte Setting** 3-65 Example 3-66 Supervisor Call (SVC) 3-67 General Wait 3-68 **Input Parameters** 3-69 Example 3-69 **General Post** 3-70 Input Parameters 3-70 Example 3-71 Event Wait 3-71 **Input Parameters** 3-72 Output Values 3-72 Example 3-73 Event Post 3-73 Input Parameters 3-74 Example 3-74 Transfer Control by ID 3-75

Transfer Table Entry 3-75 Input parameters 3-76 Example 3-76 Free Second Request Block 3-77 Input Parameters 3-77 Output Values 3-77 Example 3-77 Assign 3-78 Input Parameters 3-79 Output Values 3-79 Example 3-79 Free Assigned Areas 3-80 **Input Parameters** 3-80 Example 3-81 **Increment System Event Counters** 3-81 **Input Parameters** 3-81 3-81 **Inline Parameters** Example 3-81 Sense Data Switches 3-82 Output Parameters 3-82 Example 3-82 Set Task Privileged 3-82 **Input Parameters** 3-82 Example 3-83 Post Action Controller Status Word 3-83 **Input Parameters** 3-83 Example 3-83 Fast Transfer 3-84 **Input Parameters** 3-84 Example 3-85 Fast Exit 3-85 3-85 **Input Parameters** Example 3-86 Queue/Dequeue 3-86 **Input Parameters** 3-87 Example 3-87 System Control Block Access 3-88 **Input Parameters** 3-88 **Output Parameters** 3-89 Example 3-89 Transfer Control by Address 3-90 Input parameters 3-91 Example 3-91 Main Storage Exit 3-92 **Input Parameters** 3-92 Example 3-92 Get Page 3-93 3-93 **Input Parameters Output Parameters** 3-93 Example 3-93 Maintain User Area Pages 3-94 Input Parameters 3-94 **Output Parameters** 3-95 Example 3-95

Asynchronous Task Wait 3-95 **Input Parameters** 3-96 **Output Parameters** 3-96 3-96 Example Set Transient Area Not Busy 3-97 **Input Parameters** 3-97 Example 3-97 Post Action Control Element 3-97 **Input Parameters** 3-98 Example 3-98 Log Trace Information 3-99 **Input Parameters** 3-99 Example 3-100 Scan System Queue 3-100 **Input Parameters** 3-100 **Output Parameters** 3-101 Example 3-101 Task Post 3-101 **Input Parameters** 3-102 Example 3-102 Task Wait 3-102 **Input Parameters** 3-103 Example 3-103 Specific Resource Dequeue 3-103 **Input Parameters** 3-104 Example 3-104 Resource Enqueue/Dequeue 3-105 **Input Parameters** 3-107 Example 3-108 Dump Task/Terminate Task 3-109 **Input Parameters** 3-109 Example 3-109 Test and Set 3-110 **Input Parameters** 3-110 3-111 Output Values Example 3-111 Task Block Priority Queue 3-111 Input Parameters 3-111 Example 3-112 Asynchronous Task Ready Check 3-112 **Input Parameters** 3-113 Example 3-113 Prepare Print Buffer (Not Ideographic) 3-113 **Input Parameters** 3-114 Example 3-114 Prepare Print Buffer (Ideographic) 3-115 **Input Parameters** 3-116 Example 3-116 Post Task by Task ID 3-117 **Input Parameters** 3-118 Example 3-118 Translated Assign 3-119 **Input Parameters** 3-120 **Output Parameters** 3-120 Example 3-121

Translated Free 3-121 **Input Parameters** 3-122 Example 3-122 Time of Day 3-123 **Input Parameters** 3-123 Example: 3-123 MAP 3-123 **Input Parameters** 3-124 **Output Registers** 3-124 Example 3-125 Parameter List 3-125 QLOCK 3-125 **Input Parameters** 3-125 Example 3-125 ATASK 3-126 **Input Parameters** 3-126 **Output Registers** 3-126 Example 3-126 DTASK 3-127 **Input Parameters** 3-127 Example 3-127 TWAL 3-128 **Input Parameters** 3-128 **Output Registers** 3-128 Example 3-128 3-129 DTWAL **Input Parameters** 3-129 Example 3-129 WRK 3-130 **Input Parameters** 3-130 **Output Registers** 3-131 Example 3-131 Parameter List 3-131 SMFC 3-132 **Input Parameters** 3-132 Fixed Disk IOS 3-132 **Input Parameters** 3-133 **Diskette IOS** 3-133 **Input Parameters** 3-134 Work Station/Printer IOCH 3-134 Input Parameters 3-135 Work Station IOCH 3-135 **Input Parameters** 3-135 Data Communications IOCH 3-136 **Input Parameters** 3-136 Local Area Network IOCH 3-137 **Input Parameters** 3-137 Diskette Data Compression 3-138 **Input Parameters** 3-138 Tape IOS 3-138.1 **Input Parameters** 3-138.1 1255 Magnetic Character Reader IOS 3-139 **Input Parameters** 3-139 DSC I/O 3-140

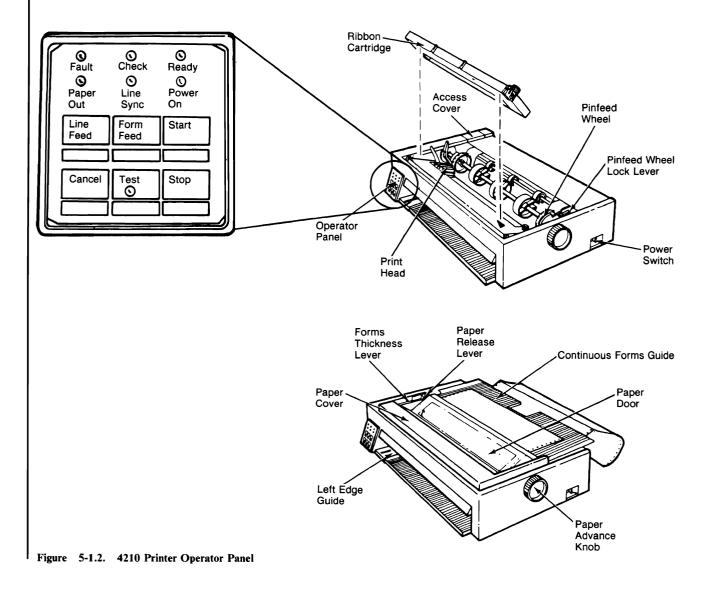

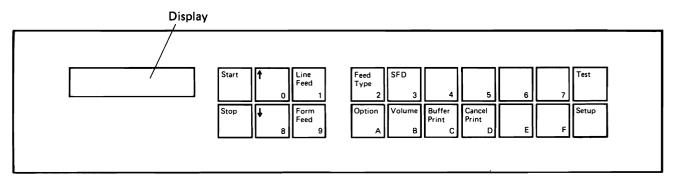

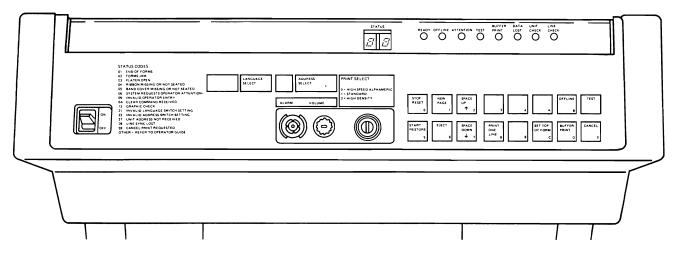

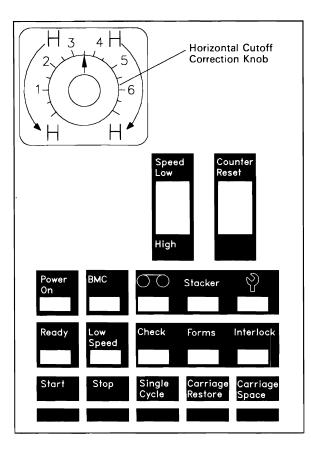

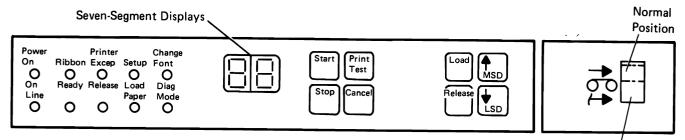

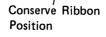

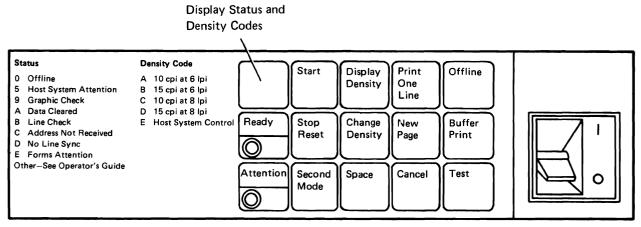

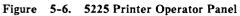

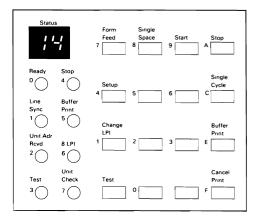

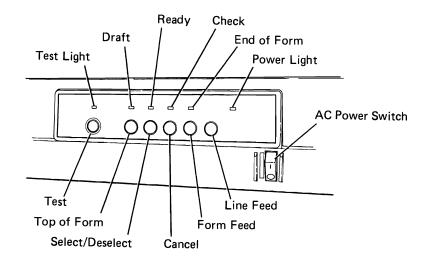

**Input Parameters** 3-140 Action Control Element Build and Queue 3-141 Input Parameters 3-141 **Output Values** 3-142 Control Storage Transient Scheduler 3-142 Input Parameters 3-142 Example 3-143 Task Work Area Accesses 3-143 3-143 **Input Parameters** Example 3-144 Main Storage Relocating Loader 3-145 **Input Parameters** 3-145 Example 3-146 **Chapter 4. Programming Considerations** 4-1 Conditioning the Program Status Registers 4-1 **Chapter 5.** Printers 5-1 Printers Used 5-1 **Physical Characteristics** 5-2 3262 Printer (5360 System Unit Only) 5-2 3812 Printer 5-3 4210 Printer 5-3 4214 Printer 5-4.1 4224 Printer 5-4.2 4234 Printer 5-5 4245 Printer 5-6 5219 Printer 5-7 5224 and 5225 Printers 5-8 5224 Model 12 and 5225 Model 11 and 12 (Ideographic) 5-9 5256 Printer 5-10 5262 Printer 5-11 5553 or 5557 Printer 5-11 Printer Switches, Keys, and Lights 5-12 3262 Switches, Keys, and Lights 5-12 3812 Printer Switches, Keys, and Display 5-14 4210 Operator Panel 5-16.3 4210 Operator Panel Lights 5-16.4 4214 Printer Switches, Keys, and Display 5-16.8 4224 Printer Switches, Keys, and Lights 5-21 4234 Printer Switches, Keys, and Lights 5-23 4245 Printer Switches, Keys, and Lights 5-26 5219 Printer Switches, Keys, and Lights 5-34 5224 Printer Switches, Keys, and Lights 5-36 5225 Printer Switches, Keys, and Lights 5-37 5256 Printer Switches, Keys, and Lights 5-39 5262 Printer Switches, Keys, and Lights 5-41 5553 or 5557 Operator Panel Switches and Keys 5-44 **Programming Characteristics of Printers** 5-46 Programming Characteristics of Local and Remote Printers 5-46 Printer Unit Block 5-50 Printer Input/Output Block 5-50 Commands 5-50 Work Station Controller Commands 5-51 Printer Commands 5-51

ł

L

I

Printer IPDS Output Data Stream Commands 5-53 Printer Output SCS Data Stream Commands 5-53 Load Alternate Character Example 5-100 Printer Status Bytes and Error Recovery Procedures 5-101 3262 Status Bytes 5-103 3262 Printer Error Recovery 5-106 Chapter 6. Displays 6-1 Physical Characteristics of the Display Stations 6-2.2. Physical Characteristics of the 3179 Model 2, 3180-2, 3196, 5251, 5291, and **5292 Display Stations** 6-2.2 Physical Characteristics of the 5555 Display (Ideographic Only) 6-4 Operating Characteristics of the Display Stations 6-6.1 **Display Station Modes** 6-6.1 **Operator Aids** 6-13 Auto Shift (Ideographic Only) 6-16 Keyboards for 5555 Display 6-16 **Keyboard Key Functions** 6-18 Programming Characteristics of Display Stations 6-60 Programming Characteristics of Local Display Stations 6-60 Display Station Input/Output Block 6-63 Commands and Orders 6-63 Work Station Controller Commands 6-64 Display Commands 6-64 Commands for Word Processing 6-67 Display Station Output Data Stream Commands 6-74 Format Table 6-82 Input Fields 6-96 Write Data (Hex 11) 6-99 **Display Station Data Stream Orders** 6-101 Display Station Status Bytes and Error Recovery 6-132 Display Station Features 6-133 Magnetic Stripe Reader 6-133 Multinational Character Set 6-134 3270 Emulation Feature 6-134 Work Station Expansion Feature 6-135 Cluster Feature 6-135 Text Entry Assist Feature 6-135 **Extended Input Fields Feature** 6-135 Chapter 7. 10SR Disk Drive 7-1 Disk Surface 7-2 Disk Operating Procedures 7-5 Initial Program Load (IPL) 7-5 **Disk Operations** 7-5 Starting a Disk Operation 7-6 Disk Addressing 7-6 Time Needed for a Disk Operation 7-8 **Read Operations** 7-9 7-11 Write Operations Check Conditions and Status Bytes 7-11 Status Byte 0 7-12 7-12 Status Byte 1 7-12 Status Byte 2

Status Byte 3 7-14 Status Byte 4 7-15 7-15 Status Byte 5 Error Recovery 7-16 Error Recovery by the Input/Output Supervisor Program 7-18 Alternative Sector Assignment 7-18 7-19 Alternative Sector Processing Chapter 8. 21ED Disk Drive 8-1 Disk Surface 8-2 **Disk Operating Procedures** 8-5 Initial Program Load (IPL) 8-5 **Disk Operations** 8-6 Starting a Disk Operation 8-6 Disk Addressing 8-6 Time Needed for a Disk Operation 8-8 **Read Operations** 8-9 Write Operations 8-11 Check Conditions and Status 8-12 Status Byte 0 8-12 Status Byte 1 8-13 Status Byte 2 8-14 Status Byte 3 8-15 Status Byte 4 8-16 Status Byte 5 8-17 Error Recovery 8-18 Error Recovery by the Input/Output Supervisor Program 8-20 Alternative Sector Assignment 8-20 8-21 Alternative Sector Processing Chapter 9. 0665 Disk Drive 9-1 Disk Surface 9-2 **Disk Operating Procedures** 9-3 9-3 Initial Program Load (IPL) **Disk Operations** 9-3 Starting a Disk Operation 9-3 Disk Addressing 9-3 Time Needed for a Disk Operation 9-4 **Read Operations** 9-5 Write Operations 9-7 **Check Conditions and Status Bytes** 9-8 Status Byte 0 9-8 Status Byte 1 9-9 Status Byte 2 9-10 Error Recovery 9-11 Error Recovery by the Input/Output Supervisor Program 9-12 Alternative Sector Assignment 9-13 Chapter 10. Diskette 10-1 **Diskette Physical Characteristics** 10-1 Diskette Surface 10-2 Sector Format 10-4 Initialize the Diskette 10-5 Autoloader 10-5 Carriage Bed 10-6

Picker Mechanism 10-6 Autoloader Control Operations 10-6 Select Diskette 10-6 10-6 Eject Diskette Orient Autoloader 10-6 Abort/Orient Autoloader 10-7 **Diskette Operations** 10-7 Starting a Diskette Operation 10-7 Diskette Addressing 10-7 Diskette Seek Mechanism 10-9 **Read Operations** 10-9 Write Operations 10-10 Check Conditions and Status Information (5360 System Unit) 10-10 Status Byte 0 (5360 System Unit) 10-11 Status Byte 1 (5360 System Unit) 10-13 Status Byte 2 (5360 System Unit) 10-14 Status Byte 3 (5360 System Unit) 10-14 Status Byte 4 (5360 System Unit) 10-15 Status Byte 5 (5360 System Unit) 10-16 Status Byte 6 (5360 System Unit) 10-16 Status Byte 7 (5360 System Unit) 10-17 Recovery Actions (5360 System Unit) 10-19 Check Conditions and Status Information (5362 and 5364 System Unit) 10-21 Status Byte 0 (Status Byte 6, Bit 0 Off), 5362 and 5364 System Unit 10-21 Status Byte 0 (Status Byte 6, Bit 0 On) (5362 and 5364 System Unit) 10-22 Status Byte 1 (5362 System Unit) 10-23 Status Byte 2 (5362 System Unit) 10-24 Status Byte 3 (5362 System Unit) 10-25 Status Byte 4 (5362 System Unit) 10-25 Status Byte 5 (5362 System Unit) 10-26 Status Byte 6 (5362 System Unit) 10-27 Recovery Actions (5362 System Unit) 10-28 Error Recovery 10-29 Initial Program Load (IPL) 10-30 **Chapter 11. Work Station Attachments** 11-1 Local Work Stations 11-1 **Remote Work Stations and Controllers** 11-2 Local Area Network Work Stations 11-2.1 **Programming Characteristics of Work Stations** 11-3 General Information 11-3 **Programming Characteristics of Work Stations** 11-4 Work Station Input/Output Block 11-7 Commands 11-7 Invite (Hex FF) 11-7 Read Current Configuration (Hex 82) 11-8 Configure New Work Stations (Hex 81) 11-12 Get Printer Status (Hex 47) 11-13 Clear Printer (Hex 40) 11-13 Output Data (Hex 27) 11-14 Work Station Status Bytes and Error Recovery 11-14 11-15 Status Byte 0 Status Byte 1 11-16 Status Bytes 2, 3, and 4 11-17

Status Bytes 5 and 6 11-18 Status Byte 7 11-24 Status Byte 8 (5360 System Unit) 11-25 11-25 Status Byte 8 (5362 System Unit) Status Byte 9 11-26 Status Bytes 10 and 11 11-26 Status Byte 12 11-33 Status Byte 13 11-33 Status Bytes 14 and 15 11-33 Chapter 12. Data Communications 12-1 Local Area Network Attachment 12-3 LAN Attachment Data Rates 12-4 Standard Functions with Communications 12-4 Features 12-5 Options 12-6 **Communications Features** 12-6 **EIA/CCITT** Adapter 12-6 Internal Clock 12-6 1200 BPS Integrated Modem Adapter (38LS) 12-7 Digital Data Service Adapter 12-7 X.21 Adapter 12-8 V.35 Adapter (MLCA or ELCA Only) 12-8 **Programming Considerations** 12-8 Microcode Load Buffer 12-9 Communications Input/Output Block (IOB) 12-9 Data Buffer 12-15 12-15 Poll List Autocall Phone List 12-15 X.21 Call List 12-15 Error Recovery Block 12-16 **Extended Configuration Record** 12-16 Asynchronous Communications (ASYNC) 12-16 Binary Synchronous Communications (BSC) 12-18 Transmission Codes 12-18 **BSC** Features 12-18.1 BSC Input/Output Block 12-18.1 Posting IOBs Complete, BSC 12-23 Framing the BSC Message 12-23 **BSC** Operations 12-24 Start 2-Second Time-Out Operation (8004) 12-24 Disable Operation (8080) 12-25 Enable Operation (80C0) 12-25 Enable without Load (80D0) 12-26 Receive Operation (8100) 12-27 Receive Initial Delayed Operation: Multipoint Only (8200) 12-28 Receive Initial Operation (8300) 12-28 Transmit and Receive Overlay Operation (8400) 12-31 Transmit and Receive Initial Monitor Operation (8500) 12-31 Transmit and Receive Initial Control Operation (8501) 12-31 Transmit and Receive Operation (8600) 12-31 Transmit Initial and Receive Operation (8680) 12-34 Enable Automonitor Operation: Multipoint Tributary Station (8800) 12-34 **BSC** Data Buffer 12-37 Characters in Buffer 12-41

Control Characters in Buffer 12-41 Time-Outs 12-43 **Programming Notes** 12-44 Data Mode 12-44 Transmit Final 12-44 **ITB** Operation 12-44 Transparent Mode 12-44 Disconnect Operation 12-45 Station Address 12-45 **Receive Operation** 12-45 Synchronous Data Link Control (SDLC) 12-45 Initialization/Termination 12-45 SDLC Input/Output Block 12-46 Queue Processing by the Communications Attachment 12-53 SDLC Data Buffer 12-55 **SDLC** Operations 12-59 Disable Operation (8080) 12-59 Enable Operation (80C0) 12-59 Reenable Operation (80D0) 12-60 Transmit Poll/Final Bit (P/F Bit) On (82x0) 12-60 Receive Initial Operation: Secondary Station Only (8300) 12-61 Receive Initial-X.21 Calling: MLCA or ELCA Only (8380) 12-62 Transmit Final Operation (84x0) 12-62 Transmit Only Operation (85x0) 12-62 Transmit Initial Operation: Primary Station Only (86x0) 12-63 Receive Delayed Operation (8700) 12-63 Start Autopoll (RR) Operation (8800) 12-64 Start Autoresponse Operation (8800) 12-65 Start Autopoll (RNR) Operation (8900) 12-65 DSR Wait Primary Station (8E00) 12-66 Stop Autopoll Operation: Primary Station (8F00) 12-66 Stop Autoresponse Operation: Secondary Station (8F00) 12-67 Station Address 12-68 **SDLC Status Bytes** 12-68 Zero Bit Insertion/Deletion 12-68 NRZI Transmission Coding 12-69 SDLC Error Recording 12-69 SDLC Poll List 12-70 Timer Controls 12-73 System Measurement Facility (SMF) Support 12-75 Autoresponse Mode (Secondary) 12-76 Autocall (MLCA or ELCA Only) 12-77 Autocall IOB 12-78 Autocall Number List (MLCA or ELCA Only) 12-79 Autocall Time-Outs (MLCA or ELCA Only) 12-80 Autocall Commands 12-81 Dial Command (8C00) 12-82 X.21 Adapter Feature 12-82 X.21 Description 12-82 **X.21 IOB** 12-83 12-85 X.21 Call List X.21 Call Progress Signals 12-86 X.21 Time-Outs 12-88 X.21 Commands 12-90

X.21 Answer Function (SDLC/BSC Interface) 12-92 Communications Line Wrap Test 12-93 MLCA Controller Wrap (MLCA or ELCA only) 12-95 X.25 12-98 X.25 Description 12-98 Microcode Overview 12-98 Data Areas 12-101 Logical Channel Reference 12-101 Queues 12-101 **Receive Data Flow** 12-102 Transmit Data Flow 12-103 **Program Instructions** 12-104 CSP Microcode Interface 12-104 X.25 Operations 12-117 3270 Remote Attachment 12-131 Local Area Network (LAN) Attachment Feature 12-132 LAN Input/Output Block 12-133 Data Flows with the 5360 and 5362 System Units 12-136 Data Flows with the 5364 System Unit 12-136 Session Activation 12-137 LAN Operations 12-147 Enable Operation 12-147 **Open Station Operation** 12-148 LAN Status Bytes and Error Reporting 12-149 Ring Error Monitor 12-149 **Ring Error Monitor Interfaces** 12-149 Chapter 13. 8809 Tape Drive 13-1 Physical Characteristics 13-1 Tape Unit Pushbuttons and Indicators 13-1 **Operator Panel Pushbuttons** 13-2 **Operator Panel Indicators** 13-2 Operations 13-3 **Data Operations** 13-3 Non-Data Operations 13-3 Disconnected Operations 13-3 Set Speed Operations 13-4 Gap Length Operation 13-4 **Reset** Operation 13-4 Status Bytes 13-5 Status Byte 0 13-5 Status Byte 1 13-6 Status Byte 2 13-7 Status Byte 3 13-8 Status Byte 4 13-9 Status Byte 5 13-9 Status Byte 6 13-10 Status Byte 7 13-10 Status Byte 8 13-12 Status Byte 9 13-13 Status Byte 10 13-14 Status Byte 11 13-15 Status Byte 12 13-16 Status Byte 13 13-17 Status Byte 14 13-17

T

1

Status Byte 15 13-18 Error Recovery 13-18 Chapter 14. 1255 Magnetic Character Reader 14-1 DTF 14-2 IOB 14-4 Chapter 15. 6157 Tape Drive 15-1 Physical Characteristics 15-2 6157 Tape Unit Operator Controls 15-3 Operations 15-4 Power On/Reset Operation 15-4 **Data Operations** 15-4 Non-Data Operations 15-4 Status Operations 15-5 Error Logging by the Host System 15-5 Error Recovery 15-5 Chapter 16. 9332 Disk Drive 16-1 9332 Disk Drive Operator Controls 16-2 Power On/Off Switch 16-2 Power Ready LED 16-2 Unit Ready LED 16-2 **Disk Operations** 16-3 16-3 Starting a Disk Operation Time Needed for a Disk Operation 16-3 Start Input/Output Operations 16-4 **Read Operations** 16-4 Write Operations 16-7 **Check Conditions and Status** 16-8 Status Byte 0 16-8 Status Byte 1 16-9 Sense Byte Summary 16-9 Handle Status Function 16-10 Error Recovery 16-10 Logging and Reporting of Errors 16-11 Media Errors 16-12 **Appendix A. Instruction Formats** A-1 Glossary G-1 Index X-1

# **About This Manual**

This manual describes the machine instructions, status bytes, and other information needed to understand system programs from the hardware viewpoint.

## Who should use this manual . . .

This reference manual is intended for persons interested in the operation and the characteristics of the 5360 System Unit, the 5362 System Unit, and the 5364 System Unit at the machine code level. Readers should be familiar with data processing techniques and should understand programming at the machine code level.

## What you should know ....

Before reading this manual you should be familiar with the information in the following IBM system publications:

- Data Communications Concepts, GC21-5169

- System Reference, SC21-9020

- Operating Your System—5360, 5362, SC21-9452

- Operating Your System—5364, SC21-9453

- System Problem Determination, SC21-7919 for the 5360 System Unit, SC21-9063 for the 5362 System Unit, or SC21-9375 for the 5364 System Unit.

# If you need more information . . .

You might need some or all of the following information while using this manual.

- System Data Areas, LY21-0592, provides the IOB bytes for each device and the priority level of the error conditions.

- Program Problem Diagnosis and Diagnostic Aids, SY21-0593, tells how to determine the cause of the problem and what to do if the problem continues.

- Communications and Systems Management Guide, SC21-8010, contains information about the Communications and Systems Management feature, which includes change management (DSNX support for a DSX network) and problem management (alert support for an NCCF/NPDA network).

- Diskette General Information, GA21-9182, provides information on how to load and operate the diskette.

- System Messages, SC21-7938, explains the messages you may see on your display screen.

- Programming with Assembler, SC21-7908, provides additional information about some of the machine instructions that are used with the assembler.

- 1255 Magnetic Character Reader Reference and Logic Manual, GN21-8001, provides additional information about how to program and operate the Magnetic Character Reader.

- X.25 Interface for Attaching IBM SNA Nodes to Packet-Switched Data Networks-General Information Manual, GA27-3345, provides additional information about the elements of CCITT Recommendation X.25.

- Enhanced 5250 Emulation Program User's Guide, G570-2202, provides information for using the IBM Personal Computer as a 5250 work station (display and/or printer).

- 3270 Device Emulation Guide, SC21-7912, provides configuration and operating information for BSC 3270 device emulation and SNA 3270 device emulation.

- Scientific Macroinstructions Functions Reference Manual, SA21-9275, provides information about scientific macroinstructions.

- Using System/36 Communications, SC21-9082, provides information about using communications with System/36.

# How this manual has changed ...

The following information has been added since the last edition of this manual:

- 9332 Disk Drive

- 3196 Display Station

• 3197 Display

- 3812 Printer

- 4210 Printer

- 4234 Printer

- 4245 Printer

- Local Area Network (LAN) attachment

- 6157 Tape Drive

- 3270 Remote Attachment

- Increase in main memory size

- Three additional ideographic languages

- Second asynchronous communications line for the 5364 System Unit

•

• Previously omitted information and diagrams.

XXII System/36 Functions Reference Manual

.

# Abbreviations and Acronyms

| Α     | add to register                                                  |

|-------|------------------------------------------------------------------|

| Α     | address field                                                    |

| ac    | alternating current                                              |

| ACE   | action control element                                           |

| ACK   | acknowledgment                                                   |

| ACR   | address compare register                                         |

| ACR   | abandon call and retry                                           |

| ACU   | autocall unit                                                    |

| adv   | advance                                                          |

| AID   | attention identification                                         |

| ALC   | add logical characters                                           |

| ALI   | add logical immediate                                            |

| ALT   | alternate                                                        |

| AL1   | arithmetic logical 1                                             |

| AL2   | arithmetic logical 2                                             |

| AM    | amplitude modulation                                             |

| A/N   | alphanumeric                                                     |

| A/N/K | alphanumeric and Katakana                                        |

| APA   | all points addressable                                           |

| AQE   | allocation queue element                                         |

| ARR   | address recall register                                          |

| ASCII | American National Standard Code for Information Interchange      |

| ASF   | auto sheet feed                                                  |

| ATR   | address translation register                                     |

| AZ    | add zoned decimal                                                |

| BC    | branch on condition                                              |

| BCC   | block check character                                            |

| BOR   | beginning of read                                                |

| BOT   | beginning of tape                                                |

| bpi   | bits per inch                                                    |

| bps   | bits per second                                                  |

| BSC   | binary synchronous communications                                |

| С     | control field                                                    |

| CC    | completion code                                                  |

| сс    | cause code                                                       |

| CCITT | Consultative Committee on International Telegraphy and Telephony |

| CCR   | configuration control register                                   |

| CE    | customer engineer                                                |

| CF    | Cluster feature                                                  |

| CGCS  | coded graphic character set                                      |

| CHRNX | cylinder, head, record length, number of records                 |

|       |                                                                  |

| CLC<br>CLI<br>CMR<br>COD<br>CPI<br>CPGID<br>CPS<br>CRC<br>CRQ<br>CS<br>CSB<br>CSIPL<br>CSP<br>CTF<br>CTS | compare logical characters<br>compare logical immediate<br>control mode register<br>change of direction<br>characters per inch<br>code page global identification<br>call progress signal<br>cyclic redundancy check<br>call request<br>communication services<br>common storage block<br>control storage initial program load<br>control storage processor<br>continuous forms<br>clear to send |

|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ъ                                                                                                        | delete record                                                                                                                                                                                                                                                                                                                                                                                    |

| D<br>dd                                                                                                  | delete record                                                                                                                                                                                                                                                                                                                                                                                    |

| DBA                                                                                                      | diagnostic code<br>data buffer address                                                                                                                                                                                                                                                                                                                                                           |

| DBA                                                                                                      | data bus in                                                                                                                                                                                                                                                                                                                                                                                      |

| DBO                                                                                                      | data bus ni<br>data bus out                                                                                                                                                                                                                                                                                                                                                                      |

| DCB                                                                                                      | data control block                                                                                                                                                                                                                                                                                                                                                                               |

| DCL                                                                                                      | device control language                                                                                                                                                                                                                                                                                                                                                                          |

| DCP                                                                                                      | diagnostic control program                                                                                                                                                                                                                                                                                                                                                                       |

| DDFF                                                                                                     | distributed disk file facility                                                                                                                                                                                                                                                                                                                                                                   |

| DDSA                                                                                                     | Digital Data Service Adapter                                                                                                                                                                                                                                                                                                                                                                     |

| DFCA                                                                                                     | device function controller attachment                                                                                                                                                                                                                                                                                                                                                            |

| DID                                                                                                      | document insertion device                                                                                                                                                                                                                                                                                                                                                                        |

| DISC                                                                                                     | disconnect                                                                                                                                                                                                                                                                                                                                                                                       |

| DE                                                                                                       | disk enclosure                                                                                                                                                                                                                                                                                                                                                                                   |

| DLE                                                                                                      | data link escape                                                                                                                                                                                                                                                                                                                                                                                 |

| DLE SYN                                                                                                  | transparent synchronous idle                                                                                                                                                                                                                                                                                                                                                                     |

| DLO                                                                                                      | data line occupied                                                                                                                                                                                                                                                                                                                                                                               |

| DM                                                                                                       | disconnected mode                                                                                                                                                                                                                                                                                                                                                                                |

| DMA                                                                                                      | direct memory access                                                                                                                                                                                                                                                                                                                                                                             |

| DOD                                                                                                      | document on demand                                                                                                                                                                                                                                                                                                                                                                               |

| DP                                                                                                       | data processing                                                                                                                                                                                                                                                                                                                                                                                  |

| DPQ                                                                                                      | data processing quality                                                                                                                                                                                                                                                                                                                                                                          |

| DPR                                                                                                      | digit present                                                                                                                                                                                                                                                                                                                                                                                    |

| DQ                                                                                                       | draft quality                                                                                                                                                                                                                                                                                                                                                                                    |

| DSA                                                                                                      | data storage attachment                                                                                                                                                                                                                                                                                                                                                                          |

| DSC                                                                                                      | distant station connected or data storage controller                                                                                                                                                                                                                                                                                                                                             |

| DSR                                                                                                      | data set ready                                                                                                                                                                                                                                                                                                                                                                                   |

| DSX                                                                                                      | distributed systems executive                                                                                                                                                                                                                                                                                                                                                                    |

| DSNX                                                                                                     | distributed systems node executive                                                                                                                                                                                                                                                                                                                                                               |

| DTE                                                                                                      | data terminal equipment                                                                                                                                                                                                                                                                                                                                                                          |

| DTR                                                                                                      | data terminal ready                                                                                                                                                                                                                                                                                                                                                                              |

| DTF                                                                                                      | define the file                                                                                                                                                                                                                                                                                                                                                                                  |

| DTT                                                                                                      | define the table                                                                                                                                                                                                                                                                                                                                                                                 |

| DUB                                                                                                      | device unit block                                                                                                                                                                                                                                                                                                                                                                                |

| EC                                                                                                       | exemption condition (5219)                                                                                                                                                                                                                                                                                                                                                                       |

| EBCDIC                                                                                                   | extended binary coded decimal interchange code                                                                                                                                                                                                                                                                                                                                                   |

| ECC                                                                                                      | error checking and correction                                                                                                                                                                                                                                                                                                                                                                    |

| ECM                                                                                                      | event control mask                                                                                                                                                                                                                                                                                                                                                                               |

| ED        | edit                                                |  |  |

|-----------|-----------------------------------------------------|--|--|

| EIA/CCITT | Electronic Industries Association/Consultative      |  |  |

|           | Committee on International Telegraphy and Telephony |  |  |

| ELCA      | eight-line communications attachment                |  |  |

| ELLC      | enhanced logical link control                       |  |  |

| ENQ       | enquire                                             |  |  |

| EOT       | end of transmission or end of tape                  |  |  |

| EOJ       | end of job                                          |  |  |

| ERB       | error recovery block                                |  |  |

| ERAP      | error recording and analysis procedures             |  |  |

| ETB       | end of transmission block                           |  |  |

| ETX       | end of text                                         |  |  |

|           |                                                     |  |  |

| F         | flag                                                |  |  |

| FC        | frame check                                         |  |  |

| FCS       | frame check sequence                                |  |  |

| FDIOCH    | fixed disk input output control handler             |  |  |

| FDIOS     | fixed disk input output supervisor                  |  |  |

| FID       | font identification                                 |  |  |

| FIFO      | first-in-first-out                                  |  |  |

| FMD       | function management data                            |  |  |

| FRMR      | frame reject                                        |  |  |

|           |                                                     |  |  |

| GCGID     | graphic character set global identification         |  |  |

| GCID      | global character set identification                 |  |  |

| GFI       | general failure index                               |  |  |

| GFID      | graphic font identification                         |  |  |

|           |                                                     |  |  |

| H         | head                                                |  |  |

| HDX       | half-duplex                                         |  |  |

| HDLC      | high level data link control                        |  |  |

| I         | information field                                   |  |  |

| -<br>I/O  | input/output                                        |  |  |

| IAR       | instruction address register                        |  |  |

| ID        | identification                                      |  |  |

| IDE       | information description element                     |  |  |

| IDEO      | ideographic                                         |  |  |

| IPDS      | intelligent printer data stream                     |  |  |

| IGC       | ideographic character                               |  |  |

| IOB       | input/output block                                  |  |  |

| IOCH      | input/output control handler                        |  |  |

| IOS       | input/output supervisor                             |  |  |

| IPL       | initial program load                                |  |  |

| ips       | inches per second                                   |  |  |

| IRS       | inter record separator                              |  |  |

| ITB       | intermediate text block                             |  |  |

| ITC       | insert and test characters                          |  |  |

| IUS       | intermediate unit separator                         |  |  |

| 105       | intermediate unit separator                         |  |  |

| JC        | jump on condition                                   |  |  |

|           |                                                     |  |  |

| kbd       | keyboard                                            |  |  |

| L        | load                                      |

|----------|-------------------------------------------|

| LA       | load address                              |

| LAC      | load alternate characters                 |

| LAN      | Local Area Network                        |

| LC       | logical channel                           |

| LCCB     | -                                         |

|          | logical channel control block             |

| LCD      | liquid crystal display                    |

| LCGN     | logical channel group number              |

| LCI      | logical channel indicator                 |

| LCID     | logical channel identification            |

| LCN      | logical channel number                    |

| LCRN     | logical channel reference number          |

| LCRR     | length count recall register              |

| LCT      | logical channel table                     |

| LED      | light-emitting diode                      |

| LGID     | local character set identification        |

| LIFO     | last-in-first-out                         |

| LLC      | logical link control                      |

| LPDA     | link problem determination aids           |

| LPI      | lines per inch                            |

| LPMR     | load program mode register                |

| LRC      | longitudinal redundancy check             |

| LSD      | Index Down key on 5219 Printer            |

| LU       | logical unit                              |

|          | 0                                         |

| MAB      | memory address buffer                     |

| MCR      | magnetic character reader                 |

| MDT      | modify data tag                           |

| MIC      | message identification code               |

| MLCA     | multiline communications attachment       |

| MLT      | modified line tag                         |

| MPL      | main program level or maximum page length |

| MRJE     | multi-leaving remote job entry            |

| MSAR     | main storage address register             |

| MSD      | Index Up key on 5219 Printer              |

| MSF      | manual sheet feed                         |

| MSIPL    | main storage initial program load         |

| MSP      | main storage processor                    |

| MSR      | magnetic stripe reader                    |

| MVC      | move characters                           |

| MVI      | move logical immediate                    |

| MVX      | move hexadecimal character                |

|          | nove nexadecimal character                |

| NAC      | network access control                    |

| NAK      | negative acknowledgment                   |

| NAP      | network access processor                  |

| NCB      | network control block                     |

| NCP      | network control parameter                 |

| NDM      | normal disconnect mode                    |

| NEP      | never ending program                      |

| NIU      | network information unit                  |

| NLQ      | near letter quality                       |

| NPDA     | network problem determination application |

| Nr       | number received                           |

| NRF      | no record found                           |

| NRM      | normal response mode                      |

| - 1- 111 |                                           |

| NRZI         | nonreturn to zero inverted                     |

|--------------|------------------------------------------------|

| NS           | number sent                                    |

| 145          | number sent                                    |

| OC           | over current                                   |

| OCB          | operations control block                       |

| OCR          | optical character reader                       |

| ov           | over voltage                                   |

| 01           | over voltage                                   |

| P/F          | poll/final                                     |

| PACT         | prefix address contained translation register  |

| PAR          | program address register                       |

| PATR         | PACT register for ATRs                         |

| PCPL         | physical current print line                    |

| PCSP         | PACT register for CSP access                   |

| PDS          | printer data stream                            |

| PIAR         | PACT register for IARs                         |

| PIC          | parent interconnect control                    |

| PIO          | programmed I/O                                 |

| PIU          | path information unit                          |

| PLA          | programmable logic array                       |

| PLO          | phase lock oscillator                          |

| PMR          | program mode register                          |

| PND          | present next digit                             |

| PPQ          | process pending queue                          |

| Pr           | packet receive sequence number                 |

| PREG         | PACT register for register area                |

| PRPQ         | programming request for price quotation        |

| Ps           | packet send sequence number                    |

| PSDN         | packet switching data network                  |

| PSH          | physical service header                        |

| PSM          | proportional spacing mode                      |

| PSR          | program status register                        |

| PTIOCH       | printer terminal input/output control handler  |

| PU           | physical unit                                  |

| PUB          | printer unit block                             |

| PUBQHDR      | printer unit block queue handler               |

| PVC          | permanent virtual circuit                      |

| PWI          | power indicator                                |

| OUDD         | avovo hoodor                                   |

| QHDR<br>QLLC | queue header<br>qualified logical link control |

| QLLC         | quanned logical link control                   |

| R            | record number                                  |

| RD           | request disconnect                             |

| RDOTF        | read data on the fly                           |

| RDS          | receive data space                             |

| RFM          | read file mark                                 |

| RID          | receive initial delayed                        |

| RIM          | request initialization mode                    |

| RNR          | receive not ready                              |

| ROTF         | read file mark on the fly                      |

| RPM          | revolutions per minute                         |

| RPOA         | recognized private operating agency            |

| RQD          | request definite response                      |

| RR           | receive ready                                  |

|              |                                                |

| RSDL                                                                                                                                            | receive signal line detect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RSP                                                                                                                                             | response                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| RTS                                                                                                                                             | request to send                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| RVI                                                                                                                                             | reverse interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| S                                                                                                                                               | subtract from register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SABM                                                                                                                                            | set synchronous balanced mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SBF                                                                                                                                             | set bits off masked                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SBN                                                                                                                                             | set bits on masked                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SCS                                                                                                                                             | SNA character string                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SCT                                                                                                                                             | subsystem control table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| SDLC                                                                                                                                            | synchronous data link control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SERDES                                                                                                                                          | serialization deserialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SFD                                                                                                                                             | select font density                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SHM                                                                                                                                             | short-hold mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SI                                                                                                                                              | shift in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SICB                                                                                                                                            | serial interface control block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| SLC                                                                                                                                             | subtract logical characters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SLCA                                                                                                                                            | single line communications attachment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

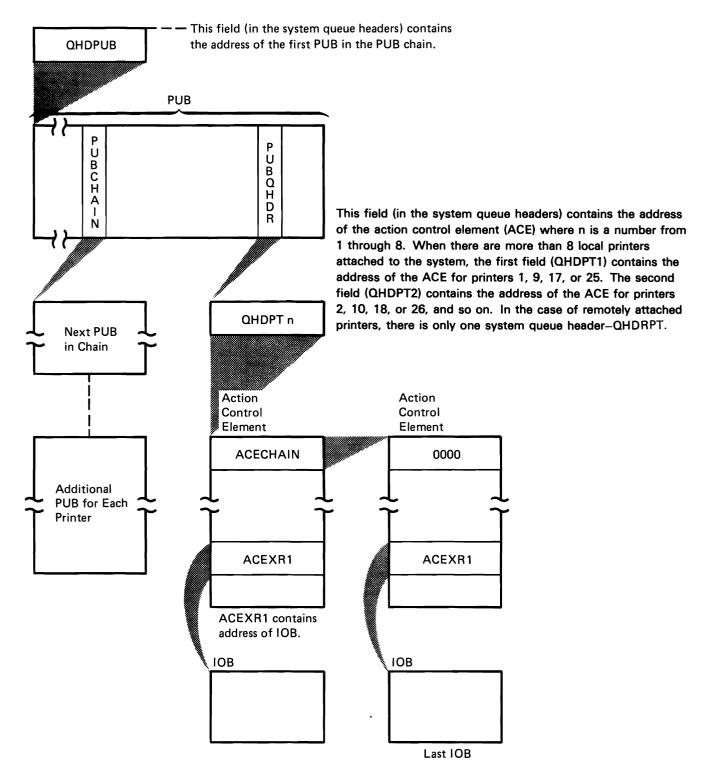

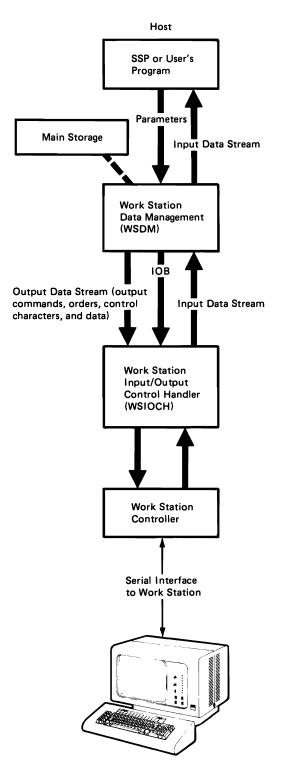

| SLUIT                                                                                                                                           | subtract logical immediate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |