どししし

Series/1

GA34-0246-0 File No. S1-09

IBM Series/1 Feature-Programmable Multiline Communications Feature Description

# Series/1

|                                                                                                                 | A STATE AND AN                                                               | THE SAME VALUE AND                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                 |                                                                                                                  |                                                                                                                 | COM DECISION AND A DE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                 | in the second  |                                                                                                                 | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                 |                                                                                                                  |                                                                                                                 | The state of the second s |

|                                                                                                                 |                                                                                                                  |                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                 |                                                                                                                  |                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                 |                                                                                                                  | · · · · · · · · · · · · · · · · · · ·                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Contract AN PERSONAL AND A CONTRACT  | and the second |                                                                                                                 | 1 T C C S S (17)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                 |                                                                                                                  |                                                                                                                 | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                 | · .                                                                                                              |                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                 |                                                                                                                  |                                                                                                                 | 化二乙酰乙酰乙酰乙酰乙酰乙酰乙酰乙酰乙酰乙酰乙酰乙酰乙酰乙酰乙酰乙酰乙酰乙酰乙酰                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                 |                                                                                                                  |                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                 | · · · ·                                                                                                          | ·                                                                                                               | · ^ ^ · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Sale Sale Sale Sale Sale Sale Sale Sale                                                                         |                                                                                                                  |                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| A REAL AND A | ,                                                                                                                | e en la balente de la companya de la | and the second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

GA34-0246-0

File No. S1-09

IBM Series/1 Feature-Programmable Multiline Communications Feature Description

#### First Edition (May 1983)

This is a major revision of and absoletes GA34-0028 and Technical Newsletters GN34-0604, GN34-0722, and GN34-0793.

Use this publication only for the purpose stated in the Preface.

Changes are periodically made to the information herein; any such changes will be reported in subsequent revisions or Technical Newsletters.

It is possible that this material may contain reference to, or information about, IBM products (machines and programs), programming, or services that are not announced in your country. Such references or information must not be construed to mean that IBM intends to announce such IBM products, programming, or services in your country.

Publications are not stocked at the address given below. Requests for copies of IBM publications should be made to your IBM representative or the IBM branch office serving your locality.

This publication could contain technical inaccuracies or typographical errors. A form for readers' comments is provided at the back of this publication. If the form has been removed, address your comments to IBM Corporation, Information Development, Department 27T, P. O. Box 1328, Boca Raton, Florida 33432. IBM may use or distribute any of the information you supply in any way it believes appropriate without incurring any obligation whatever. You may, of course, continue to use the information you supply.

© Copyright International Business Machines Corporation 1983

This publication describes the Series/1 Feature-Programmable Multiline Communications Feature. The reader should be an experienced Series/1 assembler language programmer who writes, maintains, and debugs machine-level language programs. The reader should also be familiar with binary and hexadecimal numbering systems and stored-program concepts.

The subject matter is presented in two chapters and two appendices:

- Chapter 1 introduces the feature-programmable multiline communications feature.

- Chapter 2 describes the Series/1 machine-level language that the processor uses to transfer data to and from the attachment and devices that connect to the communications line.

- Appendix A contains a summary of the commands, device control blocks (DCBs), cycle-steal status words, and condition codes associated with the attachment feature.

- Appendix B lists the control and data characters used by the attachment feature.

### **Prerequisite Publications**

- IBM Series/1 Principles of Operation, GA34-0152.

- Refer to *IBM Series/1 Graphic Bibliography*, GA34-0055, for the name and order number of the appropriate feature description manual for your processor.

### **Related Publications**

- IBM Series/1 System Selection Guide, GA34-0143

- IBM Series/1 Customer Site Preparation Manual, GA34-0050

- IBM Series/1 Pocket Digest, GX34-0104

.

| Chapter 1. Introduction                             |       |

|-----------------------------------------------------|-------|

| Configurations                                      |       |

| Interfaces                                          | . 1-3 |

| Data Links                                          | . 1-4 |

| Point-to-Point Nonswitched                          | . 1-4 |

| Point-to-Point Switched                             | . 1-4 |

| Multipoint Nonwsitched                              |       |

| Direct Connect                                      |       |

| Establishing a Switched-Line Data Link              |       |

| Initiating a Call                                   |       |

| Answering a Call                                    |       |

|                                                     | . 1-0 |

| Chapter 2. Operations                               | 2 1   |

| Transmission Codes                                  |       |

| Receive/Transmit Mode                               |       |

| Data Flow                                           |       |

|                                                     |       |

| Line Error Checking                                 |       |

| Timers                                              |       |

| Timer 1                                             |       |

| Timer 2                                             |       |

| Commands                                            |       |

| Prepare                                             | . 2-5 |

| Halt I/O                                            | . 2-6 |

| Device Reset                                        | . 2-6 |

| Read ID                                             | . 2-7 |

| Write Data                                          | . 2-7 |

| Start Control                                       |       |

| Start Diagnostic 1                                  |       |

| Start Diagnostic 2                                  |       |

| Diagnostic Data Words                               |       |

| Start                                               |       |

| Data Transmission                                   |       |

|                                                     |       |

| Transmit                                            |       |

| Data Reception                                      |       |

| Expanded Mode                                       |       |

| Bit Rate                                            |       |

| Control Characters                                  |       |

| Start Cycle-Steal Status                            |       |

| Word 2                                              |       |

| Interrupt Status Byte                               |       |

| Interrupt Information Byte (IIB)                    | 2-43  |

| Status After Resets                                 | 2-44  |

| Error Recovery                                      | 2-45  |

| Operate I/O Condition Codes                         | 2-45  |

| Interrupt Condition Codes                           |       |

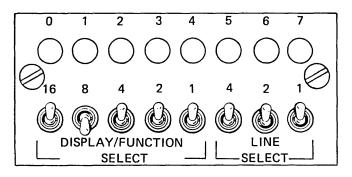

| Jumper Options                                      |       |

| Communications Indicator Panel                      |       |

| LINE SELECT Switches                                |       |

| DISPLAY/FUNCTION SELECT Switches                    |       |

|                                                     | 2-30  |

| Annondiy A. Multi-Lino Attachmont Deforence Summary | A 1   |

| Appendix A. Multi-Line Attachment Reference Summary |       |

| I/O Commands                                        |       |

| Device Control Block (DCB) — General Format         | A-1   |

| Device Control Block (DCB) — Set Mode and Set Control (Asynchronous) | A-2        |

|----------------------------------------------------------------------|------------|

| Device Control Block (DCB) — Set Mode (Synchronous)                  | A-2        |

| Set Mode (Synchronous)                                               | A-2        |

| Control Word                                                         | A-3        |

| Cycle-Steal Status Words                                             | A-4        |

| Word 0                                                               | A-4        |

| Word 1                                                               | A-4        |

| Word 2                                                               | A-4        |

| Interrupt Condition Codes Reported                                   | A-5        |

| Interrupt Information Byte (IIB)                                     | A-5        |

|                                                                      |            |

| Appendix B. Communications Operator's Self-Test Procedure            | <b>B-1</b> |

|                                                                      |            |

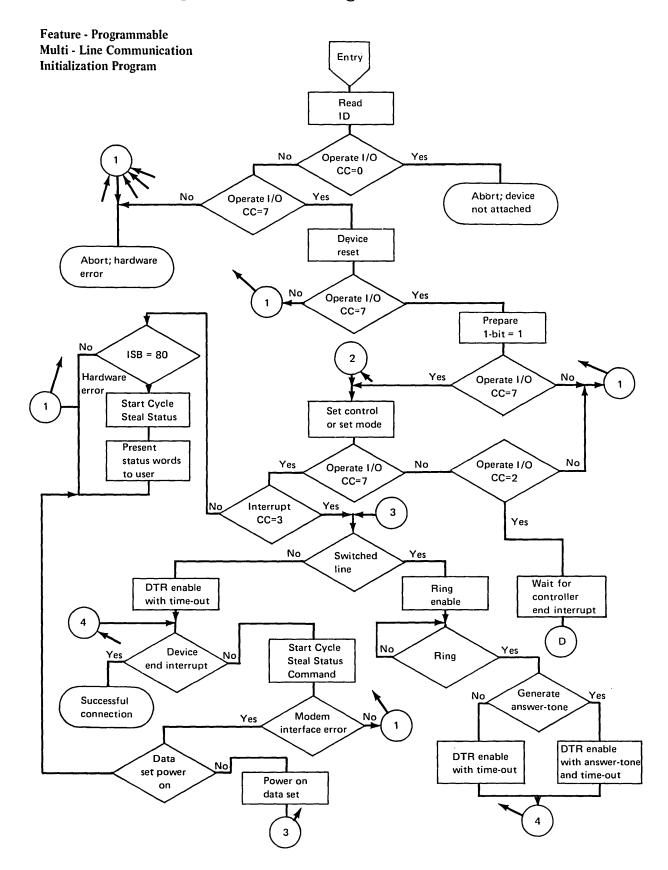

| Appendix C. Multiline Adapter Initialization Program                 | C-1        |

|                                                                      | <b>D</b> 4 |

| Appendix D. Transmission Codes                                       | D-1        |

| • •                                                                  | ¥7 4       |

| Index                                                                | X-1        |

.

## **Chapter 1. Introduction**

This chapter provides an overview of the Feature-Programmable Multiline Communication feature which uses asynchronous or synchronous transmission, depending on which of these options is programmed. Up to eight lines can operate at 7,200 bits per second (bps) or at combinations of different speeds.

The programmable multiline attachment controller is designed to provide control circuitry for one or two programmable 4-line adapter features. The programmable multiline attachment contains hardware and a microprocessor to service the 4-line adapters.

Each line of the multiline communication feature is programmable. The serial transfer of data to and from remote terminals or host systems is described in this chapter. The following communication characteristics apply:

- Data transmission is serial-by-bit, using either asynchronous (start-stop) or synchronous methods of character transmission.

- The feature can communicate with different terminals/systems using ASCII or any transmission code with 5, 6, 7, or 8 bits per character.

- The program defines line control characters.

- The bit rate can range from 37.5 to 1,200 bps, or from 300 to 19,200 bps. Aggregate throughput is 64,000 bps (based on a 12-bit character).

- Mu'tipoint control is provided in which the program can recognize secondary station a <sup>1</sup>-resses in a multipoint network.

- The feature provides answer-tone generation and break character recognition.

- Internal and external (modem) clocking capability (asynchronous only).

- Block check character reception for one or two characters is provided.

- Parity generation and checking can be specified as odd, even, or no parity.

- The stop bit length can be either 1 or 2 characters.

- Synchronous operation can have either 1 or 2 synchronization characters.

- Up to seven different change-of-direction (COD) characters can be recognized.

- Echoplex capability.

- Current loop (20 milliampere) capability or EIA RS232C or CCITT V.24 Interface.

- Expanded mode provides for the following attachment operations:

- Continuous Receive

- Continuous echoplex

- Attention interrupt

- With the following character recognition and detection

- Two-character COD

- Two-character longitudinal redundancy check (LRC)

- Extended COD with block check capability.

#### Configurations

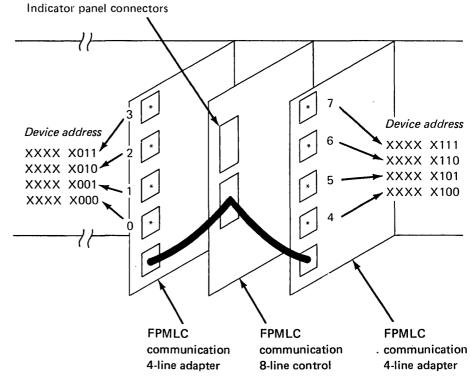

The programmable communication control feature has a multiline configuration and provides control for up to eight lines. This configuration contains either two or three feature cards: two cards for one to four lines, and three cards for five to eight lines.

Note: When referring to the Feature-Programmable 8-Line Communications Control and one or two Feature-Programmable 4-Line Communication Adapters the term attachment is used.

\*Modem interface connectors

Note: XXXX = basic device address

Note: See "Jumper Options" for additional information.

Each line operates in a half-duplex mode (unless expanded mode is selected) and can be connected to a duplex modem to avoid excessive modem turnaround. If a line is connected to a duplex modem, the attachment still operates in half-duplex mode. However, the request-to-send jumper on the feature card should be installed.

#### Interfaces

An EIA<sup>1</sup>RS232-C and CCITT<sup>2</sup> V.24 interface is provided for each line. The interface directly drives or ends an external modem. The Feature-Programmable Multiline Communication feature also provides local attachment capabilities using a 20-milliampere current loop.

The attachment can communicate with remote stations over private lines, leased common-carrier facilities, or switched voice-grade common-carrier lines. It also can be directly connected to remote stations.

Some modems disconnect automatically when the communication feature's DTR signal is deactivated. To deactivate this signal, issue a Start command, with a disable operation specified in the device control block, or use the communications indicator panel.

<sup>&</sup>lt;sup>1</sup> Electronic Industries Association

<sup>&</sup>lt;sup>2</sup> The International Telegraph and Telephone Consultative Committee.

## **Data Links**

Each communication line can operate with one of the following types of data links:

- Point-to-point nonswitched

- Point-to-point switched

- Multipoint nonswitched

- Direct connect

### **Point-to-Point Nonswitched**

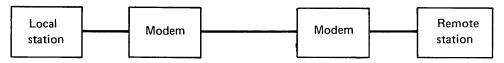

A point-to-point nonswitched data link consists of a local station connected to a single remote station. Such a line is nonswitched because of a permanent connection between the local station and the remote station through their respective modems.

,

### **Point-to-Point Switched**

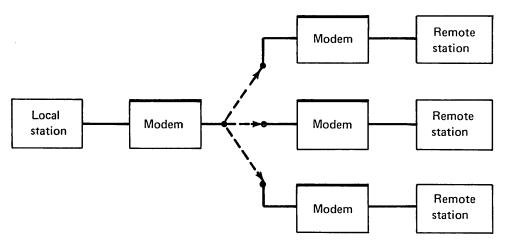

A point-to-point switched data link consists of a local station connected to one of several remote stations after a link has been established between the local station and the remote station. The connection is maintained only for the duration of the communication.

### Multipoint Nonwsitched

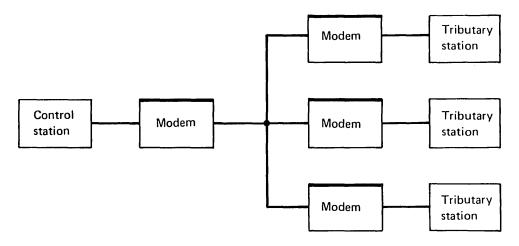

A multipoint nonswitched data link consists of a primary station connected to several secondary stations through their respective modems. The primary station polls the secondary stations, using unique station addresses. Only the addressed station responds to the poll.

### **Direct** Connect

A direct-connect data link consists of two stations connected using an EIA RS232-C, CCITT V.24, or current loop connection.

## **Establishing a Switched-Line Data Link**

### Initiating a Call

- 1. Load the program and make sure that the DTR signal is active.

- 2. Place the modem in talk mode.

- 3. Dial the remote station. The operator of the remote station will answer your call, or you will hear a high-pitched tone indicating that the remote modem is in auto-answer mode. If you talk to the operator, request that the remote modem be placed in data mode (or equivalent).

- 4. Place your modem in data mode (or equivalent) and hang up the receiver.

## Answering a Call

- 1. Lift the receiver and talk to the operator of the other system.

- 2. Make sure that the program is loaded and the DTR signal is active.

- 3. Put your modem in data mode (or equivalent) before the caller puts the calling modem in data mode, and hang up the receiver.

### **Transmission Codes**

In asynchronous operation, the attachment supports transmission codes with 5, 6, 7, or 8 bits per character plus parity and one or two stop bits. The adapter always adds a start bit. In synchronous operation, the attachment supports any transmission code with 5, 6, 7, or 8 bits per character plus parity and one or two synchronization characters. (When two synchronization characters are used, they may be the same character or different characters.) The attachment operates either with no parity bit or with an additional bit for even or odd parity checking.

Any code that meets the preceeding requirements may be used at the programmer's discretion.

#### **Receive/Transmit Mode**

In normal receive mode, when the set control or set mode operations have been used to initialize the adapter, the following conditions are in effect:

- Seven change-of-direction (COD) characters are operable. Two of the CODs can be conditioned, by command, to receive a single character block check character.

- The receive with echoplex functions of the attachment are directly controlled by the Series/1 program using the defined start command operations. In this operating mode, the attachment receives data only when device control block (DCB) receive or DCB transmit with prereceive operations are being processed.

In normal receive mode, the attachment recognizes any one of the seven characters defined in the set mode/set control DCB and treats them as COD characters. When any one of the defined characters is received, the attachment presents a device end interrupt request or begins a DCB command chaining operation except when an incorrect length record is detected. All received characters are placed in storage.

In expanded mode (more information about expanded mode is described under "Data Reception" later in this chapter) the two-character COD causes the adapter to interpret the COD table in conjunction with a delineating character to determine an ending sequence. The user-specified delineating character is the first character received and the second character will be any of the seven programmable characters in the COD table. If two delineating characters are received consecutively followed by a character in the COD table, reception continues until a single delineating character followed by a COD is detected. Typically, the delineating character would be a DLE or ESC character.

In transmit mode, there is no control character comparison. All ending conditions must be controlled by byte count. When the byte count is reduced to 0, a device-end interrupt request or chaining occurs.

**Note:** See DCB description under "Start."

Valid data is placed in storage as it is received. If parity checking is requested, the data is checked for odd or even parity, and then the parity bit is removed from the data character. Data received with incorrect parity is placed in storage as hex 00. The data may be placed in storage exactly as received by placing the DISPLAY/FUNCTION SELECT switches on the communication indicator panel (if installed) to 11110. This applies to any and all lines.

In expanded mode, the inhibit zero insertion affects the adapter error procedure when a bad parity character is received (assumes parity check enabled). Normal adapter operation is to replace the bad parity character with a binary zero character. When this mode is enabled, the adapter does not zero the character but provides the character as it was received (incorrect data parity) with the parity bit removed.

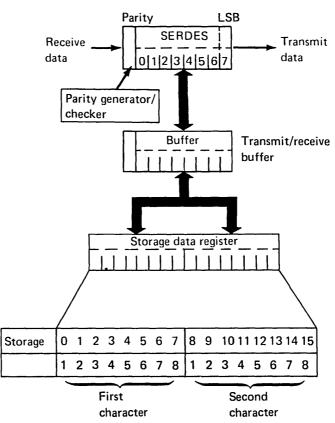

Data is transmitted as it comes from storage; therefore, data must be organized in the exact bit configuration required by the code being used and in the sequence in which it is to be transmitted. Illustrated below is the attachment's storage data register and the bits in storage.

**Note:** The attachment transmits by sending out the low order bit of the byte first. The received characters are stored in the same manner; that is, the first bit received is the low order bit of the byte. If the character is less than 8 bits, it must be right justified. If the data address (DCB word 7) is odd, only one character is moved in or out of storage on the first data transfer.

| Line Error Checking |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | The attachment checks for line errors through programmed parity checking. The DCB in set mode format specifies even, odd, or no parity. If even or odd parity is specified, the parity bit is generated by the adapter in transmit mode and checked by the adapter in receive mode.                                                                                                                                                                                                                                     |

|                     | Note: If the set control DCB is processed, no parity is specified.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                     | Asynchronous operation requires that one or two stop bits (as defined in the set mode/set control DCB) be transmitted with each character. The attachment checks each received character for only one stop bit.                                                                                                                                                                                                                                                                                                         |

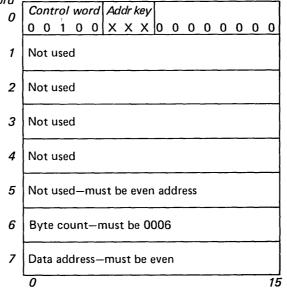

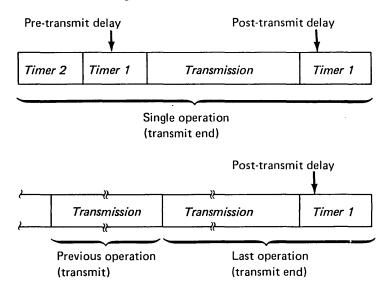

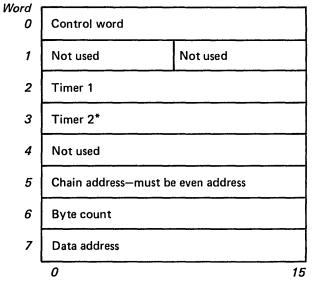

| Timers              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                     | The attachment has two programmable timers (timer 1 and timer 2). Each timer is controlled by a 16-bit word in the DCB. Both timer values are reduced independently at a rate of 3.33 milliseconds per count. The maximum time that either timer can count is 218.2 seconds. The timers use a count (hex FFFF to 0000). When the count reaches 0000, the attachment begins or ends an operation. The timers are used with various operations defined in the control word of the DCB; these operations are listed below. |

| Timer 1             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                     | • Receive time-out (see "Receive with Time-Out" under "Operations" later in this chapter)                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                     | Generate answer tone or break                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                     | • Transmit delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                     | — Slows down turnaround (pretransmit delay)                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                     | <ul> <li>Allows last character to exit modem before deactivating request to send<br/>(posttransmit delay)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                    |

|                     | • Carrier detect time-out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Timer 2             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                     | • Program delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                     | • Clear to send time-out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                     | • Data set ready time-out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                     | Ring indicator time-out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                     | <ul> <li>Data terminal ready disable delay</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                     | The desided information about the second the time with restingly and the second                                                                                                                                                                                                                                                                                                                                                                                                                                         |

For detailed information about the use of the timers with particular operations, see the description of the operations.

e

.

#### Commands

The program begins all communication operations by issuing an Operate I/O instruction.

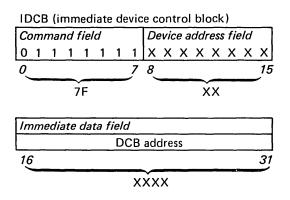

The Operate I/O instruction points to the immediate device control block (IDCB), which contains one of the following commands:

- Prepare

- Halt I/O

- Device Reset

- Read ID

- Write Data

- Start Control

- Start Diagnostic 1

- Start Diagnostic 2

- Start

- Start Cycle-Steal Status

The programmer's must ensure that the program always tests the Operate I/O condition codes following an Operate I/O instruction.

Also, the programmer should exercise care in modifying the DCB words before an interrupt request signifying the end of the operation. All of the DCBs might not have been fetched because the attachment is slower that the Series/1 processor.

Prepare

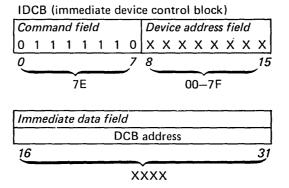

The Prepare command is used to control the interrupt parameters of the addressed device. The data word contains the priority level and I-bit. The IDCB for the Prepare command has the following format:

| IDCB | (immediate | device | control | bl | ock | ) |

|------|------------|--------|---------|----|-----|---|

|------|------------|--------|---------|----|-----|---|

| Са | omi | mai | nd | fiel | d |   |   | De | evic | e a | ddi | ress | fie | eld |    |

|----|-----|-----|----|------|---|---|---|----|------|-----|-----|------|-----|-----|----|

| 0  | 1   | 1   | 0  | 0    | 0 | 0 | 0 | х  | Х    | Х   | Х   | Х    | Х   | Х   | Х  |

| 0  |     |     |    |      | _ |   | 7 | 8  |      |     |     |      |     |     | 15 |

|    |     |     | e  | 60   |   |   | - |    | _    |     | 00- | -FI  | =   |     | -  |

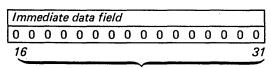

| Immedia | ate data field |       |       |    |

|---------|----------------|-------|-------|----|

|         | 0's            | I     | _evel |    |

| 16      |                | 26 27 | 30    | 31 |

*Level:* This four-bit field specifies the priority interrupt level assigned to the device. Bits 27-30 indicate priority levels.

| Example    |       |

|------------|-------|

| Bits 27-30 | Level |

| 0000       | 0     |

| 0001       | 1     |

| 0010       | 2     |

| 0011       | 3     |

1

A Prepare command issued to any device on this attachment gives all of the devices in the attachment the same priority interrupt level. The I-bit information applies only to the specific device addressed.

**I-Bit:** This bit determines if the device is allowed to present interrupt requests. An I-bit value of 1 allows requests; a value of 0 prevents requests.

The prepared attachment stores the level data and presents it to the processor each time an enabled device presents an interrupt request. This data is reset during a system reset or a power-on reset, or is changed by the successful process of another Prepare command issued to the attachment. The Prepare command causes an interrupt request to be presented if one was pending on the device and the I-bit is set to 1. On a multiline attachment, the device returns an operate I/O condition code 1 to this command if it has an interrupt request pending, and the I-bit in the IDCB is set to 0.

Halt I/O

The Halt I/O command halts all I/O activity on the I/O channel. Any pending interrupt requests, including controller end (CCO), are cleared. Except for the fact that the I-bits and priority level do not change, this instruction performs the same function as a system reset. The format of the IDCB for this command follows:

IDCB (immediate device control block)

| C | omi | mai | nd | fiel | d |   |   | De | evic | e a | ddi | ress | fie | eld |    |

|---|-----|-----|----|------|---|---|---|----|------|-----|-----|------|-----|-----|----|

| 1 | 1   | 1   | 1  | 0    | 0 | 0 | 0 | X  | Х    | Х   | Х   | Х    | Х   | Х   | Х  |

| Q |     |     |    |      |   |   | 7 | 8  |      |     |     |      |     |     | 15 |

|   |     |     | F  | 0    |   |   |   |    | -    |     |     | κx   |     |     |    |

#### **Device** Reset

The Device Reset command resets the addressed device and clears any pending interrupt requests (except controller end). The following are not affected:

- Line control characters

- Bit rate constant

- Number of data bits specified by the DCB

- DTR line

- Controller end interrupt

(See "Status After Resets" later in this chapter.) The IDCB for the Device Reset command has the following format:

IDCB (immediate device control block)

Command field

Device address field

0

1

1

1

1

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

A Device Reset command issued to the attachment causes the attachment to become busy while the reset functions are being performed. A controller busy (CC6) is reported if a Start command follows a Device Reset or another Start command too closely. When the attachment is capable of accepting another command, a controller end interrupt request (CC0) is presented by the base address of the multiline attachment (line 0) at which time the program should reissue the Start command.

Read ID

The Read ID command puts the attachment's identification (ID) word into the IDCB's immediate data field. The ID word contains physical information about the attachment that can be used to tabulate the system's configuration. The Read ID command is generally used in diagnostic programming. The format of the IDCB for this command follows:

| IDCB (immed  | iate devic | e con | trol b | lock | :)    |      |    |

|--------------|------------|-------|--------|------|-------|------|----|

| Command fiel | d          | Devid | ce add | ress | s fie | eld. |    |

| 00100        | 000        | хх    | хх     | Х    | Х     | Х    | х  |

| Q            | 7          | 8     |        |      |       |      | 15 |

| 20           |            |       |        | хx   |       |      |    |

| Immediate da | ta field   |       |        |      | _     |      |    |

|              | Identific  | ation | word   |      |       |      |    |

| 16           |            |       |        |      |       | -    | 31 |

|              | Two-line   | 2     | 116    |      |       |      |    |

|              | Four-line  | e 22  | 216    |      |       |      |    |

|              | Six-line   | 23    | 316    |      |       |      |    |

|              | Eight-lin  | e 20  | 016    |      |       |      |    |

Note: If the controller card has jumpers installed for addresses that are not valid, the controller responds to commands as though the 4-line adapter card was present; therefore, the ID of the controller should match the number of attachment lines present to prevent errors. For example, an ID of 2016 or 2316 defines a controller with two 4-line attachments. If there is only one 4-line attachment present, the ID is 2216 or 2116.

Reference CE binder MLD sheet SC xxxx for controller card jumper layout.

#### Write Data

This command is provided as a way to process character by character operation in the expanded operating mode to provide programmed echoplex. DTR, DSR, RTS, CTS must be active when this command is issued.

This command is similar to a Transmit End Start command except there is no DCB associated with this command. Data is transferred to the attachment in the IDCB. Chaining, pre and posttransmit delays, and modem control operations are not supported. The addressed device is Device Busy until a Device End or Exception Interrupt is presented notifying the program that the adapter is capable of accepting more data.

The Write Data IDCB has the following format:

| Command field |     |      |     |    |      |      | Device address field |    |   |   |     |    |   |   |    |

|---------------|-----|------|-----|----|------|------|----------------------|----|---|---|-----|----|---|---|----|

| 0             | 1   | 0    | 1   | 0  | 0    | 0    | 0                    | х  | х | х | х   | х  | х | х | X  |

| Q             |     |      |     |    |      |      | 7                    | 8  |   |   |     |    |   |   | 15 |

|               |     |      | 9   | 50 |      |      | -                    |    |   | C | 00- | 7F |   |   | -  |

| In            | nm  | edia | ate | da | ta f | ielo | 1                    |    |   |   |     |    |   |   |    |

| Da            | ata |      |     |    |      |      |                      |    |   |   |     | 0  |   |   |    |

| 16            | ;   |      |     |    |      |      | 23                   | 24 | ! |   |     |    |   |   | 31 |

#### Start Control

The Start Control command is used for the following operations:

- Write attachment storage

- Read attachment storage

- Start trace

- Trace dump

- Set expanded mode

Note: See description of DCB see "Start."

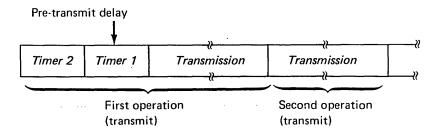

| ID            | CE  | 3 (ii | mm  | ned     | iate | e de | evic | e c                  | ont  | rol | bl | ock | () |   |    |

|---------------|-----|-------|-----|---------|------|------|------|----------------------|------|-----|----|-----|----|---|----|

| Command field |     |       |     |         |      |      | De   | Device address field |      |     |    |     |    |   |    |

| 0             | 1   | 1     | 1   | 1       | 1    | 0    | 0    | X                    | Х    | Х   | Х  | Х   | Х  | Х | X  |

| 0             |     |       |     |         |      |      | 7    | 8                    |      |     |    |     |    |   | 15 |

|               |     |       |     | ν.<br>C |      |      | -    |                      |      | •   | >  | (X  |    |   |    |

| In            | nme | edia  | ate | da      | ta f | iela | 1    |                      |      |     |    |     |    |   |    |

|               |     |       |     |         |      | D    | СВ   | ado                  | dres | SS  |    |     |    |   |    |

| 16            | ;   |       |     |         |      |      |      |                      |      |     |    |     |    |   | 31 |

Issuing this command can cause the attachment to become inoperable, if certain conditions/parameters are not adhered to. If this happens, the attachment can only be restored to operation by switching power off and then on again.

The data address (DCB word 7) must always be even. Otherwise, the attachment ends the operation with an exception interrupt request and the DCB specification check bit in the interrupt status byte is set to 1.

Write Attachment Storage: The DCB format for this operation follows:

| Word | DCB (device control block)       |

|------|----------------------------------|

| 0    | Control word-0X00                |

| 1    | Not used                         |

| 2    | Not used                         |

| 3    | Not used                         |

| 4    | Not used                         |

| 5    | Chain address—not used           |

| 6    | Byte count—must be 432 (hex 1B0) |

| 7    | Data address—must be even        |

|      |                                  |

This operation begins if DCB word 0 bit 2 is set to 0 and the byte count is 432. Starting at the address specified in DCB word 7, the attachment cycle-steals 432 bytes of data from processor storage into storage associated with the attachment. A device end interrupt request is presented when the cycle-stealing is completed. The 432 bytes of data transferred is used by IBM Engineering to make functional changes in the attachment.

If DCB word 0 bit 2 is set to 0 and the byte count is not 432, the attachment ends the operation with an exception interrupt request and the DCB specification check bit in the interrupt status byte is set to 1.

Read Attachment Storage: The DCB format for this operation follows.

| DCB (device control block)         |

|------------------------------------|

| Control word-2X00                  |

| Not used                           |

| Not used                           |

| Not used                           |

| Not used                           |

| Chain address—not used             |

| Byte count—must be 1024 (hex 0400) |

| Data address—must be even          |

|                                    |

This operation begins if DCB word 0 bit 2 is set to 1 and the byte count is 1024. Starting at the address specified in DCB word 7, the attachment cycle-steals 1024

bytes of data from the attachment into storage. A device end interrupt request is presented when the cycle-stealing is completed.

If DCB word 0 bit 2 is set to 1 and the byte count is not 1024, the attachment ends the operation with an exception interrupt request and the DCB specification check bit in the interrupt status byte is set to 1.

Start Trace: The DCB format for this operation follows.

| Word | DCB (device control block)            |

|------|---------------------------------------|

| 0    | Control word-0000                     |

| 1    | Not used                              |

| 2    | Bit-dependent (see description below) |

| 3    | Not used                              |

| 4    | Not used                              |

| 5    | Chain address—not used                |

| 6    | Byte count-must be 0                  |

| 7    | Data address—not used                 |

This operation begins if DCB word 0 bit 2 is set to 0 and the byte count is 0. An array is generated in attachment storage to provide the following information about the last seven DCBs issued to a single address (only one address can be traced at a time):

- The DCB control words

- The DCB addresses

- The interrupt status byte and interrupt condition codes

- The cycle-steal status word 1s information

Data shifts through this array and is traced for predefined error conditions. These conditions are defined in DCB word 2 by having one or several bits set to 1.

The bits and their meanings follow:

- 0 Overrun

- 1 Time-out

- 2 Log all status word 1 errors (all other bits must be off)

- 3 DCB reject

- 4 Not used

- 5 Parity error

- 6 Break detected

- 7 Stop bit error

- 8 Not used

- 9 Modem interface error

- 10-11 Not used

- 12 Error during prereceive/adapter buffer full

- 13-14 Not used

- 15 Adapter buffer not empty

After an error condition is detected, the trace operation stops and information about the last seven DCBs is available to the operator when the trace dump operation is performed. The trace operation also stops when DCB word 2 is set to 0 or when any interrupt status byte except A0 or 80 is presented.

*Trace Dump:* The DCB format for this operation follows:

| Word | DCB (device control block)       |

|------|----------------------------------|

| 0    | Control word-2X00                |

| 1    | Not used                         |

| 2    | Not used                         |

| 3    | Not used                         |

| 4    | Not used                         |

| 5    | Chain address-must be even       |

| 6    | Byte count—must be 64 (hex 0040) |

| 7    | Data address-must be even        |

This operation begins if DCB word 0 equals 2X00 and the byte count is 64. Data for error analysis is dumped from an array in storage to the data address specified in DCB word 7 and is made available to the operator through an output device.

This data is the following information about the last seven DCBs issued to a single address:

- The DCB control words

- The DCB addresses

- The interrupt status byte and interrupt condition codes

- The status word 1 information

This data also includes status words 0 and 2 for the last DCB if the trace operation stops due to an error detected.

**Note:** The field containing the interrupt status byte and interrupt condition codes for the last DCB is followed by FFFF; the field containing status word 1 for the last DCB is followed by FFFF.

The field containing the interrupt status byte and interrupt condition code for the last DCB is followed by 0000; the field containing status word 1 for the last DCB is followed by 0000.

The interrupt status byte and interrupt condition codes are presented in the following format:

| Interrupt status byte | Reset indicator | Condition code |

|-----------------------|-----------------|----------------|

|-----------------------|-----------------|----------------|

The condition codes and their meanings follow:

#### Condition

| 00101010 |                                                 |

|----------|-------------------------------------------------|

| code     | Meaning                                         |

| 00       | No interrupt returned                           |

| 02       | Exception interrupt returned                    |

| 03       | Device end interrupt returned                   |

| F0       | Operation ended by reset                        |

| F2       | Exception interrupt returned followed by reset  |

| F3       | Device end interrupt returned followed by reset |

|          | - •                                             |

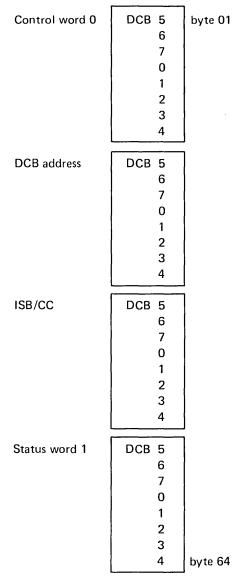

The trace dump storage array appears in storage as follows:

Trace dump storage array

The trace dump printout is as follows:

.

|                | DCB5                   | DCB6 | DCB7           | DCB0 |   | DCB1                     | D      | CB2                                                                                                                                                                                                              | DCB3 | DCB4 |

|----------------|------------------------|------|----------------|------|---|--------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|

| Control word 0 |                        |      | 2004           | SWO  |   |                          |        |                                                                                                                                                                                                                  |      |      |

| DCB address    |                        |      | XXXX           | SW2  | 2 |                          |        |                                                                                                                                                                                                                  |      |      |

| ISB/CC         |                        |      | 8002           | FFFF |   |                          |        |                                                                                                                                                                                                                  |      |      |

| Status word 1  |                        |      | 8000           | FFFF |   |                          |        |                                                                                                                                                                                                                  |      |      |

|                | DCBs without<br>errors |      | Failing<br>DCB |      |   | - SW0<br>- SW2<br>- FFFF | er<br> | CBs without<br>rrors<br>Status word 0 for failing DCB<br>Status word 2 for failing DCB<br>Indicates that trace has stopped<br>on preset error condition<br>(Note: 0000 indicates that<br>trace is still running) |      |      |

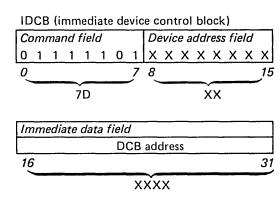

*Set Expanded Mode:* To enable and disable the expanded operating mode the Start Control command is used.

The IDCB has the following format:

| ID | CE            | 3 (i | mm | ned | iate | e de | evic | ce c | ont                  | trol | bl | ock | :) |   |    |

|----|---------------|------|----|-----|------|------|------|------|----------------------|------|----|-----|----|---|----|

| Co | Command field |      |    |     |      |      |      |      | Device address field |      |    |     |    |   |    |

| 0  | 1             | 1    | 1  | 1   | 1    | 0    | 0    | X    | Х                    | Х    | Х  | Х   | Х  | Х | Х  |

| Q  |               |      |    |     |      |      | 7    | 8    |                      |      |    |     |    |   | 15 |

|    | 7C            |      |    |     |      |      |      |      |                      | 5    | ίX |     |    | - |    |

| Immediate data field |      |

|----------------------|------|

| DCB add              | ress |

| 16                   | 31   |

#### **DCB** Format

| Word    | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | 0 0 0 1<br>Not used<br>Not used<br>X field Y field<br>Not used<br>Must be zero<br>Not used                                                                                                                                                                                            |

|---------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| X-field | =                                    | Delineating Character used in Two Character Change of<br>Direction Mode. Bit 10 of the Y field must be on to<br>activate the mode.                                                                                                                                                    |

| Y-field | -                                    | Bit 08 = priority DCB fetch<br>Bit 09 = two-character LRC mode<br>Bit 10 = two-character COD mode<br>Bit 11 = inhibit zero insert mode<br>Bit 12 = 4 CODs with LRC mode<br>Bit 13 = continuous echoplex mode<br>Bit 14 = attention interrupt mode<br>Bit 15 = continuous receive mode |

.

Note: See "Operations" for a description of the modes listed in the Y field.

These modes are stored in a bit significant manner; a 0 disables the mode and a 1 enables the mode.

These extensions are applicable on a per line basis within the Feature-Programmable Multiline adapter. The various adapter modes of operation can be used together. However, certain combinations of modes such as continuous echoplex without continuous receive or attention interrupt without continuous receive are illogical.

(Device Reset, System Reset, Halt I/O resets the expanded mode of operation.)

#### Start Diagnostic 1

The format of the IDCB for this command follows:

When a Start Diagnostic 1 command is issued to the attachment, the following sequence of operations takes place:

- 1. The DCB is fetched.

- 2. A test of the attachment registers is processed. When one or more registers identifies an error, the attachment enters a wait state and no interrupt request is presented.

- 3. A read only storage check sum is calculated and the results are stored at the data address specified in the DCB.

Note: When the attachment recognizes Start Diagnostic 1, it dedicates itself to processing that command and no operations should be pending at other addresses controlled by this attachment.

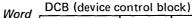

| Wa                    | DCB (device control block)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                       | O         Control word         Addr key           0         0         1         0         X         X         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0 |  |  |  |  |

|                       | 1 Not used                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|                       | 2 Not used                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|                       | 3 Noτ used                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|                       | 4 Not used                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|                       | 5 Not used-must be even address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |