1

0

GA34-0024-02 File No. S1-07

IBM Series/1 4962 Disk Storage Unit and 4964 Diskette Unit Description

| 10027      | ee vwv eer me v | anneet for Acrimited | <br>n reger van regers                                                                                              | the restart to the rest | and the second | andarán an instruction de second | 4-C reparation of the second second                                                                              | en a monte                    | ordentencebación stratura | anywards edur w woo | a week offer one will a | a. 1999 amagazation | rencomment accurate the  | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ | our week week and an and | or while, hep-scoop.ov - comin | and the second se | a san nadi ni na a | ×             | elander and the     | A 460 MA 400 MAN |                   |                       | 1000 1010 LOSA | 000 ma or 20m J          | A 64 44               |

|------------|-----------------|----------------------|---------------------------------------------------------------------------------------------------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------|-------------------------------|---------------------------|---------------------|-------------------------|---------------------|--------------------------|-----------------------------------------|--------------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------|---------------------|------------------|-------------------|-----------------------|----------------|--------------------------|-----------------------|

| Z          |                 |                      |                                                                                                                     |                         | A 1                                                                                                              | 817.1                            |                                                                                                                  |                               |                           |                     |                         |                     |                          |                                         |                          | C                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1. 1. 1.           |               |                     |                  |                   |                       |                |                          |                       |

| herig" i - |                 |                      |                                                                                                                     |                         |                                                                                                                  | 2.11                             |                                                                                                                  |                               |                           |                     |                         |                     |                          |                                         |                          |                                | · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 11 S. M            | · · / · · · · | S. 2                |                  |                   |                       |                |                          |                       |

| Q\$%       |                 |                      |                                                                                                                     |                         |                                                                                                                  | ć.                               |                                                                                                                  |                               |                           |                     |                         |                     |                          |                                         |                          |                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                    |               |                     |                  |                   |                       |                |                          |                       |

| Nrc.       |                 |                      |                                                                                                                     |                         | 1.1                                                                                                              |                                  |                                                                                                                  |                               |                           |                     |                         |                     |                          |                                         | 1.10.10                  |                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                    |               |                     |                  |                   |                       |                |                          |                       |

| S.         |                 |                      |                                                                                                                     |                         |                                                                                                                  |                                  |                                                                                                                  |                               |                           |                     |                         |                     |                          |                                         |                          |                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                    |               |                     |                  |                   |                       |                |                          |                       |

| S. 19 8 -  |                 |                      |                                                                                                                     |                         |                                                                                                                  |                                  |                                                                                                                  |                               |                           |                     |                         |                     |                          |                                         |                          |                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                    |               |                     |                  |                   |                       |                |                          |                       |

| 1.14       |                 |                      |                                                                                                                     |                         |                                                                                                                  |                                  |                                                                                                                  |                               |                           |                     |                         |                     |                          |                                         |                          |                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                    |               |                     |                  |                   |                       |                |                          |                       |

| 1860       |                 |                      |                                                                                                                     |                         |                                                                                                                  |                                  |                                                                                                                  |                               |                           |                     |                         |                     |                          |                                         |                          |                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                    |               |                     |                  |                   |                       |                |                          |                       |

| S.         |                 |                      |                                                                                                                     |                         |                                                                                                                  |                                  |                                                                                                                  |                               |                           |                     |                         |                     |                          |                                         |                          |                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                    |               |                     |                  |                   |                       |                |                          |                       |

| ( Sugar    |                 |                      | <br>e de constation de la cons |                         |                                                                                                                  | data and a state state and and   | and the second | and and all the second second |                           |                     | and a set of the set of |                     | the second second second | and the state has done                  |                          | an anna fan aile 10- aile a    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                    |               | המשפטה לראות המשפטה | •                | via er alternatio | star are datus stars. |                | ing the character counds | n<br>Incala dana Mari |

|            |                 |                      | <br>                                                                                                                |                         |                                                                                                                  |                                  |                                                                                                                  |                               |                           |                     | AN 11 AL 1              |                     |                          |                                         |                          |                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                    |               |                     |                  |                   |                       |                |                          |                       |

|            |                 |                      |                                                                                                                     |                         |                                                                                                                  |                                  |                                                                                                                  |                               |                           |                     |                         |                     |                          |                                         |                          |                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                    |               |                     |                  |                   |                       |                |                          |                       |

GA34-0024-02

File No. S1-07

IBM Series/1 4962 Disk Storage Unit and 4964 Diskette Unit Description

#### Third Edition (June 1985)

This is a reprint of GA34-0024-01 incorporating changes released in the following Technical Newsletters:

GN34-0406-00(dated 19 October 1977) GN34-0550-00(dated 17 August 1979)

References in this publication to IBM products, programs, or services do not imply that IBM intends to make these available in all countries in which IBM operates.

Publications are not stocked at the address given below. Requests for copies of IBM publications should be made to your IBM representative or to the IBM branch office serving your locality.

A form for readers' comments has been provided at the back of this publication. If the form has been removed, address comments to IBM Corporation, Systems Publications, Department 27T, P.O. Box 1328, Boca Raton, Florida 33432. IBM may use or distribute whatever information you supply in any way it believes appropriate without incurring any obligation to you.

©Copyright International Business Machines Corporation 1976,1977

## Contents

Preface v Prerequisite Publications v Related Publications v Chapter 1. IBM Series/1 4962 Disk Storage Unit and 4964 Diskette Unit 1-1 Introduction 1-1 IBM 4962 Disk Storage Unit 1-1 Models 1-1 IBM 4964 Diskette Unit 1-2 Models 1-2 Basic Data Exchange 1-2 Disk Specifications 1-3 Diskette Specifications 1-3 Disk/Diskette Attachments 1-3 Operator Controls 1-3 Chapter 2. Disk/Diskette Data Format 2-1 Disk Surface Format 2-1 Servo Tracks 2-1 Data Tracks 2-1 Cylinders 2-2 Sectors 2-2 Diskette 2-3 Diskette Surface Format 2-4 Cylinders 2-4 Index 2-4 Tracks 2-4 Sectors 2-5 Chapter 3. Programming Disk Operations 3-1 Data Transfer Operations 3-1 Direct Program Control (DPC) 3-1 Cycle Steal (CS) Mode 3-1 Initiating a Disk Operation 3-1 Operate I/O Instruction 3-1 Using the IDCB 3-1 I/O Commands and Disk Operations 3-2 Command Execution Under Direct Program Control 3-3 Prepare Command 3-3 Device Reset Command 3-4 Read Device ID Comma Id 3-4 Command Execution in CS Mc de 3-4 Using the DCB 3-6 DCB Control Word (DCB Wo. 0) 3-6 Seek Control Word (DCB Word 1) 3-6 Physical Sector Count and Flag (DCB Word 2) 3-7 Alternate Sector Assignment 3-7 Cylinder Address (DCB Word 3) 3-7 Head Selection and Sector Number (DCB Word 4) 3-8 Chain Address (DCB Word 5) 3-8 Byte Count (DCB Word 6) 3-8 Data Address (DCB Word 7) 3-8.1 DCB Command Chaining 3-8.1 Start Command 3-9 Programming Considerations 3-10 Seek Operation 3-10 Seek Recalibrate Operation 3-11 Read Data Operation 3-11 Write Data Operation 3-12

Read Verify Operation 3-12 Write Sector ID Operation 3-13 Read Sector ID Operation 3-13 Write Sector ID Skewed Operation 3-14 Read Sector ID Skewed Operation 3-14 Read Diagnostic Operation 3-15 Immediate ID Operations 3-15 Start Cycle Steal Status Command 3-16 Programming Considerations 3-16.1 Status Information 3-16.1 Condition Codes 3-16.1 Interrupt ID Word 3-17 Cycle Steal Status Words 3-19 I/O Interrupts 3-19 End-of-Operation Interrupts 3-20 Attention Interrupts 3-20 Resets (Disk) 3-20 Initial Program Load (IPL) 3-20 Data Security 3-21 Chapter 4. Programming Diskette Operations 4-1 Data Transfer Operations 4-1 Direct Program Control (DPC) 4-1 Cycle Steal (CS) 4-1 Initiating a Diskette Operation 4-1 Operate I/O Instruction 4-1 Using the IDCB 4-1 I/O Commands and Diskette Operations 4-2 Command Execution Under Direct Program Control 4-3 Prepare Command 4-3 Device Reset Command 4-4 Read Device ID Command 4-4 Command Execution in CS Mode 4-4 Using the DCB 4-6 DCB Control Word (DCB Word 0) 4-6 Seek Control Word (DCB Word 1) 4-6 Format Data Word (DCB Word 2) 4-7 Sector Length and Cylinder (DCB Word 3) 4-7 Head Selection and Sector Number (DCB Word 4) 4-7 Chain Address (DCB Word 5) 4-8 Byte Count (DCB Word 6) 4-8 Data Address (DCB Word 7) 4-8 DCB Command Chaining 4-8 Start Command 4-9 Programming Considerations 4-9 Seek Operation 4-10 Seek Recalibrate Operation 4-10 Write Data/Data AM Operation 4-11 Write Data/Control AM Operation 4-12 Read Verify Operation 4-12 Read Data Operation 4-13 Read Sector ID Operation 4-13 Format Track Operation 4-14 Start Cycle Steal Status Command 4-15 Programming Considerations 4-15 Status Information 4-16 Condition Codes 4-16 Interrupt ID Word 4-16 Cycle Steal Status Information 4-19 I/O Interrupts 4-19

End-of-Operation Interrupts 4-20 Attention Interrupt 4-20 Resets (Diskette) 4-20 Initial Program Load (IPL) 4-20

Index X-1

This manual is intended for those interested in the physical characteristics and operation of either the IBM Series/1 4962 Disk Storage Unit or the 4964 Diskette Unit. It assumes the reader understands data processing terminology and is familiar with binary and hexadecimal numbering systems. The manual contains the machine code information required to plan, correct, and modify programs written in the assembler language.

Chapter 1, "IBM Series/1 4962 Disk Storage Unit and 4964 Diskette Unit," describes the characteristics and capacities of disk and diskette units and the functions of Series/1 4962/4964 Attachment Features.

Chapter 2, "Disk and Diskette Data Format," describes how data is arranged on the disk and diskette surfaces.

Chapter 3, "Programming Disk Operations," describes the instructions and control blocks required to execute input/output operations on the disk unit. This chapter also contains disk unit status and interrupt information.

Chapter 4, "Programming Diskette Operations," describes the instructions and control blocks required to execute input/output operations on the diskette unit. This chapter also contains diskette unit status and interrupt information.

#### **Prerequisite Publications**

IBM Series/1 Model 5 4955 Processor and Processor Features Description, GA34-0021 IBM Series/1 Model 3 4953 Processor and Processor Features Description, GA34-0022 IBM Series/1 System Summary, GA34-0035

#### **Related Publications**

IBM Series/1 Installation Manual–Physical Planning, GA34-0029 IBM Series/1 Configurator, GA34-0042 IBM Diskette General Information Manual, GA21-9182 IBM Series/1 Operator's Guide, GA34-0039

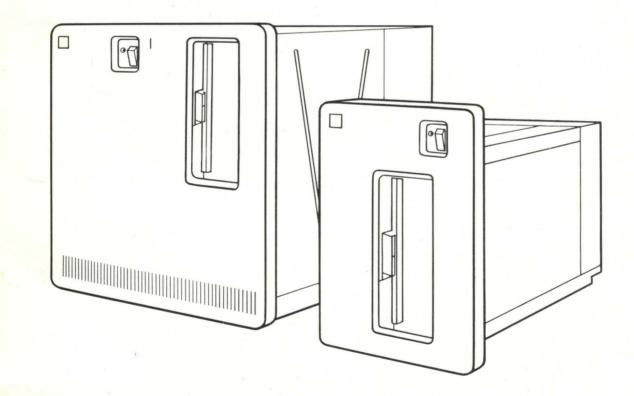

Series/1 4964 Diskette Unit

## Chapter 1. IBM Series/1 4962 Disk Storage Unit and 4964 Diskette Unit

## Introduction

The IBM Series/1 4962 Disk Storage Unit and 4964 Diskette Unit are direct access storage devices designed for use with IBM Series/1 processors.

#### IBM 4962 Disk Storage Unit

The 4962 Disk Storage Unit consists of a fixed disk and access mechanism, the disk drive electronics that retrieve and record data on the disk, and the cables that connect the disk storage unit to an IBM Series/1 processor attachment.

The disk and access mechanism are sealed in an enclosure that:

- eliminates operator handling

- reduces exposure to external contaminants

- eliminates preventive maintenance

#### Models

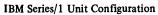

Six models of the 4962 Disk Storage Unit are available. All models have Initial Program Load (IPL) capability and can be mounted in either an Electronic Industries Association rack (RS-310B) or an IBM 4997 Model-1 or Model 2 Rack Enclosure.

IBM 4962 Disk Storage Unit

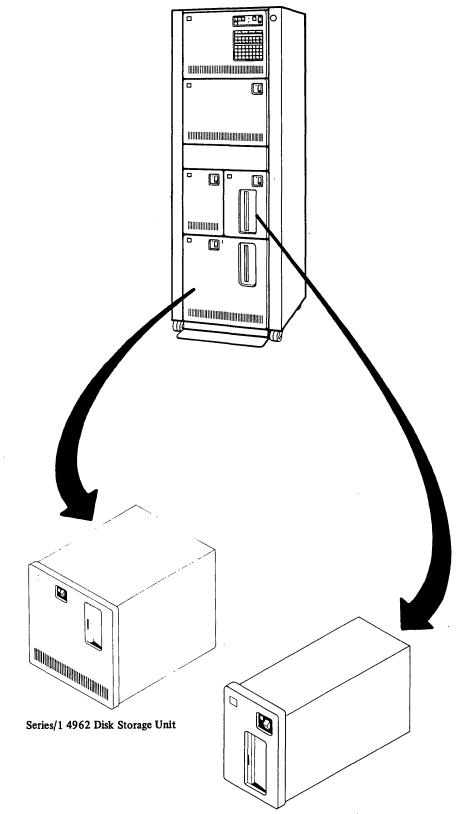

*Model 1* contains a fixed disk with a maximum formatted storage capacity of 9,308,160 bytes. The disk is accessed by two movable heads.

*Model 1F* contains a fixed disk that is accessed by two movable heads and eight fixed heads. Maximum formatted storage capacity is 9,308,160 bytes for the movable heads and 122,880 bytes for the fixed heads.

*Model 2* is a combination disk and diskette unit that contains:

- A fixed disk with a maximum formatted storage capacity of 9,308,160 bytes. The disk is accessed by two movable heads.

- A removable diskette with a maximum formatted storage capacity of 606,208 bytes (512-byte sectors). The diskette is accessed by two movable heads.

*Model 2F* is a combination disk and diskette unit that contains:

- A fixed disk that is accessed by two movable heads and eight fixed heads. Maximum formatted storage capacity is 9,308,160 bytes for the movable heads and 122,880 bytes for the fixed heads.

- A removable diskette with a maximum formatted storage capacity of 606,208 bytes (512-byte sectors). The diskette is accessed by two movable heads.

*Model 3* contains a fixed disk with a maximum formatted storage capacity of 13,962,240 bytes. The disk is accessed by three movable heads.

*Model 4* is a combination disk and diskette unit that contains:

- A fixed disk with a maximum formatted storage capacity of 13,962,240 bytes. The disk is accessed by three movable heads.

- A removable diskette with a maximum formatted storage capacity of 606,208 bytes (512-byte sectors). The diskette is accessed by two movable heads.

Disk units in all models of the 4962 are functionally identical and can be designated as either the primary or alternate system IPL device. The diskette unit in the 4962 Model 2, 2F, and 4 is functionally identical to the 4964 Diskette Unit. Each disk and diskette unit, alone or combined, attaches to individual Series/1 attachments that allow totally independent and fully overlapped operation.

#### IBM 4964 Diskette Unit

The 4964 Diskette Unit retrieves and records data on removable one-sided or two-sided magnetic diskettes. The unit consists of an access mechanism, the diskette drive electronics that record and retrieve data on the diskette and a single cable for connecting the diskette unit to an IBM Series/1 processor attachment. IBM 4964 Diskette Unit

#### Models

One model of the 4964 Diskette Unit is available. The 4964 Model 1 has Initial Program Load (IPL) capability. It can be designated as either the primary or alternate system IPL device. The unit has two movable heads for reading and writing data. An IBM Diskette 2 (two-sided diskette) recorded in 512-byte sector format provides maximum storage capacity (606,208 bytes). An IBM Diskette 1 (onesided diskette) recorded in 128-byte format provides Basic Data Exchange.

The diskette unit mounts in one-half the width of an Electronic Industries Association rack (RS-310B) or an IBM 4997 Model 1 or Model 2 Rack Enclosure.

#### **Basic Data Exchange**

An IBM 4964 Diskette Unit and Attachment Feature connected to a Series/1 processor can exchange diskette data with the following IBM devices using a one-sided diskette recorded in basic data exchange format (128-byte sector format):

- IBM 3540 Diskette Input/Output Unit

- IBM 3741 Data Station

- IBM 3742 Dual Data Station

- IBM 3747 Data Converter

- IBM 3773/3774/3775/3776 Communication Terminals

- IBM 3881 Optical Mark Reader, Model 3

- IBM 3890 Document Processor

- IBM 5231 Controller, Model 2

- IBM 5320 System Unit-System/32

#### **Disk Specifications**

The functional specifications of the disk unit are:

| Rotational speed             | 2964 ± 3%  | RPM          |

|------------------------------|------------|--------------|

| Time of rotation             | 20.2       | ms           |

| Average rotational delay or  |            |              |

| latency                      | 10.1       | ms (nominal) |

| Data Transfer Rate           |            |              |

| To or from channel*          | 380,000    | bytes/sec    |

| On and off disk              |            |              |

| (instantaneous)              | 889,000    | bytes/sec    |

| Movable Head Storage         |            |              |

| Sectors per track            | 60         |              |

| Bytes per sector             | 256        |              |

| Bytes per track              | 15,360     |              |

| Tracks per cylinder          |            |              |

| Models 1, 1F, 2, 2F          | 2          |              |

| Models 3, 4                  | 3          |              |

| Bytes per cylinder           |            |              |

| Models 1, 1F, 2, 2F          | 30,720     |              |

| Models 3, 4                  | 46,080     |              |

| Cylinders                    | 303        |              |

| Total Storage Capacity       |            |              |

| Models 1, 1F, 2, 2F          | 9,308,160  | bytes        |

| Models 3, 4                  | 13,962,240 | bytes        |

| Access Times                 |            |              |

| Cylinder to cylinder         | 10         | ms (maximum) |

| Average seek (101 cylinders) | 40         | ms (maximum) |

| Fixed Head Storage           |            |              |

| Number of heads              | 8          |              |

| Sectors per track            | 60         |              |

| Bytes per sector             | 256        |              |

| Bytes per track              | 15,360     |              |

| Total storage capacity       | 122,880    | bytes        |

|                              |            |              |

\*Time average for multiple sector transfers over two rotations of the disk.

#### **Diskette Specifications**

The functional specifications of the IBM 4964 Diskette Unit and the diskette unit included with 4962 Models 2, 2F, and 4 are:

Maximum data storage capacity

| (formatted with 512-byte sectors) | 606  | kilobytes     |

|-----------------------------------|------|---------------|

| Data transfer rate                | 31.2 | kilobytes/sec |

| Data tracks/diskette surface      | 74   | tracks        |

| Rotational speed                  | 360  | RPM           |

| Latency                           | 83.8 | milliseconds  |

| Track-to-track access time*       | 40   | milliseconds  |

\*Derived from:

T (number of track crossing x 5 ms) + (35 ms settling time)

Diskette data tracks contain either 128, 256, or 512-byte sectors. Refer to "Format Track Operation" in Chapter 4.

|                   | 128 Bytes<br>Per Sector | 256 Bytes<br>Per Sector | 512 Bytes<br>Per Sector |

|-------------------|-------------------------|-------------------------|-------------------------|

| IBM<br>Diskette 1 | 246,2721                | 284,160                 | 303,104                 |

| IBM<br>Diskette 2 | 492,544                 | 568,320 <sup>2</sup>    | 606,208                 |

<sup>1</sup>The basic data exchange format for an IBM Diskette 1. <sup>2</sup>Preinitialized format of an IBM Diskette 2.

#### Disk/Diskette Attachments

IBM Series/1 processor attachment features used with the 4962 and 4964 units:

- interpret and control execution of commands

- provide the path for data between the channel and the disk/diskette

- serialize and deserialize data

- furnish status information to the channel

- check the accuracy of data transferred to and from the channel

- check sector buffer parity (disk attachment only)

- perform a Cyclic Redundancy Check (CRC) of each data field and sector ID transferred to or from the disk/diskette

A 1024-byte buffer is used in every I/O operation that transfers data to or from the disk. Buffering sectors of data eliminates the possibility of overrunning the channel.

#### Note. Diskette data is not buffered.

Attachment feature cards for the disk and diskette units plug into feature card slots in the IBM Series/1 processor card file or the IBM Series/1 4959 Input/Output Expansion Unit.

#### **Operator Controls**

A Power On/Off switch and Power On indicator are located on the front panel of the 4962 and 4964 units.

- 1. Power switch. Power is applied to the disk/diskette unit when this switch is placed in the ON position. Nominally, 16 seconds after power is applied the disk unit is 'ready' for operations.

- 2. Power On indicator. This light indicates the power switch is in the *ON* position.

- 3. Diskette access door. This door must be closed and latched after inserting or removing a diskette.

1-4 GA34-0024

.

## Chapter 2. Disk/Diskette Data Format

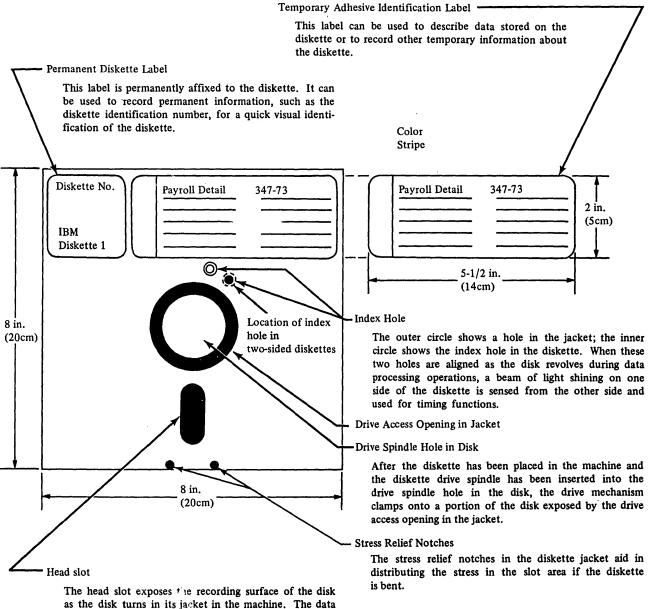

This chapter describes how data is arranged or formatted on the disk and diskette. Cylinder, track, and sector descriptions are included for both the disk and diskette. The functions of the diskette index hole are also explained.

#### **Disk Surface Format**

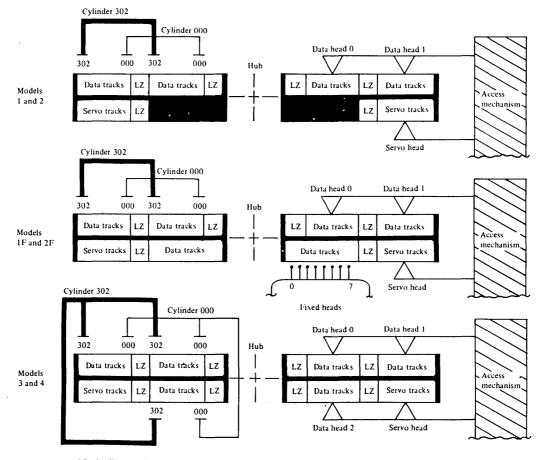

On all models of the 4962, one side of the disk is divided into two data bands; the inner band is accessed by head 0, and the outer band by head 1. Each band contains a head landing zone (LZ) and 303 data tracks. A band of 303 factory written servo tracks on the other side of the disk is used for tracking and seeking.

On 4962 Models 1F, 2F, 3, and 4, a third band of data is located on the servo-track side of the disk. Models 1F and 2F have an eight-track band that is accessed by fixed heads, and Models 3 and 4 have a 303-track band that is accessed by a third movable head. See Figure 2-1. Note. To insure data integrity, data under the fixed heads should be refreshed after each power-on. The IBM Series/1 Realtime Programming System relieves the user of this responsibility.

#### Servo Tracks

Factory written servo tracks assure precise head positioning. Combinations of timing and position pulses define the beginning of each track and sector.

#### Data Tracks

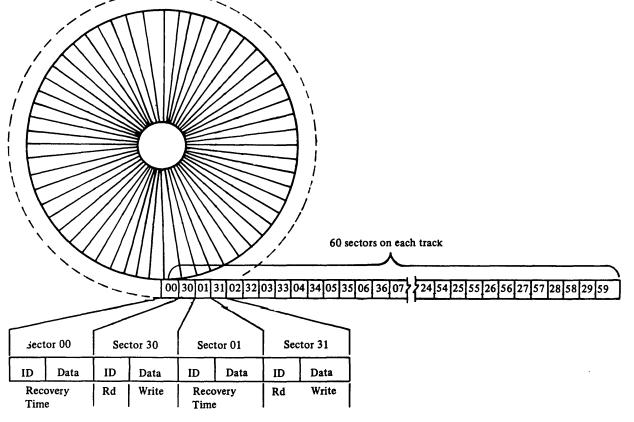

Data tracks accessed by the movable read/write heads are numbered 000 to 302. Each track is divided into sixty, 256-byte, fixed length sectors. Individual track capacity is 15,360 data bytes.

LZ = landing zone for movable heads

Figure 2-1. IBM 4962 disk surface format

## **Cylinders**

A cylinder consists of two tracks, one in each data band accessed by the movable heads. See Figure 2-1. Cylinder 000<sup>o</sup> is located toward the center of the disk, and cylinder 302 is located toward the outer edge of the disk. Two of the 303 cylinders are reserved; cylinder 001 is reserved for alternate sector<sup>\*</sup>s, and cylinder 302 is reserved for maintenance use.

#### Sectors

The sector is the addressable unit on the disk surface. Each sector consists of an identification field (sector ID) and a 256-byte data field. Before accessing the data field, the sector ID is read to verify that the correct sector has been found. Sectors on the disk are numbered 00, 30, 01, 31 ... 28, 58, 29, 59 to allow recovery time between writing a data field and reading the next sector ID. See Figure 2-2. For programming purposes the sectors can be considered consecutively numbered. For example, moving from sector 06 to sector 07 is a shift of one sector.

Records are stored in the data portions of sectors. If a record is less than 256 bytes, the remainder of the sector is padded with binary zeros before the data field CRC is written. If a record is longer than 256 bytes, it is written over as many sectors as its length requires. Records must not exceed track capacity (60 sectors).

#### Sector ID Field Format

The sector ID field is seven bytes in length. Each sector on the disk has a unique ID field. The ID field has the following format:

| 1    | 2      | 3       | 4         | 5           | 6         | 7 |

|------|--------|---------|-----------|-------------|-----------|---|

| Flag | Cylind | er addr | Head addr | Sector addr | CRC bytes | 7 |

|      |        |         |           |             |           |   |

where:

| flag             | indicates the disk surface condition for the sector                                                                                                                                                                                                                                                                                                               |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| cylinder address | indicates the cylinder on which the sector is located                                                                                                                                                                                                                                                                                                             |

| head address     | indicates the head used to access the sector                                                                                                                                                                                                                                                                                                                      |

| sector address   | indicates the number of the sector on the track                                                                                                                                                                                                                                                                                                                   |

| CRC              | indicates the cyclic redundancy check bytes<br>calculated and written for the sector ID field.<br>CRC bytes are also written for the data field<br>after the data area. The CRC bytes are recal-<br>culated each time information is read from the<br>disk and compared with the CRC bytes written<br>previously. An unequal comparison sets error<br>indicators. |

Further information on specifying the fields in the sector ID can be found under "Using the DCB" in Chapter 3.

Figure 2-2. Sector numbering

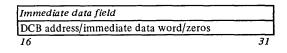

#### Diskette

The diskette storage medium is a magnetically coated disk that is permanently enclosed in a jacket. Small slots in the jacket allow the read/write heads to contact the surfaces as the disk rotates within the jacket. The disk and jacket, together, are referred to as a *diskette*. See Figure 2-3.

The head slot exposes the recording surface of the disk as the disk turns in its jacket in the machine. The data recording and sensing unit of the diskette unit, which is called a *read/write head* and is similar to the record/ playback head in a tape recorder, moves to specified positions along the length of the slot. Moving to a specified position is called *accessing a track*.

Figure 2-3. Diskette storage medium

## **Diskette Surface Format**

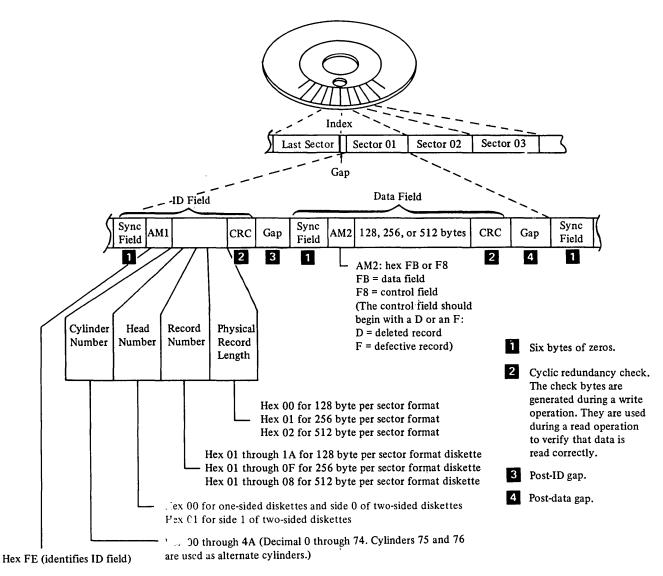

Depending on the type of diskette (IBM Diskette 1 or Diskette 2), one or both sides are formatted with tracks divided into sectors. The Diskette 1 contains 74 data tracks on the head 0 side of the diskette. The head 1 side of the Diskette 1 is blank and cannot be used. The Diskette 2 contains 74 data tracks on both sides of the diskette. The number of sectors on each track-26, 15, or 8-depends on the sector length-128, 256, or 512 bytes respectively.

## **Cylinders**

On a Diskette 1, *the terms cylinder and track are synonomous*. On a Diskette 2, a cylinder consists of the pair of tracks (one on each side) that can be read or written without moving the heads.

## Index

When the index hole in the diskette passes a light source, an index timing pulse is generated. The index timing pulse signals the beginning of a track and occurs each time the diskette rotates. The index timing pulse is used to begin Format Track operations and to determine whether a Diskette 1 or Diskette 2 is installed in the diskette unit. See Figure 2-4.

An attempt to access the head 1 side of a Diskette 1 ends the operation and sets the DCB specification check in the interrupt status byte to 1. Refer to "Interrupt Status Byte" in Chapter 4.

## Tracks

Diskette surfaces are divided into 77 tracks with each track divided into fixed-length sectors. A sector is a physical location on the diskette; sector format is described in the following section. A sector can hold all or part of a record. If the record is shorter than the sector length, unused bytes are padded with binary zeros. If a record is longer than the sector length, the record is written over as many sectors as its length requires.

The data storage capacity of a track depends on track format. Tracks can be formatted with one of three fixedlength sector sizes:

| Sector Size |                   | Track Storage |

|-------------|-------------------|---------------|

| Capacity    | Sectors per Track | Capacity      |

| 128 bytes   | 26                | 3328 bytes    |

| 256 bytes   | 15                | 3840 bytes    |

| 512 bytes   | 8                 | 4096 bytes    |

The ability to choose a sector size is especially useful if records length requirements change from job to job and thus from diskette to diskette. The sector size that provides the most efficient use of diskette space can be chosen depending on the record length required.

Tracks must be numbered from 00 (outermost) to 76 (innermost). The tracks should be used in the following ways:

- Reserve track 00 for system use as a label track.

- Reserve track 01 through 74 for data; until used for data they contain unallocated free space.

- Reserve tracks 75 and 76 for use as alternates.

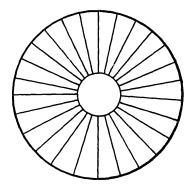

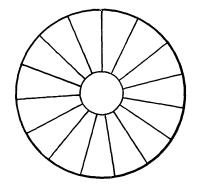

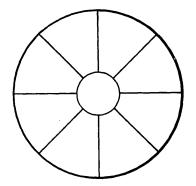

26 Sectors

15 Sectors

8 Sectors

## Sectors

Each sector consists of a sector identifier (sector ID) and a data field. The sector ID holds the unique address for the sector. Refer to the following section, "Sector ID Format."

Sector numbers are assigned beginning with 01 for the first sector after index. There are 26 sectors if the sector length for the diskette is 128 bytes, 15 sectors if the length is 256 bytes, and 8 sectors if the length is 512 bytes.

Figure 2-4. Diskette track format

#### Sector ID Format

The sector ID consists of seven bytes, and each sector on the diskette has a unique ID. The sector ID has the following format:

| ID. |  |

|-----|--|

| _           | -    |      |      |      |      |      |      |

|-------------|------|------|------|------|------|------|------|

| Γ           | AM1  | С    | Н    | R    | N    | CRC  | CRC  |

|             | Byte |

| <u>ا</u> لم |      |      |      |      |      |      |      |

AM1. This Address Marker (AM) signals the start of each sector. The AM1 byte is always X'FE'.

**C-Byte**. The C-byte contains a binary number that designates the cylinder in which the sector is located (cylinders 00 through 76). The C-byte corresponds to the cylinder address byte in the Device Control Block (DCB). Refer to "Using the DCB" in Chapter 4.

H-Byte. The H-byte identifies the head used to access the sector. Because the diskette unit contains two heads, 0 and 1, this byte must contain a value of either X'00' or X'01'. Otherwise, the response to all data transfer operations except Read Sector ID is 'no record found'. The H-byte corresponds to the head selection byte in the Device Control Block (DCB). Refer to "Using the DCB" in Chapter 4.

**R-Byte.** The R-byte identifies the sector number. The sector number must be specified with a binary number that represents 01 through 26 for 128-byte sectors, 01 through 15 for 256-byte sectors, or 01 through 08 for 512-byte sectors. The R-byte in the sector ID corresponds to the sector number byte in the Device Control Block (DCB). Refer to "Using the DCB" in Chapter 4 and the note after "CRC Bytes" in this chapter.

# **N-Byte**. The N-byte designates the byte length of each sector on the track. The N-byte must contain hexadecimal:

- 00 for tracks formatted with 128-byte sectors

- 01 for tracks formatted with 256-byte sectors

- 02 for tracks formatted with 512-byte sectors

Using any other N-byte designation causes a DCB specification check for all data transfer operations except Read Sector ID. The N-byte corresponds to the sector length byte in the Device Control Block (DCB). Refer to "Using the DCB" in Chapter 4 and the note after "CRC Bytes" in this chapter.

**CRC Bytes.** A two-byte Cyclic Redundancy Check (CRC) field is calculated as each sector ID is written. The CRC bytes are written immediately after the sector ID bytes. They are also calculated and written after the data field in each sector. The CRC bytes are recalculated each time information is read from the diskette and compared with previously written CRC bytes. An unequal comparison sets error indications.

The cyclic redundancy check provides the following error detection capability:

- 100% of odd bit errors

- 100% of single burst failures of 16 bits or less

- 99.9985% of random errors

Note. During all data transfer operations except Read Sector ID, the C-byte, H-byte, R-byte, and N-byte of the sector ID are specified as a search argument in the DCB. The required sector is located by comparing sector IDs on the diskette with the search argument in the DCB. When an equal comparison occurs, the data transfer begins. This chapter describes the I/O commands required to perform input/output operations on the IBM 4962 Disk Storage Unit. The commands that can be issued, the instruction and control blocks required for each command, and the individual disk operations are described. Status information and I/O interrupts are also described in this chapter.

## **Data Transfer Operations**

Data is transferred on the I/O channel in a parallel operation (16 data bits plus 2 parity bits). On a write operation, parity bits are removed and the data bits are transferred serially to the disk. On a read operation, the data bits are read serially from the disk, parity bits are added, and the information is transferred one word at a time into processor storage. The direction in which data moves on the channel is determined by the I/O command. The command also determines whether data is transferred to or from processor storage under direct program control only, or under direct program control and in cycle steal mode.

## Direct Program Control (DPC)

An I/O command executed under direct program control transfers a word of data or control information into or from processor storage. After moving the immediate data, the processor continues with other instructions.

## Cycle Steal (CS) Mode

When data is transferred in cycle steal mode, processing and I/O operations are overlapped. Overlapping allows the processor to execute other instructions while the disk unit is cycle stealing the data required to complete an I/O operation. Data is moved to or from processor storage by stealing cycles from the processor.

## Initiating a Disk Operation

Every I/O operation to the disk unit requires (in processor storage):

- 1. an Operate I/O instruction

- 2. an I/O command, device address, and an immediate data field.

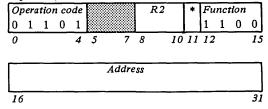

## **Operate I/O Instruction**

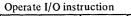

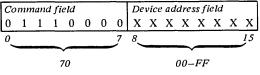

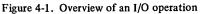

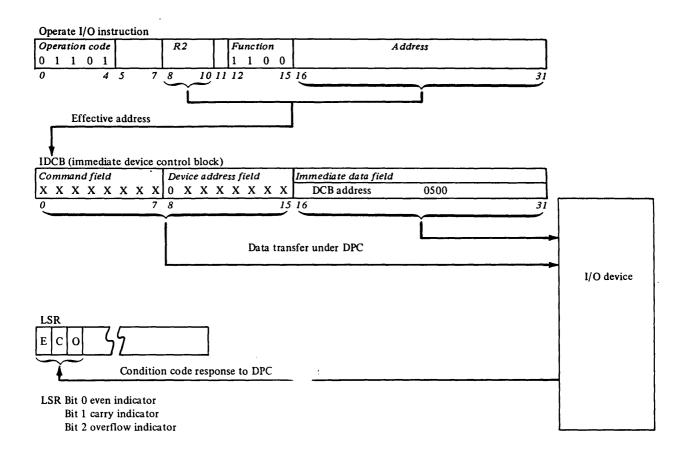

The Operate I/O instruction points to an Immediate Device Control Block (IDCB) in storage containing an I/O command, device address, and immediate data field. Refer to the following section for more detail. Every Operate I/O instruction must have an associated IDCB.

Note. The Operate I/O instruction is described more completely in IBM Series/1 processor unit description manuals. Refer to the Preface of this manual for titles and order numbers.

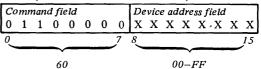

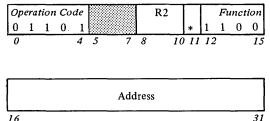

The format of the Operate I/O instruction is:

Operate I/O instruction

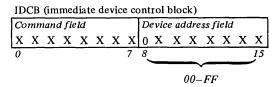

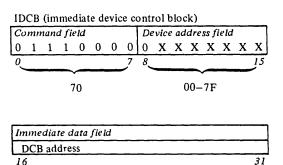

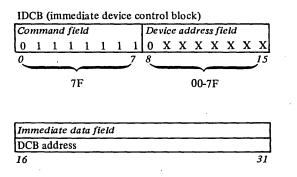

## Using the IDCB

An Immediate Device Control Block (IDCB) must be reserved in processor storage for every I/O command issued to the disk unit. Before issuing an Operate I/O instruction to the disk unit, an I/O command must be stored in the command field of the associated IDCB. The immediate data field of the IDCB must contain a data word, a DCB address or zeros. I/O commands that execute only under direct program control require a data word or zeros, while commands that also transfer data in cycle steal mode require a DCB address. Refer to the following section.

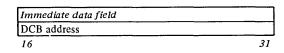

The format of the IDCB is:

## I/O Commands and Disk Operations

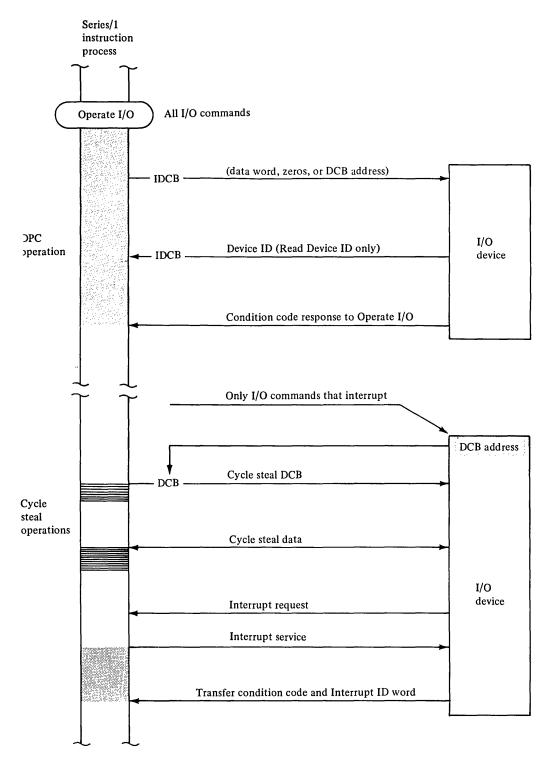

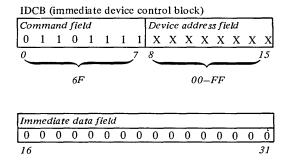

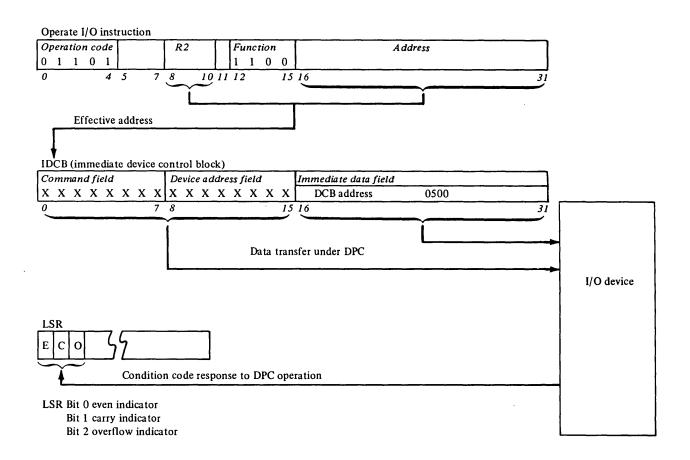

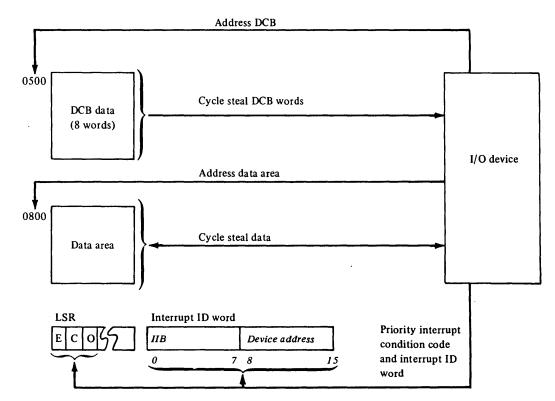

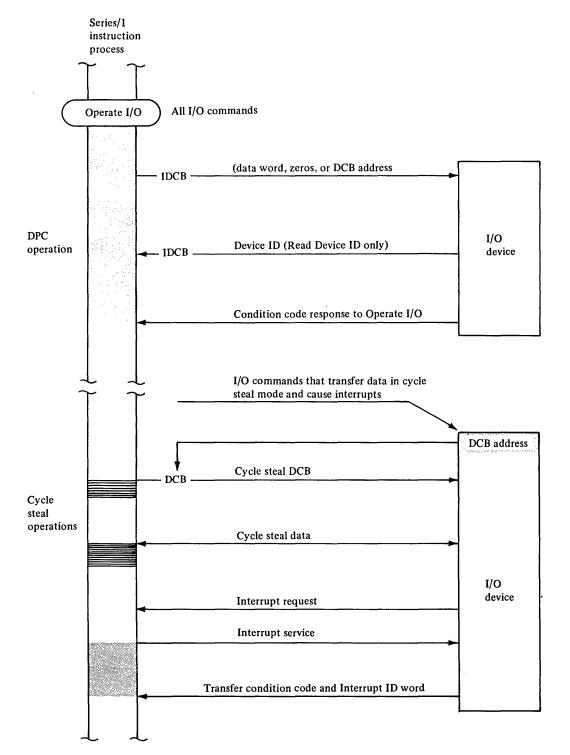

The I/O command, stored in the IDCB, determines whether a single word of immediate data is transferred under direct program control only or, following the DPC operation, additional words of data are to be transferred into or from processor storage in cycle steal mode. See Figure 3-1.

Figure 3-1. Overview of an I/O operation

## Command Execution Under Direct Program Control

Prepare, Device Reset, and Read Device ID commands transfer a single word of data to or from the immediate data field of an IDCB in storage. Command execution is complete when a condition code is reported to the processor following the DPC operation. Refer to "Condition Codes" later in this chapter. Processing of other instructions resumes when the I/O operation ends. See Figure 3-2.

Figure 3-2. I/O operation initiated and executed exclusively under direct program control

#### **Prepare Command**

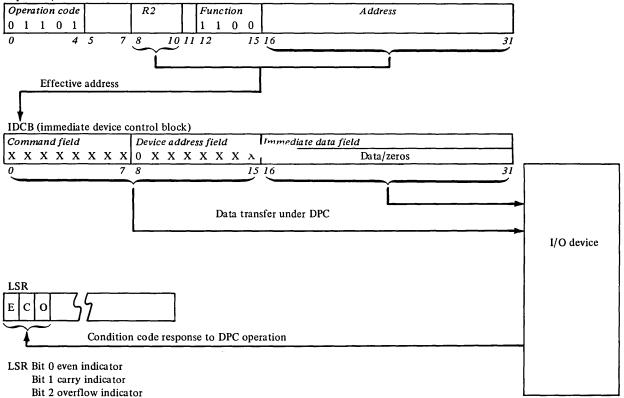

Before using any of the interrupt-causing commands, a Prepare command must be issued to the disk unit. The Prepare command transfers a word containing interrupt parameters from the IDCB immediate data field associated with the command to the *Prepare Register* in the disk attachment. The interrupt parameters in this word establish whether the disk unit is allowed to interrupt, and if so, the level on which processing operations can be interrupted. The Prepare command is executed under direct program control and does not cause an interrupt.

*Note.* Refer to "Prerequisite Publications" in the Preface of this manual. Processor description manuals contain information about interrupt levels.

#### **Device Reset Command**

The Device Reset command resets all pending interrupts and previously established control and status conditions. The device ID, device address, data address, residual address, and prepare registers are not reset by this command. The command code and device address in the IDCB supply the information required to execute the Device Reset command. Although the IDCB immediate data field is not used and not checked, set the bits to zero. The Device Reset command is executed under direct program control and does not cause an interrupt.

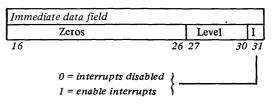

The format of the IDCB for a Device Reset command is:

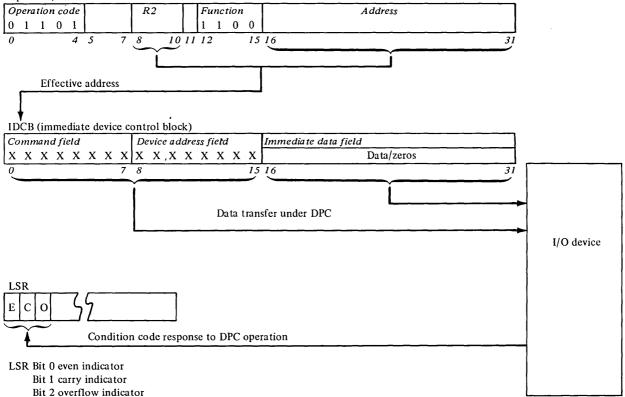

#### **Read Device ID Command**

The Read Device ID command loads the disk unit device ID word into the immediate data field of the IDCB associated with the command. Read Device ID executes under direct program control: the device ID is transferred immediately into storage, and a condition code is reported to the processor. Refer to "Status Information" later in this chapter. The Read Device ID command does not cause an interrupt.

The format of the IDCB for the Read Device ID command is:

IDCB (immediate device control block)

| Со | тm | anc | t fie | ld |   |   |   | De | vice | ad | dres   | ss fi | eld |   |    |

|----|----|-----|-------|----|---|---|---|----|------|----|--------|-------|-----|---|----|

| 0  | 0  | 1   | 0     | 0  | 0 | 0 | 0 | X  | х    | х  | Х      | х     | Х   | Х | Х  |

| 0  |    |     |       |    |   |   | 7 | 8  |      |    |        |       |     |   | 15 |

| ~  | -  | -   |       | _  |   |   | - | -  |      |    | $\sim$ | _     |     | - | ·  |

|    |    |     | 20    |    |   |   |   |    |      | (  | 00-    | FF    |     |   |    |

| Im | me | diat | e d | ata , | fiel | d |   |   |   |   |   |   |   |   |    |

|----|----|------|-----|-------|------|---|---|---|---|---|---|---|---|---|----|

| 0  | 0  | 0    | 0   | 0     | 0    | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0  |

| 16 |    |      |     |       |      |   |   |   |   |   |   |   |   |   | 31 |

During command execution, the device ID is transferred under DPC to this field. After execution of the Read Device ID command, the immediate data field in the IDCB associated with the command contains:

| Immediat | e data field    |    |

|----------|-----------------|----|

|          | Model dependent |    |

| 16       |                 | 31 |

00AA = without fixed heads (Models 1 and 2) 00BA = with fixed heads (Models 1F and 2F) 00CA = with three movable heads (Models 3 and 4)

#### **Command Execution in CS Mode**

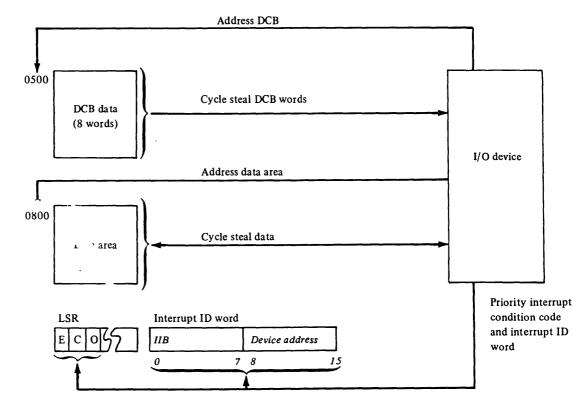

Start and Start Cycle Steal Status commands transfer data in cycle steal mode. The DCB address associated with either command, however, is transferred under DPC from the IDCB immediate data field in processor storage to the disk unit. See Figure 3-2. When the disk unit accepts the command and DCB address, a condition code is reported to the processor. The processor continues with other operations and the disk unit begins cycle stealing the data required to complete the I/O operation. When the transfer of data in cycle steal mode ends, an interrupt request is sent to the processor. At interrupt presentation time a condition code and interrupt ID word are transferred to the processor. The I/O operation ends and the processor continues with other operations.

The immediate data field of an IDCB containing either a Start or Start Cycle Steal Status command must point to a Device Control Block (DCB). See Figure 3-3. The DCB must contain the control information and device parameters required to execute an I/O operation in cycle steal mode. Refer to the following section.

Figure 3-3. I/O operation initiated under direct program control and executed in cycle steal mode

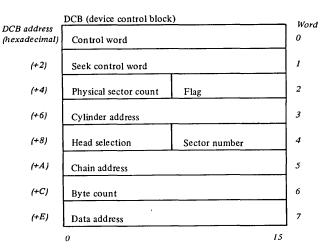

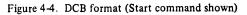

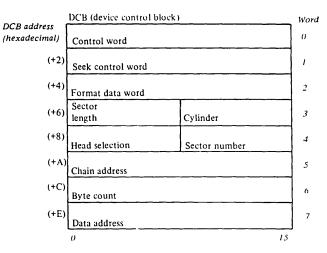

## Using the DCB

A Device Control Block (DCB), comprised of eight contiguous words in processor storage, must be reserved for every I/O operation that moves data in cycle steal mode. See Figure 3-4. A separate DCB is required for:

- a Start command

- a Start Cycle Steal Status command

- all disk operations included in a DCB command chaining sequence (refer to "DCB Command Chaining" later in this chapter.)

Device parameters that define and control the I/O operation must be stored in each DCB.

| DCB address   | DCB (device control bloc | k)            |           |

|---------------|--------------------------|---------------|-----------|

| (hexadecimal) | Control word             |               | Word<br>0 |

| (+2)          | Seek control word        |               | 1         |

| (+4)          | Physical<br>sector count | Flag          | 2         |

| (+6)          | Cylinder address         |               | 3         |

| (+8)          | Head selection           | Sector number | 4         |

| (+A)          | Chain address            |               | 5         |

| (+C)          | Byte count               |               | 6         |

| (+E)          | Data address             |               | 7         |

|               | 0                        |               | 15        |

Figure 3-4. DCB format (Start command shown)

General information about each word and field in the DCB is supplied in the sections that follow; specific information appears in the description for each operation later in this chapter.

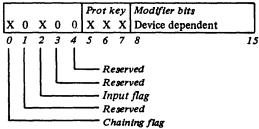

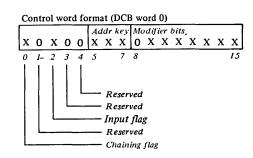

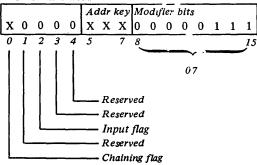

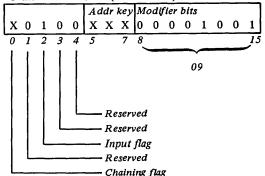

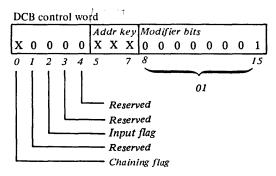

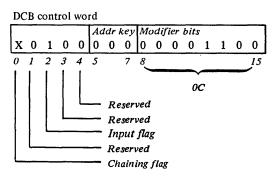

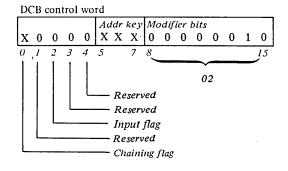

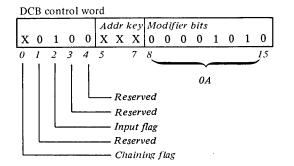

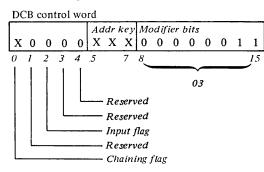

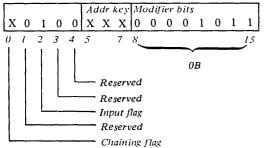

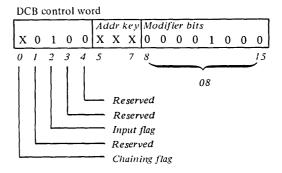

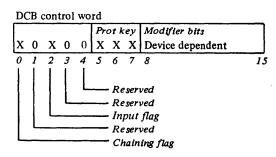

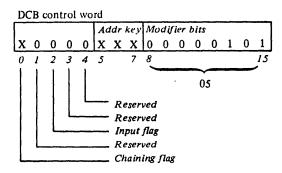

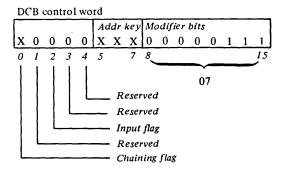

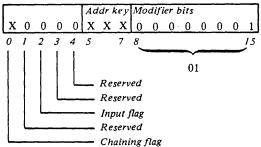

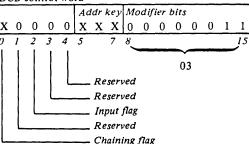

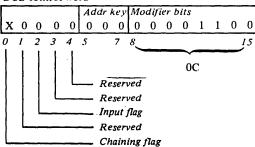

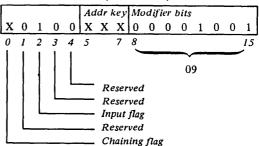

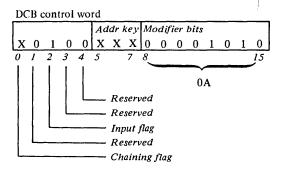

## DCB Control Word (DCB Word 0)

Figure 3-5 shows the format of the DCB control word. This word occupies the first position of each DCB associated with a Start or Start Cycle Steal Status command. The DCB control word delineates the disk operation.

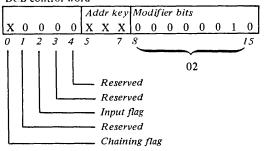

#### DCB control word

Figure 3-5. DCB control word format

The meaning of the bits is as follows:

|          | U                         |                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| g-<br>ry | Bit 0<br>(chaining flag)  | Set this bit to 1 to specify DCB command<br>chaining. When the operation called for by the<br>current DCB ends, the chain address stored in<br>DCB word 5 points to the next DCB in the<br>chained sequence. Refer to "DCB Command<br>Chaining" later in this chapter.                                                                                                                                              |

| ng       | Bit 1<br>(reserved)       | Set this bit to 0 to avoid future code obsolescence.                                                                                                                                                                                                                                                                                                                                                                |

| ra-      | Bit 2<br>(input flag)     | Set the input flag bit to 1 for disk operations<br>that transfer data into processor storage. Set the<br>bit to 0 for disk operations that transfer data<br>from storage and for Seek/Seek Recalibrate<br>operations.                                                                                                                                                                                               |

| orđ      | ·                         | <i>Note.</i> If the input flag bit setting is not consistent with the type of operation: the operation ends and an interrupt request is sent to the processor. At interrupt presentation time, an exception condition and a DCB specification check are presented to the processor.                                                                                                                                 |

|          | Bit 3<br>(reserved)       | Set this bit to 0 to avoid future code obsolescence.                                                                                                                                                                                                                                                                                                                                                                |

|          | Bit 4<br>(reserved)       | Set this bit to 0 to avoid future code obsolescence.                                                                                                                                                                                                                                                                                                                                                                |

|          | Bits 5–7<br>(address key) | These bits represent the cycle steal address key<br>required for storage authorization at cycle steal<br>request time.                                                                                                                                                                                                                                                                                              |

|          | Bits 8–15                 | The bits in this field are device dependent<br>modifiers of the Start command. A bit con-<br>figuration must be selected that represents the<br>disk operation to be performed. The selected<br>disk operation must be compatible with the<br>setting of the input flag bit (bit 2). The hexa-<br>decimal designation for each disk operation and<br>the corresponding setting of bit 2 are shown in<br>Figure 3-6. |

| -<br>r   |                           | Note. Burst mode (bit 15) is not supported by the 4962 and 4964.                                                                                                                                                                                                                                                                                                                                                    |

| Bit 2 | DCB control word<br>modifier bits 8–15 | Hexadecimal<br>equivalent | Operation              |

|-------|----------------------------------------|---------------------------|------------------------|

| 0     | 0000001                                | 01                        | Write Data             |

| 0     | 00000010                               | 02                        | Write Sector ID        |

| 0     | 00000011                               | 03                        | Write Sector ID Skewed |

| 1     | 00001001                               | 09                        | Read Data              |

| 1     | 00001100                               | 0C                        | Read Verify            |

| 1     | 00001010                               | 0A                        | Read Sector ID         |

| 1     | 00001011                               | 0B                        | Read Sector ID Skewed  |

| 1     | 00001000                               | 08                        | Read Diagnostic        |

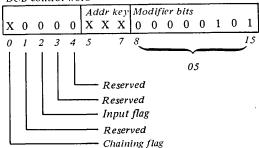

| 0     | 00000101                               | 05                        | Seek                   |

| 0     | 00000111                               | 07                        | Seek Recalibrate       |

Figure 3-6. DCB control word modifier bit configurations

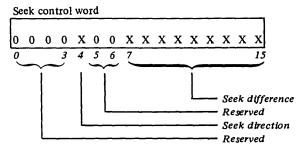

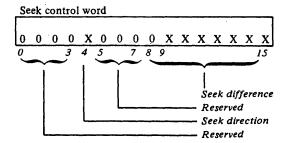

## Seek Control Word (DCB Word 1)

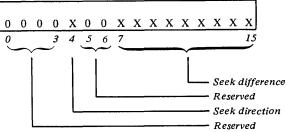

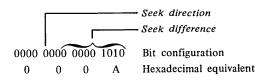

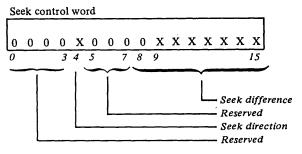

The seek control word is used, in conjunction with the head address specified in the high-order byte of DCB word 4, to control Seek operations. The seek control word specifies the direction of the seek—either toward the outer perimeter of the disk or toward its center—and the number of cylinders to be crossed. Figure 3-7 shows the format of the seek control word. Notes.

- 1. Use the seek control word only for Seek operations.

- 2. If the seek control word is set to zero, no seek movement occurs.

- 3. Because they are not required for a Seek operation, set DCB word 3, DCB word 6, and the sector number in DCB word 4 to zero. The search argument and byte count are not used in Seek operations.

Figure 3-7. Seek control word format

The meaning of the seek direction and seek difference fields are as follows:

| Bit 4                          | To increase the cylinder number (seek toward                                                                                                                                                                                                                   |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (seek direction)               | the outer edge of the disk), set this bit to 0. To<br>seek to a lower cylinder number (toward the<br>center of the disk), set this bit to 1.                                                                                                                   |

| Bits 7–15<br>(seek difference) | These nine bits specify the seek difference (the<br>number of cylinders to be moved). If a seek dif-<br>ference of zero is specified, no movement occurs<br>and a device end condition code is transferred<br>to the processor at interrupt presentation time. |

Bits 0-3 and 5-6 in the seek control word are reserved and must be set to zeros to avoid future code obsolescence.

## Physical Sector Count and Flag (DCB Word 2)

DCB word 2 is comprised of two one-byte fields: the physical sector count and the flag byte of the search argument.

#### **Physical Sector Count**

This byte is required only for the sector-counting disk operations: Write Sector ID, Write Sector ID Skewed, Read Sector ID, Read Sector ID Skewed, and Read Diagnostic. These disk operations are used to locate a specific sector on the disk without reading sector ID bytes. Factory written sector bytes are recorded at the beginning of every sector location on the disk. The sector counting operations locate a specific sector on a track, by counting these sector bytes. A physical sector byte count that is one less than the desired physical sector location must be stored in the DCB associated with each sector-counting disk operation. For example:

| Physical   |

|------------|

| byte count |

| 59         |

| 00         |

| 01         |

| 02         |

|            |

## Flag

A search argument comprised of the flag byte, the cylinder address in DCB word 3, and the head and sector addresses in DCB word 4 is used to locate the first sector in a Read Data, Write Data, or Read Verify operation. Sector IDs are read from the disk track, and compared to the search argument. When an equal comparison occurs, the transfer of data begins. The flag byte is the first byte of the sector ID; bits 6 and 7 specify the disk surface condition for the sector. Bits 0-5 are reserved and must be set to zero to avoid future code obsolescence. Bits 6 and 7 have the following meanings:

Bits 6-7 Disk surface condition indicator

- 00 good primary sector

- 10 defective primary sector

- 01 good alternate sector

- 11 defective alternate sector (cylinder 001)

#### Alternate Sector Assignment

A recurring error condition, such as no-record found or cyclic-redundancy-check, indicates that a sector should be assigned to an alternate physical location on the disk. The defective sector should be flagged as defective and further reference to it should be directed to the alternate location by placing the alternate sector address in the defective sector's ID.

The ID of the selected alternate sector on cylinder 001 is written identical to the original sector except for the flag bits. The flag bits are written to identify it as an assigned alternate sector.

If the original sector has a defective ID field, data recovery is accomplished by the read diagnostic operation.

Recovered or reconstructed data should be written into the newly defined alternate sector and the data should be verified. Then the original sector ID should be written to reflect the address of the alternate sector and the ID should be verified. The flag byte is written to show it as a defective sector. If the original sector has a defective ID field, it must be rewritten using the write sector ID skewed operation.

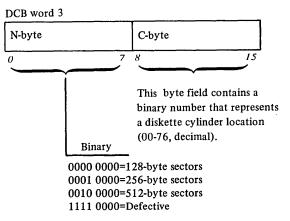

## Cylinder Address (DCB Word 3)

The cylinder address of the required sector must be specified in DCB word 3. The cylinder address is the second and third bytes in the sector ID. A right adjusted binary number from 000 to 302 must be specified to identify the cylinder containing the data to be accessed. The cylinder address is part of the search argument used to locate the first sector involved in a Read Data, Write Data, or Read Verify operation.

#### Notes.

- 1. Bits 0-6 of the cylinder address must always be set to zeros.

- A cylinder address of 152 should be specified in the DCB search argument for Write Sector ID and Write Sector ID Skewed operations on the fixed R/W heads.

## Head Selection and Sector Number (DCB Word 4)

DCB word 4 consists of two one-byte fields: head selection and sector number.

#### **Head Selection**

Head selection can only be accomplished with the Seek operation. To change head selection without changing cylinders, perform a Seek operation with the desired head designation in the head selection byte and a seek difference of zero in the seek control word (DCB word 1). The possible bit configurations (and their hexadecimal equivalents) for the head selection byte are:

|                      |   | Head selection byte bit configurations | Hexadecimal<br>equivalents |

|----------------------|---|----------------------------------------|----------------------------|

| Select movable head: | 0 | 0000 0000                              | 00                         |

|                      | 1 | 0000 0001                              | 01                         |

|                      | 2 | 0000 0010                              | 02                         |

| Select fixed head:   | 0 | 1000 0000                              | 80                         |

|                      | 1 | 1000 0001                              | 81                         |

|                      | 2 | 1000 0010                              | 82                         |

|                      | 3 | 1000 0011                              | 83                         |

|                      | 4 | 1000 0100                              | 84                         |

|                      | 5 | 1000 0101                              | 85                         |

|                      | 6 | 1000 0110                              | 86                         |

|                      | 7 | 1000 0111                              | 87                         |

#### Sector Number

The low-order byte of DCB word 4 specifies the sector number. A right-adjusted binary number from 00 to 59 must be used to specify the sector to be accessed.

## Chain Address (DCB Word 5)

To chain disk operations, set the chaining flag bit in the DCB control word (DCB word 0) to 1. The address of the next DCB in the chain must be specified in the chain address (DCB word 5). The address must be an even number. If the chained-to address is an odd number (bit 15 is on), no data is transferred, and a DCB specification check is set in the interrupt status byte and transferred to the processor at interrupt presentation time.

## Byte Count (DCB Word 6)

The byte count specifies the number of bytes to be transferred between processor storage and the disk unit. The byte count must be an even number and cannot be zero. If bit 15 is set on (indicating an odd byte count) or the count is zero: the operation ends, no data transfer takes place, and a DCB specification check is presented to the processor.

Several I/O operations to the disk unit require a specific hexadecimal value in the byte count:

1. The byte count for a Start Cycle Steal Status command must contain X'0008'.

2. For disk operations initiated with a Start command, the following hexadecimal values must be stored in the byte count:

| Disk operation         | Byte count (in hex) |

|------------------------|---------------------|

| Read Sector ID         | 0006                |

| Read Sector ID Skewed  | 0006                |

| Write Sector ID        | 0006                |

| Write Sector ID Skewed | 0006                |

| Read Diagnostic        | 0100                |

| Write Sector ID Skewed | 0006                |

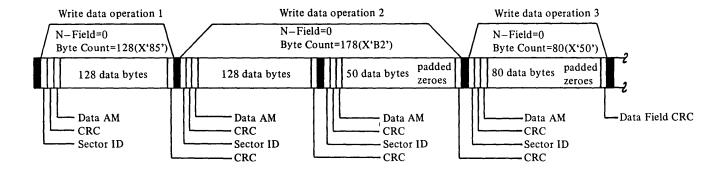

3. For Read Data, Write Data, and Read Verify operations, the byte count depends on the program requirements. For these operations, the byte count has the following format:

| No. of full sectors |   | No, of bytes in partial |    |  |  |

|---------------------|---|-------------------------|----|--|--|

| 0                   | 7 | 8                       | 15 |  |  |

Bits 0-7 specify the number of *full* sectors to be transferred. For example: if a record is exactly 512 bytes long (two sectors), store X'02' in bits 0-7 of the byte count.

Bits 8-15 are used if the record is less than a full sector, or if the last sector in a multi-sector transfer contains less than 256 bytes of data. Use a hexadecimal value to specify the number of bytes in a partially filled sector.

#### Example:

To transfer an 80-byte record, specify (in hexadecimal) 00 50

L number of bytes in partial sector

number of full sectors

To transfer a 256-byte record, specify (in hexadecimal)

01 00

02

L number of bytes in partial sector

number of full sectors To transfer a 600-byte record, specify (in hexadecimal)

58

L number of bytes in partial sector \_\_\_\_\_ number of full sectors

*Note.* On write operations involving a sector that is only partially filled with data, the disk unit writes the data called for in the DCB and then pads the balance of the sector with binary zeros. When the record is subsequently read, the padded zeros are included in the data field CRC verification. Only the number of data bytes specified in the DCB byte count, however, are transferred into storage.

#### Data Address (DCB Word 7)