•--

STUDENT TEXT ABR30533-1

**Computer Systems Department**

# LONG RANGE INPUTS C694-416L-ST

# 15 April 1967

Keesler Technical Training Center Keesler Air Force Base, Mississippi Computer Systems Department KTTC, Mississippi

Student Text ABR30533-1 15 April 1967

Long Range Inputs

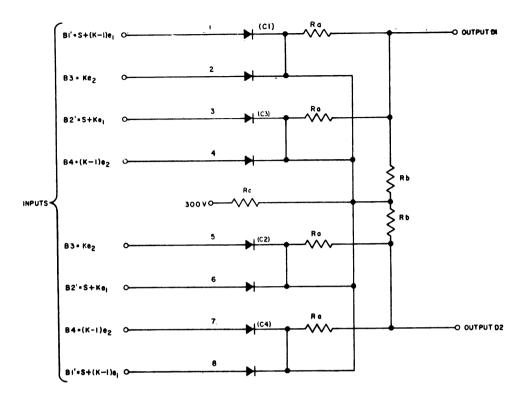

This Student Text has been reproduced intact from materials originally prepared to support a Type I course offered at the contractor's facility; therefore, the format differs from that usually used in preparing ATC training materials. This text provides student study and reference material in support of Course ABR30533-1.

#### CONTENTS

|     | SUBJECT                                                                                                                       | PAGE |

|-----|-------------------------------------------------------------------------------------------------------------------------------|------|

| Ι.  | INTRODUCTION TO LONG RANGE INPUTS                                                                                             | 0010 |

|     | A. Scope of Course                                                                                                            | 0010 |

|     | B. Inputs in General                                                                                                          | 0010 |

|     | C. LRI Data Flow                                                                                                              | 0030 |

|     | D. Transmission of Data                                                                                                       | 0050 |

|     | E. Phone Line and Drum Words                                                                                                  | 0060 |

|     | F. Physical Layout of Unit Number 41                                                                                          | 0120 |

|     | G. LRI Controls an Simplex Maintenance Console                                                                                | 0140 |

|     |                                                                                                                               | 0160 |

|     | H. Introduction to LRI Monitor<br>~I. Introduction to the Test Pattern Generator XTL TEXT · R / 35+<br>J. Input Switching /59 | 0180 |

|     | J. Input Switching                                                                                                            | 0190 |

|     | K. Summary Questions                                                                                                          | 0240 |

| п.  | TAPE CORE THEORY (REVIEW)                                                                                                     | 0280 |

|     |                                                                                                                               | 0280 |

|     | A. Introduction to Tape Cores<br>B. Physical Description                                                                      | 0280 |

|     | B. Physical Description<br>C. Theory of Operation                                                                             |      |

|     | · -                                                                                                                           | 0280 |

|     | D. Core Shift - Model C                                                                                                       | 0290 |

|     | E. Typical Core Shift Register Operation                                                                                      | 0310 |

|     | F. Core Prime, Models A, B, C, and D                                                                                          | 0320 |

|     | G. Core Shift Drivers                                                                                                         | 0320 |

|     | H. Summary Questions                                                                                                          | 0330 |

| ш.  | LRI CHANNEL OPERATION                                                                                                         | 0340 |

|     | A. LRI Pulse Generation Circuitry                                                                                             | 0340 |

|     | B. LRI Channel Block Diagram Analysis                                                                                         | 0360 |

|     | C. Logic Analysis, Data Converter and Synchronizer                                                                            | 0440 |

|     | D. Logic Analysis, Primary Core Shift Register and Control                                                                    | 0460 |

|     | E. Logic Analysis, Parity Alarm and Busy Bit Detector                                                                         | 0490 |

|     | F. Logic Analysis, Word #1 & 2 Buffer, and Fast Shift Control                                                                 | 0520 |

|     | G. Introduction to LRI Drum Demand Generation                                                                                 | 0550 |

|     | H. Logic Analysis Readout Control of Channel                                                                                  | 0580 |

|     | I. Summary Questions                                                                                                          | 0610 |

| IV. | DUPLEX SWITCHING                                                                                                              | 0690 |

|     | A. General                                                                                                                    | 0690 |

|     | B. Driving of A and B Signal Relays                                                                                           | 0700 |

|     | C. Core Data Switching                                                                                                        | 0740 |

|     | D. Write Level Switching                                                                                                      | 0750 |

|     | E. Readout Alarm Switching                                                                                                    | 0750 |

|     | F. Timing Pulse and Level Switching                                                                                           | 0770 |

|     | G. Drum Demand Switching                                                                                                      | 0770 |

|     | H. Site Neon Indication Switching                                                                                             | 0780 |

|     | I. Status Indication Switching                                                                                                | 0790 |

|     | J. Summary Questions                                                                                                          | 0790 |

|      | SUBJECT                                                        | PAGE         |

|------|----------------------------------------------------------------|--------------|

| v.   | LRI COMMON EQUIPMENT OPERATION                                 | 0830         |

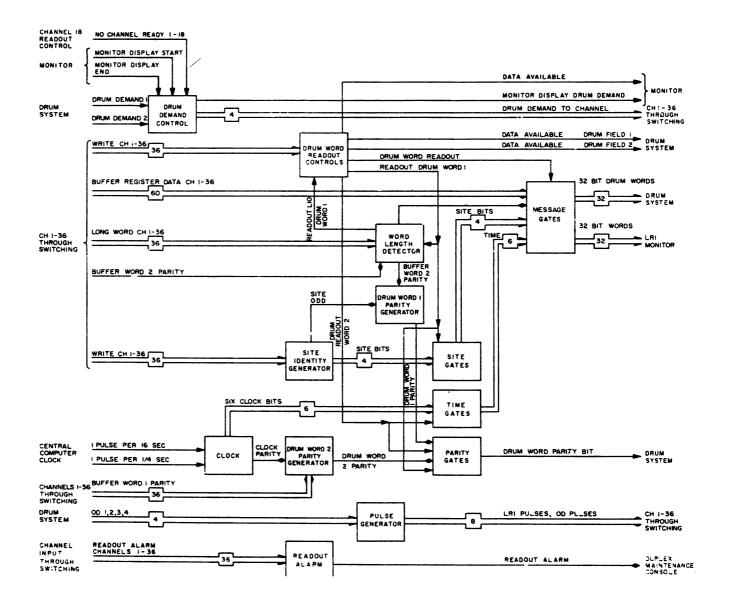

|      | A. Common Equipment Block Diagram                              | 0830         |

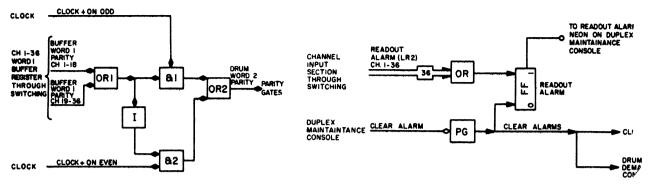

|      | B. Logic Analysis, Drum Demand Control                         | 0870         |

|      | C. Logic Analysis, Site Identity Generators                    | 0950         |

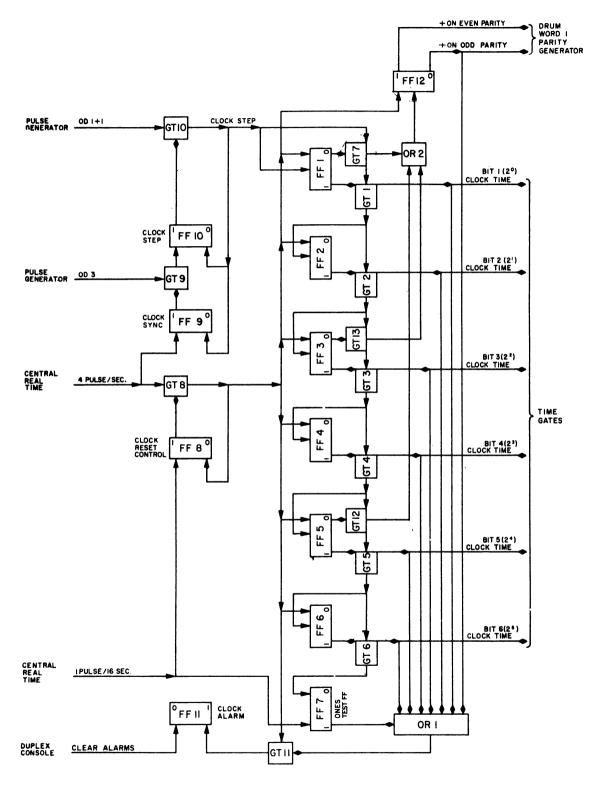

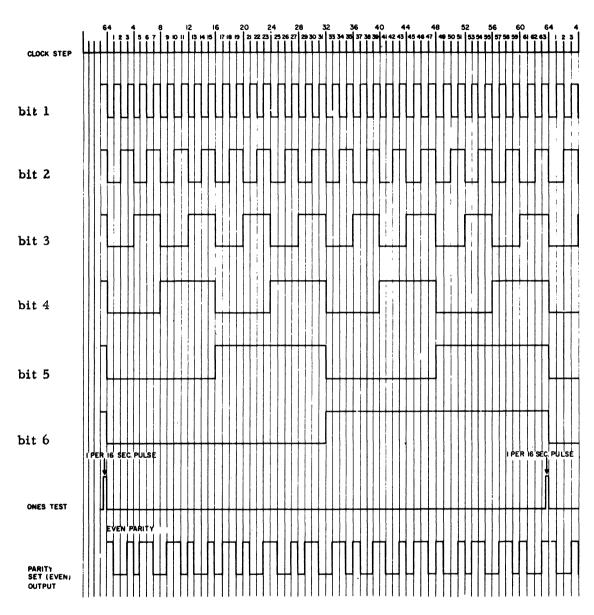

|      | D. Logic Analysis, LRI Clock                                   | 0970         |

|      | E. Logic Analysis, Parity Generator                            | 1030         |

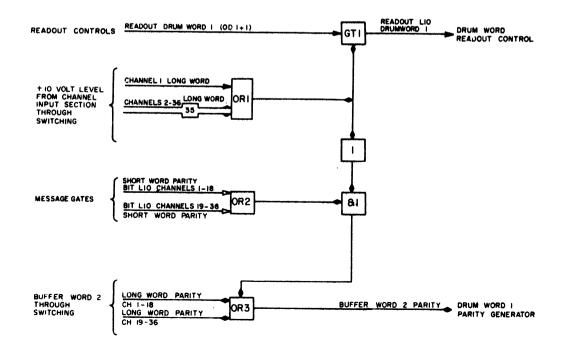

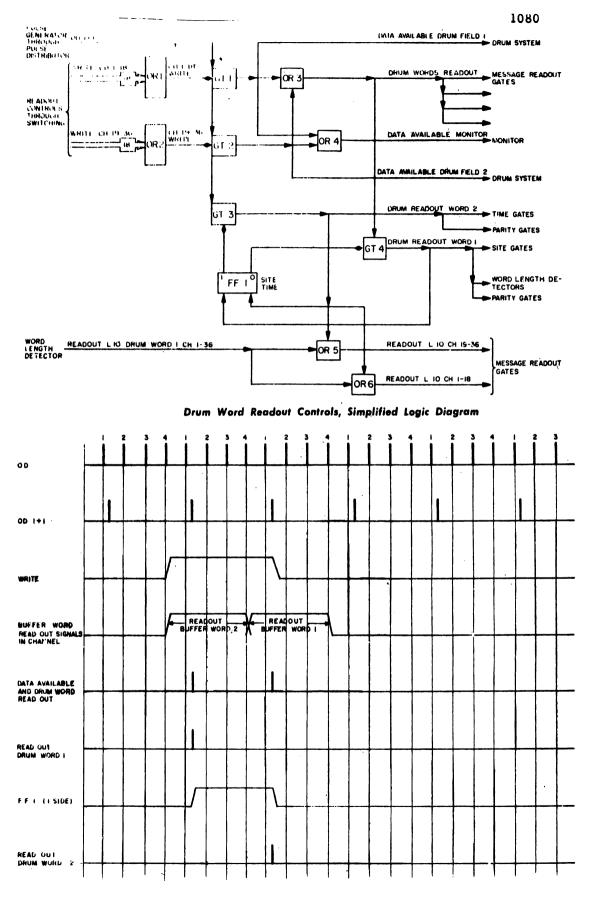

|      | F. Logic Analysis, Drum Word Readout Controls                  | 1060         |

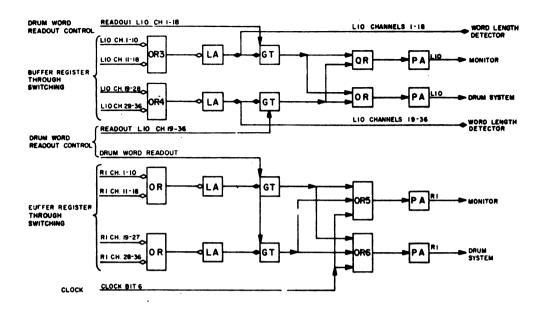

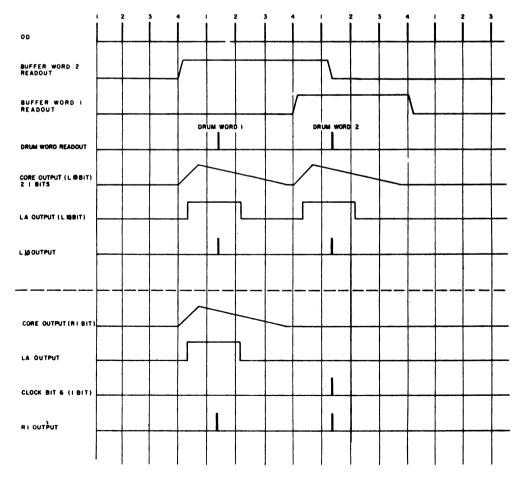

|      | G. Message Gates, Readout Circuitry                            | 1090         |

|      | H. Word Length Detector Circuit                                | 1110         |

|      | I. Readout Alarm Circuit                                       | 1130         |

|      | J. Review of LRI Control Panels on Simplex Maintenance Console | 1130         |

|      | K. LRI Controls and Indications on Duplex Maintenance Cosnole  | 1160         |

|      | L. Summary Questions                                           | 1170         |

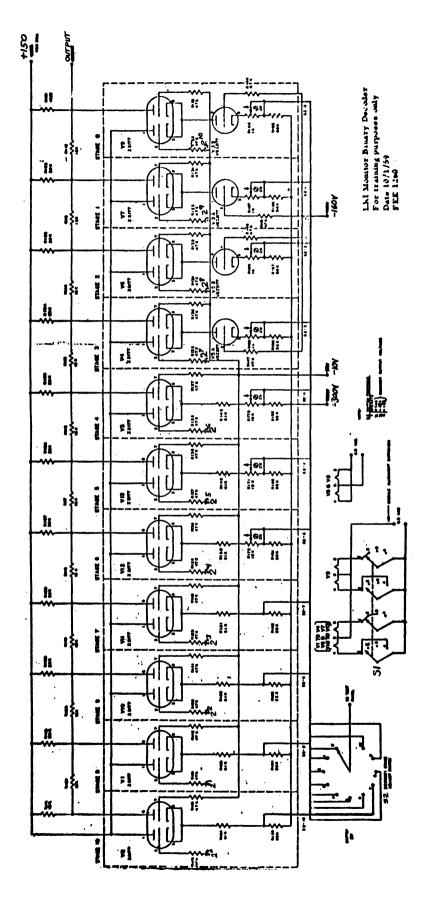

| VI.  | LRI MONITOR, GINARY SECTION (SYSTEMS 17 AND BEYOND)            | 1240         |

|      | A. Introduction to LRI Monitor                                 | 1240         |

|      | B. Block Diagram Analysis of LRI Monitor                       | 1290         |

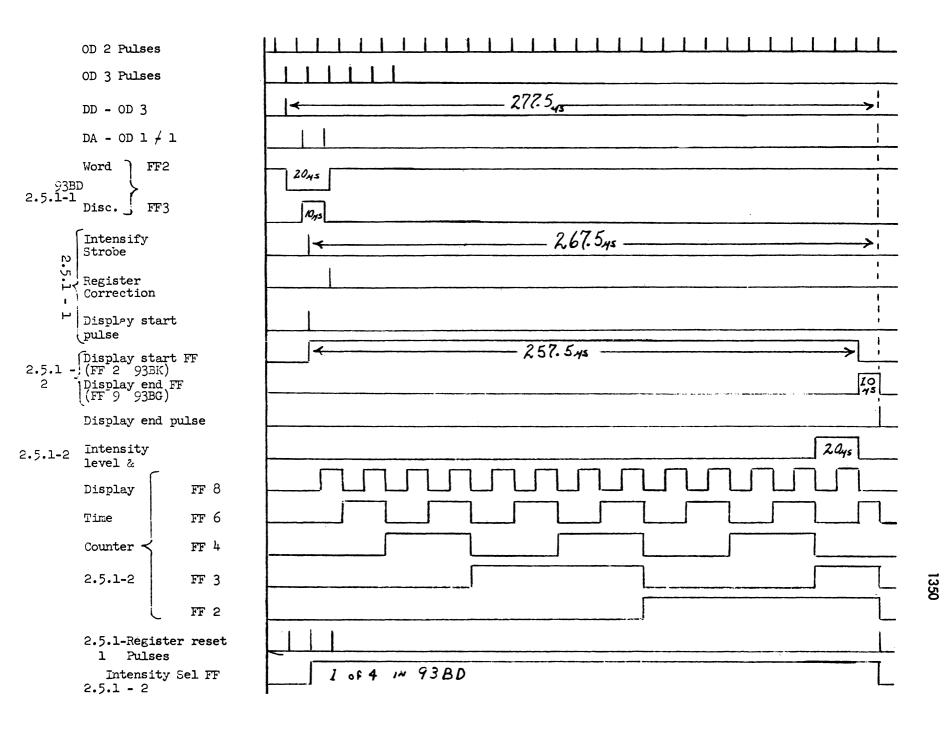

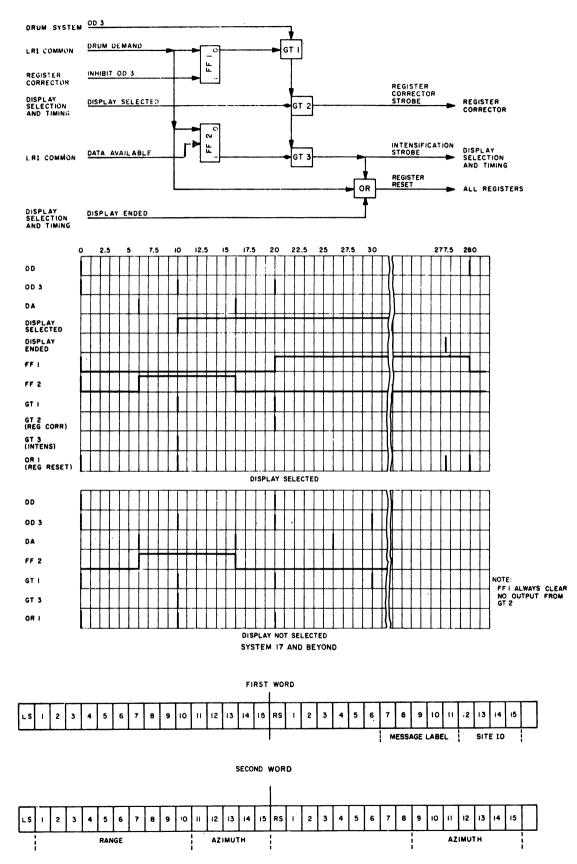

|      | C. Timing and Control of LRI Monitor                           | 1330         |

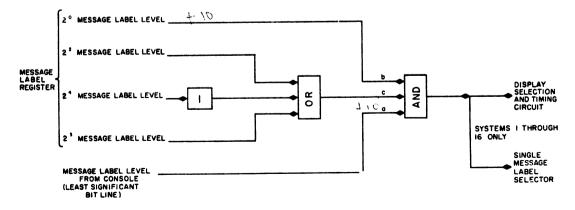

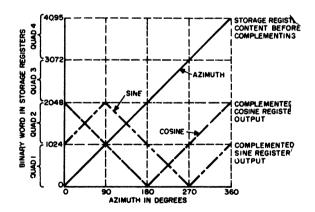

|      | D. Display Selection and Timing Control                        | 1510         |

|      | E. Summary Questions                                           | 1540         |

| VII. | LRI MONITOR, ANALOG AND CONSOLE SECTION                        | 16 <b>40</b> |

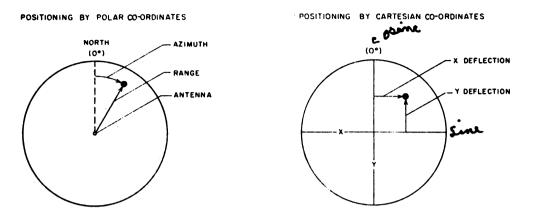

|      | A. Introduction to Analog Section                              | 1640         |

|      | B. Binary Decoder Operation                                    | 1660         |

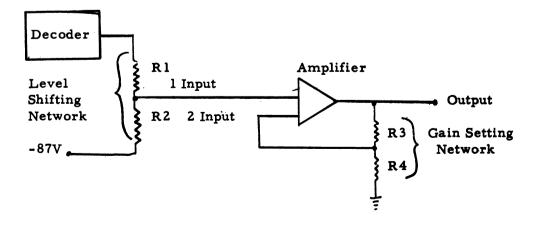

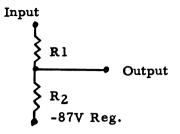

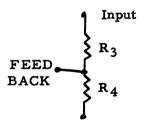

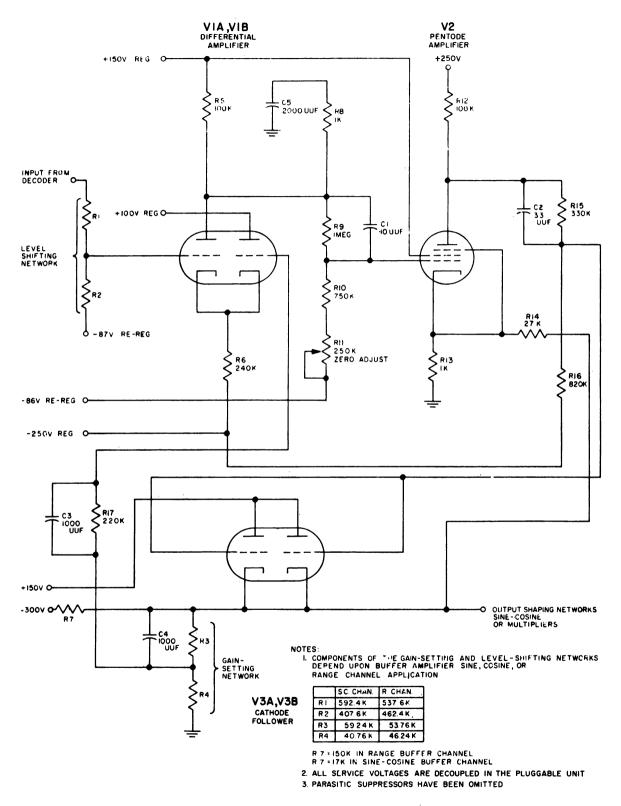

|      | C. Buffer Amplifier Operation                                  | 1710         |

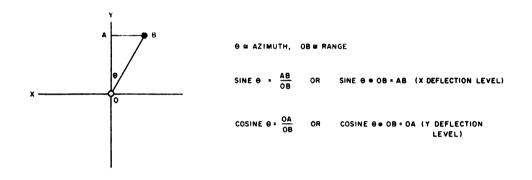

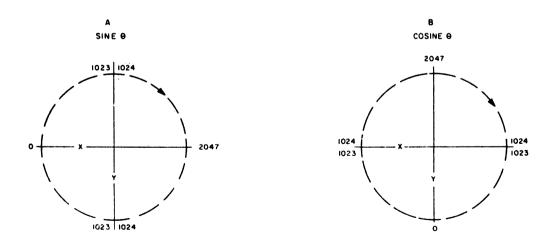

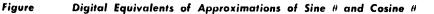

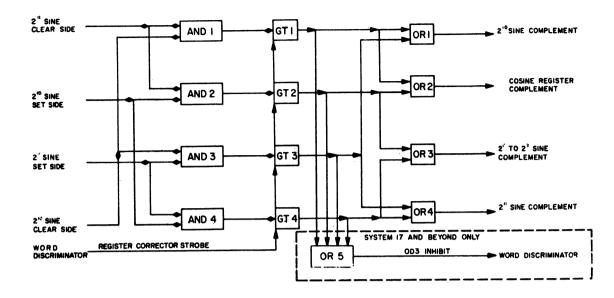

|      | D. Sine Cosine Approximators                                   | 1750         |

|      | E. Multiplier Operation                                        | 1770         |

|      | F. Distribution Power Amplifier Operation                      | 1870         |

|      | G. Alignment Panel                                             | 1870         |

|      | H. Introduction to Monitor Consoles                            | 1890         |

|      | I. Monitor Console Controls                                    | 1900         |

|      | J. Monitor Console Operation                                   | 1920         |

|      | K. Summary Questions                                           | 1970         |

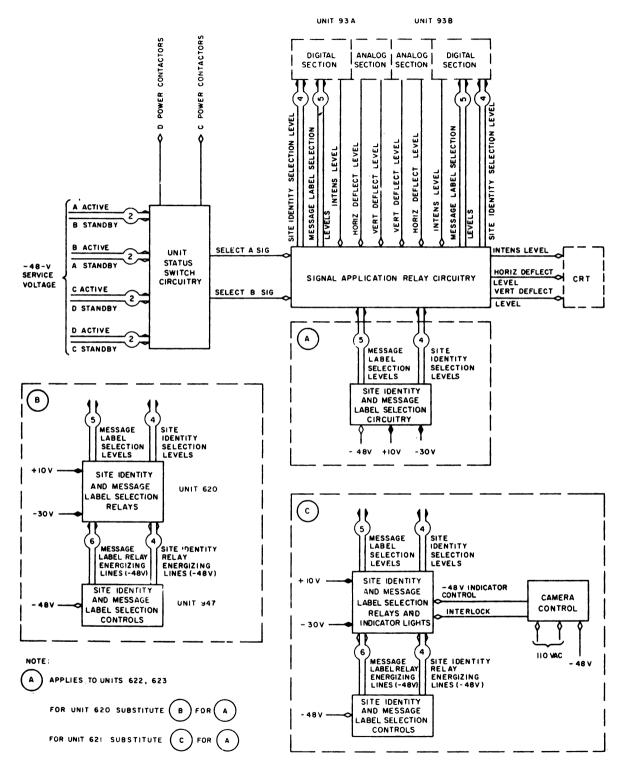

| IX.  | LRI MONITOR, SWITCHING SECTION AND CAMERA CONTROL              | 2010         |

|      | A. Introduction                                                | 2010         |

|      | B. Unit Status Switch                                          | 2050         |

|      | C. Signal Application Control Relays                           | 2070         |

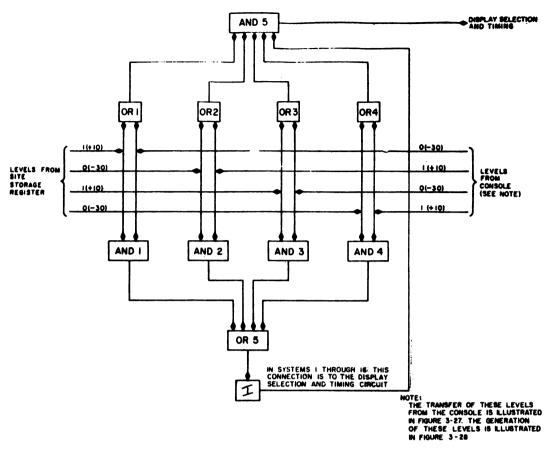

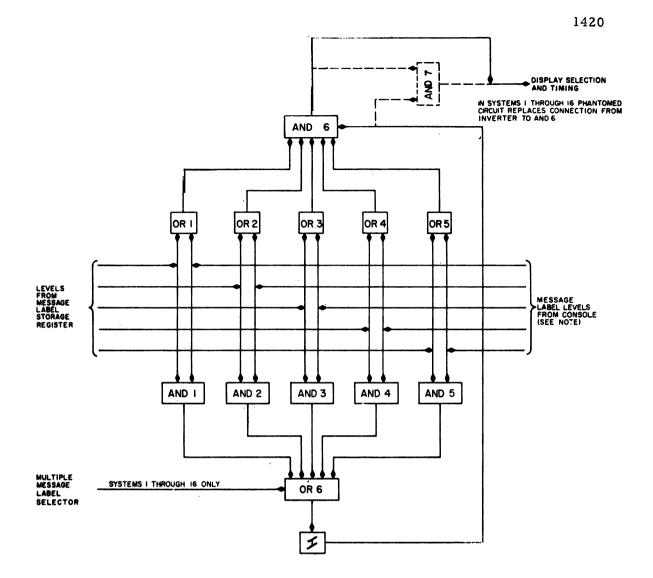

|      | D. Site Identity and Message Lable Selector Circuitry          | 3080         |

|      | E. Camera Control Circuit                                      | 2120         |

|      | F. Summary Questions                                           | 2190         |

# TABLE OF CONTENTS

- I. Introduction to Long Range Inputs

- A. Scope of Course

- 1. This text presents both an introduction to LRI and also a detailed explanation of the LRI equipment.

- 2. A short review of Tape Core Theory is given.

- 3. A detailed presentation of the LRI Monitor frame and consoles, both old and new systems.

- B. Inputs in General

- 1. Introduction

- a. The AN/FSQ-7 Combat Direction Central is a dataprocessing system of the high-speed digital-computer type performing operations on data in binary form. It receives information of the air defense situation continuously, automatically, and in large volume, and must process this information without delay. These requirements call for an elaborate Input System, quite different from anything usually found in data-processing systems. Input Systems in general, and then the AN/FSQ-7 Input System, are discussed below.

- 2. Input Systems in General

- a. Consider first a simple data-processing system such as a desk calculator. This instrument is a slow-speed mechanical, decimal, digital computer. It is capable of accurate and efficient computation, but a means must be provided for the operator to introduce into the machine the problem which he wishes solved. This means is the calculator keyboard. The operator expresses the problem by depressing keys which, in turn, operate the necessary mechanisms in the machine. The keyboard is the input "system" of the calculator.

- b. More elaborate mechanical and electronic-mechanical data-processing systems can process a much greater volume of data in a given time than any desk computer. In fact, data cannot be inserted manually into such a machine fast enough to take advantage of its capabilities, and is therefore transferred to punched cards or punched tapes. This makes possible an accumulation of input data which the computer can then accept at a rate compatible with its data-processing capacity

- Computing machines operating by means of moving c. parts are inherently slow compared to modern electronic computers using pulsed electronic signals. Again, however, the Input System must be adequate to the potentialities of the computer. Modern computers, therefore, transfer data to magnetic tapes or drums or to magnetic core or flip-flop registers: temporary storage devices capable of releasing data to the computer at high-speed regardless of the speed at which the data was originally introduced.

- d. In all of the systems considered above, data is, in a sense, prepackaged; i.e., offered in a form most suitable to the operation of the machine. Under these circumstances a comparatively simple Input System suffices. However, the AN/FSQ-7 Combat Direction Central is not an isolated machine; it is part of the SAGE Complex. This relationship imposes a special set of operational requirements on the Central and on its Input System, which must, specifically, be adequate to the following conditions:

- 1) Input data originates at distant points and is transmitted to the Combat Direction Central over phone lines. The data format and rate of transmission is established by phone-line characteristics, not by the characteristics of the computer.

- 2) Input data is of several types. Each type originates at many sources. The computer must be capable of processing data of all types and from all sources.

- 3) The types and densities of data traffic are determined by the tactical situation, not by computer requirements. The Input System must accept all data, make the necessary discernments as to its validity, process it, store it temporarily, transfer it according to certain priority specifications, etc. The result of these steps, the "product" of the Input System, is analogous to the prepackaged input to more conventional computers. The Input System might also be thought of as a digital computer feeding another digital computer.

- The Input System of the AN/FSQ-7 Combat Direction e. Central receives three types of data:

- Long-range radar input (LRI): data from long-range 1) radar (P) sites. P<sub>hime</sub>

- Gap-filler input (GFI): data from gap-filler sites, supplementing the long-range radar sites.

- Crosstell (XTL): data from other Combat Direction or Combat Control Centrals.

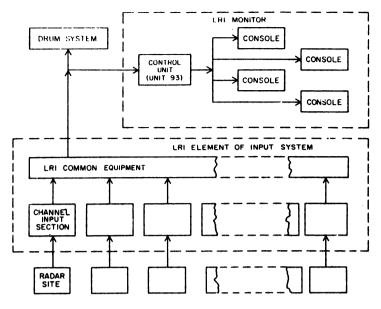

These three types of data are processed by the LRI, and XTL elements, respectively. In addition, the Input System includes a LRI monitor associated with the LRI element and a test pattern generator (TPG) used to test the three elements.

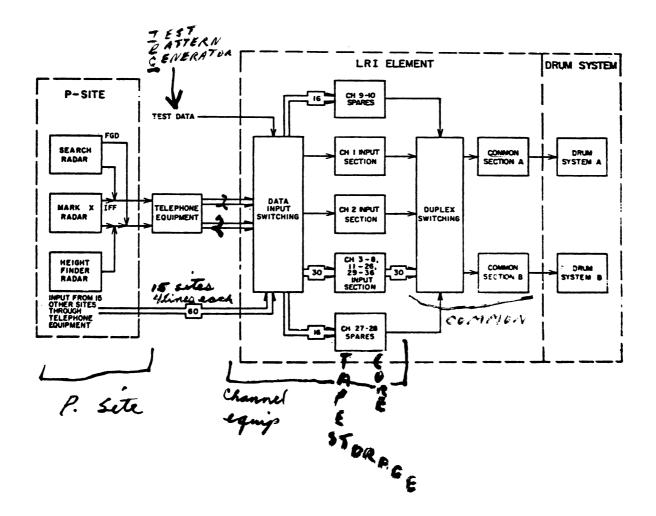

- C. LRI Data Flow

- 1. Block Diagram Over-all

- a. P Site LRI site

- 1) Target detected

- a) Up Graded

- 1) MTI

- 2) FGD

- 3) Mapping

- 2) Message generated

- 3) Message transmitted

- b. Channel equipment

- 1) Message received and processed

- 2) Temporary storage

- c. Common equipment

- 1) Provide transfer path from channel to drum.

- d. Drums Storage

- e. Computer Final processing

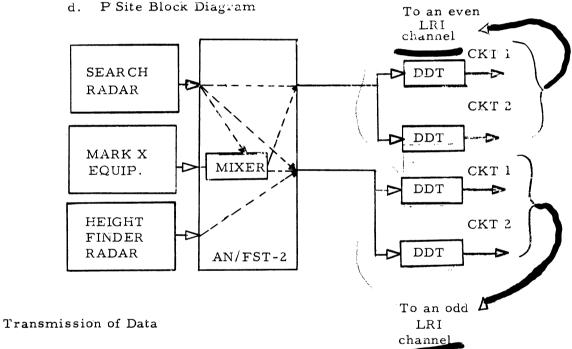

- 2. P Site

- a. Radar equipment

- 1) Search radar (Fine Grain Data FGD) 5 ... 3 P. 2070

- a) Range 200 miles

- b) 1/4 mile increments

- c) Azimuth increments Approx..1<sup>0</sup>

- 2) Mark X equipment

- a) Sends out a signal which when received by aircraft equipped with MK X causes that equipment to return a coded message to the land-based MK X set. The coded message identifies the aircraft as friendly.

- b) The indication of a friendly aircraft is sent to the AN/FST-2 where it is combined with the Search Radar return on that aircraft to make-up a complete MK X Radar message.

- 3) Height finding radars

- a) Two at each P site

- b) Each covers 180° of terrain

- c) Output upon request either Computer or Manual.

- b. Computer equipment AN/FST-2 (at P site)

- 1) Beam splitting

- a) Enables azimuth of search radar to come in 0.1° increments.

- 2) Convert radar returns to binary information.

- 3) Controls transmission sequence of messages over two outputs. One output it sends MK X and Search Radar messages and on the second it sends MK X, Search, and Height Finder radar messages with Height messages having priority.

- 4) Temporary storage awaiting transmission.

- 5) Combines MK X inputs with Search Radar to give a MK X Radar message.

- Transmission equipment DDT's с.

- 1) Digital Data Transmitters

- a) Amplitude modulation of a carrier

- 2) Phone Lines

- Monoages sent over two phone lines Ulinia a) 2 ser channel for reliability - Circuit 1 and 2.

- b) May be sent over one line only to a site if data from this radar is necessary during an emergency. Then the phone line would be Circuit 1.

D.

- 1. Repetition rates

- "Timing" pulses a.

- 1) Every 1/1300 sec. - 770 usec.

- Continuous transmission 2)

- "Data" pulse ь.

- 1) Random

- Represents a "l" 2)

- Co-incident with and in place of a timing pulse 3)

- 4) Twice the amplitude of timing pulses.

- c. "Sync" pulse

- 1) Represents a timing control.

- 2) Every 52/1300 sec. 40 M Sec.

- 3) Transmitted whether data is present or not.

- 4) Three times the amplitude of timing pulses used to synchronize in our equipment, also in tel. equipment to set AGC level.

- 2. One P site supplies information for 2 LRI channels normally a pair (an odd and even).

- a. Two different messages may be transmitted simultaneously.

- b. One of the two channels will receive any of the three message types odd channel.

- c. Other channel will not receive HF messages other two message types only - even channel.

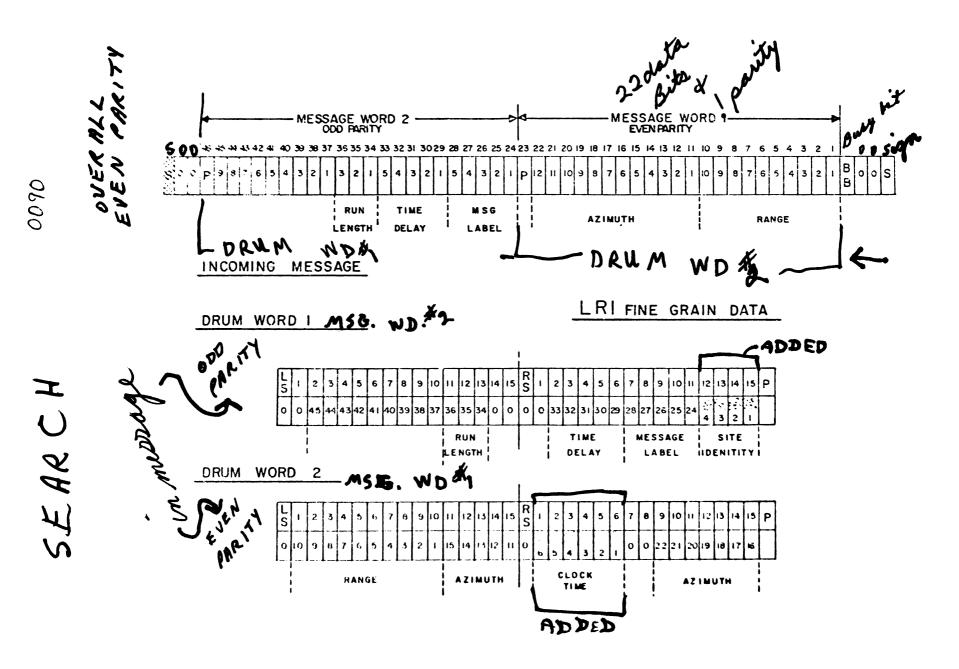

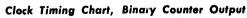

- E. Phone Line and Drum Words

- 1. Introduction to LRI Messages, Fine Grain Data message, Height Finder message and Mark X message all have the following makeup:

- a. Total of 52 bits

- b. Sync first

- c. Two zeros

- d. Busy-bit indicates a message being transmitted always a 1 - no message, no busy bit.

- e. Twenty-two data bits

- f. Parity count of first 22 bits (even)

- g. Twenty-two data bits

- h. Parity count of second 22 bits (odd)

- i. Two zeros

- j. Sync of next message

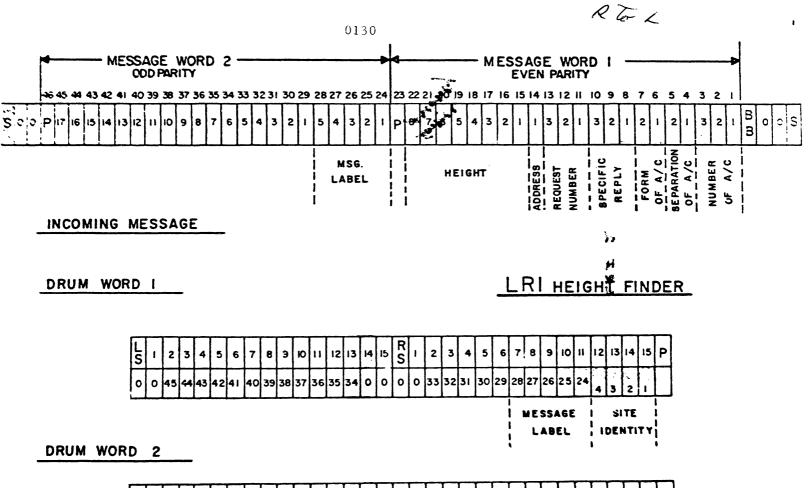

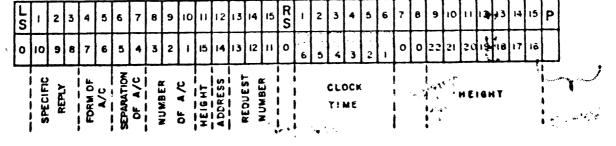

- 2. Introduction to LRI Drum Words

- a. Drum word one

- 1) Parity odd

- 2) Contains site ID plus data from message word 2.

- b. Drum word two

- 1) Parity odd

- Contains clock time plus data from message word 1.

- c. Input word terms explained

- d. Site identity bits

- 1) R12-R15 of Drum Word One

- 2) Binary coding identifying source of message.

- e. Clock Time Bits

- 1) R1-6 of Drum Word Two

- 2) Binary count indicating the time at which the message was written on the drum.

Analysis of LRI Search Data

- a. Long-range search radar data is upgraded at the radar site by these processes: moving target indicator (MTI), fine-grain data (FGD), and manual mapping.

- b. The MTI apparatus endeavors to eliminate all radar returns except those produced by a moving object.

- c. Fine-grain data apparatus uses the technique of beam-splitting to achieve a much higher degree of azimuth resolution when locating a target than is possible with conventional radar. (Beam-splitting notes the azimuths at which the first and last radar returns are received from a target during one sweep and then computes the average or middle azimuth. The disadvantage of beam-splitting -- the time delay between initial detection of a target and the reporting of the averaged azimuth -- is overcome by noting the duration of the delay in the LRI message). Fine-grain data apparatus also tends to reject noise by establishing minimal criteria for an acceptable target.

- d. Finally, manual mapping is used to eliminate unwanted radar returns which have survived the other filtering techniques. In manual mapping, targets are presented on a display screen and an operator uses an opaquing

fluid to blot out those targets or areas which are of no tactical significance. Un-opaqued target indications are picked up by a photoelectric device, and generate descriptive messages for transmission to the Combat Direction Central. These messages contain the following information:

- 1) Target range from the radar set

- 2) Target azimuth with respect to true north from the radar set.

- Time delay between initial detection of target and transmission of message.

Run length, indication of size of target or existence of multiple targets at reported location.

- 5) Message label which identifies the message source as search radar rather than IFF or height finder.

- e. It is the function of the LRI common and channel equipment to change the message makeup into the two drum words.

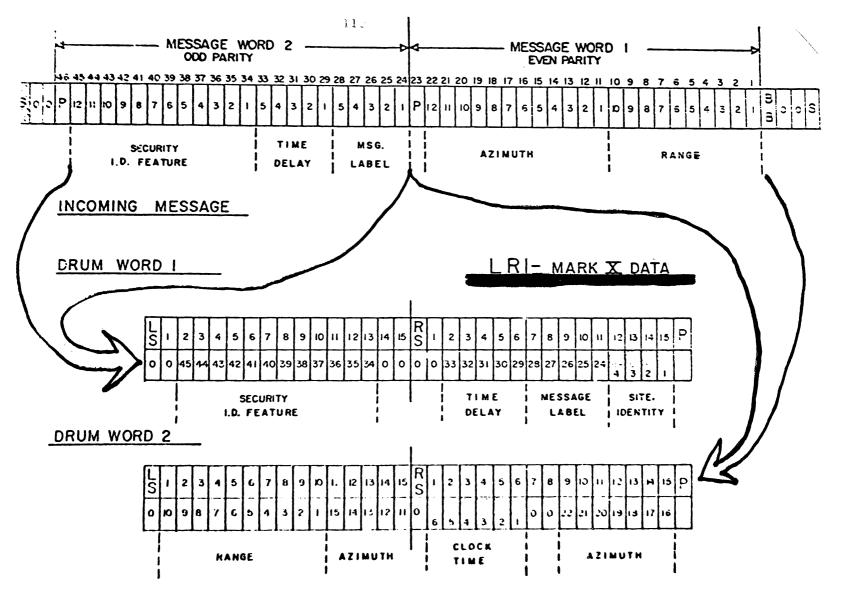

- 4. Analysis of Mark X Data

3)

- a. The MK X IFF radar beacon enables radar systems to distinguish between friendly and hostile aircraft. Friendly aircraft carry transponders (receivertransmitters) which reply in a prescribed code when interrogated by a ground interrogator (transmitterreceiver). The response is usually displayed alongside the radar return, indicating to the operator that the target is friendly.

- b. The MK X IFF radar beacon sends messages to the Note: Refer to Direction Central which contain the following Page 0110 information in binary form: for Message Layout

- 1) Target range from the radar set

- 2) Target azimuth with respect to true north from the radar set.

Note: Refer to Page 0090 for Message Layout

- Time delay between initial detection of target and transmission of message, up to 16 seconds, with an accuracy of 1/4 second.

- 4) Security identification feature (SIF), if used.

- 5) Message label which identifies message source as IFF rather than search radar or height finder.

- c. In order to obtain a simultaneous report of the MK X IFF response with the radar report of the target, the MK X set and its associated radar are synchronized, when sweeping, in azimuth and range. This synchronization allows the MK X IFF to generate range and azimuth information on friendly targets by noting the radar azimuth when a response is received and the time between interrogation and response. The IFF range and azimuth data is in FGD form.

- d. The LRI channel and common equipment will convert the message into the two drum words illustrated on Page

- 5. Analysis of Height Finder Data

- The height-finder radar equipment associated with а. a P-site supplies target-height data on specific targets to the Combat Direction Central in response to requests received from the Central. The heightfinder radars are semiautomatic; that is, the radar antenna is automatically positioned to the azimuth of the target for which height information is requested. In addition, the range cursor on the range-height indicator is automatically positioned at target range. The last measured or estimated height is also supplied to the height-finder operator to aid in identifying the target. New target height determined by the heightfinder is automatically encoded and sent to the DC as part of the height-finder request. The height-finder message contains the following information in binary form:

| 1) | New target height.                         | Note:       | Refer to |

|----|--------------------------------------------|-------------|----------|

| 2) | Predominate formation of multiple targets. | Page        | 0130     |

|    |                                            | for Message |          |

|    |                                            | make-       | up.      |

- Separation between aircraft in multiple targets.

- 4) Number of aircraft in multiple targets.

- 5) Request number.

- Address identifying which of two heightfinders is replying.

- 7) Special reply (if any).

- 8) Message label which identifies the message label as height-finder rather than search radar or IFF.

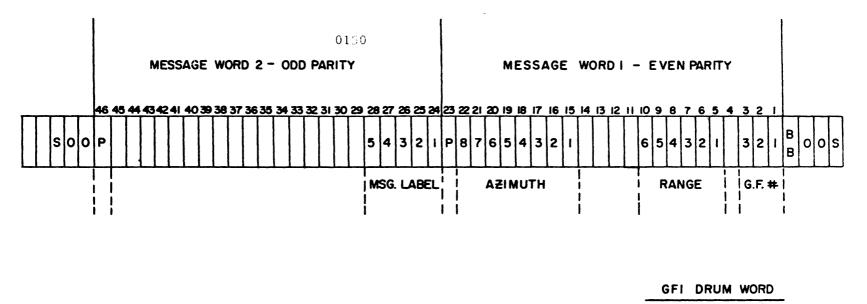

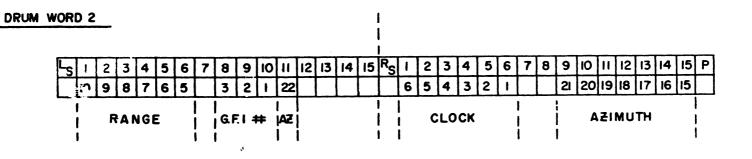

- 6. Analysis of GFI Data

- a. The mapping of the gap filler radar will be done at the "P" site. The gap filler illformation will then be fed into the A/N FST-2 where it will be sent to the LRI, input equipment.

- b. The incoming GFI message has a 52 bit format, as in all messages coming to the LRI element. The message consists of the gap filler number, range and azimuth of the target and message label.

- c. Maximum of six GFI sites per "P" site.

- F. Physical Layout of Unit Number 41

- 1. Channel equipment

- a. 36 channels

- 1) Numbered 1 thru 36

- 2) 9, 10, 27 and 28 are spares

- b. Two channels per module

- 2. Common equipment

- a. Two commons

- 1) Common A for Computer A

- 2) Common B for Computer B

- b. Three modules per common.

Note: Refer to **Page** 0150 for Message make-up

Channels 1-18 supply data for LRI-1 field a. Channels 19-36 supply data for LRI-2 field ь. CURES Channel 9 is spare for 1, 3, 5, 7, 11, 13, 15 & 17 c. Channel 10 is spare for 2, 4, 6, 8, 12, 14, 16 & 18 d. Channel 27 is spare for 19, 21, 23, 25, 29, 31, 33 & 35 е. Channel 28 is spare for 20, 22, 24, 26, 30, 32, 34 & 36 f. 4. Module Assignment for Unit 41 LRS 2 LRI 1 Module Module Channel Channel Ν 1-2 19-20 - 21-22 3 - 4 $\mathbf{P}$ 5-6 - 23-24  $\boldsymbol{C}$ R 7-8 D S 25-26 E 9-10 т - '27-28 - 11-12 х 29-30 Y 31-32 - 13-14 -- 15-16 33-34 м 17 - 183B G F н v Common A Common B U w

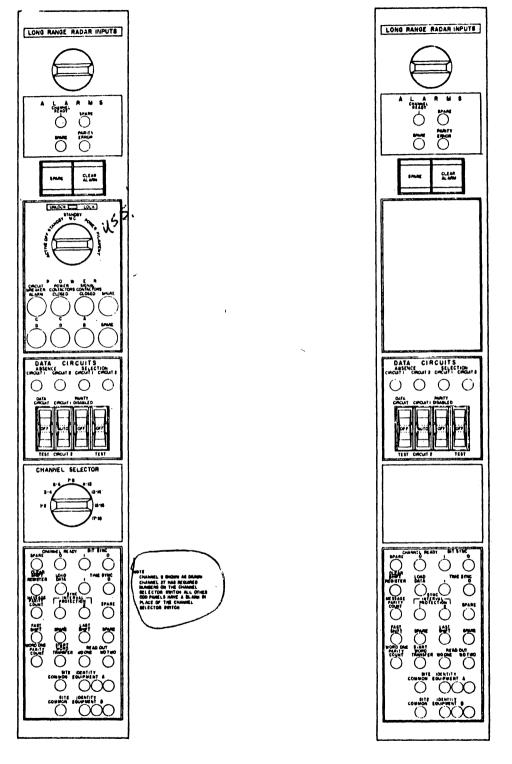

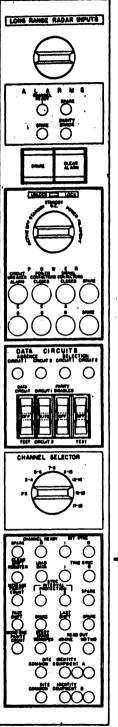

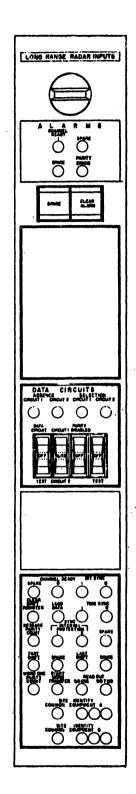

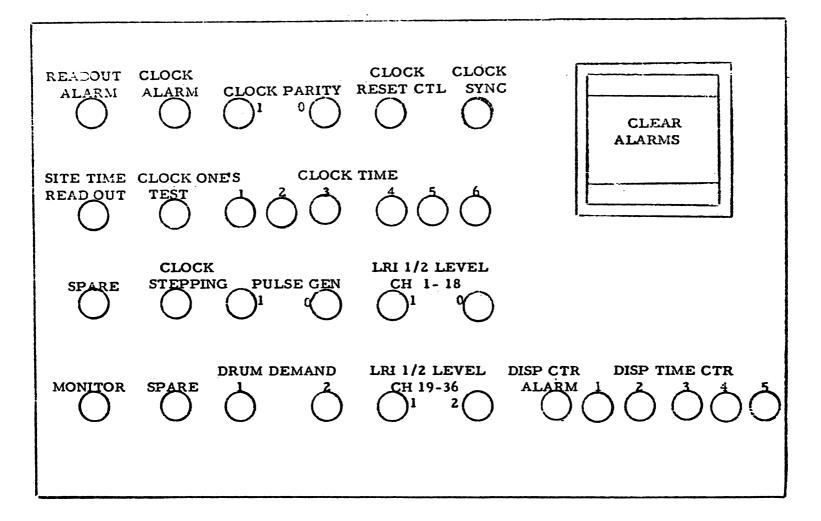

G. LRI Controls on Simplex Maintenance Console UNIT HT

- 1. Function of Simplex Maintenance Console

- a. Maintenance control of simplexed portions of Input System.

- b. A control panel provided for each channel of inputs.

- c. Control of input test pattern generators.

- 2. Long Range Inputs

3.

Channel assignment

- a. One panel for each 36 channels.

- b. Bottom half of modules C thru H.

- c. Each module in Unit 41 (LRI) contains two channels.

DRUM WORD I 8 9 10 11 12 13 14 15 <sup>R</sup>S 2 3 8 9 10 11 12 13 14 15 P 2 3 4 5 6 7 5 6 7 4 1 ۲s Ł SITE IDENT. MSG. LABEL

0150

- d. Status of both channels in a module is controlled by the Unit Status switch on the Odd Channel control panel.

- e. The Spare channels always replace a channel pair: that is, one LRI module.

- 3. Long Range Panel Controls

- a. Associate indicator or control with panel location.

- b. Include the following:

- Channel Ready set alarm will not be cleared by "Clear Alarm" - there will be no audible alarm. The Channel Ready 1 neon is now in the upper left-hand corner of the Alarms and no longer in the bottom neon panel.

- Channel Ready switch allows a readout protection circuit to be tested. Located in the position of the blank switch in Data Circuits panel.

- c. Flip-flop neons will not be discussed at present. They will be discussed later when their function is known.

- H. Introduction to the Long-Range Radar Input Monitor

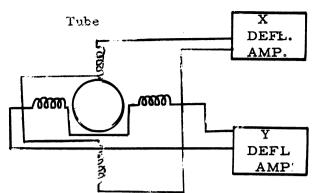

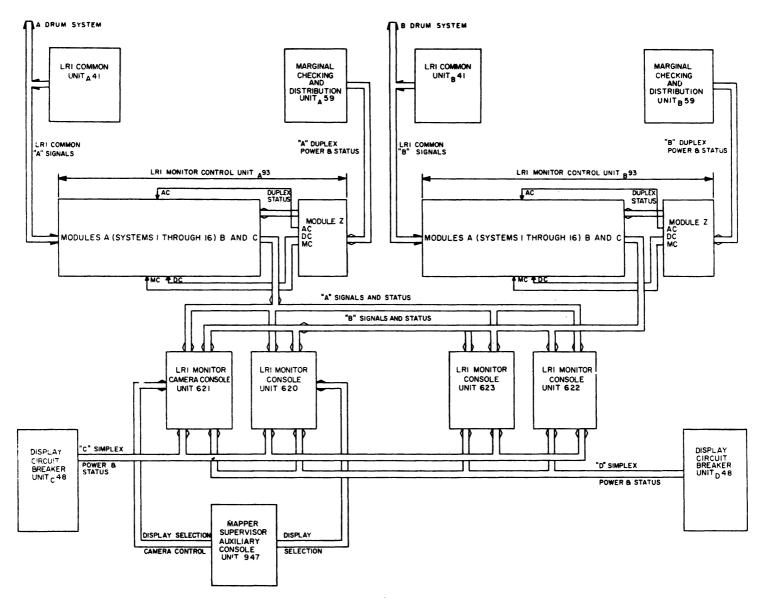

- LRI messages in transit to the Drum System are also made available to the LRI monitor. The LRI monitor provides the means for selecting LRI data for display. It thus enables operating personnel to make preliminary analyses of LRI coverage and data independently of the Central Computer, and it assists maintenance personnel to evaluate the operational efficiency of the Input System.

- 2. The LRI monitor consists of three display consoles, units 620, 622, and 623, and the LRI monitor control unit, unit 93, which contains the circuits that serve all three consoles. LRI messages are selected for display by means of keyboard controls at the consoles or, in the case of units 620 and at an auxiliary control console, unit 953. The following selection principle is employed. Each processed LRI message contains a message label indicating whether the message contains search, MK X IFF, or height-finder data, and a site identity code (added in the drum input section) indicating the source of the data. An operator selects a message or messages for display by using the keyboard controls to specify the message label.

LRI Control Panel, Odd and Odd-Spares

LRI Contro<mark>l Panel,</mark> Even and Even-Spar**es**

and site identity of interest to him. The target information in the selected messages is then presented, in PPI form, on the cathode-ray tube (CRT) of the display console at which, or for which, the display was requested.

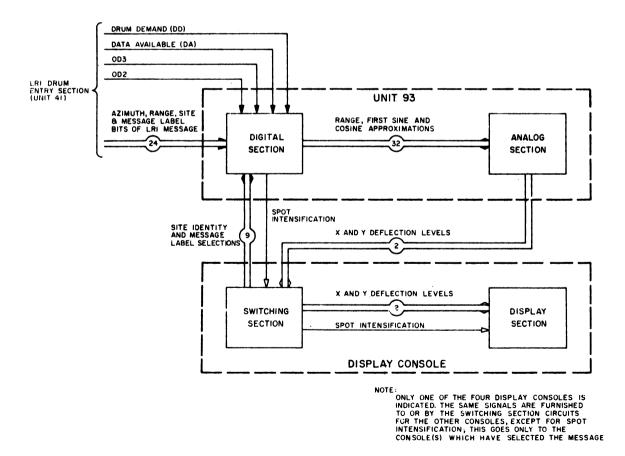

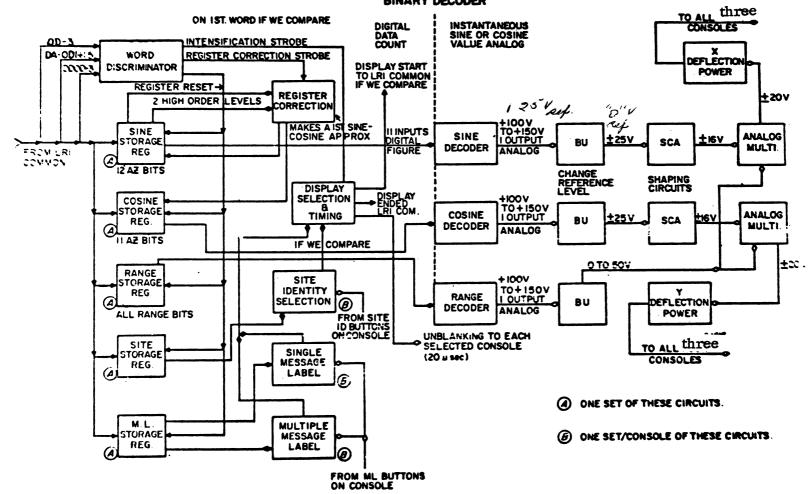

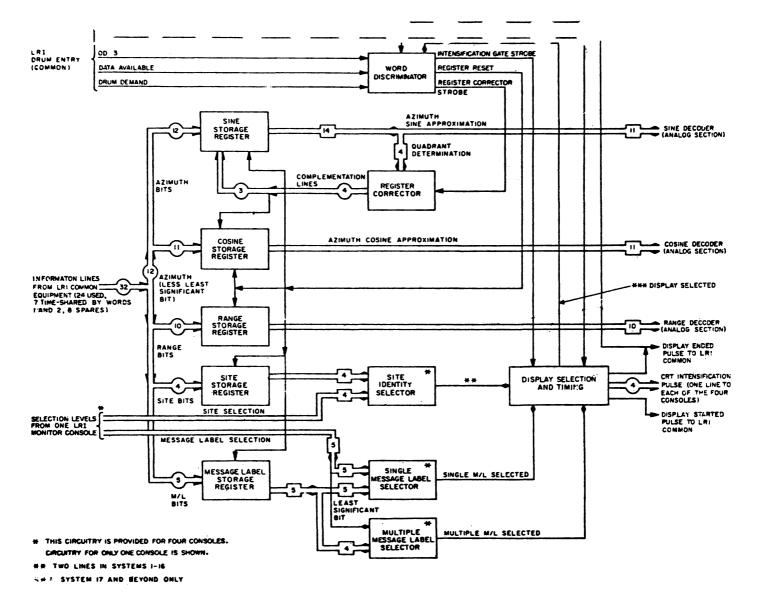

- 3. Functionally, the LRI monitor consists of four sections: digital, analog, display, and switching. The digital section accepts the LRI message, determines whether it has been selected for display by comparing its message label and its identity with requests expressed at keyboard controls, and begins the processing of the target information in selected messages. The analog section transforms the digital target information into analog form. The display section presents the target information in a PPI display on one or more of the CRT screens. The switching section contains the circuitry used to express message selections and to associate the consoles with either the active or the standby duplex machine.

- I. Introduction to the Test Pattern Generator

- 1. General

- a. Test Pattern Generator is provided to generate test signals simulating the phone-line inputs to the Input System. The equipment is essentially three test pattern generators serving the LRI, XTL, and GFI elements. By means of a switch associated with a channel, signals from the appropriate TPG may be substituted for the phone-line inputs to the particular channel by providing a known and controlled input to the various channels, the TPG offers the means of thoroughly checking the operation of an element during installation and subsequent to it.

- 2. Test Signals

- a. The test signals generated by the LRI TPG go out on three lines: timing, sync, and data. The timing signal is a continuous 1,300-cps sine wave. The sync and data signals are individual sine waves generated in synchronism with the timing signal, together they form the message, the composition of which may be varied manually or by computer command.

- J. Input Switching

- 1. Introduction

- a. A block diagram illustrating the flow of LRI data from a P site to the LRI drum field is shown on Page 0200 The data flow for all 16 P sites is identical to that illustrated for the single P site.

- b. A radar P site contains three radar units, each originating different information:

- A long-range search radar set producing target coordinate information in fine-grain data (FGD) form.

- 2) Mark X identification friend or foe (IFF) radar with a selective identification feature.

- 3) A semiautomatic height-finder radar producing height-above-ground data for each target.

In normal operation, as shown on Page 0200 each P-site sends data to two LRI channels. The two channels will be an odd and even pair such as channels 1-2, 3-4, 29-30, or 35-36. The data sent to one of the two channels will be search radar and Mark X information. All three types of messages are sent to the other channel. The output of the P-site intended for an odd channel is sent to two digital data transmitters (DDT's) and is then transmitted over separate phone lines to the Central. Therefore, an odd channel receives identical information over two input lines (designated circuit 1 and circuit 2). Similar circuitry exists for the even channel to receive information.

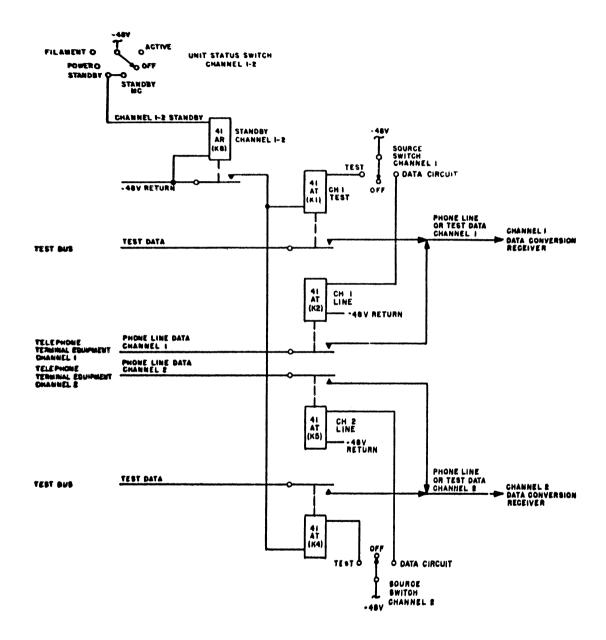

#### Input Data Switching

The data-input switching circuit selects either telephone line data or test signals from the LRI TPG as the inputs to be directed to each LRI channel. Page 0210 shows the relay switching circuits involved in selecting the input for channels 1 and 2. The relay switching circuits for any other pair of channels (except for spare channels) is the same as that shown for channels 1 and 2. For this reason, only channels 1 and 2 are discussed here.

# LRI INFORMATION FLOW, SIMPLIFIED DIAGRAM

When the channel 1 source switch (located on the simplex maintenance console) is set to the DATA CIRCUIT position, relay  $41AT(K_2)$  is energized and the telephone line inputs are connected to the data conversion receiver in channel 1. The telephone line inputs and test data inputs consist of data, sync, and timing lines, but, for simplicity, shown on Page 0210 as a single line.

When relay 41AT(K1) is energized, test data is connected to the data conversion received in channel 1. In order for this relay to be energized, two conditions must be met: (1) The unit status switch for channels 1 and 2 must be in the STANDBY or STANDBY MC position so that standby relay 41AR(K8) is energized. This relay controls the -48V return line for channel 1 test relay 41AT(K1) and channel 2 test relay 41AT(K4).

2) The source switch for channel 1 must be in the TEST position so that the control voltage will be applied to the channel 1 test relay.

The purpose of the standby relays is to prevent test signals from being sent to the active computer. The inputs for channel 2 are selected in the same manner as described above for channel 1.

- d. Spare-Channel Switching

- Spare-channel switching is the operation of electrically substituting a pair of spare channels (channels 9 and 10 or channels 27 and 28) for a pair of channels within a group. It is accomplished by setting the CHANNEL SELECTOR switch (on the ODD spare channel control panels, simplex maintenance console) to the numbers of the channels to be replaced. Three functions are thereby performed.

- a) The alternate telephone circuit for the replaced channel is connected to the spare channel.

- b) The telephone-terminal-equipment indicators of the spare channel are substituted for these indicators on the replaced channel.

- c) A write level generated in a spare channel is applied to the site can for the replaced

channel. A write level causes readout of site identity by a site can to associate the source of a message with the message data. In spare-channel switching it is necessary to associate the site identity related with the replaced channel with message data processed by the spare channel.

- 2. Logic Analysis of Input Switching

- a. Requirements to be met:

- 1) The two channels of module must have same status.

- 2) Test data cannot be fed to an "Active" channel.

- 3) Each channel can select data independent of its sister channel.

- 4) A channel being replaced by a spare also has its sister channel replaced by a spare.

- K. Summary Questions

- 1. How many different types of messages are used in LRI? Name and discuss each type briefly.

- 2. How many azimuths in the LRI circle?

- 3. What is the size of an LRI increment (range and azimuth)?

- 4. How many binary bits are necessary to make up the maximum LRI azimuth count? How many bits are necessary to make up the maximum LRI range count?

- 5. What is the difference between FGD and Mark X Azimuth and Range counts?

- 6. At what frequency does LRI data arrive at the DCR's?

- 7. Are sync bits received by the LRI channel equipment when no data is being received? When consecutive messages are being received at what rate do the sync bits arrive?

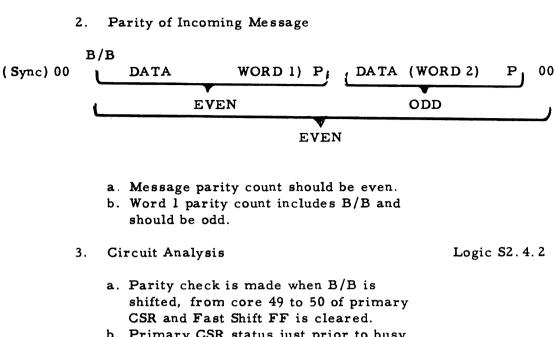

- 8. Explain the parity make up of the two message words to result in the desired telephone line parity. Will this parity need to be changed before data is written on the LOG Drum?

- 9. If consecutive FGD messages are being received by an LRI channel, what is the time elapse between the last data bit of one message and the first data bit of the following message? (Consider parity as data)

- 10. Does a Height Finder message contain Range and Azimuth?

- 11. What is meant by "Run Length?"

- 12. Give the bit length of each type of LRI message. How many of these bits actually contain information for the computer?

- 13. What is the LRI unit number?

- 14. What is the maximum number of LRI channels for one computer? Which channels are spares?

- 15. Is LRI simplexed or duplexed equipment?

- 16. What LRI information is written on LRI Field #1? LRI Field #2?

- 17. How many phone lines are used to transmit data from one LRI site to the computer? How many of these are spares?

- 18. Channel 19 can transfer data to which of the 4 LRI drum fields?

- 19. The 10th data bit received on the phone line goes to which bit of which drum word for a FGD message? MK X message? HF message?

- 20. Which incoming data bits indicate type of message?

- 21. Which channels can be replaced by Channel 28?

- 22. Referring to Logic S2.4.1

Make a point to point wiring diagram of "Sync" line from Channel #13 on alternate phone line #11 to channel #9 input.

Specify which relays must be energized.

List the conditions necessary to pick each of the relays.

Ignore channel 10 and channel 14 relays as well as all other channel relays.

- II Review of Tape Core Theory

- NOTE: Tape core theory and special circuits used with tape cores was covered in Basic Circuits and also in the GFI Course. Refer to Basic Circuit Manuals or the MRD Manual for additional circuit information.

- A. Introduction to Tape Cores

- 1. A special circuit.

- 2. A magnetic storage device capable of storing one bit.

- 3. Various applications require minor alterations.

- 4. Models used in LRI will be discussed here.

- B. Physical Description

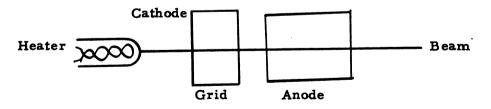

- 1. A small bobbin (ceramic) wound with a magnetic alloy tape.

- 2. Coils of wire wound through center.

- 3. Number of turns per winding and number of windings varies with application.

- C. Theory of Operation

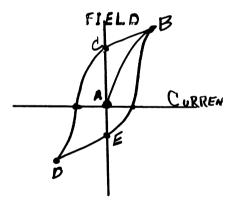

- 1. Hysteresis Loop

- a. Originally at Point A.

- (1) No current.

- (2) No field.

- b. Current applied to winding of + polarity.

- (1) Field goes to B.

- c. Current Removed.

- (1) Current to 0.

- (2) Flux to C slight decrease from B.

- d. Current Reversed.

- (1) Large change of field.

- (2) Changes polarity.

- (3) Field to point D.

- e. Current Removed.

- (1) Current to 0.

- (2) Flux to E slight decrease from D.

- f. Current Reversed.

- (1) Large change of field.

- (2) Changes polarity.

- 2. Squareness of loop depends upon ability of core to retain magnetism.

- a. When at point C a "1" is stored.

- b. When at point E a "0" is stored.

- 3. Core is primed by passing a current through a "prime" winding.

- 4. Core is sensed for a "1" by passing a current through a "reset or drive or shift" winding which switches the core to "0".

- 5. When core goes from a "1" to a "0", a sizeable change in flux takes place.

- 6. If core was already at "0", flux change is slight.

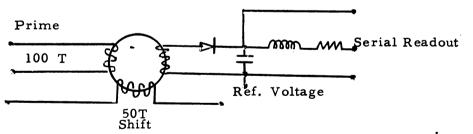

- D. Core shift Model C

Parallel Readout

- 1. Definition

- a. A core shift (CS) is a logic circuit which possesses two stable states of magnetization and is used as a storage device.

- b. There are 15 models of CS's utilized in AN/FSQ-7 and -8 equipments. The most significant differences between each model are in the number of windings used and the number of turns in each winding. The basic CS contains three windings: an add-in (or read-in) winding, a readout winding, and a drive winding. All other CS's contain a fourth winding, the reset winding. In addition, several models contain a fifth winding, either inhibit or feedback, depending on its application in a circuit. Basically, the principles of operation for all CS's are identical. For this reason, only the basic CS is described in detail below.

- 2. Prime Winding

- a. Input is from various sources.

- (1) Another cCS (serial readout.

- (2) A core prime.

- (3) Cathode follower.

- b. Suitable current for a duration of time are main requirements.

- 3. Shift Winding

- a. Normally from a CSD.

- b. To shift bit to next core 2.5 usec. pulse.

- c. To reset cores 7.5 usec. or longer.

- 4. Output Winding

- a. Output voltage developed across capacitor.

- b. Diode prevents capacitor discharging through output winding.

- c. Reference voltage normally used is 15V.

- d. Parallel readout used to condition a GT.

- e. Serial readout used to prime another core.

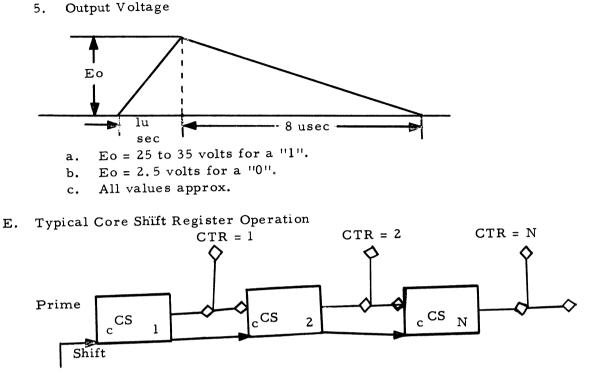

- 1. Core 1 is primed all other cores  $\doteq 0$ .

- 2. First Shift

- a. Clears core 1.

- b. Primes core 2.

- c. CTR = 1 output pulse.

- 3. Second Shift

- a. Clears core 2.

- b. Primes core 2.

- c. CTR = 2 output pulse.

- 4. Noth Shift

- a. Clears core N.

- b. Primes next core if there is one.

- c. CTR = N output pulse.

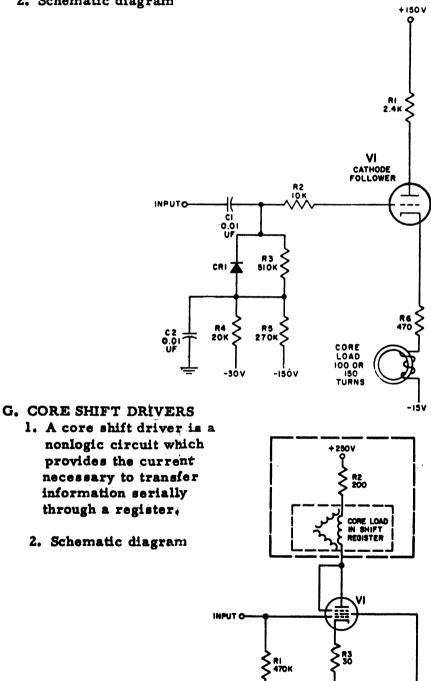

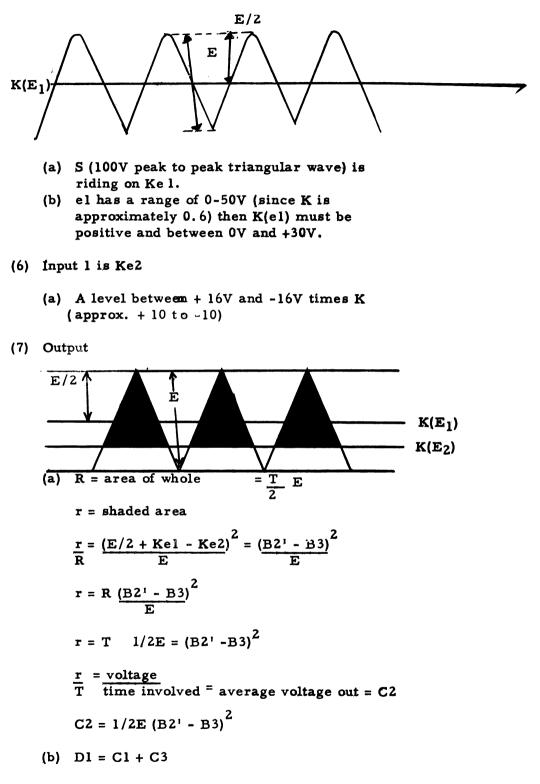

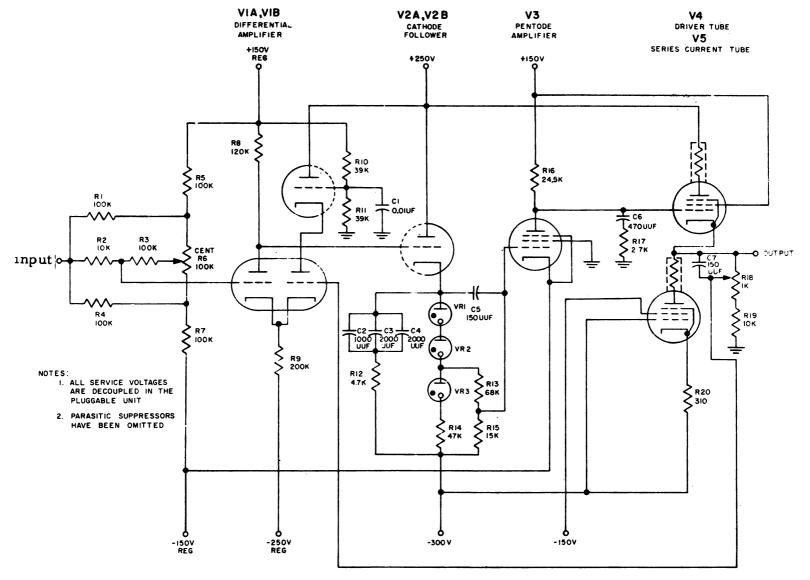

- F. CORE PRIME, MODELS A, B, C, AND D

- I. A core prime (CP) is a nonlogic power-amplifying circuit which provides a high current output pulse utilized to set a core shift to the 1 state.

- 2. Schematic diagram

NOTES L SERVICE VOLTAGES ARE DECOUPLED IN THE PLUGGABLE UNIT 2. PARASITIS SUPPRESSORS HAVE BEEN OMITTED

+150V

- 30V

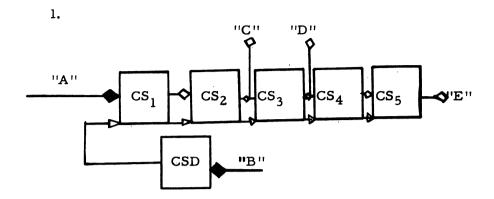

H. Summary Questions

Consider the above simplified core register. Assume  $CS_1$  is primed for each "1" bit at input "A" and a shift pulse is applied to input "B" every 770 miscroseconds. The message to be shifted through is 473<sub>8</sub>. Data bits are primed into  $CS_1$  in correct sequence. Answer the following questions.

- a. Will the levels at "C", "D" or "E" be up during the fifth shift pulse?

- b. The output at "E" will equal what octal number?

- c. The first "1" bit is shifted out at "E"; how many milliseconds after it entered at "A"?

- d. The last "l" bit will give an output at "D"; how many microseconds after the first data bit was read out at "E"?

- e. If a reset pulse is applied to "B" 12 milliseconds after the first shift pulse, what will be the outputs at "C", "D" and "E" ("1" or "0")?

## III. LRI Channel Operation

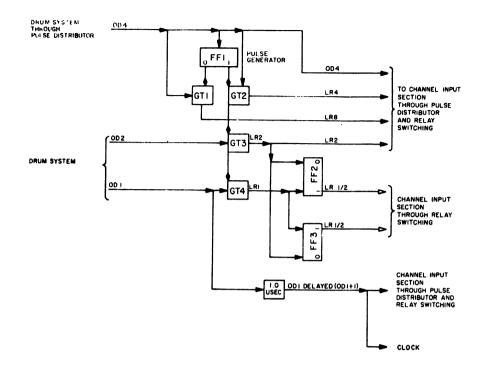

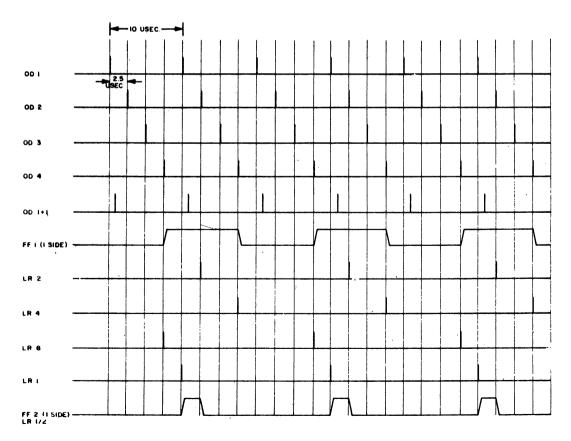

- A. LRI Pulse Generation Circuitry

- 1. Purpose

- a. Distribute drum timing pulses to channel equipment

- b. Generate LRI pulses and distribute to channel equipment.

- 2. Block Diagram of Pulses

3. Circuit Analysis

Logic A2.4.6

- a. Inputs

- 1. OD1 (12D)

- 2. OD2 (9D)

- 3. OD3 (12A)

- 4. OD4 (12D)

- b. Outputs

- 1. OD1-D (11E) 2. OD4 (12E) 3. LR2 (9E) 4. LR4 (9E) 5. LR8 (10E) 6. LR 1/2 (8E)

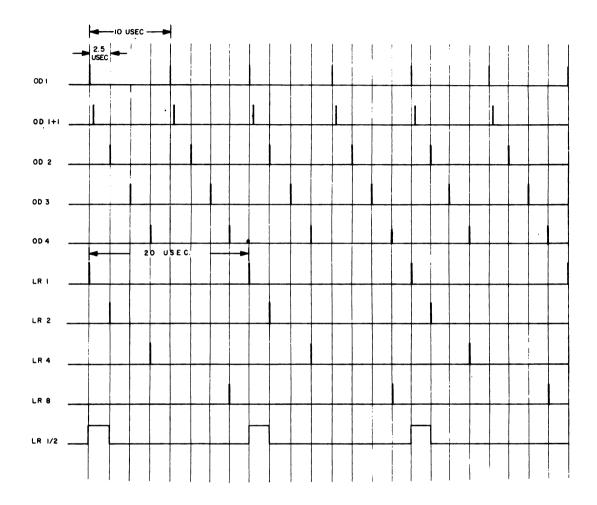

Note: Page 0350

Relation of LRI pulses to drum OD timing pulses, timing chart.

NOTE: LR pulses occur every 20 usec, due to the complementing of the pulse generator FF (10D) by the OD-1 pulses.

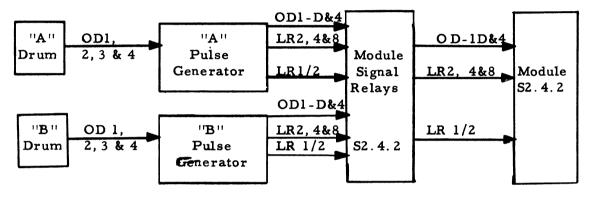

- B. LRI Channel, Block Diagram Analysis

- 1. Simplified diagram of LRI channel circuitry.

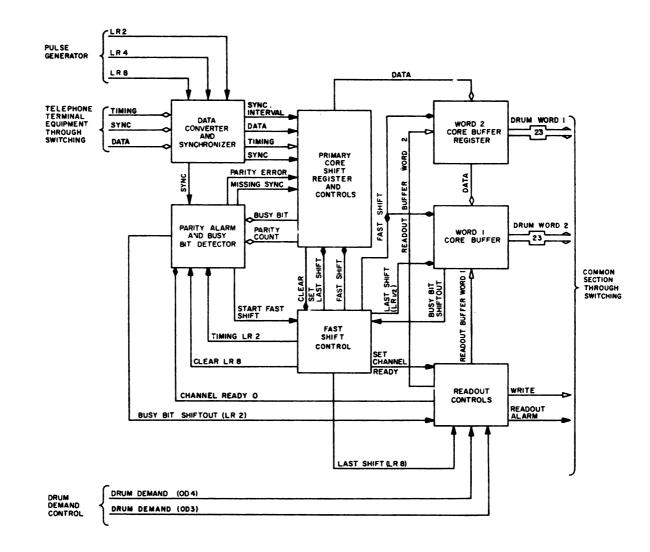

- 2. Data Converter and Synchronizer

- Convert incoming phone line signals to a. standard pulses and levels.

- Synchronize to LRI timing. b.

- Generate necessary pulses to perform c. channel operations.

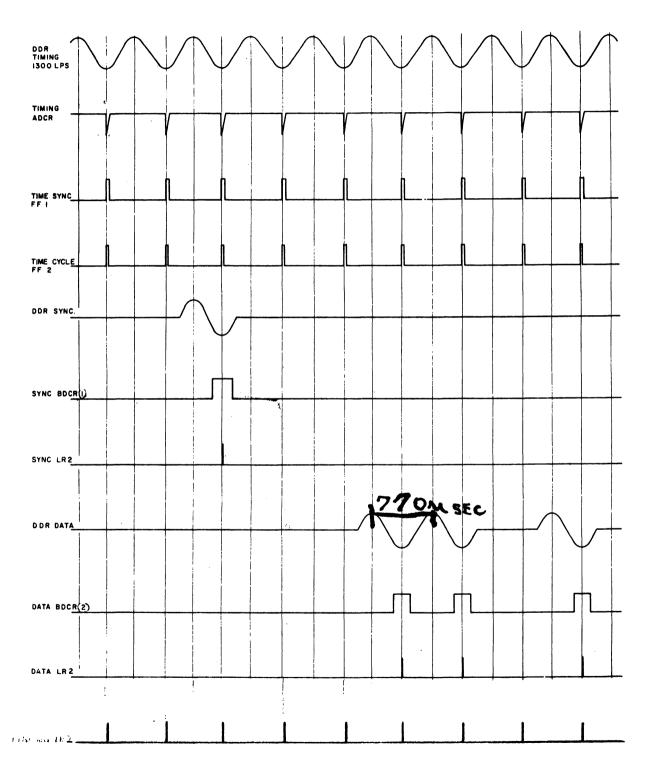

- d. Refer to timing chart.

Note: Page 0380

# Data Conversion and Synchronizer, Timing Chart

- 3. Primary Core Shift Register

- a. Store message as it is received bit by bit.

- b. Isolates incoming data from Word 1 & 2 core buffer storage to allow sufficient time for previous message to be written on drum.

- c. Signals the Fast Shift if a complete good parity word is received.

- d. Sends outputs to Parity Check.

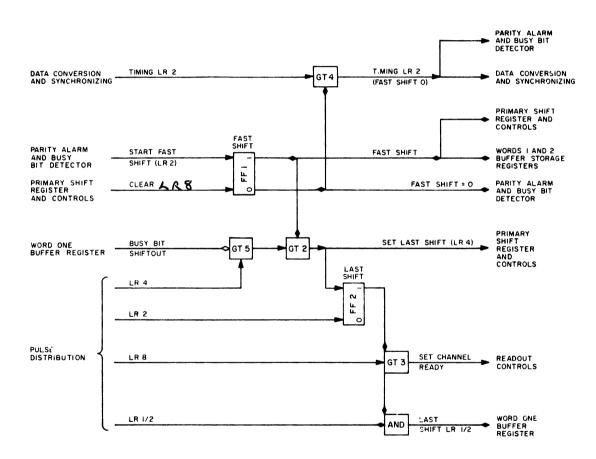

2.4.2 11-14A 41AG+ 41AF

### 4. Parity Check

- a. Check parity of entire message.

- b. Check parity of Word 1 of message.

- c. Prevent acceptance of a message with either or both parity errors.

- 5. Fast Shift Control

- a. Rapidly shift message from primary core shift register into word 1 & 2 core buffer storage after a complete good parity message is stored in Primary CSR.

- b. Generates one more shift (last shift) for word 1 Core Buffer after the Fast Shifts.

2,4,2

- 6. Word 1 & 2 Core Buffers

- a. Store entire incoming message that has been received serially.

- b. Maintain storage until data is written on drum.

CS 31

Ļ

CS30 THROUGH CS12

<del>7</del> 7

CS 11

cs 10 R9

RIO THROUGH RIS

(19)

LI THROUGH LB

19

LIO BB FAST SHIFT CONTROLS

2.4.2

- 7. Readout Controls

- a. Control transfer of message from channel to drum.

- b. Provide synchronism between channel common equipment and drum

C. Logic Analysis, Data Converter & Synchronizer

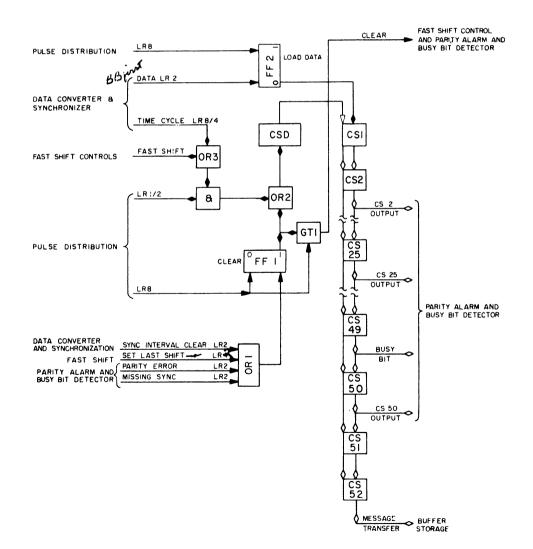

Logic S2.4.2

- 1. Note that Logic S2.4.2 shows two separate but identical LRI channels.

- 2. The two channels read out to common equipment through one set of relays.

- 3. The two channels (odd and even) are in one module and normally receive their inputs from one "P" site.

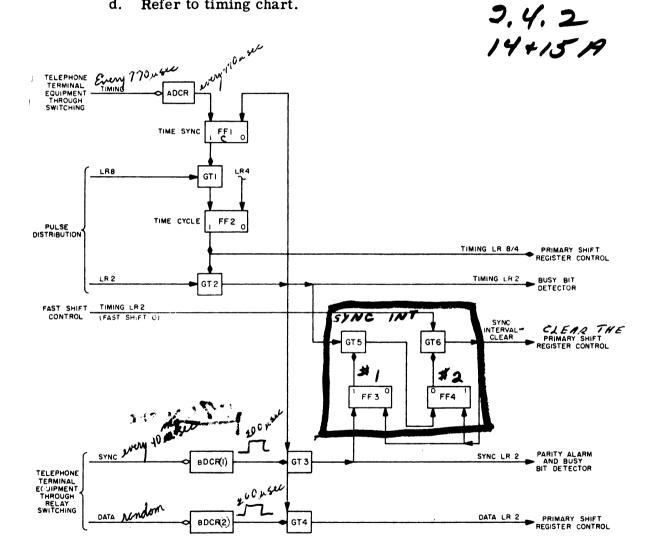

- 4. Over all operation of data converter and synchronizer.

- a. The data converter and synchronizer converts the timing since wave inputs into timing-levels, and sync or data sine wave inputs into standard pulses, which are synchronized with LRI timing (LR) pulses for use within other circuits of the LRI channel input section. The data converter and synchronizer also provides a pulse to the primary shift register control to cause clearing of the primary shift register after a sync bit has been received by the data conversion receiver DCR 1.

- b. The three classes of signals contained in an LRI message (timing, sync, and data) are sent from the telephone terminal equipment to the LRI element over separate lines. Relays in the input switching section permit the data converter and synchronizing circuit to accept messages from either the telephone line or the test bus. Each type of signal is applied to a data conversion receiver (DCR). The timing is applied to the model A DCR which converts the 1, 300-cycle sine wave to a nonstandard pulse. The sync and data signals go to model B DCR's whose outputs are standard levels (200 usec duration) which occur whenever there is an input signal.

- The timing pulse from the DCR sets FF1 which C. conditions GT 6 and permits the succeeding LR 8 pulse to set FF1 in 41AE. The time cycle FF conditions GT 5 (41AE) and permits the succeeding LR 2 pulse to clear the time sync FF. The clearing of the time sync FF deconditions GT 6 and prevents passage of LR 8 pulses until the next timing pulse is received. The clearing of the time cycle FF (by an LR 4 pulse) establishes the duration of the timing level (LR 8/4) at 10 usec. The timing LR 8/4 level is fed to the primary shift register control to aid in the generation of shift levels for the primary shift register. The timing LR 8/4 level is also applied to GT 5 which passes on LR 2 pulse during each timing cycle. This timing LR 2 pulse is sent to the busy bit detector circuit. The timing LR 2 pulse applied to GT 9 generates a sync LR 2 pulse when a sync bit is received by the sync DCR. For each data 1 bit received via the data DCR GT 5 passes a data LR 2 pulse to the primary shift register control to cause a 1 data bit to be loaded into the primary shift register.

- d. The sync LR 2 output is also applied to the "sync interval 1" FF (41AJ). Conditioned GT 5 passes the succeeding timing LR 2 pulse to clear the "sync interval 2" FF (41AH), conditioning GT 4. The next timing LR 2 (and fast shift FF cleared) pulse passes GT 4 and is sent to the primary shift register control to cause clearing of the cores of the primary shift register. The output of GT 4 also restores  $cFF_3$  and cFF (41AH and AJ) to their original states.

<u>NOTE:</u> Step 40 is accomplished only every sync input. It clears the primary shift register for the incoming data word.

- D. Logic Analysis, Primary Core Shift Register and Controls

- 1. Over-all Operation

- a. The primary core shift register control circuit serially receives the data of an LRI message from the data converter and synchronizer circuit at the rate of 1, 300 bits per second. The data is loaded into the primary register. After the complete LRI message has been received and inserted into the primary register, the data is transferred to the word 1 and 2 core buffer registers at the rate of 50,000 bits per second. The main purpose of the primary register is to permit a message to be received by the channel without disturbing the previous message stored in the word 1 and word 2 core buffer registers. This provides enough time for the message stored in the buffer registers to obtain access to an LRI field on the LOG drum. The time that a message can remain in the buffer registers without being disturbed by the next message is approximately equal to the time it takes to load the primary core shift register.

- b. The first data bit of an LRI message is always a 1 (busy bit); therefore, the first data LR 2 pulse generated from the busy bit clears the load data FF. The flip-flop remains cleared until an LR 8 pulse is applied to the set input. Consequently, FF 7 is cleared for 15 usec (LR 2 to following LR 8) each time a 1 data bit is received. The clear output of cFF 7 primes (inserts a 1) the first core shift (CS 1) of the primary register. The next LR 8/4 is applied through the OR and to the AND circuit. This then passes a single LR 1/2 pulse. The 2.5 usec

LR 1/2 level is applied through the 68 OR to the CSD, which then shifts the contents of each core of the primary register to the adjacent core. The next data bit is then inserted into CS 1 in the same manner as described above. When a data bit is a 0, CS 1 is not primed by the clear output of FF 2 because the data LR 2 pulse is not generated. The next shift level causes the 0 in CS 1 to be shifted to CS 2. Each shift level causes each bit to be inserted. The process continues in this manner until all the data bits are contained in the register. The shifting of the register is done at a 1,300 shifts per-second rate since an LR 1/2 level is applied to the CSD only during a timing LR 8/4 level.

The 49th shift level occurs after 49 data bits have been C. inserted into the primary register. As the 49th shift level occurs, the busy bit is transferred from CS 49 to CS 50, and the transfer is also sensed on the output line connected to the output of CS 49 (AGT<sub>2</sub> - 41AH). When the busy bit is transferred from CS 40 to CS 50, the output is a 1 which is sent to the parity alarm and busy bit detector circuit. A sync pulse received simultaneously with a busy bit output from CS 49 is an indication that the primary register contains all the data bits of a message. The fast shift control circuit is signaled that a complete LRI message is stored in the primary register, and the fast shift level is generated. The fast shift level, applied through the 33OR (41AF) permits LR 1/2 levels to shift the register. The LR 1/2 shift levels occur every 20 usec. (fast shift). Each data bit is transferred to the buffer storage.

on the output line of CS 52. The output of CS 50 is also sent to the parity alarm and busy bit detector circuit to aid in generating a signal, when the busy bit or sync bit is missing from the message.

- d. The outputs of CS 2 and CS 25 are sent to the parity alarm and busy bit detector circuit where they are used to check the parity of the message words.

- e. When the clear FF ( $_{C}$  FF  $_{0}$ , 41AF) is set by anyone of the four inputs, it will provide  $a \neq 10V$  level to the CSD. The  $\neq 10V$  level will cause the CSD to supply current to the reset or shift winding of the primary core shift register. The current will continue until FF 1 is cleared at LR 8. Therefore, the reset current will continue from LR 2 for the sync-interval-clear, parity-error, and missing-sync, until LR 8 (15 usec in duration). For the set last-shift LR 4 input to the clear FF, the reset current will have a duration of 10 usec. At LR 8 time, when cFF5 is clear, GT 5 (41AJ) is strobed, and a pulse is generated to clear the parity FF's and to clear the fastshift FF.

- 2. Special Circuits in Core Shift Register

- a. Power Cathode Followers

- 1. Model A

- a) Input-standard level

- b) Output-standard level

- c) Added information is Basic Circuit Manual.

- 2. Model GG

- a) Input-standard level

- b) Output-standard level

- c) Theory of operation

- d) Note AC coupling prevents possible damage to CSR's if a level were applied due to a circuit failure.

- b. Core Shift Driver Model C

- 1. Input

- a) Standard level

- (1) 2.5 usec. shift

- (2) 7.5 usec.  $\neq$  reset

- (3) Max. rep. rate 50KC

- 2. Output

- a) Approx. 230 m amps

- 3. Theory of Operation basic circuit manual

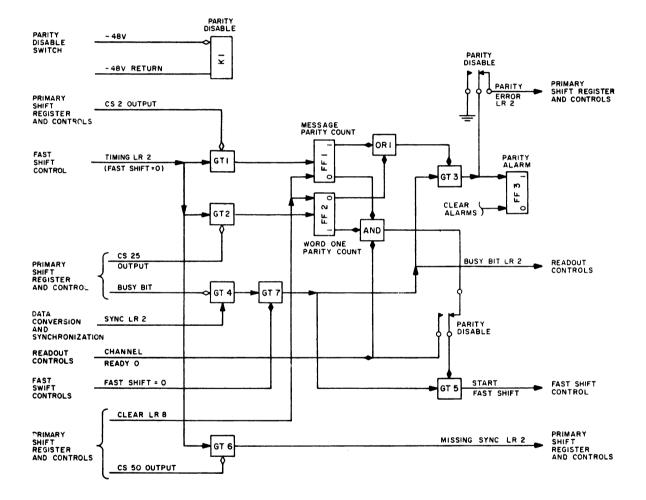

- E. Logic Analysis, Parity Alarm and Busy Bit Detector

- 1. Purpose

- a. Checks the parity of the incoming LRI message.

- b. Checks the presence of the busy bit and sync bit as the message is processed in the primary shift register.

- c. Sends a start-fast-shift signal to the fast shift control circuit, if the message parity is correct and the sync bit is present when the busy bit reaches a predetermined point in the primary shift register (an indication of a good message).

- d. Sends a parity-error pulse to the primary shift register and controls, and lights a parity error neon in the alarm section of the LRI control panel if a parity error occurs.

- e. Sends a pulse to the readout control circuit to generate an alarm, if the buffer storage registers contain a message awaiting transfer to the Drum System.

## Long Range Inputs and LRI Monitor

b. Primary CSR status just prior to busy bit output to check Fast Shift = 0 and if so to check parity.

$$\begin{bmatrix} 1 & 2 & 22 \\ 1 & 2 & 3 & 4 \end{bmatrix} \begin{pmatrix} 1 & P & 22 \\ 25 & 26 & 27 & 49 & 50 & 51 & 52 \end{pmatrix}$$

**BITS 2 21 BITS 2-21** OF WORD 2 OF WORD 1

c. Parity check.

- 1) Parity count correct.

- a) Both counts right.

- Start fast shift if channel ready b) **FF** is cleared.

- Check for "readout alarm". c)

- 2) Readout alarm

- Good message received- parity, B/B a) & Sync when Fast Shift = 0.

- b) Channel ready set means previous message is still in word 1 & 2 buffers. Should have been written by now.

- c) Alarm generated on duplex maintenance console.

- d) Message is not fast shifted but instead cleared out with next sync interval output, previous message remains intact.

- 3) Parity count incorrect.

- a) Either or both counts in error.

- b) Generate parity alarm on simplex maintenance console.

- c) Message not fast shifted but cleared out immediately.

- d. Parity Disable.

- 1) Controlled from Simplex Maintenance Console.

- Relay can be energized only if channel is in.

- a) Standby or

- b) Standby MC

- Allows message to be written on drum regardless of parity count.

- **NOTE:** The parity of the incoming message is checked by analyzing the number of data bits in the overall message word and the number of data bits in the first message word for an odd-even count. If the message parity is correct  $_{C}FF6$  in 41AH is complemented to the cleared side when all of the data bits (/B/B) have been received.

Correct parity also causes cFF2 (41AC) to be complemented to the set condition when the complete message has been received by the primary shift register. If both parity counts are correct and the channel ready FF, in the readout control circuit is cleared, the LR 2 pulse received from GT2 (41 AH) is sent to the fast shift control circuit to initiate a fast shift of the message from the primary shift register into the buffer storage. If either the message parity count or the word one parity count is incorrect, GT7 (41AH) is conditioned and passes a parityerror pulse.

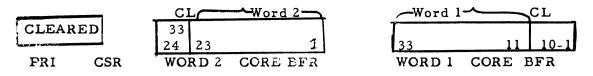

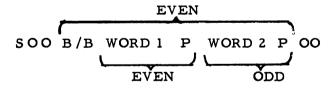

- F. Logic Analysis, Word 1 & 2 Core Buffer and Fast Shift Control

- 1. Core Buffer Description

- a. Each is a 33 core CSR.

- b. Data is fast shifted in from primary CSR in serial form.

- c. At completion of shifting.

- 1) Word 1 cores 32-10 of word 1 core buffer will contain word 1 data.

- 2) Word 2 cores 23-1 of word 2 core buffer will contain word 2 data.

- 2. Purpose of Fast Shift Control

- a. Furnishes a fast-shift level which allows the fast shifting of the message from the primary shift register into the buffer storage ( $_{e}CF7, 84 AJ$ ).

- Furnishes a last-shift LR 1/2 level to the word one buffer register (<sub>e</sub>CF2A-41AJ).

- c. Sends a pulse to set the channel ready FF in the readout control circuit (GT 3-41AJ).

- d. Sends a set last-shift LR 2 pulse to the primary shift register and controls to initiate a clear level for the register (GT6-41AJ).

- e. Sends a fast-shift = = 0 level to the parityalarm and busy-bit detector circuit to gate the busy-bit LR 2 pulse (GT6-41AK).

- f. Sends a timing LR 2 (fast-shift = -0) to the parity alarm and busy-bit detector, and to the data conversion and synchronizing, circuits as controlling signals in these circuits (GT7-41AK)

- 3. Circuit Operation

Logic S2.4.2

- a. Start of Fast Shift

- Coincidence of B/B leaving core 49 of primary CSR, sync LR-2 and Fast Shift = 0.

- 2) Good parity.

- 3) "Channel Ready" cleared.

- b. The following registers will be "fast shifted".

- 1) Primary CSR.

- 2) Word 1 & 2 core buffer registers.

- c. End of fast shift.

- 1) Busy-bit path during fast shift.

- a) Thru 51-52 of primary CSR.

- b) Thru all of word 2 core buffer.

- c) Thru word 1 core buffer cores 33 to 10.

- 2) Going from core 11 to 10 generates a "busy bit shift out" LR 2. (Clears primary CSR)

- 3) Fast shift ends at next LR 8. (GT5-41AJ)

- 4) At end of fast shift, core status is

Long Range Inputs and LRI Monitor

- d. Last shift.

- The last shift for the word 1 core buffer is necessary in order to prevent the last bit in buffer word 1 from being affected during the readout of buffer word 2. Since buffer word 2 is read out before buffer word 1, the output of core 1 in buffer register 2 would affect the bit contained in the 33rd core of buffer register 1, if there was not a last shift emptying the 33rd core.

- 2) Core 33 acts as an isolation core with no data bit in it after last shift.

- 3) LR 8 sets "chan ready".

- 4) Note AC coupling of "last shift" to increase reliability.

- e. End of Last Shift

- The shifting process ends with the first half of the LRI message in cores 10 through 32 of the word 1 core buffer register, with the parity bit in core 32. The second half of the LRI message is in the word 2 core buffer register in cores 1 through 23. The buffer word 2 parity bit is in core 23.

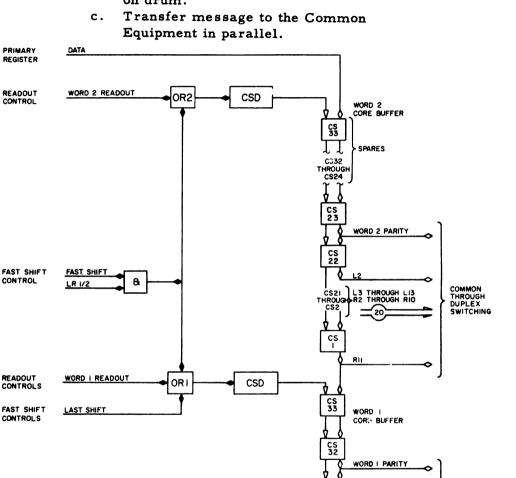

The LRI message is read out of the core buffer registers in parallel form for each word. The word 2 buffer register is read out, first. The "readout word 2" level causes an output from each core in the word 2 buffer that contains a 1 bit. This output is sent to the LRI common equipment to condition gates that pass pulses to the

drum. Following the readout of word 2, word l is read out, in a like manner, through the common section to the drum. All the data in word 1 and word 2 core buffer registers, except the parity bits and the busy bit, is sent directly to the drum. Additional information generated in the common equipment is, however, also read out to the drum so that the drum words contain more information than the core buffer words. The parity bits are also processed in the common equipment before transmittal to the drum fields so that the entire drum word will have the required odd parity. The busy bit, having served its purpose in initiating the end of fast shift, is not transmitted out of the core buffer register.

The parallel output wiring of the core buffers is so connected that the data in the drum words is rearranged differently from the order in the core buffer words.

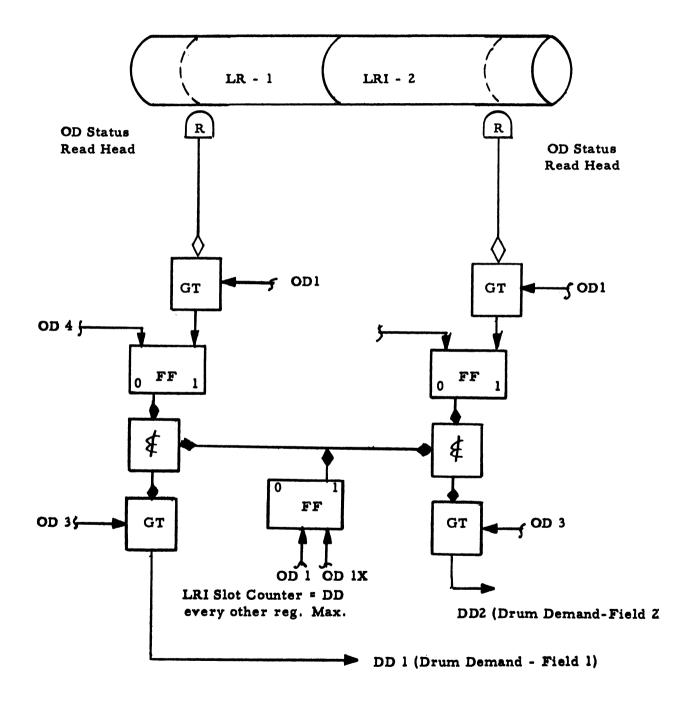

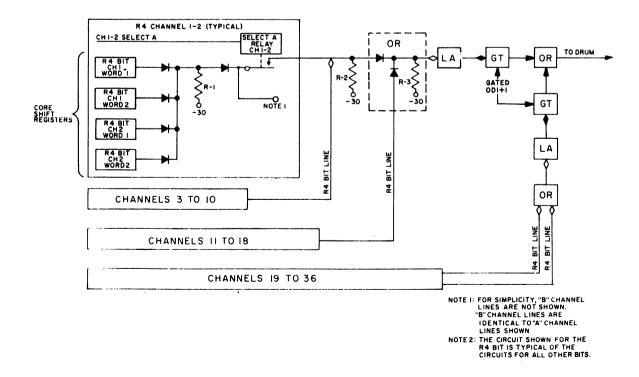

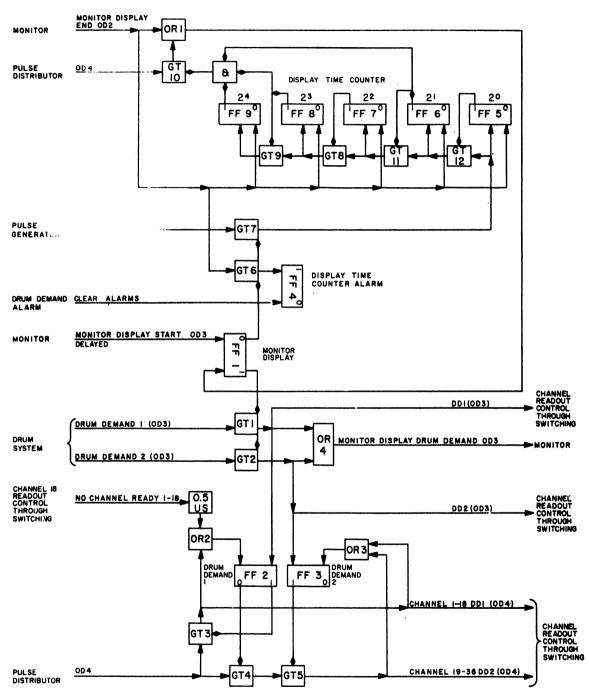

- G. Introduction to LRI Drum Demand Generation

- 1. Objectives of LRI Drum Demand Circuitry

- a. Allow channels 1-18 to feed LRI-1 field.

- b. Allow channels 19-36 to feed LRI-2 field.

- c. Control duplex switching associated with drum demands.

- d. If data is available for both fields, field 1 data shall have priority.

- e. If data is being displayed on LRI monitor, data shall not be transferred to drum.

- 2. Review Drum Control (Drum Demands)

- a. Simplified Circuit on next page

- a. Detailed analysis in drum theory of operation manuals.

- b. "Data Available" will be reviewed later.

- 3. Monitor Control

- a. Messages are transferred to monitor at same time they are sent to drum.

- b. If a message is to be displayed, further transfers to drums are prevented (no information will be lost.)

- c. This is to prevent new data from going to drum until the display has ended.

- d. This point will be cleared up later and should not be pursued at this time.

- e. When "Monitor Display" is cleared (FF3-41V(AA)) Logic S2.4.5

- 1) No drum demands get thru

- 2) Display time ctr is stepped

- 3) A count of 32 allows "monitor display" to be set

- 4) Next OD2 should be a "Display End" pulse to clear ctr.

- f. This allows time for display. Actual timing will be discussed later.

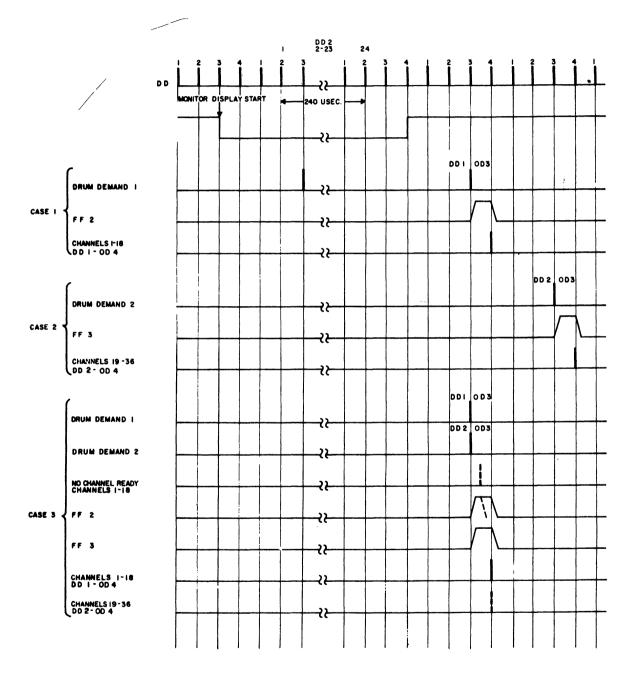

- Distribution of DD1 and DD2 (OD3) GT1 and GT2, 41V (AA)

- a. DD1 (OD3) checks channels 1-18 in numeric order that are assigned to drum.

- b. DD2 (OD3) checks channels 19-36 in numeric order that are assigned to drum.

NOTE:

Drum demands are from both "A" & "B" com.

- c. Once a channel is found ready-pulse ends search.

- d. See phantom logic of "channel ready".

- 0580

- 1) If channel is ready the "start word transfer is set".

- 2) If channel not ready-pulse goes to next channel.

- e. DD1 & 2 (OD3's) also go to LRI monitor (2.5.1).

- f. Note that any qty. of "chan. ready" FF's could be set (0 thru 36), but a max. of 2 "start word transfer" FF's could be set. This considers only one of the two drums A and B. Timing between the 2 is random.

- 5. Distribution of DD1 & 2 (OD4)

- a. None distributed unless "Drum Demand #1" or "Drum Demand #2" FF's are set.

- b. If "DD#1" is set DD1 (OD4) are sent in parallel to all channels 1-18 assigned.

- c. If "DD#2" is set and not "DD#1" then DD2 (OD4)s are sent in parallel to all channels 19-36 assigned.

- d. The receipt of a DD1 or 2 (OD4)

- 1) Start word transfer FF clear no effect.

- 2) Start word transfer FF set.

- a) Start readout.

- b) Clear "Channel ready".

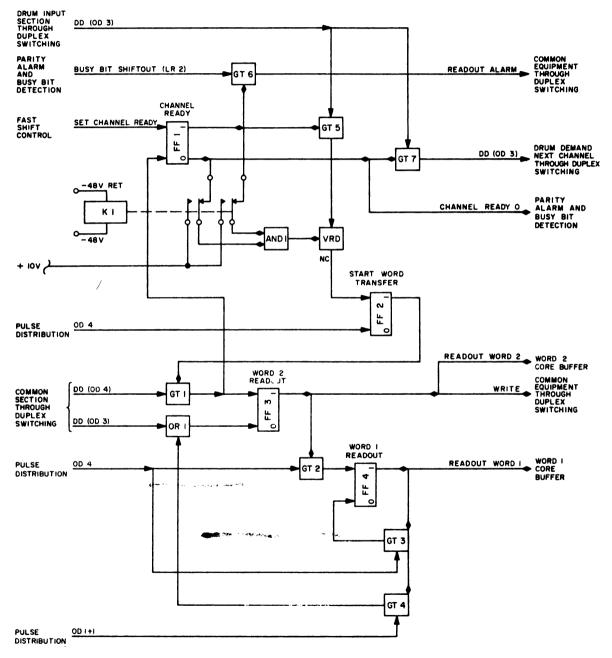

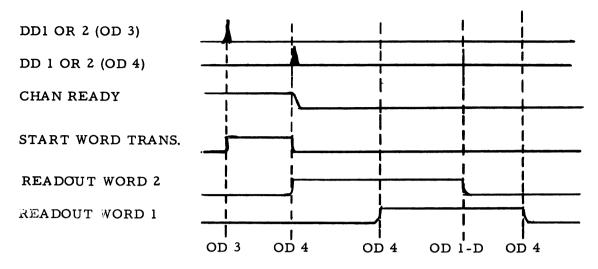

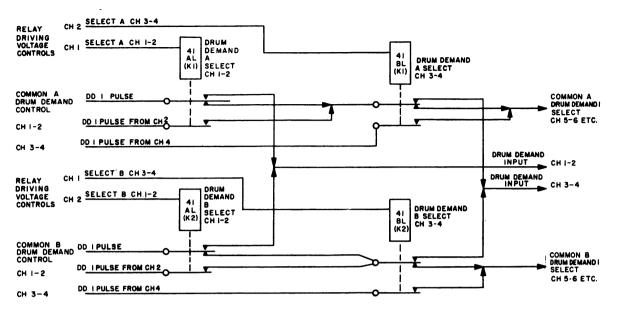

- H. Logic Analysis, Readout Control of Channel

- 1. Sequence of Events

- a. Receipt of a DD1 or 2 (OD3)

- b. Receipt of a DD1 or 2 (OD4)

- c. "Readout Word 2" generated

- d. "Readout Word 1" generated

Logic S2.4.5

Logic S2.4.5

١

- 2. Circuit Analysis

- a. Channel is ready

- 1) "Channel Ready" FF is set.

- 2) Word 1 and 2 are in respective core buffers.

- b. DD1 or 2 (OD3) PU 41AK

- 1) "Start Word Transfer" is set.

- Does not clear "Channel ready" as indicated on some logic.

- 3) Note that N/C contacts of bVRD are being used to prevent multiple readout if Channel Ready FF has both sides at  $\neq$  10.

- c. DDl or 2(OD4)

- 1) Sets "Readout Word 2" FF

- 2) Clears "Channel Ready"

- Is not gated by "channel ready" cleared, does not clear "start word transfer" as indicated on some logic.

- d. Every OD4 clears "start word transfer".

- e. "Readout Word 2" level comes up and resets "word 2 core buffer" storage and transfers data to common equipment.

- f. "Write" level comes up.

- 1) Used in common equipment.

- g. Next OD4 sets "Readout Word 1" and brings up "Readout Word 1" level.

- h. Next OD1-D clears "Readout Word 2".

- i. Next OD4 clears "Readout Word 1".

- j. Timing

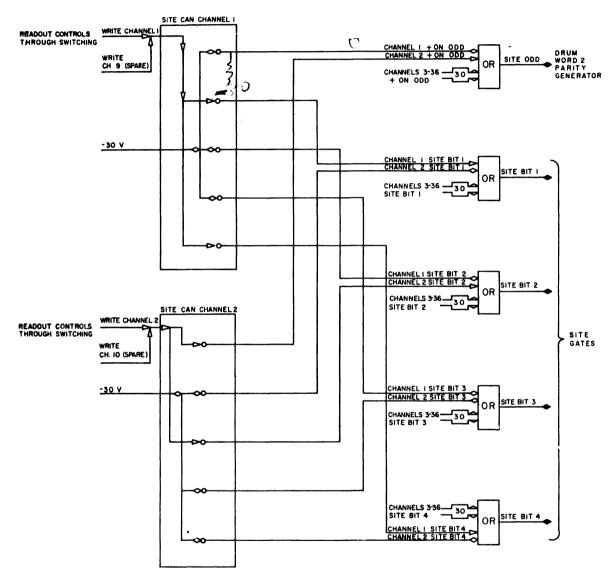

- 3. Readout of Core Buffers

- a. Word 2 buffer

- Each core has diode output to a pair of relays.

- 2) Data goes to common A or B dependent on status.

- b. Word 1 buffer

- 1) Similar to word 2 buffer.

- 2) Different bits involved.

- c. Bits transferred from

- Word 2 buffer to L2-L13 and R2-R11

of Drum Word 1 Parity goes to

Parity Generator for Drum Word 1/

- Word 1 buffer to L1-L15 and R9-R15 of Drum Word 2 - Parity goes to Parity Generator for Drum Word 2.

Summary Questions

- What is the duration of an LR-1/2 pulse? 2, 5 W 1.

- 2. What is the repetition rate of LR8 pulses? 20 ....

- Name the positions on the Unit Status Switch. off, active, standby, standby Mc sower filment What is meant by "Site Identity"? burary code identifying source 3.

- 4.

- What is maximum number of P sites feeding a Direction 5. Center? / 6

- 6. How many bits per LRI message? 5 J

- 7. How many bits constitute the "Sync Interval"? 🤦

- 8. Where are the OD pulses used in LRI originally generated? Aumo ZRIffels

- 9. What is amplitute relationship on phone line of sync, data, and timing pulses? amptitude of sync is three times that of timing or

enn

- 10. Is parity of LRI message odd of even on phone line?

- 11. Channel 5 has a circuit failure. Channels 5 and 6 were feeding data to the Active Computer (A). Which spare channels will be 9410selected? In which position will the "Spare Channel Selector" be set? In which position will the spare channel "Unit Status Switch"  $a_{\pm} = b_{\pm}$ active be set? In which position will channel 5's "Unit Status Switch" be set?

- 12. Relay 41E J(K5) has an open coil (Logic 2.4.1). What will be the affect on LRI operation?

- 13. (Logic S2.4.1) Channel 11 becomes active. Data is not being received, however, sync and timing pulses are being received normally. The spare channel is selected to replace Channel 11 and data flow to drum is restored. Channel 11 is then switched to "TEST" and operates normal. The failure would most likely be:

- Relay 41JT (K2) will not pick (a)

- (b) Relay 41EH (K4) 5c contacts will not make

- (c) Relay 41JT (K1) 5c contacts will not make

- (d) Relay 41JT (K2) 6b contacts will not open

- (e) Relay 41 ET (K2) 5b contacts will not open

- 14. (Logic S2.4.1) Make a point to point wiring diagram of the "Sync" line from Channel #13 on alternate phone line #11 to Channel #9 input. Label all points and relays. Specify relays that must be picked and the conditions necessary to pick these relays. Ignore all other channel relays.

- 15. (Logic A2.4.6) 41HNA8 (8E) is open. Which statment is most correct:

- (a) No LR 1/2 level to Unit 41.

- (b) No LR 1/2 level to Channels 1-18

- (c) No LR 1/2 level to any channel feeding the active computer.

- (d) "A" Drum LRI Field #1 would probably never be written on.

- (e) LRI data would never reach Central Computer.

- 16. Fast shift is started by readout of <u>busy but</u> from Core # <u>49</u> of primary core shift register. This readout can be checked only if the DCR output is at 410.

- 17. If message word #2 was read out of main storage but message word #1 could not be read out, what would be the affect on the next LRI message? It would have its word / dogically added to previous contents of

- 18. (Logic 2.4.2) Draw a timing chart showing the output of each of the following circuits. Begin with "Sync" bit and conclude when Busy Bit is primed into Core 1 of the Primary Storage Register:

Timing DCR Sync DCR Data DCR Time Sync FF Time Cycle FF Load Data FF Clear FF Sync Interval #1 FF Sync Interval #2 FF 41AFC1

- 19. Parity errors in Channel 11 fail to clear the CSR at Sync LR2 time. This could be due to:

- (a) 41AL (K4) la contacts open

- (b) 41JL (K4) 1c contacts open

- (C) 41AL (K4) energized

- (d) 41JL (K4) la open

- (3) 41JL (K4) lb open

- 20. Draw a timing chart for the following circuits on Logic 2.4.2 Assume a good message is stored in Word #1 and Word #2. buffers. Begin the chart with the receipt of a Drum Demand (OD3) and conclude with the fourth OD4 following.

Channel Ready FF Start Word Transfer FF Read Out Word 2 FF Read Out Word 1 FF 120 OR (41AN) (9B) 120 OR (41AM) (8A)

21 Draw a timing chart for the following circuits on Logic S2. 4. 2 Assume a good message is in the primary CSR.Begin chart at the time the following Sync Pulse arrives and conclude when the entire message is properly positioned in the buffer registers.

> Fast Shift FF Last Shift FF 68 OR (41AF) (14A) 120 OR (41AM) (8A) Channel Ready FF Glear FF

- 22. (Logic 2.4.2) FF6 in 41AH (13B) has an open filament. This would most likely cause:

- (a) Fast shift pulses to be generated during the entire message.

- (b) Fast shift pulses to be generated when data is not being received.

- (c) Channel Ready FF to never be set.

- (d) Failure to clear the primary CSR.

- Failure to set the fast shift FF.

- 23. Briefly explain how you arrived at the answer in Question #22 and why the other choices could not possibly be correct.

- 24. Logic S2. 4. 2) 41AHA1 is open (11A). The message in the Primary Core Register is good and the new message coming in has a sync bit. Which statement is most correct:

- (a) No affect under the above conditions.

- (b) Message in Primary Core Register will not be shifted out before new message is shifted in.

- (c) Parity cannot be checked for future messages.

- (d) Parity alarm will be generated for next message.

- (c) None of the above.

- 25. How long may a message remain in main storage before a new message checks main storage to determine if it is empty? (Start with the Channel Ready FF being set.)

- 26. The Fast Shift FF is set for <u>//gf</u> microseconds for each good message.

- 27. What is the minimum time that the Channel Ready FF may be set?  $10 \mu size$

- 28. Which of the following conditions will result in the Primary Core Shift Register being cleared? (Logic 2.4.2)

- (a) Time cycle FF being set at LR8 time.

- (b) Load Data FF being set at Data LR2 time.

- (c) 41ACA2 open (12B).

- (d) 41AFE6 open (14B).

- (e) 41AFC5 open (13A).

- 29. During the timing cycle that a data pulse is received the Primary CSR is !

- (a) Primed then shifted

- (b) Shifted then primed

- (c) Cleared then shifted

- (d) Cleared then primed

- (e) Shifted then cleared

- 30. (Logic 2.4.2) 51AFE6 (14B) is open. A mark X message with range of 1777<sub>8</sub> was being received. When channel ready FF is set:

- (a) Word 1 buffer would contain Word 1 and Word 2 buffer would contain Word 2.

- (b) Word 2 buffer would contain all zeros.

- (c) Word 1 buffer would contain B/B and the first bit of range.

- (d) Word 2 buffer would contain the first bit of range.

- (e) Word 1 and 2 buffers will not fast shift during this message.

- 31. (Logic 2.4.2) Connection 41AMA3 (9A) is open. This will:

- ((a)) Prevent either word from getting on drum.

- (b) Result in a readout alarm.

- (c) Cause parity of first Drum Word to always be even.

- (a) Inhibit Drum Word 1 writing but not Drum Word 2.

- (e) Allow data to be written but not read.

- 32. Briefly explain how you arrived at your answer for Question #44, and why the other choices could not possibly be correct.

### IV. Duplex Switching

## A. General

- 1. Duplex switching relates simplex equipment to the proper A or B common equipment and, ultimately, to the proper A or B computer. Simplex equipment in the active status is associated with the duplex computer currently in the active status, and simplex equipment in the standby status is associated with the duplex computer in the standby status.

- 2. Duplex switching in the LRI element provides the necessary circuitry to accomplish the following functions:

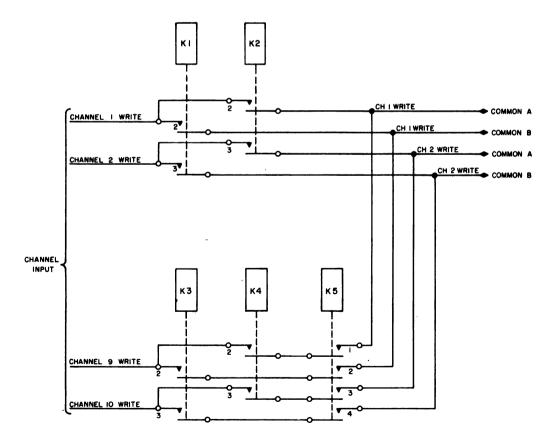

- a. Core Data Switching: Transfers the data from the core buffer registers of the 36 channel sections to the common A or common B section indicated by the status of the channel and the status of the A and B duplex computer.

- b. Write Level Switching: Transfers the write level generated in a channel input section to the proper half (A or B) of the common equipment. In spare channel switching, the write level generated by the spare channel must be switched to the site can of the replaced channel. Accordingly, when a spare channel is substituted, write level switching involves both duplex and simplex switching.

- c. Readout Alarm Switching: Directs the readout alarm pulse to the proper A or B common equipment.

- d. Timing Pulse and Level Switching: Transfers the OD pulses and the LR pulses and levels from the proper half of the common section to the channel input section to synchronize channel operations with the operation of the common section with which the channel is associated.

Drum Demand Switching: Transfers the DD pulses e. to the channel sections to initiate readout to the common equipment on a priority basis.

- f. Site Neon Indication Switching: Causes illumination of either the A or B site neons on the channel control panel (simplex maintenance console).

- g. Status Indication Switching: Sends status indication of each channel to the MDI element of the proper computer.

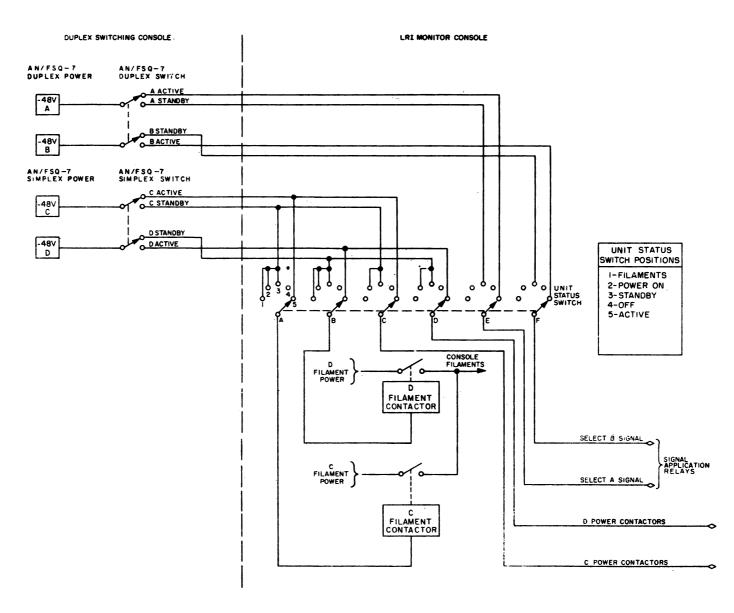

- B. Driving of A and B Signal Relays

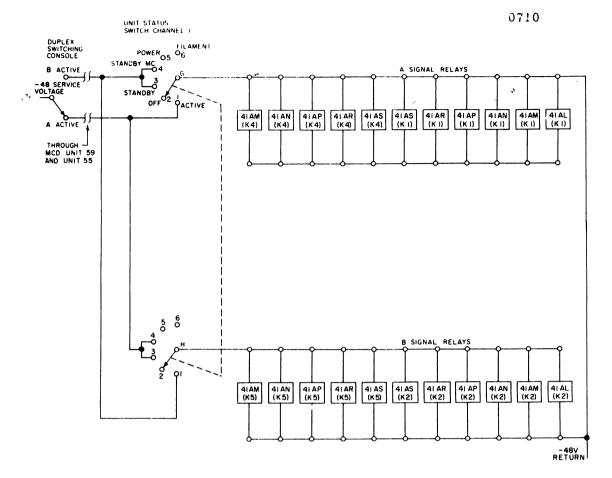

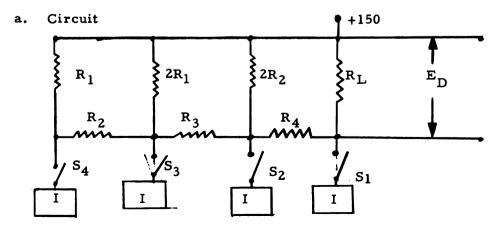

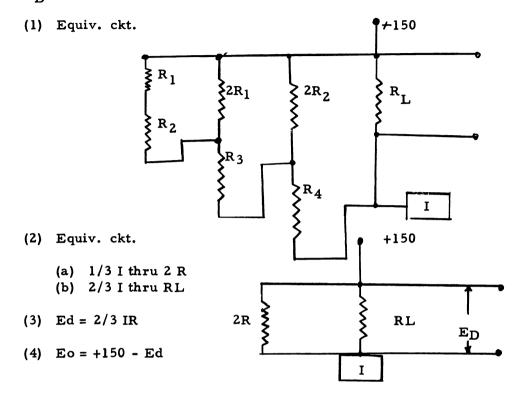

- 1. The operations listed above are accomplished by means of groups of relays, designated A signal relays and B signal relays. Only one group can be energized at any one time, depending on the status of the channel and the status of the A or B computer. A simplified circuit for these relays is shown on page 0760. The -48V driving voltage is supplied by MCD unit 59A or 59B through individual cells of power distribution unit 55. This voltage is applied to the terminals of unit status switch sections G and H. Section G controls the energizing of the A signal relays; section H controls the energizing of the B signal relays.

- 2. Simplified Circuit Analysis

- a. Assume that the A machine has been designated active and the B machine standby by the duplex selection control at the duplex switching console. Relay-driving voltage is then applied to terminal 1 (ACTIVE) of section G and terminals 3 and 4 of section H (STANDBY, STANDBY MC, respectively, of the unit status switch of each channel). If this switch is placed in the ACTIVE position, driving voltage is applied to the A signal relays; if this switch is placed in the STANDBY or STANDBY MC position, driving voltage is applied to the B signal relays. Reversing the status of the A and B machine reverses the effect of the UNIT STATUS switch positions on the signal relays.

A and B Signal Relays Driving Circuit, Simplified Schematic Diagram

- 3. The signal control relays for channel 1 are listed, and their functions are indicated on pages 0790 and 0800. Each contact group of a relay (if used) performs a specific function, and corresponding contact groups of paired A and B signal relays perform the same functions. Thus, when A signal relay 41AM(K1) is energized, contact group 2 causes transfer of the write level from channel 1 to the A drum input section; if the B signal relays are energized, contact group 2 of 41AM(K2) transfers the write level from channel 1 to the B drum input section.

- 4. When a group of signal relays for a channel are energized, one set of contacts from each relay (connected in a series array) completes a circuit to cause illumination of the related (A or B) SIGNAL CONTACTORS CLOSED lamp (X12 and X8, Logic S2.4.7, 7D). Illumination of the SIGNAL CONTACTORS CLOSED lamp indicates which computer is receiving data from the pair of channels controlled by the power section of the control panel; it also indicates that all relays in the group are energized.

| FUNCTION      | A SIGNAL RELAY | B SIGNAL RELAY |

|---------------|----------------|----------------|

| ORE DATA TRAN | ISFER          |                |

| Ll            | 41AN(K4) 3     | 41AN(K5) 3     |

| L2            | 41AN(K4) 4     | 41AN(K5) 4     |

| L3            | 41AN(K4) 5     | 41AN(K5) 5     |

| L4            | 41AN(K4) 6     | 41AN(K5) 6     |

| L5            | 41AP(K4) 2     | 41AP(K5) 2     |

| L6            | 41AP(K4) 3     | 41AP(K5) 3     |

| L7            | 41AP(K4) 4     | 41AP(K5) 4     |

| L8            | 41AS(K4) 2     | 41AS(K5) 2     |

| L9            | 41AS(K4) 3     | 41AS(K5) 3     |

| L10           | 41AS(K4) 4     | 41AS(K5) 4     |

| L11           | 41AS(K4) 5     | 41AS(K5) 5     |

| L12           | 41AR(K4) 5     | 41AR(K5) 5     |

| L13           | 41AR(K4) 2     | 41AR(K5) 2     |

| L14           | 41AR(K4) 3     | 41AR(K5) 3     |

FUNCTION OF SIGNAL RELAY CONTACTS, CHANNEL 1

FUNCTION OF SIGNAL RELAY CONTACTS, CHANNEL 1 (con'd)

| FUNCTION             | A SIGNAL RELAY  | B SIGNAL RELAY    |

|----------------------|-----------------|-------------------|

| CORE DATA TRANSFE    | R               |                   |

| L15                  | 41AR(K4) 4      | 41AR(K5) 4        |

| R1                   | 41AN(K1) 3      | 41AN(K2) 3        |

| R2                   | 41AN(K1) 4      | 41AN(K2) 4        |

| R 3                  | 41AN(K1) 5      | 41AN(K2) 5        |

| R4                   | 41AN(K1) 6      | <b>41AN(K2)</b> 6 |

| R5                   | 41AP(K1) 2      | 41AN(K2) 2        |

| R6                   | 41AP(K1) 3      | 41AP(K2) 3        |

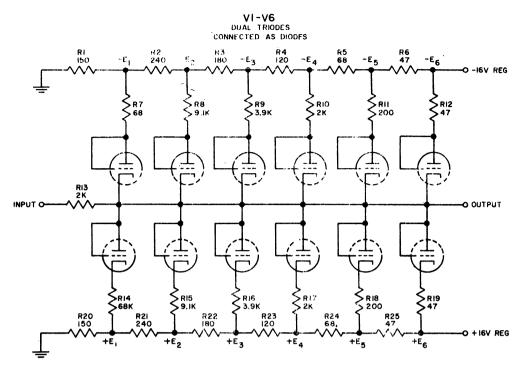

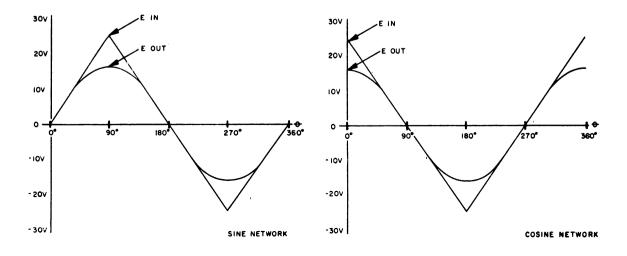

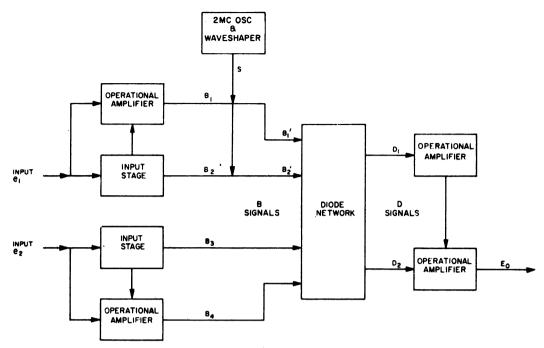

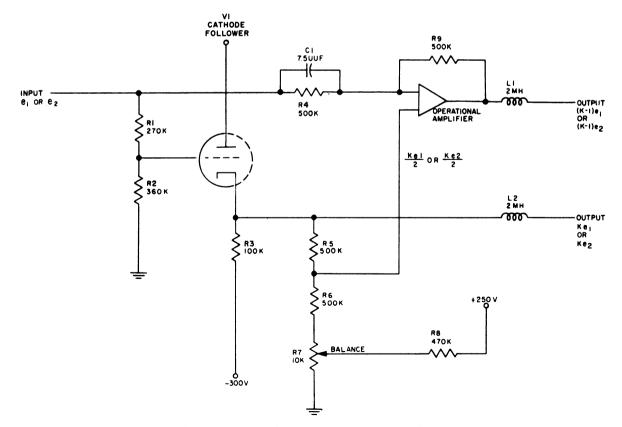

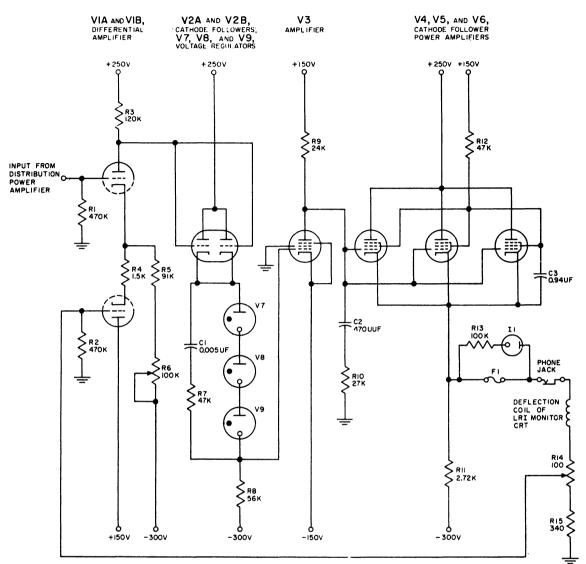

| R7                   | 41AP(K1) 4      | 41AP(K2) 4        |