# Customer Engineering

# Manual of Instruction

**DDTL Component Circuits**

IBM

# Manual of Instruction DDTL Component Circuits

>

# Preface

Double Diffused Transistor Logic (DDTL) is a moderately fast, inexpensive, group of transistor circuits that have found wide application. These circuits use germanium diodes to perform logic functions and germanium mesa transistors to power the signals. These efficient circuits consume little power and perform logic decisions in 15 to 100 nanoseconds.

The DDTL circuit group includes nearly 300 circuits. These circuits are packaged in various combinations and inter-connections to make up hundreds of unique SMS printed circuit cards. Thousands of these cards are inter-connected to perform logic decisions in IBM machines, including the 7040, 7044, 7640, 7710, 7750, and 7908.

This instruction manual describes the characteristics of the DDTL circuits and gives detailed information on those circuits that are most frequently used. There are many special circuits used for unique applications that are not described here; these circuits are described in the CE Manuals for the machines that use these circuits.

This manual assumes a knowledge of transistor theory and basic transistor circuits such as presented in the *Transistor Theory and Application*, *IBM Customer Engineering Manual of Instruction*, Form 2236783-2. From the basic knowledge assumed, three levels of circuit detail are given in this manual. The introduction deals with general characteristics and simplified explanations of common circuits. The "Circuit Operation" section gives the relation of inputs to outputs, circuit theory, and important input and output requirements for specific circuits. The Appendix has very detailed circuit analysis information on delays, transitions, and so forth, for a few of the most common circuits.

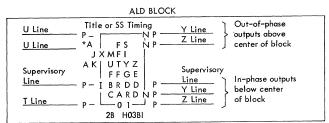

Each DDTL circuit is assigned a unique code number, usually beginning with H, for identification by engineering personnel. This H code, or block identification number, is generally printed underneath each ALD block to identify the circuit represented by that block. If two circuits differ in any way, a unique H code is assigned to each; thus, if several circuits are identical except for the value of the load resistor, each circuit has its own H code.

In this manual, circuits that are almost identical are grouped and covered as a single circuit; one circuit explanation may apply to several H codes. Use the H code index in Appendix B of this manual to locate the circuit diagram and description of a particular ALD block.

Copies of this and other IBM publications can be obtained through IBM Branch Offices. Address comments concerning the contents of this publication to: IBM Corporation, CE Manuals, Dept. B95, P.O. Box 390, Poughkeepsie, N.Y.

# Double Diffused Transistor Logic (DDTL)

| General | Circuit | Group | Characteristics |  |

|---------|---------|-------|-----------------|--|

|         |         |       |                 |  |

557

| Circuit Operation                                                                                                                                                                                                                                                                                                                                              | 16 |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|

| Fundamental Characteristics                                                                                                                                                                                                                                                                                                                                    | 16 |  |

| Line Louds                                                                                                                                                                                                                                                                                                                                                     | 16 |  |

| Line Levels<br>Single and Double Level Diode Logic                                                                                                                                                                                                                                                                                                             | 16 |  |

| Single and Double Level Diode Logic                                                                                                                                                                                                                                                                                                                            |    |  |

| Loading<br>DOT Function                                                                                                                                                                                                                                                                                                                                        | 17 |  |

|                                                                                                                                                                                                                                                                                                                                                                | 17 |  |

|                                                                                                                                                                                                                                                                                                                                                                |    |  |

|                                                                                                                                                                                                                                                                                                                                                                |    |  |

| Basic Inverter                                                                                                                                                                                                                                                                                                                                                 |    |  |

| Logical Low Power Inverter                                                                                                                                                                                                                                                                                                                                     | 20 |  |

| Emitter Follower Chain                                                                                                                                                                                                                                                                                                                                         | 21 |  |

| Powered Inverter                                                                                                                                                                                                                                                                                                                                               | 24 |  |

| Triggers and Latches                                                                                                                                                                                                                                                                                                                                           | 24 |  |

| Rinary Trigger                                                                                                                                                                                                                                                                                                                                                 |    |  |

| Control Trigger                                                                                                                                                                                                                                                                                                                                                |    |  |

| AC Trigger                                                                                                                                                                                                                                                                                                                                                     |    |  |

| No mating I atab                                                                                                                                                                                                                                                                                                                                               |    |  |

| Chift Call Character                                                                                                                                                                                                                                                                                                                                           |    |  |

|                                                                                                                                                                                                                                                                                                                                                                |    |  |

|                                                                                                                                                                                                                                                                                                                                                                |    |  |

|                                                                                                                                                                                                                                                                                                                                                                |    |  |

|                                                                                                                                                                                                                                                                                                                                                                |    |  |

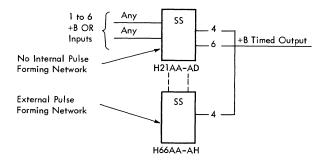

| Single-Shots                                                                                                                                                                                                                                                                                                                                                   |    |  |

| Variable Single-Shot                                                                                                                                                                                                                                                                                                                                           |    |  |

| Holdover Single-Shot                                                                                                                                                                                                                                                                                                                                           | 38 |  |

| Pulse Former Single-Shot                                                                                                                                                                                                                                                                                                                                       | 39 |  |

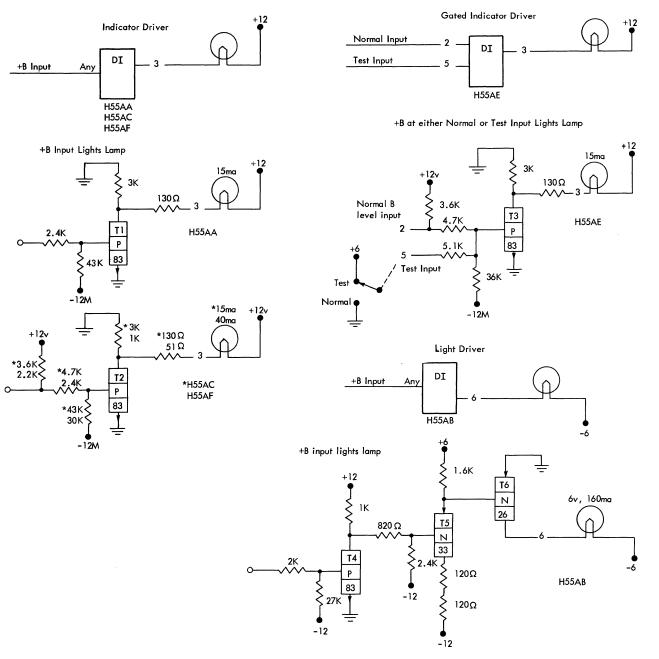

| Indicator and Relay Drivers                                                                                                                                                                                                                                                                                                                                    | 40 |  |

| Indicator Drivers                                                                                                                                                                                                                                                                                                                                              | 40 |  |

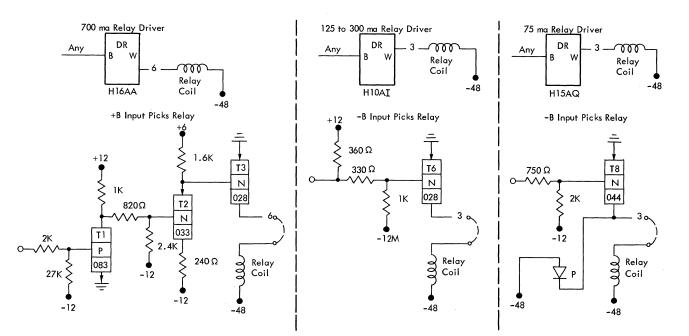

| Belay Drivers                                                                                                                                                                                                                                                                                                                                                  | 42 |  |

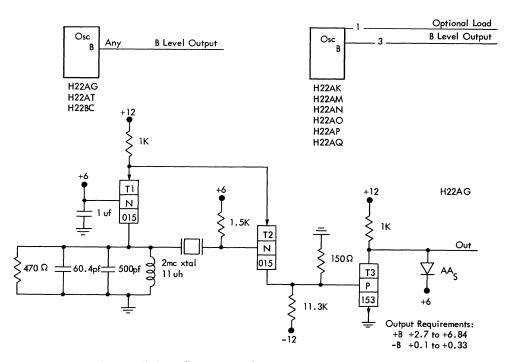

| Oscillators                                                                                                                                                                                                                                                                                                                                                    | 43 |  |

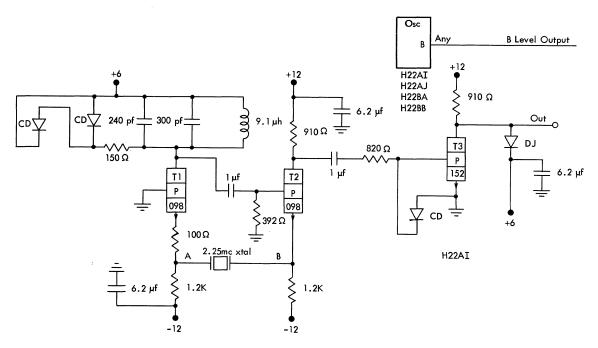

| Crystal Controlled Oscillators                                                                                                                                                                                                                                                                                                                                 |    |  |

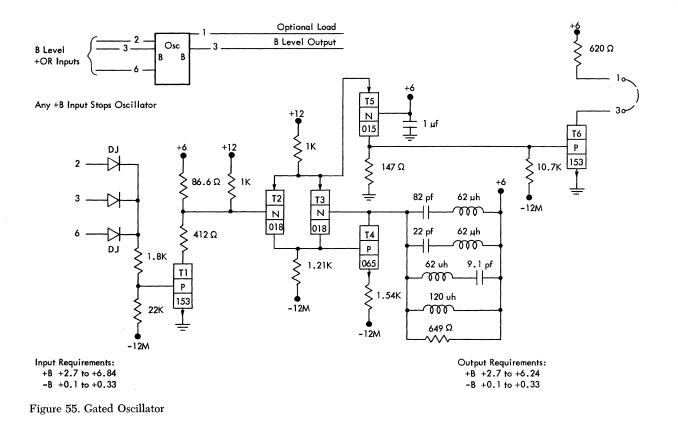

| Cated Oscillator                                                                                                                                                                                                                                                                                                                                               |    |  |

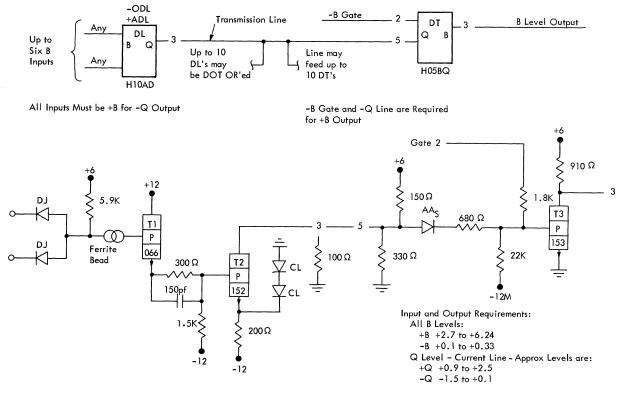

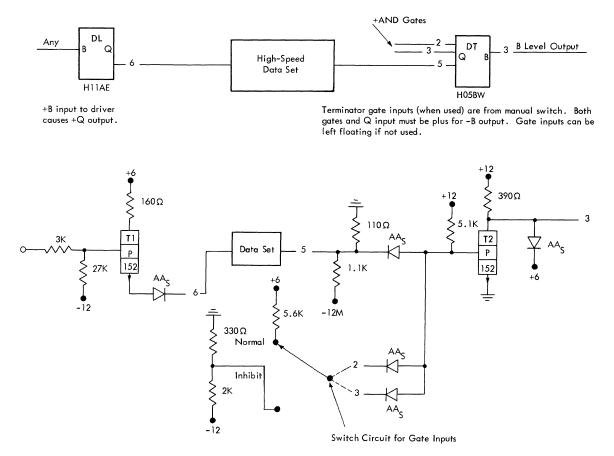

| Line Drivers and Line Terminators                                                                                                                                                                                                                                                                                                                              |    |  |

| Driver and Terminator (O Level)                                                                                                                                                                                                                                                                                                                                |    |  |

| Dilver and Terminator (Q Lever)                                                                                                                                                                                                                                                                                                                                |    |  |

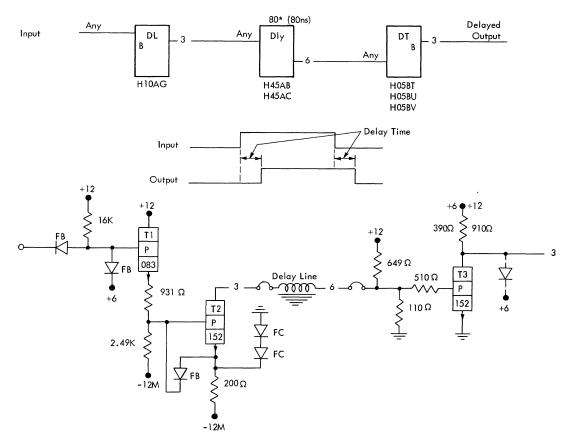

| Delay Line Driver and Terminator                                                                                                                                                                                                                                                                                                                               |    |  |

| sic Circuits17Diode Circuits17Basic Inverter18Logical Low Power Inverter20Emitter Follower Chain21Powered Inverter24iggers and Latches24Binary Trigger25Control Trigger27AC Trigger28Negative Latch30ift Cell Circuits30Shift Cell32Cell Driver33Pulse Generator34Igle-Shots35Variable Single-Shot36Holdover Single-Shot39Questor Drivers40Indicator Drivers40 |    |  |

| V or Q Level Data Set Driver and Terminator                                                                                                                                                                                                                                                                                                                    |    |  |

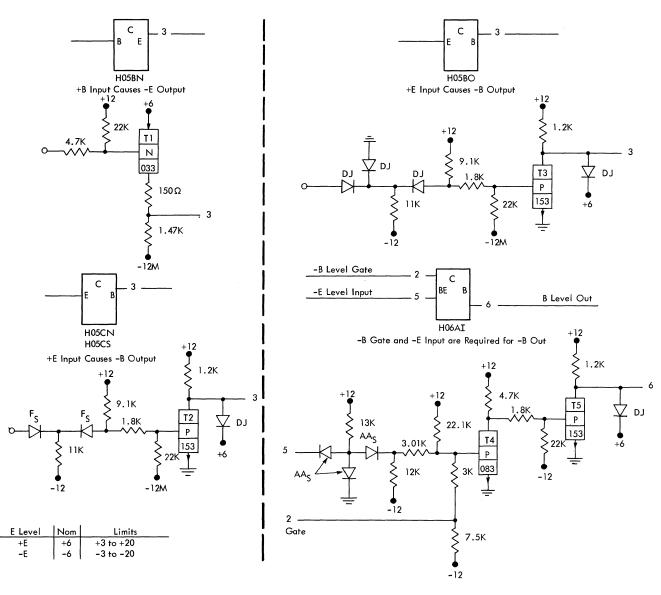

| Converters and Integrators                                                                                                                                                                                                                                                                                                                                     |    |  |

| EIA Data Set Converters                                                                                                                                                                                                                                                                                                                                        |    |  |

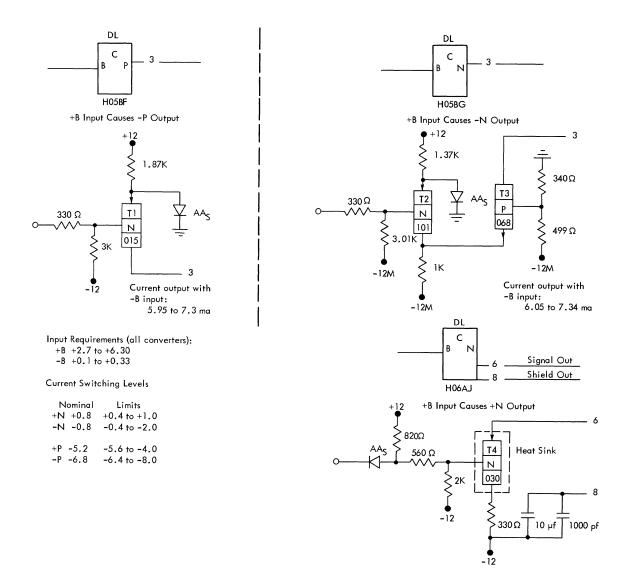

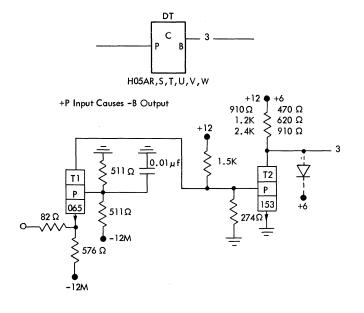

| Current Switching Converters                                                                                                                                                                                                                                                                                                                                   | 49 |  |

|                                                                                                                                                                                                                                                                                                                                                                |    |  |

ĥ

÷

| S Level Converters                       | 50         |

|------------------------------------------|------------|

| V Level Converters and Integrators       | 50         |

|                                          |            |

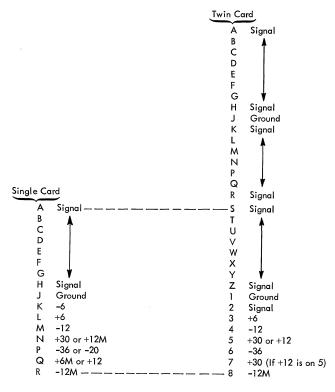

| Packaging and ALD Information            | 54         |

| SMS Twin Cards                           | 54         |

| Voltage Pin Assignments                  | 54         |

| Twin Card Lavout                         | 54         |

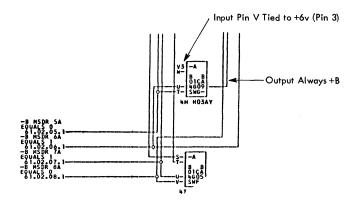

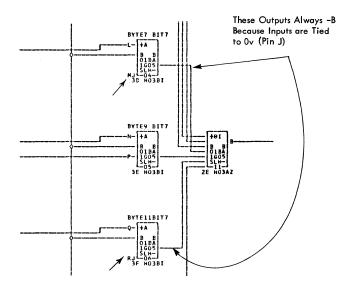

| Unused Twin Card Circuits                | 54         |

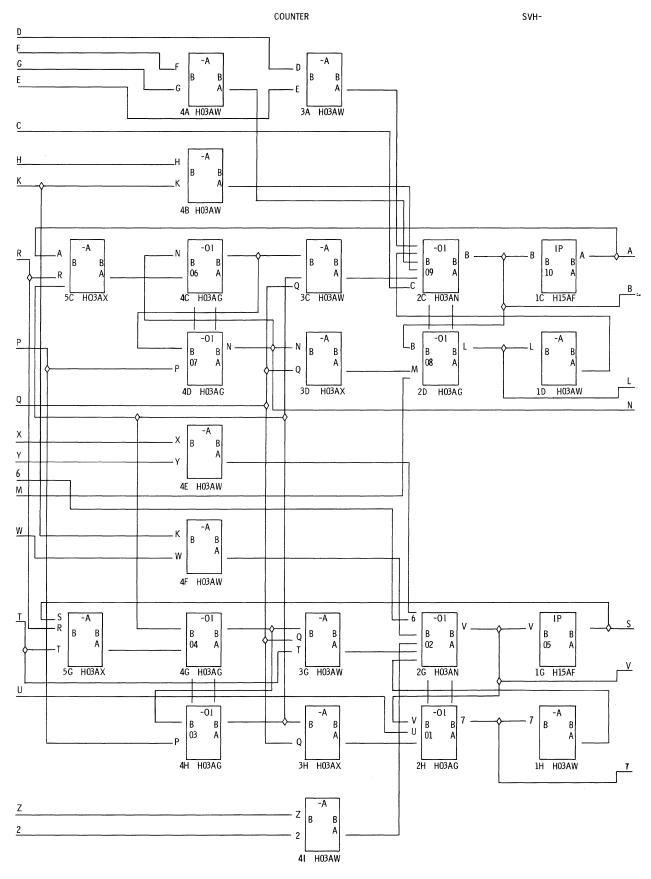

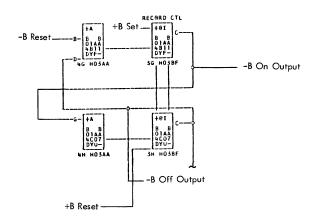

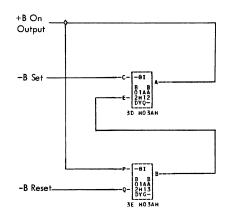

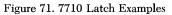

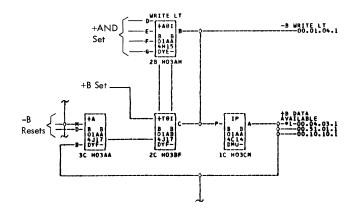

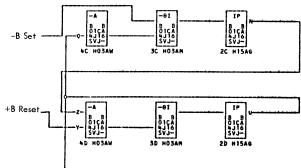

| Example DDTL Latches                     | 56         |

| 7040-7044 Example Latches                | 56         |

| 7640 Example Latches                     | 56         |

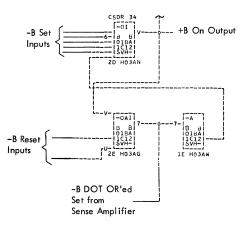

| 7710 Example Latches                     | 56         |

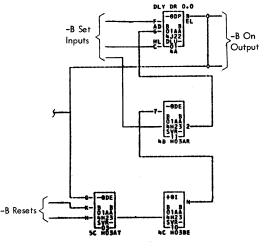

| 7750 Example Latches                     | 59         |

| 7908 Example Latches                     | 63         |

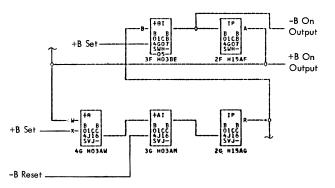

| Example Shift Cell Circuits              | 63         |

| Diagonal Latah Ose Caracteria            | 63         |

| Binary Latch Configuration               |            |

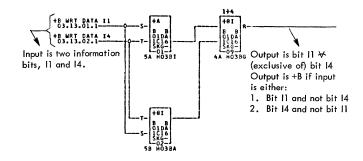

| Exclusive OR Configuration               | 66         |

| Circuit Jumpering for Troubleshooting    | 66         |

|                                          |            |

| Appendix A — Examples of Circuit Details | 68         |

| Appendix A - Examples of effect before   | 68         |

| Loading                                  |            |

| Branching Factor Equations               | 68         |

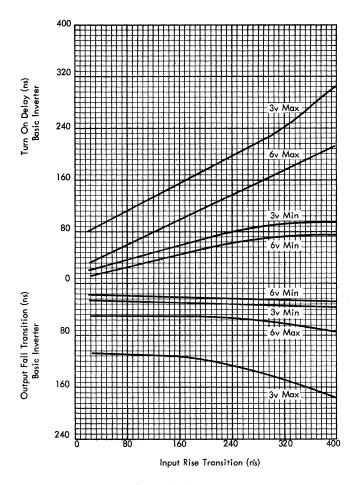

| Basic Inverter                           | 70         |

| Input Current                            | 70         |

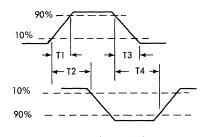

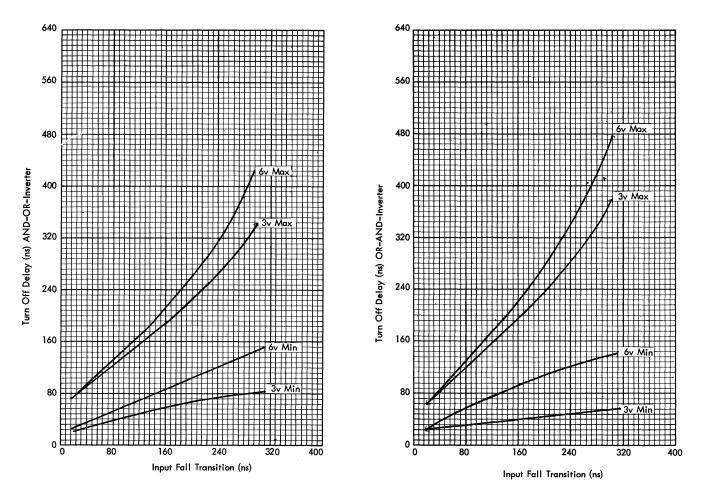

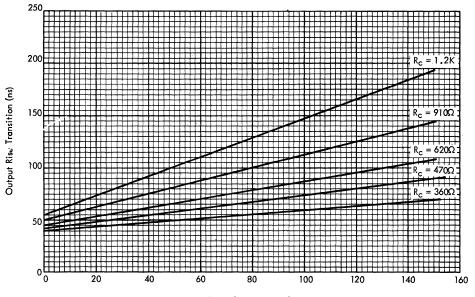

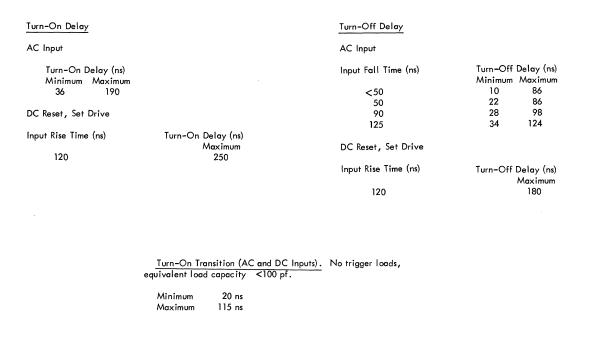

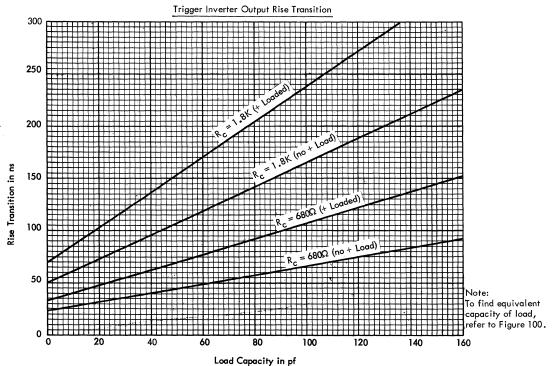

| Delays and Transitions                   | 71         |

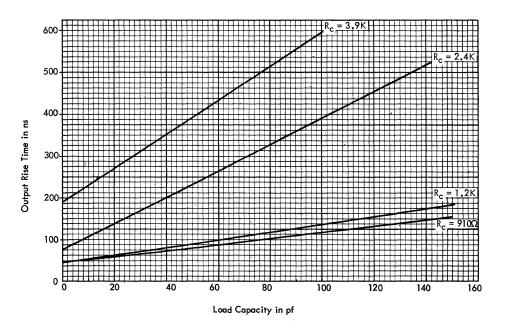

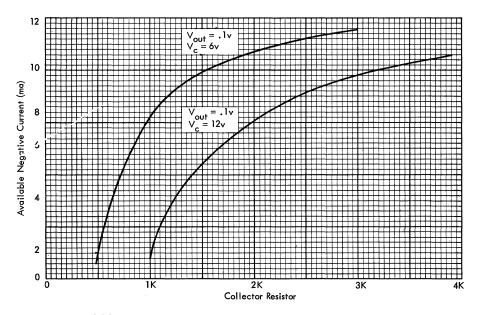

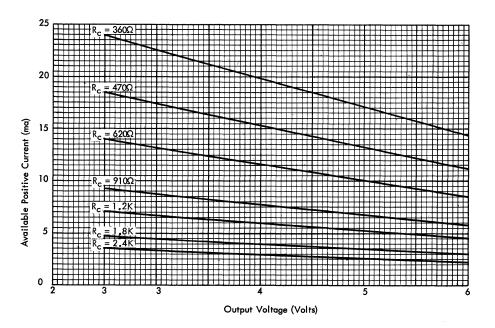

| Available Output Current                 | 71         |

| Marginal Checking                        | 71         |

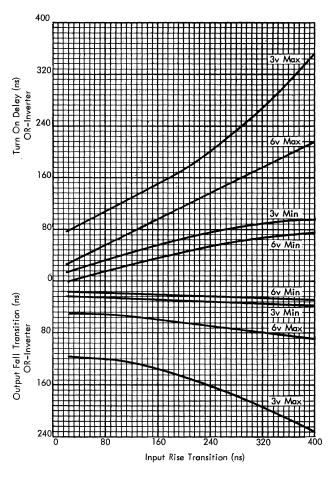

| AND Logical Low Power Inverter (+AIP)    | 71         |

| Input and Output Current                 | 71         |

| Delays and Transitions                   | 71         |

| Marginal Checking                        | $\dot{71}$ |

| Emitter Follower Chains                  | 71         |

| Input and Output Voltage and Current     | 71         |

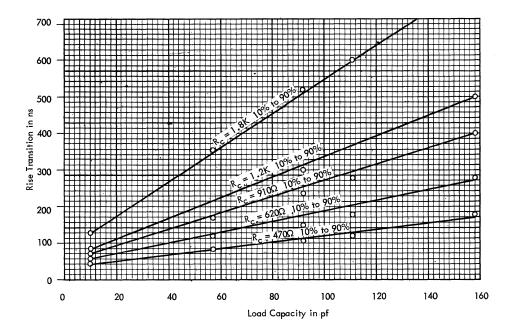

| Delays and Transitions                   | 71         |

|                                          | 71         |

| Binary Trigger                           |            |

| Input Requirements                       | 71         |

| Delays and Transitions                   | 71         |

| Appendix B — H Code Index                | 87         |

| Changer B - II and IIIacy                | 01         |

| Appendix C — ALD Reference Information   | 90         |

# a the second second

## **General Circuit Group Characteristics**

During 1954 and 1955, IBM developed a group of transistor component circuits. Although these circuits provided the three necessary functions (AND, OR, invert) to perform logic decisions, constant work improving speed, reliability, and flexibility, reducing cost and power consumption, and building special-purpose circuits has produced an overwhelming array of circuits since that time. This flood of ever-improving circuits has been partially caused by the continual improvement in speed, and reduction in cost and size of circuit components such as transistors, resistors, and capacitors.

Most of the circuits developed fall into groups (or "families") according to speed, transistor type, powering circuit, and the method used to make logic decisions (Figure 1). Because the circuit used to power signals and the method used to make logic decisions are key characteristics for understanding a new group of circuits, these characteristics are discussed in the following paragraphs.

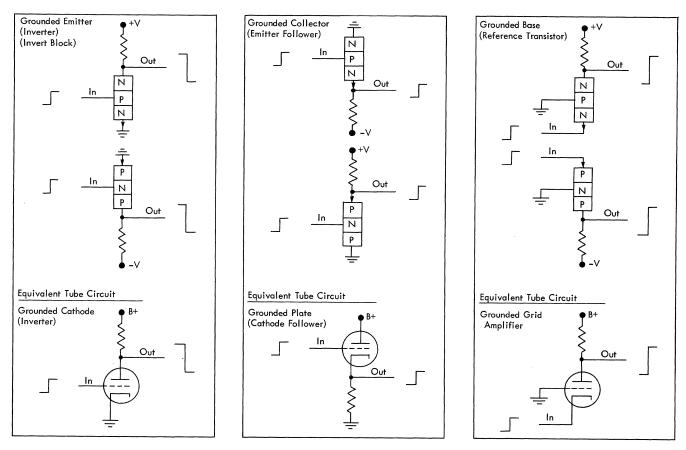

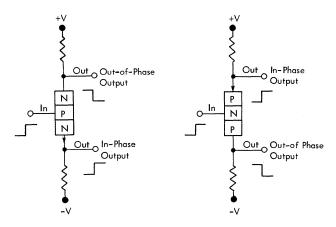

Recall from transistor theory that signals can be powered by three different transistor circuit configurations: grounded (or common) emitter, grounded collector, and grounded base (Figure 2). The grounded emitter circuit is more commonly called an inverter, or invert block. The grounded collector configuration is more commonly called an emitter follower. By combining the inverter and the emitter follower, a configuration called a split-load circuit, or phase splitter, is obtained (Figure 3).

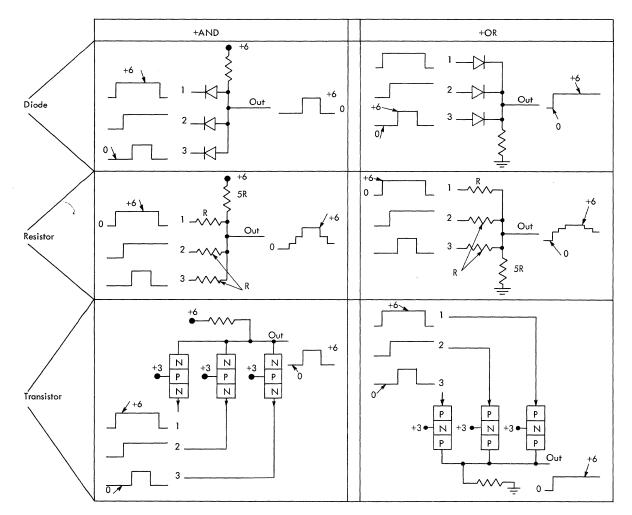

In addition to the basic transistor configurations, the transistors may be operated as linear amplifiers (small input signals) or they may be switched between saturation and cutoff (large input signals). See Figure 4.

Although each circuit group uses more than one circuit configuration for powering lines, each has a basic circuit that is used for all normal powering applications. For example, VMTL, CTRL, CTDL, SDTRL, SDTDL and DDTL use a saturating inverter; DEFL uses an emitter follower; ACM and DCM use a non-saturating split-load circuit and a non-saturating grounded base amplifier.

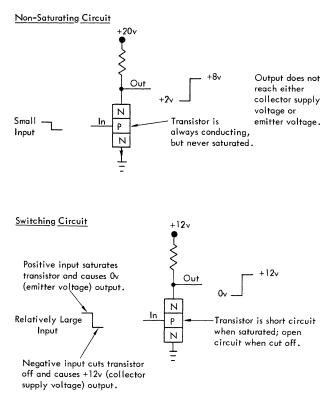

The three types of logic-performing circuits, diode, resistor, and transistor, are named for the major components in the circuits (Figure 5). Regardless of the type of input components, circuits for a particular

| Group             | Name                                                                         | Application<br>Example              | Normal Packaging                 | Primary<br>Transistor | Approx DIy<br>Per Decision |

|-------------------|------------------------------------------------------------------------------|-------------------------------------|----------------------------------|-----------------------|----------------------------|

| VMTL              | Voltage Mode Transistor Logic                                                | 608                                 | 608 Card                         | 01,051                | 1-5 usec                   |

| DCM<br>(CSDBTL)   | Diffused Current Mode<br>(Current Switching Diffused Base Transistor Logic)  | 7030, 7090,<br>7080                 | Single and Double<br>SMS Cards   | 015,065               | 10-30 ns                   |

| ACM<br>(CSAJTL)   | Alloy Current Mode<br>(Current Switching Alloy Junction<br>Transistor Logic) | 7030, 7090<br>7070, 7080            | Single SMS Card                  | 013, 063              | 50-200 ns                  |

| CTRL<br>(NOR I)   | Complementary Transistor Resistor<br>Logic (Negated OR)                      | 1620, 729 (NOR)<br>7701, 7702, 7330 | Single SMS Card                  | 033, 083              | 1-3 usec                   |

| CTDL              | Complementary Transistor Diode Logic                                         | 7070, 1401                          | Single SMS Card                  | 034, 083              | 0.3-1.5 usec               |

| SDTRL<br>(NOR II) | Saturating Drift Transistor<br>Resistor Logic                                | 7074, 1410,<br>1620, 7631           | Single and Stan-Pac<br>SMS Cards | 101                   | 50-150 ns                  |

| SDTDL             | Saturating Drift Transistor Diode<br>Logic (Negated AND)                     | 7074, 1410,<br>7631                 | Single and Stan-Pac<br>SMS Cards | 102                   | 50-100 ns                  |

| DEFL              | Diode Emitter Follower Logic                                                 | 7302 (Serial<br>12,000 & Above)     | Stan-Pac SMS Card                | 098                   | 3-10 ns                    |

| DDTL              | Double Diffused Transistor Logic                                             | 7750, 7908,<br>7040, 7640           | Single and Twin SMS<br>Cards     | 152, 153              | 15-100 ns                  |

Figure 1. Component Circuit Groups

Figure 2. Transistor Circuit Configurations

Figure 3. Split-Load Configuration

logic decision produce identical results: in the diode +AND circuit, input 1, input 2, and input 3 must be positive to prevent diode conduction; in the resistor +AND, all inputs must be plus to prevent current flow; in the transistor +AND, all inputs must be plus to hold

the transistors cut off. In each of these cases, the +AND function is satisfied by preventing current flow through the load resistor and allowing the circuit output to rise to +6v.

In the +oR circuits, input 1 plus, input 2 plus, or input 3 plus causes current flow through the load transistor to bring the output plus.

Figure 6 summarizes characteristics (powering circuit and logic-performing circuit) of the most widelyused circuit groups.

In addition to the circuit characteristics discussed, a circuit group may use either positive or negative logic; also, the circuits may be translating or nontranslating.

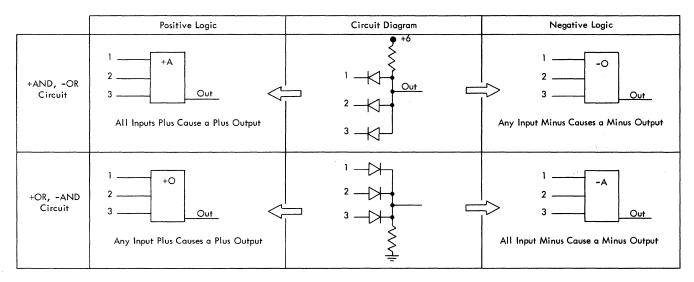

In the preceding discussion of logic-performing circuits, positive logic was assumed; that is, the up or more positive state of input and ouptut lines was considered more important, or active. The AND function was preceded by a plus sign and described as input 1 (plus), input 2 (plus), and input 3 (plus), causing a plus output. In many cases, it is desirable to use the down, or more negative, state of lines as the active

Figure 4. Transistor Operating Modes

level; thus often eliminating the need for inverters. When negative levels are considered active, the logic of a +AND is -OR (Figure 7); input 1 minus, input 2 minus, or input 3 minus causes a minus output. Similarly, a +OR is a -AND; input 1 minus, input 2 minus, and input 3 minus produce a minus output. Whenever the down or more negative state of circuit inputs is considered more important (active), the result is negative logic.

Positive logic – Up level active (+A, +O)Negative logic – Down level active (-A, -O)

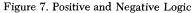

These descriptions of positive and negative logic show that any circuit can be used to make either positive or negative logic decisions; generally, machine logic is a mixture of the two. Some of the inverting circuit groups, particularly NOR (negated OR), are designed so that one basic circuit performs most machine logic. The scheme alternates between positive and negative logic to take advantage of the inverter powering circuit (Figure 8).

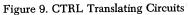

Translating circuits alternate NPN and PNP transistors to reduce the number of circuit components. In some CTRL circuits, for example, the output of an NPN transistor is an R line and is used as the input to PNP transistors; the output of a PNP transistor is an S line and is used as the input to NPN transistors (Figure 9). The two line types result from the difference in collector supply voltages for NPN and PNP transistors.

#### **DDTL Characteristics**

Computing equipment is built in wide ranges of size, speed, and complexity. As applications grow, so does the gap between the largest and smallest; the cheapest and most expensive; the fastest and slowest. No single circuit group can meet the cost, speed, reliability, and flexibility requirements of all machines; however, the DDTL circuit group is much more flexible than older groups and, therefore, covers a much wider range of applications. There are two types of powering circuits: inverters and emitter followers; there are three variations of the inverter circuit: basic (low-speed), lowpower (high-speed), and level setter; there are two kinds of collector load networks: clamped and unclamped. Including special-purpose circuits and all the standard circuit variations, the DDTL group comprises nearly 300 circuits.

The following paragraphs explain the general characteristics of standard DDTL circuits; details of specific circuits are presented under "Circuit Operation."

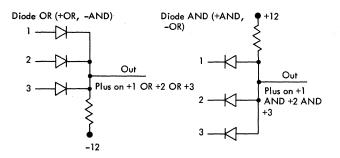

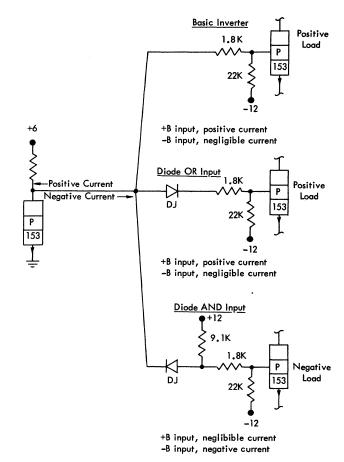

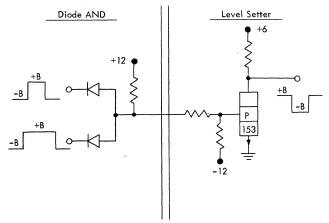

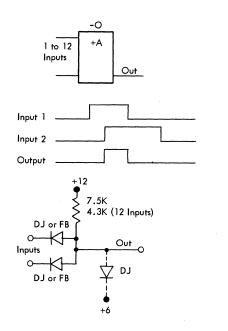

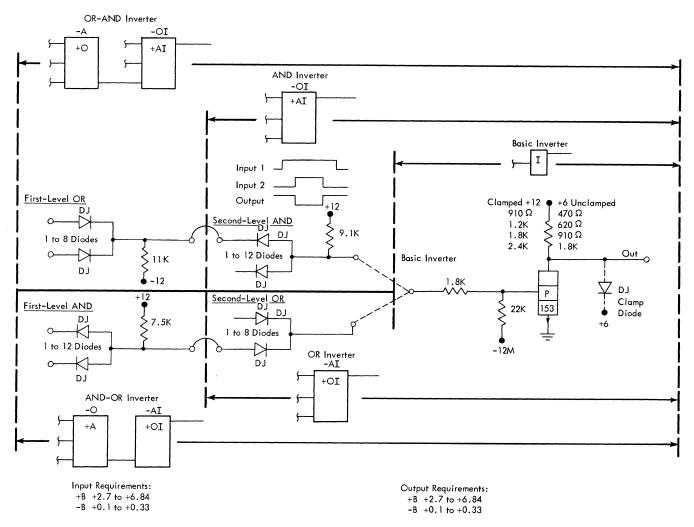

In DDTL circuits, diodes make the logic decisions. Two different diode circuits are used (Figure 10), and can be arranged in either single-level or double-level configurations. Single-level is one diode circuit between powering (transistor) circuits; double-level is two diode circuits between powering circuits (Figure 11). Double-level logic can be either diode AND's feeding a diode OR, or diode OR's feeding a diode AND. For simplicity, Figure 11 shows only two inputs to each diode circuit; most diode circuits, however, can have up to six, seven, or eight inputs, and a few can have as many as 12 inputs.

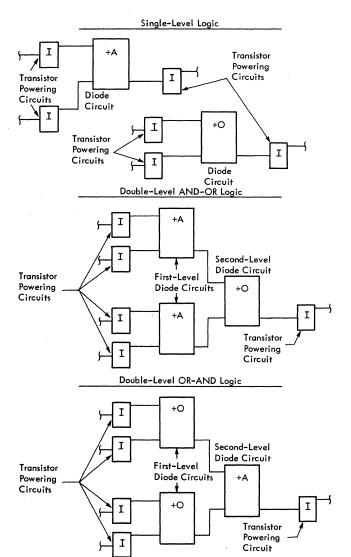

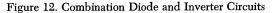

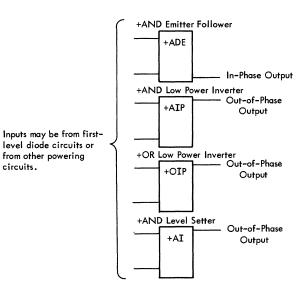

Although double-level logic is sometimes made up (shown in ALD's) of individual circuits like those shown in Figure 11, the second level of diodes is usually combined with a powering circuit such as an inverter (Figure 12). Diode logic is also combined with other DDTL powering circuits (Figure 13). Inputs to diode circuits included with powering circuits may be from other powering circuits as well as from first-level diode blocks (one or two levels of logic).

Note that the placement of a block output line in Figures 12 and 13 and in ALD's (automated logic diagrams) is significant: if the output level is in phase with the active state of the inputs (as is the case for all diode circuits), the output line is from the lower half of the block; out-of-phase outputs leave the upper half of a block. As previously explained, the sign of a

Figure 5. Logic-Performing Circuits

| Group | Principal<br>Powering<br>Circuit(s) | Saturating | Decision<br>Components | Comments                                                                                  |

|-------|-------------------------------------|------------|------------------------|-------------------------------------------------------------------------------------------|

| VMTL  | Inverter                            | Yes        | Diodes                 | First IBM transistor circuits. Converted tube circuits.                                   |

| DCM   | Split-Load and Grounded Base        | No         | Transistors            | Designed for maximum speed. First use: 7030                                               |

| ACM   | Split-Load and Grounded Base        | No         | Transistors            | Same concepts as DCM, but lower cost where slower speed acceptable.                       |

| CTRL  | Inverter                            | Yes        | Resistors              | Simple, low-cost circuits for slow-speed applications.                                    |

| CTDL  | Inverter                            | Yes        | Diodes                 | Three times faster than CTRL. Fills gap between CTRL and ACM.                             |

| SDTRL | Inverter                            | Yes        | Resistors              | Diffused mesa transistors in CTRL circuits.<br>Gives moderate speed from simple circuits. |

| SDTDL | Inverter                            | Yes        | Diodes                 | Uses PNP diffused mesa transistors.                                                       |

| DEFL  | Emitter Follower                    | No         | Diodes                 | Very high-speed. Uses Silicon transistors.                                                |

| DDTL  | Inverter                            | Yes        | Diodes                 | Simple circuits using NPN diffused mesa transistors.                                      |

Figure 6. Circuit Group Characteristics

Figure 10. DDTL Diode Circuits

2. If D AND E are plus, then F is plus.

3. If C OR F is plus, then G is minus.

Figure 11. Single-Level and Double-Level Logic

block tells whether the positive or the negative condition of inputs is active. Therefore, the reference for the system of output line placement is the sign of the block; thus, an in-phase output of a +A or a +O is plus, the out-of-phase output is minus.

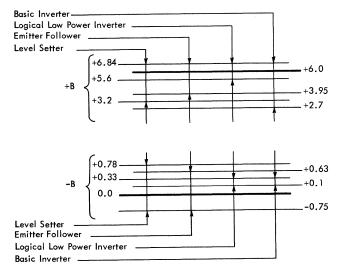

DDTL circuits are non-translating. The single line level, B, is near +6v, when up, and approximately 0v, when down; each of the DDTL powering circuits, however, has unique voltage tolerances for the up and down B levels in and out. For example, an acceptable +B level can be as low as +2.7v or as high as +6.84v.

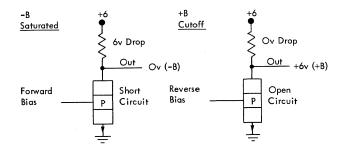

The simplest and most widely used DDTL powering circuit is the basic inverter (Figure 14). Either one or two levels of diode logic may be connected to the input of this circuit. In addition, the basic inverter may be used without diode logic to simply invert a line.

Note that the basic inverter has only four components; Figure 14 shows the general purpose of each component. The basic inverter operates as a switch; that is, with a +B input, the transistor is saturated and, therefore, is a short circuit; the output is approximately 0v. With a -B input, the transistor is cut off and, therefore, is an open circuit; the output is +6v.

The basic inverter load resistor can be one of several values. The proper value is selected depending on the number and type of loads (circuit inputs) connected to the output of the inverter. Loads can be either positive or negative; that is, a circuit may cause current to flow when given a +B (up) level or it may cause current to flow when given a -B (down) level (Figure 15). In DDTL, positive loads cause electron current to flow *into* the powering circuit; negative loads cause electron current to flow *out* of the powering circuit. Thus, positive loads lower the +B level by dropping voltage across the collector resistor; negative loads raise the -B level because they pull current from the transistor.

If the loads driven are all positive (for example, other basic inverters, Figure 15), the collector resistor

Figure 14. Basic Inverter

Figure 15. Types of Loads

value is decreased for an increased number of loads. That is, to maintain an acceptable +B level, the collector resistor of a basic inverter must be decreased in value for increased current passed through the resistor when the transistor is cut off. The value of a basic inverter collector resistor is scaled the opposite way for negative loads (current drawn when input is -B). When more negative loads are driven, a larger collector resistor is used; thus, the current that a transistor can carry in saturation is used to supply following circuits instead of simply generating heat in the collector resistor.

When a circuit drives both positive and negative loads, the value of the collector resistor must be a compromise. The compromise is necessary because *decreasing* the value of the collector resistor increases the number of positive loads that can be driven but decreases the number of negative loads that can be driven; *increasing* the collector resistor has the opposite effect.

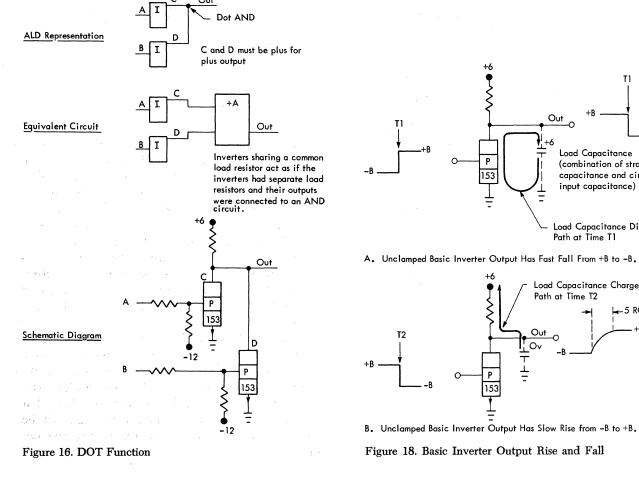

In addition to various load resistor values, two or more basic inverters may share the same load resistor. Known as a dot function, or dot or, in ddtl circuits this sharing of a common load takes the place of an AND circuit (Figure 16). The figure shows the logic of the por function referenced to the output of the circuits; that is, a DOT AND means that the equivalent logic is a +AND (or -OR) circuit substituted for the junction of the transistor collectors.

In Figure 16, basic inverters are used to illustrate the por function; the por function is not restricted to the basic inverter, however, and may be used with most circuits that contain a transistor. In ALD's, attention is usually called to a DOT function by an additional letter in the functional symbol; for example, two +AND inverters DOT OR'ed might be designated +AOI or +AAI. Because the sign of the DOT symbol is not designated, and because the symbol may be referenced to either the circuit inputs or the circuit outputs, the logic of these circuits is best determined by recalling (or drawing) the basic DDTL DOT as shown in Figure 16. Once you determine the convention for designating DOT functions within a particular machine, DOT logic is easily followed.

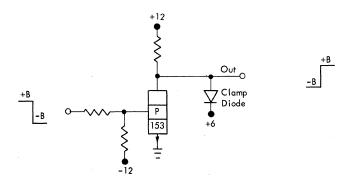

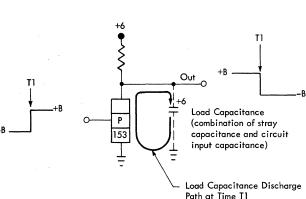

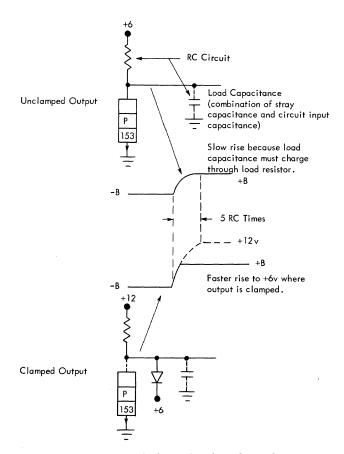

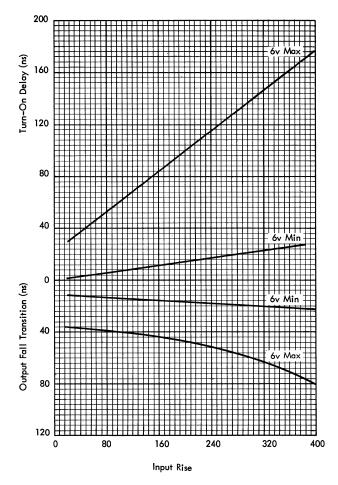

Another variation of the basic inverter is a clamped output (Figure 17). The clamped output is used when driving or blocks to improve the rise transition of the output signal. The rise transition at the output of unclamped basic inverters is slower than the fall transition (Figure 18). The fall transition is produced when

Figure 17. Basic Inverter with Clamped Output

12 (9-63)

-5 RC Times

+B

the input goes to +B and saturates the transistor (time T1, A in Figure 18). Before T1, the load capacitance (a combination of stray capacitance and the driven circuit input capacitance) was charged to +6vand must be discharged before a -B output can be obtained. At time T1, the saturated transistor is practically a short circuit across the load capacitance and, therefore, the capacitance discharges rapidly through the transistor. The slope of the fall transition is mainly determined by how fast the transistor saturates.

The output rise transition occurs at time T2 when the input falls to -B and cuts off the transistor (B in Figure 18). On this transition, the load capacitance must charge through the load resistor before the output is +B. Recall from the RC time constant theory that approximately five RC times are required for a capacitor to reach the applied voltage.

The clamped output improves the output rise transition because a greater voltage (+12) is used to charge the load capacitance (Figure 19). Because a capacitor

Figure 19. Rise Times of Clamped and Unclamped Outputs

charges to 63 percent of the applied voltage in one RC time, less than one RC time is required for the output of a clamped circuit to reach +B.

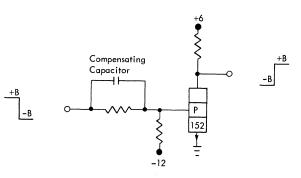

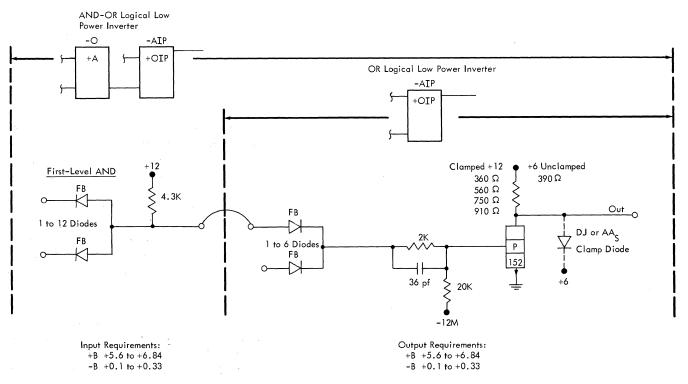

The logical low power inverter is another DDTL powering circuit. This circuit is faster than the basic inverter, and where it is used as the primary powering circuit, the logic is called high-speed DDTL, or compensated DDTL. Although the resistor values are different and a different transistor is used, except for the addition of a capacitor, the configuration of the lowpower inverter is identical to the configuration of the basic inverter (Figure 20). The compensating capacitor speeds the switching time of the circuit as follows.

Because the gain of a transistor is higher at low frequencies, lower frequencies are amplified more than high frequencies. If the input to a transistor is a signal with a sharp-rising transition, the leading edge of the output loses the steepness of the input. The compensating capacitor is a short circuit to the leading edge of the signal; this supplies an instantaneous change in base current that is very large compared to the base current that is supplied through the input resistor after the compensating capacitor has fully charged. A large, instantaneous base current causes a large output and compensates for the decreased gain of the transistor at high frequencies; hence "compensating" capacitor. Similarly, the compensating capacitor bypasses the input resistor on the fall transition, cutting the transistor off more quickly; however, the compensating capacitor affects the fall transition much less than the rise transition. On the fall transition, the transistor is cut off and the principal cause of slope comes from charging the load capacitance as explained in the discussion of clamped outputs.

The compensating capacitor speeds circuit operation by shorting the input resistor (for rapid changes); however, this same action makes the circuit more

Figure 20. Logical Low Power Inverter

susceptible to noise. Because diode logic connected to the input of the circuit reduces the noise problem, the low power inverter is never used without at least one diode.

As with the basic inverter, the collector load resistor of the low power inverter can be one of several values depending on the load driven. Also, low power inverters may share a common load network to form a **DOT AND**; the load network can be either clamped or unclamped.

To distinguish between the basic inverter (or level setter, discussed later) and the low power inverter, ALD blocks containing a basic inverter or a level setter are labeled I, AI, or OI; those containing low power inverters are labeled IP, AIP, or OIP.

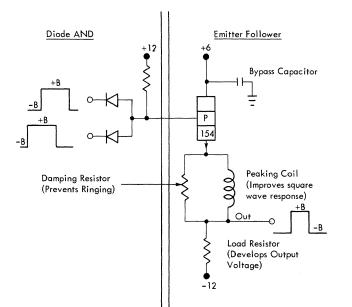

The emitter follower is another circuit used to power DDTL lines (Figure 21). Unlike the inverter circuits, the output of the emitter follower is in phase with the input, and the transistor is never saturated or cut off. Because the transistor is always conducting, the circuit output responds very rapidly to input changes. Because of the load capacitance, a peaking coil is used in the emitter circuit to further improve the squarewave response of the circuit.

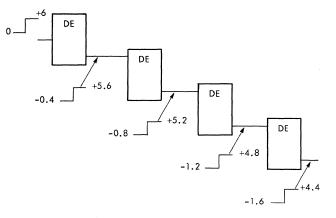

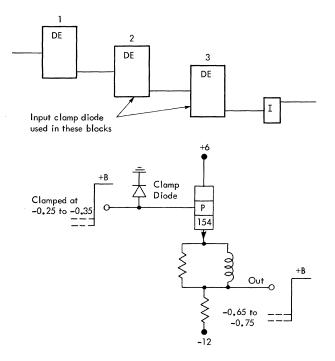

A disadvantage of emitter followers is that they shift the output signal an amount equal to the emitter-tobase voltage drop of the transistor. This shift is usually about 0.4v. If several emitter followers are used in series, the signal is soon degraded to the extent that it is not a reliable input for standard DDTL circuits (Figure 22).

Because emitter followers do not exactly reproduce input voltage levels, no more than three emitter followers can be used in series; another circuit, the level setter, is required to terminate the chain and restore the degraded signal (Figure 23). Except for resistor values, the level setter is identical to the basic inverter. Each circuit in an emitter follower chain (including the level setter) can have either one or two levels of diode logic. Depending on the configuration of diode logic used, the level shift (example, Figure 22) can be aggravated by the voltage drop of the diodes; this is partly responsible for the limit of three emitter followers in any one chain.

Figure 22. Characteristic Level Shift of Emitter Followers

Figure 23. Level Setting Circuit

Figure 21. Emitter Follower

Figure 24. Clamped Emitter Follower

As with basic inverters and low power inverters, emitter follower load resistors can be one of several values depending on the load driven. In addition, an input clamping diode is usually used in an emitter follower that is the second or third circuit of a chain. This clamping diode prevents shifting the -B level below approximately -0.75v (Figure 24).

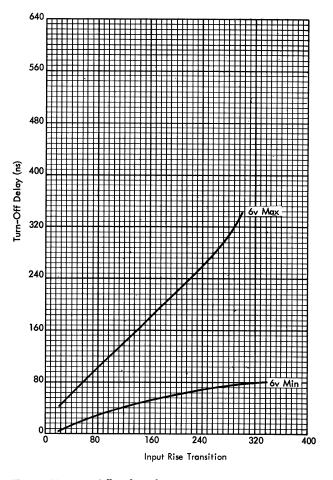

The primary characteristics of DDTL circuits are summarized in Figure 25. The "Circuit Operation" section explains standard DDTL circuits in more detail. If still greater detail is desired, refer to the Appendix for sample circuit characteristics such as currents, turn-on delays, turn-off delays, rise transitions and fall transitions.

| Transistors       | Double diffused (mesa) NPN germanium, operated<br>as switches (saturated or cut off) except for emitter<br>follower circuits. |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Decision Circuits | Single or double-level diode circuits.                                                                                        |

| Powering Circuits | 1. Basic Inverter<br>2. Low Power Inverter<br>3. Emitter Follower<br>4. Level Setter                                          |

| Line Level        | B Line (0 or +6) only (non-translating)                                                                                       |

| Logic             | Positive, negative, or mixed logic (+AND and +OR circuits provided)                                                           |

Figure 25. DDTL Characteristics

## **Circuit Operation**

Understanding a transistor circuit can be simply knowing the logic relation of the inputs to the outputs or it can involve knowing the power dissipation of components and the relation of loading and input transition times to circuit delays. Somewhere between these extremes is an understanding of how the circuit components use the input signals to generate the output signals, and the circuit input and output requirements that must be met for proper operation.

Because this manual is for those who must service, rather than design, machines that use DDTL circuits, the depth of circuit information in this section is generally restricted to:

1. Relation of circuit inputs to circuit outputs.

2. How the circuit converts input signals to output signals.

3. Important input and output requirements.

Sample detailed characteristics such as currents, delays, rise and fall transitions, and loading requirements are included in the Appendix for those who desire more detail than is presented in this section.

This manual describes only those DDTL circuits that are most widely used. Special circuits used by a particular machine are covered in the CE manuals for that machine.

#### **Fundamental Characteristics**

#### Line Levels

DDTL circuits are non-translating; the single line level, B, is near +6v when up, and approximately 0v, when down. The origin of the -B level is the collector of a saturated transistor whose emitter is connected to ground (Figure 26). The origin of the +B level is the collector of a cutoff transistor whose load resistor is connected to +6v.

There are four kinds of DDTL powering circuits: the basic inverter (low-speed or uncompensated DDTL), the logical low-power inverter (high-speed or compensated DDTL) the emitter follower, and the level setter. Each of these circuits has unique input voltage requirements (Figure 26). Although the nominal value for +B is 6v, note that an acceptable +B level may be as low as +2.7v or as high as +6.84v. Likewise, an acceptable -B level can be as low as -0.75v or as high as +0.78v.

(9-63)

16

Figure 26. B Levels

#### Single and Double Level Diode Logic

In DDTL, diode +OR circuits and diode +AND circuits make the logic decisions. These diode circuits can be arranged in either single-level or double-level configurations. Single-level is one diode circuit between powering (transistor) circuits; double-level is two diode circuits between powering circuits (Figure 11). Double-level logic can be either diode AND's feeding a single diode OR or diode OR's feeding a single diode AND. A double-level configuration of OR's into an OR, or AND's into an AND is never used.

Diode circuits (first and second level) are generally limited to six inputs, although in a few cases, diode circuits have up to 12 inputs. Inputs to a second-level circuit can be from transistor circuits as well as from first-level diode circuits (Figure 13).

#### Loading

The DDTL powering circuits can have one of several load resistors. The load resistor is the resistor in the collector circuit of an inverter, or the resistor in the emitter circuit of an emitter follower. The load resistor value is selected depending on the number and type of loads (circuit inputs) driven by a powering circuit.

Loads can be either positive or negative. A positive load is one that causes current flow when given a +Blevel; a negative load causes current flow when given a -B level. In DDTL, the direction of current flow caused by a positive load is opposite to the direction of current flow caused by a negative load.

Consider an inverter powering circuit and the two kinds of loads (Figure 15). Positive loads lower the +B level by dropping voltage across the collector (load) resistor; negative loads raise the -B level by dropping voltage across the transistor. To drive more positive loads, the load resistor must be decreased to prevent excessive voltage drop that would result in a +B level too low to operate the driven circuits. The limit for lowering the collector resistor is set by the maximum current that can be carried by the transistor; that is, as the collector resistor is lowered, more current must be carried by the transistor when it is turned on.

As an example of positive loading, assume that a basic inverter is to drive other basic inverters. With a collector resistor of 470 ohms (minimum value used) 7 ma (assuming an unclamped collector) of positive current will drop the +B level to +2.7v; this is the minimum allowable input to basic inverters.

$470\Omega \ge 7$  ma = 3.3v

6.0v - 3.3v = 2.7v

Because each basic inverter draws about 1.5 ma with a +2.7v input, one to four basic inverters can be driven. With the 470-ohm collector resistor, no negative loads can be driven because this resistor draws the maximum allowable current through the transistor when it is saturated.

The value of a basic inverter collector resistor is scaled the opposite way for negative loads. When more negative loads are driven, a larger collector resistor is used; thus, the current that a transistor can carry in saturation is used to supply the following circuits instead of simply generating heat in the collector resistor.

As an example of negative loading, assume that a basic inverter is to drive diode AND inputs that are connected to other basic inverters (Figure 15). If the collector resistor is 1.8K (maximum value used), an external current of 10.2 ma (negative current) can be safely drawn through the transistor. This current is in addition to that drawn by the 1.8K collector resistor. Because each AND input draws approximately 1 ma, one to ten of these inputs can be driven.

When a circuit drives both positive and negative loads, the value of the collector resistor must be a compromise. The compromise is necessary because decreasing the value of the collector resistor increases the number of positive loads that can be driven but decreases the number of negative loads that can be driven; increasing the collector resistor has the opposite effect.

#### **DOT Function**

By sharing a common collector resistor, DDTL inverter powering circuits can perform an additional logic decision. As many as six inverter collectors may be connected together and share a single resistor (Figure 16). Known as a DOT function, or DOT OR, in DDTL circuits this sharing of a common load resistor takes the place of a +AND or a -OR. In a DOT configuration, the conduction of any transistor drops the output to -B; therefore, the logic performed by the DOT is -OR. Considering the DOT in positive logic, all transistors must be cut off to obtain a +B output (+AND).

In ALD's, attention is usually called to a por function by an additional letter in the functional symbol; for example, two +AND inverters DOT OR'ed might be designated +AOI or +AAI. Because the sign of a DOT symbol is not designated, and because the symbol may be referenced to either the circuit inputs or the circuit outputs, the logic of these circuits is best determined by the recalling (or drawing) the basic DDTL DOT as shown in Figure 16. Once the convention for designating DOT functions within a particular machine is determined, the DOT logic is easily followed.

#### **Basic Circuits**

#### **Diode Circuits**

There are two DDTL diode circuits: +AND and +OR (Figure 27). These diode circuits are primarily for first-level or single-level use and are shown as a separate block in Systems. Second-level diode circuits are normally part of an inverter or emitter follower powering circuit and are included in the Systems block with the powering circuit (e.g., +OI, +ADE).

The limit on the number of inputs used in diode circuits is set because of diode back-current. Although reverse biased diodes have a high resistance, a small current flows from the anode to the cathode. For example, consider the diode +AND with one input at

Figure 27. Diode Circuits

-B and all other inputs at +B. The -B input will hold the common anode at 0v; a small reverse current will flow through each of the remaining diodes and these currents will add to the current flowing through the one forward-biased diode. These back currents cause additional loading on the one -B input and, if too many inputs are added, the maximum current capacity of this diode will be exceeded.

#### **Basic Inverter**

The basic inverter is the simplest DDTL powering circuit. It is the most widely used powering circuit in uncompensated (low-speed) DDTL logic.

The basic inverter can be used alone, or with one or two levels of input diode logic. Because the diode circuits may be either +AND or +OR, five basic inverter configurations are used (Figure 28):

- 1. Basic inverter (1).

- 2. AND inverter (+AI).

- 3. OR AND inverter (+0, +AI).

- 4. OR inverter (OI).

- 5. AND OR inverter (+A, +OI).

Considering the basic inverter used alone, a -B input places the transistor base at about -0.6v to -0.8v, depending on whether the -B input is near +0.1v or +0.33v. This base voltage results from the voltage divider from -12M (1.8K and 22K resistors). The negative bias is sufficient to keep the transistor cut

off; the output is +B from the collector supply voltage through the collector resistor.

With a +B input, the transistor base is driven positive and the transistor saturates. When saturated, the transistor draws base current sufficient to place the base at +0.44v. The 1.8K input resistor limits this base current to a safe value for the range of acceptable +B inputs (+2.7v to +6.84v).

The basic inverter may have either a clamped or an unclamped collector circuit. The unclamped circuit is simply a resistor to +6v. The resistor is one of four values, depending on the load to be driven (Figure 28). The clamped circuit is a resistor to +12v and a clamp diode that prevents the output from rising higher than about +6.84v. The extra 0.84v (above 6.0v) is caused by the drop of the DJ clamp diode and allowable variations of the +6v power supply. The resistor used in the clamped circuit can also be one of four values depending on the load to be driven.

The clamped output gives a faster rise from -B to +B as explained previously (Figure 19). In addition, a clamped basic inverter will drive a greater number of positive loads than an unclamped inverter. Recall from the discussion of loading that the limit for lowering a collector resistor (to increase positive load driving capabilities) is set by the maximum current capability of the transistor. Consider clamped and unclamped circuits such as shown in Figure 19. If the collector resistor in the clamped circuit is twice as

Figure 28. Basic Inverter with Diode Logic

large as the collector resistor in the unclamped circuit, an equal amount of current will flow through the two resistors when the transistors are saturated. When the transistors are cut off, the clamped load resistor can drop 9.3v before the lower +B limit of +2.7v is reached; the unclamped resistor can drop only 3.3v. Because the clamp circuit resistor is twice as large as the unclamped resistor, the current that drops the unclamped output 3.3v will drop the clamped output 6.6v. A drop of 3.3v is the limit for the unclamped output and the +B level is +2.7v. A drop of 6.6v on the clamped output, however, is not the limit and the +B level is  $\pm 12v - 6.6v = \pm 5.4v$ . Additional positive loads can be tied to the clamped output until the +B level drops to  $\pm 2.7v$ .

Consider the AND inverter (Figure 28). If any input is -B, the common anode of the diodes is clamped to

-B and the basic inverter receives a -B input to supply a +B output. If all inputs are +B, the +12vsource supplies the basic inverter with a plus voltage through the 9.1K resistor. The basic inverter transistor is driven to saturation and the output is -B. In this condition, the input diodes are reverse biased because the transistor base is clamped to about +0.44v when the transistor is saturated. The voltage divider, consisting of the 1.8K and the 9.1K resistors, places the input diode anode at about +1.9v and the diodes are cut off.

Inputs to the AND inverter can be from transistor circuits or from first-level or's. In the latter case, the entire circuit becomes an OR-AND inverter (Figure 28).

In the +oR inverter, any +B input clamps the common diode cathodes to +B, reverse biasing all other input diodes. The output of the basic inverter is -B.

If all inputs are at -B, the diode cathodes follow the -12M supply down to the most positive -B input; this input clamps the cathodes to its voltage. The -B input to the basic inverter cuts off the transistor, causing a +B output.

Inputs to the OR inverter can be from transistor circuits or from first-level AND's. If first-level AND's are used, the circuit becomes an AND - OR inverter (Figure 28).

#### **Logical Low Power Inverter**

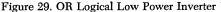

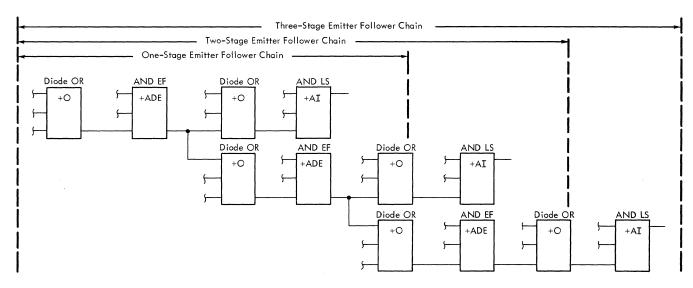

The logical low power inverter is the primary powering circuit for compensated (high-speed) DDTL logic. The circuit configuration is similar to the basic inverter; however, note the following differences (Figure 29):

- 1. Different transistor.

- 2. Different resistor values.

- 3. Addition of a compensating capacitor.

- 4. Cannot be used without diode logic.

- 5. Different input and output requirements.

The logical low power inverter is faster than the basic inverter primarily because of the compensating capacitor. This capacitor speeds the switching time of the circuit because it shorts the input resistor during signal transitions. This shorting supplies a momentary large base current that forces the transistor to react faster. Although the compensating capacitor affects both rise and fall transitions, the output rise transition (input fall) is not improved as much as the fall transition. A clamped output is used when a sharper rise transition is required. Refer to the "DDTL Characteristics" section for a more detailed discussion of the compensating capacitor.

The operation of the low power inverter is identical to the operation of the basic inverter: a - B input cuts the transistor off and the output is +B from the collector supply voltage; a + B input saturates the transistor and the output is -B (Figure 29).

As with the basic inverter, both clamped and unclamped collector circuits are used. Also, the load resistor value is changed to meet the requirements for the number and type of loads driven.

20 (9-63)

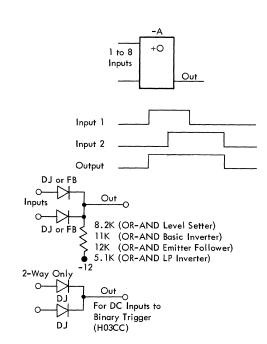

Either one or two levels of diode logic can be used at the input of the low power inverter. As with the basic inverter, the double level configurations are AND – OR inverter (Figure 29) and OR – AND inverter (Figure 30). The diode circuits perform logic exactly as the diode circuits described for the basic inverter. Note, however, that these circuits are not interchangeable with the diode circuits used with the basic inverter; a different type of diode is used and the resistor values are different.

Because of the compensating capacitor, the logical low power inverter is more sensitive to noise than the basic inverter. To reduce the possibility of noise pulses operating these circuits, input signals to the low power inverter must pass through at least one diode. If the circuit is used simply as an inverter, a +OIP, or a +AIP with only one input diode is used. In this case, the Systems block will have only one input and may be labeled IP.

Systems blocks containing +OIP's and +AIP's are sometimes labeled +O, +A, and I, OIP +OI, +AI, and I. These cases generally occur where an entire machine uses compensated DDTL (no basic inverters) or where there is a DOT function. Because a DOT function adds an additional letter to the functional symbol, the Systems block limit of four characters is exceeded when a +AIP or a +OIP is DOT'ed. For example, in one convention used, a DOT'ed +OIP (+OOIP) is shortened to +OO; a DOT'ed +OI (basic inverter) has its full designation of +OOI.

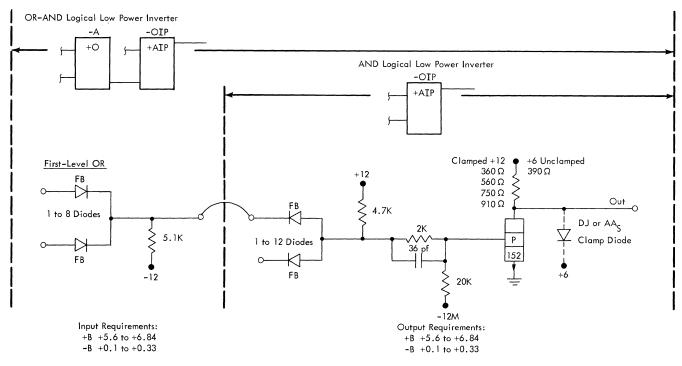

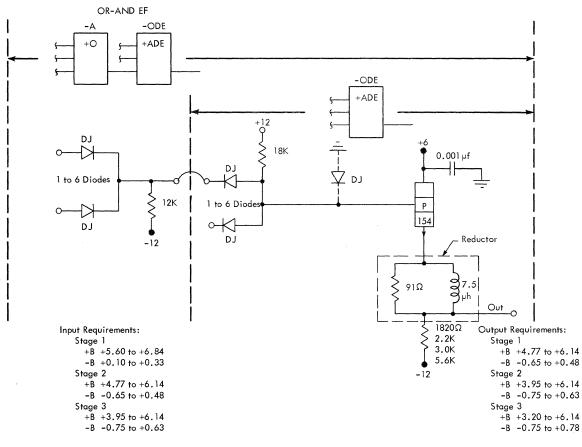

#### **Emitter Follower Chain**

Emitter follower chains consist of emitter followers and level setters. Because emitter followers shift the input signal an amount equal to the base-to-emitter drop of the transistor used, the purpose of the level setters is to restore the degraded B level at the end of the emitter follower chain. The chains are limited to three emitter followers (Figure 31). In an emitter follower chain, each emitter follower and the level setter can have one or two levels of diode logic.

The speed of an emitter follower chain is comparable to the speed of an equivalent number of logical low power inverters; therefore, these circuits can be used in compensated logic. Like the low power inverter, signals into an emitter follower must pass through at least one diode. However, unlike the low power inverter, only a +AND emitter follower is used. The only double-level logic configuration is the OR -AND emitter follower (Figure 32).

Figure 30. AND Logical Low Power Inverter

Figure 31. Emitter Follower Chain

Figure 32. AND Emitter Follower

An emitter follower transistor always conducts and is never saturated or cut off. The circuit responds rapidly to input changes because the transistor does not have to be brought out of saturation or cut off to the opposite extreme. Unlike inverters, the emitter follower load resistor is in the emitter circuit (Figure 32) and the output is in phase with the input. Note that the load resistor can be one of four values depending on the number and type of loads driven.

The DDTL emitter follower operates much the same as a tube cathode follower. As the input goes to +B, the transistor conducts harder dropping more voltage across the load resistor until the emitter voltage closely approximates the base voltage. The emitter voltage, however, is slightly negative (about 0.4v) with respect to the base. This is the bias, or the base-to-emitter voltage drop, of the transistor. On the signal swing from +B to -B, the transistor conduction reduces until the emitter voltage is again about 0.4v more negative than the base. The coil resistor combination (reductor) in the emitter circuit helps compensate for the capacitance of the load and thereby improves the squarewave response of the circuit. The 0.001 uf bypass capacitor prevents coupling the rapid current changes to other circuits.

The DJ clamp diode at the transistor base is used only if the circuit is the second or third emitter follower in a chain. This diode prevents the base voltage from going more negative than approximately -0.3v(drop of DJ diode). By using the clamp diode, the -Boutput of second and third stage emitter followers will not go below -0.75v (drop of DJ diode plus transistor emitter-to-base drop).

To restore the degrated B level from emitter followers, a level setter (Figure 33) terminates each chain. Except for resistor values, the level setter is identical to the basic inverter. Note that this difference of resistor values results in different input voltage requirements; these voltages match the B levels out of emitter followers.

Figure 33. Level Setter

A level setter may be used alone or with one or two levels of diode logic. The configurations used are level setter (1), and level setter (+AI), and OR -AND level setter (+O, +AI). As with the basic inverter, the output may be either clamped or unclamped.

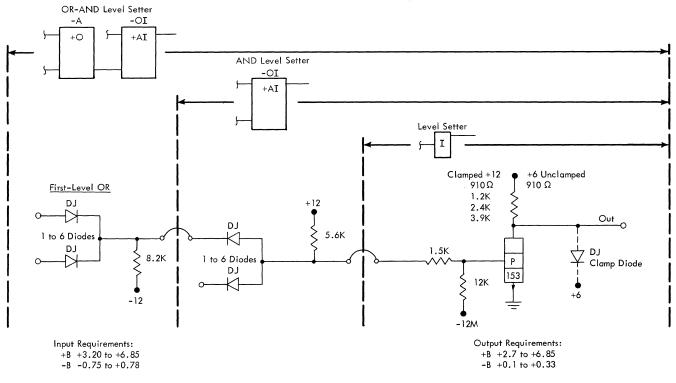

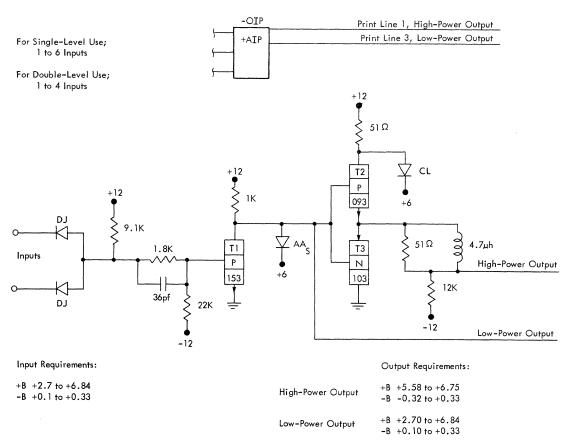

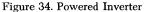

#### **Powered Inverter**

The powered inverter (Figure 34) is used to drive loads that are too great for an inverter or a level setter. The circuit has two out-of-phase outputs; one is a lowpower output, the other is a high-power output.

This circuit is a combination of a clamped AND low power inverter and a pair of complementary emitter followers. The inverter works the same as the low power inverter and the low power output is from this circuit. The low power inverter output also feeds the complementary emitter followers. The output from the emitter followers is never passive; one transistor drives it in the positive direction and the other, in the negative direction. When the low power inverter output is +B, T2 conducts to bring the common emitter circuit (and the output) to approximately the same voltage applied to the T2 base. (If the T2 input is too positive, the cL diode will clamp the T2 collector, thereby limiting the +B output to about +6.75v.) In this state, T3 is cut off because its base is positive with respect to its emitter by an amount equal to the emitter-to-base voltage drop of T2. As the low power inverter output goes to -B, T3 turns on and T2 is cut off by the emitter-to-base voltage drop of T3.

#### **Triggers and Latches**

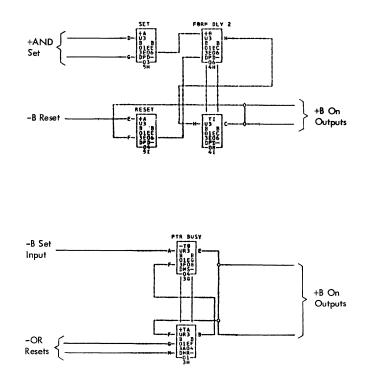

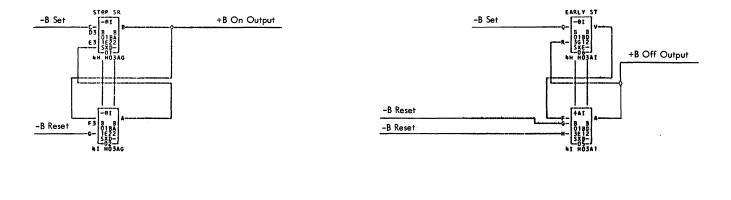

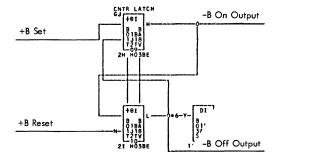

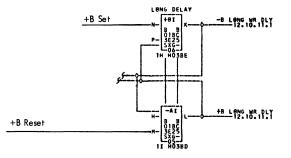

Triggers and latches are bi-stable circuits that store one of two conditions. Among their many applications, they are used for registers, counters, and rings.

A trigger is a bi-stable multivibrator and usually requires an AC shift (trigger) to change it from one state to the other. Included in the circuit, however, there may be provisions for gating (AND function) and

for DC sets and resets. This circuit is also called a flip-flop.

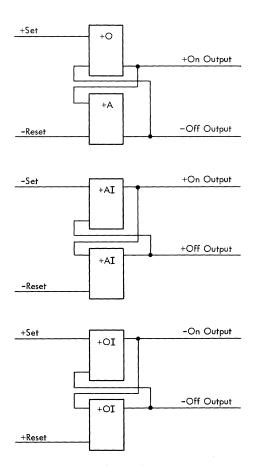

A latch is a DC device, usually made up of an AND and an OR, two AND'S or two OR'S (Figure 35). The output of each half of a latch is one input to the other half. This arrangement is called cross-coupling and the lines from one half of the latch to the other half are called feedback or latchback lines. The latchback lines hold the latch in the state caused by the last active input (set or reset), even if this input has returned to its inactive state. The state of a latch is changed by breaking the active latchback loop; this, in turn, activates the other latchback loop.

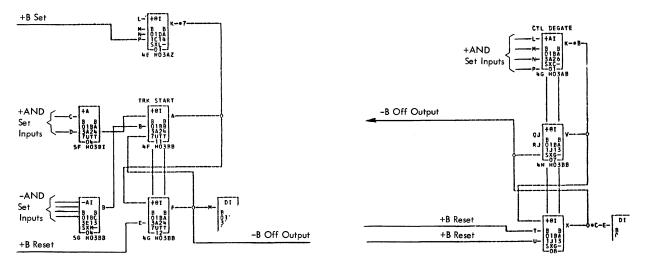

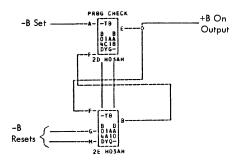

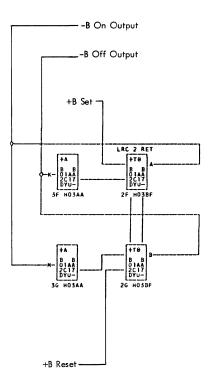

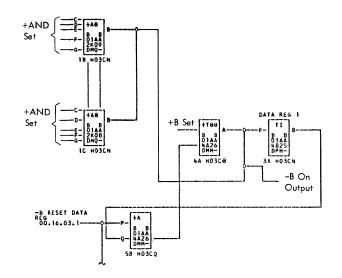

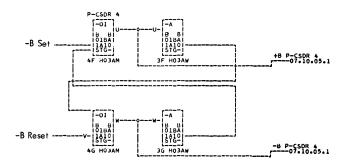

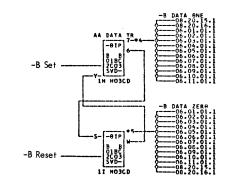

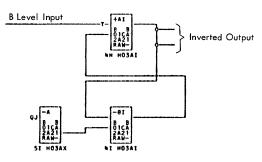

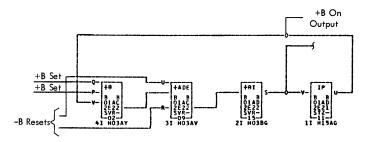

Three common DDTL triggers and a latch are described in this section. The latch is one shown as a single block in Systems diagrams. Many other latches are used; however, these are made up of two or more standard circuits with the cross coupling shown on the Systems diagrams. A number of latch examples taken from Systems are shown and described in the "Packaging and ALD Information" section of this manual.

Figure 35. Example Latches

#### **Binary Trigger**

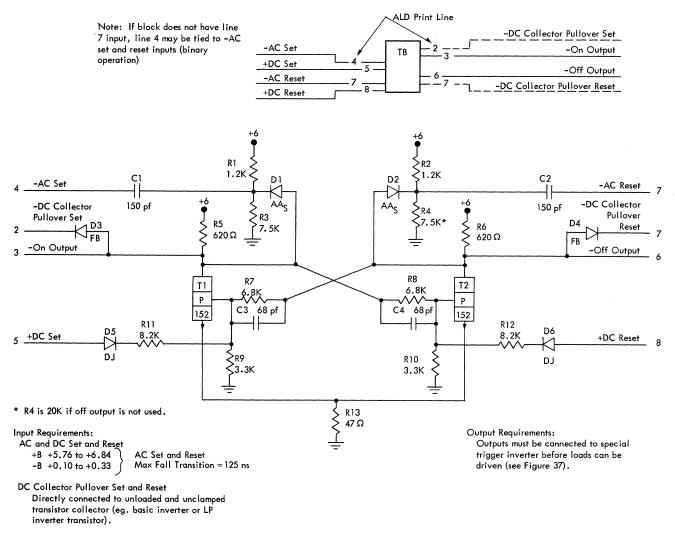

The binary trigger is the simplest and most commonly used DDTL trigger. The circuit has only two transistors (Figure 36).

The ALD representation of this circuit is shown at the top of the figure. Note that input and output lines are labeled according to the vertical position where they enter or leave the block. This designation of the lines is necessary because card pin letters are unique for a particular card; a DDTL circuit is not restricted to a particular card. In fact, in most cases, a given circuit is packaged on a great number of different cards. In addition, a circuit may be duplicated several times on one card; each circuit on a card necessarily has unique input and output pins.

The binary trigger has -AC set and reset inputs, +DC set and reset inputs, and sometimes has collector pullover set and reset inputs. The two AC inputs may come from separate sources, or they may be connected together and driven from a single source. In the latter case, each minus shift causes the trigger to change state; if the first shift turns the trigger on, the second will turn it off, the third will again turn it on, and so forth. This change of status from a single input is called binary operation, or complementing the trigger. When this arrangement is used, the Systems block will either show the single AC input connected to both 4 and 7 or connected to only 4 with no input at 7. The AC input must have a fall transition of 125 ns or less, measured from the 10 percent to 90 percent points on the waveform.

The DC inputs cannot be connected together to cause binary operation of the trigger. These inputs must be driven from separate sources. Both the AC and the DC inputs must be driven from a clamped inverter (or level setter) circuit.

Like the DC inputs, the collector pullover inputs must be driven from separate sources. Each of these inputs is a DOT connection to one of the trigger transistors. For example, assume that a collector pullover transistor is connected to input 2 (Figure 36). If either T2 or the collector pullover transistor conducts, the on output (3) is -B. The feedback from the on output (T1 collector) to the T2 base cuts off T2.

As previously discussed, simultaneous AC set and reset inputs change the state of the trigger. Simultaneous DC set and reset inputs, or simultaneous collector pullover set and reset inputs hold both on and off outputs at -B. Also, both outputs are active if one transistor is held in conduction by a DC input and the other output held at -B by a collector pullover. In these cases, the final state of the trigger is controlled by the last remaining active input.

Figure 36. Binary Trigger

The operation of the binary trigger is as follows (Figure 36). Assume that the trigger is off; transistor T2 is conducting and its current sets the common emitters slightly positive (about +1.0v). The T2 collector is slightly positive with respect to the common emitters because of the voltage drop across the transistor. The T2 collector is about +1.5v. The voltage divider consisting of R7 and R9 places the T1 base at about +0.5v (one-third of the T2 collector voltage). Because the T1 base is 0.5v negative with respect to the common emitters, T1 is held cut off.

With T1 cut off, its collector is positive and this voltage is applied through R8 to keep T2 in full conduction. In this state, D2 is reverse biased; a reset input at 7 would not be coupled through D2 and, therefore, would not affect the circuit.

With the trigger off, assume that a -AC set input is received (4). Diode D1 is forward biased; the nega-

tive shift is coupled through D1 and R8 to the T2 base, cutting off T2. The common emitters go to ground potential, and at the same time, the T2 collector goes positive driving the T1 base positive through R7. Transistor T1 is forward biased and begins conducting. The common emitters go slightly positive again, this time because of the T1 conduction. The low T1 collector voltage through R8 holds T2 cut off, the same way that T1 was previously held off by the T2 collector. The on output is near ground and the off output is at +6v.

Capacitors C3 and C4 speed the switching time of the transistors by shorting the base resistors during transitions.

If the AC set and reset inputs are tied common, a negative shift will reach only the conducting transistor base because one of the two input diodes (D1 or D2) is always reverse biased. A DC input forces the appropriate transistor into conduction by driving its base positive. Once conduction has started, the low collector voltage cuts off the other transistor.

A collector pullover input pulls the collector of the non-conducting transistor to -B. This voltage cuts off the conducting transistor, allowing its collector to rise to +B. The positive collector voltage brings the other transistor into conduction and the trigger remains in its new state even though the pullover transistor is turned off.

The binary trigger cannot directly drive standard DDTL circuits for two reasons:

1. The -B output of the trigger is more positive than the acceptable limit for standard circuits.

2. Loads would upset the balance of the circuit unless the on and off output were loaded exactly the same.

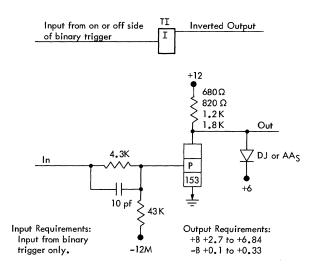

A special circuit, the binary trigger inverter (Figure 37), is used as a buffer between the binary trigger and the load to be driven. This circuit operates the same as a clamped low power inverter, but different resistor values are used to compensate for the abnormal -B level from the binary trigger.

If a binary trigger inverter is used only on the on output of the binary trigger, resistor R4 in the binary trigger (Figure 36) is changed from 7.5K to 20K. This resistor change adds positive loading to the off output to keep the trigger balanced.

Figure 37. Binary Trigger Inverter

#### **Control Trigger**

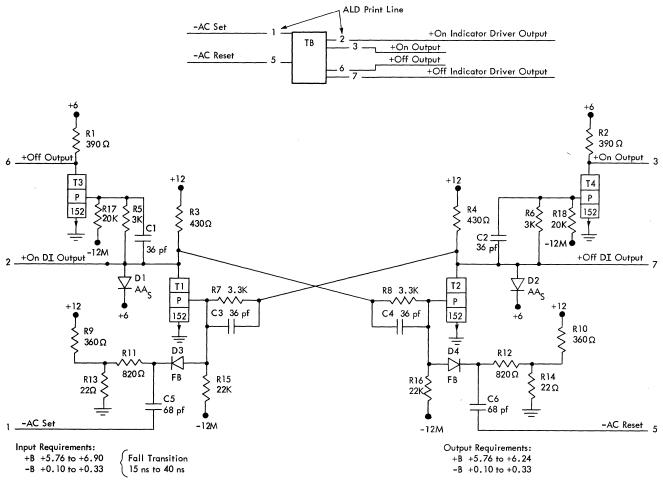

The control trigger is a four-transistor circuit, operated only by negative Ac shift inputs (Figure 38). For operation below 1 mc, clamped inverters (including level setters) may drive the input; for operation over 1 mc (up to 3 mc), a pulse generator, and possibly a cell driver, must be used. These two circuits are described in the "Shift Cell Circuits" section.

As with the binary trigger, the set and reset inputs to the control trigger can be driven from separate sources, or these inputs (1 and 5) can be tied common and driven from a single source for binary operation.

Transistors T1 and T2 make up the multivibrator portion of the circuit. The common emitter circuit used in the binary trigger is eliminated by introducing a negative bias through resistors R15 and R16. The collectors of T1 and T2 are returned to +12v and clamped to +6v; this makes it possible to drive indicator driver circuits directly from the multivibrator outputs.

Transistors T3 and T4 are trigger inverters for the off and on sides of the multivibrator; these circuits take the place of the external trigger inverters used with the binary trigger. Because trigger inverters are included in the circuit, the control trigger can drive loads directly.

Assume the trigger is off (Figure 38); transistor T1 is conducting and its collector is between  $\pm 0.10v$  and  $\pm 0.33v$ . This -B level is supplied through R5 to the T3 base and through R8 to the T2 base. Because of the voltage divider to -12M, consisting of R5 and R17, T3 is held cut off. Because of the voltage divider to -12M, consisting of R8 and R16, T2 is held cut off. The off output (6) from the T3 collector is  $\pm B$ .

Because transistor T2 is cut off, its collector attempts to go to +12v, but is clamped to near +6v by diode D2. The positive T2 collector voltage is supplied through R7 to keep T1 in full conduction and through R6 to keep T4 in full conduction. The on output (3) from the T4 collector is -B.

Assume that a negative shift arrives at the set input (1) or at both set and reset inputs (1 and 5). In this condition (trigger off), diode D4 is reverse biased so that if inputs 1 and 5 are common, a negative shift will reach only the T1 base. The negative shift is coupled through C4 and D3 to the T1 base, cutting off T1. As T1 cuts off, its collector goes positive turning on T2 and T3. The T2 collector drops to -B holding T1 and T4 cut off. The trigger is now on; the on output (3) is +B and the on DI output (2) is +B.

Capacitors C1, C2, C3, and C4 speed the switching time of the circuit by shorting the transistor base resistors during transitions.

Figure 38. Control Trigger

#### **AC Trigger**

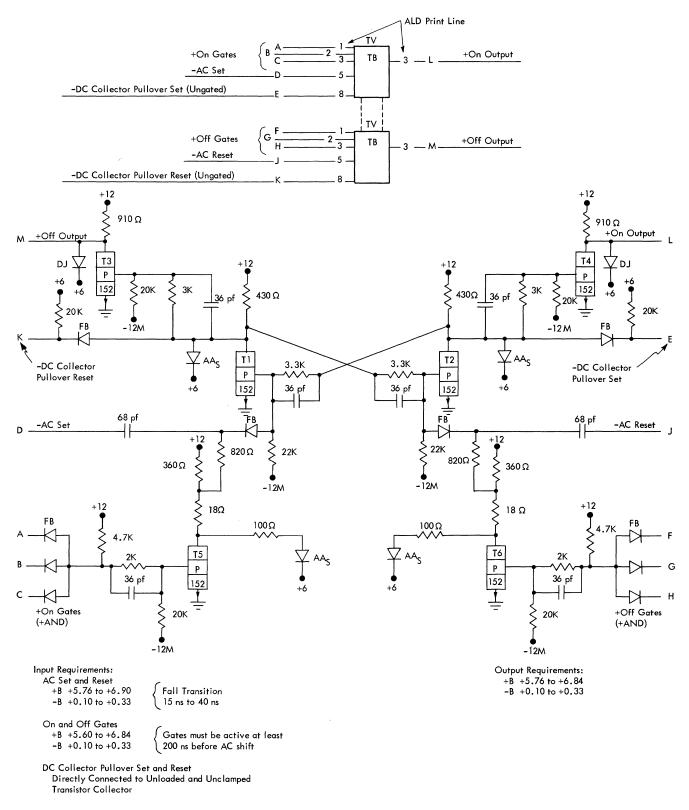

The AC trigger is a six-transistor circuit with AC set and reset inputs and collector pullover set and reset inputs (Figure 39). There are two major differences between the AC trigger and the control trigger:

1. AC trigger has collector pullover inputs.

2. AC trigger has AC inputs gated.

Only these differences are discussed in detail; refer to "Control Trigger" for a complete explanation of the trigger.

The portion of the AC trigger consisting of T1, T2, T3, and T4 is essentially the control trigger. The collector pullover inputs (K and E) on the AC trigger are the major differences. These pullover inputs operate the same as the binary trigger pullover inputs. For example, assume that the trigger is off (Figure 39). Transistor T1 is conducting and the -B level at its

collector is holding T3 and T2 cut off. The +B level at the T2 collector is holding T1 and T4 in full conduction. The on output (L) is at -B; the off output (M) is at +B. A collector pullover set input consists of an inverter transistor collector por'ed to input E. If this pullover transistor is turned on, conduction through the 20K resistor will drop input E to -B. This minus level is coupled through the diode to the T2 collector. The minus voltage at the T2 collector turns off transistors T1 and T4.

When transistor T1 turns off, its collector goes positive turning on T2. The trigger is now on, and will remain in this state even though the pullover transistor is turned off.

The T5 circuit is a +AND inverter used to gate the AC set (D) input. The T6 circuit is a +AND inverter used to gate the AC reset (J) input. Because these

Figure 39. AC Trigger

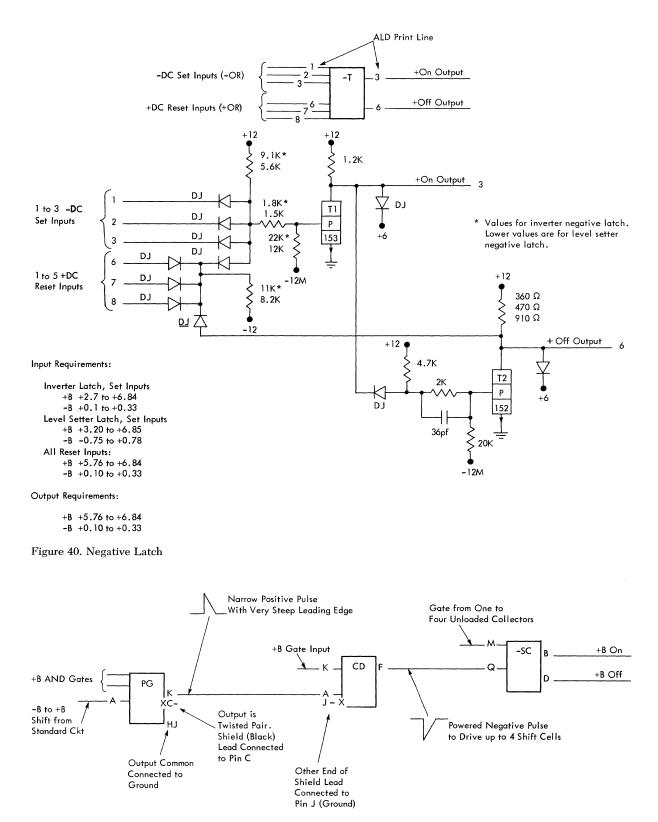

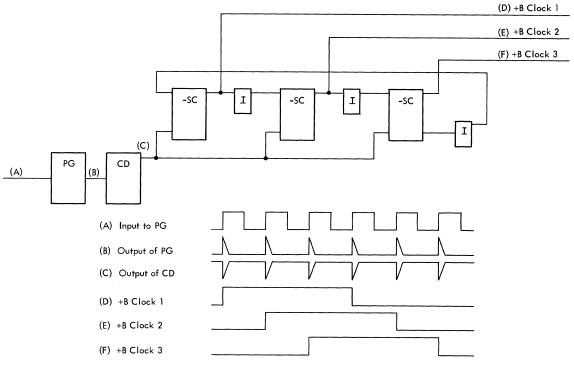

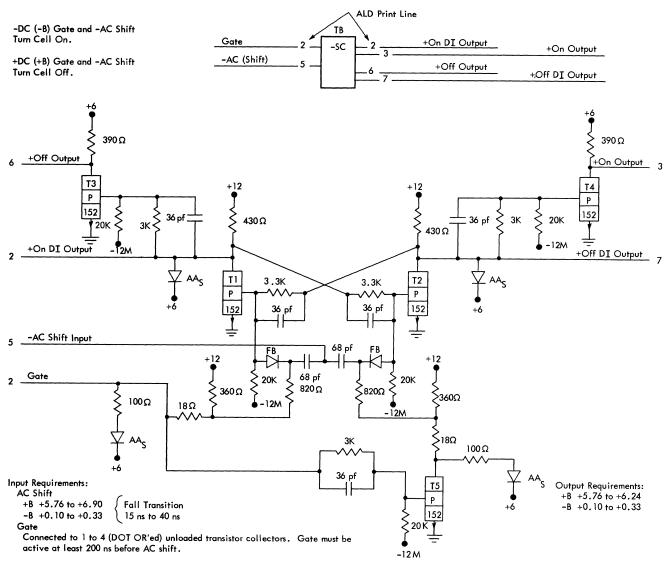

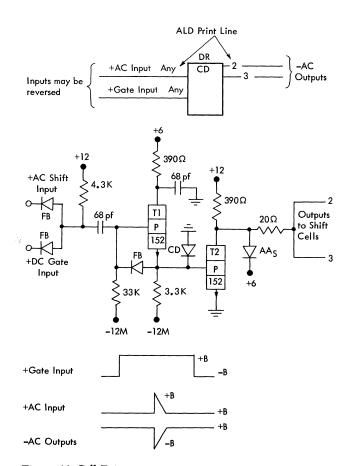

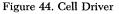

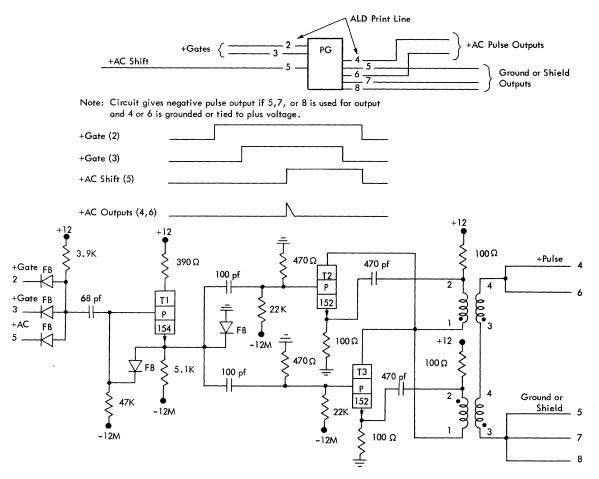

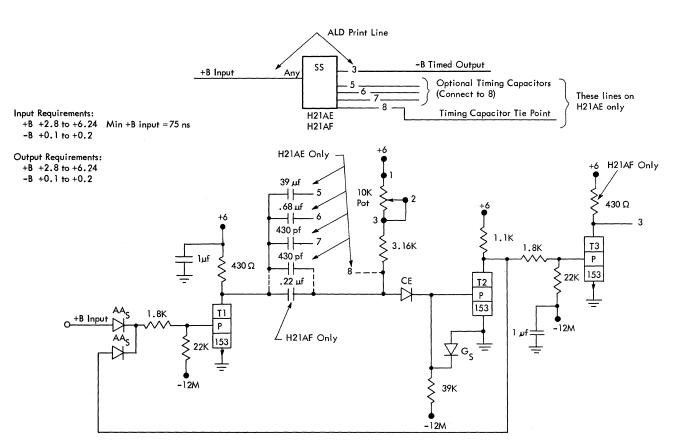

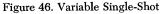

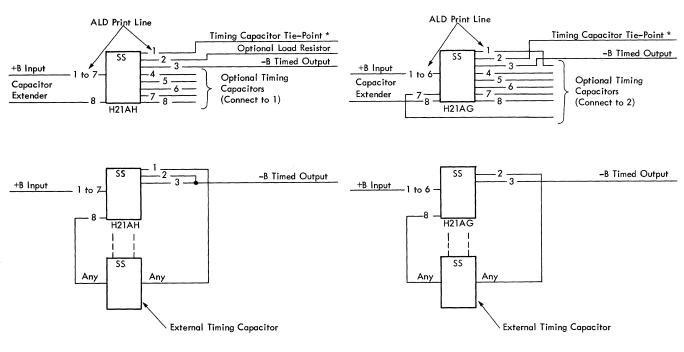

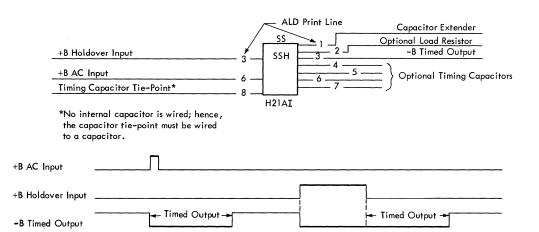

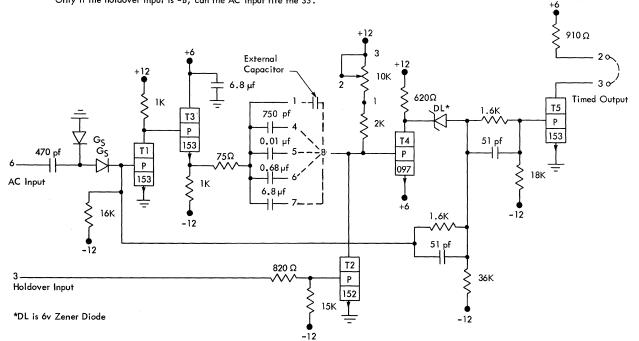

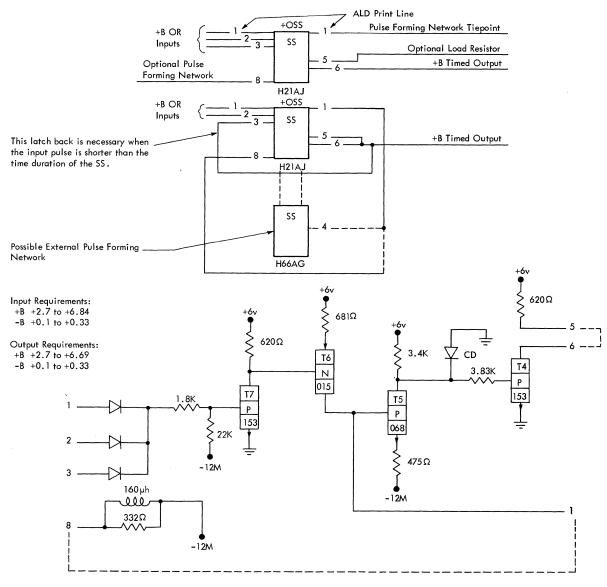

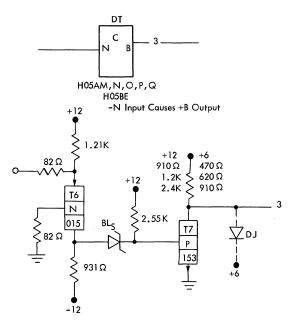

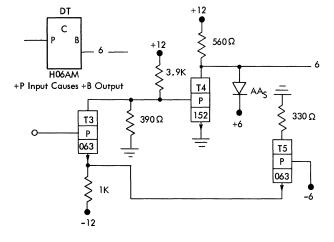

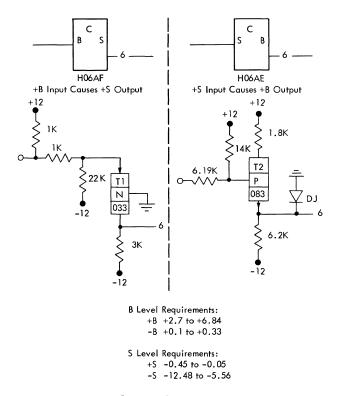

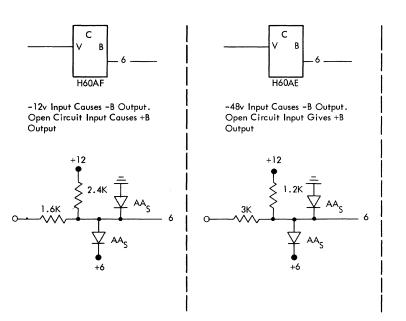

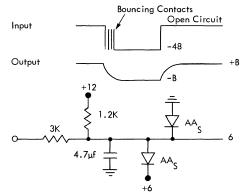

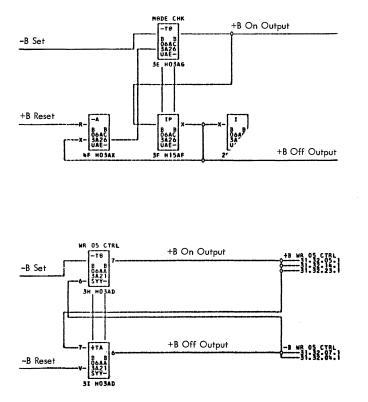

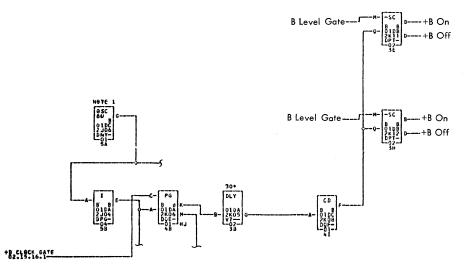

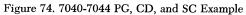

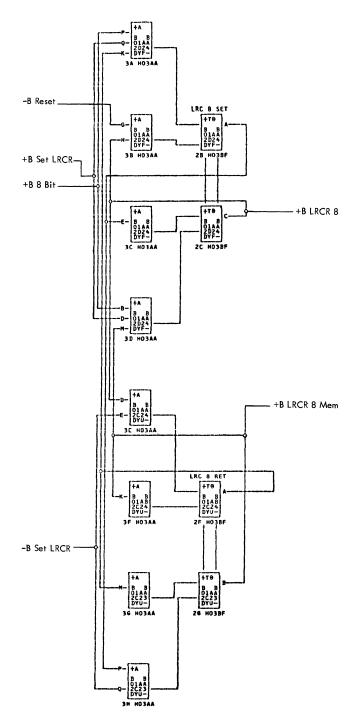

circuits are identical, only the T5 circuit is described in detail.