$\squareBM_{e}$  Customer Engineering

Instruction-Maintenance

7631 File Control

# Preface

This Customer Engineering Instruction-Maintenance Manual describes IBM 7631 File Control Model 3 operation with the IBM 1410, 7010, 7040-44, 7070-74, 7080, and 7090-94 Data Processing Systems. The manual contains seven parts:

1. "Introduction" shows the IBM 7631 File Control relationship to the IBM Data Processing Systems and the IBM 1301 Disk Storage. The magnetic disk recording, cylinder concept, data track, and format track information are also included.

2. "Operations" describes the five basic machine cycles, the prepare to verify, and the miscellaneous instruction sequences.

3. "Functional Units" presents the timing, register operation, parity circuit, format recognition, and compare circuit concepts.

4. "Interfaces" presents the 1410 1-0 Interface and Standard Interface concepts.

5. "Operation Timing" presents the five basic machine cycles, the prepare to verify, and the miscellaneous instruction timings. 6. "7320 Drum Storage Adapter" presents the drum characteristics, functional units, and operation theory.

7. "Maintenance Information" contains the CE panel operating instructions, 1410 System status conditions, 7000 system error conditions, singleshot timing, flag operation, and power control sequence.

Programming information, power supply information, and 1301 Disk Storage Fundamentals are contained in the publications:

- IBM 1301 Disk Storage with IBM 7000 Series Data Processing Systems, General Information Manual, Form D22-6576-3.

- IBM 1301 Disk Storage with IBM 1410 and 7010 Systems, Systems Reference Library, Form A22-6670-2.

- IBM 60-Cycle SMS Power Supply, Customer Engineering Manual of Instruction, Form 225-6478-1.

- IBM 1301 Disk Storage, Customer Engineering Manual of Instruction, Form 227-5582-2.

- IBM 1301 Disk Storage, Customer Engineering Maintenance Manual, Form 227-5581-4.

#### MINOR REVISION (September 1964)

This edition, Form 223-2766-1, is a relatively unchanged version of the preceding edition, Form 223-2766-0. There are no significant differences in content or terminology. Changes to text or illustrations are indicated by a bullet ( $\bullet$ ) in the table of contents or list of illustrations.

Copies of this and other IBM publications can be obtained through IBM Branch Offices. Address comments concerning the contents of this publication to: IBM Corporation, CE Manuals, Dept. B96, P.O. Box 390, Poughkeepsie, N.Y. 12602.

# Contents

| Introduction                                                             | 7               |

|--------------------------------------------------------------------------|-----------------|

| Operations Scheme                                                        | 8               |

| Control                                                                  | 10<br>10        |

| Write                                                                    | 11              |

| Sense (7000)                                                             | 11              |

| Magnetic Disk Recording<br>Cylinder Concept                              | 11<br>13        |

| Data Tracks                                                              | 13              |

| Index Area                                                               | 14              |

| Home Address 1<br>Home Address 2                                         | $14 \\ 15$      |

| Record Areas                                                             | 15              |

| AGC Areas                                                                | 15              |

| Check Areas                                                              | $\frac{15}{15}$ |

| Format Track                                                             | 16              |

| Operations                                                               | 17              |

| Control                                                                  | 17              |

| Read-Write                                                               | 19              |

| Cycles                                                                   | 19              |

| Prepare to Read-Write Cycle<br>Verify Address Cycle                      | 19              |

| Read Data Cycle                                                          | 19<br>19        |

| Write Data Cycle                                                         | 19              |

| Sense Command (7000 Systems only)                                        | 21              |

| Cycle Sequence                                                           | 21<br>21        |

| 1410 Control Cycle                                                       | $\frac{21}{23}$ |

| 7000 Control Cycle                                                       | 24              |

| Prepare to Read-Write Cycle                                              | 25<br>27        |

| Phase Selection                                                          | 28              |

| Read Data Cycle<br>Write Data Cycle                                      | 31<br>33        |

| Prepare to Verify Instruction Operations                                 | 35              |

| TRO (Track Operation)                                                    | 35              |

| TWA (Track Without Address)      CYO (Cylinder Operation)                | $\frac{41}{41}$ |

| SRO (Single Record Operation)                                            | $\overline{42}$ |

| HAO (Home Address Operation—Customer)<br>HAO (Home Address Operation—CE) | 43              |

| Wr Format (Write Format)                                                 | 43<br>44        |

| Write Check                                                              | 45              |

| Miscellaneous Instruction Operations                                     | 46              |

| Seek (1410 and 7000)                                                     | $\frac{46}{47}$ |

| No-Op (1410 and 7000)                                                    | 48              |

| Inop (1410 and 7000)                                                     | 48              |

| Prevent Seek Complete (1410)<br>Eight-Bit Mode (7000)                    | 49<br>49        |

| Six-Bit Mode (7000)                                                      | 50              |

| Sense (7000)                                                             | 50              |

| Functional Units                                                         | 51              |

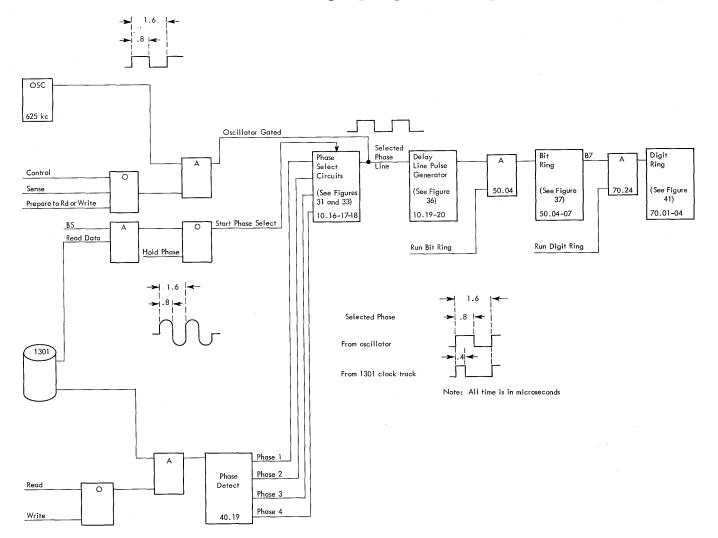

| Timing Sources                                                           | 51              |

| Phase Select Scheme                                                      | 52              |

| Read Mode                                                                | 52              |

| Read Phase Select Operation                                              | 54              |

| Hold Phase                                                                                                                                                           | . 58                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| Delay Line Pulse Generator                                                                                                                                           | 60                             |

| Bit Ring<br>Reset                                                                                                                                                    | 62                             |

| Binary Trigger Drive<br>Bit Timing<br>Holdovers                                                                                                                      | 62                             |

| Digit Ring                                                                                                                                                           |                                |

| Index Operation                                                                                                                                                      |                                |

| Registers                                                                                                                                                            | 71                             |

| Shift Register                                                                                                                                                       | 73                             |

| Serial Register                                                                                                                                                      |                                |

| Serial Register Parity                                                                                                                                               | 74                             |

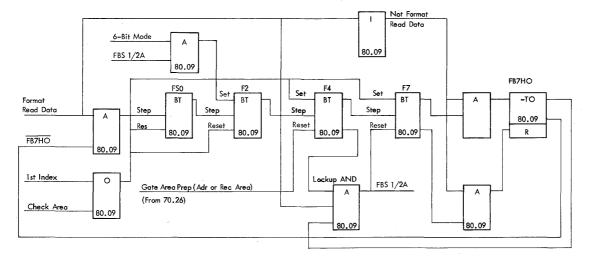

| Format Recognition Scheme                                                                                                                                            | 80                             |

| Write Mode Format Recognition                                                                                                                                        | 81                             |

| Format Skew Detector                                                                                                                                                 | 81<br>84                       |

| Format Binary Counter                                                                                                                                                | 87                             |

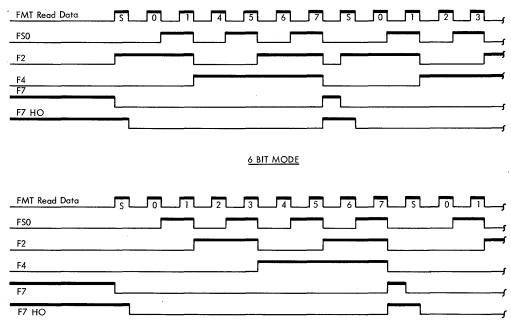

| Compare Circuit                                                                                                                                                      | 88                             |

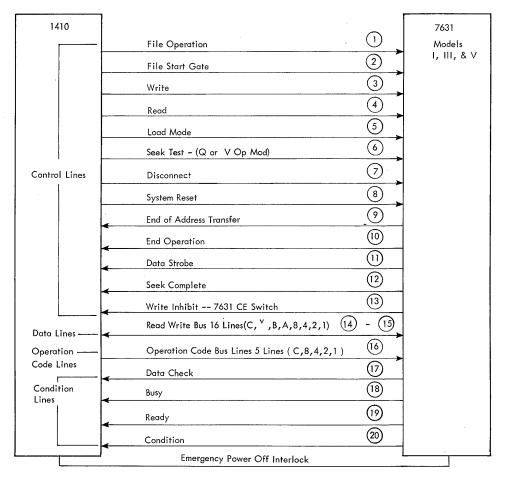

| Interfaces                                                                                                                                                           | 90                             |

| 1410 I-O Interface      1410 I-O Instruction      1410 I-O Interface Operation                                                                                       | -90<br>91<br>94                |

| 1410 I-O Interface Lines                                                                                                                                             | 101                            |

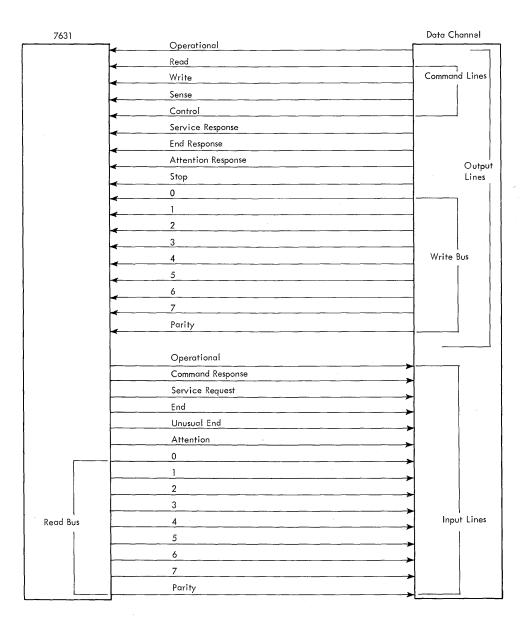

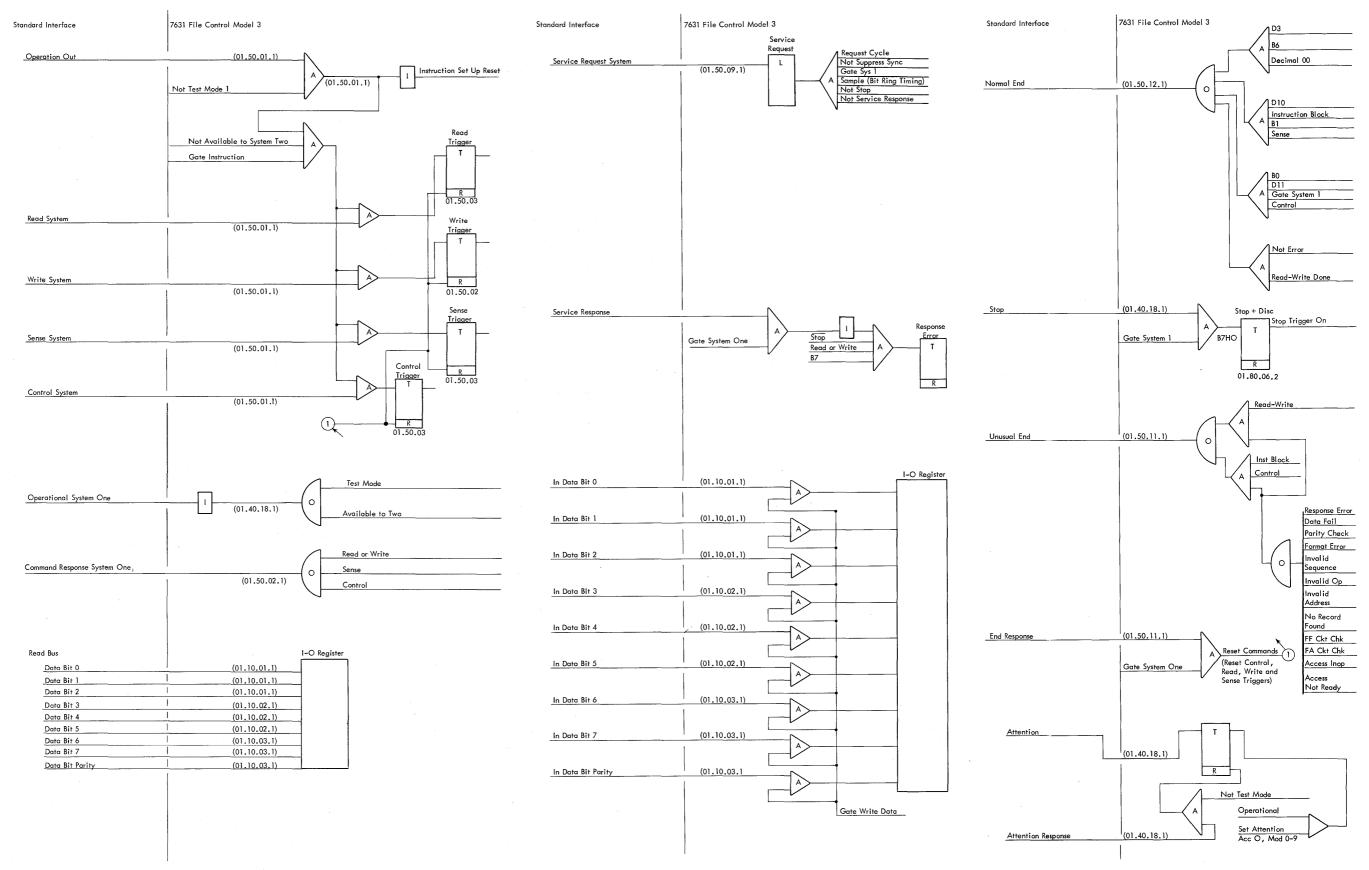

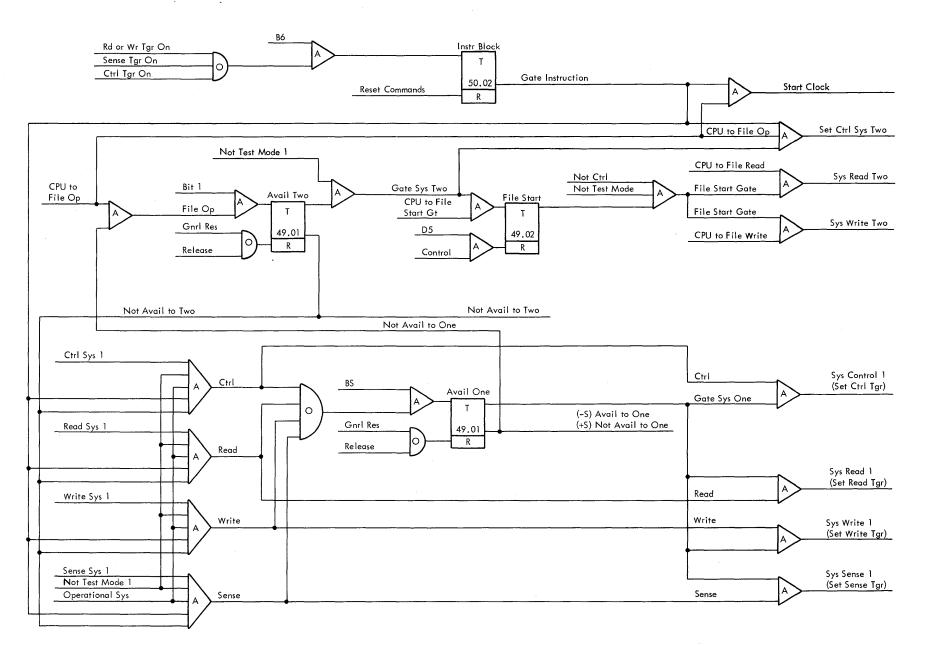

| Standard Interface<br>Initiation of an Operation<br>Definition of Standard Interface Signal Lines<br>Data Channel Lines to 7631<br>7631 Signal Lines to Data Channel | $109\\110\\110\\110\\110\\111$ |

| Operations Timings<br>Availability                                                                                                                                   | 114<br>114                     |

| 1410 Control Cycle                                                                                                                                                   | 114                            |

| Timing Operations<br>Request and Store Operations                                                                                                                    | $\frac{116}{116}$              |

| Miscellaneous Operations      7000 Control Cycle                                                                                                                     | 116<br>120                     |

| Timing Operations<br>Request and Store Circuit Operations<br>Miscellaneous Operations<br>Prepare to Read-Write Cycle                                                 | 120<br>120<br>122<br>124       |

| Verify Address Cycle<br>Home Address One Timing<br>Home Address Two Timing                                                                                           | 127<br>129<br>131              |

| Read Data Cycle                                                                                                                                                      | 132<br>134                     |

| Write Data Cycle                                                                                                                                                     | 137<br>137                     |

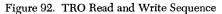

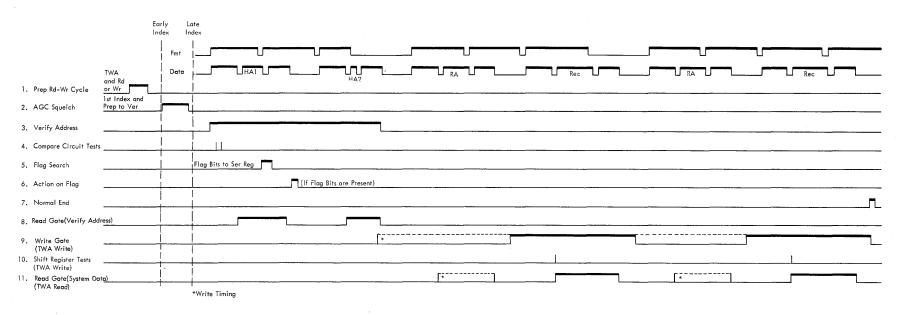

| TRO Read and Write                                                                                                                                                   | 139                            |

| TWA Read and Write                                                                                                                                                   | 141                            |

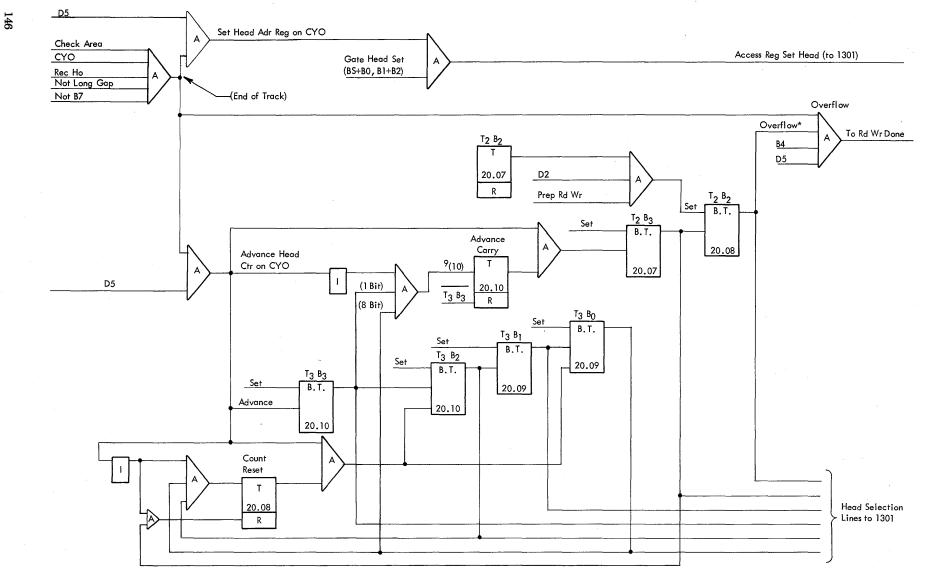

| CYO Read and Write                                                                                                                                                   | 144                            |

| SRO Read and Write                                                                                                                                                   | 145                            |

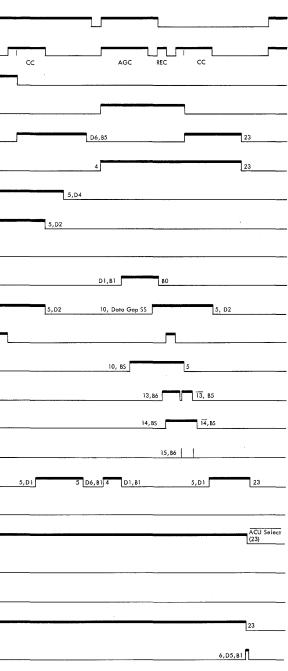

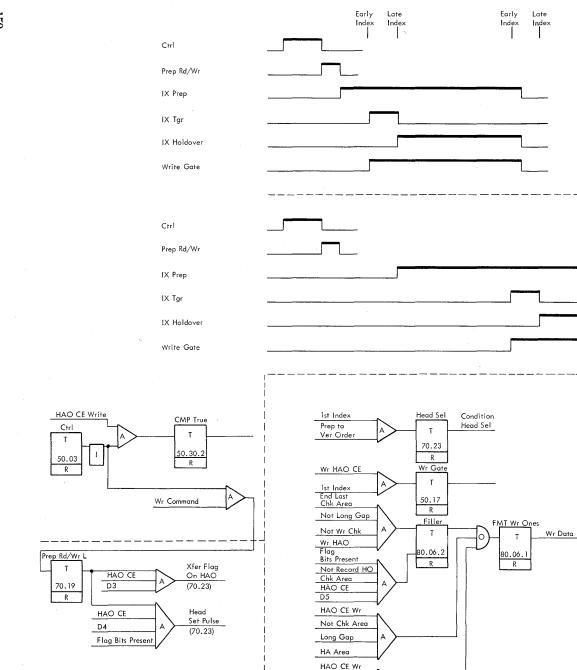

| HAO Write<br>Write Home Address One on New Files<br>(HAO-CE Write)<br>Write Home Address One and Flag on a Damaged Track                                                                                             | 148                                                                | R               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------|

| Write Home Address One and Flag on a Danaged Track<br>Write Home Address One on an Alternate Track<br>(HAO-CE Write)                                                                                                 | 143<br>151<br>153                                                  |                 |

| HAO-CE Read.<br>Read Home Address One from a Customer Track.<br>Read Alternate Track (HAO-CE).<br>HAO Customer Read (HAO-CE Switch Off).                                                                             | $153 \\ 153 \\ 154 \\ 154 \\ 154$                                  | Ċ               |

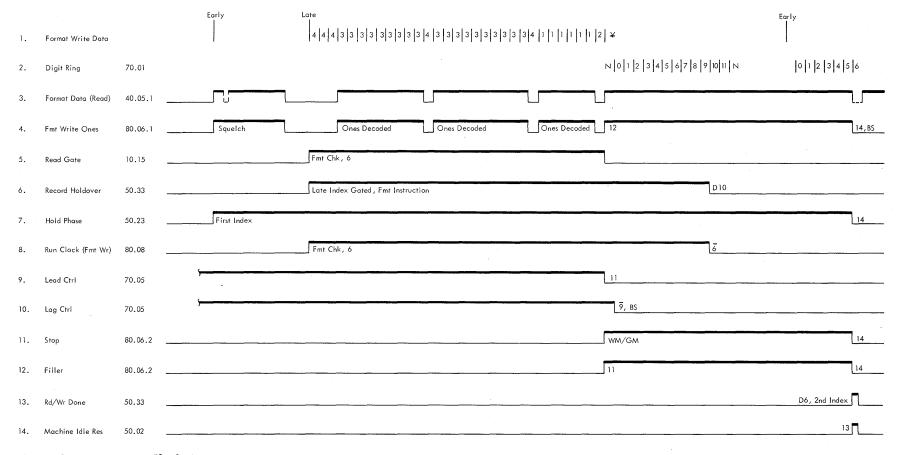

| Write Format                                                                                                                                                                                                         | 156                                                                |                 |

| Write Check                                                                                                                                                                                                          | 158                                                                |                 |

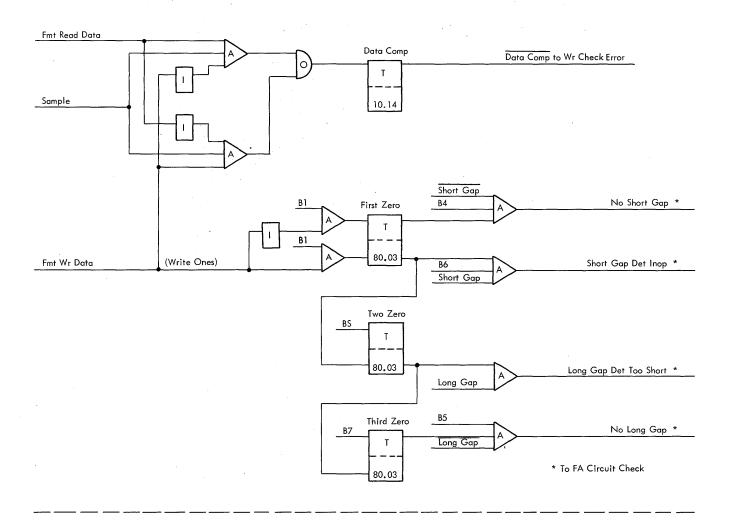

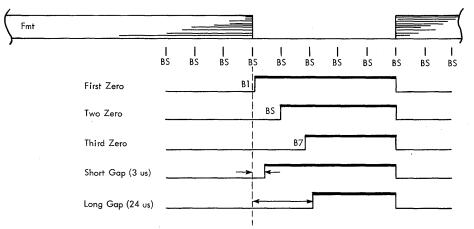

| Format Write Check<br>Compare Circuits<br>Timing Circuits                                                                                                                                                            | 163<br>163<br>163                                                  | C               |

| Sense (7000)                                                                                                                                                                                                         | 167                                                                |                 |

| Drum Control Feature                                                                                                                                                                                                 | 169                                                                |                 |

| Operational Characteristics<br>Seek<br>Write Operations<br>Read Operations<br>Write Check<br>Set Access Inoperative<br>Cylinder Operation<br>Alternate Surface Flagging<br>Address Organization<br>Instruction Times | 169<br>169<br>170<br>170<br>170<br>170<br>170<br>170<br>170<br>171 | т<br>• 1<br>• 7 |

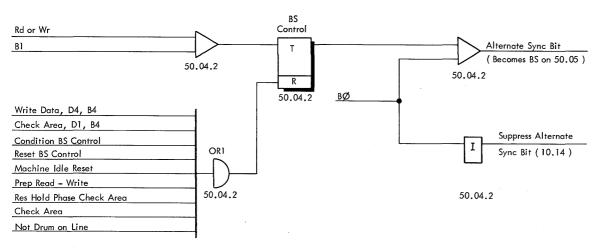

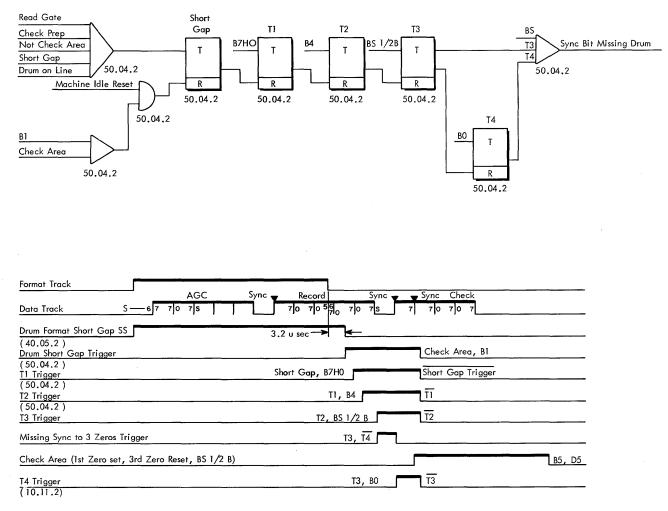

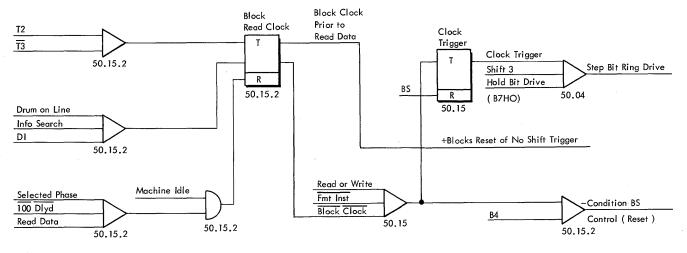

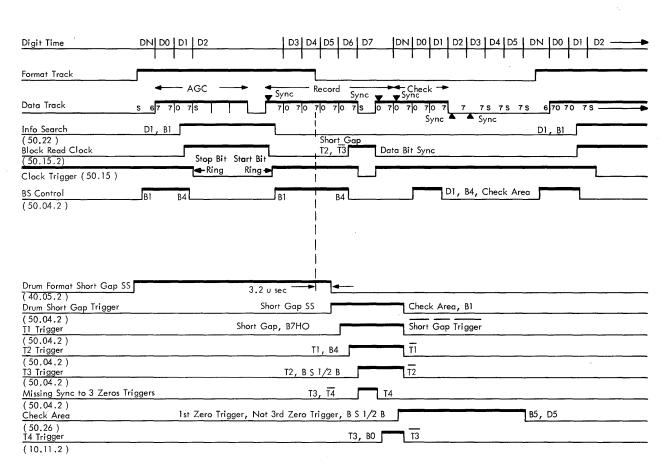

| Drum Feature Functional Units<br>Phase Pulse Control<br>Bit-Sync Control<br>Missing Sync Bit Detection<br>Clock Trigger Control                                                                                      | $\begin{array}{c} 173 \\ 174 \end{array}$                          | S               |

| Drum Operation                                                                                                                                                                                                       |                                                                    | 5<br>(          |

| Skew<br>Clocking<br>Read-Write Heads                                                                                                                                                                                 | 176<br>178                                                         | F               |

| Phase Pulse Generation.                                                                                                                                                                                              | 179                                                                | F               |

| ew Files                                   | 148               | Read Data Sequence                                                                                     | 180<br>181 |

|--------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------|------------|

| 'lag on a Damaged Track<br>Alternate Track |                   | Read Data and Read Format Delay Line Adjustment<br>Format Delay Procedure<br>Read Data Delay Procedure | 181        |

| E Switch Off)                              | $\frac{151}{153}$ | Maintenance Information                                                                                |            |

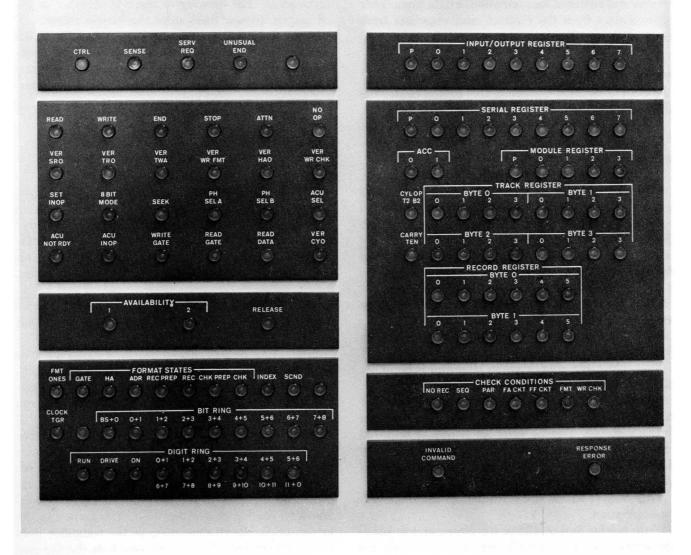

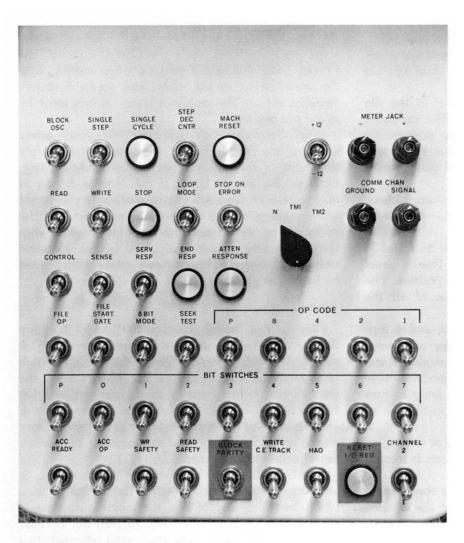

| · · · · · · · · · · · · · · · · · · ·      | 153               | Operator's Switch and Light Panel                                                                      | 183        |

| Customer Track                             |                   | Customer Engineering Test Panel and                                                                    |            |

| Switch Off)                                |                   | Machine Indicating Lamps                                                                               |            |

|                                            | 156               | 1410 Switches                                                                                          |            |

|                                            | 158               | 7000 Switches<br>Communication Channel Jacks                                                           |            |

|                                            |                   | CE Panel Operating Instructions (Test Mode One)                                                        |            |

|                                            |                   | 7631 Model 1 or 5 CE Panel Operating Instructions                                                      | 107        |

|                                            |                   | (TM1)<br>7631 Model 2 and 4 CE Panel Operating Instructions                                            | 187        |

|                                            |                   | (TM1)                                                                                                  | 187        |

|                                            |                   | 7631 Model 3 CE Panel Operating Instructions<br>Channel 1 (TM1)                                        | 188        |

|                                            |                   | 7631 Model 3 CE Panel Operating Instructions                                                           | 100        |

|                                            |                   | Channel 2 (TM1)                                                                                        |            |

|                                            |                   | Test Mode 2 CE Panel Switches                                                                          |            |

|                                            |                   | • 1410 Status Conditions<br>Busy                                                                       |            |

|                                            |                   | Not Ready                                                                                              |            |

|                                            |                   | Condition                                                                                              |            |

| · · · · · · · · · · · · · · · · · · ·      |                   | Data Check                                                                                             |            |

|                                            |                   | • 7000 Error Conditions.                                                                               |            |

|                                            |                   | Program Check<br>Exceptional Condition                                                                 |            |

|                                            |                   | Data Error                                                                                             |            |

|                                            | 174               | Unusual End                                                                                            | 191        |

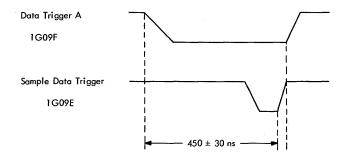

| ••••••••••                                 | 175               | Singleshot Timings                                                                                     | 191        |

|                                            |                   | Gap Detector Adjustments                                                                               | 191        |

|                                            |                   | Flag Operation                                                                                         | 192        |

|                                            |                   | Procedure to Write and Flag Tracks.                                                                    |            |

|                                            | 179               | Power Distribution and Control Sequence                                                                | 192        |

|                                            |                   |                                                                                                        |            |

|                                            |                   | •                                                                                                      |            |

# Illustrations

| FIGURE                                  | TITLE                                                          | PAGE         |

|-----------------------------------------|----------------------------------------------------------------|--------------|

| Introdu                                 | ction                                                          |              |

| 1                                       | 7631 File Control Systems Relationships                        | . 7          |

| $\overline{2}$                          | Data Characteristics of Disk Storage                           | . 8          |

| 3                                       | 1301 Addressing                                                |              |

| 4                                       | 7631 File Control Simplified Operations                        | . 10         |

| 5                                       | Magnetically Coated Disk.                                      | . 11         |

| 6                                       | Disk Data Eight-Bit Mode                                       | . 11         |

| 7                                       | Disk Data Six-Bit Mode                                         |              |

| 8                                       | Read-Write Comb                                                |              |

| 9                                       | Disk Surfaces                                                  | . 12         |

| $10 \\ \bullet 11$                      | Cylinder Concept<br>Format and Data Track                      | . 13<br>. 14 |

| •11                                     | Format and Data Track                                          | . 14         |

| Operat                                  |                                                                |              |

| 12                                      | 7000 System Order World Layout for 7631                        | . 17         |

| 13                                      | 1410 System Control Data for 7631                              | . 17         |

| 14                                      | 7631 File Control Simplified Operations                        | . 18         |

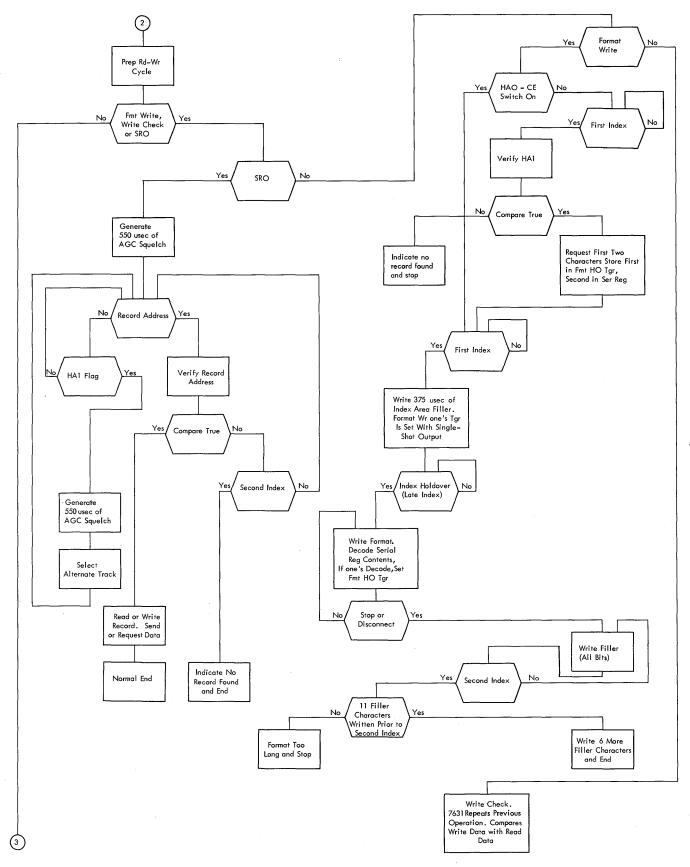

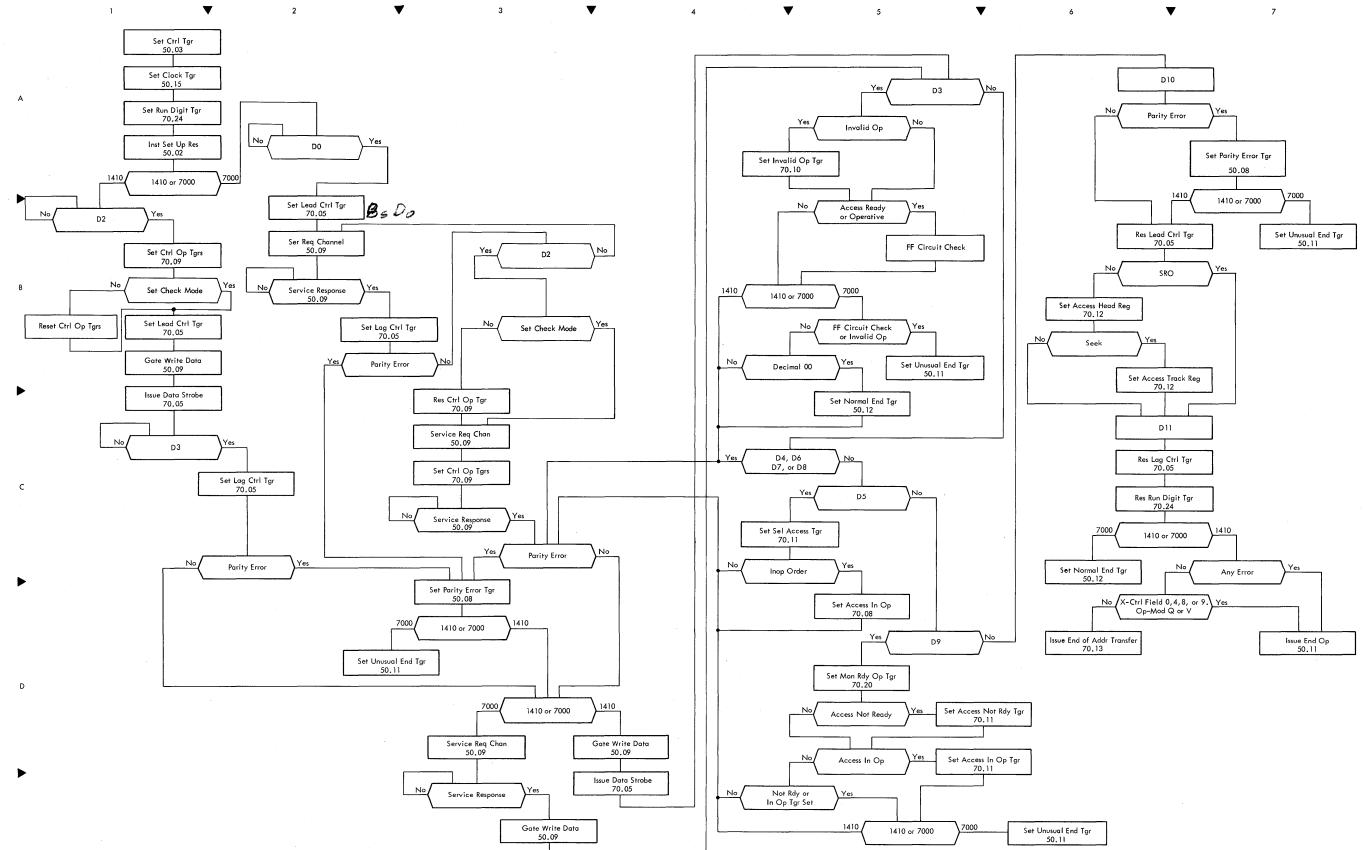

| 15                                      | Operations Flow Chart                                          |              |

| 16                                      | Control Data Flow Diagram                                      |              |

| 17                                      | 1410 Instruction Layout                                        |              |

| $\frac{18}{19}$                         | 7000 Order Layout                                              |              |

| 19<br>20                                | Verify Address Sequence                                        |              |

| 20<br>21                                | Verify Address Data Flow Diagram                               | . 29         |

| 21                                      | Read Data Sequence-Record                                      |              |

| 23                                      | Read Data Flow Diagram                                         |              |

| 24                                      | Write Data Sequence—Record Address                             | . 33         |

| 25                                      | Write Data Flow Diagram                                        | . 34         |

| •26                                     | 7631 Cycles Chart                                              |              |

| 27                                      | Instruction Flow Chart                                         |              |

| 28                                      | Shared System Three-Way Switch                                 | . 47         |

| Functio                                 | nal Units                                                      |              |

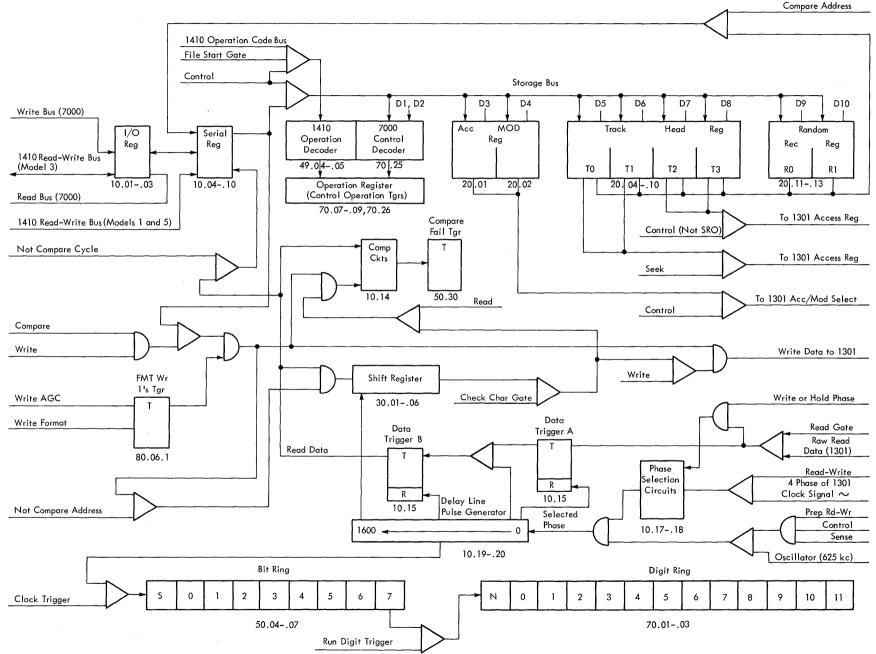

| •29                                     | Timing Scheme                                                  | . 51         |

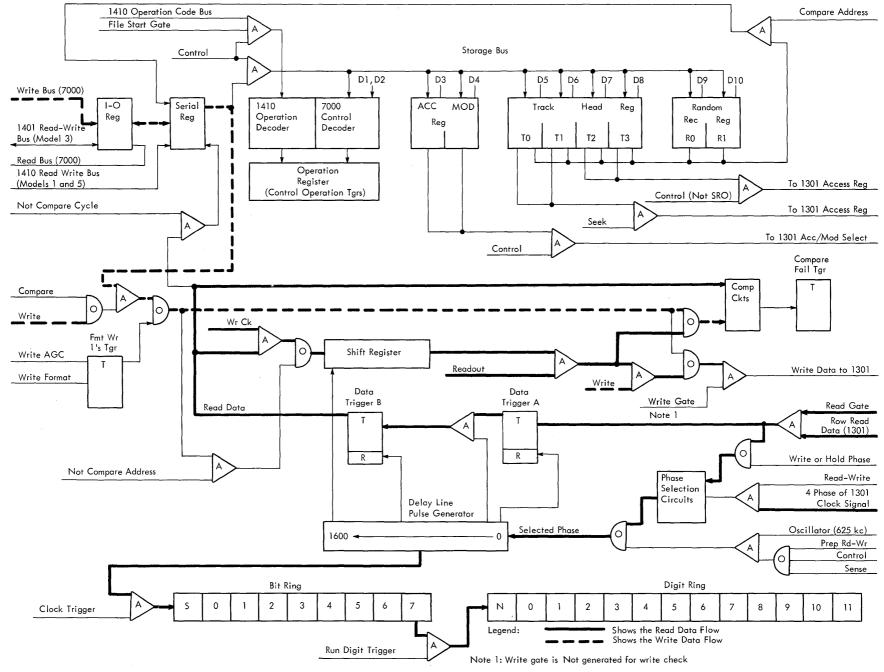

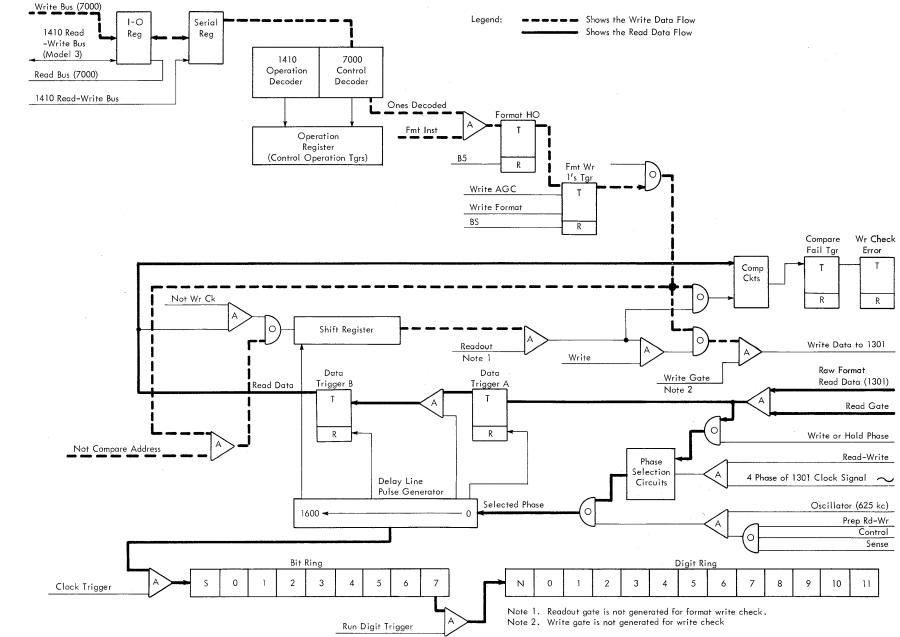

| • 30                                    | Data Flow Diagram                                              |              |

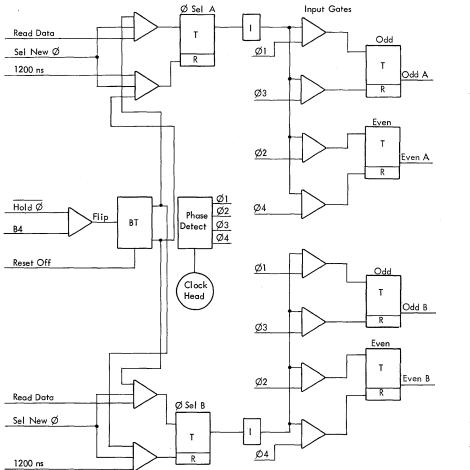

| ● 31                                    | Phase Selector Circuits—Simplified                             |              |

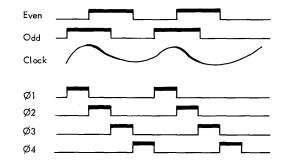

| 32                                      | Phase Detector Inputs and Outputs                              |              |

| 33                                      | Phase Selector Circuits                                        | . 57         |

| ●34                                     | Phase Gating and Select New Phase                              | . 58         |

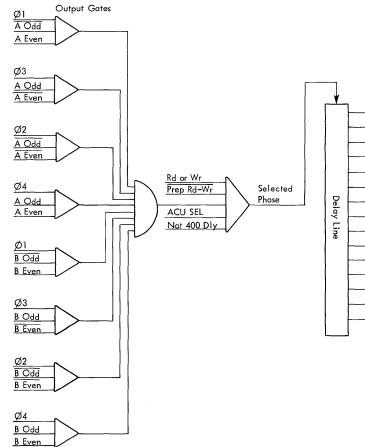

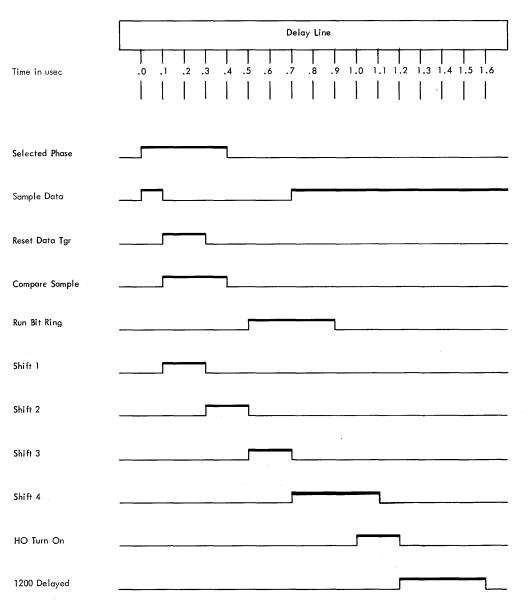

| •35                                     | Phase Selection Timing                                         | . 59         |

| 36                                      | Delay Line Pulse Generator Timing                              |              |

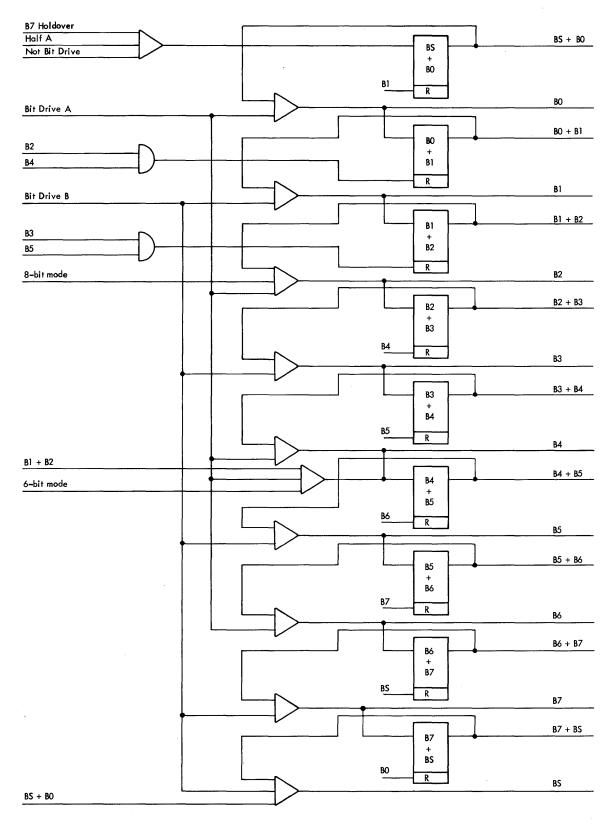

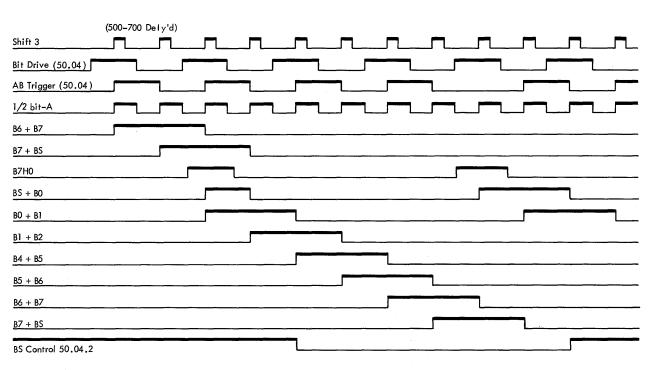

| •37                                     | Bit Ring                                                       | . 63         |

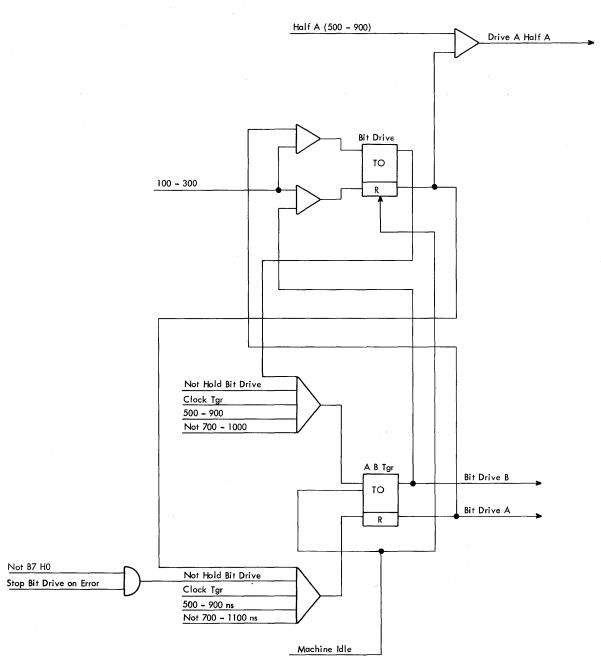

| 38                                      | Bit Ring Drive                                                 | . 64         |

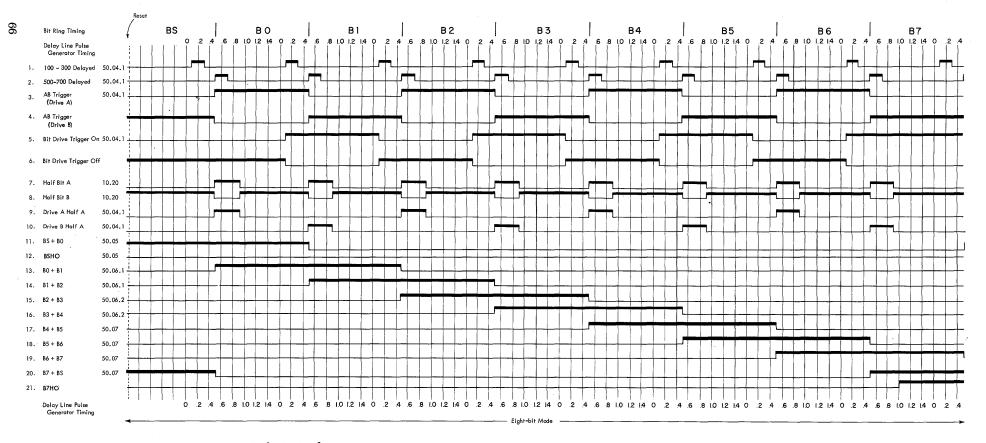

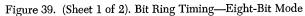

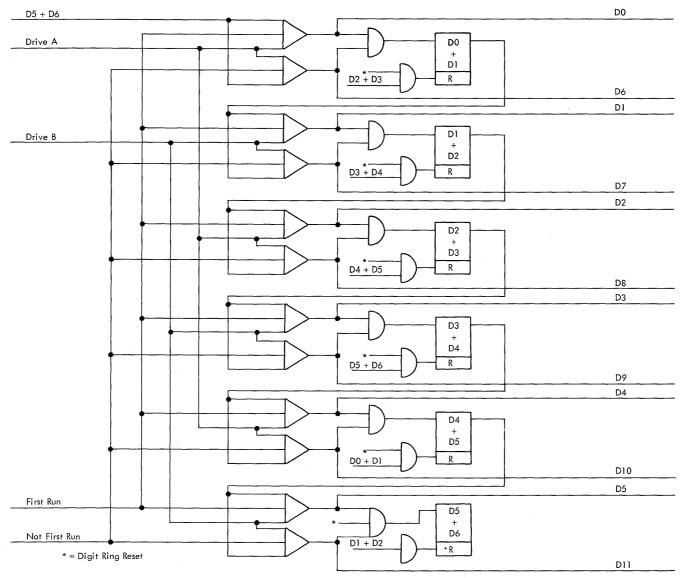

| 39<br>39                                | Bit Ring Timing—Eight-Bit Mode<br>Bit Ring Timing—Six-Bit Mode | . 66<br>. 67 |

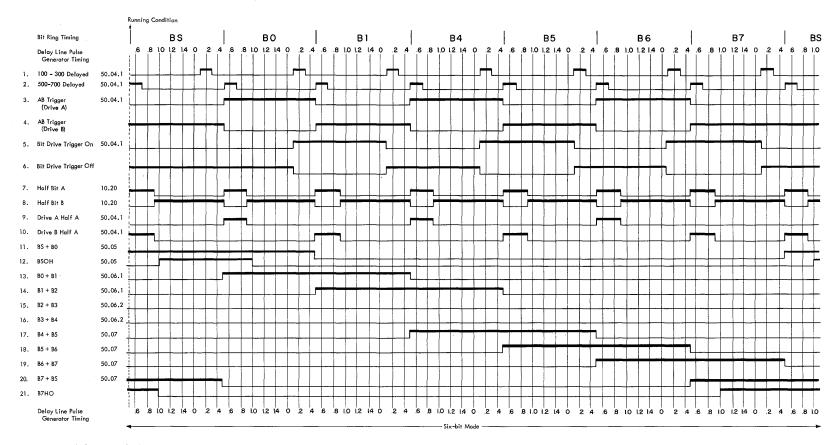

| 40                                      | Digit Ring Controls                                            | . 68         |

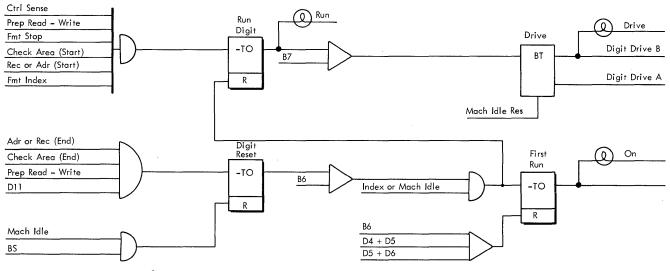

| 40                                      | Digit Ring                                                     | . 69         |

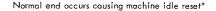

| 42                                      | Index Operation                                                | . 70         |

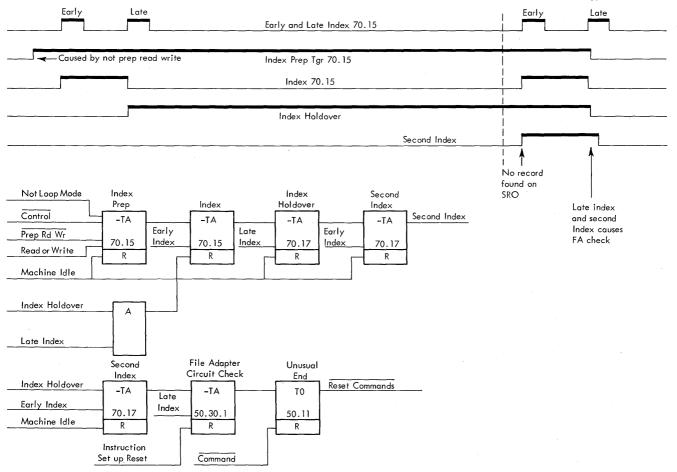

| 43                                      | Shift Register                                                 |              |

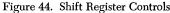

| 44                                      | Shift Register Controls                                        | . 7.3        |

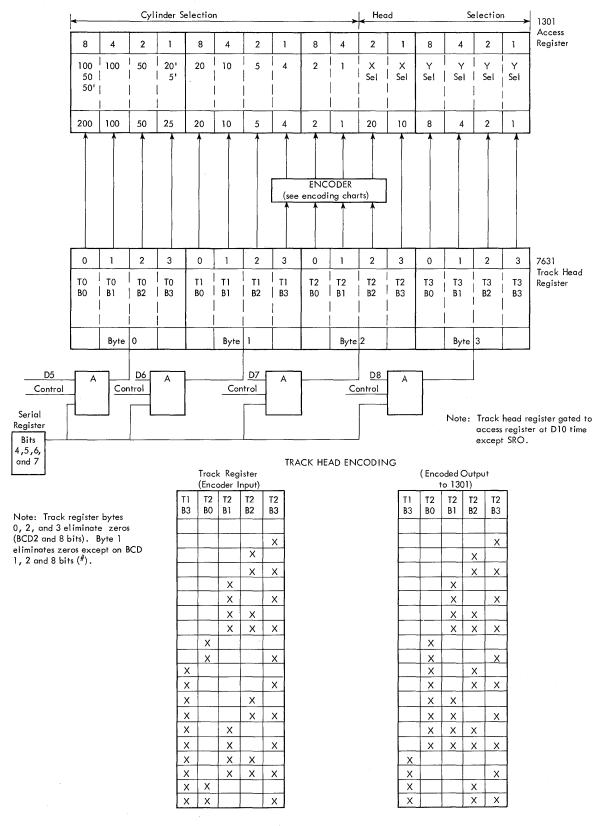

| 45                                      | 7631 Track-Head Register and 1301 Access                       |              |

| - 14 - 14 - 14 - 14 - 14 - 14 - 14 - 14 | Register Relationship                                          |              |

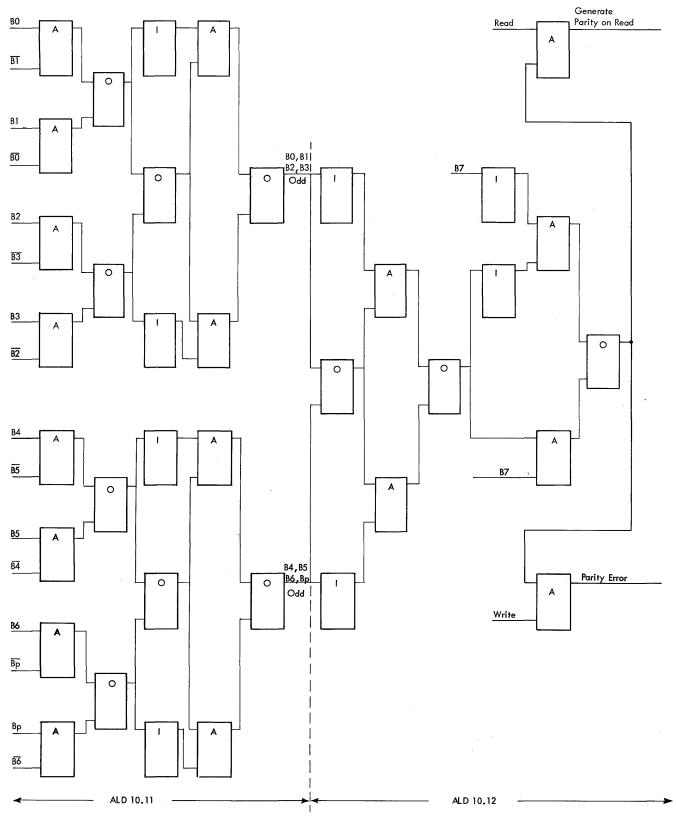

| 46                                      | Parity Circuit                                                 |              |

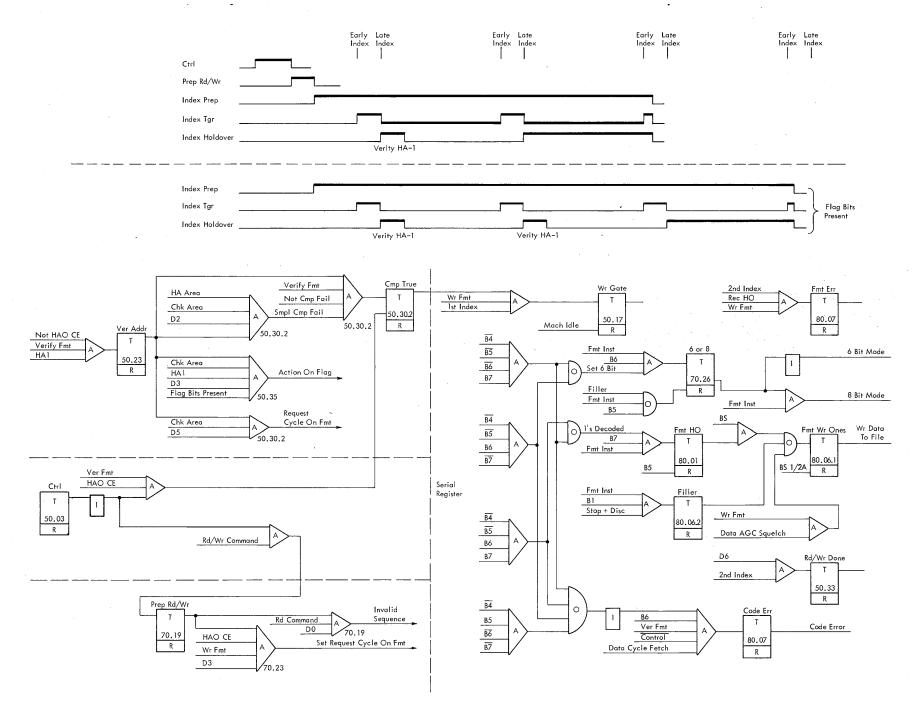

| •47                                     | Format Recognition—Write Mode                                  |              |

| ● <b>4</b> 8                            | Format Recognition Logic                                       | . 79         |

| $\frac{49}{50}$                         | Format Recognition-Read Mode—Not HAO CE                        |              |

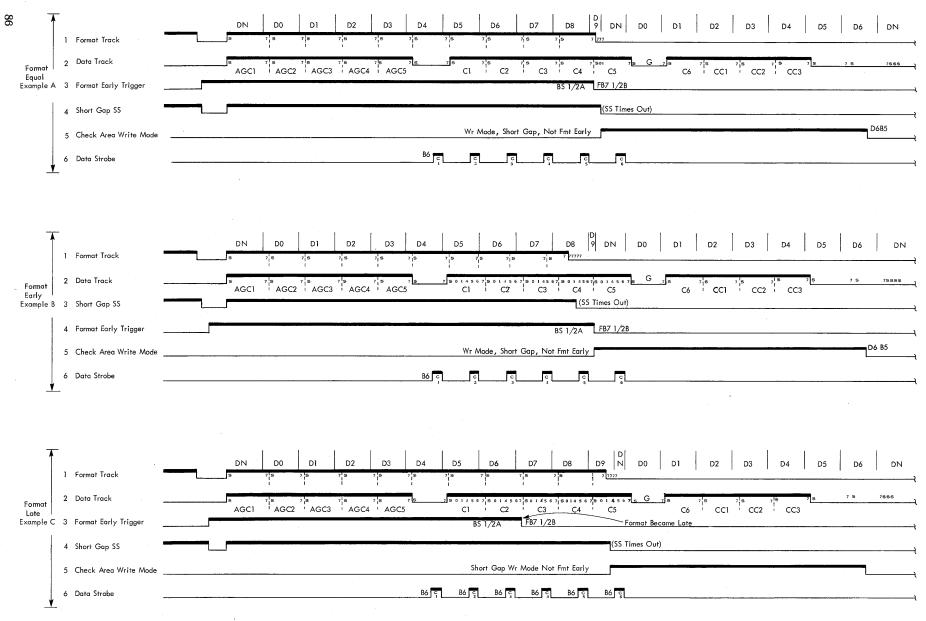

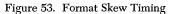

| $\frac{50}{51}$                         | Format Equal, Early, and Late                                  |              |

| 52                                      | Format Skew Detector                                           |              |

| 53                                      | Format Skew Timing                                             |              |

| 54                                      | Format Skew Errors                                             |              |

| 55                                      | Format Binary Counter                                          |              |

| 56                                      | Format Binary Counter Timing                                   |              |

| • 57                                    | Compare Circuit.                                               |              |

| Interfac                                | es                                                             |              |

| 58                                      | 7631 Model 1                                                   | . 90         |

| 59                                      | 7631 Model 3                                                   |              |

| 60                                      | 7631 Model 5                                                   | . 91         |

| 61                                      | 1410 Disk Storage Instruction Layout                           | . 92         |

| FIGURE      | TITLE                                          | PAGE  |

|-------------|------------------------------------------------|-------|

| 62          | 1410 Control Word-Data Layout                  | 93    |

| 63          | 1410-7631-1301 Disk Storage Instructions       |       |

| 64          | Control (Address Transfer) Cycle               | 95    |

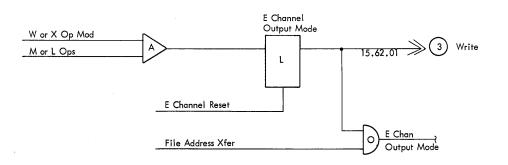

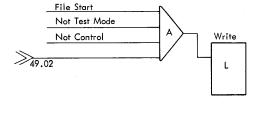

| 65          | Write Sequence                                 | 97    |

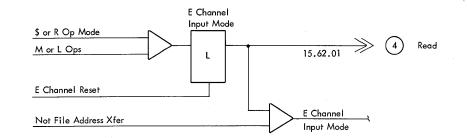

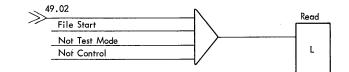

| 66          | Read Sequence                                  | 98    |

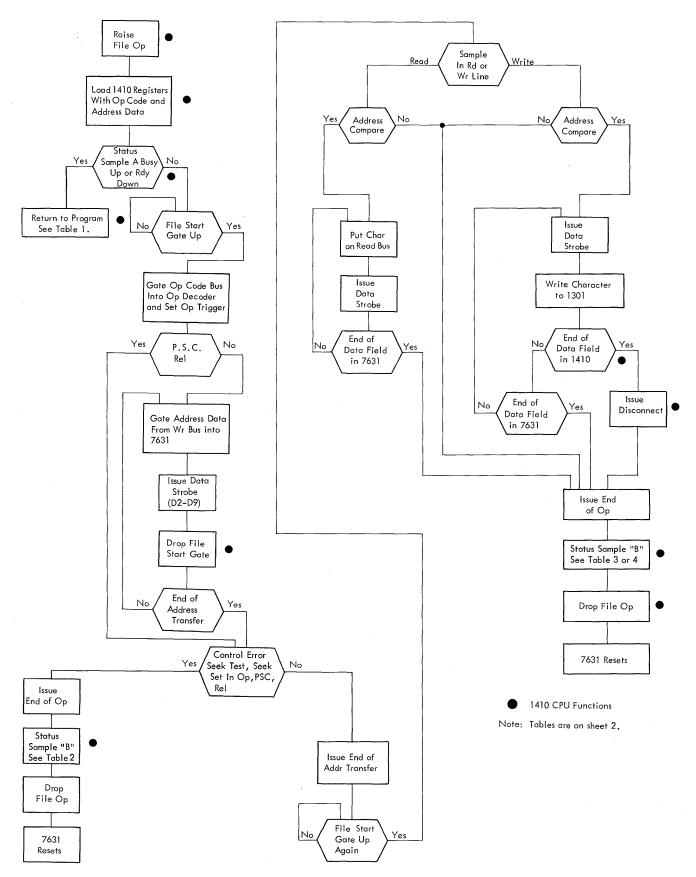

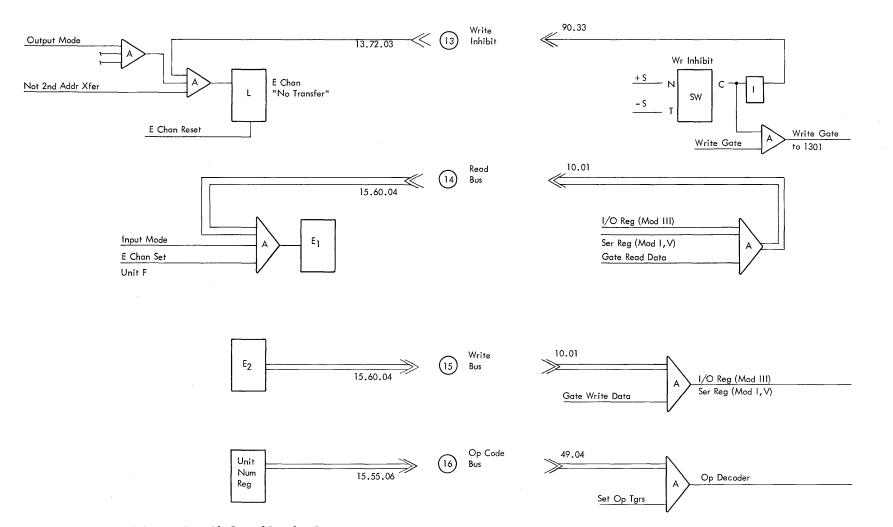

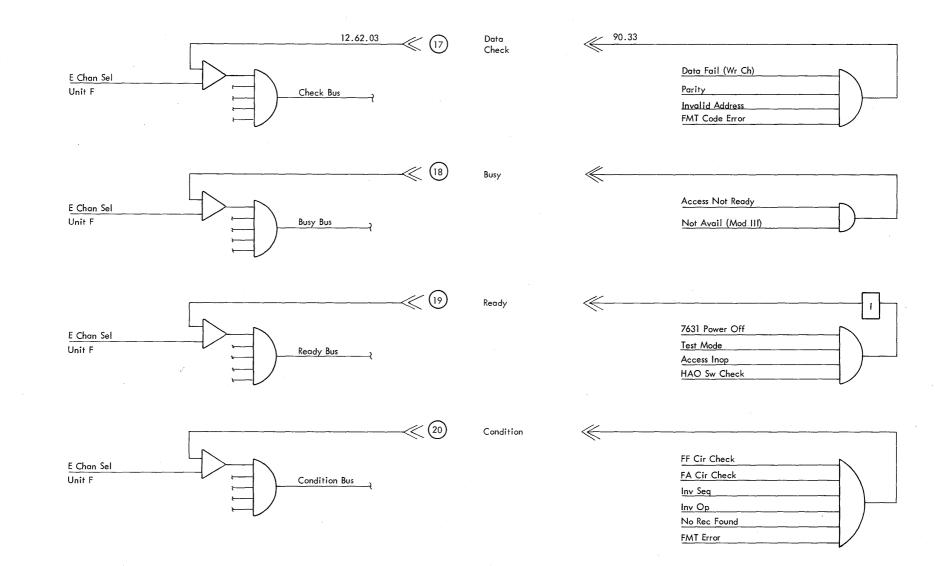

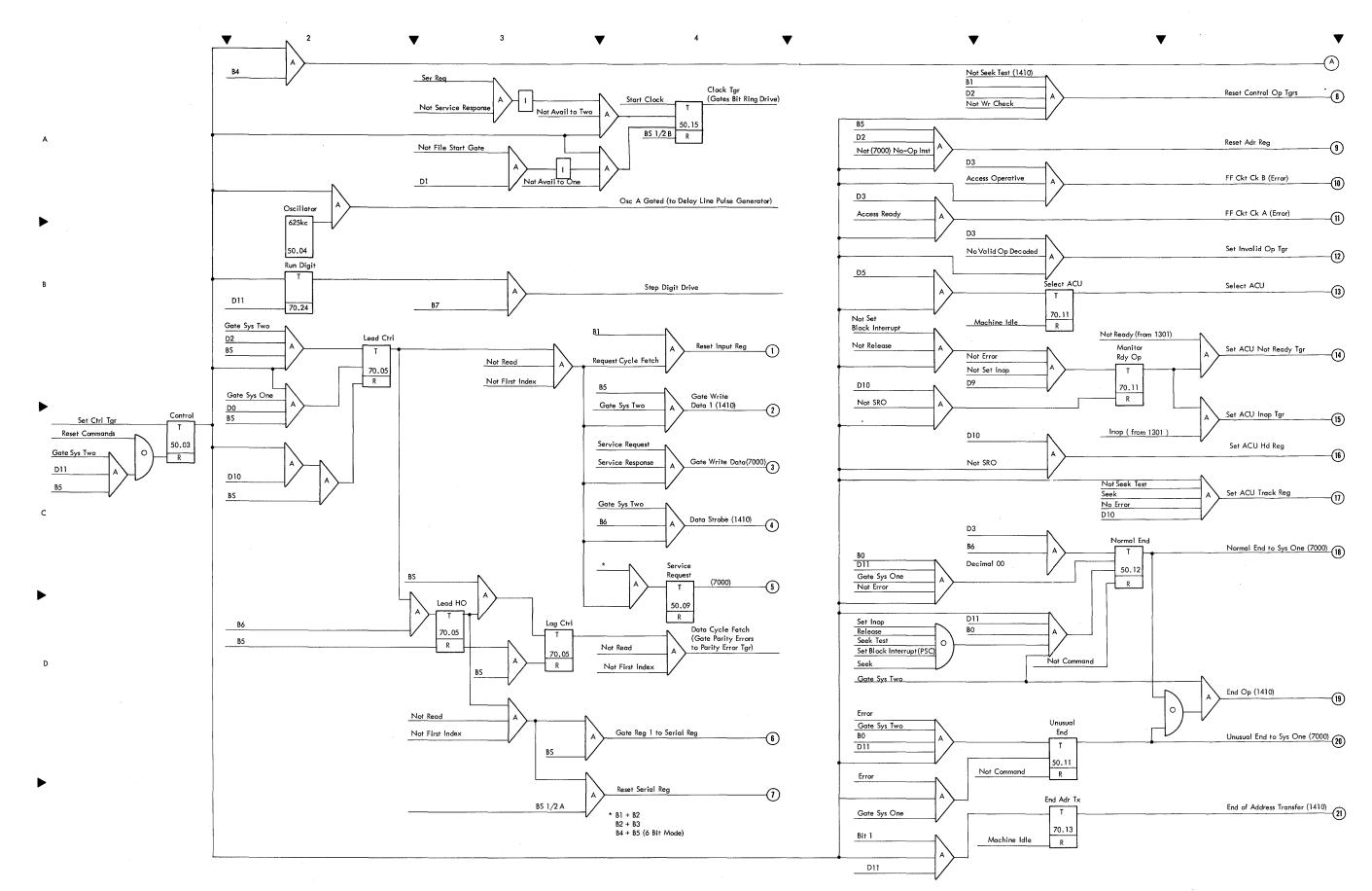

| <b>●</b> 67 | 1410-7631 Interface Flow Chart                 | 99    |

| 68          | 1410-7631 File Control Interface Lines         |       |

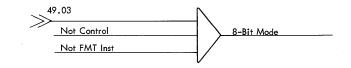

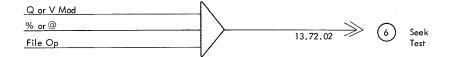

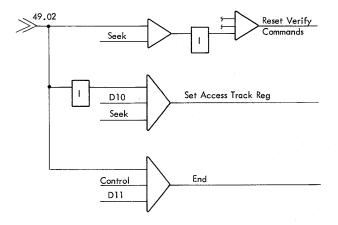

| 69          | 1410-7631 File Control Interface Logic         |       |

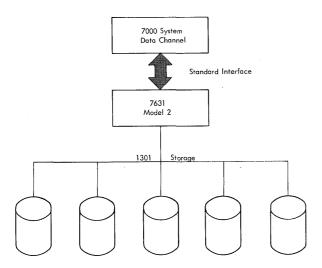

| 70          | 7631 Model 2                                   |       |

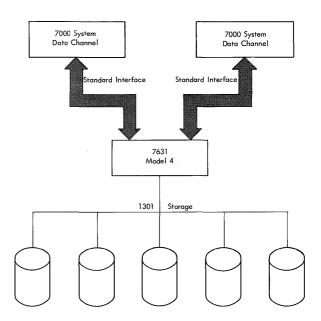

| 71          | 7631 Model 4                                   |       |

| 72          | 7000 Systems Disk Orders                       |       |

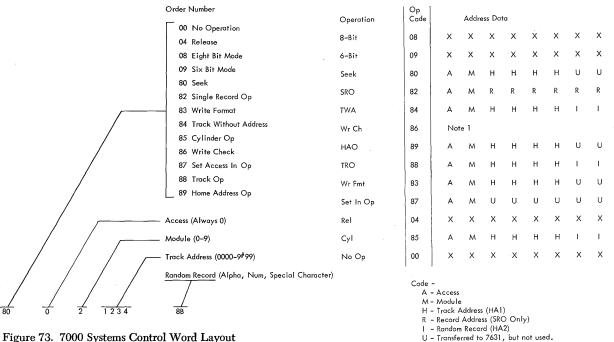

| 73          | 7000 Systems Control Word Layout               |       |

| 74          | 7000 Systems Control Words                     |       |

| 75          | Status Data Bit Assignment                     |       |

| 76          | Standard Interface                             | 112   |

| Operat      | ions Timings                                   |       |

| 77          | Availability-Model 3                           | 115   |

| 78          | Control Cycle Simplified Logic                 | 117   |

| 79          | Control Cycle Timing for 1410 and 7000 Systems | s 119 |

| • 80        | Control Cycle Flow Chart                       | 121   |

| 81          | Decimal 00 Control Cycle Timing for            |       |

|             | 7000 Systems                                   | 123   |

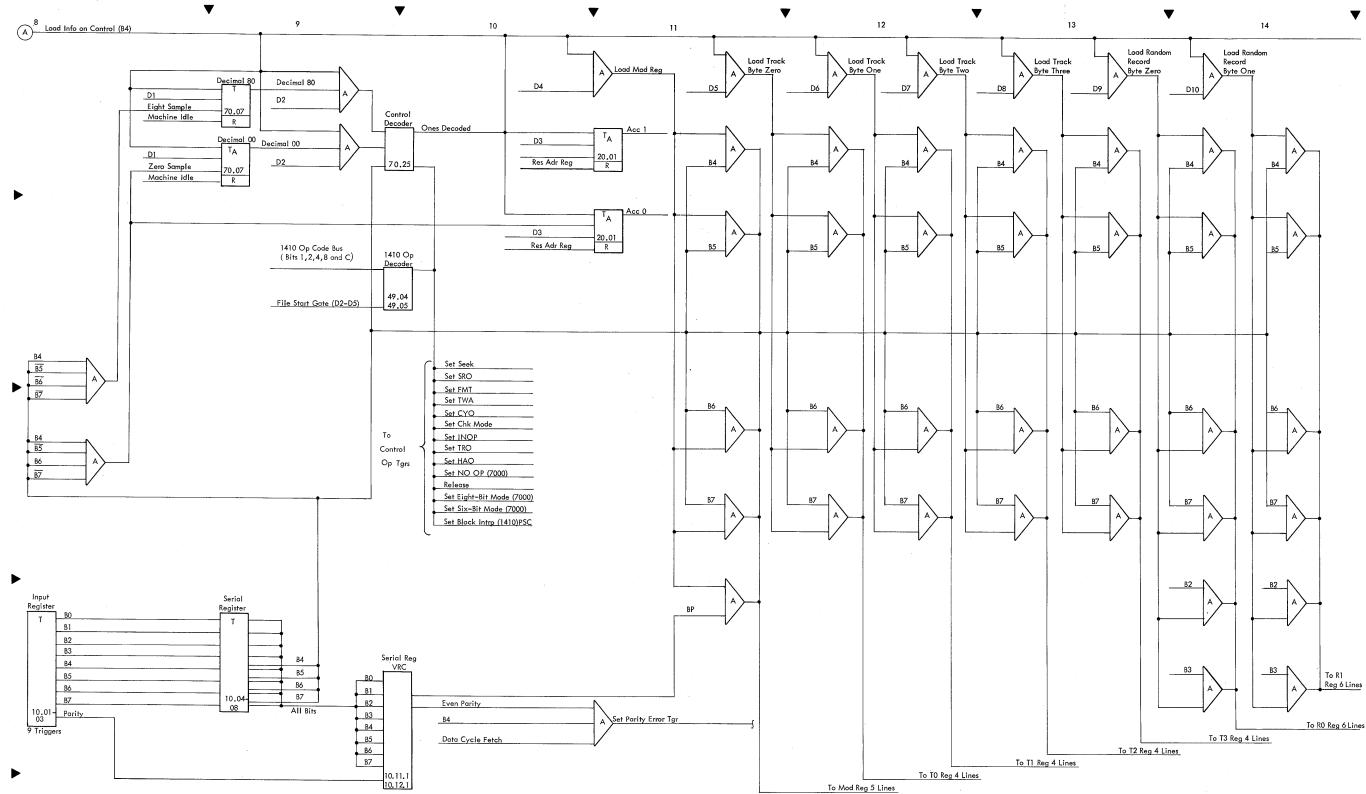

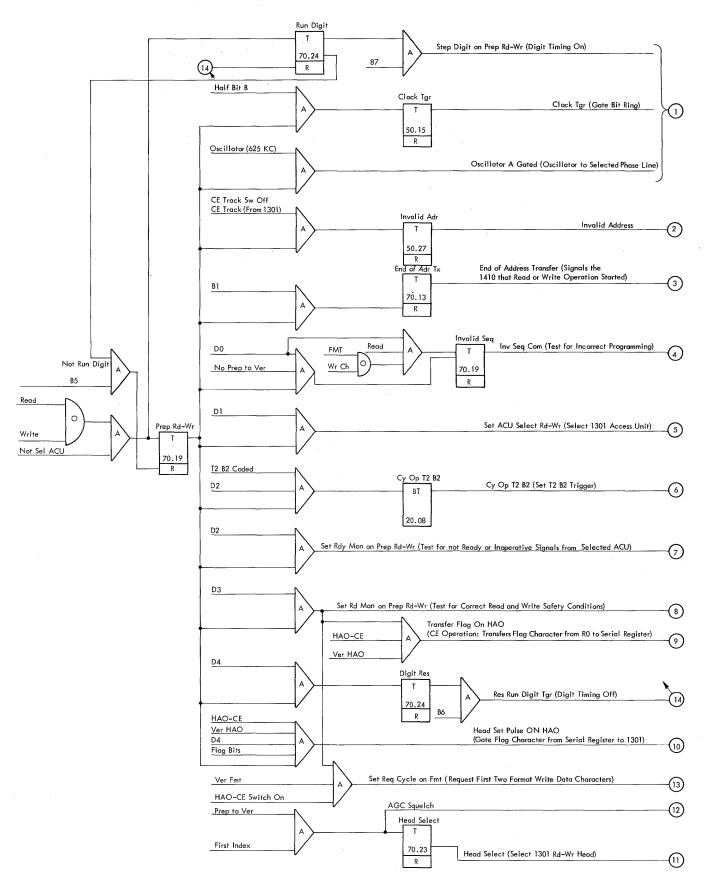

| 82          | Prep Read-Write Cycle Simplified Logic         | 125   |

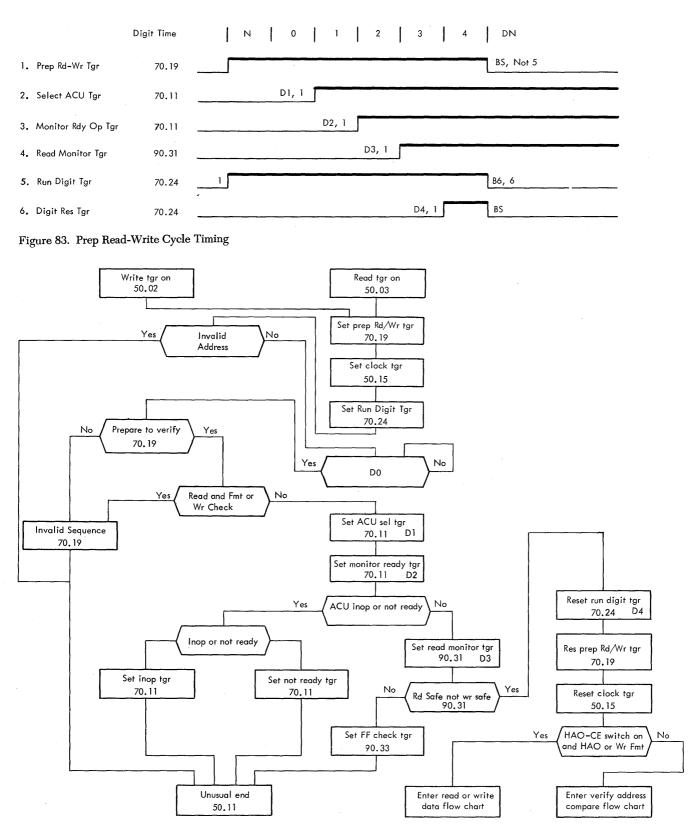

| 83          | Prep Read-Write Cycle Timing                   | 126   |

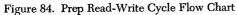

| 84          | Prep Read-Write Cycle Flow Chart               | 126   |

| 85          | Verify Address Cycle Timing                    | 128   |

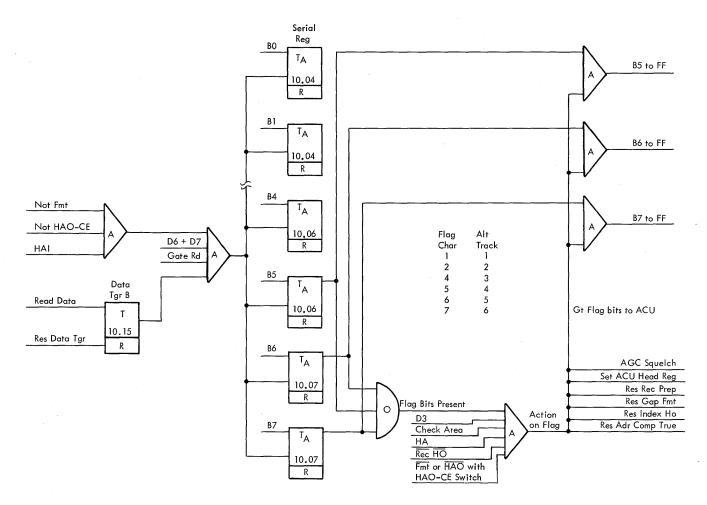

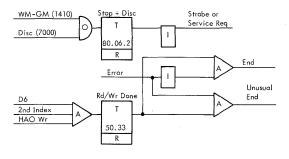

| ●86         | Flag Operation                                 | 130   |

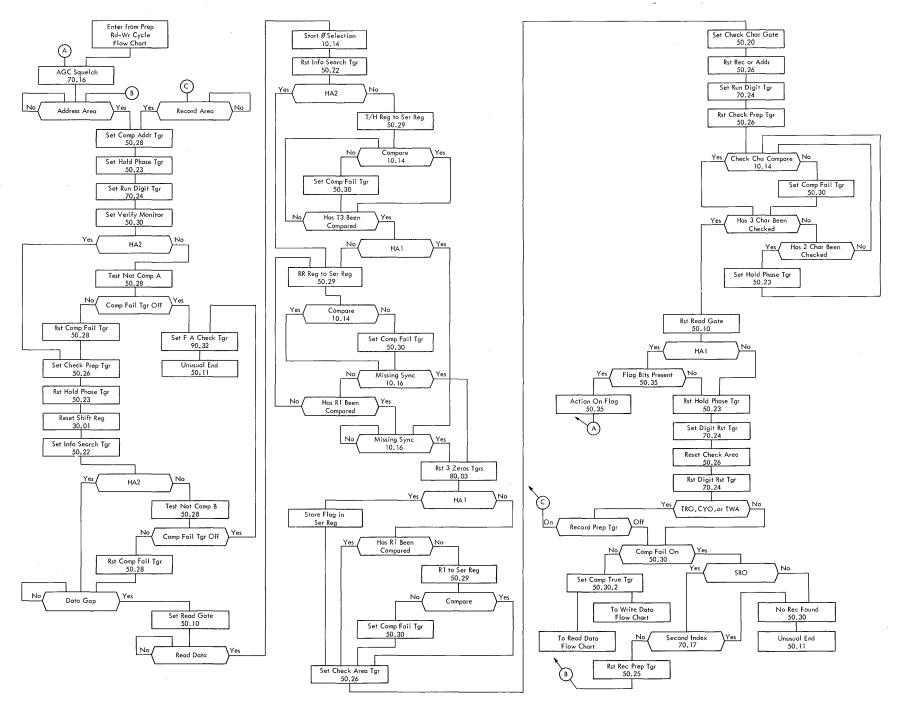

| 87          | Verify Address Cycle Flow Chart                | 133   |

| 88<br>● 89  | Read Data Cycle Timing                         |       |

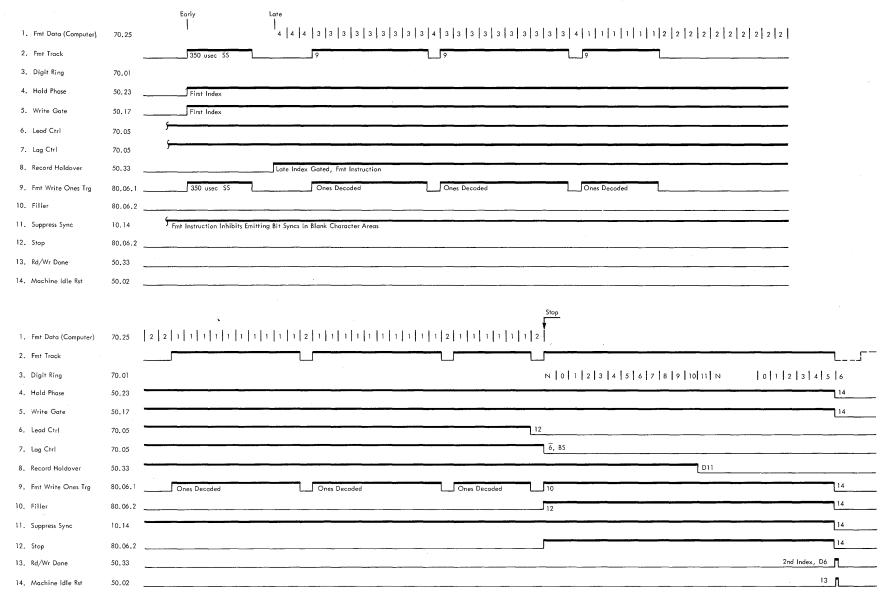

| • 89<br>90  | Write Data Cycle Timing                        |       |

| 90<br>91    | Write Data Cycle Flow Chart                    | 140   |

| 92          | TRO Read and Write Sequence                    |       |

| 93          | TWA Read and Write Sequence                    |       |

| 94          | CYO Read and Write Sequence                    |       |

| 95          | CYO Head Selection Simplified                  | 146   |

| 96          | SRO Read Timing                                |       |

| 97          | HAO-CE Write Sequence and Simplified Logic.    | 150   |

| 98          | HAO-CE Write Timing                            | 152   |

| 99          | HAO-CE Read Timing                             | 155   |

| 100         | Format Write Sequence and Simplified Logic     | 157   |

| 101         | Format Write Timing                            | 159   |

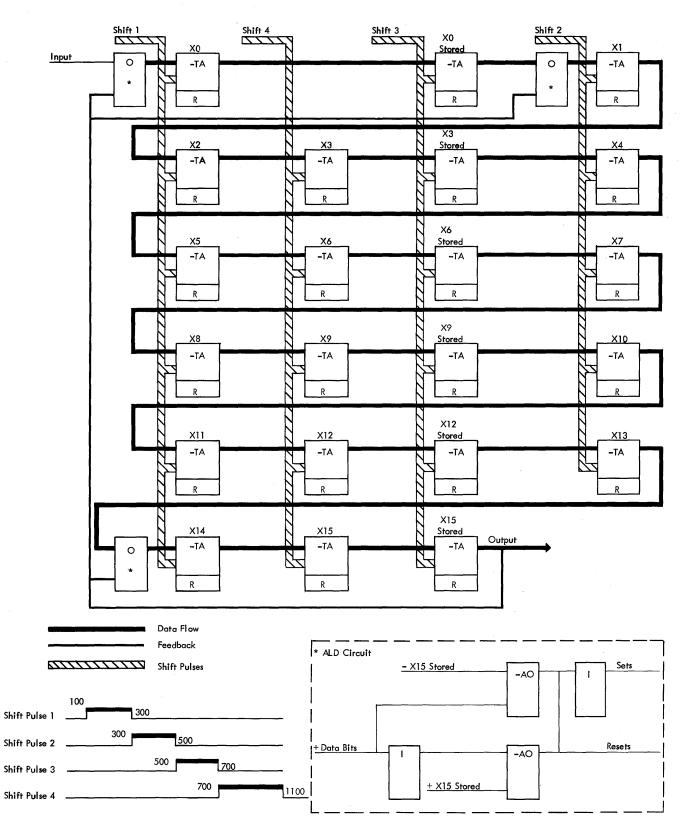

| 102         | Write Check Data Flow Diagram                  |       |

| 103         | Write Check Timing                             | 162   |

| 104         | Format Write Check Data Flow Diagram           |       |

| ●105        | Format Write Check Simplified Logic            |       |

| 106         | Format Write Check Timing                      |       |

| 107         | Status Data Bit Assignment                     | 167   |

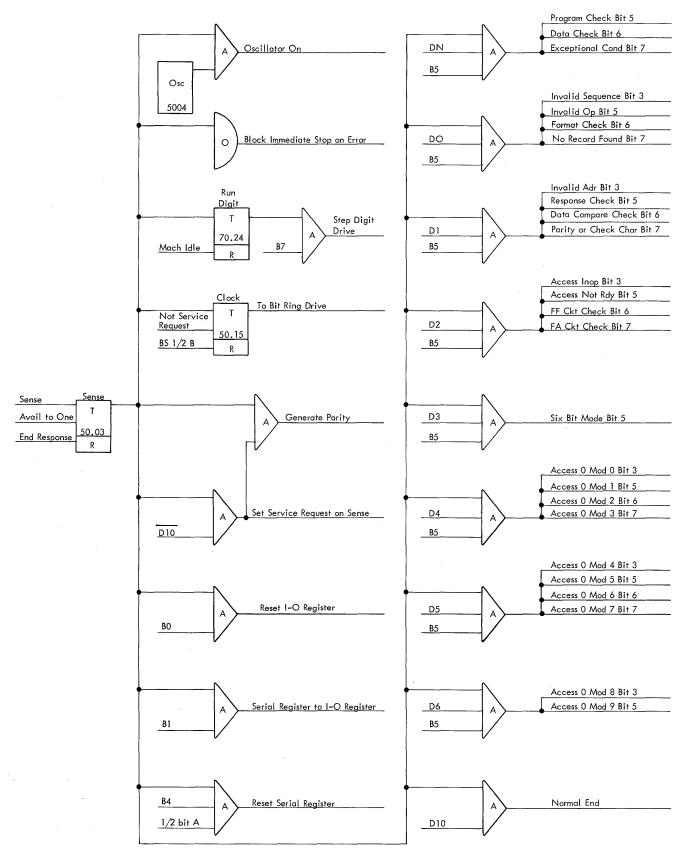

| 108         | Sense—7000                                     | 168   |

| Drum (      | Control Feature                                |       |

|             |                                                | 170   |

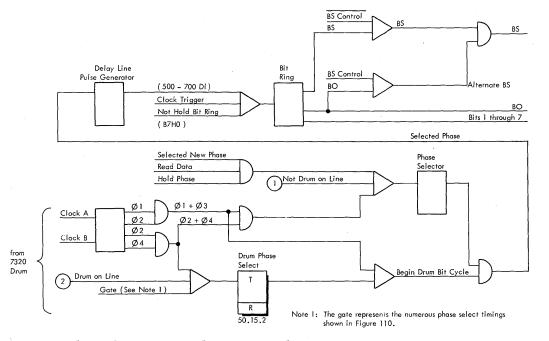

| 109         | Phase Pulse Generation and Bit Ring Control    |       |

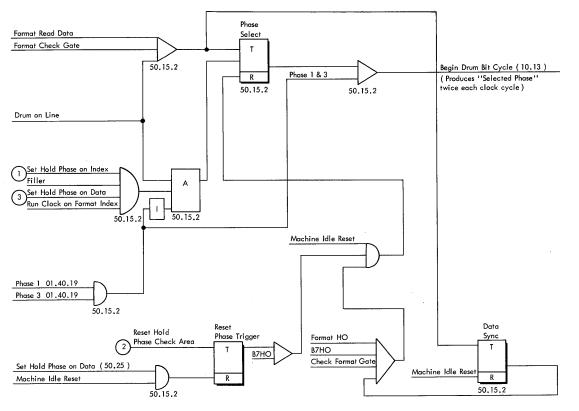

| ●110        | Drum Phase Pulse Control                       | 173   |

| 111 | Bit-Sync Control               | 174 |

|-----|--------------------------------|-----|

| 112 | Missing Sync on Read           | 175 |

| 113 | Clock Trigger Control          | 176 |

| 114 | Drum Read Sequence             | 177 |

| 115 | Drum Write Sequence            | 178 |

| 116 | Read-Write Select Phase Pulses | 179 |

| 117 | Bit Ring                       | 180 |

| 118 | Read Delay Adjustment          | 182 |

|     |                                |     |

# **Maintenance Information**

| 119  | Operators Switch and Light Panel   |

|------|------------------------------------|

| 120  | Customer Engineering Test Panel    |

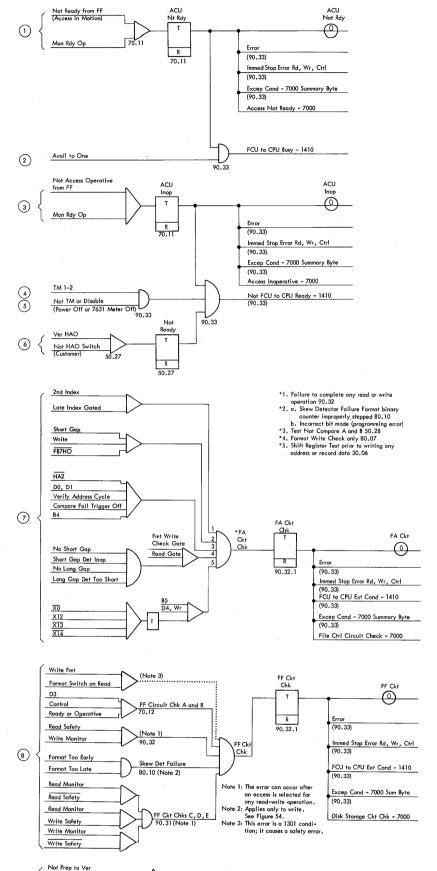

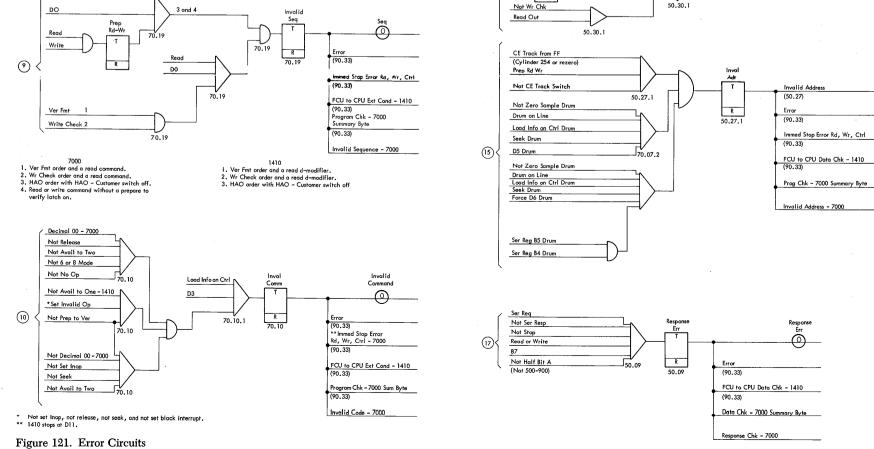

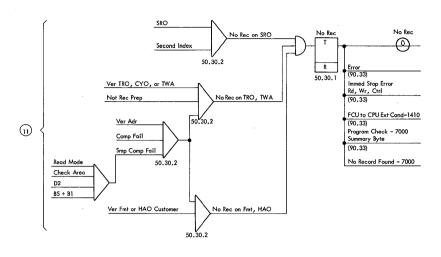

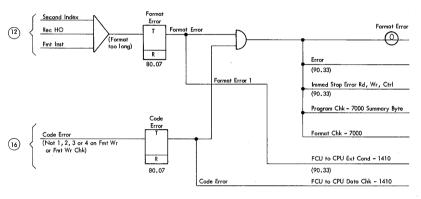

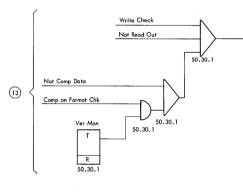

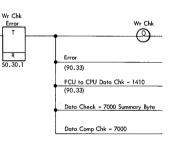

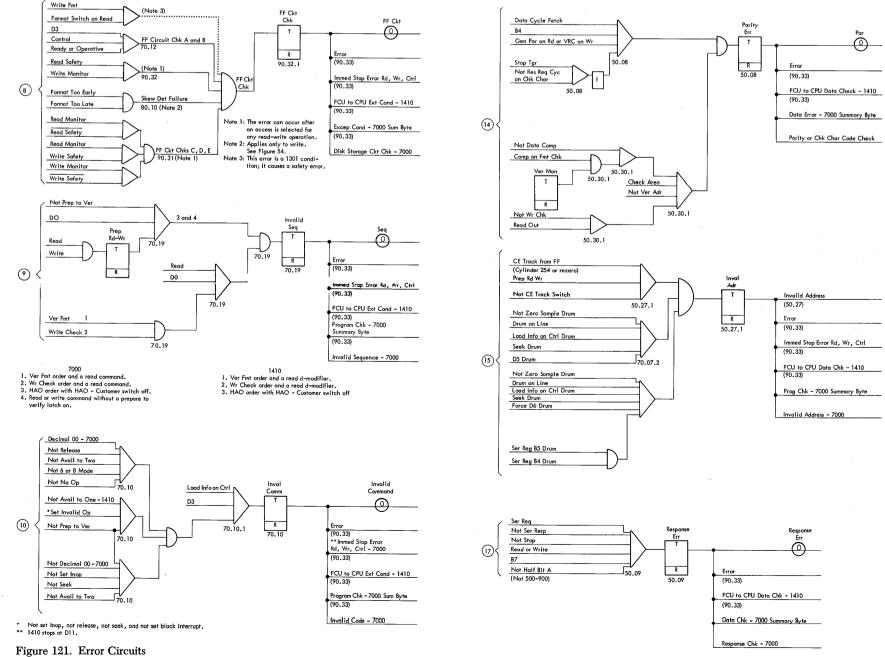

| ●121 | Error Circuits                     |

| 122  | Shift Register Test-Eight-Bit Mode |

# Safety

All IBM Customer Engineers are thoroughly familiar with IBM safety procedures; however, here are some reminders of general safety practices:

1. Do not work alone on the machine when power is on.

2. Wear safety glasses.

3. Be sure a fire extinguisher of the  $co_2$  type recommended for electrical fires is located in the room.

4. Turn DC off to prevent shorting when replacing a fuse or removing and inspecting SMS cards.

5. Discharge capacitors before working on DC power supplies.

6. Remember that 208 volts is present in the machine with power off.

# Introduction

- 7631 File Control controls data transfer between 1301 Disk Storage and 1410 and/or 7000 systems.

- 7631 is available in five models.

- 7631 controls up to five 1301's—10 modules.

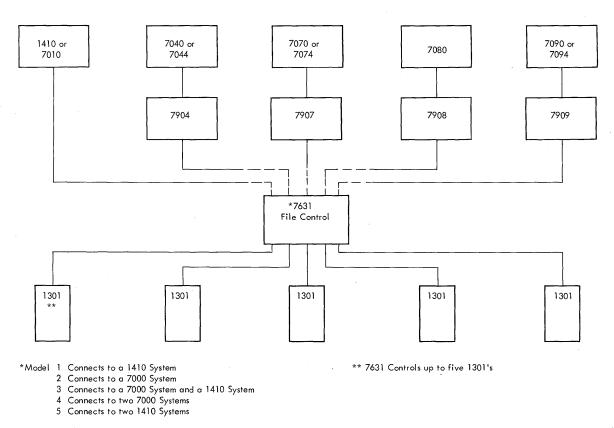

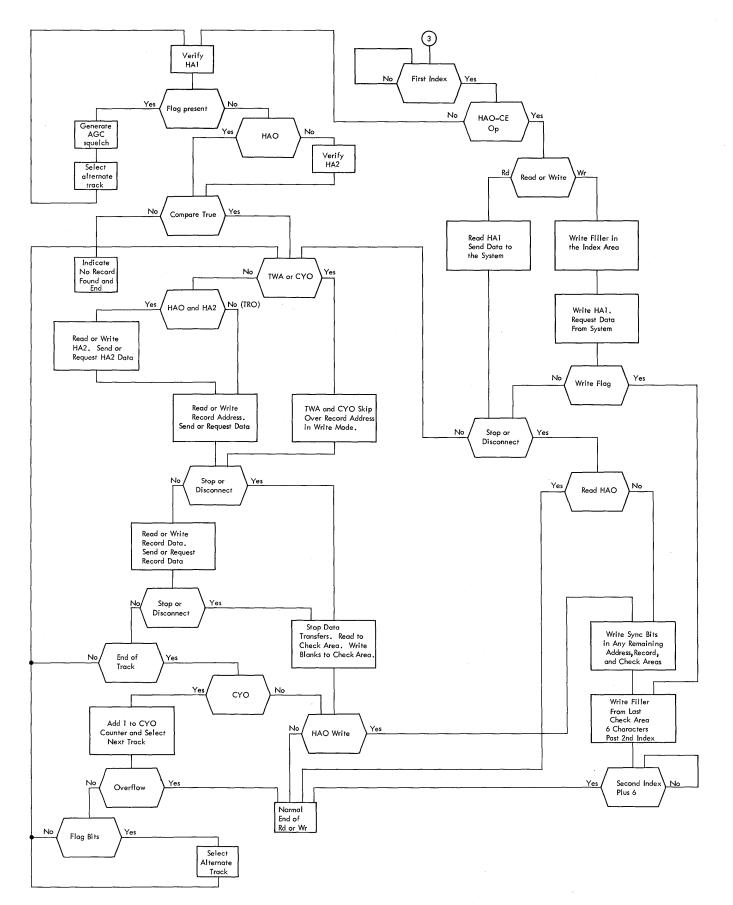

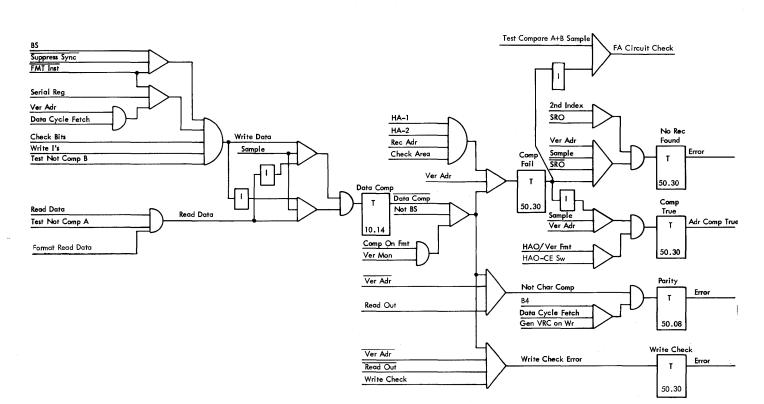

The IBM 7631 File Control unit is used to control data exchanged between the IBM 1301 Disk Storage and the IBM 1410, 7010, 7090-7094, 7080, 7070-7074, and 7040-7044 Systems (Figure 1). The 7631 File Control provides the data path, the registers, and the sequence controls necessary to exchange sense and to control data with the systems. Sense is used only for 7000 system operation. The 7631 also contains the registers necessary to position and select the 1301 read-write heads, the circuits to control magnetic reading and writing, and the timing flexibility to operate in six-bit or eight-bit mode.

The 1301 Disk Storage is available in two models:

Model 1—single module, providing capacity for 28,000,000 six-bit mode (7080) characters or, using eight-bit mode, 43,300,000 digits. Model 2-two modules, providing capacity for 56,000,000 six-bit mode (7080) characters or, using eight-bit mode, 86,600,000 digits.

7631 File Control is available in five models:

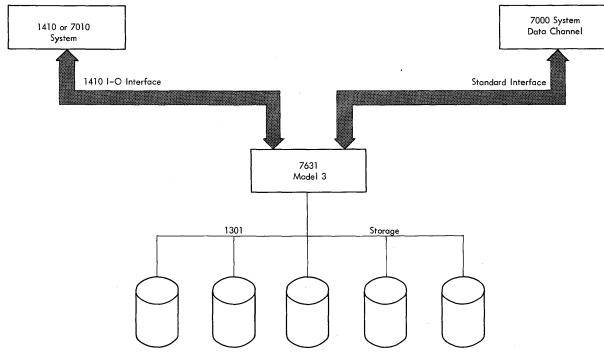

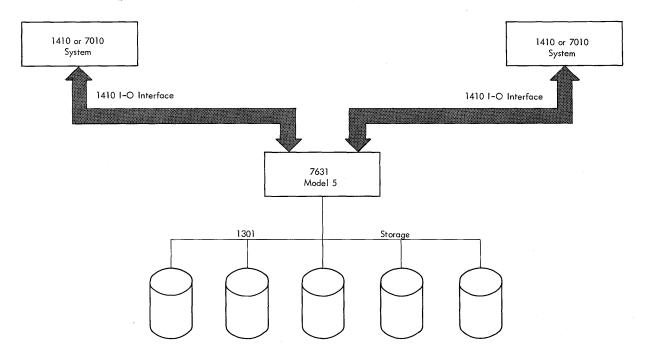

Model 1—for use with a 1410 system

Model 2-for use with a 7000 system

- Model 3-for shared use with a 7000 system and a 1410 system

- Model 4-for shared use with two 7000 systems

Model 5-for shared use with two 1410 systems

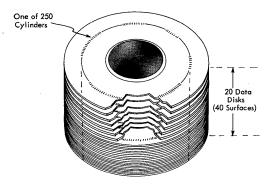

One 7631 controls up to five 1301 Disk Storage units; therefore, up to ten modules of disk storage and their access mechanisms can be controlled by one 7631. Each 1301 storage module contains 40 storage surfaces and

Figure 1. 7631 File Control Systems Relationships

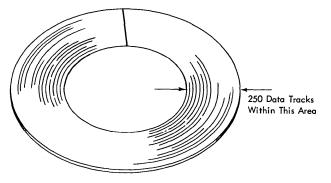

one access mechanism to position the 40 read-write heads. Each storage disk surface contains 250 concentric data tracks, and since there are 40 storage surfaces, each module contains 10,000 data tracks. Data are read or written serially by bit in six-bit or eight-bit characters or bytes. The eight-bit mode permits the use of packed mode (packing two four-bit digits into one eight-bit character) on the 7070 and 7080 systems. Data characteristics of the 1301 Disk Storage are shown in Figure 2.

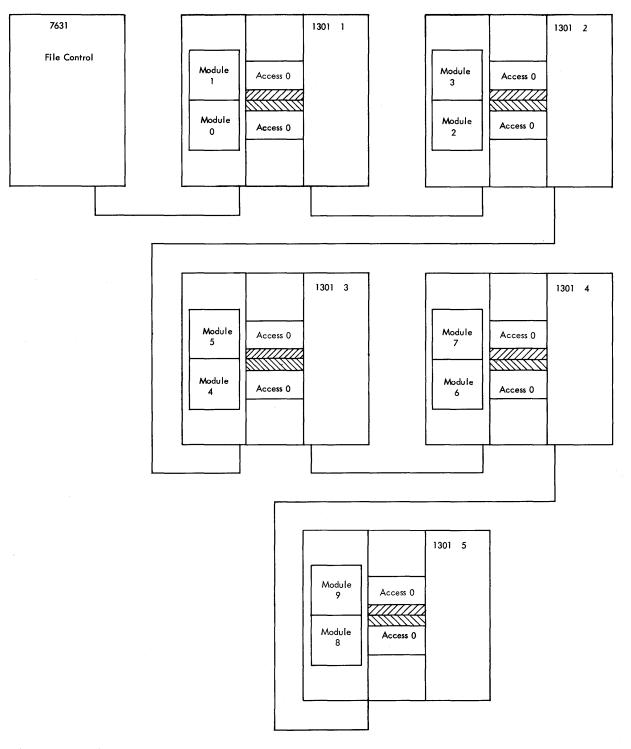

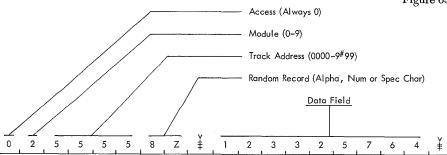

When the 1301 model 2 is used, a maximum of five

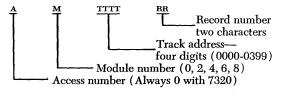

disk storage units with a total of ten modules can be connected to one 7631 File Control. The modules are addressed 0 through 9 (Figure 3). For example, to select the upper module of 1301 number 3, it is necessary to specify access zero and module five.

When 1301 model 1's are used (a single module per file frame) the access unit is in the lower half of the 1301; the access units are the even-numbered units shown in Figure 3. For example, to select the access unit in 1301 model 1 number 3, you must specify 0 and module 4.

# **Operations Scheme**

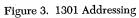

- 7631 designed to execute four commands.

- Control-set up type of file operation and specify file address where it will be done.

- Read-causes data flow from 1301 to system.

- Write-causes data flow from system to 1301.

- Sense (7000)--causes file control status data transfer to 7000 system.

The 7631 can execute four operations: control, read, write, and sense. Sense is used only for 7000 system op-

eration. All 1-0 instructions or commands issued cause the 7631 to execute one of the four operations. Each of

|                                                      |            |             |                  |                   |                      |                    | Eight-               | Bit Mode           |                    |                    |

|------------------------------------------------------|------------|-------------|------------------|-------------------|----------------------|--------------------|----------------------|--------------------|--------------------|--------------------|

|                                                      |            | Six-Bi      | t Mode           |                   | 707                  | 0/4                | 70                   | 80                 |                    |                    |

| Characteristics *                                    | 7070/4     | 7080        | 7040/4<br>7090/4 | 1410<br>7010      | Packed               | Unpacked           | Packed               | Unpacked           | 7040/4<br>7090/4   | 1410<br>7010       |

| Maximum<br>Characters per Track                      | 2,780      | 2,800       | 2,796            | 2,800             | 4,310                | 2,150              | 4,330                | 2,165              | 2,160              | 2,165              |

| Maximum Characters<br>Per Cylinder                   | 111,200    | 112,000     | 111,840          | 112,000           | 172,400              | 86,000             | 173,200              | 86,600             | 86,400             | 86,600             |

| Maximum Characters<br>Per File (2Modules)            | 55,600,000 | 56,000,000  | 55,920,000       | 56,000,000        | 86,200,000           | 43,000,000         | 86,600,000           | 43,300,000         | 43,200,000         | 43,300,000         |

| Maximum Characters<br>Per File Control<br>(5–1301's) |            | 280,000,000 | 279,600,000      | 280,000,000       | 430,000,000          | 215,000,000        | 433,000,000          | 216,500,000        | 216,000,000        | 216,500,000        |

| Character Rate                                       | 90,        | 100 Char/Se | c                | · · · · · · · · · | 140,200<br>Digit/Sec | 70,100<br>Char/Sec | 140,200<br>Digit/Sec | 70,100<br>Char/Sec | 70,100<br>Char/Sec | 70,100<br>Char/Sec |

\* Figures represent maximum utilization of space (each track written with a single record)

Figure 2. Data Characteristics of Disk Storage

the four operations causes the 7631 to operate in different sequence, and each different sequence can be divided into one or more machine cycles.

### Control

The control operation allows the file control to read in and store control data used to specify the 1301, the track, and the type of operation. There are two types of instructions (orders): miscellaneous and prepare to verify. The miscellaneous orders are used to set the bit mode for 7000 Systems, position access mechanisms, set access mechanisms inoperative, set status indicators, prevent interrupts for 1410 Systems, and to release a shared file control. The prepare to verify orders are used to define the type of read or write operation and to specify the address to be verified. The prepare to verify order must be stored in the file control before starting a read or write operation (Figure 4).

#### Read

The read signal causes the file control to execute a read operation. During the read operation the file control uses the control word data (stored during the control cycle) to select the access, module, and read-write head. Then the file control reads and compares the disk address with its stored address; if the disk address and the stored address compare, the file control transfers the specified read data from the 1301 to the requesting system (Figure 4).

### Write

The write signal causes the file control to execute a write operation. During the write operation the file control uses the stored control word to select the access, module, and read-write head. Then, the file control reads and compares the disk address with its stored address. If the disk address and the stored address

Magnetic Disk Recording

- Data is written serially by bit on 1301.

- 6 or 8 bit mode configuration.

- Data tracks are program-addressable allowing random access.

- Format track allows convenient data track arrangement of data.

The magnetic disk is a thin metal disk coated on both sides with magnetic recording material. Twenty-five disks are mounted on a vertical shaft slightly separated from each other to provide space for the movement of read-write heads. The shaft revolves, spinning the disks at a maximum of 1,790 revolutions per minute.

Data are stored as magnetized spots in concentric tracks on each disk surface (Figure 5). There are 250 customer tracks on each surface. The tracks are selected for reading and writing by positioning the read-write heads between the spinning disks. Data bits are written serially at a 1.6  $\mu$ s-per-bit rate. A written character (byte) is preceded by a sync bit (bit S) generated by the file control. The sync bit enables the file control to separate disk characters in subsequent read operations. Each bit written on the disk has a fixed relationship to the data character bits of its particular system.

Nine bits (bit S (sync), bit 0, and bits one through seven) are used to write one eight-bit mode BCD charcompare, the file control requests and writes data from the system on the specified 1301 track areas (Figure 4).

## Sense (7000)

The sense command causes the file control to transmit status data to the requesting 7000 system to indicate attention conditions, errors, and unusual conditions (Figure 4).

Figure 5. Magnetically Coated Disk

acter (Figure 6, line 1). The relative position of BCD bits to the disk data bits is shown on line 2. The eight-bit mode configuration of a BCD A is shown on line 3. The 1410 must use load mode to write word marks; the

|                                    | <u> </u> |    |    |   |   | [ |   |    |   | 1      |

|------------------------------------|----------|----|----|---|---|---|---|----|---|--------|

| Disk Data Bit Positions            | s        | 0  | 1  | 2 | 3 | 4 | 5 | 6. | 7 | Line 1 |

| BCD Bit Positions (1410 Load Mode) |          | BI | WM | В | A | 8 | 4 | 2  | 1 | Line 2 |

| BCD A in 8-Bit Mode                | 1        | 0  | 0  | 1 | 1 | 0 | 0 | 0  | 1 | Line 3 |

| 7070/4 and 7080 Pack Mode Bit Pos  |          | 8  | 4  | 2 | 1 | 8 | 4 | 2  | 1 | Line 4 |

| Digits 5 and 3 in Pack Mode        | 1        | 0  | 1  | 0 | 1 | 0 | 0 | 1  | 1 | Line 5 |

Figure 6. Disk Data Eight-Bit Mode

| Disk Data Bit Positions | S | 0 | 1. | 4 | 5 | 6 | 7 | Line I |

|-------------------------|---|---|----|---|---|---|---|--------|

|                         |   |   |    |   |   |   |   |        |

| BCD Bit Positions       |   | В | A  | 8 | 4 | 2 | 1 | Line 2 |

|                         |   |   |    |   |   |   |   |        |

| BCD A in 6-Bit Mode     | 1 | 1 | 1  | 0 | 0 | 0 | 1 | Line 3 |

|                         |   |   |    |   |   |   |   |        |

| Digit 5 in 6-Bit Mode   | 1 | 0 | 0  | 0 | 1 | 0 | 1 | Line 4 |

Figure 7. Disk Data Six-Bit Mode

word mark bit is recorded in the disk data bit 1 position. The 7070-7074 and 7080 systems can operate in packed mode so that the file control in eight-bit mode can record two non-zoned characters in the nine disk data bit recording positions (line 4). The eight-bit mode configuration of two non-zoned characters is shown on line 5.

Seven bits (bit S (sync), bit 0, bit 1 and bits 4 through 7) are used to write one six-bit mode BCD character (Figure 7, line 1). The file control circuits are designed to skip bit 2 and bit 3 time intervals in six-bit mode operation; therefore, character recording rate is increased over eight-bit mode unpacked recording, and the maximum characters per track are increased (Figure 2, "Maximum Characters Per Track" and "Character Rate"). The position of the BCD bits relative to the disk data bits is shown in Figure 7, line 2. The six-bit mode configuration of zoned and non-zoned characters is shown on lines 3 and 4.

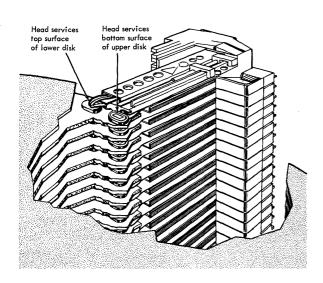

The read-write heads are mounted on an access mechanism which has 24 arms, arranged like teeth on a comb, moving horizontally between the disks. No vertical motion is involved (Figure 8). Reading and writing are possible on both sides of a disk. Two readwrite heads are mounted on each arm; one head services the bottom surface of the upper disk while the other head services the top surface of the lower disk.

The magnetic disk data surface can be used again and again. Each time new information is stored on a track, the previous record information is erased. The recorded data may be read as often as desired; data remain recorded in the tracks of a disk until written over.

Disk storage, like trays of cards or magnetic tape, provides external storage capacity to supplement computer core storage. Disk storage has a major advantage, however, in that all records contained in the 1301 are program-addressable, providing random access to any record or group of records (faster access to any record).

Although the total number of character positions of the track is fixed, the number of records and the number of characters per record can be arranged to suit the needs of a particular system. Addresses must be provided to identify the track and each record, and space must be provided in the form of gaps to separate address and record areas.

A format track provides a means of defining and monitoring the address, record, and gap areas for the data tracks. One format track monitors 40 associated data tracks, and can be changed to describe the data track format the user needs.

A disk storage module is a stack of 25 magnetic disks and an associated access mechanism. Forty surfaces of the 25 disks are used to store data. Of the other ten surfaces, six are used as alternate surfaces, one is a format surface, one is a clock surface (Figure 9) and the remaining two surfaces are not used. The data storage surfaces and the format surface each contain 250 concentric tracks that are accessible for reading and writing.

Figure 8. Read-Write Comb

DISK SURFACE MODULE 0 MODULE 1 Not Used Not Used 24 38 23 37 36 22 21 20 30 10 6-19 2-29 5 4 Alternate Alternate 3 2

Alternate

Format

Spare Clock Alternate

Not Used

Format Spare

Figure 9. Disk Surfaces

1

0

6

# Cylinder Concept

- 1301 data tracks are aligned one above the other.

- 40 tracks for each access setting = one cylinder (plus format track and alternates).

- 250 cylinders = 10,000 (plus CE) in one module.

- One module = 10,000 tracks × 2,800 characters/track = 28,000,000 characters.

- Two modules/file = 56,000,000 characters.

Because the heads and disk tracks are mechanically aligned one above the other, the vertical alignment of the tracks can be described as a cylinder of tracks (Figure 10). When the access mechanism is placed in any one of the 250 cylinders, 40 tracks of data are available without any other access motion; only electronic head switching is necessary. For example, in one access mechanism setting as many as 112,000 characters (7080) are available.

The tracks are numbered sequentially from the bottom to the top of the cylinder (corresponding to the 40 heads, 00 to 39), starting at the outermost cylinder (000) to the innermost cylinder (249). Thus, with large storage areas for reference tables, the data can be conveniently stored in a cylinder of tracks or in a number of adjacent cylinders. This technique reduces access time to a minimum. The cylinder arrangement of tracks also permits the optional feature, cylinder mode of operation, to read or write a cylinder (or part of a cylinder) of tracks in one operation.

Figure 10. Cylinder Concept

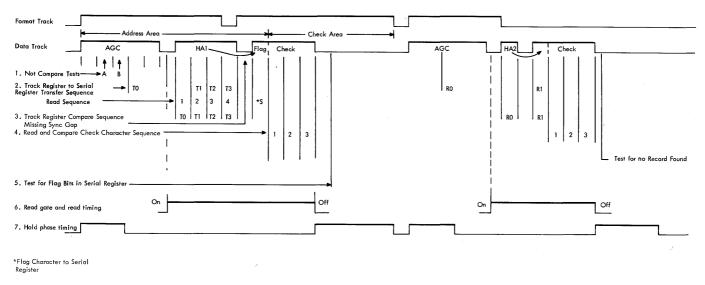

# Data Tracks

- Index timing defines beginning and end of track.

- Each track has distinct areas to record information.

- Each area consists of AGC, data and check characters.

- Each area is separated by gaps.

- The data track areas will always follow the sequence: HA1, HA2, RA, Rec, RA, Rec, etc.

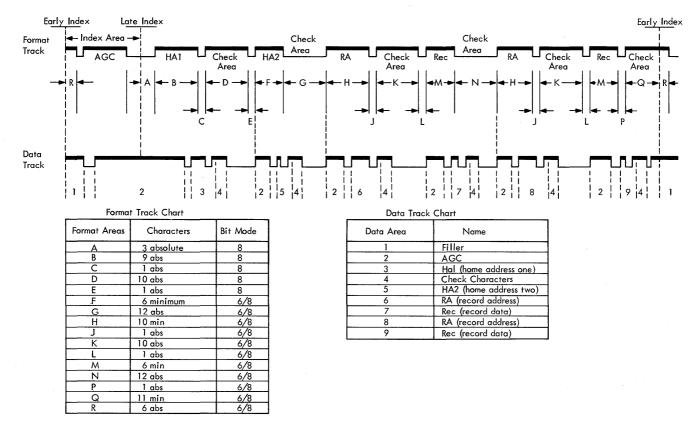

The basic fixed recording area of the 1301 is the data track. The physical make-up of the track limits it to a specific overall recording capacity. Although each track has equal overall recording capacity, this capacity depends on the number of records and number of characters per record, because track areas needed to separate and define recorded areas cannot be used for data recording (Figure 11). Each data track has seven distinct areas:

- 1. Index area

- 2. Home address area

- 3. Record addresses

- 4. Records

- 5. AGC

- 6. Check character areas

- 7. Gaps

Figure 11. Format and Data Track

### Index Area

The index point is the reference point of the track. Because the data track is circular, its beginning and end must be sensed. A magnetic slug is mounted on the outer edge of the format track disk for this purpose. Late and early index signals are generated as the slug rotates past two magnetic sensors. The magnetic sensors mounted through the array shield are physically displaced to create a 475-microsecond interval between the early and late index signals. Early index signals the end of a track and late index signals the beginning of a track to the 7631 (Figure 11, index area).

### Home Address 1

This portion of the home address is the track number (Figure 11, area 3). HAI consists of five numeric characters written by the customer engineer; it should not be written by the customer. The four high-order positions of HAI contain a four-digit track number (0000-9999) that identifies the physical track location within the module. The low-order position (fifth character) is the track flag character. The flag character function is discussed in the section, "Verify Address Cycle." The flag character must be a blank or an eight to prevent a flag operation.

The last character of each address and record is separated from the preceding address or record characters by a one-character gap. This is written to provide greater format/data skew tolerance.

Tracks are numbered sequentially starting with the bottom track of the outermost cylinder, track number 0000, and continuing up through the cylinder to track number 0039. There are 40 data tracks in each cylinder. The track numbers continue with the lowest track of the adjacent cylinder, track 0040, up the cylinder to track number 0079. Continuing through each of the cylinders, the last track number, 9999, is the top track of the innermost cylinder; therefore, adjacent tracks on the same disk always differ by 40. This provides a formula to determine the track number for any track within any cylinder: given the head number and the cylinder number, the track number is the product of the cylinder number and 40 plus the head number. For example, for cylinder number 241 and head number 20 the track number is:  $241 \times 40 = 9640 + 20 = 9660$ . The cylinder number and head number can be determined by dividing the track number by 40: the quotient will be the cylinder number, the remainder will be the head number. For example, if the track number  $0590 \div 40 = 014$  with a remainder of 30; the cylinder number is 014 and the head number is 30.

### **Home Address 2**

The second portion of the home address (HA2) is called the home address identifier or random record area (Figure 11, area 5). This portion of the address further identifies the track to the using system. HA2 is written by the user and consists of two or more numeric, alphabetic, or special characters, depending upon the requirements of the using system. Two characters are required for HA2, and although only two characters are compared during address verification operations, additional characters may be used.

HA2 can be written to serve any convenient purpose. It can be used as a coded file protect device or it can be used to identify or tag a category of records, such as receipts, withdrawals, payments, or inventory.

On certain read or write operations the file control reads and compares the first four (high-order) positions of HA1 and the first two (high-order) positions of HA2 with address data stored in the file control. The address verification assures the correct track selection before data reading or writing.

#### **Record Addresses**

Each record on the data track must be preceded by a record address, which identifies individual records, allowing random access to any file record (Figure 11, area 6).

The record address must be six or more alphameric characters. Only the first six characters are compared during the verify address cycle. The numeric portion of the four high-order characters are compared, but all bits of the fifth and sixth characters are compared.

No relationship is necessary between the record address, used to identify an individual record on a track, and the home address recorded on the track. Record addresses are assigned and written by the user to fit any convenient addressing scheme.

## **Record Areas**

The record areas contain the record data (Figure 11, area 7). There may be one or more records with a minimum of two characters and a maximum limited by the physical length of the track.

#### AGC Areas

Automatic gain control (ACC) compensates for signal variation at the selected read-write heads. A five-character burst of all bits is automatically recorded immediately before each address or record area. The fivecharacter ACC burst is recorded before every address or

.

record written. When reading, the AGC bits generate a bias voltage used to adjust the read amplifier gain before reading data bits (Figure 11, area 2).

### **Check Areas**

When writing an address or record on disk, the file control develops a three-character check code for each address or record written and records the check character code on the disk (Figure 11, area 4). When an address or record is read, the file control uses the read data to generate the same check code and compares it against the previously written check code. If a true comparison is not made, an error condition results. The check characters appear on the file as the last three characters of a four-character field. The first character of the four-character field is the last character of the preceding address or record.

#### Gaps

A one-character gap is written automatically by the file control to separate each address and record from the preceding five characters of ACC (Figure 11). When reading, this gap is detected by the data gap singleshot. The absence of ACC bits causes the data gap singleshot to time out. Data gap singleshot output rises to indicate the next bits are either address or record data.

A second one-character gap is written automatically by the file control in the main body of each address or record (Figure 11). This one-character gap separates the last address or record data character from the preceding characters. This gap is different from the onecharacter gap that separates AGC from the address or record data because it is written without a sync bit. When reading this gap, the missing sync bit conditions three file control triggers (the three zeros triggers). These triggers enable the file control to read the character after the gap as the last address or record character, and to process the remaining three characters as check characters. Check characters are read, transferred to the file control, and used to verify the validity of the address or record data read; they are never transferred to the system.

Following the check characters, a third data gap (nominally six characters in length) is present for two reasons: (1) when writing does not involve a complete track, space is provided to prevent partial erasure of the next address or record area because the erase head precedes the read-write head; (2) to allow space (time) to switch the file system from read to write status if the operation requires it. The end of this third type of gap, the start of the next address or record area, is determined by the output of two format track singleshots. These two singleshots, the short and long gap singleshots, monitor format track data and are discussed with the following section, "Format Track."

# Format Track

- Written to define storage space (data areas) of data tracks.

- Format track written as all bits or no bits.

- No bit areas (gaps) recognized by format singleshots to define data areas.

The format tracks are written to define how the storage space of the tracks is to be divided into records, identified, and used. This is similar to the field definition function performed by a keypunch program card.

Before data can be written on a data track, the format track must be written for the cylinder. Provision is made to allow reading any data track regardless of the presence or condition of the related format track. The 253 format tracks, one for each customer cylinder (250 total) plus three for CE operations, are located on one disk surface: the format disk.

Format tracks are written as areas of all bits or no bits. HA1, HA2, record address, record, and filler areas are written with all bits characters. The format track gap areas are written with no bits characters. The format track gaps are sensed with the short and long gap singleshots; the trailing edges of the gaps are sensed with the short and long gap holdover singleshots. Format gaps are either short gaps (three microseconds or greater) or long gaps (24 microseconds or greater). The sequence of format track areas must be: HA1, gap, check area, gap, HA2, gap, check area, etc.; therefore, any related data track area can be recognized with the short and long gap singleshot outputs (Figure 11, format track).

The short and long gap singleshot outputs are applied to the format recognition circuit inputs. The format recognition circuit converts the singleshot input signals to address, record, and check area outputs, which condition the file control to process the read or write data accordingly. For example, if the file system processes an address area (Figure 11, area H) and recognizes a format track short gap (Figure 11, area J), the format recognition circuit output signals check area, and check area signal conditions the file control to process the check characters because each address area is always followed by a check character area. Another example: if the file system processes a check area following an address area, and recognizes a format track short gap (Figure 11, area L), the format recognition circuit signals record area and record area signal conditions the file control to process record data because each address check area is always followed by a record area.

While the file control is processing the record area (Figure 11, area M) both the short and long gap singleshots time out in the format track long gap (Figure 11, area N). When the short gap singleshot times out, the record check area is defined because each record area must be followed by the record check area. The long gap singleshot times out and remains off until the first bit of the following address area (Figure 11, area H) is sensed. When long gap singleshot detects the trailing edge of the long gap (Figure 11, area N), the file control is conditioned to process an address area. Every time the long gap trailing edge is detected, the file control is conditioned to process an address area.

The format recognition sequence repeats. The short gap (Figure 11, area P) following the last record area is detected. The short gap signal following a record area signals the file control that the last record has been processed and all that remains to be processed are record check characters.

# **Operations**

- All 7631 operations involve one or more of the five basic cycles.

- Control cycle-sets type of operation and file address where it will be done.

- Prep read-write cycle-prepare 7631 and 1301 to read or write.

- Address verify cycle—prove correct track is selected in 1301.

- Read data cycle-transfer 1301 read data to system.

- Write data cycle-transfer system write data to 1301.

All 7631 operations involve one or more of the five basic cycles:

- 1. Control

- 2. Prep rd-wr (prepare to read-write)

- 3. Verify address

- 4. Read data

- 5. Write data

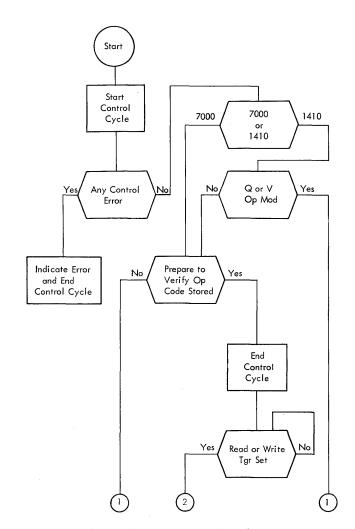

All on-line 7631 operations (except a sense command from a 7000 system) started by a 7000 control command or a 1410 file operation issued to the 7631 cause the 7631 to execute a control cycle. During the control cycle the 7631 requests and receives an order word to store in the operation and address registers. At the completion of the control cycle the 7631 has stored operation data defining the operation to be performed and the address data that tells where to perform the operation.

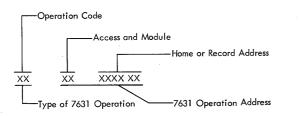

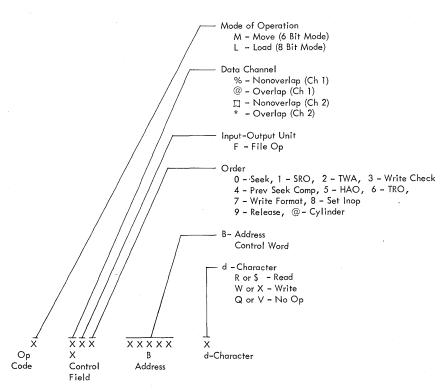

The 7000 system order word transmitted from the data channel to the 7631 during a control cycle usually contains a two-character operation code and eight characters of address information (Figure 12). Since some operations do not require address information, only the two-character operation code is transmitted to the 7631.

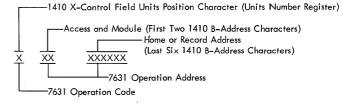

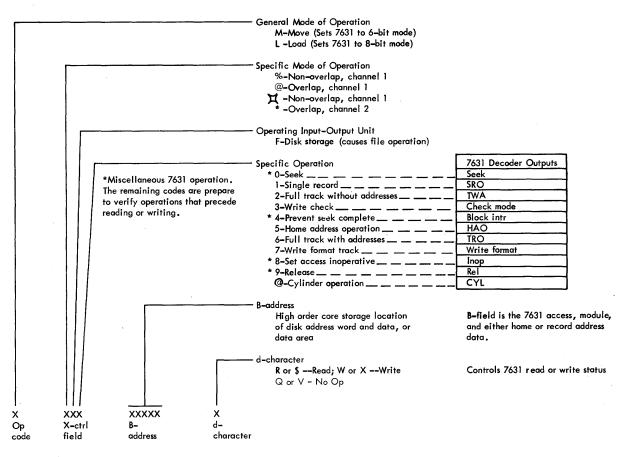

Control data transmitted from the 1410 to the 7631 always contain an op code character and eight BCD address characters (Figure 13). The op code character is transferred directly from the 1410 units number register to the 7631 operation decoder. The operation decoder output sets a 7631 control op trigger; the 1410 address data is stored in the 7631 address register.

### Control

- Requests control data from the using system.

- Decodes the operation or order code.

- Stores the control data (address data).

- Issues signals to the selected 1301 file when required.

- Signals end of control to the using system.

A control operation is a preparatory cycle for subsequent 7631 read or write operations. Essentially a control operation serves the same function in a 7631 as the

Figure 13. 1410 System Control Data for 7631

instruction readout cycle serves in a computer; the main difference is that the 7631 must obtain its control data (instructions from 1410 systems, orders from 7000

systems) from an attached system. Any file operation started by the 1410 or any control command accepted by the 7631 results in a control cycle. Once a control operation is started, the 7631 performs as described.

Briefly, the 7631 control circuits are used to store instructions or orders transferred from the system before reading or writing (Figure 14).

Access unit positioning, bit mode, the address to be verified, and the type of reading or writing are determined by control data stored in the 7631 during control cycles. Consider the control cycles that must precede reading or writing:

1. Control-seek: A control cycle (executed by the 7631 in response to the using system's file operation) stores control data that is transferred to the selected 1301 access unit. The control data transferred from the 7631 to the 1301 causes the 1301 to position the read-write heads to the correct cylinder.

2. Control-bit mode (7000 only): The 7631 reads or writes in six- or eight-bit mode. Control data decoded

Figure 14. 7631 File Control Simplified Operations

during this control cycle determines the bit-mode of the next read or write operation.

3. Control—prepare to verify: The operation code stored during this third control cycle determines the type of read or write operation: single record operation (SRO), track without address (TWA), etc. The eight bytes of control address data stored are used to select the correct 1301 access and module and to provide the address of the track or record on the following verify address cycle.

### **Read-Write**

Receipt of the read or write signal causes the 7631 to select the access mechanism and read-write head with the address data stored during the previous controlprepare to verify cycle. The 7631 then synchronizes with 1301 rotation, locates the correct read or write data area, and either requests and writes data from the system on the designated track areas, or reads the designated track areas and transfers the read data to the system (Figure 14). Each read or write sequence can be divided into cycles: prepare to read-write, verify address, and read or write data.

# Cycles

## **Prepare to Read-Write Cycle**

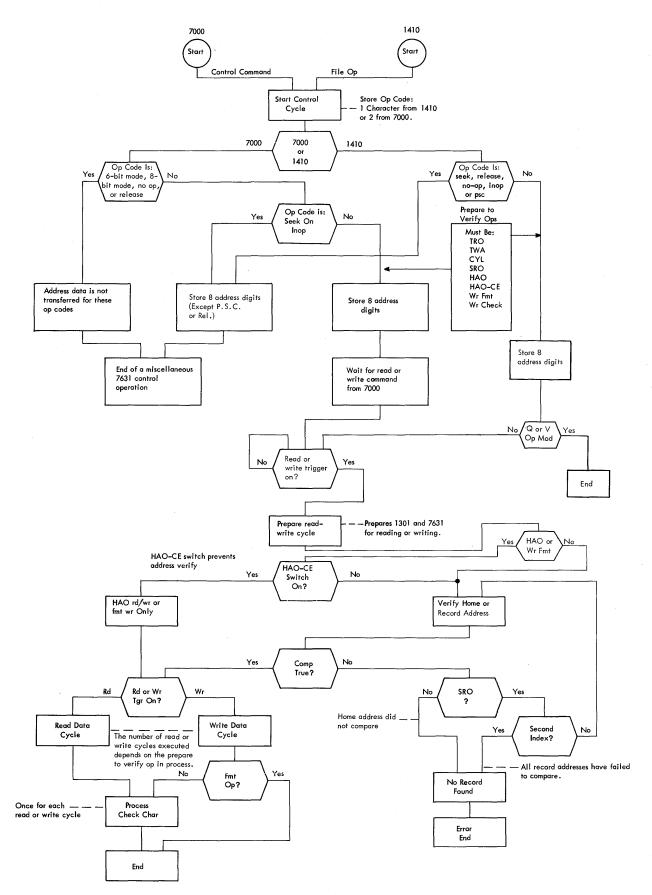

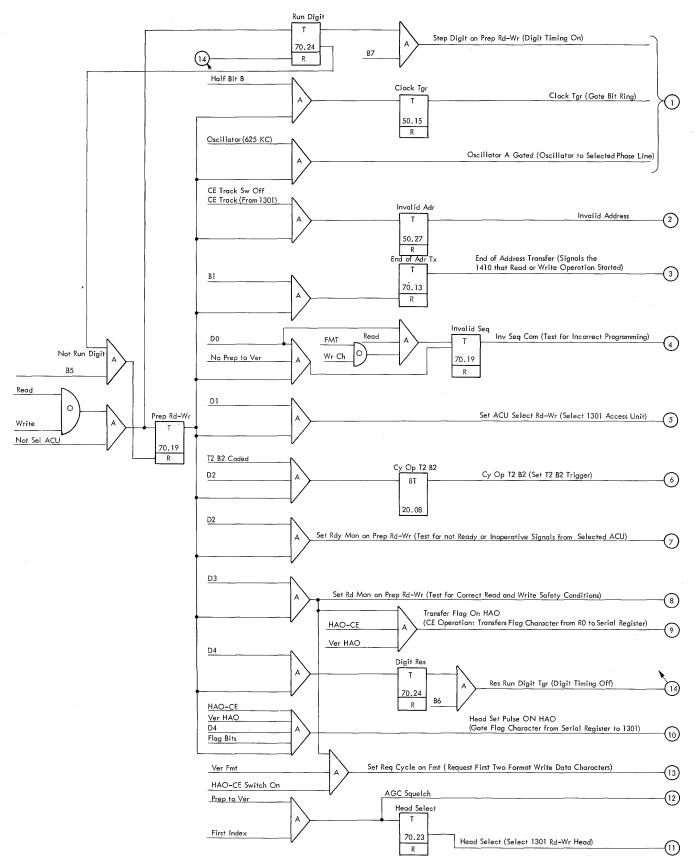

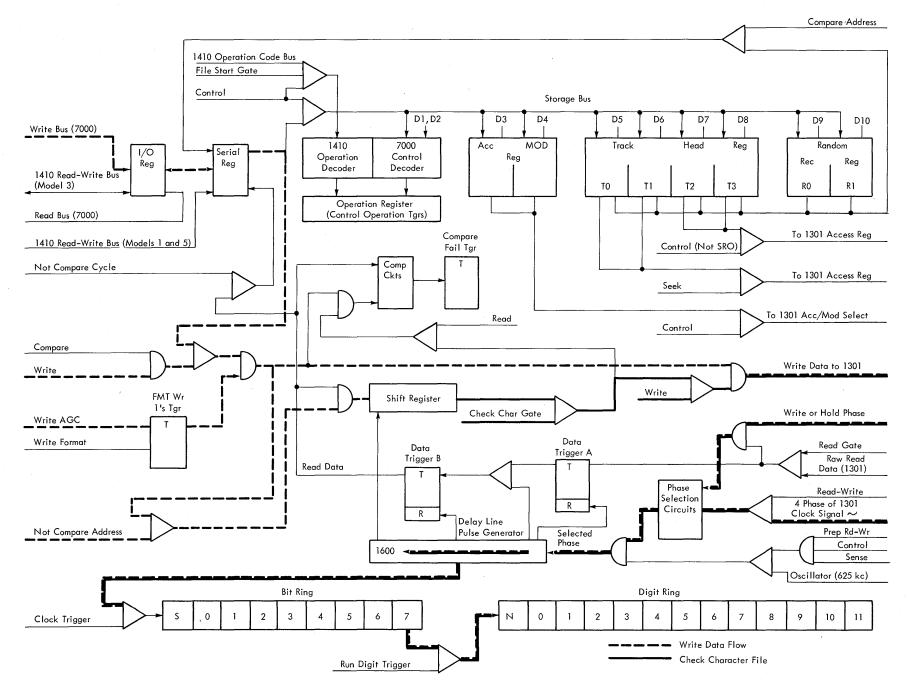

Receipt of a read or write signal causes the 7631 to start a prepare to read-write cycle. All read or write operations start with a prepare to read-write cycle, which prepares both the 7631 and the 1301 for reading or writing (Figure 15). If all the prepare to read-write cycle functions are not successfully completed, the 7631 indicates an error occurred and prevents continued read or write operation.

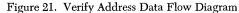

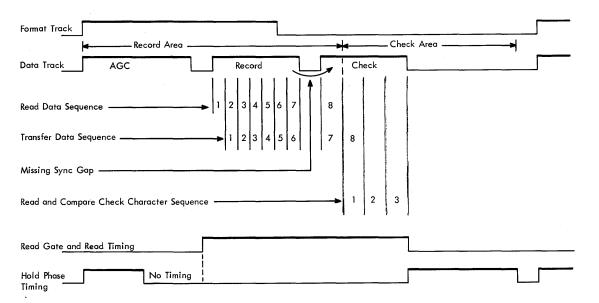

### Verify Address Cycle

The verify address cycle is executed after a successful prepare to read-write cycle, except when the HAO-CE switch is active and the operation is either HAO read, HAO write, or format write. These three operations (special CE operations) executed with the HAO-CE switch active cause the 7631 to bypass the address compare cycle. During the verify address cycle the address stored in the 7631 address register (track-head and random record sections) is compared with either the home address or the record address read from the disk (Figure 15). (If the track contains more than one record, a number of address verify cycles can occur for single record operation because record addresses are compared until the comparing record address is found.)

The address data read from the disk is compared bit by bit with the stored address data and is also used as the input to the shift register to generate check characters. After the last bits of address data are compared, the 7631 reads the check characters and compares them bit by bit with the generated check characters to verify the validity of the address data read from the disk. If a compare failure occurs during the address data or check character comparisons, the no record found trigger is set to end the operation and prevent the read or write data cycles from occurring.

### **Read Data Cycle**

Following a successful address compare cycle with the read trigger set, the 7631 locates the read data area, address or record area, depending on the type of prepare to verify operation stored, and reads each bit from the track into the 7631 serial register storage. The read bits are stored in the serial register until a complete character is assembled and the correct parity is assigned. The data character, with a parity bit, is transferred to the system and the next character is read. Each bit read from the disk is also entered into the shift register where the check characters are generated.

Check characters read from the disk after the address or record characters are compared with those generated by the shift register; the check characters are not transferred to the system but are used to determine the validity of the read data. If the check characters do not compare, the 7631 indicates a parity error after the read operation is complete. A parity error does not stop or alter the read operation except to indicate the error occurred. The read data cycle repeats for each additional address or record area if the prepare to verify operation requires additional track data transfers (Read Data Cycle, Figure 15). The read operation ends when either the 7631 reads and signals that the last of the data characters are transferred, or the system signals end after the required amount of data has been received.

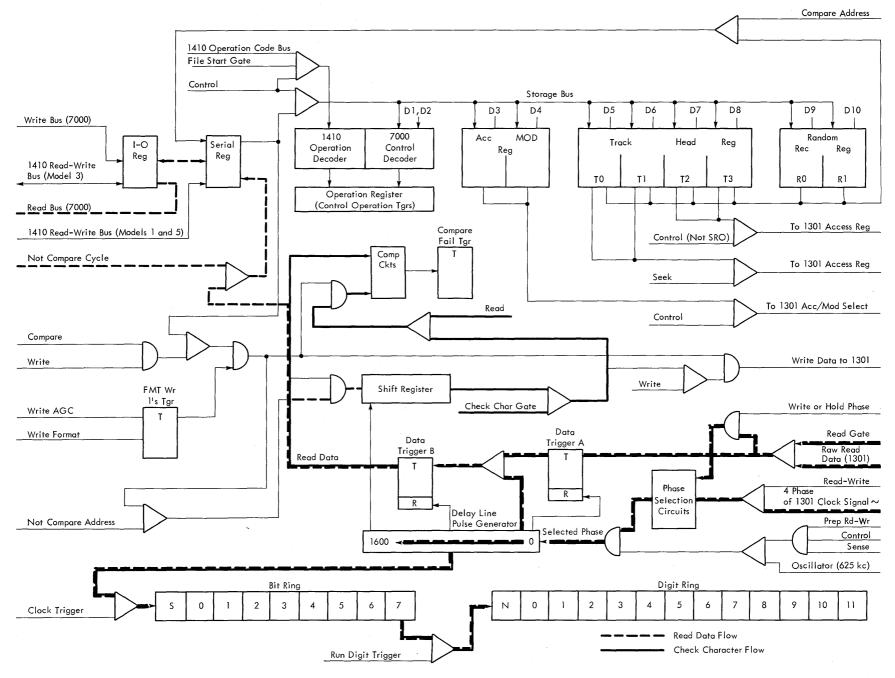

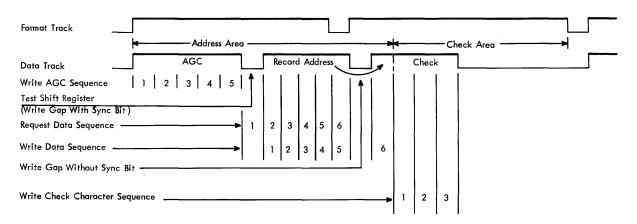

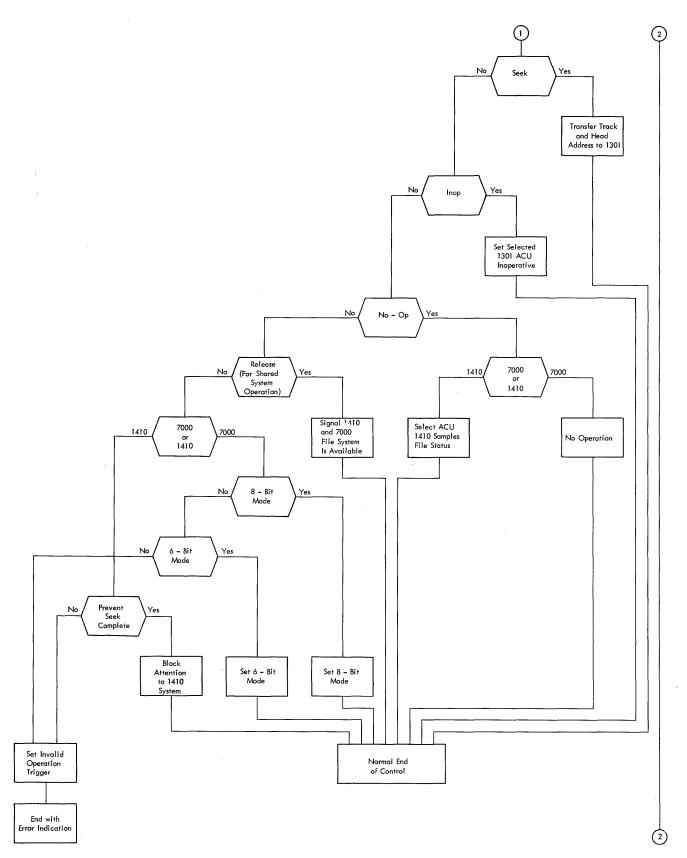

#### Write Data Cycle

Following a successful address compare cycle with the write trigger set, the 7631 starts a write data cycle. During a write data cycle the 7631 must first locate the area to be written; this area can be an address or record area depending on the type of prepare to verify operation. When the correct area is found, the 7631 generates and writes the required five-character ACC burst and the one-character gap following. After the gap the first write data character is transferred into the serial register where it is checked for correct parity. If parity is incorrect, the 7631 indicates a parity error after the write operation is complete. A write parity error does not stop the write operation, but indicates an error after the write operation completes.

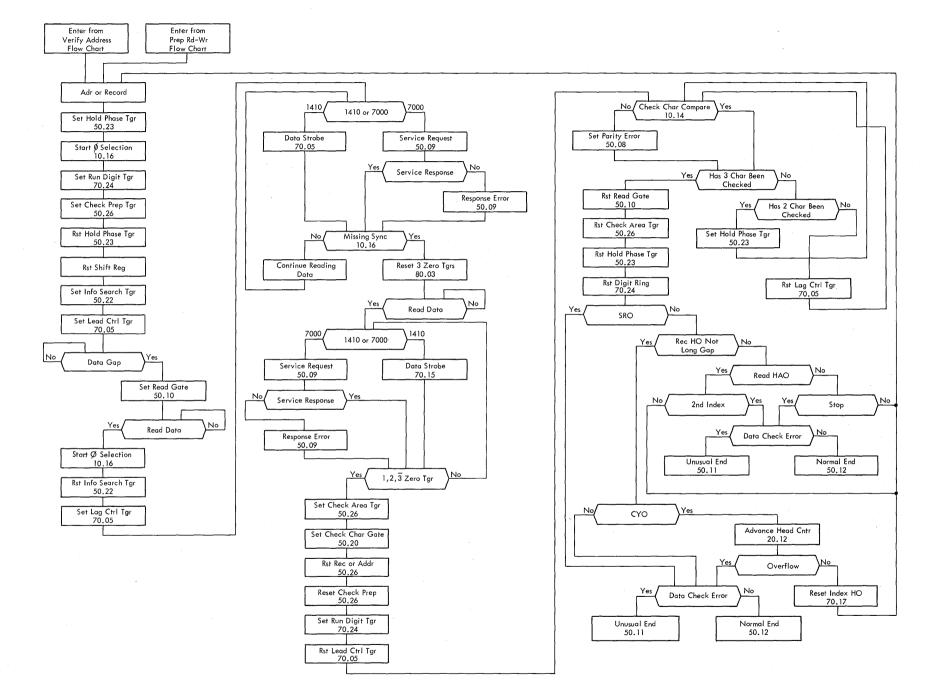

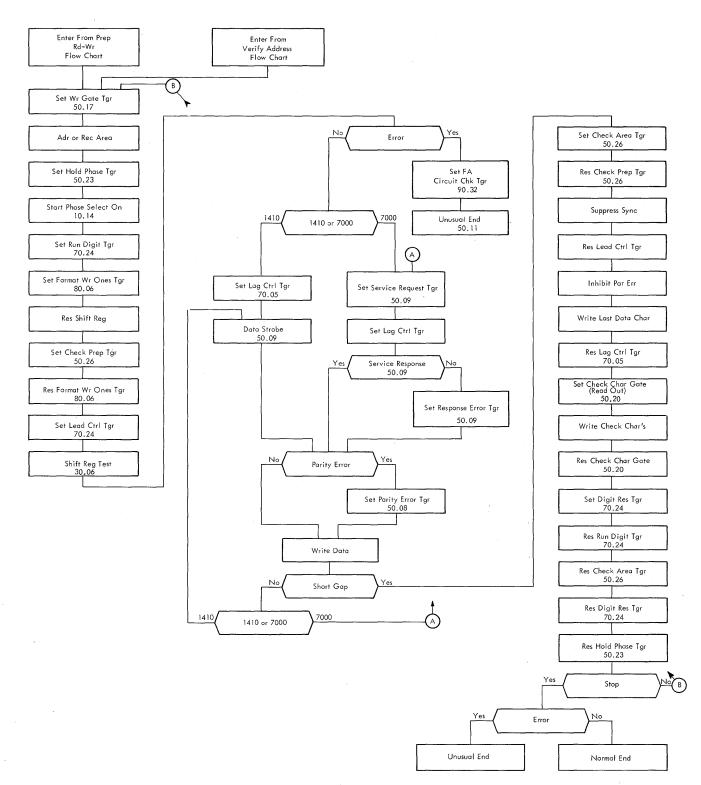

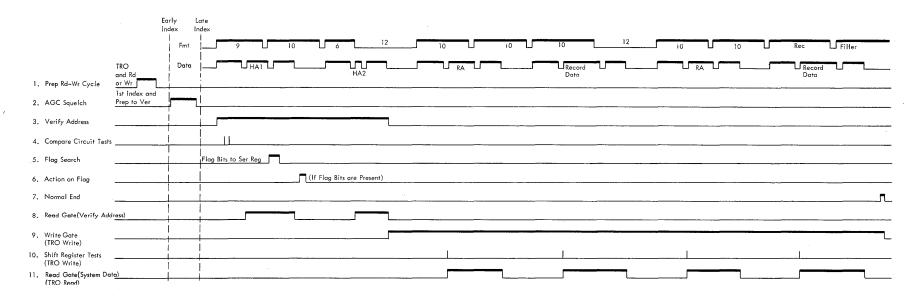

Figure 15. Operations Flow Chart

The character in the serial register is transferred bit by bit to the 1301, where it is written, and also enters the shift register where check characters are generated. The request, write data, and check character generation continue until the write data area is filled. The shift register contents (three check characters) are recorded immediately following the last character of write data to conclude the write data cycle. The write data cycle repeats for each additional address or record area if the prepare to verify operation requires additional track data transfers (Write Data Cycle, Figure 15). The write operation ends when the 7631 finds the track recording areas are filled with write data, or when the system signals end after the last write data is transferred to the 7631.

### Sense Command (7000 Systems only)

The sense command is used by the 7000 systems to obtain status information from the 7631. Receipt of the sense command causes the 7631 to transfer the status word to the 7000 system (Figure 14). The status word is made of ten 4-bit bytes of error, status, and attention information. Ten sense data transfers are required to transfer a complete sense word.

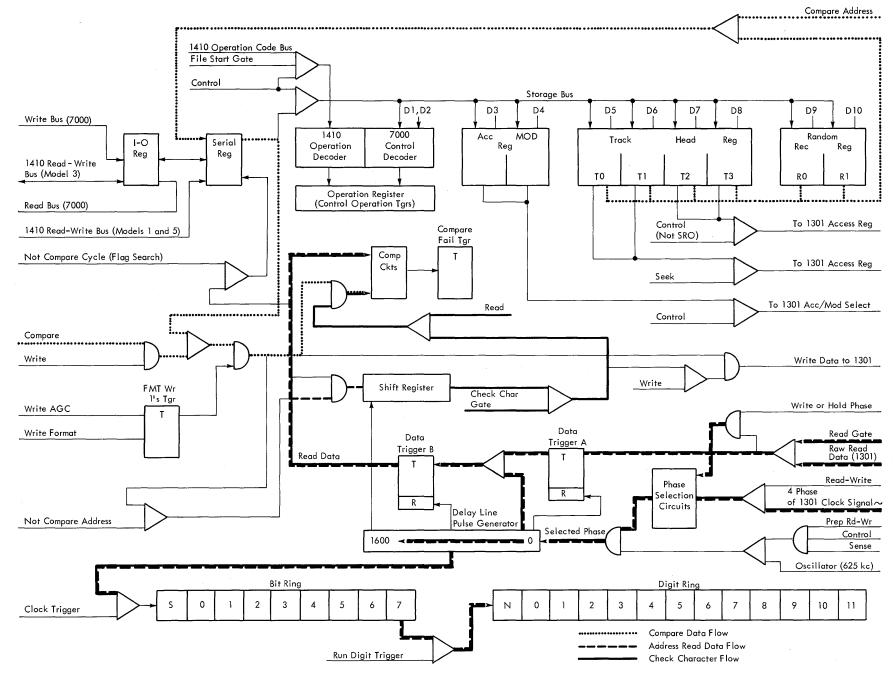

# Cycle Sequence

- Two primary timing sources are used.

- 625 KC oscillator in 7631 is used for control, prep R/W cycles and sense (7000).

- 625 KC clock track on 1301 is used for address verify, read and write cycles.

### **Machine Timing**

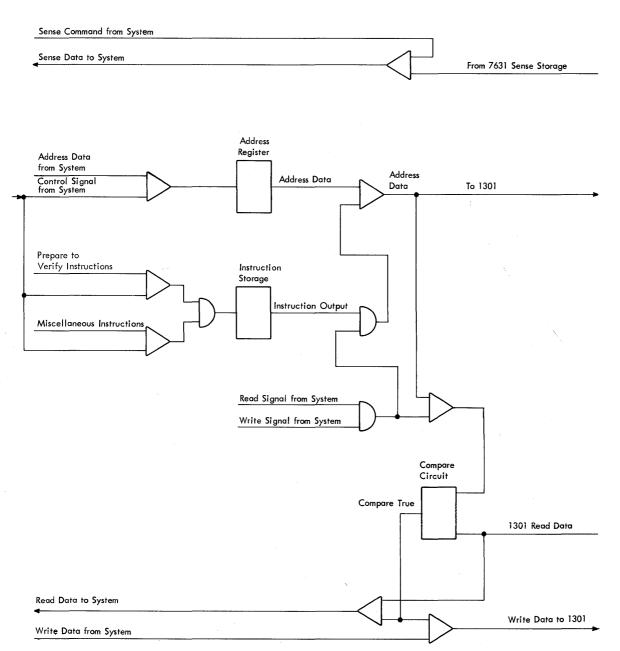

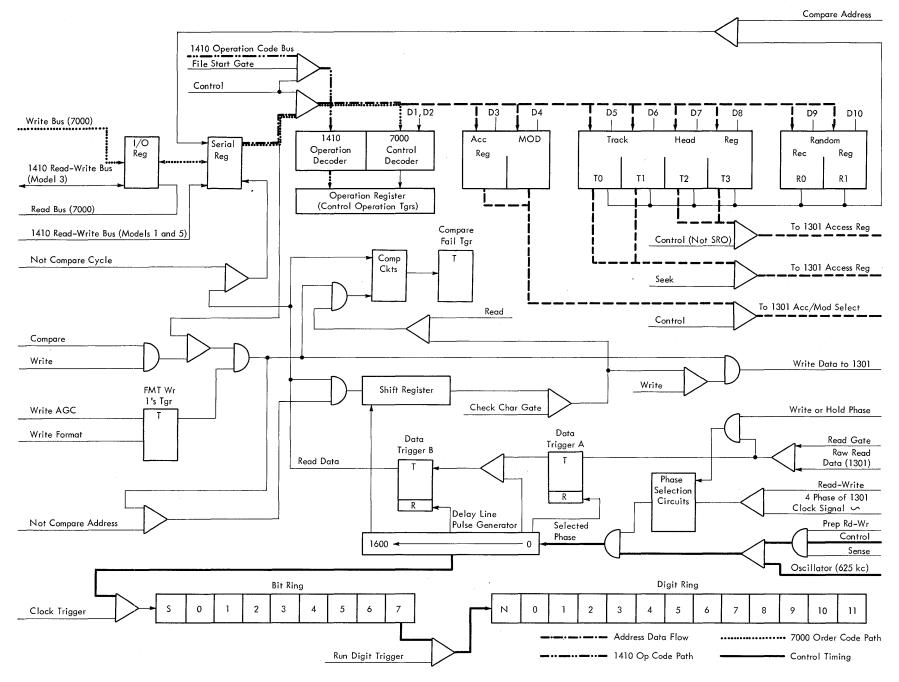

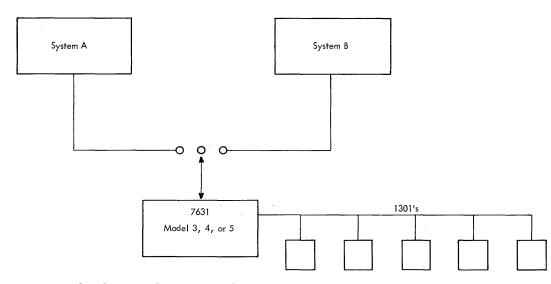

The two primary sources of timing used by the file control are:

1. A prerecorded 625-κc clock track, written on the 1301, which provides the primary timing source for operations causing bits to be written on or read from the 1301 file (Figure 16).

2. A 625-KC oscillator in the file control unit which provides timing for operations that do not cause bits to be written on or read from the 1301 (control, sense and prepare to read-write) (Figure 16).

Data operations fall into one of two categories: read or write.

*Read:* The 1301 is a mechanical device, and the data heads and clock head are not rigid and immovable, so that the timing relationship between any given data head and the clock head does not remain constant. For proper clocking during a read operation, the timing re-

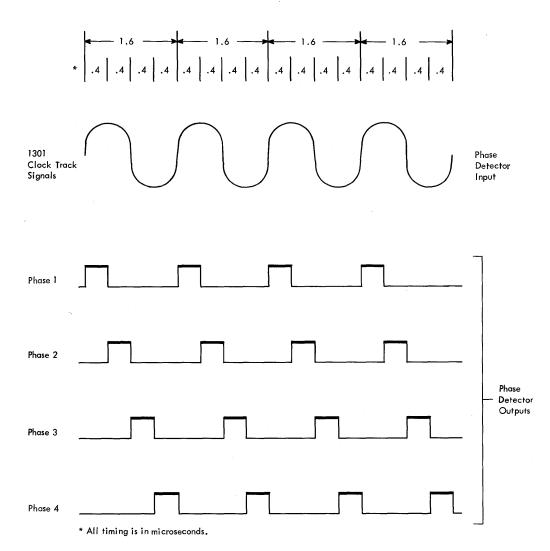

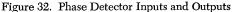

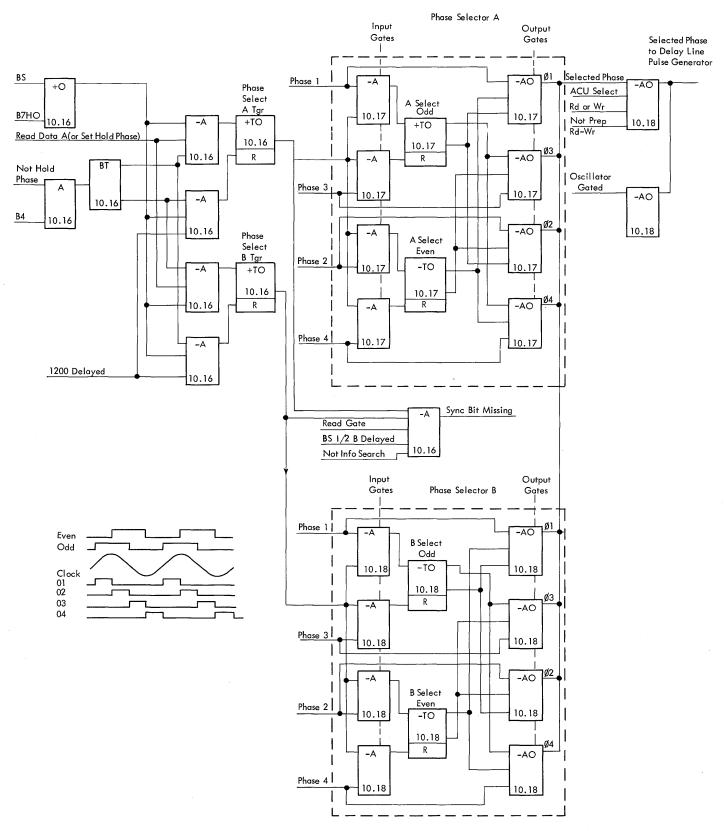

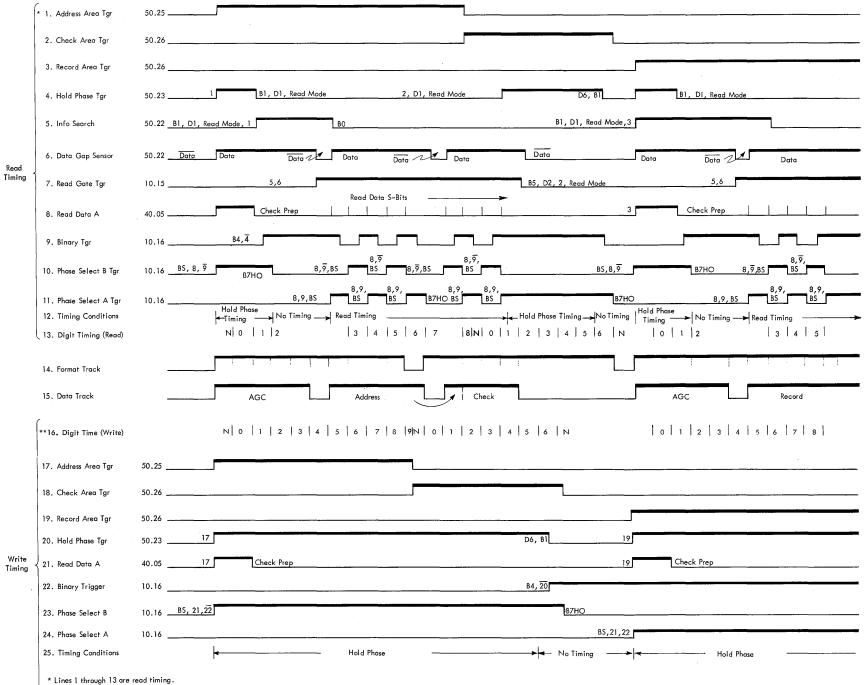

lationship of the data track and the clock track is established at bit sync time of each character. The 1.6 microsecond sine wave read from the clock disk is divided into four 400-nanosecond segments called phases 1, 2, 3, and 4. The first bit (sync bit) of each character arrives during one of these phase timings and causes the phase selection circuitry to "lock on" (select) and gate the appropriate phase pulses to the delay line. The timing sequence for each character read is started in relation to its bit-sync, insuring correct data clocking.

*Write:* When writing, the hold phase line is made active. Hold phase causes the phase selector to select one of the four timing phases and write the entire data area with the same timing phase.

Non-data operations are control, sense and prepare to read-write. During non-data operations the phase selection circuitry is degated and the 625-KC oscillator is gated to the delay line pulse generator input.

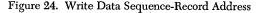

Figure 16. Control Data Flow Diagram

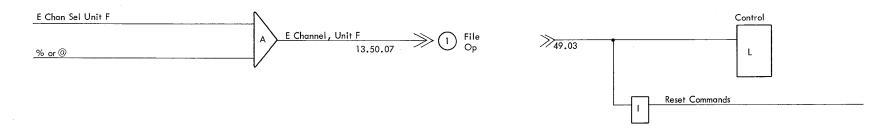

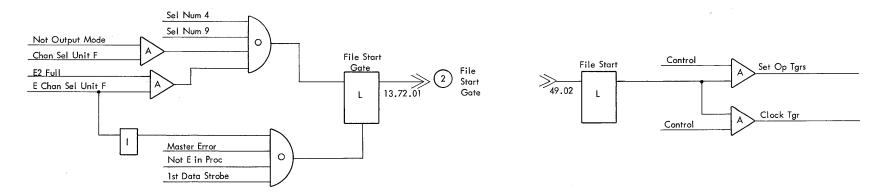

## 1410 Control Cycle

- Initiated by file operation from 1410 unit select register.

- Sets type of file operation from 1410 units number register.

- Gate address data (control word) specified by B-address of 1410 instruction into address register.

- Address register consists of access, module, track and random record registers.

- Access and module register select a module.

- Track and RR register determine which track is used.

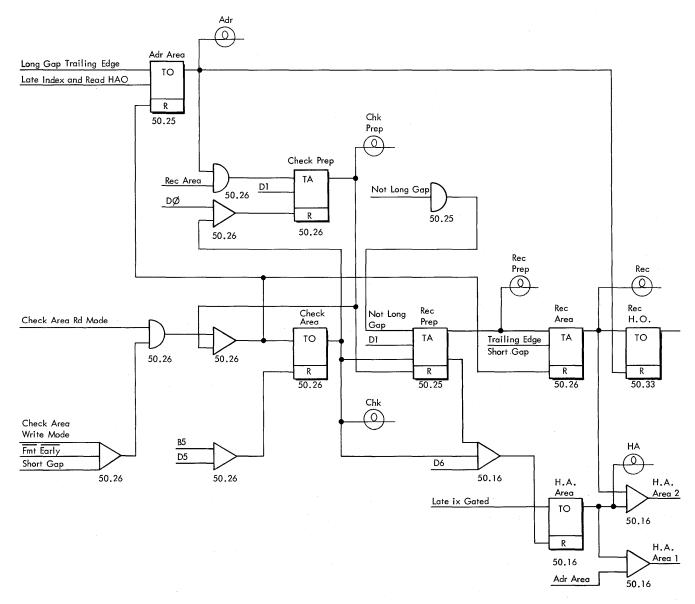

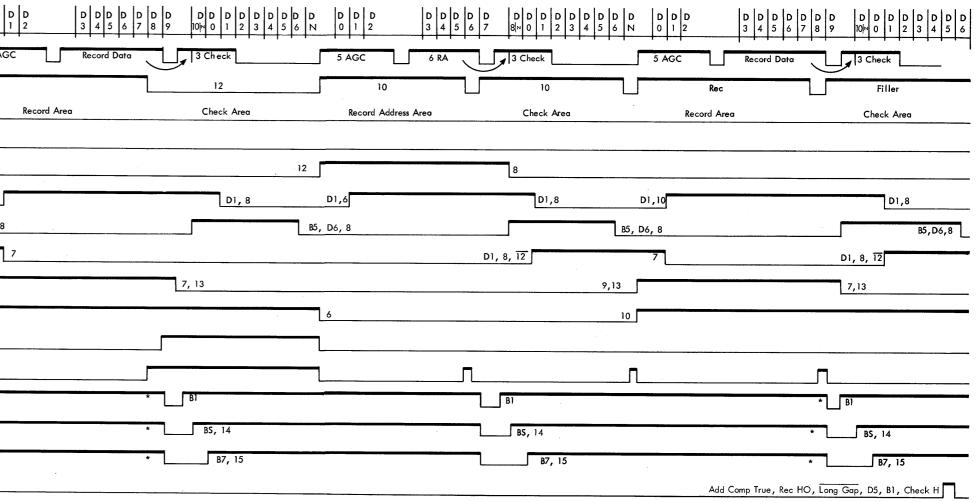

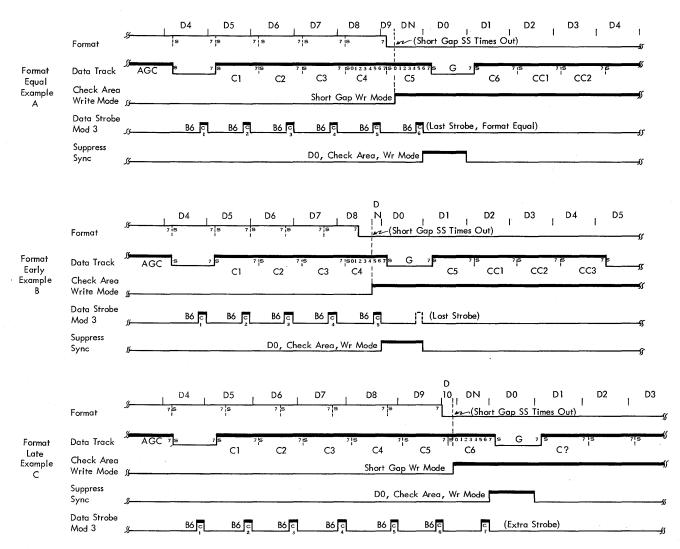

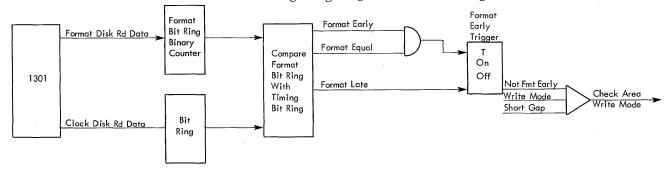

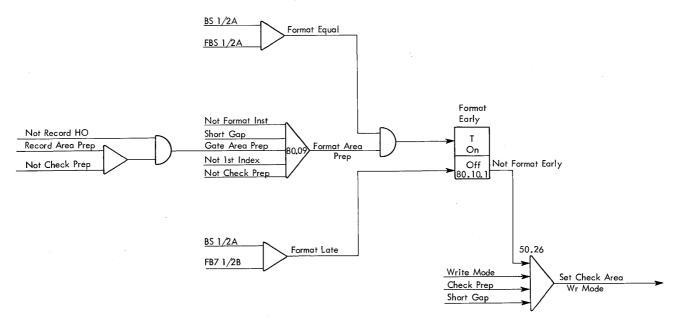

When the 1410 processes a 1301 file instruction it issues file operation to prepare the 7631 for receipt of control information, an operation code, and eight address characters. Receipt of file operation from the 1410 causes the 7631 to start the control cycle (Figure 15). Receipt of the 1410 file start gate causes the 7631 to decode the 1410 operation code. (The units number register output, the operation code, is available on the 1410 operation code bus; when the operation code is decoded the corresponding 7631 control operation trigger is set.) Figure 17 shows the 1410 instruction layout and relates operation codes to 7631 control operation triggers. Figure 16 (upper left corner) shows the 1410 operation decoder and operation register.