### SYSTEM/4 Pi

### MODEL TC

### TABLE OF CONTENTS

# PAGE

| FOREWORD                     | 1  |

|------------------------------|----|

| SUMMARY                      | 2  |

| DATA AND INSTRUCTION FORMATS | 2  |

| CHARACTERISTICS              | 3  |

| ADDRESSING                   | 4  |

| PROCESSOR ORGANIZATION       | 6  |

| MAIN STORAGE                 | 8  |

| INPUT/OUTPUT                 | 8  |

| COMPUTER PACKAGING           | 9  |

| SOFTWARE SUPPORT             | 10 |

| INSTRUCTION LIST             | 12 |

### FOREWORD

The IBM Federal Systems Division has developed a family of militarized, general purpose, digital computers called System/ 4 Pi. The name 4 Pi is derived from the number of steradians in a sphere, symbolizing the capability of these computers to address the entire spectrum of military applications.

The models in the System/4 Pi family currently under contract include:

| TC   | - Tactical Computer          |

|------|------------------------------|

| CP   | - Cost Performance           |

| CP-2 | - Cost Performance - Model 2 |

| EP   | - Extended Performance       |

These models satisfy the low-cost, limited processing requirements and expand upward to meet the requirements of the very largest data processing applications. Deliveries on all models begin in early 1967.

### MODEL TC

#### SUMMARY

The Model TC is a general purpose, stored program digital computer. It is designed for the low cost, medium range of computational performance. The hardware requirements are minimized by utilizing a byte (8 bits) data transfer format and efficient utilization of hardware registers to perform multifunctions.

The computer is subdivided into a memory, processor, and I/O section. All signals entering or leaving the computer are digital in nature. In the configuration presently being fabricated, the power is supplied from an external source.

The 2.5 microsecond, 8192 byte core memory has a parallel 8 bit transfer path to the processor section and operates within a basic 3 usec machine cycle. The computer has the capability to address 65K bytes of main store.

The processor is organized as a bus system design with an 8 bit fully parallel data flow. The processor contains the facilities for addressing main storage, for fetching or storing information, for arithmetic and logical processing of data, instruction sequencing, timing, and for initiating the communication between storage and external equipment.

Working registers are located both in hardware and memory. A total of 54 instructions are implemented. Processing rates on the order of 48,500 operations/second are attained by optimizing the machine organization, mono-lithic logic circuitry, and the high speed core memory.

A summary of Model TC characteristics is contained in Table 1.

### DATA AND INSTRUCTION FORMATS

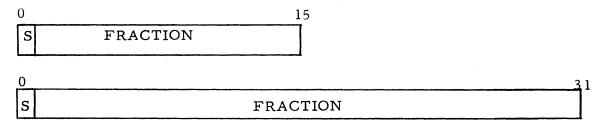

The TC computer transmits information between main storage and the processor in an 8 bit unit of information called a byte, the basic building block of all formats.

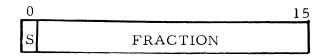

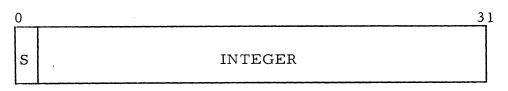

The basic arithmetic operand is the 16 bit fixed point binary word (sign + 15 bits) and is formed by two successive 8 bit memory words. There is no parity check of the memory byte. A four byte operand is used for double precision as well as products and dividends. Two byte operands must be located in main storage on

### SYSTEM/4 Pi MODEL TC CHARACTERISTICS

| ТҮІ          | PE                    | General Purpose                                                   | , Digital                                   |  |

|--------------|-----------------------|-------------------------------------------------------------------|---------------------------------------------|--|

| ORGANIZATION |                       | Byte parallel, fixed point, fractional, two's complement notation |                                             |  |

| INS          | TRUCTIONS             | 54                                                                |                                             |  |

| INS          | TRUCTION WORD         | 1, 2, or 3 bytes                                                  |                                             |  |

| DA           | TA WORD               | 16 or 32 bits                                                     |                                             |  |

| COI          | MPUTER CYCLE TIME     | 3 usec                                                            |                                             |  |

| STC          | DRAGE CYCLE           | 2.5 usec                                                          |                                             |  |

| ΤYI          | PICAL EXECTUION TIMES |                                                                   |                                             |  |

|              | ADD                   | Short Format<br>15 usec                                           | Long Format<br>18 usec (12 usec if<br>BR=0) |  |

|              | MULTIPLY              | 51 usec                                                           | 54 usec (48 usec if<br>BR=0)                |  |

|              | DIVIDE                | N/A                                                               | 54 usec (48 usec if<br>BR=0)                |  |

|              | OPERATIONS/SEC        | 48,500 typical                                                    |                                             |  |

| PH           | YSICAL                |                                                                   |                                             |  |

|              | SIZE                  | 9.75" x 17.12" x                                                  | 4" (. 37 cu. ft.)                           |  |

|              | WEIGHT                | 17.3 lbs.                                                         |                                             |  |

|              | MAIN STORAGE          | 8192 bytes (8 bits                                                | s) expandable to 65K bytes                  |  |

TTL Integrated Circuits

60 Watts

MIL-E-5400 Class 2

6,300 hours predicted.

TECHNOLOGY

ENVIRONMENT

POWER

MTBF

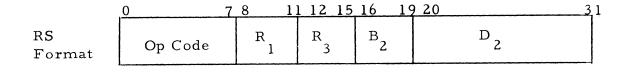

even byte boundaries. Four byte operands must be positioned so that the two least significant bits of the binary operand address are zero. Figure 1 shows the basic word formats used in the TC Computer.

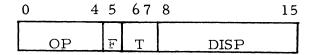

Three instruction word formats are used in the computer to provide ease of programming and to achieve good bit efficiency. These instruction formats are compatible with the 8 bit memory organization, being 8, 16, or 24 bits in length. All instructions of 16 or 24 bits in length cause a reference to main store. Some of the 8 bit instructions (e. g., SKIP ON CARRY, ZERO Q) make no reference to main store.

The short instruction format is utilized for the most common instructions, thereby minimizing the program memory size while the longer (16 bit) instructions provide greater flexibility and larger operand addressing. The 24 bit short format-immediate provides 16 bits of immediate data along with an 8 bit operation code and displacement field.

In each format, the first bit is a flag bit denoting a short or long instruction format. The short format also contains a three bit instruction code, and a four bit field which is used as either a displacement for operand addressing or to specify the number of shifts. Short format operand addressing is to a displacement of 16 syllables with respect to soft base Register 1 (operand fetching only).

The long format instruction consists of a flag bit to designate the long format, a five bit instruction code, a two bit base register field, and an 8 bit displacement field. This instruction requires two memory bytes. Operand addressing is to a displacement of 256 syllables with respect to one of three base registers. The displacement is a direct address to the first 256 syllables of memory (for most instructions) when the base register field equals zero.

### ADDRESSING

Byte locations in storage are consecutively numbered starting with 0; each number is considered the address of the corresponding byte. A group of bytes in storage is addressed by the left most byte of the group. The addressing capability permits a maximum of 65, 546 bytes, using a 16 bit binary address. The TC computer memory addressing hardware permits the addressing of 16, 384 bytes, although 8, 192 bytes are presently implemented. This set of main storage addresses includes some locations reserved for special purposes.

For addressing purposes, operands can be grouped in two classes: explicitly addressed operands in main storage and immediate operands placed as part of the instruction stream in main storage.

To permit the ready relocation of program segments and to provide for the flexible specifications of input, output, and working areas, all instructions referring to main storage have been given the capacity of employing a full address. The address used to refer to main storage is generated as follows:

-4-

### FIGURE 1

### WORD FORMATS

DATA

INSTRUCTIONS

-5-

Base Address (B) is a 16 bit number contained in a soft general register specified by the program in the B field of the instruction. The base address can be used as a means of static relocation of programs and data. The base address provides for addressing the entire main storage. A total of three base registers are located in main store and contain base addresses used in effective address generation. A special base register designated linkage register (L) is also used but only for branch type instructions.

Displacement (D) is a number contained in the instruction formats. It is included in every address computation. The displacement provides for relative addressing up to 256 syllables for long format instructions and 16 syllables for short format instructions.

In forming the address, the base address is treated as unsigned 16 bit positive binary integers. The displacement is similarly treated as a positive binary integer. The two are added as 16 bit binary numbers ignoring overflow after the displacement syllable address is converted into an effective byte address. Since every address includes a base, the sum is always 16 bits long although only 14 bits are implemented in the computer. The resulting address is the effective address of the left most operand byte.

#### PROCESSOR ORGANIZATION

The data flow in the processor section is via one of three data buses: the X Bus, the Y Bus, and the Main Eus. The X bus gates one of eight registers to the left side of the adder. The Y bus gates one of three registers to the right side of the adder. Output data from the adder is distributed to any one of seven registers via the main bus. Data inputs and outputs to and from the I/O are gated onto the main bus.

The 8 bit adder features the use of binary full adders packaged one bit per flatpack, thereby improving performance and cost packaging effectiveness. The adder executes all arithmetic and effective address update functions. In addition to the add function, the adder also has the capability to perform AND, OR, and exclusive OR functions.

The hardware registers of the processor section are also packaged very efficiently with two register bits contained in a flatpack without the need for external gating hardware. The following hardware registers are included in the design:

- 1. Accumulator (A) The 16 bit accumulator is the principal arithmetic register.

- Multiplier-Quotient Register (Q) The Q register is a 16 bit low order extension of the accumulator.

- 3. <u>Memory Buffer Register</u> (MBR) The MBR is an 8 bit register that receives the output from the memory.

- 4. Displacement Register (D) The D register is an 8 bit register that stores the address displacement. The TC computer possesses a displacement field of up to 256 syllables for long format instructions and up to 16 syllables for short format instructions. It is also used as a temporary storage register on various arithmetic operations.

- 5. Instruction Register (I) The instruction register is a 14 bit register that holds the address of the next sequential instruction.

- 6. Operation Register (O) The operation register is an 8 bit register used to store the instruction code.

- Memory Address Register (MAR) The Memory Address Register is a 14 bit register used to store and select the proper memory address. The two least significant bits are configured as a counter.

- Shift and Multiply Counter (S/M) The S/M counter is used to count iteration during shift, multiply, and divide instruction. The five bit counter allows for a maximum of 32 shifts in either direction.

- 9. <u>Status Register</u> (SR) The status register contains the wait state bit, the carry indicator, and the two interrupt masks.

The interruption system used in the TC computer permits a change in state of the computer in response to conditions external to the system. Two interrupts have been designed:

- Interrupt #0 Major priority for such interrupts as power off interrupt.

- Interrupt #1 Non-critical priority interrupts that can be interrogated by program control. An example of this is a real time clock interrupt.

An interrupt consists of storing the updated Instruction Counter (IC) and executing an automatic indirect branch. The IC is saved in a location permanently assigned to the interrupt.

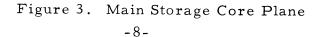

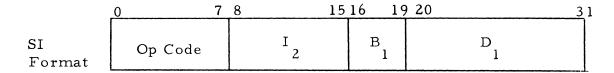

#### MAIN STORAGE

The TC computer utilizes an 8,192 word by 8 bit destructive readout core memory. The memory has a 2.5 microsecond read-write cycle time. Each cycle consists of a read followed by a write operation. The computer initiates a start memory every three microseconds. The access time of the memory is approximately .9 usec. A coincident current (3-D) selection scheme is utilized. The memory array requires four memory mats packaging two bits per mat. Operation is possible over the ambient temperature range of  $-55^{\circ}$ C to  $+100^{\circ}$ C.

The memory uses external data buffer (memory buffer) and memory address lines (14) sent from the processor section. The system is organized such that the "X" half select driver is clocked first since it drives the long dimension. The "Y" current thus has time to reach full amplitude at a slower rate, thereby reducing driver supply voltage requirements.

Timing is generated internally to the memory section. Address decoding is carried out by logic circuits internal to the memory section.

The monolithic circuits used in the memory are designed to "state-of-the-art" groundrules obtained from integrated circuit manufacturers. The high voltage, high current address driver and inhibit driver consist of monolithic pre-driver transformers coupled to discrete chip output stages packaged in flatpacks. The sense amplifier is a monolithic circuit with additional resistors added for threshold setting.

The storage element is an IBM 0.0137'' by 0.021'' by 0.0045'' (nominally 13/21) lithium nickel ferrite toroidal core that is designed to operate over a wide temperature range.

#### INPUT/OUTPUT

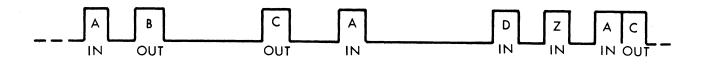

The Input/Output section of the TC computer performs the following functions:

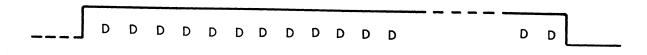

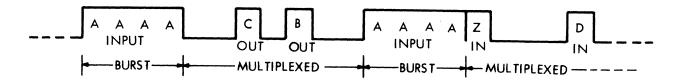

- Data Formatting The I/O section provides for a byte to serial data conversion to allow the processor to interface with other systems. The 8 bit main data bus is converted to a 1 mc serial readout of one syllable burst duration.

- Real Time Clock Generation A real time clock is located in the I/O section and is used to generate timed interrupts. The contents of the counter are periodically interrogated by the processor. Two low frequency clocks are also generated by the real time clock.

- 3. <u>Device Address Generation</u> The external device addresses are decoded in the I/O section.

- 4. Interrupt Control The buffer and control logic associated with interrupts is a part of the I/O section.

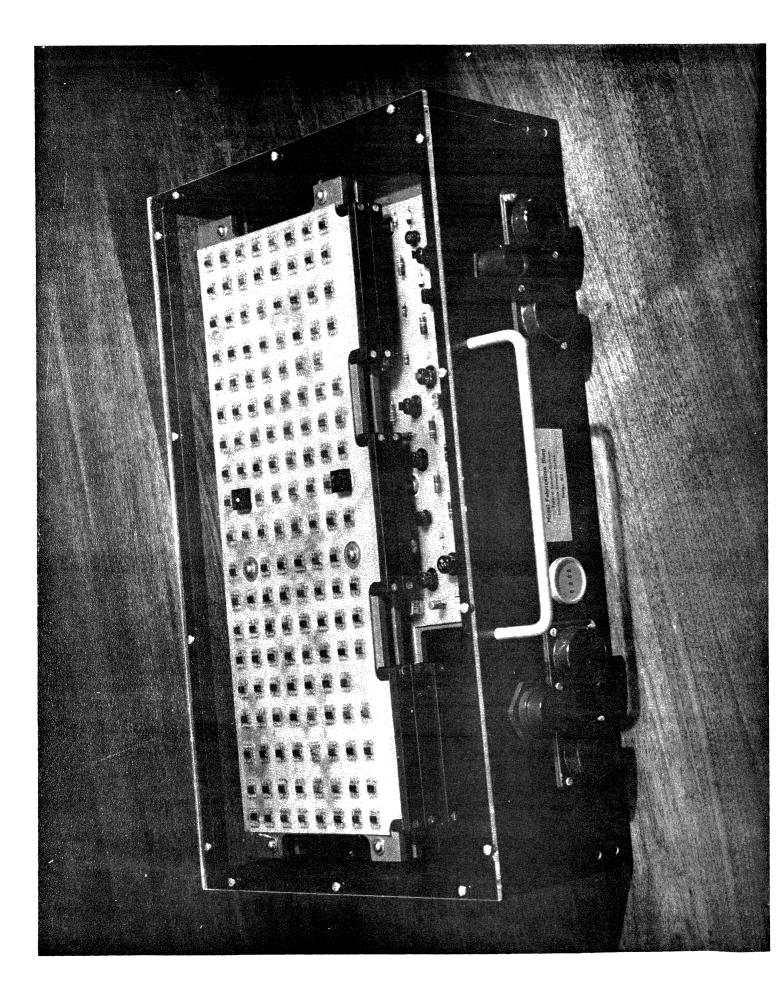

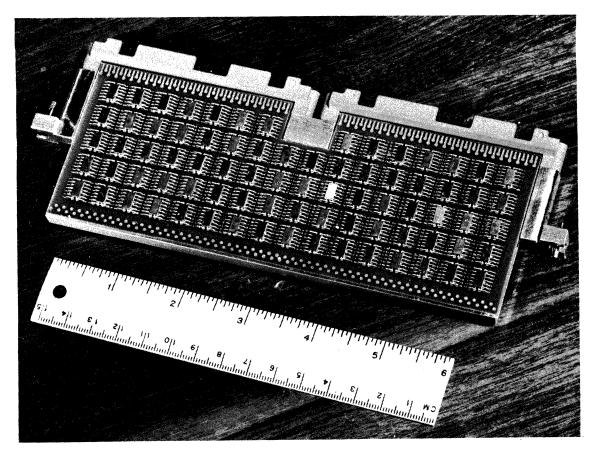

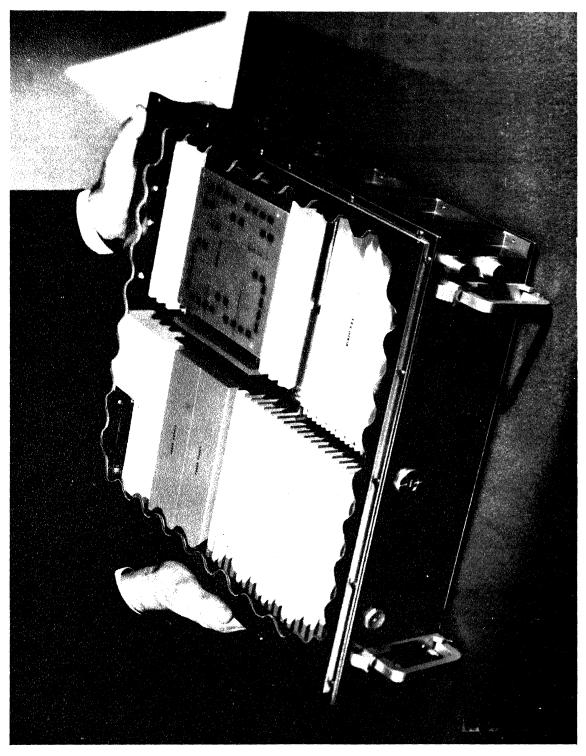

#### COMPUTER PACKAGING

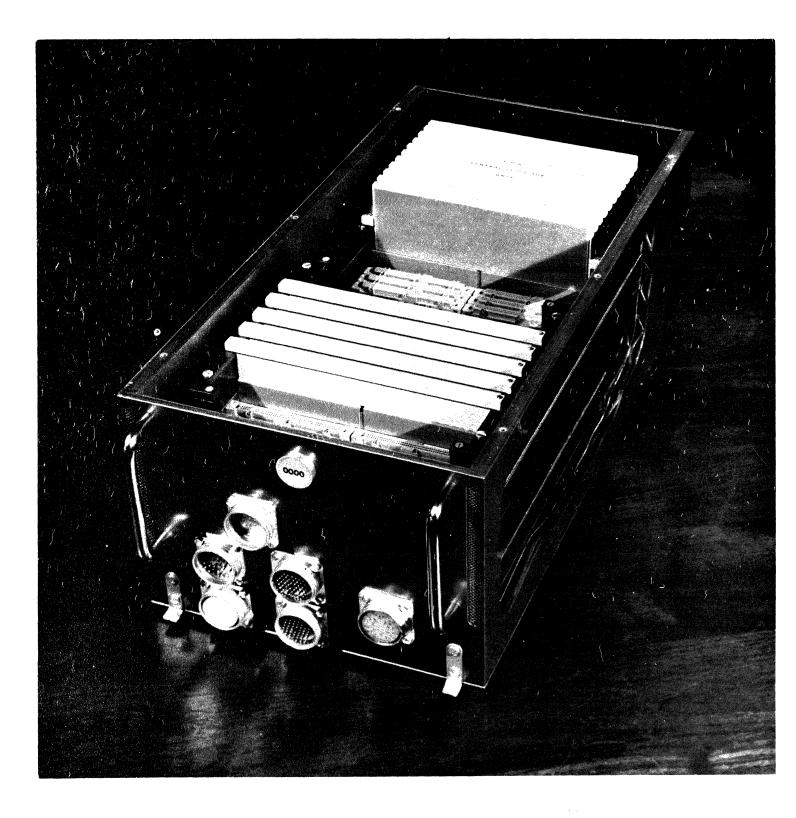

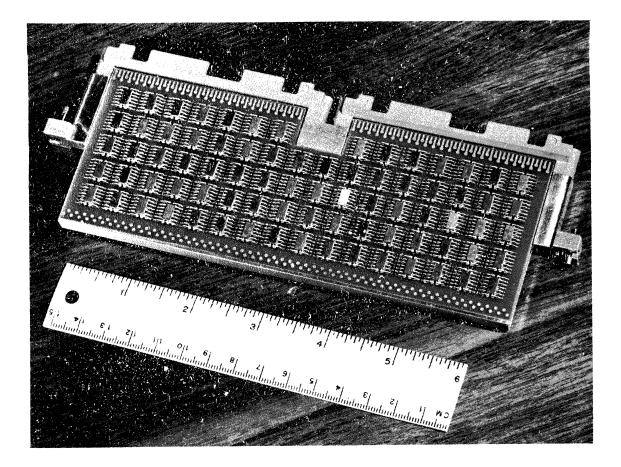

The TC computer is packaged in a ruggedized aluminum structure that contains three major subassemblies: Processor, Memory, and Input/Output and Wiring Harness. The structure has dimensions 9.75" x 17.12" x 4.0" and occupies. 37 cubic feet. The heat generated from the subassemblies is removed by an air cooled heat exchanger located in the bottom of the computer structure.

Electrical interfacing is accomplished with four input/output connectors (118 pins/connector) located on the front panel. AC and DC power is applied through separate connectors. Lightweight magnesium covers at the top and back of the unit facilitates removal of the subassemblies, provides radio frequency attenuation, and prevents entrance of foreign materials. The subassemblies are mounted at the bottom of the structure.

The computer is designed to meet the requirements of the MIL-E-5400 Class 2 specification. The three subassemblies are all of the same basic construction differing only in the type of electronic components that are mounted.

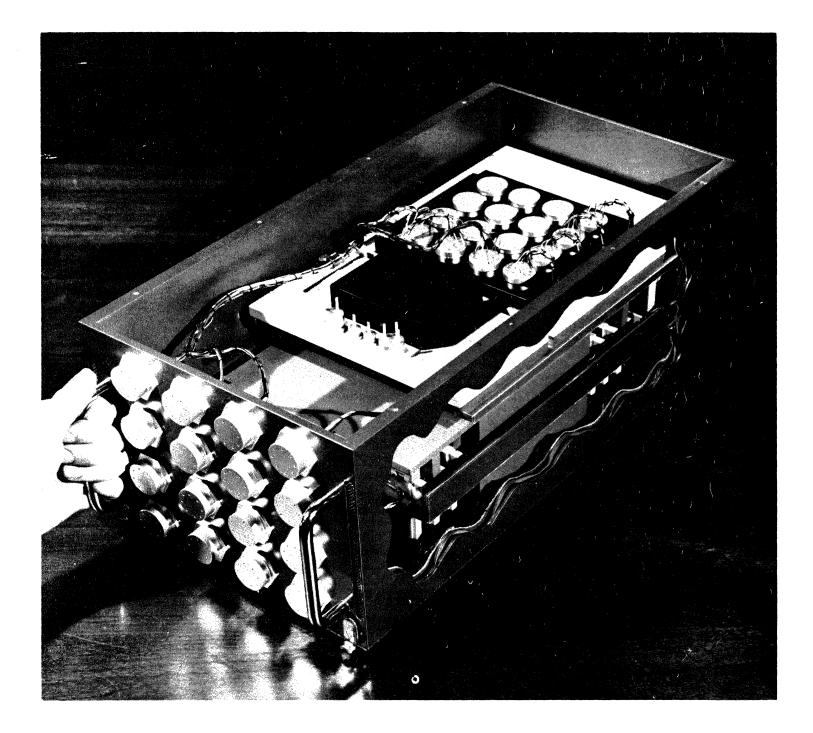

Each subassembly (page) normally consists of two rectangular shaped large SLT boards, a thermal mounting plate, the I/O connectors, and the circuit components.

The processor page contains all the logic circuitry for the computer as defined in previous sections. It consists of two SLT-type printed circuit boards on which transistor-transistor logic (TTL) integrated circuit flatpacks are soldered. These PC boards are sandwiched about a metal supporting structure which contains three 98 pin Saturn type connectors. An insulator separates each board from the supporting structure. Feedthroughs are provided to allow electrical connection between the two boards of the page. The SLT board contains two levels of signal wires and two internal ground-voltage planes.

The I/O page is identical in design to the CPU page except that due to less electronics only one SLT board and two Saturn connectors are provided.

-9-

The memory subassembly contains an 8,192 x 8 bit memory array and the necessary drive and sense circuitry packaged on two SLT boards with one Saturn connector for I/O communication.

The memory array consists of the following subdivisions:

- 4 memory planes

- 2 diode printed circuit boards

- 3 resistor termination boards

- 1 X line jumper board

The array subassembly is disconnectable from the memory page, thereby allowing flexibility in production and test.

### SOFTWARE SUPPORT

1

The support programming system provided with the Model TC will assist the problem programmer in the production of operational software for the computer by providing:

- Programming aids that will enable a program to be expressed in a language which is readily understood

- Facilities for storing, modifying, and accessing precoded programs

- A program checkout system to ensure operational program readiness

- Effective documentation manuals.

The assembler program and language will allow a programmer to make efficient use of all the features of the proposed computer while relieving him of the details of machine coding. The assembler will translate symbolic instructions into machine language instructions, assign storage locations, and perform auxiliary functions necessary to produce an executable machine language program.

Service programs will assist the programmer by providing routines for performing frequently used functions, including system tape generation and source program edit facilities. The service programs consist of a source program editor and a set of utility programs. The source program editor is designed to operate with the assembler and is, in fact, called by the assembler. The function of the editor is to update and alter existing source programs at the source statement level. The utility programs consist of the following:

- System job control program

- System tape maintenance programs

- Preparation program.

The system job control program provides for standard transition of control from one support program to another; for example, from assembler to dynamic program checkout system. This control is accomplished through user-supplied control cards specifying the processing programs desired.

The dynamic program checkout system (DPCS) will provide dynamic program analysis of the computer at the instruction word level of operation.

The DPCS will execute any given set of computer instructions as they appear on the symbolic output listing of the assembler. DPCS control will be exercised by user-provided programs written in a high level computer language (e.g. FORTRAN IV). These programs will call simulator subroutines which will manage the operation of the simulator. To aid in program debugging and checkout, the DPCS will provide a number of outputs concerning data flow, internal operation, and results of computations. These outputs will be generated by various trace and dump routines within the simulator.

The DPCS will provide an accurate simulation of the functional operation of the computer and associated input/output devices. Every mode of computer operation subject to program control will be exercised with DPCS, just as on the actual equipment. The DPCS will operate with the same arithmetic constraints as the actual computer; likewise, the DPCS will have the same program restrictions as the actual computer. The DPCS will aid in providing a near real-like situation to the simulated object program, and will greatly assist the problem programmers in debugging the operational programs.

A self-test routine to detect and isolate Model TC computer malfunctions is designed to be co-resident with the operational program. At periodic intervals the operational program transfers control to the self-test routine to begin a functional go/no-go indication. The routine is intended to exercise main working registers, data flow and controls, and instruction control logic. Failure of any active computer circuitry, as well as use of invalid data, will cause an error indication. The storage requirements of the self-test routine for Model TC are variable, depending on the degree of testing desired, and the interference allowable with the operational program.

#### INSTRUCTION LIST

A complete list of Model TC instructions and execution times is contained in Table 2.

### TABLE 2

### INSTRUCTION LIST

| OPERATION                     | FORMAT    | EXECUTION TIME |

|-------------------------------|-----------|----------------|

| ADD                           | Short     | 15             |

| ADD                           | Long      | 18*            |

| ADD                           | Immediate | 9              |

| ADD DOUBLE                    | Long      | 24*            |

| AND                           | Immediate | 9              |

| AND                           | Long      | 18*            |

| ARITHMETIC COMPLEMENT         | Short     | 3              |

| BRANCH                        | Immediate | 9              |

| BRANCH                        | Long      | 12             |

| BRANCH BACKWARD ON MINUS      | Long      | 6              |

| BRANCH BACKWARD ON PLUS       | Long      | 6              |

| BRANCH BACKWARD UNCONDITIONAL | Long      | 6              |

| BRANCH BACKWARD ON ZERO       | Long      | 6              |

| BRANCH FORWARD ON MINUS       | Long      | 6              |

| BRANCH FORWARD ON PLUS        | Long      | 6              |

| BRANCH FORWARD UNCONDITIONAL  | Long      | 6              |

| BRANCH FORWARD ON ZERO        | Long      | 6              |

| BRANCH INDIRECT               | Long      | 12             |

| BRANCH INDIRECT & STORE IC    | Long      | 18             |

| COMPARE                       | Immediate | 9              |

| COMPARE                       | Long      | 18*            |

| COMPARE DOUBLE                | Long      | 24*            |

| DIVIDE                        | Long      | 54*            |

| EXCHANGE A & Q                | Short     | 3              |

| EXCLUSIVE OR                  | Long      | 18*            |

| INPUT/OUTPUT CONTROL          | Long      | 24*            |

| LOAD A                        | Short     | 15             |

| LOAD A                        | Long      | 18*            |

| LOAD A                        | Immediate | 9              |

| LOAD BASE                     | Long      | 18             |

| LOAD BASE 1                   | Immediate | 15             |

| LOAD BASE 2                   | Immediate | 15             |

| LOAD BASE 3                   | Immediate | 15             |

| LOAD DOUBLE                   | Long      | 24*            |

| LOAD STATUS WORD              | Long      | 12             |

| MODIFY BASE                   | Long      | 18             |

| MULTIPLY                      | Short     | 51             |

| MULTIPLY                      | Long      | 54*            |

| NO OPERATION                  | Short     | 3              |

| OR                            | Long      | 18             |

| SHIFT LEFT DOUBLE             | Short     | 6-18           |

# TABLE 2

### (Cont.)

| OPERATION                     | FORMAT | EXECUTION TIME |

|-------------------------------|--------|----------------|

| SHIFT RIGHT ARITHMETIC DOUBLE | Short  | 6-18           |

| SKIP ON CARRY                 | Short  | 3              |

| STORE A                       | Short  | 15             |

| STORE A                       | Long   | 18*            |

| STORE BASE                    | Long   | 18             |

| STORE DOUBLE                  | Long   | 24*            |

| STORE IC                      | Long   | 18             |

| STORE STATUS WORD             | Long   | 12             |

| SUBTRACT                      | Short  | 15             |

| SUBTRACT                      | Long   | 18*            |

| SUBTRACT DOUBLE               | Long   | 24*            |

| TALLY                         | Long   | 12-24          |

| ZERO Q                        | Short  | 3              |

\*Execution Time is 6 usec Less if B=00.

.

### SYSTEM/4 Pi

### MODEL CP

SYSTEM/4 Pi MODEL CP PROCESSOR MOCKUP

# SYSTEM/4 Pi MODEL CP INTERFACE ADAPTER MOCKUP

### TABLE OF CONTENTS

### Page

| FOREWORD                     | 1  |

|------------------------------|----|

| SUMMARY                      | 2  |

| DATA AND INSTRUCTION FORMATS | 2  |

| CHARACTERISTICS              | 3  |

| ADDRESSING                   | 5  |

| PROCESSOR ORGANIZATION       | 5  |

| READ ONLY STORAGE            | 7  |

| MAIN STORAGE                 | 8  |

| INPUT/OUTPUT                 | 9  |

| COMPUTER PACKAGING           | 10 |

| SOFTWARE SUPPORT             | 12 |

| INSTRUCTION LIST             | 15 |

### FOREWORD

The IBM Federal Systems Division has developed a family of militarized, general purpose, digital computers called System/ 4 Pi. The name 4 Pi is derived from the number of steradians in a sphere, symbolizing the capability of these computers to address the entire spectrum of military applications.

The models in the System/4 Pi family currently under contract include:

| ΤС   | - | Tactical Computer          |

|------|---|----------------------------|

| СР   | - | Cost Performance           |

| CP-2 | - | Cost Performance - Model 2 |

| ΕP   | - | Extended Performance       |

These models satisfy the low-cost, limited processing requirements and expand upward to meet the requirements of the very largest data processing applications. Deliveries on all models begin in early 1967.

#### MODEL CP

#### SUMMARY

IBM System/4 Pi Model CP (Cost Performance) is a general purpose, single address, fixed point, digital computer. The ruggedized design and flexible logic organization provide the Model CP with the capability to operate in aircraft, aerospace, ground-based, and shipboard environments.

The Model CP is comprised of a Central Processing Unit (CPU), Main Storage (MS), Read Only Storage (ROS), Interface Adapter, and Power Supply. In the configuration currently being fabricated, the units are packaged in two separate cases.

The 2.5 microsecond main memory has a 36 bit parallel data transfer to the CPU. The data flow within the CPU is 16 bits in parallel.

The unique feature of the Model CP is the control section of the CPU. Each instruction available to the programmer is implemented as a short subroutine of "microinstructions" read from ROS. The movement of data between hardware registers and main storage, and between the registers and I/O hardware, is entirely under control of these micro-commands. The flexibility provided by this novel design feature permits adding application oriented instructions and microprogramming highly repetitive routines for increased speed and efficient performance without hardware redesign.

A summary of Model CP characteristics is contained in Table 1.

#### DATA AND INSTRUCTION FORMATS

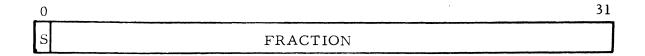

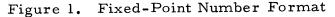

The Model CP is implemented with a standard 32 bit data word. A 16 bit halfword can also be utilized when the accuracy afforded by a full word is not required (See Figure 1).

#### Figure 1. Halfword and Fullword Data Formats

Positive numbers are always in true binary form. Negative numbers are in two's complement form. The sign bit (position 0) is always 0 for positive numbers and 1 for negative numbers.

### SYSTEM/4 Pi MODEL CP CHARACTERISTICS

| TYPE                    | General Purpose, Digital                                     |

|-------------------------|--------------------------------------------------------------|

| ORGANIZATION            | Parallel, fixed point, fractional, two's complement notation |

| INSTRUCTIONS            | 36                                                           |

| INSTRUCTION WORD        | 16 or 32 bits                                                |

| DATA WORD               | 16 or 32 bits                                                |

| COMPUTER CYCLE TIME     | 417 nsec.                                                    |

| STORAGE CYCLE           | 2.5 usec                                                     |

| TYPICAL EXECUTION TIMES |                                                              |

| ADD                     | 5.0 usec                                                     |

| MULTIPLY                | 29.58 usec                                                   |

| DIVIDE                  | 45.42 usec                                                   |

| OPERATIONS/SECOND       | 91,000*                                                      |

| PHYSICAL                |                                                              |

| SIZE                    | 9.97" x 7.38" x 19.40" (.82 cu ft.each case)                 |

| WEIGHT                  | 80 lbs. (Total)                                              |

| MAIN STORAGE            | 8192 - 36 bit words expandable to 32,768 words               |

| TECHNOLOGY              | TTL Integrated Circuits                                      |

| POWER                   | 350 Watts                                                    |

| ENVIRONMENT             | MIL-E-5400, Class 2                                          |

| MTBF                    | 2,500 hours predicted                                        |

\*Reference value only, higher speeds possible with application oriented microprograms.

The instruction words in Model CP are 16 or 32 bits long (See Figure 2).

| 0 |    | 4 5            | 56  | 5 7 | 8   |      | 15 | 5       |

|---|----|----------------|-----|-----|-----|------|----|---------|

|   | OP |                | F   | Т   |     | DISP |    | ]       |

| 0 |    |                | _ / | -   |     | 1.0  |    | -       |

|   |    | $\frac{4}{-1}$ | 2 6 |     | 89  | 10   | 15 | 16      |

|   | OP |                | F / | т   | I N | COND |    | ADDRESS |

Figure 2. Instruction Formats

31

The bits within the instruction words are used as follows:

- OP These five bits define which operation is to be performed.

- F This format bit controls the instruction format. A "zero" indicates a halfword instruction and a "one" indicates a fullword instruction.

- T These two Index Tag bits address the Index Register or Instruction Register used in the address modification.

- DISP These eight bits are called the displacement (halfword format only) and are added to the Instruction Register or the Index Register specified by T to define the effective address (EA). If T is 00, the displacement is added to the Instruction Register. The displacement is in two's complement form if negative, the sign being in bit 8. The bit in position 8 is automatically extended to the higher ordered bits (0-7) when the displacement is added to an Index Register.

- I This is an indirect bit in the two word instruction format. If "zero", addressing will be direct. If a "one", addressing will be indirect.

- IN This bit is used to specify that the Branch or Skip on Condition (BSC) instruction is to be interpreted as a "Branch Out" of an interrupt routine.

- COND Specifies the condition indicators to be interrogated on a BSC or BSI instruction.

- ADDRESS These 16 bits contain the address in a full word instruction. It can be modified by the contents of an index register or is an indirect address.

#### ADDRESSING

All core storage locations are directly addressable under program control. The effective address may be determined by examining the tag, flag and indirect address bits shown in Figure 2. The effective address is formed as shown in Table 2.

### TABLE 2

#### **EFFECTIVE ADDRESS**

| F = 0<br>(Direct Addressing)                                                         | F = 1, IA = 0<br>(Direct Addressing)                                 | F = 1, IA = 1<br>(Indirect Addressing) |  |  |  |

|--------------------------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------|--|--|--|

| $T = 00 EA = I^{1} \neq DISP^{2}$                                                    | $\mathbf{E}\mathbf{A} = \mathbf{A}\mathbf{d}\mathbf{d}\mathbf{ress}$ | $EA = C^3$ (Address)                   |  |  |  |

| T = 01 EA = $XR1 \neq DISP$ EA = Address $\neq XR1$ EA = C (Address $\neq XR1$       |                                                                      |                                        |  |  |  |

| $T = 10 EA = XR2 \neq DISP$                                                          | $\vec{EA} = C (Address \neq XR2)$                                    |                                        |  |  |  |

| T = 11 EA = XR3 $\neq$ DISP EA = Address $\neq$ XR3 EA = C (Address $\neq$ X         |                                                                      |                                        |  |  |  |

| 1 - Contents of instruction count register or index register                         |                                                                      |                                        |  |  |  |

| 2 - May be true positive quantity or negative 2's complement quantity (-128 to +127) |                                                                      |                                        |  |  |  |

| 3 - C specifies '' contents'' at location specifed by address of address $ eq$       |                                                                      |                                        |  |  |  |

XR1, XR2, or XR3

The recognition in the instruction of an indirect Address Control bit will cause the address portion to be treated as an indirect address. The address, after indexing (if specified), gives the location of the effective address. An additional memory cycle is required.

### PROCESSOR ORGANIZATION

The CPU is a single address, fixed point, two's complement, fractional arithmetic system. It consists of the basic timing, register organization, arithmetic-logic unit, I/O interface and interrupt interface.

The Model CP Data Flow contains ten 16-bit storage registers, one 18-bit buffer register, one 16-bit storage address register, one 17-bit adder, a bus system, and associated gates and controls. The data flow of the central processor is 16 bits wide. Data flow is organized around a twoclock system. A two-clock cycle is approximately 417 nanoseconds. Timing is generated from a frequency source internal to the CPU.

The computer is comprised of three main buses - the left adder bus, the right adder bus, and the buffer bus. The left adder bus will gate any one

of eight storage registers to the left side of the adder; and the right adder bus controls which storage register is gated into the right side of the adder. Output data from the adder is distributed to any of the ten storage registers via the buffer register bus (BFR). Data inputs to the central processor are gated from the I/O onto the BFR bus. Output data is read into the I/O from this same bus. Data to and from AGE equipment is also taken from this bus.

The major portion of the data flow consists of the ten storage registers. All of these are provided with appropriate circuitry to enable any register to have access to the bus system. These registers are general purpose and can be used as necessary for any function.

In the configuration currently being fabricated, the ten primary storage registers are assigned as follows:

| B <sub>1</sub><br>B <sub>2</sub>          | Operand Buffer Register               | 16 bits<br>16 bits |

|-------------------------------------------|---------------------------------------|--------------------|

| L<br>G                                    | Mask Register<br>Instruction Register | l6 bits<br>16 bits |

| A <sub>1</sub><br>A <sub>2</sub>          | Accumulator                           | 16 bits<br>16 bits |

| $\begin{array}{c} Q_1 \\ Q_2 \end{array}$ | M-Q Register                          | 16 bits<br>16 bits |

| PC<br>ST A                                | Program Counter<br>I Status Register  | l6 bits<br>16 bits |

The STAT register has the additional capability of recording machine status and controlling the ROS sequencing. Additional gating is provided for the STAT register to enable unique combinations of bits to be read for control and arithmetic operations. Three Index Registers (XR) are provided, two in storage and one in high-speed circuitry.

In addition to the previously described registers, the following registers are also used by the computer.

| SAR | Storage Address Register       | 16 bits |

|-----|--------------------------------|---------|

| SDR | Storage Data Register          | 36 bits |

| BFR | Buffer (Adder output register, | 18 bits |

|     | common second rank register)   |         |

### READ ONLY STORAGE

The processor is controlled by a permanently recorded microprogram which is stored in a read only store (ROS) and is supplemented by conventional control logic. Each time the ROS is addressed, a microinstruction is read. When decoded, the microinstruction controls the routing of data in the CPU and provides means of selecting the next microinstruction.

To understand the operation of ROS, it is helpful to note its relationship to conventional controls. Conventional controls may be characterized by sequence triggers and by the control lines activated by the sequence triggers as a function of the operation to be performed and data conditions. Each cycle that the CPU may take represents a state of the CPU as defined by the control circuitry. Each state, in turn, specifies which control lines are to be activated during that cycle and which state is to follow next. The defined state will cause the next sequence trigger to be set in the following cycle. In some cases the next state may be contingent upon a branch condition in which one of two or more sequence triggers must be selected.

In ROS-controlled processors, the sequence triggers are replaced by microinstructions or ROS words. Each ROS word consists of a predetermined bit pattern and represents a state of the CPU. The addressed ROS word controls the CPU during the particular machine cycle in use. When decoded, the ROS word defines all control lines that are to be activated during the machine cycle. Also contained in the ROS word is the address of the next ROS word to be used. If the address of the next ROS word is dependent on data conditions (for example, branch if overflow occurs), a base address and the conditions to be tested (branch test) are specified in the ROS word. In this case, one ROS word is associated with each of the possible data conditions; the ROS word whose associated conditions are satisfied is the next to be addressed. Thus, ROS eliminates the need for most of the complex sequencing networks.

Each ROS word consists of unique predetermined bit configuration grouped into control fields. The number of bits within a field determines the number of unique control signals (micro-orders) available within that field. (In a 4-bit field, for example, 16 distinct micro-orders can be defined, only one of which can be activated at any one time.) The micro-orders are grouped functionally within the fields according to two rules:

- All micro-orders grouped in a field must be mutually exclusive since only one micro-order within that field may be specified at a time.

- 2. Micro-orders that are functionally similar (such as micro-orders that control outgating to the adder right input bus) are grouped in one field for ease of decoding.

Usually, rule 1 results in rule 2.

When decoded, each micro-order activates one or more control lines that condition logic gates to perform the function specified by the micro-order. Each micro-order is assigned a mnemonic code that defines the control function performed.

### MAIN STORAGE

The MS is a three-dimensional coincident current 8, 192-word, (standard) 36-bit ferrite core array. Thirty-two bits contain data, two bits are allocated to parity, and two bits are used for storage protection. Access time for this system is approximately 0.9 usec., and it can operate continuously at a 2.5 usec. cycle. Core storage addresses begin at 0000 and end at 8, 191. Storage wrap around exists; i. e., the next sequential address above the highest numbered address is always 0000.

A storage protection capability has been implemented through the use of storage protection tests in every instruction which modifies storage. Each 36-bit storage word contains two storage protection bits; one for each halfword. These bits differentiate between protected and scratch pad locations, and are assigned when core storage is loaded to prevent inadvertent modification of the data by the program. Any attempt to store data in a protected location will be prevented by an Invalid Address interrupt in ROS control.

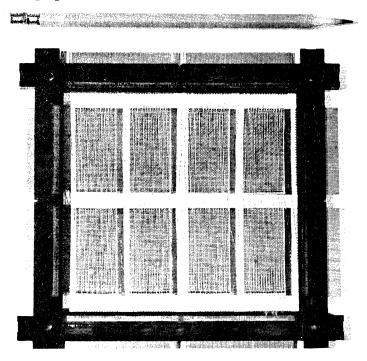

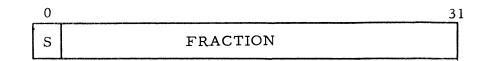

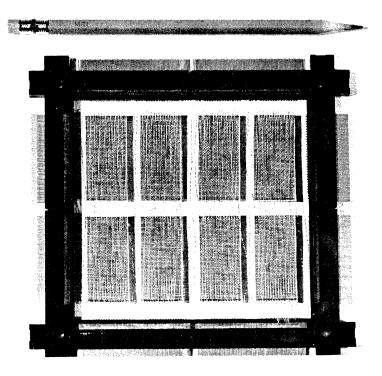

The main storage core plane (Figure 3) used in Model CP is a militarized version of a commercial IBM plane. The wiring is done by machine on high volume production equipment.

### INPUT/OUTPUT

The Interface Adapter assembly, included as part of Model CP, contains the necessary buffering and interface circuits to handle the following I/O channels:

- 3 high-speed, parallel, input channels

- 1 high-speed, parallel, output channel

- l serial output channel

- 24 discrete inputs

- 144 discrete outputs

- 24 interrupt lines

Table 3 includes the characteristics of the Interface Adapter.

| Type<br>Modes of Operation:          | Parallel and serial operation<br>Multiplex (interleave mode)<br>Multiplex (block transfer mode) |  |

|--------------------------------------|-------------------------------------------------------------------------------------------------|--|

|                                      | Direct I/O<br>Synchronous servicing of interface<br>adapter channels                            |  |

| Transfer rate:<br>Parallel<br>Serial | 260,000 words/sec (Burst Mode)<br>200 KC bit rate                                               |  |

# TABLE 3INTERFACE ADAPTER CHARACTERISTICS

Three fully buffered parallel input channels are provided. Each channel is capable of transferring a data word equal in length to the memory word size (32 bits plus check bits). Each channel consists of a data buffer register, an address register, and a count register. In addition, each channel shares the use of common circuitry consisting of the incrementer, control unit, and drivers.

A parallel output channel is provided for high speed block transfers to an external device. The output channel is functionally identical to a parallel input channel except that data is read from storage and placed in the buffer whenever a strobe pulse is received from the external device. A maximum burst rate of 260,000 words per second is provided. Provision is made for optionally adding two more parallel output channels.

A serial output channel is provided for transmission to an external device of serial data at a 200-kc bit rate. A 32-bit plus parity shifting register, loaded in the same manner as the parallel output channel, is provided. The output is fully buffered and converts data to the return to zero form. A shift clock is provided, the leading edge delayed from the leading edge of the data by 1/4 of the shift clock period. The parity of the serial output message is checked. Twenty-four discrete inputs are sampled in the interface adapter. The input signal logic levels will be compatible with the interface adapter logic circuit. One hundred forty - four discrete outputs are provided. Each discrete output is latched, and a TTL gate is provided to drive the interface line, thereby isolating the latch from the capacitive load of the line.

Twenty-four external interrupt lines are provided with four levels of priority provided. The system consists of the mask register, the demand registers, and the priority resolution network. Demands which arise from external sources set individual latches in the demand registers. The outputs from groups of these latches are combined into four different priority levels. The status of the demands at each level is forwarded to the priority resolution network.

This network compares the demands to the status of the mask register. If the current demands are of higher level than that of the mask register, a 2 bit code is generated and sent to the computer to indicate the existence of an interrupt and its level.

The demand register will record all interrupt signals which are sent to it. The status of the demand registers may be read into the computer for inspection by the program.

The demand registers retain information until it is revised under program control. If the program revises the setting of the mask register to a lower level, interrupts which had previously been masked off may be revealed and will immediately generate signals which are sent to the computer. A special command will permit general resetting of all demand registers.

The interrupt system has been configured to allow considerable flexibility for the programmer. In general, once the basic systems decisions are made, large parts of the routines associated with the handling of interrupts are either microcoded or put into monitor programs where, in either case, the operational programmer does not handle the details of interruption but merely refers to the standard routines.

### COMPUTER PACKAGING

The Model CP is packaged in two cases. The contents of each case are as follows:

Computer Case

Interface Adapter Case

Central Processing Unit Read Only Storage Power Supply Main Storage Interface Adapter Power Regulator RFI Filter The cases are dip-brazed aluminum structures which conform to standardized ATR case dimensions. Heat generated from the subassemblies within each unit is conducted to the side walls of the structure. These walls consist of a hollow rectangular extrusion which forms a passage for the cooling air. Thin corrugated sheeting is brazed within this passage to provide the necessary surface area for forced air convection cooling and to rigidize the structure. The cooling air enters the passage on the rear panel and exits at the front panel.

Electrical interfacing between units is accomplished with input-output connectors located on the front panels. Lightweight covers at the top and bottom of the units facilitate removal of subassemblies, provide radio frequency attenuation, and prevent entrance of foreign materials. The units are mounted to the vehicle structure at the bottom edges of the front and rear panels.

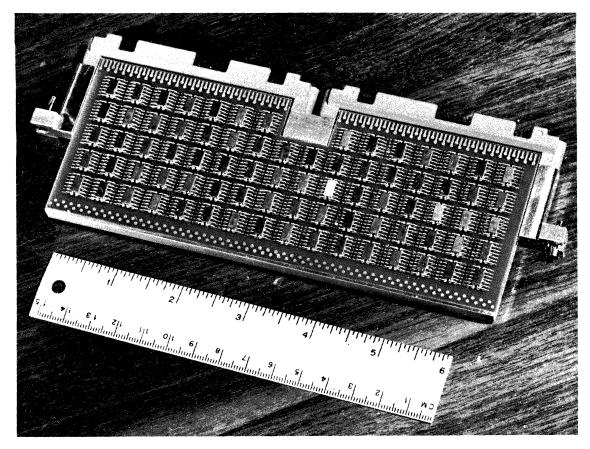

The electronics for Model CP is implemented with integrated circuits mounted on pluggable electronic subassemblies called pages (Figure 4). A page consists of two multilayer interconnection boards (MIBS) bonded to a metal frame. An insulator separates each board from the frame. Two 98-pin connectors,

Figure 4. Typical Integrated Circuit Subassembly

developed for the Saturn V Guidance Computer subassembly, are fastened along the lower edge of the frame. The connector was developed for this application and has demonstrated its performance and reliability in extensive tests and field service. It has been qualified for use in man-rated space vehicles. Feedthrough connections and test points are provided along the upper edge of the frame. The page is fastened to the supporting structure at the two mounting flanges along an axis through the page center of gravity. Additional support is provided by the connectors. The page will be cooled by thermal conduction through the frame and mounting flange thermal interface. Keyed guide pins project from the lower edge of the page to prevent mislocation during installation. A tool is furnished for page insertion and withdrawal. Guides will be provided to facilitate handling during page insertion and withdrawal.

The integrated circuit flatpacks are soldered to etched patterns on the surface of the multilayer printed circuit boards. These multilayer boards allow the flatpacks to be closely spaced. Figure 4 shows one side of a typical page with flatpacks mounted. Each page contains two multilayer boards with up to 78 flatpacks per board. Discrete components are soldered in plated holes or on the board surface depending on terminal configuration. A conformal coating is applied for component support and environmental protection.

The main storage array is fabricated from core planes which are a militarized version of planes used on the IBM System/360. Each plane has 16, 384 cores. Planes are conformally coated and foam padding is placed between planes for environmental protection of cores.

The array is mounted in a housing which serves also to mount pluggable electronic subassemblies and acts as a thermal path. Pluggable electronic subassemblies similar to those in the central computer are used to mount the memory circuits. A distribution multilayer printed circuit board is used to interconnect memory circuits and the array. The main memory assembly is removable as a module. Electrical connections to the assembly are made through pluggable input-output connectors.

The Interface Adapter section is constructed using the pluggable electronic subassemblies with some utilization of discrete components because of the nature of the circuits.

Read Only Storage is implemented with a microminiature linear ferrite 7/12 (ID/OD in mils) magnetic core. The basic core plane contains 512 by 70 cores. A core is located where a "1" bit is stored and a core is missing where a "0" bit is stored. Two wires thread each core: one drive winding and one sense winding. Two planes are required for the ROS. Monolithic circuits are used in the decode, driver, detector and latch portion of the ROS.

### SOFTWARE SUPPORT

A sophisticated package of computer programs will be provided for operation on

an IBM System/360. In addition, assemblers will be delivered which will operate on System/360 and the Model CP. This support package will assist the programmer in producing operational programs for the Model CP by providing:

- Programming aids that will enable a program to be expressed in a language which is readily understood

- Facilities for storing, modifying, and assessing precoded programs

- A program checkout system to ensure central computer operational program readiness

The software support programs delivered with the Model CP are the following:

- The assemblers will assemble programs executable on the Model CP. Programs will translate symbolic instructions into machine language instruction, assign storage locations, and perform auxiliary functions which allow the programmer to make efficient use of all of the features of the Model CP while relieving him of the details of machine language coding. This program provides for:

- The assembly of relocatable object programs

- Linkage between programs assembled at different times

- Various listings under programmer control

- A significant amount of error detection

- An assemble-and-run capability when operating with the dynamic program checkout system described below

- Automatic selection of long and short format instructions

- Macro processing

- Service Programs which assist the programmer by performing frequently used functions such as:

- Combining and relocating programs assembled at separate times

- Handling the transition from assembly to execute as described above

- Maintaining the library tape

- A dynamic program checkout system (simulator) which will provide for dynamic program analysis of the Model CP at the instruction word level of operation. This program will execute any instructions and aid in program debugging by providing:

- Simulator control through a user's FORTRAN IV program

- User program access to simulated Model CP object program computed data

- Object program correction

- Program debugging options such as dumps, snaps, and traces

- Input/output and interrupt initiation and response

The test programs supplement the processor detection circuitry to provide a comprehensive self-check. The self-check capability is used to provide three separate functions in Model CP: error detection, fault isolation, and verification of operational readiness when required.

The methods used in the operational test program are a combination of special ROS diagnostic words (micro-instructions) and programmed routines (macro instructions) contained in the main storage section. It is a resident program within the problem program and its prime purpose is to isolate to the replaceable assembly by verifying the operations of the following:

- ROS addressing

- ROS decoding

- Instruction operation and flow through the Instruction execution micro-orders

- Processor data flow

- Register, adder, and shifter functions

- Channel data transfer where possible in the operational environment

- Interrupt feature where possible under the operational confines

- Limited main storage addressing

- Limited main storage data transfer

It is designed such that it may be entered without any special initialization and can be interrupted at any time to return to the problem program.

In addition to this, conventional program routines, located in main storage, will be cycled to insure proper Instruction operation and that all paths through the instruction execution micro-order sets have been exercised.

### INSTRUCTION LIST

A complete list of Model CP instructions and execution times is contained in Table 4.

### TABLE 4

### INSTRUCTION LIST

### TYPICAL EXECUTION TIMES (USEC)

| OPERATION                     | SHORT FORMAT | LONG FORMAT |

|-------------------------------|--------------|-------------|

| ADD                           | 5.00         | 5.00        |

| ADD HALFWORD                  | 5.00         | 5.00        |

| AND                           | 5.00         | 5.00        |

| BRANCH ON CONDITION           | N/A          | 4.58        |

| BRANCH OUT ON CONDITION       | N/A          | 3.75        |

| BRANCH AND STORE INST. CTR.   | 5.83         | 8.75        |

| COMPARE                       | 5.00         | 5.00        |

| COMPARE HALFWORD              | 5.00         | 5.00        |

| DIRECT INPUT OUTPUT CONTROL   | 9.17         | 9.17        |

| DIVIDE                        | 45.42        | 45.42       |

| EXCLUSIVE OR                  | 5.00         | 5.00        |

| INSERT STORAGE PROTECT BIT    |              | 6.66        |

| LOAD A                        | 5.00         | 5.00        |

| LOAD A HALFWORD               | 5.00         | 5.00        |

| LOAD INDEX                    | 2.92         | 3.33        |

| LOAD Q                        | 5.00         | 5.00        |

| MODIFY INDEX                  | 5.00         | 5.00        |

| MODIFY STORAGE HALFWORD       | N/A          | 6.25        |

| MULTIPLY                      | 29.58        | 29.58       |

| OR                            | 5.00         | 5.00        |

| SHIFT LEFT                    | VARIES       | N/A         |

| SHIFT LEFT AND COUNT          | VARIES       | N/A         |

| SHIFT LEFT AND COUNT DOUBLE   | VARIES       | N/A         |

| SHIFT LEFT DOUBLE             | VARIES       | N/A         |

| SHIFT RIGHT ARITHMETIC        | VARIES       | N/A         |

| SHIFT RIGHT ARITHMETIC DOUBLE | VARIES       | N/A         |

| SHIFT RIGHT LOGICAL           | VARIES       | N/A         |

| SHIFT RIGHT ROTATE DOUBLE     | VARIES       | N/A         |

| SKIP ON CONDITION             | 4.58         | N/A         |

| STORE A                       | 5.83         | 5.83        |

| STORE A HALFWORD              | 5.42         | 5.42        |

| STORE INDEX                   | 6.25         | 6.25        |

| STORE Q                       | 5.83         | 5.83        |

| SUBTRACT                      | 5.00         | 5.00        |

| SUBTRACT HALFWORD             | 5.00         | 5.00        |

|                               |              |             |

# SYSTEM/4 Pi

# MODEL CP-2

SYSTEM/4 Pi MODEL CP-2 DIGITAL COMPUTER MOCKUP

# TABLE OF CONTENTS

|                              | PAGE |

|------------------------------|------|

| FOREWORD                     | 1    |

| SUMMARY                      | 2    |

| DATA AND INSTRUCTION FORMATS | 2    |

| CHARACTERISTICS              | 3    |

| ADDRESSING                   | 5    |

| PROCESSOR ORGANIZATION       | 6    |

| MAIN STORAGE                 | 7    |

| INPUT/OUTPUT                 | 8    |

| COMPUTER PACKAGING           | 9    |

| SOFTWARE SUPPORT             | 11   |

| INSTRUCTION LIST             | 12   |

## FOREWORD

The IBM Federal Systems Division has developed a family of militarized, general purpose, digital computers called System/ 4 Pi. The name 4 Pi is derived from the number of steradians in a sphere, symbolizing the capability of these computers to address the entire spectrum of military applications.

The models in the System/4 Pi family currently under contract include:

| TC -   | - | Tactical Computer          |

|--------|---|----------------------------|

| CP -   | - | Cost Performance           |

| CP-2 - | - | Cost Performance - Model 2 |

| EP -   | - | Extended Performance       |

These models satisfy the low-cost, limited processing requirements and expand upward to meet the requirements of the very largest data processing applications. Deliveries on all models begin in early 1967.

## MODEL CP-2

#### SUMMARY

The Model CP-2 is a general purpose, stored program, digital computer. It is designed for real-time control applications such as navigation, guidance, or weapons delivery.

Major subsections of the computer are storage, processor, and I/O section. All signals entering or leaving the computer are digital in nature. In the configuration presently being fabricated, a power supply is included within the processor structure.

The 2.5 microsecond, 8,448 word core storage has a parallel 36 bit transfer path to the processor section. Two parity bits and two storage protect bits insure accurate transfer and control of data located in storage. The storage section may be expanded up to 33,792, 36 bit words.

The processor is organized as a bus system design with a 16 bit fully parallel data flow. The processor contains the facilities for addressing main storage, for fetching or storing information, for arithmetic and logical processing of data, instruction sequencing, timing, and for initiating the communication between storage and external equipment.

Working registers are located in high speed hardware. A total of 35 instructions are implemented presently. Processing rates on the order of 125,000 operations/second are attained by optimizing the machine organization, monolithic logic circuitry, and the high speed core storage.

A summary of Model CP-2 characteristics is contained in Table 1.

#### DATA AND INSTRUCTION FORMATS

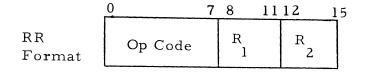

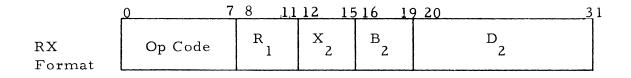

The standard or single precision data word is 32-bits long (Figure 1)

Figure 1. Data Format

# SYSTEM/4 Pi MODEL CP-2 CHARACTERISTICS

| TYPE         |                       | General Purpose, Digital                                        |                    |  |

|--------------|-----------------------|-----------------------------------------------------------------|--------------------|--|

| ORGANIZATION |                       | Parallel, fixed point, fractional,<br>two's complement notation |                    |  |

| INS          | TRUCTIONS             | 36                                                              |                    |  |

| INS          | TRUCTION WORD         | 16 or 32 bits                                                   |                    |  |

| DAT          | TA WORD               | 16 or 32 bits                                                   |                    |  |

| CON          | MPUTER CYCLE TIME     | 417 nsec                                                        |                    |  |

| STC          | DRAGE CYCLE           | 2.5 msec                                                        |                    |  |

| TYI          | PICAL EXECUTION TIMES |                                                                 |                    |  |

|              |                       | Short Format                                                    | Long Format        |  |

|              | ADD                   | 3.75 usec                                                       | 5 usec             |  |

|              | MULTIPLY              | 18.13 usec                                                      | 19.38 usec         |  |

|              | DIVIDE                | 47.29 usec                                                      | 48.54 usec         |  |

|              | OPERATIONS/SEC        | 125,000 typical                                                 |                    |  |

| PHY          | YSICAL                |                                                                 |                    |  |

|              | SIZE                  | 10" x 7.6" x 19.6                                               | b" (.86 cu. ft.)   |  |

|              | WEIGHT                | 47 lbs.                                                         |                    |  |

|              | MAIN STORAGE          | 8,448 - 36 bit wo<br>33,792 words                               | ords expandable to |  |

|              | TECHNOLOGY            | TTL Integrated C                                                | Circuits           |  |

| POWER        |                       | 240 Watts                                                       |                    |  |

|              | ENVIRONMENT           | MIL-E-5400, Cla                                                 | ass 2              |  |

|              | MTBF                  | 4,000 hours pred                                                | licted             |  |

Positive numbers are always in true binary form. Negative numbers are in two's complement form. The sign bit, position 0, is always 0 for positive numbers and 1 for negative numbers.

A half-precision data word of 16 bits is provided to increase processing speeds in areas where full accuracy is not required. Addressing is to the half-word level, but 32-bit data words must have an even address.

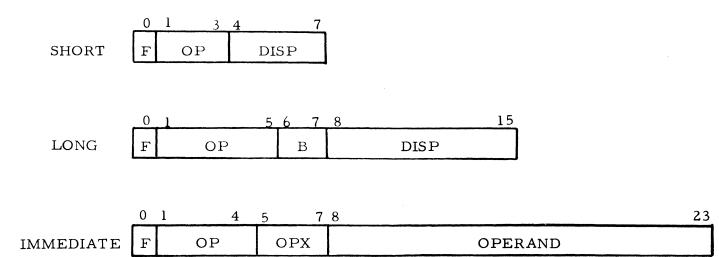

Two basic instruction word formats are used (Figure 2).

## Short Instruction Format

| 0  | 45 | 67 | ' 8 | 9      | 10  | 15 | 16 31   |

|----|----|----|-----|--------|-----|----|---------|

| OP | F  | Т  | I   | I<br>N | CON | 1D | ADDRESS |

Long Instruction Format

Figure 2. Instruction Word Formats

In a typical program, long format instructions are used infrequently, allowing a larger program to be contained in storage. The bits within the instruction words are used in the following manner:

- OP These 5 bits define which operation is to be performed by the computer.

- F This format bit controls the instruction format. A "zero" indicates a normal instruction, and a "one" indicates a long instruction.

- T These two Index Tag bits address the Index Register or Instruction Register (I) used in the address modification.

- DISP These bits are called the displacement and, with normal format instructions only, are usually added to the Instruction Register or the index register specified by T. The modified address is defined as the effective address (EA). If T is 00, the displacement is added to the

Instruction Register. The displacement is in 2's complement form if negative.

- IA Except for the Modify Index and Skip instruction with T=00, the Indirect Addressing bit is used in the long instruction format. If "zero", addressing will be direct. If a "one", addressing will be indirect.

- INT This bit specifies that the Branch or Skip on Condition (BSC) instruction is to be interpreted as a "Branch Out" when used in an interrupt routine.

- COND These six bits specify the condition of indicators that are interrogated on a BSC or Branch and Store Instruction Counter (BSI) instruction.

- ADDRESS These 16 bits usually specify a core storage address in a long instruction. The address can be modified by the contents of an index register, or used as an indirect address if the IA bit is on.

## ADDRESSING

All core storage locations are directly addressable under program control. The effective address may be determined by examining the tag, flag, and indirect address bits shown in Figure 2.

The recognition in the instruction of an indirect address control bit will cause the address portion to be treated as an indirect address. The address after indexing, if specified, gives the location of the effective address. An additional storage cycle is not required if index register one is used. One level of indirect addressing is provided.

The effective address for operands is formed as shown in Table 2.

## TABLE 2

| INDEX REG. | RELATIVE ADDR.             | DIRECT ADDR.  | INDIRECT ADDR.    |

|------------|----------------------------|---------------|-------------------|

| 0          | Program Counter<br>+ DISP* | ADDRESS       | C (ADDRESS)**     |

| 1          | XR1 + DISP                 | ADDRESS + XR1 | C (ADDRESS + XR1) |

| 2          | XR2 + DISP                 | ADDRESS + XR2 | C (ADDRESS + XR2) |

| 3          | XR3 + DISP                 | ADDRESS + XR3 | C (ADDRESS + XR3) |

## EFFECTIVE ADDRESS GENERATION

\*DISP may be positive or negative (2's complement) \*\*C means "contents of" ADDRESS field in instruction

## PROCESSOR ORGANIZATION

The processor is organized as a single address, fixed point, two's complement, fractional arithmetic system. It consists of the basic timing, register organization, arithmetic logic unit, I/O interface, and interrupt interface.

The data flow contains eight 16-bit storage registers, two 16-bit buffer registers, one 16-bit storage address register, one 32-bit storage data register, one 16-bit operation code register, one 17-bit adder, a bus system, and associated gates and controls. The data flow of the central processor is 16 bits wide. Data flow is organized around a two-clock system with a cycle of approximately 417 nanoseconds. Timing is generated from a frequency source internal to the CPU.

Functions of the hardware registers are as follows:

Al and A2 - These two 16-bit registers comprise the accumulator, the principal arithmetic register. The quotient is also contained in the accumulator following a division operation.

<u>B1 and B2</u> - These two 16 bit auxiliary registers are used to hold the multiplicand or divisor.

IX1 - A 16-bit register used in calculating an effective address.

<u>Program Counter</u> - This 16-bit register is used to determine the location of the next instruction to be fetched from storage.

Storage Address Register - A 16-bit register used to determine the next storage location fetched. May be loaded from either the Program Counter or with the calculated effective operand address. Storage Data Register - A 32-bit register used to hold the word read from the storage array.

Operation Register - A 16-bit register which holds the current instruction to be executed.

Next Instruction Register - A 16-bit register containing the next instruction to be executed, or part of the current instruction for long formats.

Buffer Register - A 16-bit register which contains the output of the adder. Its contents are distributed over the bus system to other hardware registers.

#### MAIN STORAGE

The MS is a three dimensional, coincident current, 8,448 word, 36-bit ferrite core array. Thirty-two bits contain data, two bits are allocated to parity, and two bits are used for storage protection. Access time for this system is approximately 0.9 usec, and it can operate continuously at a 2.5 usec cycle. Core storage addresses begin at 0000 and end at 8,447.

The nonalterable storage capability has been implemented by storage protection tests in every instruction which modifies storage. Each 36-bit storage word contains two storage protection bits, one for each half-word. These bits differentiate between protected and scratch pad locations, and are assigned when core storage is loaded from either the AGE or from the I/O Unit to prevent inadvertent modification of the data by the program. Any attempt to store data in a protected location will be prevented by an Invalid Address interrupt in computer control.

DRO cores with storage protection and power sequencing effectively provide program protection equivalent to most NDRO storage elements. DRO also allows complete flexibility in assigning storage between program and scratch pad, thus simplifying programming and allowing maximum use of the total storage capacity.

The storage element used is an IBM 13/21 (ID/OD in mils) lithium nickel ferrite. It is designed to operate over a temperature range of -55°C to +105°C.

The plane (Figure 3) used in the core array is a militarized version of a commercial IBM plane. The plane is approximately  $6'' \ge 6'' \ge 0.156''$  and contains 16,896 cores.

Welded connections are used throughout the memory array. This plane is machine-wired on IBM high volume production equipment. Foam pads are placed between the coated planes to meet the vibration requirements.

Figure 3. Core Plane

## INPUT/OUTPUT

The input-output section of the computer provides high-speed data transfer on two independent two-way, 17-bit parallel channels. The number of channels can be expanded to three without redesign or engineering modification to the computer. Input-output data transfer on two of the channels is accomplished under external control. Data transfer on the third channel is accomplished under program control. This growth capacity consists of one external controlled output channel and one program controlled input channel.

In addition, the input-output section provides capacity for discrete inputs and outputs. Storage cycle requests for externally controlled channels have priority over all other normal storage cycle requests and are honored at the completion of the existing storage cycle.

Each externally-controlled input channel has a block of 2048, 17-bit words of storage reserved for input data. Direct input to storage will occur under control of the external device, but only when the automatic input/output mode has been enabled by a program instruction, which specifies the channel to be enabled. Each externally controlled input channel is capable of data transmission at a word rate of 60 KC interleaved with information transmission on the other externally controlled channels. Externally-controlled output channels function in much the same manner, referencing a 2048 word block of storage and transferring data out at a 60KC word rate.

The processor may handle up to 40 discrete input lines, with eight of these operating as interrupt lines.

The interrupts are tested upon the completion of each instruction.

Interrupts are divided into two levels. The highest level consists of one interrupt, and the other level contains the remaining seven. The recognition of an interrupt in the lowest level causes all other interrupts in that level to be inhibited until the interrupt processing program is completed. The high-level interrupt is not inhibited while a low-level interrupt is being processed. Occurrence of the high priority interrupt causes a program branch. Upon completion of the high priority interrupt program, the interrupted program is resumed. The interrupted program could have been the main program or any one of seven lower priority interrupt programs.

Provisions are also included in the I/O Section for handling 16 discrete outputs.

## COMPUTER PACKAGING

The Model CP-2 is packaged using pluggable construction. The pluggable electronic subassembly, called a page, consists of two multilayer printed circuit boards bonded to a metal frame. An insulator separates each board from the frame. Two 98-pin connectors, identical to the ones being used for the Saturn Guidance Computer subassembly, are fastened along the lower edge of the frame. The connector was developed for this application and has demonstrated its performance and reliability in extensive tests and field service. It has been qualified for use in man-rated space vehicles. Feed-through connections and test points are provided along the upper edge of the frame. The page is fastened to the supporting structure at the two mounting flanges along an axis through the page center of gravity. Additional support is provided by the connectors. The page will be cooled by thermal conduction through the frame and mounting flange thermal interface. Keyed guide pins prevent installation in the wrong locations.

The multilayer printed circuit boards are made of several layers of etched, copper-clad, epoxy-glass laminates which are bonded together under heat and pressure. These boards have been in production since 1962 and have been successfully used in many systems produced by IBM including the Titan II, Titan III, Gemini, Saturn I, and Saturn V Guidance Computers. The integrated circuit flatpacks are soldered to etched patterns on the surface of the multilayer printed circuit boards. Figure 4 shows one side of a typical page with flatpacks mounted. Each page contains two multi-layer boards with up to 78 flatpacks per board. Discrete components are soldered in plated holes or on the board surface, depending on terminal configuration. A conformal coating is applied for component support and environmental protection.

## Figure 4. Typical Integrated Circuit Subassembly

The storage array is mounted in a housing which serves also to mount pluggable electronic subassemblies and acts as a thermal path. Pluggable electronic subassemblies similar to those in the computer are used to mount the storage circuits. A distribution multilayer printed circuit board is used to interconnect storage circuits and the array. The main storage assembly is removable as a module. Electrical connections to the assembly are made through pluggable input/output connectors.

The power supply assembly consists of three pluggable regulator modules and a transformer - RFI filter assembly. High-power components are fastened directly to the base plates for maximum heat transfer. A conformal coating is applied to the printed circuit board assemblies for environmental protection.

## SOFTWARE SUPPORT

A sophisticated package of computer programs will be provided for operation on an IBM System/360. This support package will assist the programmer in producing operational programs for the Model CP-2 by providing:

- Programming aids that will enable a program to be expressed in a language which is readily understood

- Facilities for storing, modifying, and accessing precoded programs

- A program checkout system to ensure central computer operational program readiness.

The software support programs delivered with the Model CP-2 are the following: