GA33-0013-3

3725 Communication Controller

**Principles of Operation**

System/370, 30xx, and 4300 Processors

1

3725 Communication Controller

**Principles of Operation**

System/370, 30xx, and 4300 Processors

**Publication Number**

GA33-0013-3

File Number S/370/30xx/4300-09

#### Fourth Edition (January 1984)

This is a major revision of GA33-0013-2, which is now obsolete. Changes to the text or to an illustration are indicated by a vertical line to the left of the change.

Reference in this publication to IBM products, programs, or services does not imply that IBM intends to make these available in all countries in which IBM operates. Any reference to an IBM program product in this publication is not intended to state or imply that only IBM's program product may be used. Any functionally equivalent program may be used instead.

The information contained in this manual is subject to change from time to time. Any such changes will be reported in subsequent revisions or Technical Newsletters.

Publications are not stocked at the addresses given below. Requests for IBM publications should be made to your IBM representative or to the IBM branch office serving your locality.

A form for readers' comments is provided at the back of this publication. If the form has been removed, comments may be addressed to either of the following:

- International Business Machines Corporation, Department 812LG, 1133 Westchester Avenue, White Plains, New York 10604, USA

- IBM France, Centre d'Etudes et Recherches, Department 0798, 06610 La Gaude, France

IBM may use or distribute any of the information you supply in any way it believes appropriate without incurring any obligation to you.

C Copyright International Business Machines Corporation 1983, 1984

#### PREFACE

This publication is intended to help users to write a control program or modify an IBM supplied Network Control Program or Emulation Program. The reader should have an understanding of basic data communication and a thorough knowledge of System/370 channel operations. The <u>Introduction to the IBM 3725</u> <u>Model 1 Communication Controller</u> (GA33-0010), or the <u>Introduction to the IBM <u>3725 Model 2 Communication Controller</u> (GA33-0021) is a prerequisite publication. A related publication is the <u>IBM 3725 Communication Controller Operating Guide</u> (GA33-0014).</u>

This manual is divided into five chapters and seven appendixes.

#### Chapter 1. Introduction

Provides a general description of the 3725 and its functional units.

#### Chapter 2. Structure of the 3725

Describes the system structure, the storage scheme, the registers, the interrupt scheme, and the interrupt levels assigned to each adapter.

# Chapter 3. Instruction Set

Describes each of the 3725 instructions with their mnemonics, format, and condition codes.

#### Chapter 4. Central Control Unit (CCU)

Describes the operation and programming requirements of the Central Control Unit.

## Chapter 5. Channel Adapter

Describes the operation and programming requirements of the Channel Adapter and how it communicates with the CCU.

#### Appendix A. CCU External Registers

Provides summary information on the CCU registers in convenient tabular form.

# Appendix B. CA Input/Dutput Instruction Summary Charts

Provides summary information on the channel adapter input/output instructions in convenient tabular form.

# Appendix C. Communication Scanner Commands

Provides summary information on the communication scanner commands in convenient tabular form.

# Appendix D. MOSS Commands

Provides summary information on the MOSS commands in convenient tabular form.

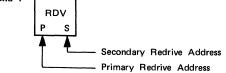

# Appendix E. Redrive Logic

Provides information on the use of the redrive logic.

# Appendix F. Initial Program Load

Provides information on initial program loading (IPL).

# Appendix G. Branch Trace

Provides information on branch tracing operations.

# **CONTENTS**

Į

1

C

| Chapter 1. Introduction                                  |

|----------------------------------------------------------|

| Characteristics of the 3725                              |

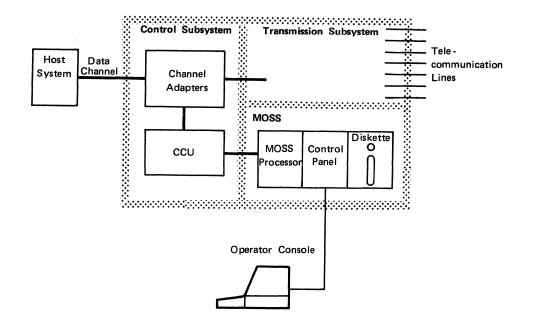

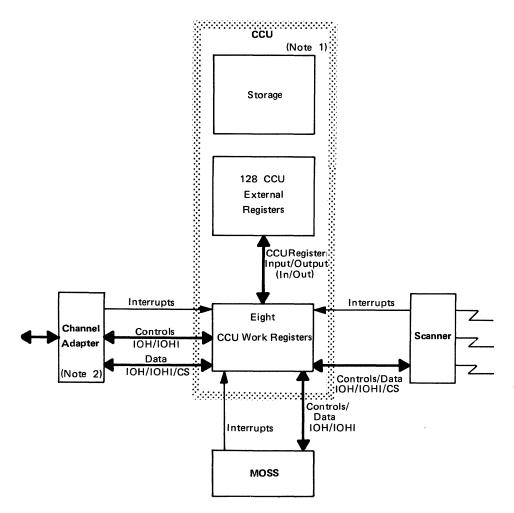

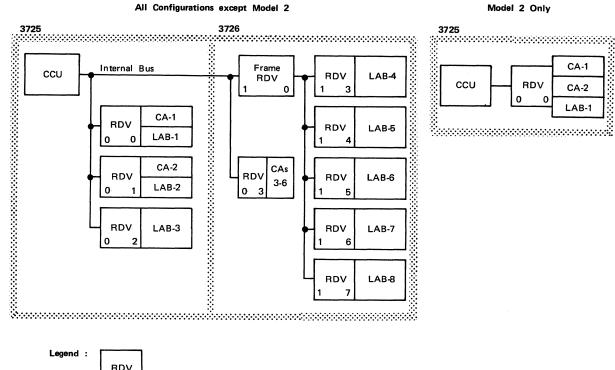

| 3725 Simplified Block Diagram                            |

| System Programs                                          |

| Control Subsystem                                        |

| Central Control Unit (CCU)                               |

| Storage                                                  |

| Storage Protection                                       |

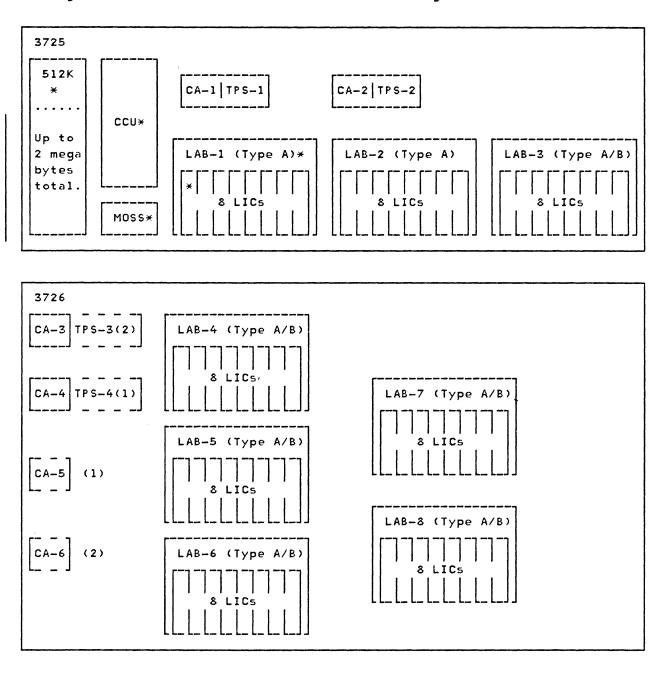

| Channel Adapter (CA)                                     |

| Two-Processor Switch (TPS)                               |

| Transmission Subsystem (TSS)                             |

| Line Attachment Base (LAB)                               |

| Communication Scanner                                    |

| Line Interface Couplers (LIC)                            |

| Interface Clocking                                       |

| Direct Attachment                                        |

| Maintenance and Operator Subsystem (MOSS)                |

| Physical Characteristics                                 |

| General Programming Concepts                             |

| 3725 Input/Output Instructions                           |

|                                                          |

| Chapter 2. Structure of the 3725                         |

| Storage                                                  |

| Storage Addressing Scheme                                |

| Storage Boundaries                                       |

| Storage Protection                                       |

| Storage Protection by User Protect Key                   |

| Read-Only Protection                                     |

| Addressing Exception Protection                          |

| Central Control Unit (CCU)                               |

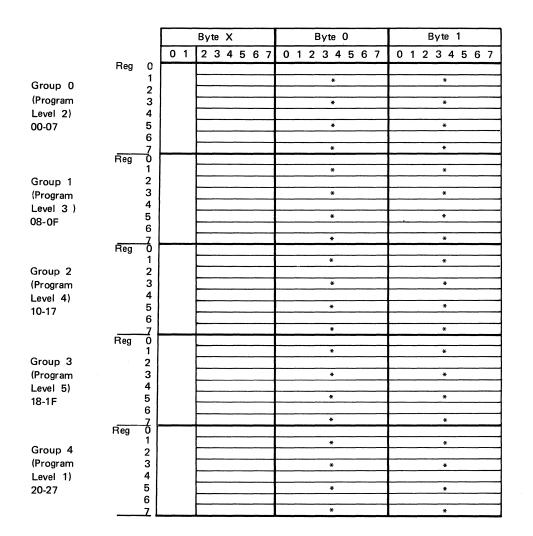

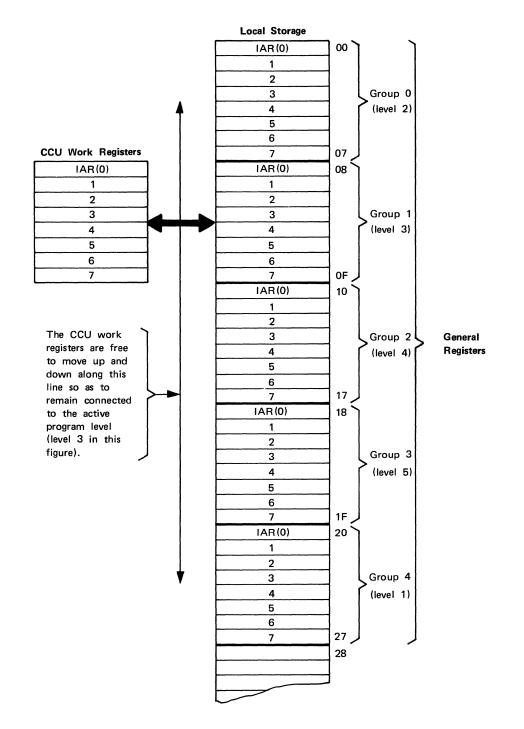

| CCU Registers                                            |

| CCU General Registers                                    |

| Condition Latches                                        |

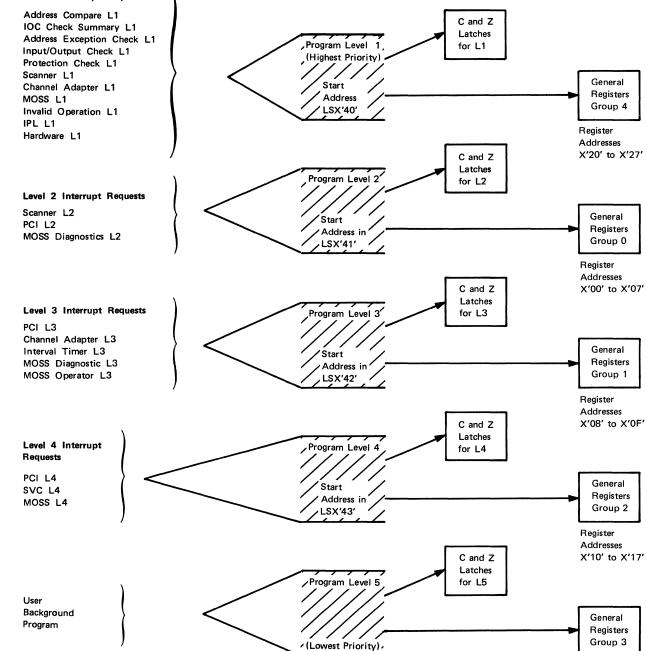

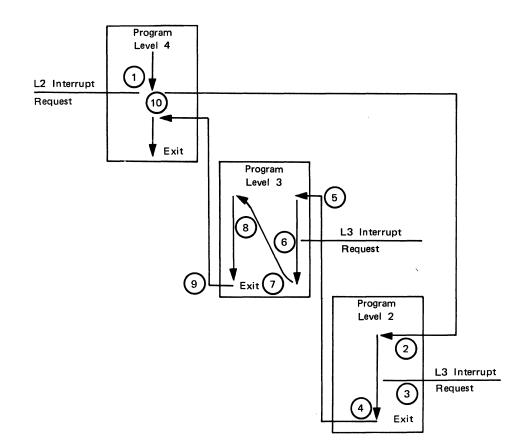

| Program Levels                                           |

| Background Program Level 5                               |

| Interrupt Program Level 4                                |

| Interrupt Program Level 3                                |

| Interrupt Program Level 2                                |

| Interrupt Program Level 1                                |

| Interrupts                                               |

| Channel Adapter (CA)                                     |

| Communication Scanner                                    |

| Maintenance and Operator Subsystem (MOSS)                |

|                                                          |

| Chapter 3. Instruction Set                               |

| Instruction Format                                       |

| Instruction Set Summary                                  |

| Instruction Set Summary                                  |

| <b>1 1 2 1 1 2 1 1 1 2 1 1 2 1 1 1 2 1 1 1 1 1 1 1</b> 1 |

۷

|   | Instruction Set Detailed Bit Structure                                                          |

|---|-------------------------------------------------------------------------------------------------|

|   | Load Instructions $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $3-6$ |

|   | Load Register Immediate                                                                         |

| 1 | Load Register                                                                                   |

|   | Load Halfword Register                                                                          |

|   | Load Character Register                                                                         |

|   | Load Register with Offset                                                                       |

|   | Load Halfword Register with Offset                                                              |

|   | Load Character Register with Offset                                                             |

|   | Load                                                                                            |

|   | Load Halfword                                                                                   |

|   | Insert Character                                                                                |

|   | Insert Character and Count                                                                      |

|   | Load Address                                                                                    |

|   | Store Instructions                                                                              |

|   | 3-15<br>Store                                                                                   |

|   |                                                                                                 |

|   |                                                                                                 |

|   |                                                                                                 |

|   | Store Character and Count                                                                       |

|   | Add Instructions                                                                                |

|   | Add Register Immediate                                                                          |

|   | Add Register                                                                                    |

|   | Add Halfword Register                                                                           |

|   | Add Character Register                                                                          |

|   | Subtract Instructions                                                                           |

|   | Subtract Register Immediate                                                                     |

|   | Subtract Register                                                                               |

|   | Subtract Halfword Register                                                                      |

|   | Subtract Character Register                                                                     |

|   | Compare Instructions                                                                            |

|   | Compare Register Immediate                                                                      |

|   | Compare Register                                                                                |

|   | Compare Halfword Register                                                                       |

|   | Compare Character Register                                                                      |

|   | Test Register Under Mask                                                                        |

|   | XOR Instructions                                                                                |

|   | XOR Register Immediate                                                                          |

|   | XOR Register                                                                                    |

|   | XOR Halfword Register                                                                           |

|   | XOR Character Register                                                                          |

|   | OR Instructions                                                                                 |

|   | OR Register Immediate                                                                           |

|   | OR Register                                                                                     |

|   | OR Halfword Register                                                                            |

|   | -                                                                                               |

|   |                                                                                                 |

|   | AND Instructions                                                                                |

|   | AND Register Immediate                                                                          |

|   | AND Register                                                                                    |

|   | AND Halfword Register                                                                           |

|   | AND Character Register                                                                          |

|   | Branch Operations                                                                               |

|   | Branch                                                                                          |

|   | Branch on Z Latch                                                                               |

|   | Branch on C Latch                                                                               |

vi

| Branch on Count                                                        | 3-39                                 |

|------------------------------------------------------------------------|--------------------------------------|

|                                                                        | 3-40                                 |

|                                                                        | 3-41                                 |

|                                                                        | 3-41                                 |

|                                                                        | 3-42                                 |

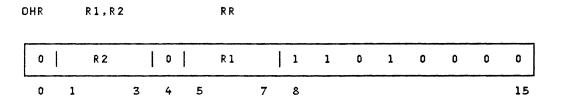

| Input/Output Instructions (RE, RR, and RA)                             | 3-43                                 |

| CCU Register Input                                                     | 3-43                                 |

| CCU Register Dutput                                                    | 3-44                                 |

| Adapter Input/Output                                                   | 3-44                                 |

| Adapter Input/Output Immediate                                         | 3-47                                 |

|                                                                        |                                      |

| Chapter 4. Central Control Unit (CCU)                                  | 4-1                                  |

| CCU Registers                                                          | 4-2                                  |

| Operation Register                                                     | 4-2                                  |

| Storage Address Register (SAR)                                         |                                      |

| CCU Work Registers                                                     |                                      |

| Instruction Address Register (IAR)                                     |                                      |

| CCU External Registers                                                 |                                      |

| General Registers                                                      |                                      |

| Local Storage Map                                                      |                                      |

| CCU Input/Output Instructions                                          |                                      |

| Input/Output Instruction Summary                                       |                                      |

| Input/Output X'00' through X'27' (General Registers)                   |                                      |

| Input/Output X'28' through X'2F' (Reserved)                            |                                      |

| Input/Output X'30' through X'35' (Channel Adapter CS Address Pointers) |                                      |

|                                                                        | 4-10                                 |

|                                                                        | 4-10                                 |

|                                                                        | 4-10                                 |

|                                                                        | 4-10                                 |

|                                                                        | 4-10                                 |

|                                                                        | 4-11                                 |

| · · · · · -                                                            | 4-11                                 |

| · · ·                                                                  | 4-11                                 |

|                                                                        | 4-11                                 |

|                                                                        | 4-11<br>4-11                         |

|                                                                        | +-11<br>4-12                         |

|                                                                        | +-12<br>4-12                         |

|                                                                        | 4-12                                 |

|                                                                        | 4-13                                 |

|                                                                        | 4-13                                 |

|                                                                        | 4-14<br>4-16                         |

|                                                                        |                                      |

|                                                                        | 4-17                                 |

|                                                                        | 4-18                                 |

|                                                                        | 4-20                                 |

|                                                                        | 4-20                                 |

|                                                                        | 4-22                                 |

|                                                                        | 4-23                                 |

|                                                                        |                                      |

|                                                                        | 4-24                                 |

| [[utnut X177] (Mscool] oncous [[ontrol 2]]                             | 4-25                                 |

|                                                                        | 4-25<br>4-26                         |

| Output X'78' (Force ALU Checks)                                        | 4-25<br>4-26<br>4-27                 |

| Dutput X'78' (Force ALU Checks)                                        | 4-25<br>4-26<br>4-27<br>4-28         |

| Dutput X'78' (Force ALU Checks)                                        | 4-25<br>4-26<br>4-27<br>4-28<br>4-30 |

(

C

| Output X'7A' (High Resolution Timer/Utilization Counter Control) . |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input X'7B' (Branch Trace Address Pointer)                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Output X'7B' (Set PCI Level 2)                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Input X'7C' (Branch Trace Buffer Count)                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Output X'7C' (Set PCI Level 3)                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Input X'7D' (CCU Hardware Check Register)                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Output X'7D' (Set PCI Level 4)                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Input X'7E' (CCU Level 1 Interrupt Requests)                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Output X'7E' (Set Program Interrupt Mask Bits)                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Input X'7F' (CCU L2, 3, or 4 Interrupt Requests)                   | 4-40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Output X'7F' (Reset Program Interrupt Mask Bits)                   | 4-42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CCU Error Handling                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CCU Hardware Errors                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CCU Program Errors                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CCU Special Topics                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Storage Protection                                                 | 4-44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Setting Up the User Protect Key                                    | 4-44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Setting Up the Storage Key                                         | 4-45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Setting Up the Address Exception Key                               | 4-46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Setting Up the Read-Only Key                                       | 4-47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Time Measurement in the 3725                                       | 4-48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| High/Low Resolution Timer                                          | 4-48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Utilization Counter                                                | 4-49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 100-Millisecond Interval Timer (Interrupting)                      | 4-50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                    | 1 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CCU Diagnostic Facilities                                          | 4-50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CCU Diagnostic Facilities                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |