IBM System/370

Principles of Operation

|                    | IBM System/370          |

|--------------------|-------------------------|

|                    |                         |

|                    |                         |

|                    | Principles of Operation |

|                    | r incipies of Operation |

|                    |                         |

|                    |                         |

|                    |                         |

|                    |                         |

|                    |                         |

|                    |                         |

|                    |                         |

|                    |                         |

|                    |                         |

|                    |                         |

|                    |                         |

|                    |                         |

|                    |                         |

|                    |                         |

| Publication Number | File Number             |

| GA22-7000-10       | S370-01                 |

|                    |                         |

|                    |                         |

|                    |                         |

|                    |                         |

#### Eleventh Edition (September 1987)

This major revision obsoletes and replaces GA22-7000-8, GA22-7000-9, and Technical Newsletters GN22-0644 and GN22-0683. Significant changes or additions to the text and illustrations are indicated by a vertical line to the left of the change.

Changes are made occasionally to the information herein; before using this publication in connection with the operation of IBM equipment, refer to the latest  $\underline{IBM}$   $\underline{System/370}$ ,  $\underline{30xx}$ ,  $\underline{and}$   $\underline{4300}$   $\underline{Processors}$   $\underline{Bibliography}$ , GC20-0001, for the editions that are applicable and current.

IBM may have patents or pending patent applications covering subject matter described herein. Furnishing this publication does not constitute or imply a grant of any license under any patents, patent applications, trademarks, copyrights, or other rights of IBM or of any third party, or any right to refer to IBM in any advertising or other promotional or marketing activities. IBM assumes no responsibility for any infringement of patents or other rights that may result from the use of this publication or from the manufacture, use, lease, or sale of apparatus described herein.

Licenses under IBM's utility patents are available on reasonable and nondiscriminatory terms and conditions. Inquiries relative to licensing should be directed, in writing, to: IBM Corporation, Director of Contracts and Licensing, Armonk, NY, USA 10504.

References in this publication to IBM products, programs, or services do not imply that IBM intends to make these available in all countries in which IBM operates.

Publications are not stocked at the address given below. Requests for IBM publications should be made to your IBM representative or to the IBM branch office serving your locality.

A form for reader's comments is provided at the back of this publication. If the form has been removed, comments may be addressed to: IBM Corporation, Central Systems Architecture, Department E57, PO Box 390, Poughkeepsie, NY, USA 12602. IBM may use or distribute whatever information you supply in any way it believes appropriate without incurring any obligation to you.

4

(c) Copyright International Business Machines Corporation 1970, 1972, 1973, 1974, 1980, 1981, 1987

This publication provides, for reference purposes, a detailed definition of the machine functions performed by System/370.

The publication applies only to systems operating in the System/370 mode. The IBM 370-XA Principles of Operation, SA22-7085, should be consulted regarding the functions of the architecture which apply to systems operating in the 370-XA mode, and the IBM 4300 Processors Principles of Operation for ECPS:VSE Mode, GA22-7070, should be consulted regarding the functions of the architecture which apply only to systems operating in the VSE mode.

The publication describes each function at the level of detail needed to prepare an assembler-language program that relies on that function. It does not, however, describe the notation and conventions that must be employed in preparing such a program, for which the user must instead refer to the appropriate assembler-language publication.

The information in this publication is provided principally for use by assembler-language programmers, although anyone concerned with the functional details of System/370 will find it useful.

This publication is written as a reference and should not be considered an introduction or a textbook. It assumes the user has a basic knowledge of data-processing systems. IBM publications relating to System/370 are listed and described in the <u>IBM System/370</u>, 30xx, and 4300 Processors Bibliography, GC20-0001.

All facilities discussed in this publication are not necessarily available on every model. Furthermore, in some instances the definitions have been structured to allow for some degree of extendibility, and therefore certain capabilities may be described or implied that are not offered on any model. Examples of such capabilities are the number of channel-mask bits in the control register, the size of the CPU address, and the number of CPUs sharing main storage. The allowance for this type of extendibility should not be construed as implying any intention by IBM to provide such capabilities. For information about the characteristics and availability of facilities on a specific model, see the functional characteristics publication for that model.

Largely because this publication is arranged for reference, certain words

and phrases appear, of necessity, earlier in the publication than the principal discussions explaining them. The reader who encounters a problem because of this arrangement should refer to the index, which indicates the location of the key description.

The information presented in this publication is grouped in 13 chapters and several appendixes:

<u>Chapter 1</u>, <u>Introduction</u>, highlights some of the major facilities of System/370.

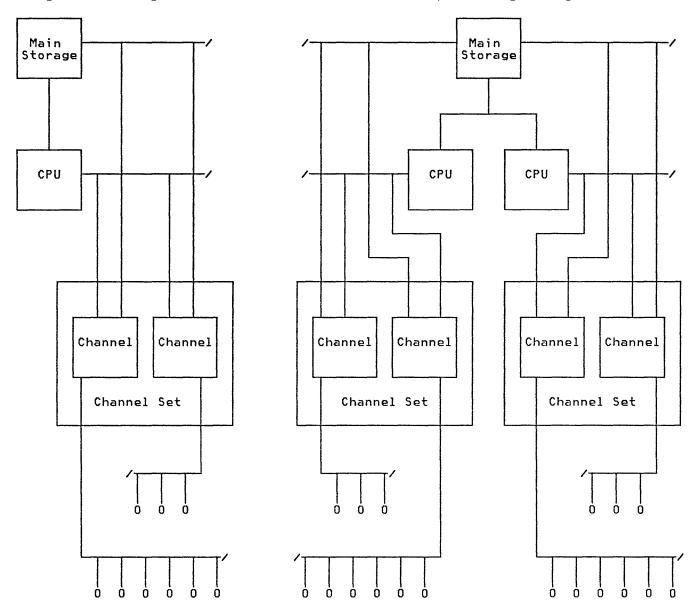

Chapter 2, Organization, describes the major groupings within the system -- the central processing unit (CPU), storage, and input/output -- with some attention given to the composition and characteristics of those groupings.

Chapter 3, Storage, explains the information formats, the addressing of storage, and the facilities for storage protection. It also deals with dynamic address translation (DAT), which, coupled with special programming support, makes the use of a virtual storage possible in System/370. Dynamic address translation eliminates the need to assign a program to a fixed location in real storage and thus reduces the addressing constraints on system and problem programs.

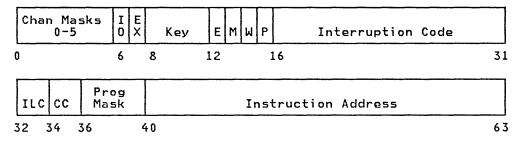

Chapter 4, Control, describes the facilities for the switching of system status, for special externally initiated operations, for debugging, and for timing. It deals specifically with CPU states, control modes, the programstatus word (PSW), control registers, program-event recording, timing facilities, resets, store status, and initial program loading.

Chapter 5, Program Execution, explains the role of instructions in program execution, looks in detail at instruction formats, and describes briefly the use of the program-status word (PSW), of branching, and of interruptions. It contains the principal description of the dual-address-space (DAS) facility. It also details the aspects of program execution on one CPU as observed by other CPUs and by channels.

Chapter 6, Interruptions, details the mechanism that permits the CPU to change its state as a result of conditions external to the system, within the system, or within the CPU itself. Six classes of interruptions are identified and described: machine-check interruptions, program interruptions, supervisor-call interruptions, external

interruptions, input/output interruptions, and restart interruptions.

<u>Chapter</u> 7, <u>General Instructions</u>, contains detailed descriptions of logical and binary-integer data formats and of all unprivileged instructions except the decimal and floating-point instructions.

<u>Chapter</u> 8, <u>Decimal</u> <u>Instructions</u>, describes in detail decimal data formats and the decimal instructions. The decimal instructions are a part of the commercial instruction set.

Chapter 9, Floating-Point Instructions, contains detailed descriptions of floating-point data formats and the instructions provided by the floating-point facility and by the extended-precision floating-point facility.

Chapter 10, Control Instructions, contains detailed descriptions of all of the semiprivileged and privileged instructions except for the I/O instructions.

<u>Chapter 11, Machine-Check Handling,</u>

describes the mechanism for detecting,

correcting, and reporting machine

malfunctions.

<u>Chapter</u> 12, <u>Operator</u> <u>Facilities</u>, describes the basic manual functions and controls available for operating and controlling the system.

Chapter 13, Input/Output Operations, explains the programmed control of I/O devices by CPUs and by channels. It includes detailed descriptions of the I/O instructions, channel-command words, and other I/O-control formats.

## The Appendixes include:

- Information about number representation

- Instruction-use examples

- Lists of the instructions arranged in several sequences

- A summary of the condition-code settings

- A list of the System/370 facilities

- A table of the powers of 2

- Tabular information helpful in dealing with hexadecimal numbers

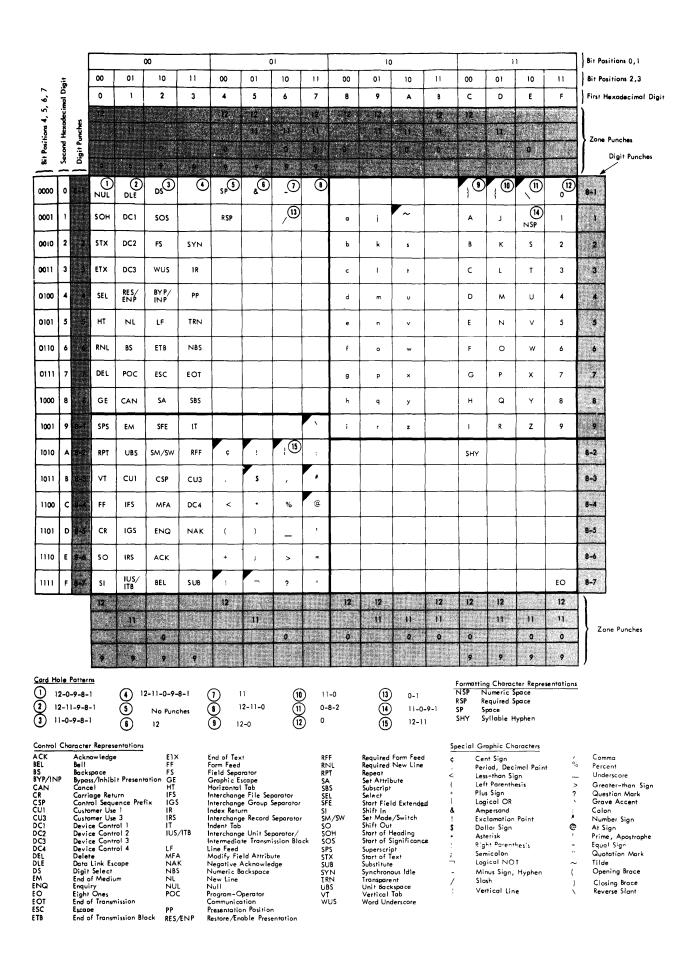

- An EBCDIC chart

- A discussion of changes affecting compatibility between System/360 and System/370

A discussion of changes affecting compatibility within System/370

#### SIZE NOTATION

In this publication, the letters K and M denote the multipliers 2<sup>10</sup> and 2<sup>20</sup>, respectively. Although the letters are borrowed from the decimal system and stand for kilo (10<sup>3</sup>) and mega (10<sup>6</sup>), they do not have the decimal meaning but instead represent the power of 2 closest to the corresponding power of 10. Their meaning in this publication is as follows:

| Symbol   | Value                   |

|----------|-------------------------|

| K (kilo) | 1,024 = 2 <sup>10</sup> |

| M (mega) | 1,048,576 = 220         |

The following are some examples of the use of K and M:

2,048 is expressed as 2K. 4,096 is expressed as 4K. 65,536 is expressed as 64K (not 65K). 2<sup>24</sup> is expressed as 16M.

When the words "thousand" and "million" are used, no special power-of-2 meaning is assigned to them.

## BYTES, CHARACTERS, AND CODES

Although the System/360 architecture was originally designed to support the Extended Binary-Coded-Decimal Interchange Code (EBCDIC), the instructions and data formats of the architecture are for the most part independent of the external code which is to be processed by the machine. For most instructions, all 256 possible combinations of bit patterns for a particular byte can be processed, independent of the character which the bit pattern is intended to represent. For instructions which use the zoned format, and for those few instructions which are dependent on a particular external code, the instruction TRANSLATE may be used to convert data from one code to another code. Thus, a machine operating in the System/370 mode can process EBCDIC, ASCII, or any other code which can be represented in eight or fewer bits per character.

In this publication, unless otherwise specified, the value given for a byte is the value obtained by considering the bits of the byte to represent a binary code. Thus, when a byte is said to

contain a zero, the value 00000000 binary, or 00 hex, is meant, and not the value for an EBCDIC character "0," which would be F0 hex.

## OTHER PUBLICATIONS

The channel-to-channel adapter is described in the publication <u>IBM Channel-to-Channel Adapter</u>, SA22-7091.

The I/O interface is described in the publication <u>IBM</u> <u>System/360</u> and

System/370 I/O Interface Channel to Control Unit Original Equipment Manufacturers' Information, GA22-6974.

Mathematical assists are described in the publication IBM System/370 Mathematical Assists, SA22-7094, which describes the instructions ARCTANGENT, COMMON LOGARITHM, COSINE, EXPONENTIAL, MULTIPLY AND ADD, NATURAL LOGARITHM, RAISE TO POWER, SINE, and SQUARE ROOT.

Vector operations are described in the publication <u>IBM System/370 Vector Operations</u>, SA22-7125.

.This page is intentionally left blank.

## CONTENTS

|     | General-Purpose Design Compatibility Compatibility among System/370 Models Compatibility between System/360 and System/370 System Program Availability CHAPTER 2. ORGANIZATION | 1-2<br>1-3<br>1-3<br>1-3<br>1-4<br>1-4 | during ASN Translation  ASN Authorization                            | 3-17<br>3-17<br>3-17<br>3-17 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|----------------------------------------------------------------------|------------------------------|

|     | Compatibility among System/370 Models                                                                                                                                          | 1-3<br>1-3<br>1-4                      | ASN-Authorization Controls Control Register 4 ASN-Second-Table Entry | 3-17<br>3-17<br>3-17         |

|     | Models Compatibility between System/360 and System/370 System Program Availability  CHAPTER 2. ORGANIZATION                                                                    | 1-3<br>1-4                             | Control Register 4                                                   | 3-17<br>3-17                 |

|     | Compatibility between System/360 and System/370                                                                                                                                | 1-3<br>1-4                             | ASN-Second-Table Entry                                               | 3-17                         |

|     | and System/370                                                                                                                                                                 | 1-4                                    | Authority-Table Entries ASN-Authorization Process                    | 3-18                         |

|     | Availability                                                                                                                                                                   | 1-4                                    | ASN-Authorization Process                                            | 0 40                         |

|     | Availability                                                                                                                                                                   |                                        | mon macher reaction tropess                                          | 3-18                         |

|     | CHAPTER 2. ORGANIZATION                                                                                                                                                        |                                        | Authority-Table Lookup                                               | 3-19                         |

|     | CHAPTER 2. ORGANIZATION                                                                                                                                                        |                                        | Recognition of Exceptions                                            |                              |

|     |                                                                                                                                                                                | 2-1                                    | during ASN Authorization .                                           | 3-20                         |

|     | Main Storage                                                                                                                                                                   | 2-3                                    | Dynamic Address Translation                                          | 3-20                         |

|     | CPU                                                                                                                                                                            | 2-3                                    | Translation Control                                                  | 3-22                         |

|     | PSW                                                                                                                                                                            | 2-3                                    | Translation Modes                                                    | 3-22                         |

|     | General Registers                                                                                                                                                              | 2-4                                    | Control Register 0                                                   | 3-23                         |

|     | Floating-Point Registers                                                                                                                                                       | 2-4                                    | Control Register 1                                                   | 3-24                         |

|     | Control Registers Vector Facility                                                                                                                                              | 2-4<br>2-4                             | Control Register /                                                   | 3-24<br>3-25                 |

| i   | I/0                                                                                                                                                                            | 2-4                                    | Segment-Table Entries                                                | 3-25                         |

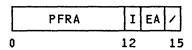

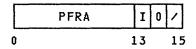

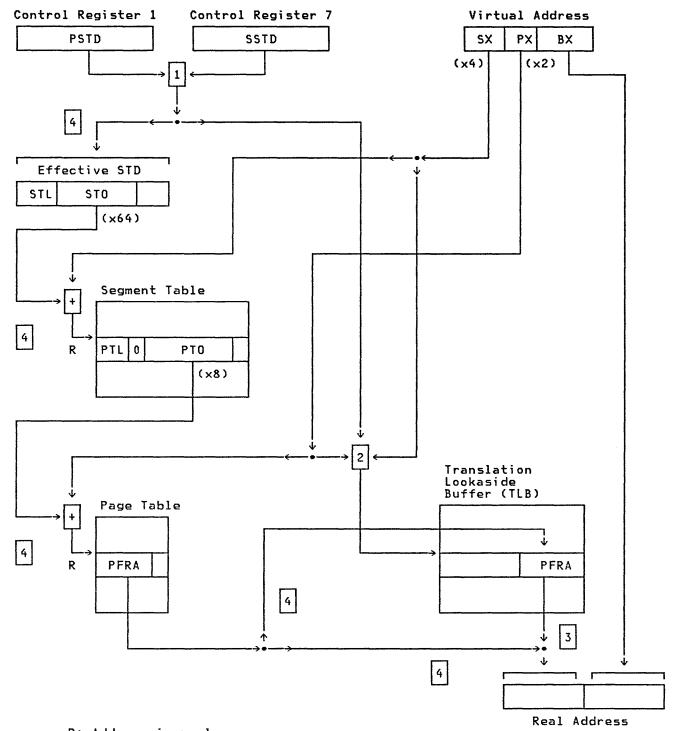

|     | Channel Sets                                                                                                                                                                   | 2-6                                    | Segment-Table Entries Page-Table Entries                             | 3-26                         |

|     | Channels                                                                                                                                                                       | 2-6                                    | Summary of                                                           | 3 20                         |

|     | I/O Devices and Control Units                                                                                                                                                  | 2-6                                    | Dynamic-Address-Translation                                          |                              |

|     | Operator Facilities                                                                                                                                                            | 2-6                                    | Formats                                                              | 3-26                         |

|     |                                                                                                                                                                                |                                        | Translation Process                                                  |                              |

|     | CHAPTER 3. STORAGE                                                                                                                                                             | 3-1                                    | Effective Segment-Table                                              |                              |

|     | CHAPTER 3. STORAGE Storage Addressing                                                                                                                                          | 3-2                                    | Designation                                                          | 3-27                         |

|     | Storage Addressing with                                                                                                                                                        |                                        | Inspection of Control Register                                       |                              |

|     | Extended Address Fields                                                                                                                                                        | 3-3                                    | 0                                                                    | 3-30                         |

|     | Information Formats Integral Boundaries                                                                                                                                        | 3-3                                    | Segment-Table Lookup                                                 | 3-30                         |

|     | Integral Boundaries                                                                                                                                                            | 3-3                                    | Page-Table Lookup                                                    | 3-31                         |

|     | Byte-Oriented-Operand Facility                                                                                                                                                 | 3-5                                    | Formation of the Real Address                                        | 3-31                         |

| 1,  | Address Types                                                                                                                                                                  | 3-5<br>3-5                             | Recognition of Exceptions                                            | 3-31                         |

|     | Real Address                                                                                                                                                                   | 3-5                                    | during Translation Translation-Lookaside Buffer .                    | 3-31                         |

|     | Virtual Address                                                                                                                                                                | 3-5                                    | Use of the                                                           | 3 31                         |

|     | Primary Virtual Address                                                                                                                                                        | 3-5                                    | Translation-Lookaside Buffer                                         | 3-32                         |

|     | Secondary Virtual Address .                                                                                                                                                    | 3-6                                    | Modification of Translation                                          | 5 52                         |

|     | Logical Address                                                                                                                                                                | 3-6                                    | Tables                                                               | 3-36                         |

|     | Instruction Address                                                                                                                                                            | 3-6                                    | Address Summary                                                      | 3-38                         |

|     | Instruction Address Effective Address                                                                                                                                          | 3-6                                    | Addresses Translated                                                 | 3-38                         |

|     | Storage Key                                                                                                                                                                    | 3-6                                    | Handling of Addresses                                                | 3-39                         |

|     | Storage-Key 4K-Byte-Block                                                                                                                                                      |                                        | Assigned Storage Locations                                           | 3-41                         |

|     | Facility                                                                                                                                                                       | 3-7                                    |                                                                      |                              |

|     | Storage Keys with Storage-Key                                                                                                                                                  |                                        | CHAPTER 4. CONTROL                                                   | 4-1                          |

|     | 4K-Byte-Block Facility Not                                                                                                                                                     | 7 7                                    | Stopped, Operating, Load, and                                        |                              |

|     | Installed                                                                                                                                                                      | 3-7                                    | Check-Stop States                                                    | 4-2<br>4-2                   |

|     | Storage Keys with Storage-Key<br>4K-Byte-Block Facility                                                                                                                        |                                        | Stopped State                                                        | 4-2                          |

|     | Installed                                                                                                                                                                      | 3-7                                    | Load State                                                           | 4-3                          |

|     | Storage-Key-Exception Control                                                                                                                                                  | 3-7                                    | Check-Stop State                                                     | 4-3                          |

|     | Storage-Key-Instruction                                                                                                                                                        | <b>.</b>                               | Program-Status Word                                                  | 4-3                          |

|     | Extensions                                                                                                                                                                     | 3-7                                    | EC and BC Modes                                                      | 4-4                          |

|     | Protection                                                                                                                                                                     | 3-7                                    | Program-Status-Word Format in EC                                     |                              |

|     | Key-Controlled Protection                                                                                                                                                      | 3-8                                    | Mode                                                                 | 4-6                          |

|     | Segment Protection                                                                                                                                                             | 3-9                                    | Program-Status-Word Format in BC                                     |                              |

|     | Low-Address Protection                                                                                                                                                         | 3-9                                    | Mode                                                                 | 4-8                          |

|     | Reference Recording                                                                                                                                                            | 3-10                                   | Control Registers                                                    | 4-8                          |

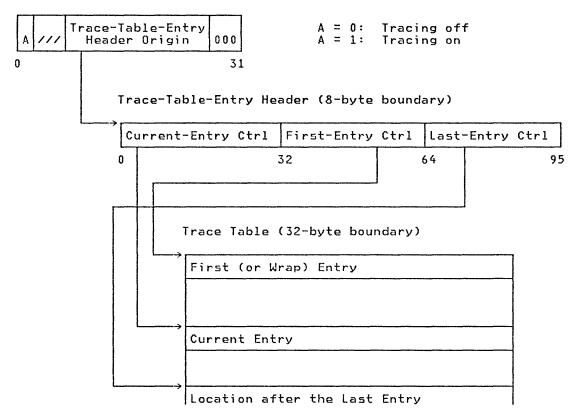

|     | Change Recording                                                                                                                                                               | 3-10                                   | DAS Tracing                                                          | 4-11                         |

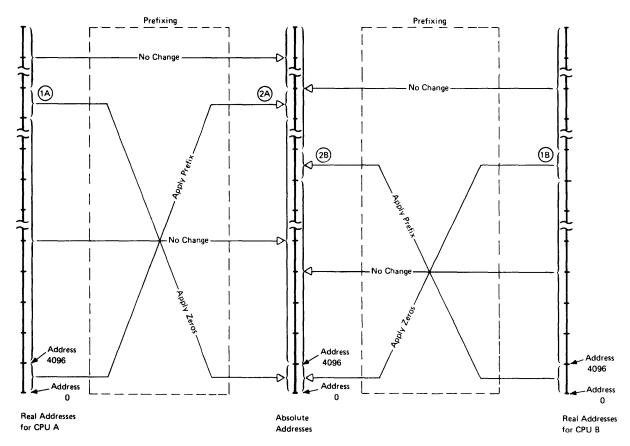

|     | Prefixing                                                                                                                                                                      | 3-11                                   | Protection for DAS Tracing .                                         | 4-13                         |

|     | Address Spaces                                                                                                                                                                 | 3-12                                   | Other Actions Associated with                                        | 4. 17                        |

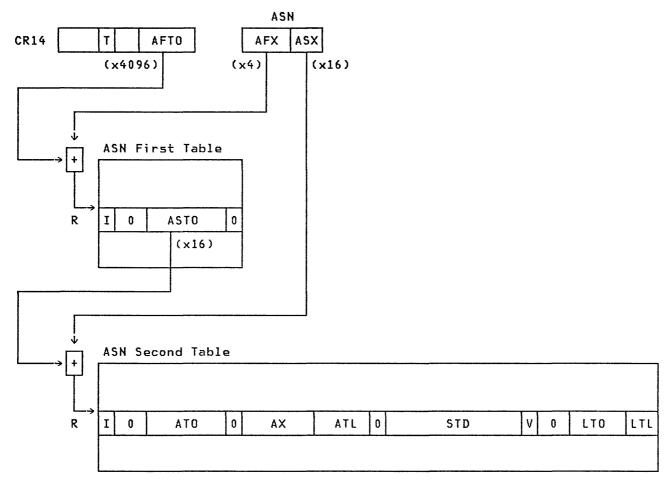

|     | ASN Translation                                                                                                                                                                | 3-13                                   | DAS Tracing Serialization for DAS Tracing                            | 4-13                         |

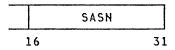

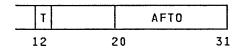

|     | ASN-Translation Controls                                                                                                                                                       | 3-13<br>3-14                           | Trace-Table Designation                                              | 4-13<br>4-13                 |

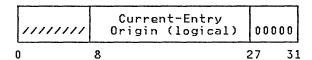

|     | ASN-First-Table Entries                                                                                                                                                        | 3-14                                   | Trace-Table-Entry Header                                             | 4-13                         |

|     | ASN-Second-Table Entries                                                                                                                                                       |                                        | Interlocks                                                           | 4-14                         |

|     | ASN-Translation Process                                                                                                                                                        |                                        | Trace Entry                                                          | 4-14                         |

| Mr. | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,                                                                                                                                         | ~ ~ ~                                  |                                                                      |                              |

|     | ASN-First-Table Lookup                                                                                                                                                         | 3-16                                   | Program-Event Recording                                              |                              |

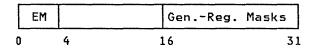

| Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4-16 | Execution of Interruptible       |       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------------------|-------|

| Identification of Cause                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-17 | Instructions                     | 5-9   |

| Tuencincación di cadae                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |                                  | ,     |

| Priority of Indication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4-17 | Exceptions to Nullification and  |       |

| Storage-Area Designation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4-18 | Suppression                      | 5-11  |

| PER Events                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      | Storage Change and Restoration   |       |

| Successful Branching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4-19 | for DAT-Associated Access        |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |                                  |       |

| Instruction Fetching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4-19 | Exceptions                       | 5-11  |

| Storage Alteration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4-19 | Modification of DAT-Table        |       |

| General-Register Alteration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      | Entries                          | 5-12  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-20 |                                  | J 12  |

| Indication of PER Events                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      | Trial Execution for Editing      |       |

| Concurrently with Other                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      | Instructions and TRANSLATE       | 5-12  |

| Interruption Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-20 | Interlocked Update for           |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |                                  | 5-12  |

| Direct Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4-23 | Nullification and Suppression    |       |

| Read-Write-Direct Facility                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4-23 | Dual-Address-Space Control       | 5-13  |

| External-Signal Facility                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      | Summary                          | 5-13  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-23 | DAC E                            | 5-14  |