## Systems

# IBM System/370 Principles of Operation

The IBM System/370 is a data processing system that is based on the IBM System/360 but that extends the capabilities of that system. This manual describes extensions to the functional design of the System/360 that are incorporated in models of the System/370.

The reader is assumed to have an understanding of the System/360, as described in the *IBM System/360 Principles of Operation*, GA22-6821. The *System/370 Princples of Operation* should be used in conjunction with the *System/360 Principles of Operation*.

For information about the characteristics, functions, and features of a specific System/370 model, use the functional characteristics manual for that model.

## Preface

Just as the *IBM System/360 Principles of Operation* is the machine reference manual for the IBM System/360, this publication is the machine reference manual for the IBM System/370. It deals, however, only with those functions that are additional to or different from those of the System/360, and the reader therefore must rely directly on the *IBM System/360 Principles of Operation*, GA22-6821

Note that this publication is not written as an introduction or as a textbook but as a reference document. Other manuals are available that serve those other functions. It assumes the reader has a basic knowledge of data processing systems and, specifically, the IBM System/360. Such basic information can be found, for example, in the *Introduction* to *IBM Data Processing Systems*, GC20-1684, and in the *IBM System/360 System Summary*, GA22-6810.

The information in this manual is aimed most directly at those readers concerned with the preparation of programs to be run on the System/370, where in such preparation a knowledge of the machine language and system functions is pertinent. At the same time, the book contains information that may be of particular interest to system designers.

#### First Edition (June 1970)

Requests for copies of IBM publications should be made to your IBM representative or to the IBM branch office serving your locality.

This manual has been prepared by the IBM Systems Development Division, Product Publications, Dept. B98, PO Box 390, Poughkeepsie, N.Y. 12602. A form for readers' comments is provided at the back of this publication. If the form has been removed, comments may be sent to the above address.

<sup>©</sup> Copyright International Business Machines Corporation 1970

## Contents

| Modifications to System/360.         Comparison         Comparison | 5 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Handling Invalid Decimal Sign                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5 |

| Time-of-Day Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6 |

| Control Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7 |

| Masking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 8 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 8 |

| Extended I/O Masking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 8 |

| Machine-Check Handling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 9 |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 9 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 9 |

| CPU Recovery Action                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |

| Bit-Correction Capability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |

| CPU Retry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |

| Check Stop State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1 |

| Machine-Check Logout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1 |

| Machine-Check Control Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1 |

| Hard Stop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |

| Extended Logout Masks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1 |

| Machine-Check Subclass Masks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2 |

| Summary of Machine-Check Masking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |

| Machine-Check Extended Logout Pointer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3 |

| Interruption Action                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |

| Machine-Check Interruption Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4 |

| Subclass                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |

| Time of Interruption Occurrence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |

| Storage Error Type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |

|                                                    | - |

|----------------------------------------------------|---|

| Machine-Check Code Validity Bits                   |   |

| Machine-Check Extended Logout Length               |   |

| Machine-Check Extended Interruption Information 16 | 5 |

| CPU Identification                                 | 5 |

| Storage Validation                                 | 5 |

| Programmed Validation                              | 5 |

| Validation on Input Operations                     |   |

| Permanently Allocated Storage Locations            |   |

| Input/Output Operations                            | ł |

|                                                    |   |

| Block-Multiplexing Control                         |   |

| • •                                                |   |

| Limited Channel Logout                             |   |

| Extended Channel Logout 20                         | , |

| Instructions                                       | L |

| Compare Logical Characters Under Mask              |   |

| Compare Logical Long                               |   |

| Insert Characters Under Mask                       |   |

| Load Control                                       |   |

| Move Long                                          |   |

|                                                    |   |

| Set Clock                                          |   |

| Shift and Round Decimal                            |   |

| Start I/O Fast Release                             |   |

| Store Channel ID                                   |   |

| Store Characters Under Mask                        | 3 |

| Store Clock                                        | 3 |

| Store CPU ID                                       | ) |

| Store Control                                      | ) |

| Index                                              | ) |

#### **REMOVAL OF USASCII MODE**

System/360 provides for the USASCII-8 code by a mode under control of PSW bit 12. When bit 12 of the PSW is one, the codes preferred for the USASCII-8 are generated for decimal results. When PSW bit 12 is zero, the codes preferred for EBCDIC are generated.

In System/370, the USASCII mode and the associated meaning of PSW bit 12 are removed. All instructions whose execution in System/360 depends on the setting of PSW bit 12 are executed in the System/370 EBCDIC mode.

When bit 12 is a one, a program interruption for specification exception occurs.

#### HANDLING AN INVALID DECIMAL SIGN

In System/360 an invalid decimal operand causes the operation to be terminated. In System/370, the operation is suppressed, instead of terminated, when an invalid sign is detected. The action applies to all instructions that check the validity of decimal operands: ADD DECIMAL, SUB-TRACT DECIMAL, ZERO AND ADD, COMPARE DECI-MAL, MULTIPLY DECIMAL, DIVIDE DECIMAL, and CONVERT TO BINARY. It includes also the new instruction SHIFT AND ROUND DECIMAL. The action is:

| Sign    | Digit               | Instruction |

|---------|---------------------|-------------|

| Code    | Code                | Execution   |

| Valid   | All valid           | Completed   |

| Valid   | One or more invalid | Terminated  |

| Invalid | All valid           | Suppressed  |

| Invalid | One or more invalid | Suppressed  |

The time-of-day clock provides a consistent measure of elapsed time suitable for time-of-day indication. The cycle of the clock is approximately 143 years.

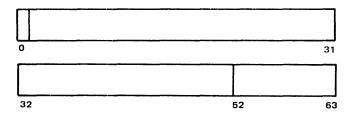

The time-of-day clock is a binary counter with this format:

The bit positions of the clock are numbered 0 to 63, corresponding to the bit positions of a fixed-point number of double precision. Time is measured by incrementing the value of the clock, following the rules for fixed-point arithmetic.

The resolution of the time-of-day clock is one microsecond, and the clock is incremented by adding a one in bit position 51 every microsecond.

The program is not alerted to the overflow as the clock value changes from a large positive value to a large negative value because of a carry from bit position 1 into bit position 0. No interruption condition is generated as a result of the overflow. When incrementing the clock causes a carry to be propagated out of bit position 0, the carry is ignored, and counting continues from zero on.

The clock can be inspected by using the STORE CLOCK instruction, which causes the current clock value to be stored in main storage. The clock can be set to a specific value by SET CLOCK, which causes the current clock value to be replaced by the operand designated by the instruction. The SET CLOCK instruction is executed only when the clock security switch on the operator intervention panel is set to permit changing the value of the clock.

The operation of the clock is not affected or inhibited by any normal activity or event in the system. The clock runs when the CPU is in the wait or stopped state or in the instruction-step, single-cycle, or test mode. Its operation is not affected by system reset or the IPL procedure. Depending on the implementation, the clock may or may not run with CPU power off.

Three states are distinguished for an operational clock: set, not-set, and error. The state determines the condition code set by STORE CLOCK.

When the power for the clock is turned on, the value of the clock is set to zero, and the clock enters the not-set state.

The clock enters the set state when SET CLOCK causes the clock's contents to be set, that is, when SET CLOCK is executed without encountering any exceptions and with the clock operational and the clock-security switch in the enabled position. The clock can be placed in the set state from either the not-set or the error state.

The clock enters the error state whenever the clock stops or misses a time increment, such as may occur when the power supply is temporarily disconnected, or when a malfunction is detected that is likely to have affected the validity of the clock's value.

The operation of the clock is interlocked such that successive executions of STORE CLOCK do not provide the same clock value unless the clock validity indicator is off or the clock value has been changed in between by execution of SET CLOCK. The control registers provide for loading and storing control information.

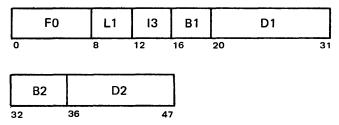

Two instructions, LOAD CONTROL and STORE CON-TROL, are provided. LOAD CONTROL furnishes a means of loading control information from main storage into control registers; STORE CONTROL permits information to be transmitted from control registers to main storage. These instructions operate in a manner similar to LOAD MULTIPLE and STORE MULTIPLE.

The structure provides for sixteen 32-bit registers for control purposes. These registers are not part of addressable storage.

One or more specific bit positions in control registers are assigned to each function requiring register space. A model may, however, furnish more control register bit positions than required by the installed function. For example, a model may provide register positions for more channel mask bits than the number of channels installed. It depends on the model and on the installed functions whether additional unassigned control register bit positions are furnished.

Only the general structure of the control register function is described here; a description of the assignment and meaning of register positions appears with the description of the function with which the register position is associated. Figure 1 lists the functions to which each control register field belongs.

| Word | Bits | Name of Field               | Function                   | Value<br>after<br>Reset |

|------|------|-----------------------------|----------------------------|-------------------------|

| 0    | 0    | Block-Multiplex Mode        | Block-Multiplexing Control | 0                       |

| 0    | 24   | Timer Mask                  | Extended External Masking  | 1                       |

| 0    | 25   | Interrupt Key Mask          | Extended External Masking  | 1                       |

| 0    | 26   | External Signal Masks       | Extended External Masking  | 1                       |

| 2    | 0-31 | Channel Masks               | Extended I/O Masking       | 1                       |

| 14   | . 0  | Hard Stop Mode              | Machine-Check Handling     | 1                       |

| 14   | 1    | Synchronous MCEL* Mask      | Machine-Check Handling     | 1                       |

| 14   | 2    | I/O Extended Logout         | Machine-Check Handling     | 0                       |

| 14   | 4    | Recovery Report Mask        | Machine-Check Handling     | 0                       |

| 14   | 5    | Configuration Report Mask   | Machine-Check Handling     | 0                       |

| 14   | 6    | External Damage Report Mask | Machine-Check Handling     | 1                       |

| 14   | 7    | Warning Mask                | Machine-Check Handling     | 0                       |

| 14   | 8    | Asynchronous MCEL Mask      | Machine-Check Handling     | 0                       |

| 14   | 9    | Asynchronous Fixed Log Mask | Machine-Check Handling     | 0                       |

| 15   | 8-31 | MCEL Pointer                | Machine-Check Handling     | 512                     |

Figure 1. Allocation of Control Register Fields

## EXTENDED EXTERNAL MASKING

Extended external masking provides for selective masking of interruptions due to timer, key, and external signals 2-7. It consists of three subclass mask bits in control register 0, defined as:

Timer Mask (T): Bit 24 of control register 0 controls whether the CPU is enabled for an interruption due to the timer. An external interruption due to the timer value becoming negative can occur only when both the external mask bit in the PSW and the timer mask bit in control register 0 are one. The bit is set to one by system reset.

Key Mask (K): Bit 25 of control register 0 controls whether the CPU is enabled for interruption due to a signal from the key. An external interruption due to pressing the interrupt key can occur only when both the external mask bit in the PSW and the key mask bit in control register 0 are one. The bit is set to one by system reset.

Signal Mask (S): Bit 26 of control register 0 controls whether the CPU is enabled for interruption by external signals 2-7. An external interruption due to the presence

of external signals 2-7 can occur only when the external mask bit in the PSW and the signal mask bit in control register 0 are one. The bit is set to one by system reset.

## **EXTENDED I/O MASKING**

Extended I/O masking provides for selective masking of each channel. It provides a set of bits in control register 2 starting at bit position 0 and extending for as many contiguous bit positions as the number of channels supplied. The assignment is such that a bit is assigned to the channel with an address equal to the position of the bit in control register 2.

The channel mask bits in control register 2 for all available channels are set to one by system reset. The state of channel mask bits for unavailable channels is unpredictable. Interruptions from channels 6 and up are controlled by the I/O mask bit (PSW bit 6) in conjunction with the corresponding channel mask bit: the channel can cause an interruption only when the I/O mask is one and the corresponding channel mask is one. Interruptions from channels 0-5 are controlled by channel masks 0-5 in the PSW. Bits 0-5 in control register 2 do not participate in controlling I/O interruptions; they are, however, preserved in the control register.

The machine-check interruption furnishes a means of reporting equipment malfunction and certain external disturbances, and it supplies the program with information about the location and the nature of the cause. In some cases, depending on the nature of the malfunction, the system may either take correcting action or circumvent the failing components.

## MACHINE-CHECK CONDITIONS

Equipment malfunctions and other conditions responsible for machine-check interruptions are called machine-check conditions. Machine-check conditions are subdivided into several subclasses.

An equipment malfunction resulting in the loss of integrity of a process in the system is called a damage condition. Damage conditions are divided into five subclasses identifying the process affected: system damage, instruction-processing damage, timer damage, time-of-day clock damage, and external damage. Malfunctions that cannot be isolated to a specific process are indicated as system damage.

An equipment malfunction that is successfully corrected or circumvented without loss of system integrity is called a recovery condition. Depending on the model and the type of malfunction, some recovery conditions may be discarded. Recovery conditions are grouped into one subclass called system recovery.

Machine-check conditions not directly related to equipment malfunctions are called alert conditions. The alert conditions contain two subclasses: automatic configuration and warning.

System damage and instruction-processing damage conditions may result in termination of the current instruction or cause interruptions to be lost, and are referred to as hard machine-check conditions. All other subclasses of machinecheck conditions are called soft machine-check conditions.

## HANDLING OF CONDITIONS

In normal operation, the system is assumed to have correct parity in storage and registers. A machine-check condition is generated whenever instructions or data with invalid parity are fetched and processed or whenever invalid parity on the protection key or the key in storage makes it impossible to establish reliably whether protection applies to the particular type of storage reference. When instructions or data with invalid parity are fetched but are not used, the program is not necessarily alerted. Similarly, a machine-check condition is not necessarily indicated when the key in storage on a fetch-type reference has bad parity but protection does not apply because the system does not have fetch protection installed.

Once valid information has been placed in storage and in registers, a machine-check condition can be caused only by machine malfunction and never by logically invalid data or instructions. Specification of an unavailable system component, such as a storage unit, channel, or I/O device, does not cause indication of equipment malfunctioning. Instead, such an error causes the appropriate program or I/O interruption condition or sets the condition code.

Depending on the model and type of error, a malfunction detected during an I/O operation may cause a machinecheck condition or may result in the placing of identifying information in the I/O status information associated with the operation, or both. When a CCW or data with invalid parity are fetched from storage but are not used in the I/O operation, it depends on the model and the type of error whether equipment malfunctioning is indicated. When an equipment malfunction occurring in an I/O operation is not treated as a machine-check condition, indication of the error to the program and the logging of diagnostic information are not subject to the machine-check mask, PSW bit 13.

## CPU RECOVERY ACTION

Two basic techniques, bit correction and retry, are used for recovery from machine-detected malfunctions.

## **Bit-Correction Capability**

Within certain units of the system, a bit-correction capability is provided by either appending additional check bits to a group of bytes or by converting the check bits of a group of bytes into an arrangement which provides for error checking and correction (ECC). The group of bytes associated with a single ECC code is called an ECC block. The number of bytes in an ECC block, and the manner in which the conversion or appending is accomplished depend on the type of unit involved and may vary among models. When ECC is provided, a reference which results in a single-bit error in the ECC block is automatically corrected.

The automatic correction of a single-bit error causes: (1) the transmittal of correct information to the requesting area, and (2) possibly an attempt to correctly restore the information in the location from which the data was obtained. When the cause of the error does not affect the restore operation, the contents of the location will be correct. If the fault causes the restore operation to return the data with a single-bit error, a subsequent readout of that location will correct the error only if no other bit error is encountered. Thus, a persistent error, as well as a one-time occurrence, is corrected when only one bit is affected.

When multiple-bit errors are detected the information is not corrected. The condition of the check bits on the information transmitted to the requesting area depends on the model. Correction of multiple-bit errors requires special procedures and is described in "Storage Validation."

#### **CPU Retry**

In models with machine-retry capability, information about the state of the machine is saved periodically. The logical point in the processing to which this saving of information pertains is called a hardware checkpoint. When an error occurs, recovery is attempted by returning the machine state to that existing at the latest hardware checkpoint and proceeding from that point. The interval between checkpoints is model-dependent. In some cases, several checkpoints are established within a single instruction; in others, checkpoints are established only at the beginning of instructions, or even less frequently.

If, after a restart at the checkpoint, the machine error does not reoccur or is circumvented, a recovery condition is recognized.

When, after repeated restarts at the checkpoint, the machine cannot proceed beyond the point of error, a hard machine-check condition is recognized.

#### Point of Interruption

Due to the checkpoint capability the interruption resulting from a hard machine-check may occur at a point in the recovery cycle which is prior to the error. Additionally, due to the nature of the malfunction, it is possible that not all of the status reflects the same instant. For example, the general registers modified by a BXLE instruction may have been updated, but the instruction address in the current PSW still points to the beginning of the instruction; or, during the execution of a LPSW instruction, only a portion of the current PSW may have been replaced. As a result, the model may have some choice as to which point in the recovery cycle the interruption is taken, and in some cases, the status which can be indicated as valid depends on the point chosen.

The point during processing at which an error occurs is called the point of error. The point in the processing that is used as a reference point by the machine to determine and indicate the validity of the status stored when the machinecheck interruption occurs is called the point of interruption.

Only certain points in the processing may be used as a point of interruption. For soft machine-check conditions, the point of interruption does not precede the point of error; the point of interruption must be after one instruction is completed, including the associated program or SVC interruption, if applicable, and before the next instruction is begun. It may also be at one of the interruption points of an interruptible instruction. In some cases, the point of interruption may be several instructions past the point of error.

Hard machine-check conditions that are delayed (disallowed and presented later when allowed) can occur only at the same points of interruption as soft machine-check conditions. When hard machine-check conditions are not delayed, the point of interruption may occur at two additional places:

- 1. The interruption point immediately preceding the point of error. In this case, a special bit, called the backup bit, is set in the interruption code to indicate that the status reflects a state prior to the error. When the backup bit is one and all status is indicated as valid, the machine has successfully returned to a point prior to the error, and no additional damage has occurred. This situation is indicated as damage condition rather than system recovery because the malfunction has not been circumvented and damage would have occurred if the process had continued.

- 2. The point after the instruction is completed but before the associated program or SVC interruption occurs. In this case, a valid PSW is defined as that which would have been stored in the old PSW for the program or SVC interruption. Even though all status may be indicated as valid, damage has occurred because the associated interruption is lost.

When a hard machine-check condition occurs, the point of interruption that is chosen affects the amount of damage that must be indicated. An attempt is made, when possible, to minimize the damage that must be indicated. In general, the order of preference is in the sequence beginning at the interruption point immediately preceding the point of error. When a point of interruption must be chosen, which is after an associated program or SVC interruption, the damage cannot be isolated to the point prior to the program or SVC interruption, and system damage must be indicated. When the status information stored as a result of a hard machine-check condition does not all reflect the same logical point, an attempt is made when possible to choose the point of interruption so as to make the instruction address which is stored in the machine-check old PSW valid.

## CHECK STOP STATE

When the CPU is in the check stop state, the condition is appropriately indicated by an error light and/or audible signal. The exact indication is model-dependent. The system light is off, and the state of the manual light depends on the model.

The machine enters the check stop state only as the result of machine malfunction. The machine may be removed from the check stop state by system reset or IPL.

When the CPU is in the check stop state, instructions and interruptions are not executed. The timer is not updated, and channel operations may be suspended. The CPU cluster meter does not run, and the clock-out and metering-out lines are down. The stop key and start key are not operative during this state.

## MACHINE-CHECK LOGOUT

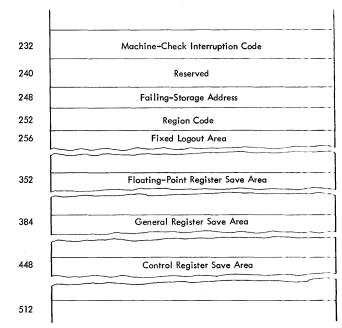

The storing of model-dependent information into main storage as a result of, or in association with, a machine error is called a machine-check logout. When a machine-check logout occurs during the machine-check interruption it is called synchronous. If a machine-check logout occurs without a machine-check interruption, or if the logout and the interruption are separated by instruction processing or by instruction retry, then the logout is called asynchronous. Machine-check logout can occur in either of two areas. The 96-byte area, starting at location 256, is called the fixed-logout area. In addition, a machine-check extendedlogout area (MCEL) is defined. The starting location of the MCEL area is specified by the contents of control register 15. The length of the MCEL area depends on the model.

To preserve the initial machine error conditions, some models perform an asynchronous logout before invoking automatic CPU recovery action. In some models the diagnostic information is either stored before recovery or afterwards, but not at both times. On other models both may occur either into the same portion of the logout area or into different portions.

Machine-check logouts are referred to as four different types: synchronous fixed logout (SFL), asynchronous fixed logout (AFL), synchronous machine-check extended logout (SMCEL), and asychronous machine-check extended logout (AMCEL).

## MACHINE-CHECK CONTROL REGISTERS

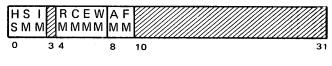

Control register 14 contains mask bits which specify whether certain conditions can cause machine-check interruptions, and it also contains mask bits to control the conditions under which a logout may occur. Bits 3 and 10-31 are reserved.

#### Control Register 14

#### Hard Stop

Hard Stop (HS): Bit 0 of control register 14 controls the system action taken when a hard machine-check condition occurs during a hard machine-check interruption or with PSW bit 13 zero. If the hard stop bit is one, the machine enters the check stop state; if the hard stop bit is zero, the machine may attempt to continue or may enter the check stop state, depending on the type of error and the model. The hard stop bit is set to one by system reset. If damage occurs to control register 14 the hard stop bit is assumed to be one.

#### **Extended Logout Masks**

Synchronous Machine-Check Extended Logout Mask (SM): Bit 1 of control register 14 controls the logout action during a machine-check interruption. If the bit is one, the machine-check extended logout area may be changed during the interruption; if the bit is zero, the area may be changed only under control of the asynchronous machinecheck extended logout mask bit (bit 8 of control register 14). Bit 1 of control register 14 is set to one by system reset.

Input/Output Extended Logout Mask (IM): Bit 2 of control register 14, when one, permits the channel to log out into the I/O extended logout area as part of an I/O interruption. When the I/O extended logout mask is zero, I/O extended logouts cannot occur. This bit is set to zero by system reset.

Asynchronous Machine-Check Logout Mask (AM): Bit 8 of control register 14, in conjunction with PSW bit 13, controls asynchronous change of the machine-check extended logout area. When this bit and PSW bit 13 are both one, the machine may change the machine-check extended logout area at any time. This bit is set to zero by system reset.

**Programming Note:** The maximum logout information is obtained by setting both the synchronous and asynchronous machine-check extended logout mask bits to one. Both of these bits must be zero to prevent any changes to

the machine-check extended logout area. When AMCEL is allowed, use of the MCEL area for other than logout may produce unpredictable results.

Asynchronous Fixed Logout Mask (FM): Bit 9 of control register 14, when one, permits the fixed logout area to be changed at any time. When this bit is zero, the fixed logout area may be changed only during a machine-check interruption or during an I/O interruption. This bit is set to zero by system reset.

**Programming Note:** When the AFL mask bit is one, program use of the fixed logout area should be restricted to the fetching of data from this area. Store operations on channel programs reading into the fixed logout area may cause machine checks on undetected errors if the store occurs during CPU retry. Note that this is an exception to the rule that programming errors do not cause machine-check indications.

## **Machine-Check Subclass Masks**

Bits 4–7 of control register 14, in conjunction with PSW bit 13, control various machine-check subclass conditions. When PSW bit 13 is one and the subclass mask is one, the associated condition initiates a machine-check interruption. If the subclass mask is zero, the associated condition does not initiate an interruption, but the condition may be presented with another condition which initiates the interruption. All conditions presented are then cleared.

Recovery Report Mask (RM): Bit 4 of control register 14 controls recovery conditions. This bit is set to zero by system reset.

Configuration Report Mask (CM): Bit 5 of control register 14 controls automatic configuration conditions. This bit is set to zero by system reset.

External Damage Report Mask (EM): Bit 6 of control register 14 controls the following machine-check conditions: timer damage, time-of-day clock damage, and external damage. This bit is set to one by system reset.

Warning Mask (WM): Bit 7 of control register 14 controls all warning conditions. This bit is set to zero by system reset.

## Summary of Machine-Check Masking

Machine-check masking is summarized in Figures 2, 3, and 4.

| Subclass Condition |                                 | Mask        | Action when CPU<br>Disabled for<br>Subclass Condition |                                       |  |

|--------------------|---------------------------------|-------------|-------------------------------------------------------|---------------------------------------|--|

|                    |                                 |             | Hard Stop<br>Bit = 0                                  | Hard Stop<br>Bit = 1                  |  |

| SD                 | System Damage                   | 13          | P*                                                    | Check Stop                            |  |

| PD                 | Instruction Processing Damage   | 13          | P*                                                    | Check Stop                            |  |

| TP                 | Timer Damage                    | 13 and EM   | P*                                                    | P*                                    |  |

| CD                 | Time–of–Day Clock Damage        | 13 and EM   | P*                                                    | P*                                    |  |

| SR                 | System Recovery                 | 13 and RM   | D                                                     | D                                     |  |

| ED External Damage |                                 | 13 and EM   | P*                                                    | P*                                    |  |

| AC                 | Automatic Configuration         | 13 and CM   | Р                                                     | Р                                     |  |

| w                  | Warning                         | 13 and WM   | Р                                                     | Р                                     |  |

| Act                | ion Code Definition             |             |                                                       | · · · · · · · · · · · · · · · · · · · |  |

| F                  | Indication held pending.        |             |                                                       |                                       |  |

| 1                  | D Indication may be held pendin | g or may be | discarded.                                            |                                       |  |

| Ľ                  | System integrity is undependat  | le.         |                                                       | -                                     |  |

Figure 2. Machine-Check Condition Masking

| PSW<br>Bit 13                                                                                 | SMCEL<br>Mask                                                                                                                        | AMCEL<br>Mask       | Machine-Check Extended Logout Action             |  |  |  |

|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------------------------------------------|--|--|--|

| 0                                                                                             | х                                                                                                                                    | X                   | No MCEL                                          |  |  |  |

| ר                                                                                             | 0                                                                                                                                    | 0                   | No MCEL                                          |  |  |  |

| 1                                                                                             | 1                                                                                                                                    | 0                   | MCEL may occur only during                       |  |  |  |

| [                                                                                             | [                                                                                                                                    |                     | machine-check interruption.*                     |  |  |  |

| 1                                                                                             | 0                                                                                                                                    | 1                   | MCEL may occur at any time.**                    |  |  |  |

| 1                                                                                             | 1                                                                                                                                    | 1                   | MCEL may occur at any time.                      |  |  |  |

| AFL Ma                                                                                        | sk                                                                                                                                   | Fixed Logout Action |                                                  |  |  |  |

| 0 CPU portion of fixed logout area may be changed<br>only during machine-check interruption.* |                                                                                                                                      |                     |                                                  |  |  |  |

| Any portion of fixed logout area may be changed<br>at any time.                               |                                                                                                                                      |                     |                                                  |  |  |  |

| Notes:                                                                                        |                                                                                                                                      |                     |                                                  |  |  |  |

| X Indicates the same action occurs whether the bit is zero or one.                            |                                                                                                                                      |                     |                                                  |  |  |  |

| *                                                                                             | <ul> <li>Logout prior to instruction retry is not permissible in this<br/>state even though recovery reports are allowed.</li> </ul> |                     |                                                  |  |  |  |

| **                                                                                            |                                                                                                                                      |                     | he AMCEL mask bit is ignored, and no this state. |  |  |  |

Figure 3. Machine-Check Logout Masking

|    | Bit Description                | Control<br>Register 14<br>Bit Position | State of Bit'<br>on<br>System Reset |

|----|--------------------------------|----------------------------------------|-------------------------------------|

| нs | Hard Stop                      | 0                                      | 1                                   |

| SM | Synchronous MCEL Mask          | 1                                      | 1                                   |

| IM | IOEL Mask                      | 2                                      | 0                                   |

| RM | Recovery Report Mask           | 4                                      | 0                                   |

| СМ | Configuration Report Mask      | 5                                      | 0                                   |

| EM | External Damage Report Mask    | 6                                      | 1                                   |

| WM | Warning Mask                   | 7                                      | 0                                   |

| AM | Asynchronous MCEL Mask         | 8                                      | 0                                   |

| FM | Asynchronous Fixed Logout Mask | 9                                      | 0                                   |

Figure 4. Machine-Check Control Register Bits

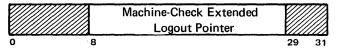

#### Machine-Check Extended Logout Pointer

Control Register 15

Bits 8-28 of control register 15, with three low-order zeros appended, specify the starting location of the machinecheck extended logout area. Bits 0-7 and 29-31 are reserved. The contents of control register 15 are set to 512 (decimal) by system reset.

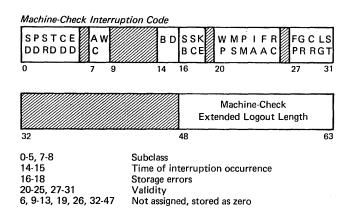

#### INTERRUPTION ACTION

A machine-check interruption causes the PSW reflecting the point of interruption to be stored as the old PSW at location 48; extended machine-check interruption information is stored, consisting of the information in all the control registers, general registers, and floating-point registers, a region code, and a failing storage address. Then the machine-check interruption code (MCIC) of eight bytes is stored. A new PSW is fetched from location 112. Additionally, sometime before the storing of the machinecheck interruption code, one or several machine-check logouts may have occurred. If the machine-check interruption code cannot be stored successfully or the new PSW cannot be fetched successfully, the CPU enters the check stop state if the hard stop bit is one.

A machine-check interruption due to a soft machinecheck condition can occur only when both PSW bit 13 and the associated subclass mask are one. A soft machine-check interruption does not terminate the execution of the current instruction; the interruption is taken after the execution of the current instruction has come to its normal ending and after the associated program or supervisor-call interruption, if any, has been taken. No program or supervisor-call interruptions are eliminated. When the soft machine-check condition occurs during the execution of a system function, such as a timer update, the machine-check interruption takes place after the system function has been completed.

A machine-check interruption due to a hard machinecheck condition can occur only when the machine-check mask, PSW bit 13, is one. The interruption terminates the execution of the current instruction and may eliminate the program and supervisor-call interruptions, if any, that would have occurred as a result of the instruction. Proper execution of the steps, including the storing of the old PSW and diagnostic information, depends on the nature of the malfunction. When a hard machine-check condition occurs during the execution of a system function, such as a timer update, the sequence is not necessarily completed.

When PSW bit 13 is zero and a hard machine-check condition is generated, subsequent action depends on the state of the hard stop bit, bit 0 of control register 14. When the hard stop bit is zero, the machine-check condition is held pending, and an attempt is made to complete the execution of the current instruction and to proceed with the next sequential instruction. It should be noted that operation in this mode may result in loss of system integrity. When the hard stop bit is one, processing stops immediately, and the CPU enters the check stop state. Depending on the model and type of error, the CPU may enter the check stop state even when the hard stop bit is set to zero.