GA33-3005-1

## **Systems**

# IBM System/370 Model 135 Functional Characteristics

## **Systems**

## IBM System/370 Model 135 Functional Characteristics

This publication describes the capabilities, features, input/output channels, integrated adapters, and operations of the IBM System/370 Model 135. The information includes the relationship of System/370 Model 135 to the IBM System/360.

The publication is intended for users and potential users (such as systems analysts and programmers) of the System/370 Model 135. The reader is assumed to have a working knowledge of *IBM System/360 Principles of Operation*, GA22-6821, *IBM System/370 Principles of Operation*, GA22-7000, and *IBM System/370 System Summary*, GA22-7001.

## First Edition (March, 1971)

Changes are periodically made to the information herein; before using this publication in connection with the operation of IBM systems, refer to the latest System Library Newsletter, *Accumulative Index of Publications and Programs*, GN20-0360, for the editions that are applicable and current.

.

Requests for copies of IBM publications should be made to your IBM representative or to the IBM branch office serving your locality.

A form for readers' comments is provided at the back of this publication. If the form has been removed, comments may be addressed to IBM United Kingdom Laboratories Ltd., Product Publications, Hursley Park, Winchester, Hants, England. Comments become the property of IBM and will be sent to the author for appropriate action.

© Copyright International Business Machines Corporation 1971

This publication is intended for users and potential users, such as systems analysts and programmers, of the IBM System/370 Model 135 who require information about the capabilities, features, input/output channels, integrated adapters, and operations of this system. The reader is assumed to have a working knowledge of *IBM System/360* Principles of Operation, GA22-6821, *IBM System/370* Principles of Operation, GA22-7000, and *IBM System/370* System Summary, GA22-7001.

In "Introduction", the relationship between System/370 Model 135 and the IBM System/360 is shown, with emphasis on the Model 135 as providing extensions of the System/360 facilities. In "System Structure and Operation", the Model 135 is described in terms of its basic concept, the principal functions, and its units. "CPU Characteristics" and "Input/Output Characteristics" give detailed information on the standard features and optional features of the processing unit, input/output channels, and integrated adapters. These feature descriptions, although principally defining the Model 135, also directly relate the system to System/360 in terms of extended and/or compatible facilities.

Appendix A defines the abbreviations and special terms used in this publication. Appendix B details the Model 135 instruction timings.

#### **Associated Publications**

The following publications are referred to in this manual:

- 1. IBM System/360 Principles of Operation, GA22-6821 (see Note).

- 2. IBM System/360 DOS Program Planning Guide for MCAR/CCH Function for IBM System/370 Model 135, GC24-5089.

- 3. IBM System/360 OS Program Planning Guide for the DOS Emulator on IBM System/370, Models 135, 145, and 155, GC24-5076.

- 4. IBM System/360 Component Descriptions 2314 Direct Access Storage Facility and 2844 Auxiliary Storage Control, GA26-3599.

- 5. IBM System/370 Principles of Operation, GA22-7000 (see Note).

- 6. IBM System/370 System Summary, GA22-7001.

- 7. IBM System/370 Input/Output Configurator, GA22-7002.

- 8. IBM System/370 Model 135 Configurator (U.S.A. only), GA33-3006.

- 9. IBM System/370 Model 135 Configurator (Countries other than U.S.A.), GA19-0044.

- 10. IBM 2701 Data Adapter Unit Principles of Operation, GA22-6864.

- 11. IBM 2701 Data Adapter Unit Original Equipment Manufacturers' Information, GA22-6844.

- 12. IBM 2703 Transmission Control Component Description, GA27-2703.

- 13. Emulating the IBM 1401, 1440, and 1460 on the IBM System/370 Models 135 using DOS/360, GC33-2004.

- Emulating the IBM 1401, 1440, and 1460 on the IBM System/370 Models 135, 145, and 155 using OS/360, GC27-6945.

- 15. General Information Binary Synchronous Communications, GA27-3004.

*Note:* Manuals GA22-6821 and GA22-7000 are referred to jointly in the text as "the Principles of Operation manuals".

The titles of other publications that may help the reader are given in *IBM System/360 and System/370 Bibliography*, GA22-6822 and its associated newsletter *Accumulative Index of Publications and Programs*, GN20-0360.

## Contents

| Introduction                                                              |       | •     | •    |      | •  | •   | •   | •   | •    | • | • | • | 1  |

|---------------------------------------------------------------------------|-------|-------|------|------|----|-----|-----|-----|------|---|---|---|----|

| Performance Characteristics                                               |       |       |      |      |    |     |     | •   |      |   |   |   | 1  |

| CPU Main Storage Capacity                                                 |       |       |      |      |    |     |     |     |      |   |   |   |    |

| System Features                                                           |       |       |      |      |    | •   |     |     |      |   |   |   | 1  |

| Selective Features .                                                      |       |       |      |      |    |     |     |     |      |   | • |   | 1  |

| Standard Features .                                                       |       |       |      |      |    |     |     |     |      | • |   |   | 1  |

| Standard Features<br>Optional Features .                                  |       |       |      |      |    |     |     |     |      |   |   |   | 2  |

| Compatibility Features                                                    |       |       |      |      |    |     |     |     |      |   |   |   | 2  |

| Compatibility Features<br>System/360 Program Comp                         | atib  | oilit | v    |      |    |     |     |     | •    |   |   |   | 2  |

| System Residence and Main                                                 | ten   | anc   | e St | tora | ge | Rec | uir | eme | ents |   |   |   | 2  |

|                                                                           |       |       |      |      |    |     |     |     |      |   |   |   |    |

| System Structure and Operation                                            | atio  | n.    |      |      |    |     |     |     |      |   |   |   | 3  |

| Data Flow                                                                 |       |       |      |      |    |     |     |     |      |   |   |   |    |

| Console File                                                              | •     | •     | •    | •    | •  | •   | •   | •   | •    | • | • | • | 4  |

| Console File                                                              | dina  |       | •    | •    | •  | •   |     | •   | •    | • | · | • | 4  |

| Main Storage                                                              | TITIE |       | •    | •    | •  | •   |     |     |      | • | · |   | 4  |

| Main Storage<br>Permanently Assigned Are                                  | •     | •     | •    | •    | •  | •   | •   | •   | •    | • | • | : |    |

| Control Storage                                                           | cas   |       | •    | •    | •  | •   | •   | •   | •    | • | • |   | •  |

| Control Storage                                                           | •     | •     | •    | •    | •  |     |     | •   | •    | • | • | · |    |

| Access                                                                    |       |       |      |      | •  | •   | •   | •   | •    | • | • | · |    |

|                                                                           |       |       | •    |      | •  | •   | •   | •   | •    | • | • | · |    |

| Work Storage                                                              | •     | •     | •    | •    | •  |     |     | •   | •    | • | · |   |    |

| Zone Allocation                                                           |       |       |      | •    |    |     | •   | •   | •    | · | · | · | •  |

| Priority Allocation .                                                     | •     | •     | •    | •    | •  | •   |     | •   |      | • | • |   | -  |

| Auxiliary Storage<br>Arithmetic and Logic Unit<br>Input/Output Facilities | •     | •     | •    | •    | •  | ·   |     | •   |      |   | • | · |    |

| Arithmetic and Logic Unit                                                 |       | •     | •    | •    | •  | •   |     | •   |      |   | • |   |    |

| Input/Output Facilities                                                   | •     | •     | •    | •    | •  | •   |     | •   |      | • | • |   |    |

| Internal I/O Interface                                                    | •     | •     |      | •    | •  | •   |     |     | •    | • | · | • |    |

| Integrated I/O Adapters                                                   | •     | •     | •    | •    | •  | •   |     | •   |      |   | · |   |    |

| Channels                                                                  | •     | •     | •    | •    | •  | •   | ·   | •   | •    | • | • | • | 7  |

|                                                                           |       |       |      |      |    |     |     |     |      |   |   |   |    |

| CPU Characteristics                                                       |       |       |      |      |    | •   | •   | •   | •    | • | • | • | 9  |

| Instruction Sets<br>Basic Instruction Set .                               |       | •     | •    | •    |    | •   |     |     | •    |   | • |   |    |

| Basic Instruction Set .                                                   | •     |       |      | •    | •  | •   | •   | •   |      |   |   |   |    |

| Floating-Point Arithmetic                                                 | :     |       |      | •    | •  | •   | •   | •   | •    | • |   |   | 10 |

| CPU Facilities<br>Byte-Oriented Operands                                  |       |       |      | •    |    |     |     |     |      |   |   |   |    |

| Byte-Oriented Operands                                                    |       |       | •    | •    |    |     |     |     |      |   |   |   | 10 |

| Storage Protection .                                                      |       |       |      | •    |    |     |     |     |      |   |   |   | 10 |

| Storage Protection .<br>Time-of-Day Clock .                               |       |       | •    | •    | •  | •   |     |     |      | • |   |   | 11 |

| Interval Timer                                                            |       |       |      | •    | •  |     |     | •   | •    |   |   |   | 11 |

| CPU Identification .                                                      |       |       | •    |      |    |     |     |     |      |   |   |   | 11 |

| Channel Identification                                                    |       |       |      |      | •  |     |     |     |      |   |   |   |    |

| Direct Control and Extern                                                 |       |       |      |      |    |     |     |     |      |   |   |   |    |

| System Control                                                            |       |       |      |      |    |     |     |     |      |   |   |   | 11 |

| System Control<br>Control Registers                                       |       |       |      |      |    |     |     |     |      |   |   |   | 11 |

| Machine-Check Handling                                                    |       |       |      |      |    |     |     |     |      |   |   |   | 12 |

|                                                                           |       |       |      |      |    |     |     |     |      |   |   |   |    |

| Input/Output Characteristic                         | s            | •         | •      | •       | •    | •         | •    | •   | •    | • | • | • | 15 |

|-----------------------------------------------------|--------------|-----------|--------|---------|------|-----------|------|-----|------|---|---|---|----|

| CHANNEL FACILITIES .                                |              |           |        |         |      |           |      |     |      |   |   |   |    |

| Byte-Multiplexer Channel                            |              |           |        |         |      |           |      |     |      |   |   |   |    |

| Mode of Operation .                                 |              |           |        |         |      |           |      |     |      |   |   |   |    |

| Error Handling                                      |              |           |        |         |      |           |      |     |      |   |   |   | 16 |

| Interruption Handling                               |              |           |        |         |      |           |      |     |      |   |   |   | 17 |

| Subchannels                                         |              |           |        |         |      |           |      |     |      |   |   |   | 17 |

| Subchannels                                         |              |           |        |         |      |           |      |     |      |   |   |   | 19 |

| Mode of Operation .                                 |              |           |        |         |      |           |      |     |      |   |   |   | 19 |

| Mode of Operation                                   |              |           |        |         |      |           |      |     |      |   |   |   | 19 |

| Direct Access Storage Dev                           | ice          | s oi      | n Se   | elec    | tor  | Cha       | nne  | els |      | • |   |   | 21 |

| Block Multiplexing                                  |              |           |        |         |      |           |      |     |      |   |   |   | 21 |

| Block Multiplexing<br>Device Addressing .           |              |           |        |         |      |           |      |     |      |   |   |   | 22 |

| Channel-Available Interru                           | ptie         | on (      | Con    | diti    | ion  |           |      |     |      |   |   |   | 22 |

| Standard I/O Interface .                            |              |           |        |         |      |           |      |     |      |   |   |   | 22 |

| Console Printer-Keyboard                            |              |           |        |         |      |           |      |     |      |   |   | ÷ | 22 |

| Printer-Keyboard Comma                              | nđ           | Wo        | rds    | •       |      |           |      |     |      |   |   | Ż | 25 |

| Printer-Keyboard Comma<br>Unit Status Byte          |              |           |        |         |      |           |      |     |      |   |   | ÷ | 26 |

| Channel Status Byte .                               |              | •         |        |         |      |           |      |     |      |   |   |   | 27 |

| Sense Ryte                                          | •            | •         | ·      | •       | •    | •         | •    | •   | •    |   | • | • | 27 |

| Sense Byte                                          | •            | •         | •      | ·       | •    | •         | •    | •   | •    | • | • | • | 27 |

| Restart Procedure .                                 | •            | •         | •      | •       | •    | •         | •    | •   | •    | • | • | • | 29 |

| INTEGRATED ADAPTERS                                 | 2            | •         | •      | •       | •    | •         | •    | •   | •    | • | • | · | 30 |

| Integrated Communications                           | , <b>.</b> . | tan       | tor    | •       | •    | •         | •    | •   | •    | • | • | • | 30 |

| Integrated Communications<br>Types of Communication | Tii          | nap<br>no | lei    | ·       | •    | •         | •    | •   | ·    | • | • | • | 30 |

| Operation                                           | LII          | le        | •      | •       | •    | •         | •    | •   | •    | · | • | • | 21 |

| Operation                                           |              |           | •<br>• | •<br>(E | •    | •<br>•1~~ |      | •   | •    | • | • | • | 21 |

| Terminal Adapter Type I<br>Terminal Adapter Type II | MO           |           | 11     | Eq      |      | uen       | () F | eat | ure  |   | • | • | 22 |

| Terminal Adapter Type II                            | 1 (1         | Equ       | uva    | ient    | ) F  |           | ire  |     | •    | • | • | • | 32 |

| Synchronous Data Adapte                             |              |           |        |         |      |           |      |     |      |   |   |   |    |

| Integrated File Adapter                             | •            | ·         | ·      | •       | •    | •         | •    | ·   | ·    | · | · | · | 33 |

| Mode of Operation and U                             |              |           |        |         |      |           |      |     |      |   |   |   |    |

| Control Commands .<br>Sense I/O Command (X'0        | •            | •         | ·      | ·       | ·    | •         | ·    | ·   | ·    | · | · | • | 35 |

| Sense I/O Command (X <sup>0</sup>                   | 4′)          |           | •      | •       | ·    | ·         | ·    | ·   | ·    | • | · | · | 39 |

| Read Commands                                       |              |           |        |         |      |           |      |     | ·    | • | • | · | 39 |

| Write Commands                                      |              |           |        |         |      | ·         |      |     | ·    | • | • | • | 39 |

| Search Commands .                                   | •            | •         | ·      | ·       | ·    | •         | •    | ·   | ·    | • | · | • | 40 |

| Addressing                                          | •            | •         | •      | •       | •    | •         | ·    | ·   | ·    | • | · | ٠ | 40 |

| Addressing<br>Status Information .                  | •            | •         | •      | ·       | •    | •         | •    | •   | •    | · | • | • | 41 |

| Appendix A. Definitions                             |              |           |        |         |      |           |      |     |      |   |   |   |    |

|                                                     |              |           |        |         |      |           |      |     |      |   |   |   |    |

| Abbreviations<br>Glossary                           | •            | •         | ÷      | ÷       | ÷    | :         | ÷    | :   | :    | : | : | : | 43 |

|                                                     |              |           |        |         |      |           |      |     |      |   |   |   |    |

| Appendix B. System/370 N                            | loc          | iel       | 135    | In      | stru | ctic      | on I | imi | ings |   | • | • | 45 |

| Index                                               | •            |           |        |         |      | •         |      |     |      |   |   |   | 53 |

## Illustrations

v

| Figure   | Title                                                                                       | Page |

|----------|---------------------------------------------------------------------------------------------|------|

| Frontis- |                                                                                             |      |

| piece    | IBM System/370 Model 135                                                                    | . vi |

| 1        | CPU – Simplified Data Flow                                                                  | . 3  |

| 2        | Example of Microinstruction Timing                                                          | . 6  |

| 3        | System/370 Instruction Timing                                                               | . 9  |

| 4        | Byte-Multiplexer Channel – Data Rates and Times .                                           | . 16 |

| 5        | Byte-Multiplexer Subchannels – Availability and Allocation                                  | . 17 |

| 6        | Device Address Byte for Nonshared Byte-Multiplexer                                          |      |

|          | Subchannel (16 Subchannels in System)                                                       | . 18 |

| 7        | Device Address Byte for Nonshared Byte-Multiplexer<br>Subchannel (64 Subchannels in System) | . 18 |

| 8        | Device Address Byte for Shared Byte-Multiplexer                                             | . 10 |

| 0        | Subchannel                                                                                  | . 18 |

| 9        | Selector Channels – Data Rates and Response Times                                           | . 20 |

| 10       | IBM 3210 Console Printer-Keyboard Model 1                                                   | . 23 |

| 11       | IBM 3215 Console Printer-Keyboard Model 1                                                   | . 23 |

| 12       | 3210 and 3215 – Keys, Indicators, and Controls .                                            | . 24 |

| 13       | EBCDIC Graphic Codes                                                                        | . 25 |

| 14       | Console Printer-Keyboard – CCW Command Codes                                                | . 25 |

| 15       | Alter/Display Function Mnemonics                                                            | . 28 |

| 16       | Summary of Recommended Actions after Unit                                                   |      |

|          | Check from Console Printer-Keyboard                                                         | . 29 |

| 17       | Integrated File Adapter – Operational Commands                                              | . 36 |

*Note:* The illustrations in this manual have a code number to the right of the caption. This is a publishing control number and is unrelated to the subject matter.

The IBM System/370 comprises a series of compatible, general purpose data processing systems that are designed for teleprocessing as well as for commercial and scientific applications. The System/370 provides a successor range of models to the IBM System/360 that, in addition to incorporating the basic System/360 capabilities, provides many extensions and improvements.

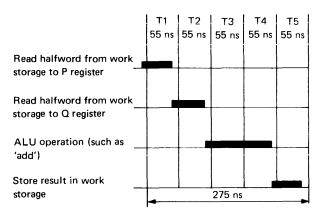

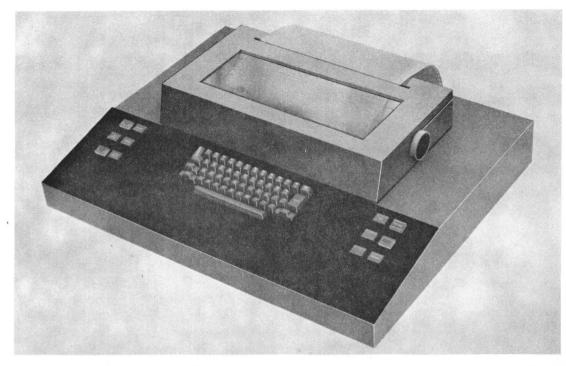

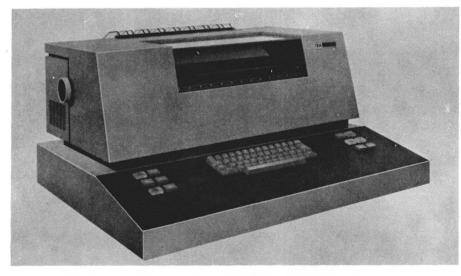

The System/370 Model 135 (see Frontispiece) presents to users of intermediate systems, such as the System/360 Models 25 and 30, a varied and comprehensive potential for expansion without the need for reprogramming. Most System/360-supported programs can be run on the Model 135.

## PERFORMANCE CHARACTERISTICS

Typical performance characteristics of the System/370 Model 135 are as follows:

Storage access width: Two bytes or four bytes. The control storage access width is two bytes; the main storage access width is two or four bytes, depending on the operation.

*Basic machine cycle time:* A minimum of 275 nanoseconds (ns), the actual time depending on the type of control instruction.

Storage cycle time: 660 ns for a cycle steal operation, 770 ns for a read operation, and 935 ns for a write operation. The cycle times for the read and write operations include the fetch time of the next microinstruction.

## **CPU MAIN STORAGE CAPACITY**

Various models of the IBM 3135 Processing Unit are available for the System/370 Model 135. These central processing units (CPU's) differ only in the size of main storage:

| Model of 3135 | Main Storage Size     |

|---------------|-----------------------|

| FE            | 98,304 (96K) bytes    |

| GD            | 147,456 (144K) bytes  |

| GF            | 196, 608 (192K) bytes |

| DH            | 245,760 (240K) bytes  |

|               |                       |

## SYSTEM FEATURES

The features of the System/370 Model 135 are classified as selective, standard, and optional.

#### Selective Features

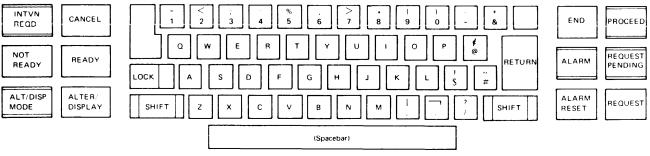

Either of the following console printer-keyboards can be chosen:

IBM 3210 Console Printer-Keyboard Model 1

IBM 3215 Console Printer-Keyboard Model 1.

## **Standard Features**

The standard features of the system represent the basic capability of any System/370 Model 135. They include:

- 1. System/360 standard features, including some improved functions.

- 2. Changes to System/360 standard features.

- 3. Various System/370 features.

## System/360 Features

The following features of the System/360 are incorporated in the standard features of the System/370 Model 135:

- 1. The System/360 Instruction Set, including decimal arithmetic.

- 2. All other definitions that are contained in the Principles of Operation manual\* (except those items shown under "Changes to System/360 Features"), including:

Byte-multiplexer channel

Byte-oriented operands

Interval timer

Storage protection (store and fetch).

3. Specific definition of the following functions (which, in the System/360, are permitted unpredictable operations), without affecting the operation of programs written for the System/360 when these are run on the System/370 Model 135:

Handling of invalid decimal sign

Protection exception in edit and edit-and-mark

operations

Imprecise interruptions.

## Changes to System/360 Features

One standard feature of the System/360 is redefined for use in the System/370 Model 135 and two standard features are omitted:

- 1. The 'halt I/O' instruction is modified so that the same operation code is also used by the 'halt device' instruction.

- 2. American National Standard Code for Information Interchange (ASCII) is omitted.

- 3. The multisystem operation mode is omitted.

<sup>\*</sup> IBM System/360 Principles of Operation, GA22-6821, and IBM System/370 Principles of Operation, GA22-7000.

## System/370 Features

The following features of the System/370 are included in the Model 135 standard features:

Control registers

Error recovery (machine-check handling)

Extended external masking

Limited channel logout (extended channel status word)

OS/DOS compatibility

System/370 Commercial Instruction Set

Time-of-day clock.

## **Optional Features**

The optional features of the Model 135 are as follows:

Block multiplexing

Direct control

Expanded control storage (36,864 bytes or 49,152 bytes, depending on other features required)

Extended-precision floating point

First selector channel

First and second selector channels

Floating point

Integrated communications adapter (ICA)

Integrated file adapter (IFA)

1401/1440/1460 compatibility.

## **Compatibility Features**

## **OS/DOS** Compatibility

The OS/DOS compatibility feature allows a Disk Operating System (DOS) emulator program to run under Operating System (OS) with MFT\*. The DOS emulator program in turn allows System/360 programs that were written for a DOS system to be run in the OS job stream on the System/370 Model 135. For further details, refer to *IBM System/360 OS – Program Planning Guide for the DOS Emulator on IBM System/370, Models 135, 145, and 155,* GC24-5076.

## 1401/1440/1460 Compatibility

The 1401/1440/1460 compatibility feature enables certain operations associated with the IBM 1401, 1440, and 1460 Data Processing Systems to be executed. This compatibility feature allows an emulator program to emulate one of the three systems. For further details, refer to *Emulating the IBM 1401, 1440, and 1460 on the IBM System/370 Models 135, 145, and 155 using DOS/360, GC33-2004, and Emulating the IBM 1401, 1440, and 1460 on the IBM System/370 Models 135, 145, and 155 using OS/360, GC27-6945.*

#### SYSTEM/360 PROGRAM COMPATIBILITY

All programs that are written for a System/360 (Model 25 and above) operate on a System/370 Model 135 that has a comparable hardware configuration, except for the following programs:

- 1. Time-dependent programs.

- 2. Programs written deliberately to cause program checks.

- 3. Programs using machine-dependent data, such as machine logs.

- 4. Programs using the ASCII mode (program status word [PSW] bit 12).

- 5. Programs that depend upon the reserved lower storage area being smaller than 512 bytes.

- 6. Programs that depend upon devices or architecture not available in System/370 (such as the single disk storage file of the System/360 Model 44).

- 7. Programs that depend upon the validity of storage data after the system power supply has been turned off and restored.

The System/370 Model 135 is not necessarily compatible with any model of System/360 for those functions that are specified as model-dependent in *IBM System/360 Principles* of Operation, GA22-6821.

*Note:* Programs written for System/360 can be run initially in the stop-after-log mode in order to facilitate error recording.

## SYSTEM RESIDENCE AND MAINTENANCE STORAGE REQUIREMENTS

The optimum performance and maximum availability of the System/370 Model 135 are maintained when a diskstorage facility is provided for residence of the operating system and the application-program files, for the storage of diagnostic tests, and for the storage of error-logout information. In this manual, these residence and storage requirements are assumed to be contained either in an IBM 2319 Disk Storage Model A1 (attached through the integrated file adapter feature) or in a similar disk-storage device (attached through a selector channel). The user has the following options:

- 1. Using the IFA with a 2319 Disk Storage.

- 2. Using a selector channel or block-multiplexer channel with a disk-storage device. (In this manual, a selector channel or block-multiplexer channel with a 2314-type direct access storage facility is assumed.)

- 3. Electing not to use the associated Recovery Management Support package described in the *IBM System/360* DOS – Program Planning Guide for MCAR/CCH Function for IBM System/370 Model 135, GC24-5089.

<sup>\*</sup> MFT: Multiprogramming with a fixed number of tasks

The operation of the System/370 Model 135 depends on the microprogram-controlled 3135 Processing Unit, which has the following functions:

- 1. To execute the instructions of the system.

- 2. To provide channel and control unit functions for various input/output (I/O) devices that are integrated adapters.

- 3. To control the operation of System/370 channels.

The CPU performs these operations by means of the following principal units and functions which, together, constitute the basic structure of the system:

Console file Main storage Control storage Work storage Auxiliary storage Arithmetic and logic unit (ALU) Input/output facilities.

The principal power supply for the CPU is obtained from a motor-generator frequency-converter set, the IBM 3046 Power Unit Model 1. This power unit converts the mainline power supply frequency (50 hertz or 60 hertz, depending on the country of installation) to a frequency of about 400 hertz. The power unit also protects the CPU power supplies from mainline power supply disturbances.

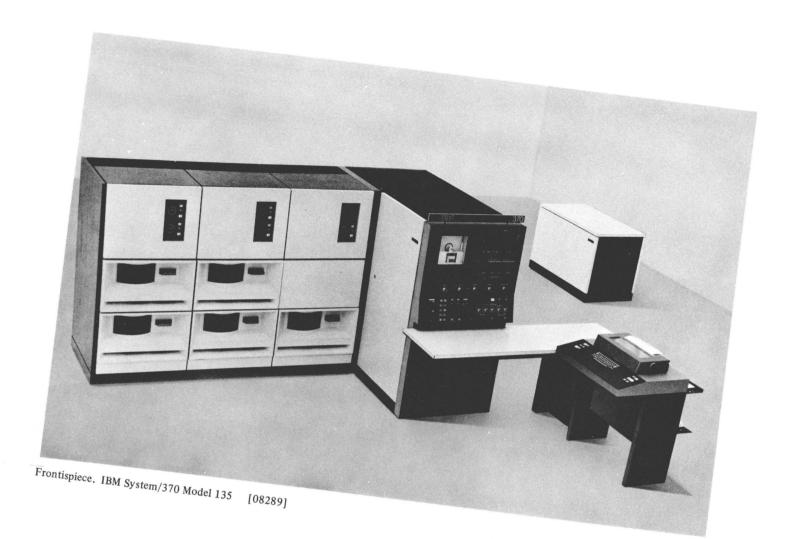

#### DATA FLOW

A concept of the System/370 Model 135 operation is provided by the simplified data flow of the CPU (Figure 1). Microinstructions from the console file are loaded into control storage during the initial microprogram load (IMPL) procedure. Control word data from control storage is entered directly into a control data register, and one control word is fetched for each machine cycle. For sequential microinstruction fetching, the contents of a backup address register are transferred to a storage address register through an incrementer; the information is then returned to the backup address register, ready for the next machine cycle.

Data transfer operations to or from both main storage and control storage are controlled by the microprogram,

Figure 1. CPU – Simplified Data Flow [08290]

with the work storage being used as a source or destination for the data. For access to main storage data, a 24-bit address is transferred from work storage into the storage address register.

Note: Control storage is not available to the programmer.

Data is transferred between main storage and the I/O interface or between control storage and the I/O interface along a work storage bus.

## CONSOLE FILE

The console file is a read-only, single-drive disk storage unit that provides all the microcode which is loaded into control storage during the IMPL procedure. Four disks are supplied with the console file:

- 1. An initial microprogram disk, which carries a bootstrap loader routine, initial microdiagnostic routines, and the microprogram (particular to the system features installed) that is required for System/370 operation.

- 2. A device diagnostic program disk, which carries the microprogram for checking the CPU and the timing of mechanical actions within the integrated I/O attachments; this disk is for use by maintenance engineers only.

- 3. Two automatic system checkout program (ASCP) disks, which provide a stand-alone program that tests and reports on the reliability of the CPU, I/O channels, and integrated adapters. This program does not overwrite control storage; a second IMPL procedure is therefore not necessary after using this program.

#### Initial Microprogram Loading

Initial microprogram loading occurs automatically when system power is applied or when the START CONSOLE FILE pushbutton (on the system control panel of the 3135) is pressed. In either case, the IMPL indicator comes on and power is applied to the console file. When the console file attains operating speed, disk reading starts and microcode is loaded from the console file into control storage under control of the bootstrap loader routine.

During the initial stages of the IMPL procedure, microprogram checkout routines are performed before the microprogram is loaded into control storage. When the checkout routines have been successfully executed, the error checking and correction (ECC) mode is changed by microprogram to a mode in which all correctable storage errors on data-fetch cycles cause an error condition. This new mode permits a storage-mapping microdiagnostic program to be executed, which determines the location of single-bit errors in storage.

The functional microprogram is then loaded into control storage. When loading is completed, power to the console file is turned off and the system reset microprogram is executed. After system reset, the IMPL indicator goes off and the CPU stops until an external action, such as initial program load, is taken.

#### **MAIN STORAGE**

The main storage consists of monolithic storage cells. Its size depends on the model of 3135 in the system (see "CPU Main Storage Capacity"). The storage cycle time is the same for each size of main storage.

A storage data word of 72 bits is used, of which 64 bits (one doubleword) are data bits and eight bits are check bits. The check-bit code enables any single-bit error to be detected and corrected automatically. This error checking and correction code also allows double errors and some multiple errors to be detected.

The ECC logic, located separately from the storage logic, handles both main storage errors and control storage errors.

#### **Permanently Assigned Areas**

In the System/370 Model 135, program-storage addressing begins at location 0 and continues upward through the highest installed program-storage byte location. To ensure compatibility between System/370 models and System/360 models, however, fixed program-storage allocations (that is, permanently-assigned main storage areas) for all configurations of the System/370 Model 135 are as follows:

| Word A  | 4ddress | Length   | Purpose/Function                                    |

|---------|---------|----------|-----------------------------------------------------|

| Decimal | Hex     |          |                                                     |

| 0       | 00      | 2 words  | Initial program-loading PSW and Restart New PSW     |

| 8       | 08      | 2 words  | Initial program-loading<br>CCW1 and Restart Old PSW |

| 16      | 10      | 2 words  | Initial program-loading CCW2                        |

| 24      | 18      | 2 words  | External old PSW                                    |

| 32      | 20      | 2 words  | Supervisor-call old PSW                             |

| 40      | 28      | 2 words  | Program old PSW                                     |

| 48      | 30      | 2 words  | Machine-check old PSW                               |

| 56      | 38      | 2 words  | Input/output old PSW                                |

| 64      | 40      | 2 words  | Channel status word                                 |

| 72      | 48      | 1 word   | Channel address word                                |

| 76      | 4C      | 1 word   | -                                                   |

| 80      | 50      | 1 word   | Timer                                               |

| 84      | 54      | 1 word   | -                                                   |

| 88      | 58      | 2 words  | External new PSW                                    |

| 96      | 60      | 2 words  | Supervisor-call new PSW                             |

| 104     | 68      | 2 words  | Program new PSW                                     |

| 112     | 70      | 2 words  | Machine-check new PSW                               |

| 120     | 78      | 2 words  | Input/output new PSW                                |

| 128     | 80      | 8 words  | (Reserved)                                          |

| 160     | A0      | 8 words  | I/O communications area                             |

| 192     | C0      | 10 words | (Reserved)                                          |

| 232     | E8      | 2 words  | Machine-check interruption code                     |

| 240     | F0      | 2 words  | (Reserved)                                          |

| 248-512 | F8-200  | 66 words | Diagnostic logout area                              |

All remaining byte locations of main storage are available for programming functions.

#### CONTROL STORAGE

The basic control storage consists of 24,576 bytes of monolithic storage. The unit functions as a read/write control storage and accommodates the microcode for controlling all standard features of the system as well as the following features:

Direct control First selector channel First and second selector channel Floating-point arithmetic Integrated file adapter 3210-1 adapter.

The basic control storage can be expanded by two increments of 12,288 bytes to a capacity of 49,152 bytes, according to the feature-configuration of the system.

In general, the microprogram for any feature is assigned to a specific area of control storage. If a feature is not included in the system, its allocated space in control storage is normally left vacant. *In specific cases*, however, where the user can be saved the purchase of an increment of control storage, unused control storage space is sometimes allocated to another feature; for example, in the basic control storage, if the floating-point feature is not installed, microcode for the 3215-1 adapter can replace the microcode for the 3210-1 adapter. This flexibility of control storage allocations is further illustrated by the various expansion-block requirements.

The first increment (up to 36,864 bytes) is needed if any one of the following features is included in the system:

3215-1 adapter *and* the floating-point arithmetic feature 1401/1440/1460 compatibility

Extended-precision floating point arithmetic

Integrated communications adapter

Block multiplexing

Additional 48 subchannels for byte-multiplexer channel. The second increment of control storage (up to 49,152 bytes) is required when either:

- 1. The 1401/1440/1460 compatibility feature is installed and the ICA is equipped with the Synchronous Data Adapter Type II (Equivalent) feature, or

- 2. Any three (or more) of the following features are installed:

- a. 1401/1440/1460 compatibility.

- b. Block multiplexing.

- c. Terminal Adapter Type I Model II (Equivalent), in the ICA.

- d. Terminal Adapter Type III (Equivalent), in the ICA.

- e. Synchronous Data Adapter Type II (Equivalent), in the ICA.

The control storage is loaded with microcode from the console file during the initial microprogram load procedure. Data is lost whenever power is removed, and the control storage must be reloaded by the IMPL procedure when power is restored following a power-off condition.

## Access

Control-storage data is written in words of 72 bits, consisting of 64 data bits (one doubleword) and eight check bits; the check bits provide error checking and correction facilities as for main storage. When access is made to the control storage, eight bytes of microcode data are transferred to a storage data register in the control storage unit. The data is then fetched from this register in halfwords (two bytes), each halfword representing the microprogram control word.

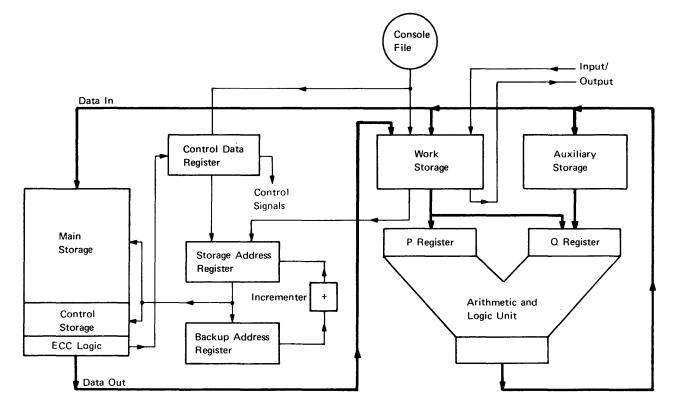

The rate of access depends on the execution time that is required for the particular microinstruction being implemented. The minimum time between successive accesses to control storage is 275 nanoseconds; this time is based on a machine clock period of 55 nanoseconds and a minimum cycle of 5 clock beats (see Figure 2).

#### Addressing

All control storage locations can be read and written by microprogram, using indirect addressing from a work storage address. Some locations can also be addressed directly, by an address contained in the microinstruction.

## WORK STORAGE

Work storage is used as a source or destination of data/information by both main storage and control storage. Work storage is divided functionally into eight zones, each zone consisting of eight halfwords.

#### Zone Allocation

A specific zone of work storage is allocated as a work area to the CPU and each input/output feature of the system, as follows:

| Zone | Feature                                               |

|------|-------------------------------------------------------|

| 0    | CPU                                                   |

| 1    | Console (logout and system reset)                     |

| 2    | Byte-multiplexer channel and console printer-keyboard |

| 4    | Integrated communications adapter                     |

| 5    | Integrated file adapter                               |

| 6    | First selector channel                                |

| 7    | Second selector channel                               |

A zone may be capable of handling more than one I/O feature, as shown for zone 2, for example.

### **Priority Allocation**

The central data flow can handle only one task at a time and only one zone of work storage is active at any one time in a microprogram task. A microprogram interruption system permits microprogram service, on a priority basis, to the CPU or the various I/O features (channel and integrated adapters) using the central data flow.

The CPU and I/O features are each assigned a level, or number of levels, of priority according to their relative importance. Several adapters may be allocated to one priority and, in this case, a sublevel order is applied. If numerous requests of the same priority level are received simultaneously, they are serviced in a specific order before any further requests are accepted at that level. This action prevents one adapter from excluding others of the same priority.

When a microprogram interruption request is accepted by the central data flow hardware, the status of the interrupted microprogram, in particular the next microprogram address from which a restart will be made, is preserved in the allocated zone of work storage. The status for up to seven individual microprograms can be preserved.

## **AUXILIARY STORAGE**

An additional high-speed store – called auxiliary storage – provides general registers, floating-point registers, and sixteen halfwords of working area that are used mainly for multiply and divide functions. Auxiliary storage is used only by the CPU.

## ARITHMETIC AND LOGIC UNIT

The ALU has an access width of two bytes and provides the following functions:

Add Subtract OR Exclusive OR AND AND Not Pass Complement.

Data is processed by the ALU according to the function that is required by the microinstruction and the results are written into work storage. Data that is transferred between work storage and auxiliary storage is passed through the ALU.

An ALU operation cycle on two bytes (halfword) requires a minimum of five beats of the basic 55-nanosecond system clock (Figure 2). Each extra halfword that is operated upon in a cycle requires a further three beats.

Figure 2. Example of Microinstruction Timing [08291]

#### **INPUT/OUTPUT FACILITIES**

## Internal I/O Interface

The internal input/output interface provides data transfer facilities between the CPU hardware and the hardware of the various integrated adapters and channel adapters. The interface is used by microinstructions that transfer data between work storage and I/O attachments or send control fields to the I/O attachments. It is also used during cycle steal transfers between main or control storage and the attachments.

#### Integrated I/O Adapters

Certain input/output devices are attachable to the System/370 Model 135 through adapter circuits that are connected directly to the CPU circuitry. These integrated adapters eliminate the need for the standard interface associated with channel and control-unit combinations. The program, however, is not affected by the method of attachment used.

Integrated adapter features (shown in italics) are available for the following devices:

1. 2319 Disk Storage. (Integrated file adapter.) This device contains three disk storage modules. When the device is attached, either one, but not both, of the following additional disk storage devices can be connected to the 2319:

IBM 2312 Disk Storage Model A1 (containing one disk storage module).

IBM 2318 Disk Storage Model A1 (containing two disk storage modules).

2. Up to eight start/stop or binary synchronous data communication lines. (Integrated communications adapter.)

Further details about the attachment of these devices are given under "Integrated Adapters" in the section "Input/Output Characteristics".

## Channels

The range of I/O devices that may be attached to the system is expanded by the use of the byte-multiplexer channel and two selector channels. The byte-multiplexer channel (channel 0) is capable of providing up to 64 subchannels, eight of which can be shared subchannels. Each of the two selector channels can be enhanced by the block-multiplexer feature, which provides 17 subchannels for the interleaved (multiplexed) execution of two or more channel programs.

This section describes the functional characteristics of the CPU and the central data flow area in greater detail than that outlined under "System Structure and Operation". Channel and integrated I/O facilities are described in the section "Input/Output Characteristics".

## **INSTRUCTION SETS**

All instructions of the System/370 Model 135 are implemented by microprogram. The instruction set that is

available to the system can be considered in three groups:  $1 \quad A$  basis instruction set that includes the System (270)

- 1. A basic instruction set that includes the System/370 standard and commercial instruction sets.

- 2. A floating-point arithmetic instruction set that can include extended-precision floating-point arithmetic instructions.

- 3. Instructions for compatibility features.

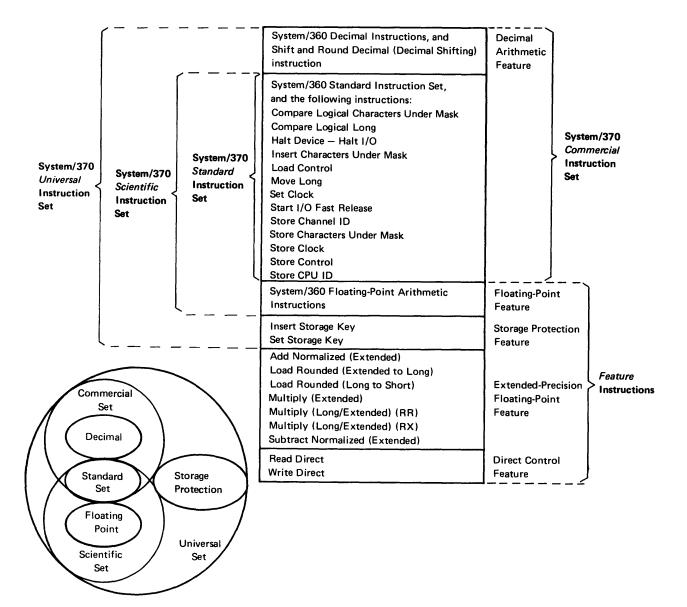

Instruction word formats and definitions are dealt with in detail in the Principles of Operation manual. The general organization of System/370 instructions is shown in Figure 3.

Figure 3. System/370 Instruction Sets [08292]

#### **Basic Instruction Set**

The basic instruction set of the Model 135 consists of the System/370 commercial instruction set (System/370 standard instruction set plus decimal arithmetic with decimal shifting), and the following instructions:

'Halt I/O' - 'halt device'

Storage protection instructions; see "CPU Facilities".

#### System/360 Instructions

The instructions of the System/360 standard set are implemented by an instruction-fetch (I-fetch) microinstruction that obtains the instruction from control storage, partially decodes the instruction, then branches to a microprogram routine to complete the instruction or group of instructions.

#### Start I/O Fast Release

The Model 135 executes the 'start I/O fast release' instruction as a 'start I/O' instruction.

## Halt I/O - Halt Device

The 'halt I/O' and 'halt device' instructions are available for terminating input/output operations. Either instruction may be used, depending on the program requirement for the channel.

The 'halt I/O' instruction operates in the same manner as the correspondingly named System/360 instruction (described in the Principles of Operation manual). Its definition, however, requires that bit 15 of the instruction word must be specified as 0. This bit is part of the high-order address byte, which is ignored in the System/360 instruction.

If bit 15 of the instruction word is set to 1, the instruction becomes 'halt device'. This instruction offers the program greater flexibility than does 'halt I/O' for controlling the termination of I/O operations. For example, it permits the CPU to:

- 1. Stop data transfer with a given device.

- 2. Terminate action at a given device.

- 3. Terminate a current burst operation on a channel only if the channel is working with the addressed device.

#### **Floating-Point Arithmetic**

The floating-point arithmetic facilities consist of two groups of instructions: floating-point and extendedprecision floating-point. The basic floating-point instruction set is a prerequisite for the extended-precision floatingpoint set.

#### **Basic Floating-Point Arithmetic Instructions**

The basic floating-point arithmetic group of instructions is the same as the System/360 floating-point instruction set (described in the Principles of Operation manual).

#### Extended-Precision Floating-Point Arithmetic Instructions

The extended-precision floating-point arithmetic instruction set consists of the following instructions:

Add normalized (extended) Load rounded (extended to long) Load rounded (long to short) Multiply (extended) Multiply (long/extended), RR format Multiply (long/extended), RX format Subtract normalized (extended).

The extended-precision format uses two long-precision number formats (two doublewords) to provide a fraction of 28 hexadecimal digits (112 bits), which is approximately equivalent to 34 decimal digits. One long-precision number is designated as the high-order part of the extendedprecision number, and the other as the low-order part. The sign and characteristic of the high-order part are also the sign and characteristic of the whole extended-precision number.

## **CPU FACILITIES**

The following general facilities are available to the CPU to enhance the flexibility and control of the System/370 Model 135:

Byte-oriented operands Channel identification CPU identification Direct control and external interruption Interval timer Storage protection (store and fetch) Time-of-day clock.

## **Byte-Oriented Operands**

The byte-oriented operand feature allows the main-storage operands of unprivileged instructions to appear on any byte boundary without causing a specification exception and a program interruption. When this facility is used, the operation which is termed "boundary alignment" affects storage references made by the CPU with RX-format and RSformat instructions.

The feature applies to fixed-point operands, floatingpoint operands, and logical operands. It does not apply to instruction addresses, privileged instructions and channel command words (CCWs). The definition of the feature and the limitations of boundary alignment operations are given in the Principles of Operation manual.

Note: Optimum performance is achieved only when operands are aligned in accordance with System/360 procedure.

#### **Storage Protection**

The storage protection feature, which includes both storage protection and fetch protection, allows the contents of main storage to be protected from destruction or improper handling during the execution of a program. The protection is achieved by the matching of storage keys (associated with blocks of main storage) and protection keys (associated with the PSW or an I/O operation) to identify the right of access to a storage location. A special 64-word, eight-bit store is used to hold the storage keys. The feature includes the instructions 'insert storage key' and 'set storage key' and is defined in the Principles of Operation manual.

## Time-of-Day Clock

The time-of-day clock feature provides a consistent measurement of elapsed time that can be used for indicating the time of day. The feature consists of a 64-bit binary counter with bit positions that correspond to those of a fixed-point number in double-precision format. Time is measured by the clock increasing its value incrementally, in accordance with the rules of fixed-point arithmetic. The resolution of the clock is at least one microsecond.

The feature includes the instructions 'store clock' and 'set clock'. The 'store clock' instruction allows the clock to be inspected, thereby causing the current clock value to be placed in main storage. The 'set clock' instruction allows the clock to be set to a specific value, and causes the current clock value to be replaced by an operand that is designated by the instruction.

The clock does not run and the clock value is lost when the system power is off; the clock value is lost also when the IMPL procedure is carried out.

#### **Interval Timer**

The interval timer provides program interruption on a program controlled basis. The storage word at main-storage locations 80-83 (decimal) is reserved for the interval timer feature. Any value stored at this location is automatically reduced by decrementing bit 23 every 3.333 milliseconds, provided the interval-timer switch is in the NORM (normal) position. The high-order 24 bits provide a full cycle of about 15.5 hours.

The program in process can be automatically interrupted by an external interruption, provided PSW system-mask bit 7 is on, when the interval timer word goes from a positive value to a negative value. The interruption is identified by setting PSW bit 24 on.

#### **CPU Identification**

Information identifying the CPU is stored in an eight-byte field of main storage that is designated by the operand address of the 'store CPU ID' instruction. The format of the stored information is as follows:

| Bits 0-7   | (Reserved)        |

|------------|-------------------|

| Bits 8-31  | CPU serial number |

| Bits 32-47 | CPU model number  |

| Bits 48-63 | Contain all zeros |

#### Channel Identification

Information that identifies a designated channel is stored in a four-byte field of main storage at location 168 of the I/O communications area (location 160 through 191). Bits 16 through 23 of the sum that is formed by adding the contents of the register B1 and the contents of the D1 field of the 'store channel ID' instruction identify the channel to which the instruction applies. The format of the stored information is as follows:

Bits 0-3 Contain a code to identify the type of channel: 0000 indicates selector channel 0001 indicates byte-multiplexer channel 0010 indicates block multiplexer channel Bits 4-32 Contain all zeros

#### **Direct Control and External Interruption**

The direct control feature provides two instructions, 'read direct' and 'write direct', for transferring a single byte of information between an external device and main storage. The feature also provides six external interruption lines, each of which, when active, sets up the conditions for an external interruption. Detailed definitions of the instructions and the external interruptions are given in the Principles of Operation manual.

#### SYSTEM CONTROL

The System/370 Model 135 operates under the control of the current PSW and control registers. The current PSW is loaded from main storage by means of the 'load PSW' instruction, and is stored in various permanently assigned areas of main storage when an interruption is accepted; see the Principles of Operation manual. The control registers are part of control storage.

System and CPU recovery from hardware errors is controlled by an automatic machine-check handling procedure.

## **Control Registers**

The control registers consist of up to sixteen 32-bit registers that are located in fullword areas 0 through 15 of control storage. Registers and/or specific bit positions within a register are allocated to each system feature that requires control register facilities. The usage of the registers and the bit positions available depends on the number of features installed.

Two instructions, 'load control' and 'store control', are associated with the control registers. 'Load control' allows control information to be loaded from main storage into the control registers; 'store control' allows information to be transferred to main storage from the control registers.

#### Instructions

'Load Control': The main storage area from which the contents of the control registers are obtained starts at the

location designated by the second-operand address and continues through as many storage words as the number of control registers specified. The control registers are loaded in ascending order of their addresses, starting with the control register specified by the R1 field and continuing up to and including the control register specified by the R3 field, with control register 0 following control register 15.

'Store Control': The main storage area into which the contents of the control registers are placed starts at the location designated by the second-operand address and continues through as many storage words as the number of control registers specified. The contents of the control registers are stored in ascending order of register addresses, starting with the control register specified by the R1 field and continuing up to and including the control register specified by the R3 field, with control register 0 following control register 15. The contents of the control registers remain unchanged.

## External Masking

The external masking arrangements of the System/370 Model 135 provide the means for selective masking of interruptions due to timer, interruption key, and external signals (bits 24, 25, 26 respectively). The extended external masking feature is implemented by three subclass mask bits in control register 0, in conjunction with the external mask bit of the PSW, as defined in the Principles of Operation manual.

## Machine-Check Handling

The error-recovery facilities and machine-check interruption procedures of System/370 Model 135 comply with the general definitions that are contained in the Principles of Operation manual. Specific definitions for Model 135 can be considered in the following phases:

- Error checking, with automatic correction whenever possible

- Internal logout

- Error analysis and actions

- Instruction retry, with error recovery whenever possible Machine-check logout

- Check stop.

## Error Checking and Correction

Both main storage and control storage are provided with an error checking and correction code that automatically corrects any single-bit error and detects any double-bit error. In addition, if more than 255 single-bit error corrections are made in any one 416-microsecond period, the CPU sets bits 2 and 17 in the machine-check interruption code. (If a storage error is not corrected, the CPU sets bits 1, 14, and 16 in the machine-check interruption code.)

A single-bit correction adds 165 nanoseconds to the execution time of the microinstruction within which it is

performed. During this period, the data is corrected and passed to the CPU. The data in storage is not corrected. Each correction increments an eight-bit hardware counter that is reset every 416 microseconds.

The error checking and correction code is derived from eight bits that are associated with each doubleword in main storage and control storage.

## Internal Logout

For any hardware error other than normal-rate, corrected single-bit errors, the CPU generates an internal logout as a preliminary action to error analysis. Error analysis is followed either by a recovery or, if a machine-check interruption proves necessary, by a synchronous machinecheck logout. This internal logout records the hardwareindicated error conditions in two special buffers that are maintained in a private control storage area: the machinecheck interruption code (MCIC) buffer and the logout buffer. The buffer area consists of ten halfwords that are allocated as follows:

- 1. One fullword is allocated to the MCIC buffer to provide an image of the machine check interruption code, which is stored at location 232 of main storage.

- 2. Eight halfwords are allocated to the logout buffer to provide:

- a. An immediate storage for hardware error signals.

- b. The address of the "failed" microinstruction.

- c. The identity of the adapter that is in error.

- d. The current storage address.

- e. Information relating to the interruption status of the CPU and the state of the 'instruction retry' latches.

## Error Analysis

An internal logout invokes a microprogram that analyzes the error status and decides the next action. If the error status is such that the extent of the damage cannot be determined, the system-damage bit is set and all validity bits are reset in the MCIC buffer. A *machine-check interruption* is requested, and the subsequent action depends on the value of bit 13 in the program status word and of the hardstop bit in control register 14.

If the error status is such that the current CPU instruction sequence has not been affected, a specific interruption is requested and normal instruction execution is resumed. No validity bits are reset in the MCIC buffer. Typical causes and the subsequent actions are as follows:

- 1. Channel program affected. The subchannel is set up to request an I/O interruption with channel-control check.

- 2. Damage to time-of-day clock or interval timer. A machine-check interruption is requested.

- 3. Single-bit storage errors have been corrected at a rate of more than 255 in 416 microseconds. The storage error corrected bit is set in the MCIC buffer and a machine-check interruption is requested.

If the error status indicates that the current CPU instruction sequence cannot be immediately resumed, the microprogram analyzes the recovery possibilities by an instruction-retry routine.

#### Instruction Retry

The system can attempt to recover from intermittent failures automatically by restarting the instruction, from the beginning, when an error is detected - but only if the source data was not changed before the point of error. The instruction is retried up to eight times. The success of the retry depends on the cause of the error.

## Validity Bits

The validity bits of the machine-check interruption code have the following significance:

- 1. *If zero:* At a point of error preceding the interruption, the contents of the indicated storage registers were modified in error.

- 2. If one: At all preceding points of error, the contents of the indicated storage registers remained valid.

## Machine-Check Logout

Each internal logout normally leads to an error inter-

ruption. The contents of the logout buffer are copied to main storage during the interruption. Because the data flow area and microprograms of the System/370 Model 135 are used for the control of channels and integrated adapters as well as for CPU control, the logout buffer contents can relate to either a machine-check condition or a channel control check. Thus the interruption may relate to either a CPU error or a channel error.

## Check Stop

The system enters the check-stop condition if any one of the following situations arises:

- 1. Any hardware error is detected when the system is in the manual-stopped state.

- 2. Repeated errors occur during the error analysis microprogram.

- 3. PSW bit 13 and the hardstop bit in control register 14 are both ones, and an error occurs during a machinecheck interruption which is already attempting to report system damage or instruction processing damage.

- 4. PSW bit 13 is zero and the hardstop bit is one, and an error occurs which causes the system damage bit or the instruction-processing-damage bit to be set in the MCIC buffer.

·

The input/output devices that can be connected to the System/370 Model 135 are listed in *IBM System/370 Input/Output Configurator*, GA22-7002. Most of these devices are attached to the CPU through either a *byte-multiplexer channel* or a *selector channel* operating across a standard I/O interface. Some I/O devices, however, are attached directly to the CPU through special adapters that replace the standard channel/control-unit combination and I/O interface; devices that can be attached in this manner are dealt with in this section under "Integrated Adapters".

## **Channel Facilities**

The channel facilities of the System/370 Model 135 consist of one byte-multiplexer channel and two selector channels, with a block-multiplexer feature available for the selector channels.

#### BYTE-MULTIPLEXER CHANNEL

The byte-multiplexer channel conforms to the definitions given in the Principles of Operation manual. Communication with the input/output devices attached to the channel is through a standard I/O interface that is extended to include a disconnect-in line and a mark-out line.

The byte-multiplexer channel is intended for the attachment of low-speed input/output devices. Functionally, it interprets I/O instructions, translates them into commands and controls at the interface to operate the devices, transfers data between the devices and main storage, and controls interruptions that are raised either by device requests to the program or by error conditions. The channel is addressed as channel 0.

## Mode of Operation

The channel multiplexes (interleaves) data to or from the I/O devices, on request and for one device at a time, in groups of sequential bytes as required by the particular device being serviced. An unbuffered burst-mode device can be attached to the channel, but this is not recommended if there is any possibility of the burst-mode device operating concurrently with the integrated file adapter, the integrated communications adapter, or a selector channel.

## Data Rates

Data times and rates for the byte-multiplexer channel are

given in Figure 4; these assume that there is no activity on the selector channels, the IFA, or the ICA. *Data-chaining* data rates which, if exceeded, cause an overrun condition are also given in Figure 4.

Delays within the control unit are assumed to be greater than delays within the channel. As control unit delays increase, so the time for each additional byte in burst mode increases, by 2.2-microsecond increments, up to 13.3 microseconds. One larger increment to 19.2 microseconds per additional byte then occurs, after which the time per byte increases linearly with the increase in control unit delay.

## Control

Byte-multiplexer channel operations are implemented mainly by microprogram. To facilitate this control, I/O operations utilize the CPU data flow area, the arithmetic and logic unit, general registers, and zone 2 of CPU work storage. Work storage zone 2 is also shared with the integrated 3210-1 or 3215-1 adapter.

In addition to these areas, an area of 16 bytes is reserved in control storage for each I/O device that is attached to the channel. This area holds the unit control word (UCW), which contains information for controlling the current operation of the device. Also, one halfword of directly addressable control storage is used as an interruption buffer to present the CPU with information when it makes an interruption. The hardware of the byte-multiplexer channel includes seven bytes of external registers that contain interface tags, data, and various controls.

Input/output operations are initiated by a common microprogram at CPU level, and control is transferred to the channel when it becomes necessary to select a device at the I/O interface. This need occurs when the channel detects a condition that requires the channel microprogram; a hardware-generated request is then sent to the CPU to transfer control. This request can be caused either by the 'operational in' signal falling, by a CPU interruption to request initiation of an I/O operation or timeout, or by any of the following signals received at the interface:

Address in Disconnect in Select in Service in Status in.

When the byte-multiplexer channel has completed the initial selection routine, it sets a condition code in an I/O operation buffer that consists of three halfwords of CPU

#### DATA TIMES AND RATES

| Channel Operation                                                    | Time<br>(microseconds) | Maximum<br>Data Rate<br>(bytes per second) |

|----------------------------------------------------------------------|------------------------|--------------------------------------------|

| One byte-multiplexed transfer                                        | 24                     | 41,000                                     |

| One byte-multiplexed transfer with PCI                               | 26                     | 38,000                                     |

| Each additional byte in burst mode                                   | 6.7                    | 149,000                                    |

| Command chaining with TIC and PCI (if no other activity on channels) | 56                     | -                                          |

#### DATA CHAINING TIMES AND RATES (See Note)

| Channel Operation              | Time<br>(microseconds) | Data Rate<br>(bytes per second) |

|--------------------------------|------------------------|---------------------------------|

| Data chaining within channel   | 22                     | 45,000                          |

| Data chaining with TIC         | 28                     | 35,000                          |

| Data chaining with PCI         | 34                     | 30,000                          |

| Data chaining with TIC and PCI | 40                     | 25,000                          |

Note: If these chaining rates are exceeded, an overrun condition is caused.

PCI: Program-controlled interruption TIC: Transfer in channel

Figure 4. Byte-Multiplexer Channel – Data Rates and Times [08293]

work storage. This buffer information also contains the UCW address, the CCW command code, the device address, and a byte of flags. When control is returned to the CPU, this condition code is examined and a channel status word (CSW) is stored, if required, by using information already placed in the UCW by the channel.

When an I/O device initiates a multiplexer interface sequence for data or status transfer and raises the 'address in' signal, the channel requests a microprogram interruption. The channel then generates the UCW address and loads the UCW from control storage into work storage; the UCW contains the information that is needed to continue the operation at the unit. When the interface sequence is finished and the 'operational in' signal falls, the updated UCW is stored back in control storage and control is restored to the CPU. Control is also restored to the CPU during a multiplexer interface sequence if the delay between in-tag signals exceeds 10 microseconds.

#### **Error Handling**

Channel programming errors are mostly detected by the common I/O microprogram. The following errors are

detected by either channel hardware or microprogram:

- 1. Channel-data check. This is caused by bad parity on the I/O interface bus-in lines, with the 'service in' signal raised.

- 2. *Channel-control check.* This is caused by bad parity in the data or address on the bus from the CPU.

- 3. *Interface-control check.* This is caused by one of the following:

- a. Bad parity on the I/O interface bus-in lines, with 'address in' or 'status in' raised.

- b. More than one in-tag signal is raised.

- c. The 'service out' and 'command out' signals are raised.

- d. The 'select in' and 'operational in' signals are raised.

- e. Interface stops during selection or re-selection that last for more than 64 microseconds.

- f. Interface stops during data transfers that last for more than 30 seconds; during the timeout period, the channel behaves as if it is in burst mode to new I/O instructions.

- g. A wrong address is received with 'address in' response to 'address out'.

- h. The 'disconnect in' signal is raised.

- 4. Channel-protection check. This is caused when a protected address is encountered during data servicing or chaining.

- 5. Channel-program check. This is caused by one of the following:

- a. When an invalid address is encountered during data servicing or chaining.

- b. When an invalid CCW format is encountered during a start I/O operation or chaining.

CPU errors that are detected when the byte-multiplexer channel is in control are handled by the CPU check system. If the errors are successfully retried, the channel is not informed. If retries are unsuccessful and channel checks are not disabled, the control passes to the multiplexer channel error microprogram, which then sets channel-control check.

Channel-control check or interface-control check raises an error line to the CPU. The higher-priority error handler obtains control and takes action depending on 'stop on error' and console disable mode. An 'inhibit error' latch in the channel is set to prevent interface-control check from raising a trap request; this enables the error handler to set up a channel microprogram start address and to restore control to the channel. The channel then enters an error analysis microprogram, which performs interfacedisconnect, selective-reset, or channel-reset operations as necessary, and stores status and logout information in the UCW. The channel raises an I/O program interruption request, unless the error occurred during an I/O instruction, in which case a condition code of 1 is set and a CSW is stored with an I/O logout.

#### **Interruption Handling**

To handle interruptions at user program level, an 'interruption request' latch is provided in the CPU for the byte-multiplexer channel. A halfword interruption buffer is provided in control storage for the channel, but the buffer is also shared by the adapters. A further halfword interruption buffer is associated with the channel for use in error conditions.

When the channel detects a condition that requires an interruption to the user program, it tests its 'interruption request' latch. If the latch is off, it is set on, and the address of the I/O device associated with the interruption is placed in the interruption buffer. In the case of a channel-end type interruption, the status that is needed for the subsequent storing of a CSW is accepted from the device and is placed in the UCW. In all other cases, device status remains in the device and is fetched, when the interruption is accepted, by a pseudo 'test I/O' instruction; the channel mask is examined and, if enabled, the 'program interruption' latch is set. The device address in the interruption buffer can be used to retrieve, from the UCW, the information that is required for storing a CSW.

*Note:* Program-controlled interruptions (PCIs) are given priority over all other channel interruptions except those requested by error conditions.

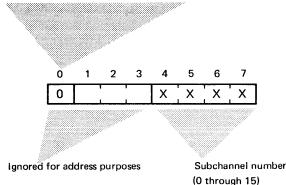

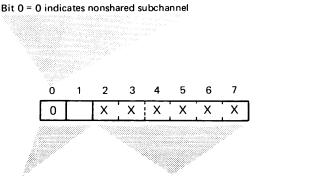

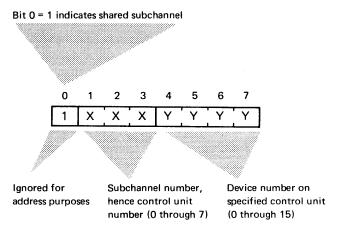

#### Subchannels

The byte-multiplexer channel contains either 16 or 64 subchannels. Each I/O unit attached to the channel requires a subchannel to hold information for controlling the current operation at the unit. A subchannel may be shared by more than one device or it may be nonshared. A *shared* subchannel is used for an I/O unit that can have several devices attached, only one of which requires the subchannel at any one time; a *nonshared* subchannel is used for an I/O unit having only one device.

The allocation of subchannels for the System/370 Model 135 is summarized in Figure 5. The integrated communications adapter is addressed as if it were on channel 0

|                                         | With Total Number of Subchannels |                           |  |  |  |

|-----------------------------------------|----------------------------------|---------------------------|--|--|--|

|                                         | =16                              | =64                       |  |  |  |

| Maximum Number of Nonshared Subchannels | 16                               | 64                        |  |  |  |