## Field Engineering Theory of Operation

(Manual of Instruction)

Restricted Distribution

This manual is intended for internal use only and may not be used by other than IBM personnel without IBM's written permission.

Specifications contained herein are subject to change without notice. Revisions and/or supplements to this publication will be issued periodically.

System/360 Model 44

ş,

à

**Floating Point Feature**

# Field Engineering Theory of Operation

(Manual of Instruction)

**Restricted** Distribution

This manual is intended for internal use only and may not be used by other than IBM personnel without IBM's written permission.

Specifications contained herein are subject to change without notice. Revisions and/or supplements to this publication will be issued periodically.

System/360 Model 44

**Floating Point Feature**

#### PREFACE

This volume describes the Floating Point Feature of the IBM 2044 Processing Unit, the processor for the IBM System/360 Model 44. Chapter 1 of the volume introduces the concepts of floating-point arithmetic and defines its application within the hexadecimal system used in the IBM 2044. Chapter 2 describes the functional parts of the floating point feature and the interaction of the feature with the basic central processing unit. Chapter 3 describes in detail the operation of the floating-point instruction set.

The manual assumes knowledge of the System/ 360 as described in IBM System/360 Principles of Operation, Form A22-6821.

The volumes that constitute the <u>IBM Field</u> <u>Engineering Theory of Operation</u> manual for the IBM System/360 Model 44, and their form numbers, are:

- System/360 Model 44, Introduction and Functional Units, Form Y33-0001: Gives a general introduction to digital computers and computing techniques, defines the relationship of the IBM 2044 to the System/360 and describes the various parts which form the processing unit.

- System/360 Model 44, Principles of Operation Processing Unit, Form Y33-0002: Describes the operation of the instructions for the accelerator and basic machine (other than floating-point instructions), and program and machine interrupts.

System/360 Model 44, Principles of Operation - Channels, Form Y33-0003: Describes the Common Channel area, the Multiplexor Channel 0 and the High Speed Multiplexor Channel.

These volumes are referenced in other volumes by the main element of their titles.

Reference is also made in these volumes to the following associated manuals:

System/360 Model 44, Single Disk Storage Drive, Form Y33-0006: Gives an introduction to the operation of the control unit and describes in detail the functional parts and the operations that may be performed.

Field Engineering Maintenance Manual (FEMM), <u>IBM System/</u> <u>360 Model 44</u>, Form Y33-0007: Contains information for servicing the 2044 Processing Unit.

Field Engineering Maintenance Diagrams (FEMD), <u>IBM System/</u> <u>360 Model 44</u>, <u>Volume 2</u>, Form Y33-0008: Contains maintenance information in the following categories: Data Flow Charts, Flow Charts, Timing Charts, MAP's.

Other related manuals that describe units used in the System/360 Model 44 are:

- Field Engineering Manual of Instruction (FEMI), <u>1052 Adapter</u>, Form 223-2808.

- Field Engineering Maintenance Manual (FEMM) Single Disk Storage/Direct Access, Form Y26-3663.

#### First Edition

This manual makes obsolete Field Engineering Theory of Operation, System/360 Model 44, Form Z33-0005-0.

The manual is written basically to Engineering Change Level 390049 and in some cases anticipates Engineering Change Level 390063. Significant changes or additions to the information in the manual will be covered in subsequent revisions of FE supplements.

This publication was prepared by IBM European Laboratories, Product Publications. A form is provide at the back of this manual for reader's comments. If the form has been removed, comments may be addressed to: IBM Corporation, FE Manuals, Dept. B96, PO Box 390, Poughkeepsie, N.Y. 12602

#### CONTENTS

|                                                                                                                                                 | Page              |

|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| CHAPTER 1. INTRODUCTION                                                                                                                         | 1- 1              |

| Properties of Numbers                                                                                                                           | 1- 1              |

| ,                                                                                                                                               | 1- 1              |

| Hexadecimal and Decimal Conversion (Examples) ,                                                                                                 | 1- 2              |

|                                                                                                                                                 | 1- 3              |

| 8                                                                                                                                               | 1-4               |

| Multiply                                                                                                                                        | 1-4               |

| Divide                                                                                                                                          | 1-4               |

| Shifting                                                                                                                                        | 1-4               |

|                                                                                                                                                 | 1-4               |

| Floating-Point Exceptions                                                                                                                       | 1-4               |

|                                                                                                                                                 | 1- 5              |

| Variable-Precision Feature                                                                                                                      | 1- 5              |

|                                                                                                                                                 |                   |

|                                                                                                                                                 | 2- 1              |

| Floating-Point Data Flow                                                                                                                        | 2- 1              |

|                                                                                                                                                 | 2- 2              |

| Characteristic Addition                                                                                                                         | 2- 2              |

|                                                                                                                                                 | 2-2               |

| 6                                                                                                                                               | 2-2               |

| Characteristic Decrementing                                                                                                                     | 2- 2              |

|                                                                                                                                                 | 2- 3              |

| Arithmetic Components                                                                                                                           | 2-4               |

| Floating-Point Registers                                                                                                                        | 2-4               |

| Use                                                                                                                                             | 2-4               |

| Input                                                                                                                                           | 2-4               |

| Output                                                                                                                                          | 2-4               |

| $Controls \ldots \ldots$ | 2-4               |

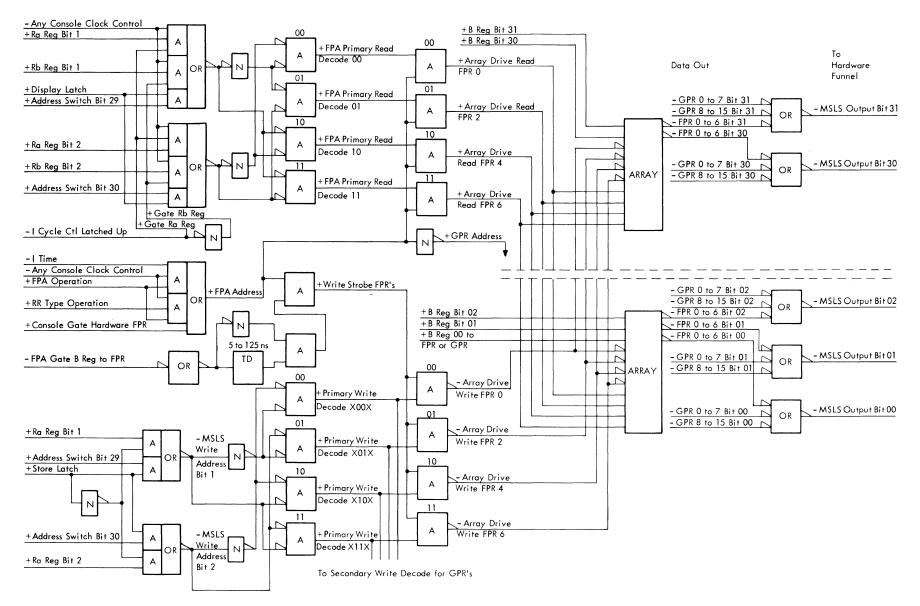

| Read Controls                                                                                                                                   | 2-4               |

| Write Controls                                                                                                                                  | 2-6               |

| Description                                                                                                                                     | 2- 6              |

| Display and Store Facilities                                                                                                                    | 2- 6              |

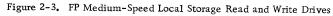

| Floating-Point Scratch Register                                                                                                                 | 2- 6              |

| Use                                                                                                                                             | 2- 6              |

| Input                                                                                                                                           | 2- 6              |

| Output  .  .  .  .  .  .  .  .  .                                                                                                               | 2- 7              |

| $Controls \dots \dots$                    | 2- 7              |

|                                                                                                                                                 | 2- 7              |

| Display                                                                                                                                         | 2- 7              |

| Exponent Register A                                                                                                                             | 2- 7              |

|                                                                                                                                                 | 2- 7              |

| Input                                                                                                                                           | 2- 7              |

| Output                                                                                                                                          | 2- 7              |

| -                                                                                                                                               | 2- 7              |

|                                                                                                                                                 | 2- 7              |

| -                                                                                                                                               | 2-8               |

| 1 /                                                                                                                                             | 2- 8              |

|                                                                                                                                                 | 2- 8              |

|                                                                                                                                                 | 2- <sup>`</sup> 8 |

|                                                                                                                                                 | 2- 8              |

| 1                                                                                                                                               | 2- 8              |

|                                                                                                                                                 | 2-8               |

|                                                                                                                                                 | - 0<br>2- 9       |

|                                                                                                                                                 | 2-9               |

|                                                                                                                                                 | 2-9               |

|                                                                                                                                                 | 2-9               |

|                                                                                                                                                 | 2- 9<br>2- 9      |

|                                                                                                                                                 | 2- 9<br>2- 9      |

|                                                                                                                                                 | 2- 9<br>2- 9      |

|                                                                                                                                                 | 2- 9<br>2-10      |

| *                                                                                                                                               | 2-10              |

| ,                                                                                                                                               | 2-10              |

| Use                                                                                                                                             |                   |

| ge |                                                                                                                               | Page     |

|----|-------------------------------------------------------------------------------------------------------------------------------|----------|

| 1  | Input and Output                                                                                                              | 2-10     |

| 1  | Controls  .  .  .  .  .  .  .  .  .                                                                                           | 2-10     |

| 1  | Description                                                                                                                   | 2-11     |

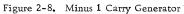

| 2  | Minus 1 Carry Generator                                                                                                       | 2-11     |

| 3  | Use                                                                                                                           | 2-11     |

| 4  |                                                                                                                               | 2-11     |

| 4  |                                                                                                                               |          |

| -  |                                                                                                                               | 2-11     |

| 4  | $Controls \dots \dots$  | 2-11     |

| 4  | Description                                                                                                                   | 2-11     |

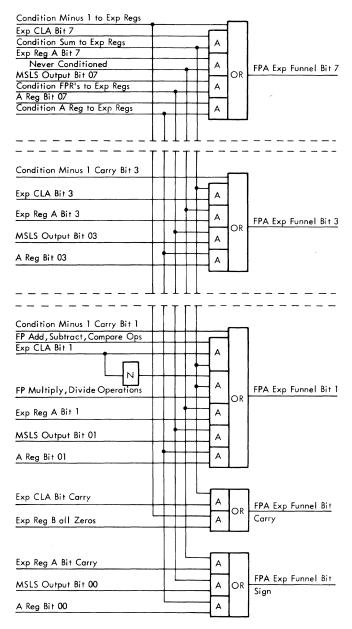

| 4  | Exponent Funnel                                                                                                               | 2-11     |

| 4  | Input                                                                                                                         | 2-12     |

| 5  | Output                                                                                                                        | 2-12     |

| 5  | Controls                                                                                                                      | 2-12     |

|    | Description                                                                                                                   | 2-12     |

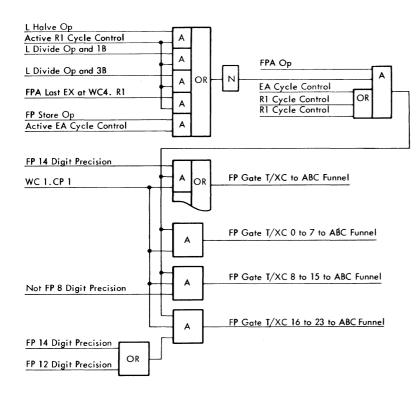

| 1  | ABC Funnel (Variable-Precision Controls)                                                                                      | 2-13     |

| 1  |                                                                                                                               | 2-13     |

| 2  |                                                                                                                               |          |

| _  | Input and Output                                                                                                              | 2-13     |

| 2  | Controls  .  .  .  .  .  .  .  .  .                                                                                           | 2-13     |

| 2  | Description                                                                                                                   | 2-13     |

| 2  | Console Facilities                                                                                                            | 2-14     |

| 2  | Exponent Underflow and Overflow Detection                                                                                     | 2-14     |

| 3  | Examples of Underflow/Overflow Detection                                                                                      | 2-15     |

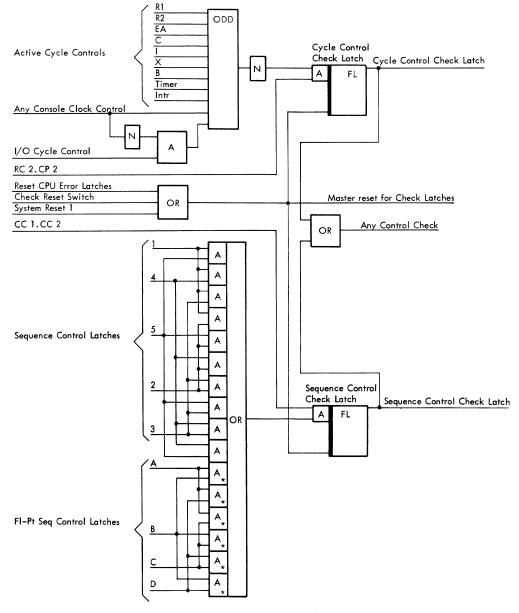

| 4  | FP Check Circuits                                                                                                             | 2-16     |

| 4  | FP Sequence Control Checking                                                                                                  | 2-16     |

| 4  |                                                                                                                               | 2-17     |

| 4  |                                                                                                                               | 2-17     |

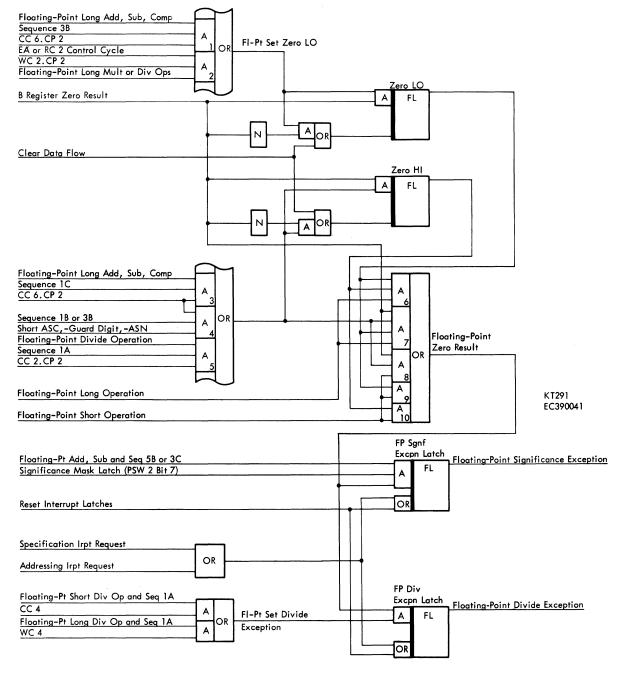

| 4  |                                                                                                                               | 2-19     |

| -  | Divide Exception                                                                                                              |          |

| 4  | Exponent Overflow Exception                                                                                                   | 2-19     |

| 4  | Exponent Underflow Exception                                                                                                  | 2-20     |

| 6  |                                                                                                                               |          |

| 6  | CHAPTER 3. PRINCIPLES OF OPERATION                                                                                            | 3- 1     |

| 6  | Load and Store Instructions                                                                                                   | 3- 1     |

| 6  | Load Instructions                                                                                                             | 3- 1     |

| 6  | Short Precision                                                                                                               | 3- 1     |

| 6  | Long Precision                                                                                                                | 3-1      |

| 7  |                                                                                                                               | 3-1      |

| 7  |                                                                                                                               | 3-2      |

|    |                                                                                                                               |          |

| 7  | Long Precision $\ldots$                                                                                                       | 3-2      |

| 7  | Halve Instructions                                                                                                            | 3- 2     |

| 7  | Short Precision                                                                                                               | 3- 2     |

| 7  | Long Precision                                                                                                                | 3- 2     |

| 7  | Add and Subtract Instructions (Short-Precision Operands)                                                                      | 3- 3     |

| 7  | Step 1 - Fetching of Operands                                                                                                 | 3-3      |

| 7  | Operand-Fetch (RX Format)                                                                                                     | 3-3      |

| 7  | Operand-Fetch (RR Format)                                                                                                     | 3-4      |

| 8  | Step 2 - Matching of Characteristics and Adding of                                                                            |          |

| 8  | $\mathbf{Fractions}  \cdot  \cdot  \cdot  \cdot  \cdot  \cdot  \cdot  \cdot  \cdot  $                                         | 3-4      |

| 8  |                                                                                                                               | 3-5      |

|    | Operand 1 Exponent H                                                                                                          |          |

| 8  | Operand 1 Exponent LO                                                                                                         | 3-6      |

| 8  | $Exponents EQ \dots $   | 3-6      |

| 8  | End Conditions                                                                                                                | 3- 6     |

| 8  | Step 3 - Recomplementing of Fraction Result                                                                                   | 3- 6     |

| 9  | Step 4 - Correcting of Fraction Overflow and Normalizing                                                                      |          |

| 9  | of Result                                                                                                                     | 3- 7     |

| 9  | Step 5 - Storing of Result and Setting of Condition Code.                                                                     | 3- 7     |

| 9  | Analysis of B Register Sign Bit                                                                                               | 3- 7     |

| 9  | Setting of Condition Code                                                                                                     | 3-8      |

| 9  | -                                                                                                                             | 3-8      |

|    | Examples of Short-Precision Add/Subtract                                                                                      |          |

| 9  | Compare Instructions (Short-Precision Operands)                                                                               | 3-12     |

| 10 | Step 1 - Fetching of Operands                                                                                                 | 3-12     |

| 10 | Step 2 - Matching of Characteristics and Subtracting of                                                                       | <b>.</b> |

| 10 | $Fractions \dots \dots$ | 3-12     |

|    |                                                                                                                               |          |

### CONTENTS (continued)

|                                                                 | Page |

|-----------------------------------------------------------------|------|

| Step 3 - Analysis of Result and Setting of Condition Code.      | 3-12 |

| Add and Subtract Instructions (Long-Precision Operands)         | 3-13 |

| Step 1 - Fetching of Operands                                   | 3-13 |

| Step 2 - Matching of Characteristics and Adding of              |      |

| Fractions                                                       | 3-14 |

| Step 3 - Recomplementing of Fraction Result                     | 3-15 |

| Step 4 - Correction of Fraction Overflow and Normalization      | 0 10 |

| of Result                                                       | 3-15 |

| Step 5 - Storage of Results and Setting of Condition Code .     | 3-15 |

|                                                                 | 3-16 |

| Examples of Long-Precision Add/Subtract                         |      |

| Example 1                                                       | 3-16 |

| Example 2                                                       | 3-17 |

| Compare Instructions (Long-Precision Operands)                  | 3-19 |

| Step 1 - Fetching of Operands                                   | 3-19 |

| Step 2 - Matching of Characteristics and Subtracting of         |      |

| Fractions                                                       | 3-20 |

| Step 3 - Analysis of Result and Setting of Condition Code .     | 3-20 |

| Multiply Instructions (Short-Precision Operands)                | 3-20 |

| Step 1 - Fetching of Operands and Initialization                | 3-21 |

| Step 2 - Fraction Multiply Cycles and Addition of               |      |

| Characteristics (Exponent)                                      | 3-21 |

| Step 3 - Post-Normalization of Product                          | 3-22 |

| Step 4 - Storing the Result                                     | 3-22 |

| Step 5 - Test for FP Exceptions                                 | 3-22 |

| Introduction to Multiply Instructions (Long-Precision Operands) |      |

| Principles of Long-Precision Multiply                           |      |

|                                                                 |      |

| Execution of Long-Precision Multiply (Precision = 10, 12, 14)   | 3-23 |

| Step 1 - Operand Fetch and Pre-Normalization                    | 3-25 |

| Sequence 1A, R2 Cycle (RR Format)                               | 3-25 |

| Double EA Cycles, Sequence 1A (RX Format)                       | 3-25 |

| Sequence 5A                                                     | 3-25 |

| Sequence 2A                                                     | 3-25 |

| R1 Cycle                                                        | 3-25 |

| Sequence 3A                                                     | 3-26 |

| Sequence 4A                                                     | 3-26 |

| Setting of Zero HI and LO Latches                               | 3-26 |

| Step 2 – Low-Order Product                                      | 3-26 |

| Sequence 1B                                                     | 3-26 |

| Sequence 3B                                                     | 3-26 |

| Sequence 2B                                                     | 3-27 |

| Step 3 - First Cross-Product                                    |      |

| Sequence 4B                                                     | -    |

| 6 2D                                                            | 3-27 |

| Sequence 5B                                                     | 3-27 |

|                                                                 | 3-27 |

| Step 4 - Second Cross-Product                                   |      |

| Sequence 1C $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$        | 3-28 |

| Sequence 2C                                                     | 3-28 |

| Sequence 3C                                                     | 3-28 |

| Sequence $5C$                                                   | 3-28 |

| Sequence 4C                                                     | 3-28 |

| Sequence 1D                                                     | 3-28 |

| Sequence 3D                                                     | 3-28 |

| Step 5 - High-Order Product                                     | 3-28 |

| Sequence 4D                                                     | 3-28 |

| Sequence 2D                                                     | 3-28 |

|                                                                 |      |

|                                                             |   | Page  |

|-------------------------------------------------------------|---|-------|

| Step 6 - Post-Normalization, Exception Test and Result      |   |       |

| Store                                                       |   | 3-29  |

| Sequence 5D                                                 |   | 3-29  |

| R1 Cycle                                                    |   | 3-29  |

| Execution of Long-Precision Multiply (Precision = 8)        | • | 3-29  |

| Step 1 - Operand Fetch and Pre-Normalization                |   | 3-29  |

| Step 2 - Multiplication                                     |   | 3-30  |

| Sequence 1B                                                 |   | 3-30  |

| Sequence 2B                                                 |   | 3-30  |

| Step 3 - Post-Normalization, Exception Test and Product     |   |       |

| Store                                                       |   | 3-30  |

| FP Common Multiply Cycles                                   |   | 3-31  |

| Divide Instructions (Short-Precision Operands)              |   | 3-32  |

| Instruction Execution                                       |   | 3-33  |

| Operand 2 Fetch and Pre-Normalizing Cycles                  |   | 3-33  |

| Operand 1 Fetch and Pre-Normalizing Cycles                  |   | 3-34  |

|                                                             |   | 3-34  |

| Quotient Store Cycle                                        |   | 3-35  |

| Introduction to Divide Instructions (Long-Precision Operand |   |       |

| Execution of Long-Precision Divide (Precision = 10, 12, 14  | ) | 3-35  |

| Step 1 - Operand 2 Fetch and Pre-Normalizing                |   | 3-35  |

|                                                             |   | 3-35  |

|                                                             |   | 3-36  |

|                                                             |   | 3-36  |

| Sequence 2A                                                 |   | 3-36  |

|                                                             |   |       |

|                                                             |   |       |

| Sequence $3\Lambda$                                         |   |       |

| Sequence $4A$                                               |   |       |

| Step 3 - Divide Cycles and High-Order Quotient Storing      |   |       |

|                                                             |   | 3-37  |

|                                                             |   |       |

| Sequence $4B$                                               |   |       |

| R1 Cycle                                                    |   | 2 2 7 |

| Sequence 1B or Sequences 1B, 2B, 3B                         |   |       |

| Step 4 - Low-Order Quotient Storing and Testing for         | • | 0 07  |

| Exceptions                                                  |   | 3-37  |

|                                                             |   | 3-37  |

|                                                             |   | 3-37  |

|                                                             |   | 3-37  |

| Execution of Long-Precision Divide (Precision = 8)          | • | 3-37  |

| Step 1 - Operand 2 Fetch and Pre-Normalizing                |   |       |

| Step 2 - Operand 1 Fetch and Pre-Normalizing                |   |       |

| Step 3 - Divide Cycles                                      |   | 3-38  |

|                                                             | : | 3-38  |

|                                                             | • | 3-38  |

| Sequence 1C $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$    | • | 3-38  |

| Sequence $3C$                                               | • |       |

| R1 Cycle $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$       | • | 3-39  |

| FP Common Divide Cycles                                     | • | 3-39  |

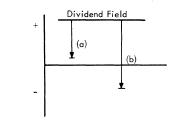

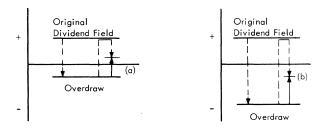

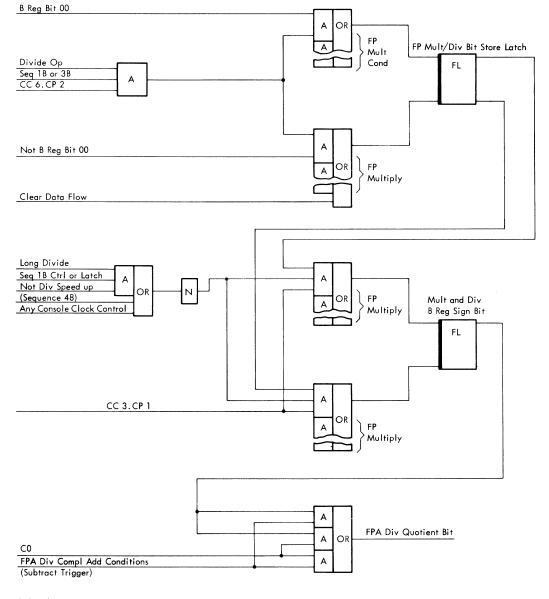

| Principles of FP Divide                                     | • |       |

| FP Common Divide, Single Arithmetic Cycles                  | • | 3-42  |

| FP Common Divide, Double Arithmetic Cycles                  | • | 3-43  |

|                                                             |   |       |

| APPENDIX A. POWERS OF 16                                    |   | Δ_ 1  |

| MILIUMA IONERS OF 10                                        | • |       |

#### ILLUSTRATIONS

| Figure | Title Pa                                             | age | Figure | Title                                                                              | Page |

|--------|------------------------------------------------------|-----|--------|------------------------------------------------------------------------------------|------|

| CHAPTE | R 1. INTRODUCTION                                    |     | 3- 5   | Example of FP Complement Add with                                                  |      |

| 1-1    | Floating-Point Format                                | - 1 |        | Recomplement (Opnd 1 Exp HI Condition)                                             | 3-10 |

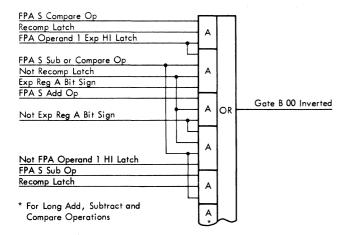

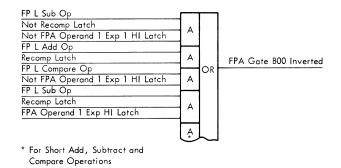

| 1- 2   | Floating-Point Instruction Details 1-                | - 6 | 3- 6   | Logic for Gate B00 Inverted on Long-Precision<br>Add, Subtract, Compare Operations | 3-15 |

| CHAPTE | R 2. FUNCTIONAL UNITS                                |     | 3- 7   | Example of Long-Precision Add (Opnd 1 Exp LO                                       |      |

| 2-1    | Exponent Arithmetic Data Flow                        | - 1 |        | Condition) $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                            | 3-16 |

| 2-2    | FP Sequence Controls and Latches                     | - 3 | 3-8    | Example of Long-Precision Complement Add with                                      |      |

| 2-3    | FP Medium-Speed Local Storage Read and Write         |     |        | Recomplement (Opnd 1 Exp HI Condition)                                             | 3-18 |

|        | Drives                                               | - 5 | 3- 9   | Principles of Long-Precision Multiply                                              | 3-23 |

| 2-4    | Typical Scratch Register Position 2-                 | - 7 | 3-10   | Single-Cycle Chart for Long-Precision Multiply                                     |      |

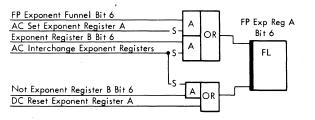

| 2- 5   | Typical Exponent Register A Position (Bit 6) 2-      | - 8 |        | (Precision = 10, 12, 14)                                                           | 3-24 |

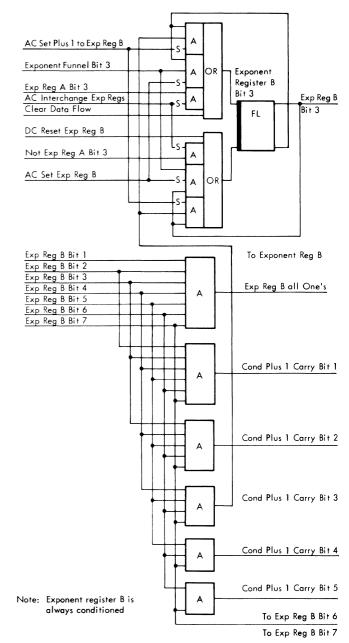

| 2- 6   | Typical Exponent Register B Position and Plus 1      |     | 3-11   | Single-Cycle Chart for Long-Precision Multiply                                     |      |

|        | Carry Generator                                      | - 9 |        | (Precision = 8)                                                                    | 3-30 |

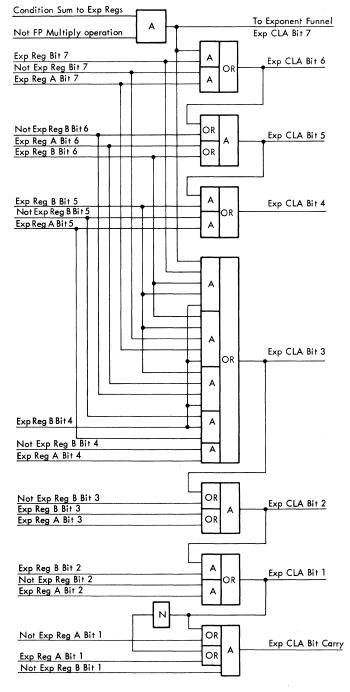

| 2- 7   | Exponent CLA                                         | -10 | 3-12   | Instructional Diagram of B Register Extension                                      |      |

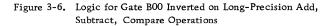

| 2-8    | Minus 1 Carry Generator                              | -11 |        | Sign Bit for Multiply Cycles                                                       | 3-32 |

| 2-9    | Exponent Funnel 2-                                   | -12 | 3-13   | Initial Shift Counter Values for Common Multiply                                   |      |

| 2-10   | FP Variable-Precision True/Criss-Cross Controls . 2- | -13 |        | Loop                                                                               | 3-32 |

| 2-11   | FP Underflow/Overflow Condition Detection 2-         | -15 | 3-14   | Single-Cycle Chart for Long-Precision Divide                                       |      |

| 2-12   | Control Checking                                     | -17 |        | (Precision = 10, 12, 14)                                                           | 3-34 |

| 2-13   | FP Significance and Divide Exceptions 2-             | -18 | 3-15   | Single-Cycle Chart for Long-Precision Divide                                       |      |

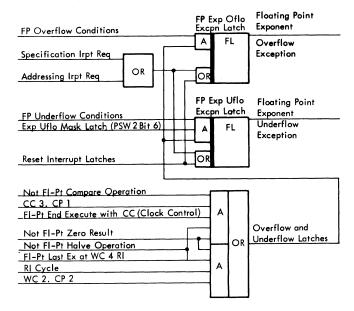

| 2-14   | Exponent Overflow and Underflow Exceptions 2-        | -19 |        | $(Precision = 8) \dots \dots \dots \dots \dots \dots \dots$                        | 3-38 |

|        |                                                      |     | 3-16   | Initial Shift Counter Values for FP Common                                         |      |

| CHAPTE | ER 3. PRINCIPLES OF OPERATION                        |     |        | Divide - Single Arithmetic Cycles                                                  | 3-39 |

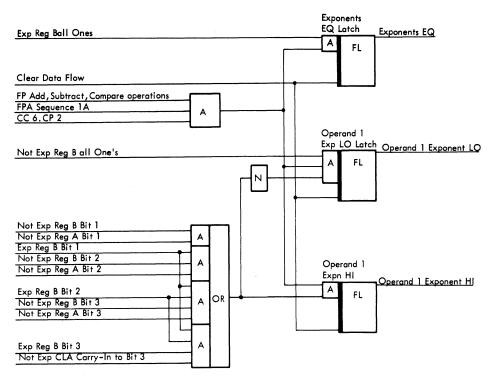

| 3-1    | Operand 1 Exponent HI, LO and EQ Latches 3-          |     | 3-17   | Initial Shift Counter Values for FP Common                                         |      |

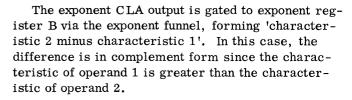

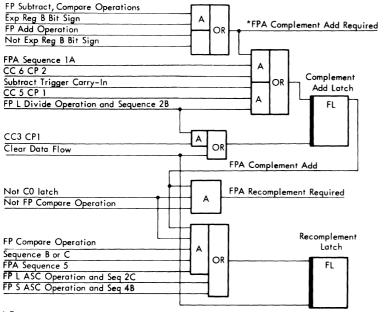

| 3-2    | FPA Complement and Recomplement Latches 3-           | - 5 |        | Divide - Double Arithmetic Cycles                                                  | 3-39 |

| 3- 3   | Logic for Gate B00 Inverted on Short-Precision       |     | 3-18   | Example of Full Reduction Cycle                                                    | 3-40 |

|        | Add, Subtract, Compare Operations 3-                 | - 8 | 3-19   | Examples of Combined Correction and Reduction                                      |      |

| 3- 4   | Example of FP Normalized Addition (Opnd 1            |     |        | Cycle                                                                              |      |

|        | Exp LO Condition)                                    | - 9 | 3-20   | FP Quotient Bit Controls                                                           | 3-41 |

|        |                                                      |     |        |                                                                                    |      |

#### ABBREVIATIONS

The following abbreviations are used in this manual.

| ALS<br>CPU<br>Dec<br>EQ<br>EXOR<br>FP<br>FPR<br>GPR<br>Hex<br>HI<br>HW<br>I-Fetch<br>LO<br>MSLS<br>Op<br>Opnd<br>PSW | Arithmetic and Logic Section<br>Central Processing Unit<br>Decimal<br>Equal<br>Exclusive OR<br>Floating-Point<br>Floating-Point Register<br>General-Purpose Register<br>Hexadecimal<br>High<br>Hardware (funnel)<br>Instruction-Fetch<br>Low<br>Medium-Speed Local Storage<br>Operation<br>Operand<br>Program Status Word |

|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| *                                                                                                                    | 1                                                                                                                                                                                                                                                                                                                         |

| SDR                                                                                                                  | Storage Data Register                                                                                                                                                                                                                                                                                                     |

| T/XC                                                                                                                 | True/Criss-Cross                                                                                                                                                                                                                                                                                                          |

Ċ,

#### PROPERTIES OF NUMBERS

Scientific and engineering applications demand extensive handling of numbers with values that vary from the very large to the very small. To allow for the handling of these numbers, and to obtain results with sufficient precision, registers in computers would need an excessively large capacity.

Since register size is generally limited, and the result of a calculation using very large or very small numbers is usually meaningful only in the significant digits, the floating-point (FP) system of arithmetic is applied to the calculations.

This system of representing numbers is, in effect, a shorthand method which allows the significant digits of a number to be used in a calculation and the magnitude of the number to be held separately from the calculation.

In decimal notation this type of operation is familiar. For example, the timing of computer operations is expressed in milliseconds, microseconds or nanoseconds. This expression produces a number in which extraneous zeros are removed and only relevant significant digits remain. Thus an operation that takes 0.000015 seconds is expressed as  $15 \times 10^{-6}$  seconds (15 microseconds) and an operation that takes a much shorter time, such as 0.000000015 seconds can be expressed, with the same ease, as  $15 \times 10^{-9}$  seconds (15 nanoseconds).

Similarly, large numbers may be expressed in this manner. For example, light travels approximately 6,000,000,000,000 miles in one year that is,  $6 \times 10^{12}$  miles.

In the foregoing examples, the significant digits and the power of ten to which they are raised may be expressed in a smaller number of positions than the original number.

It is usual in floating-point representation to place place the point immediately to the left of the mostsignificant digit. Thus 15 microseconds becomes  $.15 \times 10^{-4}$  seconds and 15 nanoseconds becomes  $.15 \times 10^{-7}$  seconds, while 6,000,000,000,000 miles becomes  $.6 \times 10^{13}$  miles.

The number of significant digits held determines the accuracy of the calculation and is called the "precision".

#### SYSTEM/360 FLOATING-POINT NUMBERS

- Floating-point numbers are recorded in the hexadecimal number system.

- The significant digits are recorded as hexadecimal fractions.

- The exponent is the value to which the base 16 is raised.

- The characteristic can be a number from 0 to 127. The characteristic has a value of exponent plus 64, giving a range of exponents of -64 to +63.

- Floating-point numbers are recorded in fixed-length format:

For short precision in a single word. For long precision in a double word.

- Bit 0 of either format denotes the sign of the fraction.

- Bits 1 to 7 of either format denote the characteristic.

- Bits 8 to 31 for short precision or bits 8 to 63 for long precision denote the fraction.

- Negative fractions are always carried in true form

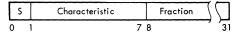

The format in which floating-point numbers are held is shown in Figure 1-1.

Chapter 1, Introduction and Functional Units, Form Y33-0001, shows that floating-point numbers are not expressed with a base of 10 as in the decimal system but use, instead, the hexadecimal system with a base of 16. Thus, numbers in System/ 360 format are expressed as a fraction to the base 16 times a power of 16, whereas decimal representation is a fraction to the base 10 times a power of 10.

The format chosen for System/360 floatingpoint data allocates seven binary digits to express

Short-Precision Floating-Point Format:

Long-Precision Floating-Point Format:

Figure 1-1. Floating-Point Format

the power or exponent. The allocation provides an allowable range of 0 to 127.

Since provision must be made for the representation of either positive or negative exponents, a system of expressing the exponent in "excess 64 arithmetic" is used. This is done by adding + 64 to each exponent and the result or characteristic is expressed in the seven binary digits allocated. This method allows both positive and negative exponents to be expressed as a positive binary number. Thus the characteristic is contained in seven digits allowing a range of 0 through + 64 to + 127, representing an exponent reange of - 64 through 0 to + 63 (as characteristic = exponent = + 64).

The format chosen for the fraction allows either 6 or 14 hexadecimal digits in the fraction and thus the range of numbers is from a fraction  $\times$  16<sup>63</sup> to a fraction  $\times$  16<sup>-64</sup>; the precision of expressing the fraction may range from the short-precision 6 hexadecimal digits to the long-precision 14 hexadecimal digits.

The sign of the floating-point number is held separately from both the fraction and characteristic and, as usual, is a single digit with a 1 representing a minus and a 0 representing a plus. The fraction is always in true form.

The following are sample normalized short floating-point numbers. The last two rows represent the smallest and the largest positive normalized numbers.

$= + 1/16 \times 16^{-64} = 0 \ 0000000 \ 0001 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000 \ 0000$

#### Hexadecimal and Decimal Conversion (Examples)

Refer to the Appendix of the manual for a Powers of 16 table.

**Conversion Example 1**

Convert the hexadecimal (hex) number 1B2.3C to decimal (dec) notation.

Result:

$$(1 \times 16^{2}) + (11 \times 16^{1}) + (2 \times 16^{0}) + (3 \times 1/16^{1}) + (12 \times 1/16^{2})$$

= 256 + 176 + 2 + 0.1875 + 0.0469

= 434.2344

Conversion Example 2

Convert the decimal number 434.2344 to hexadecimal notation.

a. Convert 434 to hexadecimal.

| 434 ÷ 16  | = 27 and a remainder of <u>2</u>     |

|-----------|--------------------------------------|

| 27 ÷ 16   | = 1 and a remainder of <u>B</u> (11) |

| 1 ÷ 16    | = 0 and a remainder of <u>1</u>      |

| 434 (dec) | = 1B2 (hex)                          |

b. Convert 0.2344 to hexadecimal.

| 0.2344 x 16  | = <u>3</u> . 7504 |

|--------------|-------------------|

| 0.7504 x 16  | = <u>12</u> .0064 |

| 0.0064 x 16  | = <u>0</u> . 1024 |

| 0.2344 (dec) | = 0.3C0 (hex)     |

c. Combine the results of the above two steps.

434.2344 (dec) = 1B2. 3C (hex)

Conversion Example 3

Convert the decimal number 2277.302 to a System/ 360 short-precision floating-point number.

a. Convert 2277 to hexadecimal.

| 2277 ÷ 16  | = 142 and a remainder of <u>5</u>           |

|------------|---------------------------------------------|

| 142 ÷ 16   | = 8 and a remainder of $\underline{E}$ (14) |

| 8÷16       | = 0 and a remainder of $\underline{8}$      |

| 2277 (dec) | = 8E5 (hex)                                 |

b. Convert 0.302 to hexadecimal.

| 0.302 x 16  | = <u>4</u> . 832  |

|-------------|-------------------|

| 0.832 x 16  | = <u>13</u> . 312 |

| 0.312 x 16  | = <u>4</u> . 992  |

| 0.302 (dec) | = 0.4D5 (hex)     |

c. Combine results of steps (a) and (b) and express as a fraction multiplied by a power of 16 (exponent).

2277.302 (dec) = 8E5.4D5 (hex) =  $0.8E54D5 \times 16^3$  (hex)

d. Convert the exponent to binary representation and add to 64 to form the characteristic.

Characteristic = 1000011, that is (64 + 3)

e. Assemble sign (bit 0), characteristic (bits 1 to 8) and fraction (bits 9 to 31) to form System/360 short-precision floating-point number.

Result = 0 1000011 1000 1110 0101 0100 1101 0101

#### Conversion Example 4

Convert to decimal notation the following System/ 360 short-precision floating-point numbers.

0 1000010 0001 0101 1100 0000 0000 0001

a. Obtain the exponent in decimal form.

Characteristic = 66Exponent = 66 - 64 = +2

b. Express each unit of the fraction as a decimal number times a power of 16.

Fraction =  $(1 \times 16^{-1}) + (5 \times 16^{-2}) + (12 \times 16^{-3}) + (1 \times 16^{-6})$

c. Multiply each unit of the fraction by 16 to the power of the exponent. (Add exponents.)

```

Result = 16^2 x Fraction

Result = (1 \times 16^1) + (5 \times 16^0) + (12 \times 16^{-1}) + (1 \times 16^{-4})

```

- d. Calculate result (using if necessary the Powers of 16 table).

- Result =  $16 + 5 + (12 \times 0.0625) + (0.000015)$ = 21.750015 (to 6 decimal places)

- e. Add sign.

Result = + 21. 750015

Conversion Example 5

Convert to decimal notation the following System/ 360 short-precision floating-point number.

1 0111110 1111 1001 0000 0001 0000 0000

a. Obtain the exponent in decimal form.

Characteristic = 62Exponent = 62 - 64 = -2

b. Express each unit of the fraction as a decimal number times a power of 16.

Fraction =  $(15 \times 16^{-1}) + (9 \times 16^{-2}) + (1 \times 16^{-4})$

c. Multiply each unit of the fraction by 16 to the power of the exponent. (Add exponents.)

Result =  $16^{-2}$  x Fraction =  $(15 \times 16^{-3}) + (9 \times 16^{-4}) + (1 \times 16^{-6})$ = 0.003 662 109 375 + 0.000 137 101 + 0.000 000 059 604 = 0.003 799 498 180 = 3.7995 x 10^{-3}

d. Add sign.

Result =  $-3.7995 \times 10^{-3}$

#### Terms Used in System/360 FP Arithmetic

<u>Characteristic</u>: The exponent plus 64, expressed as a seven-bit binary number.

Exponent: The number (or power) by which the base (or radix) 16 is raised.

<u>FP Number</u>: The floating-point number consists of a sign bit, a seven-binary-bit characteristic and either a 6- or 14- hexadecimal-digit fraction.

<u>Fraction</u>: The fraction is either 6 or 14 hexadecimal digits, numbered from 0 to 5 or 0 to 13 respectively. The radix point is in front of the leftmost digit.

<u>Guard Digit</u>: A hexadecimal digit which is preserved in the (hexadecimal) digit-6 position of shortprecision results, to take part in the postnormalizing process if it is required by the instruction.

<u>Hexadecimal</u>: A number system using a base (or radix) of 16.

<u>Normalization</u>: The process of shifting left the hexadecimal digits of the fraction portion of an unnormalized number until the leftmost hexadecimal digit becomes significant. The characteristic is reduced by one for each shift left executed. Note that the first three binary digits may be zero, provided that the first hexadecimal digit is significant.

<u>Pre-normalization</u>: The process of normalizing operands prior to performing arithmetic operations.

<u>Post-normalization</u>: The process of normalizing results.

<u>Precision</u>: The accuracy with which the fraction is expressed and a measure of the length of the operands and results. Short-, variable- and longprecision operands contain 6, 8 to 14, and 14 hexadecimal digits respectively.

<u>Radix Point</u>: A general term for use with any number system to describe a function equivalent to that of the decimal point in decimal notation.

<u>Un-normalized Number</u>: A number in which the fraction digits contain one or more hexadecimal zeros prior to the first significant hexadecimal digit.

Variable-Precision: A preset precision (determined by a console switch) which defines the number of hexadecimal digits which are to be used in calculations. The precision switch on System/360 Model 44 allows a precision of 8, 10, 12 or 14 hexadecimal digits, and causes long operands to be truncated to the defined precision on the cycle when low-order digits are fetched.

#### RULES FOR FLOATING-POINT ARITHMETIC

#### Multiply

- The exponents are added

- The fractions are multiplied.

- If necessary, the result is normalized.

#### Example (in decimal notation):

```

\begin{array}{ll} (0.25 \times 10^4) \times (0.33 \times 10^{-7}) \\ \mbox{Add exponents:} & 4+(-7)=-3 \\ \mbox{Multiply fractions:} & 0.25 \times 0.33=0.0825 \\ \mbox{Result:} & 0.0825 \times 10^{-3} \\ \mbox{Normalized:} & 0.825 \times 10^{-4} \\ \end{array}

```

This sequence is executed with one instruction.

#### Divide

- The divisor exponent is subtracted from the dividend exponent.

- The fractions are divided.

- If necessary, the result is normalized.

Example (in decimal notation):

$\begin{array}{ll} (0.222 \ x \ 10^{-2}) \ + \ (0.4 \ x \ 10^{-5}) \\ \text{Subtract exponents:} & -2 - (-5) = + \ 3 \\ \text{Divide fractions:} & 0.222 \ + \ 0.400 = 0.555 \\ \text{Result:} & 0.555 \ x \ 10^3 \end{array}$

Normalization not necessary (in this example).

#### Shifting

- Shift Left: for each digit position shifted, the value of the exponent is reduced by one.

- Shift Right: for each digit position shifted, the value of the exponent is increased by one.

Examples (in decimal notation);

| a. | Shift-left-three: | $.000073 \times 10^{7}$   |

|----|-------------------|---------------------------|

|    | Result =          | .073000 x 10 <sup>4</sup> |

| ь. | Shift-right-two:  | .560000 x 10 <sup>6</sup> |

|    | Result =          | .005600 x 10 <sup>8</sup> |

|    |                   |                           |

#### Add and Subtract

- The number with the smaller exponent is shifted to the right and the value of its exponent increased until the values of both exponents are equal.

- The fractions are added (or subtracted).

- The exponent remains unchanged.

- If specified, the result is normalized.

Example (using decimal notation):

Add  $0.00217 \times 10^{10}$  and  $0.8 \times 10^{3}$

1. The number with the smaller exponent is shifted right until exponents become equal.

$\begin{array}{c} 0.00217 \\ x 10^{10} \\ 0.0000008 \\ x 10^{10} \end{array}$

2. The fractions are added (or subtracted).

0.00217008 x 10<sup>10</sup>

3. If specified, the result is normalized.  $0.217008 \times 10^8$

#### FLOATING-POINT EXCEPTIONS

• Normal exceptions apply to FP instructions and data:

Operation. Protection. Addressing. Specification (Basic).

• Additional exception conditions are used with the FP feature:

Specificiation (floating-point). Exponent overflow. Exponent underflow. Significance. Floating-point divide.

Exceptional instructions, data, or results cause a program interrupt. When the interrupt occurs, the current Program Status Word (PSW) is stored as an old PSW, and a new PSW is obtained. The interrupt code in the old PSW identifies the cause of the interrupt. The following exceptions cause a program interrrupt in floating-point arithmetic.

1. Operation Exception: Occurs when the floatingpoint feature is not installed, and an attempt is made to execute a floating-point instruction. The instruction is suppressed and the condition code, data in registers, and storage data are unchanged.

- 2. Protection Exception: Occurs if the storage protect feature is installed and the storage key of a store-instruction location does not match the protection key in the PSW. The operation is suppressed and the condition code, data in registers, and storage data are unchanged.

- 3. Addressing Exception: Occurs when an address designates a location outside the available storage for the installed system. The operation is terminated and the resultant data and the condition code, if affected, are unpredictable and should not be used for further computation.

- 4. Specification Exception: Occurs when a short operand is not located on a 32-bit boundary, a long operand is not located on a 64-bit boundary, or a floating-point register address other than 0, 2, 4 or 6 is specified. The instruction is suppressed, and the condition code, data in registers, and storage data are unchanged.

- 5. Exponent Overflow Exception: Occurs when the result exponent of an addition, subtraction, multiplication or division overflows (that is, is greater than +63) and the result fraction is not zero. The operation is terminated; the resultant data is unpredictable and should not be used for further computation. The condition code is set to binary 11 for addition or subtraction and remains unchanged for multiplication and division.

- 6. Exponent Underflow Exception: Occurs when the result exponent of an addition, subtraction, multiplication or division underflows (that is, is less than -64) and the result fraction is not zero. A program interrupt occurs if the exponent underflow mask bit is one. The operation is completed by replacing the result with a true zero. The condition code is set to 00 for addition and subtraction and remains unchanged for multiplication and division. The state of the mask bit does not affect the result.

- 7. Significance Exception: Occurs when the result fraction of an addition or subtraction is zero. A program interrupt occurs if the significance mask bit is one. The mask bit also affects the result of the operation. When the significance mask bit is zero, the operation is completed without further change to the characteristic of the result. In either case, the condition code is set to 00.

- 8. Floating-Point Divide Exception: Occurs when a division by a number with zero fraction is attempted. The division is suppressed and the condition code, data in registers, and storage data are unchanged.

INSTRUCTIONS AND INSTRUCTION FORMAT

- RR and RX formats are used for FP instructions.

- The R1 and R2 fields must specify floating-point register 9, 2, 4 or 6.

- For long-precision instructions the actual precision is determined by the setting of the variable-precision switch.

The standard RR and RX formats are used in the floating-point instruction set.

For floating-point instructions, R1 and R2 fields must specify one of the Floating-Point Registers (FPR's), 0, 2, 4 or 6, that are provided with the feature. If either R1 or R2 specifies other than one of these FPR's, a specification exception and a program interrupt occur.

In common with the standard instruction set, results replace the first operand, except for storing operations, when the second operand is replaced.

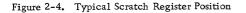

Figure 1-2 lists the floating-point instructions, their mnemonics, operation (op) codes and formats, and the exceptions that cause a program interrupt.

#### VARIABLE-PRECISION FEATURE

- Applies to long-precision instructions.

- Precision of 8, 10, 12 or 14 digits can be selected.

- Operands are truncated on operand-fetch.

- Truncated positions are replaced by zeros.

- Results are stored in long-precision format (without truncation) regardless of the setting of the variable-precision switch.

- Results are truncated when they are next fetched.

- Truncation does not occur on console display.

The Model 44 user may specify that long-precision instructions shall be executed with less than 14 digits of precision. Specifying is made by means of a console rotary switch marked 'floating-point precision'. This switch has four positions (14, 12, 10, 8) which refer to the number of hexadecimal digits of the fraction that are to be processed by longprecision instructions.

When the switch is set to 14, the full 14-digit (56-bit) fraction is processed and results of floatingpoint instructions are identical to those obtained on other System/360 Models with floating-point facili-

Introduction 8/66 1-5

| Name                   | Precision | Туре     | Mnemonic | Op Code | Exceptions     |

|------------------------|-----------|----------|----------|---------|----------------|

| Load                   | Long *    | RR       | LDR      | 28      | s              |

| Load                   | Long *    | RX       | LD       | 68      | A, S           |

| Load                   | Short     | RR       | LER      | 38      | s              |

| Load                   | Short     | RX       | LE       | 78      | A, S           |

| Load and Test          | Long *    | RR, C    | LTDR     | 22      | S              |

| Load and Test          | Short     | RR, C    | LTER     | 32      | S              |

| Load Complement        | Long *    | RR, C    | LCDR     | 23      | S              |

| Load Complement        | Short     | RR, C    | LCER     | 33      | s              |

| Load Positive          | Long *    | RR, C    | LPDR     | 20      | s              |

| Load Positive          | Short     | RR, C    | LPER     | 30      | s              |

| Load Negative          | Long *    | RR, C    | LNDR     | 21      | s              |

| Load Negative          | Short     | RR, C    | LNER     | 31      | s              |

| 2000 Hoganite          | 311011    |          | ENER     | 01      | 5              |

| Add Normalized         | Long *    | RR, C, N | ADR      | 2A      | S, U, E, LS;   |

| Add Normalized         | Long *    | RX, C, N | AD       | 6A      | A, S, U, E, LS |

| Add Normalized         | Short     | RR, C, N | AER      | 3A      | S, U, E, LS    |

| Add Normalized         | Short     | RX, C, N | AE       | 7A      | A, S, U, E, LS |

| Add Un-normalized      | Long *    | RR, C    | AWR      | 2E      | S, E, LS       |

| Add Un-normalized      | Long *    | RX, C    | AW       | 6E      | A, S, E, LS    |

| Add Un-normalized      | Short     | RR, C    | AVR      | 3E      | S, E, LS       |

| Add Un-normalized      | Short     | RX, C    | AV       | 7E      | A, S, E, LS    |

| Subtract Normalized    | Long *    | RR, C, N | SDR      | 2B      | S, U, E, LS    |

| Subtract Normalized    | Long *    | RX, C, N | SD       | 6B      | A, S, U, E, LS |

| Subtract Normalized    | Short     | RR, C, N | SER      | 3B      | S, U, E, LS    |

| Subtract Normalized    | Short     | RX, C, N | SE       | 7B      | A, S, U, E, LS |

| Subtract Un-normalized | Long *    | RR, C    | SWR      | 2F      | S, E, LS       |

| Subtract Un-normalized | Long *    | RX, C    | SW       | 6F      | A, S, E, LS    |

| Subtract Un-normalized | Short     | RR, C    | SUR      | -3F     | S, E, LS       |

| Subtract Un-normalized | Short     | RX, C    | SU       | 7F      | A, S, E, LS    |

| Compare                | Long *    | RR, C    | CDR      | 29      | s, 3, 1, 13    |

| Compare                | Long *    | RX, C    | CD       | 69      | A, S           |

| Compare                | Short     | RR, C    | CER      | 39      | s'             |

| Compare                | Short     | RX, C    | CE       | 79      | A, S           |

| Halve                  | Long *    | RR       | HDR      | 24      | s s            |

| Halve                  | Short     | RR       | HER      | 34      | s              |

| harte                  | 511011    |          | TIER     | 54      | 5              |

| Multiply               | Long *    | RR, N    | MDR      | 2C      | S, U, E        |

| Multiply               | Long *    | RX, N    | MD       | 6C      | A, S, U, E     |

| Multiply               | Short     | RR, N    | MER      | 3C      | S, U, E        |

| Multiply               | Short     | RX, N    | ME       | 7C      |                |

| memply                 | JION      | 121,11   |          |         | A, S, U, E     |

| Divide                 | Long *    | RR, N    | DDR      | 2D      | S, U, E, FK    |

| Divide                 | Long *    | RX, N    | DD       | 6D      | A, S, U, E, FK |

| Divide                 | Short     | RR, N    | DER      | 3D      | S, U, E, FK    |

| Divide                 | Short     | RX, N    | DEK      | 7D      | A, S, U, E, FK |

| Statue                 | JION      | N, N     | DL       | ,0      | ~, 3, U, E, FN |

| Store                  | Long *    | RX       | STD      | 60      | P, A, S        |

| Store                  | Short     | RX       | STE      | 70      | P, A, S        |

|                        | 511011    |          | JIL      | /0      | ', ~, 3        |

#### Legend:

Addressing exception Condition code is set A C

E Exponent-overflow exception FK Floating-point divide exception

LS Significance exception

P Protection exceptionS pecification exception

U \*

Exponent-underflow exception Precision determined by FP precision switch

N Normalized operation

Figure 1-2. Floating-Point Instruction Details

1-6 8/66 Model 44 Floating Point FETO

ties. At the 12, 10 and 8 settings, all long-precision instructions of the floating-point set operate on fractions that are truncated to 12, 10 or 8 digits respectively; these results will normally differ in precision, and possibly in significance, from those of other models with floating-point facilities. Short-precision instructions are unaffected by the switch.

Truncation occurs at the ABC funnel at the time that operands are fetched from core storage. Since the least-significant halves of the FPR's are located in extension storage, the least-significant half of all floating-point operands (whether located in main storage or in an FPR) must pass through the Storage Data Register (SDR) and ABC funnel. Truncation applies in this way to all long-precision operands, whether fetched for RR or for RX instructions. Once truncation has occurred, the operand(s) may be extended with zeros to a full 56-bit fraction, and processed as such; this processing is amplified in the sections of the manual concerning specific instructions. It follows that where shifting has occurred (to align fractions whose exponents differ) non-zero results in the low-order bytes may be placed in the result register, and manual display of FPR's may show a full-length non-zero fraction, regardless of the setting of the variable-precision switch.

In order to fetch the contents of an FPR, one of the 22 long-precision FP instructions must be given. Since all these instructions truncate on fetching, the Central Processing Unit (CPU) program can never access fraction bytes beyond the selected precision. For the programmer, therefore, results may be considered to be stored truncated.

÷ •

#### CHAPTER 2. FUNCTIONAL UNITS

#### FLOATING-POINT DATA FLOW

- Floating-point registers are used instead of the general-purpose registers for storing floating-point operands.

- FP fraction arithmetic is performed by the basic CPU arithmetic and logic data flow.

- Two registers are added to the basic arithmetic data flow, the AX register and the floating-point scratch register.

- A separate exponent arithmetic data flow is provided for characteristic handling and consists of: Exponent registers A and B Exponent carry look-ahead Exponent funnel Plus 1 and minus 1 carry generators.

- Four FP sequence latches are added for control purposes.

The floating point feature provides additional registers, data flow and control circuitry to enable the floating-point instructions to be executed. These additions cause the console facilities and the checking features of the Model 44 to be extended.

Floating-point operands are not stored in the General-Purpose Registers (GPR's) but are contained in separate FPR's which are provide with the floating point feature. These FPR's are numbered 0, 2, 4 and 6 and can contain long-precision (double-word) floating-point operands. Note that GPR's are used, however, during the I-fetch of RXtype floating-point instructions.

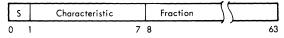

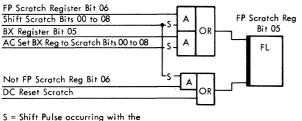

The fraction arithmetic is performed in the basic Arithmetic and Logic Section (ALS) of the CPU but a separate section of data flow is provided for characteristic arithmetic. This section of the data flow (shown in Figure 2-1 and in FEMD Figure 1001) contains the following units:

Exponent funnelExponent CLAExponent register APlus 1 carry generatorExponent register BMinus 1 carry generator

This additional section of the data flow is logically equivalent to the main arithmetic section; the exponent registers A and B and the exponent CLA perform the same logical function on input data as the A and B Registers and the main CLA.

Two additional registers, each of 32 bits, are provided in the main data flow to facilitate the handling of long-precision operands. The registers are the AX register (which can be accessed only by a 32-bit interchange with the A register) and the FP scratch register (which can be loaded from the B register and read out to the Hardware (HW) funnel).

The floating-point instructions in general require lengthy execute times, and four additional FP sequence latches are used to provide adequate controls for the execute phase of these instructions.

During the execute phase of these instructions, the normal rules for single-cycle operation, apply as stated in "Console" in FEMM <u>IBM System/360</u> <u>Model 44</u>, Form Y33-0007. The additional data flow registers, all FPR's, and the status of the FP sequence latches and their control latches can be displayed from the console. The FPR's and AX register may be stored into, also from the console.

The FP sequence latches are subject to the same type of control check as the basic sequence latches. Other program checks are provided for the exceptions which can occur with floating-point operation; these exceptions include specification (floatingpoint), significance, FP divide, exponent overflow and exponent underflow.

Figure 2-1. Exponent Arithmetic Data Flow

#### CHARACTERISTIC ARITHMETIC

- Characteristic arithmetic is performed in the exponent register area.

- The fraction sign is stored in this area but does not take part in characteristic arithmetic.

- Any carry from characteristic arithmetic is preserved for exponent underflow/overflow detection circuits.

- Arithmetic processes include: Characteristic addition Characteristic subtraction Characteristic incrementing Characteristic decrementing

The characteristic arithmetic is performed in the exponent register area (Figure 2-1). The whole characteristic (fraction sign and characteristic) is brought from the main data flow to exponent registers A and B via the exponent funnel.

Characteristic arithmetic is, however, performed only on bits 01 to 07 and any carries are preserved in the exponent registers. Thus, these registers are nine bits wide and consist of bit 'sign', bit 'carry' and bits 01 to 07.

The arithmetic processes which may be performed by the exponent register area are: characteristic addition, subtraction, incrementing and decrementing. The result of this arithmetic, formed in exponent register B and gated to the HW funnel at the appropriate time, consists of the fraction sign (bit 'sign') and the characteristic (bit 01 to 07). Bit 'carry' is used for exception detection and is not gated out as part of the characteristic result.

Thus, the different bus widths as shown in Figure 2-1, contain seven, eight or nine bits, depending on their use. Inputs and outputs of the exponent register area are seven data bits with the fraction sign bit. Inputs to each of the three carry units are seven data bits while the output of these same carry units is eight bits (seven data bits and a carry bit).

#### Characteristic Addition

• Used for the multiply instruction.

The exponent register area is used for characteristic addition for the multiply operation. For this operation the two characteristics are added and 64 is subtracted from the result (using 'excess 64 arithmetic') to obtain the true result characteristic.

| Example                 |       | Exponent |

|-------------------------|-------|----------|

| Characteristic 1:       | 98    | + 34     |

| Characteristic 2:       | _32_+ | - 32 +   |

| Sum of characteristics: | 130   |          |

| Less 64:                | 64    |          |

| Result characteristic:  | 66    | + 2      |

#### Characteristic Subtraction

- Used for the divide instruction.

- Used for exponent matching for add, subtract, and compare instructions.

The exponent register area is used for characteristic subtraction associated with the divide instruction. One characteristic is subtracted from the other and 64 is added to the result ('excess 64 arithmetic') to provide the true result characteristic.

#### Example

|                                          |            | Exponent |

|------------------------------------------|------------|----------|

| Characteristic 1:                        | 73         | + 9      |

| Characteristic 2:                        |            | - 15 -   |

| Difference of characteristics:<br>Add 64 | 24<br>64 + |          |

| Result Characteristic:                   | 88         | + 24     |

For the add, subtract and compare instructions, an arithmetic difference between the two characteristics is needed to determine the number of shifts required for matching the exponents of the two operands; the difference is obtained by subtraction.

#### Characteristic Incrementing

- Used during shift-right-four operations (digit shifting).

- Used for some characteristic adjustment during the divide instruction.

For digit shifting of a fraction to the right, the corresponding increment of one must be performed on the exponent for each position shifted. This function can be performed on a characteristic in exponent register B by the plus 1 carry generator.

#### Characteristic Decrementing

- Used during shift-left-four operations (digit shifting).

- Used for some characteristic adjustment during the divide instruction.

For digit shifting of the fraction to the left, the corresponding decrement of one must be performed on the exponent for each position shifted. This function can be performed on a characteristic in exponent register B by the minus 1 carry generator.

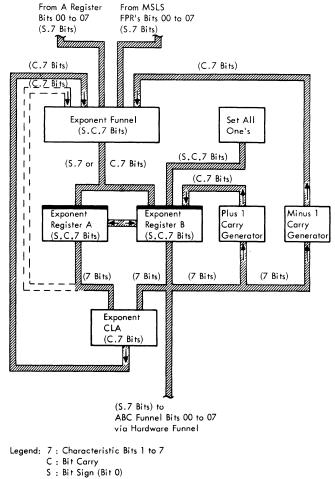

#### CONTROL COMPONENTS

- Lengthy execute times require additional sequence latches.

- Four additional FP sequence latches (A, B, C, D) are required.