File Number S360-01 Form A24-3510-0

## Systems Reference Library

# IBM System/360 Model 25 Functional Characteristics

This reference publication augments the <u>IBM System/360</u> <u>Principles of Operation</u>, Form A22-6821. It describes the relationship of the Model 25 to other System/360 models: system capabilities, system control panel, input/output channels and integrated I/O attachments, operations, instruction timings, and system features.

The reader should have a knowledge of the System/360 as defined in the <u>IBM System/360 Principles of Operation</u>. IBM publications relating to the Model 25 are <u>IBM</u> <u>System/360 Model 25, 1401/1460 and 1440 Compatibility</u> <u>Features</u>, Form A24-3512, and <u>IBM System/360 Model 25</u> <u>Configurator</u>, Form A24-3511. Other literature applicable to the Model 25 is listed in the <u>IBM</u> <u>System/360 Bibliography</u>, Form A22-6822, and the <u>IBM</u> <u>System Summary</u>, Form A22-6810.

## First Edition (January 1968)

Significant changes or additions to the specifications contained in this publication will be reported in subsequent revisions or Technical Newsletters.

Copies of this and other IBM publications can be obtained through IBM Sales Offices. This manual has been prepared by the IBM Systems Development Division, Product Publications, Dept. 171, P.O. Box 6, Endicott, N.Y. 13760 A form has been provided at the back of this publication for readers' comments. If the form has been removed, comments may be addressed the same as above.

International Business Machines Corporation 1968

$$\odot$$

| TOW OWOMEN (200 NODEL 20 EVERAMIONAL                    | INTEGRATED DISK ATTACHMENT CONTROL      |

|---------------------------------------------------------|-----------------------------------------|

| IBM SYSTEM/360 MODEL 25 FUNCTIONAL<br>CHARACTERISTICS 5 | (DAC), IBM 2311 63                      |

| CHARACTERISTICS                                         | (DAC), IDA 2511                         |

| System Features 5                                       | Optional Features 63                    |

| System Control 9                                        | IBM 2311 Disk Storage Drive 63          |

| Model-Dependent Implementation of                       | Addressing                              |

| System/360 Functions 10                                 | Disk-Storage Operation 74               |

|                                                         | Operation Commands                      |

| SYSTEM CONTROL PANEL                                    | Status Information                      |

|                                                         | Sense Information                       |

| Indicators or Displays 11                               | Special Functions                       |

| CPU Status Indicators                                   | Track Orientation                       |

| Operator Control Section                                | Defective Disk-Pack Surfaces            |

| Operator Intervention Section 14                        | Optional Features, Operation            |

| Customer Engineering Controls 17                        | Error Recovery Procedures               |

| Use Meter (CPU) · · · · · · · · · · · · · · · · · · ·   | Resets, DAC and/or 2311 Unit            |

|                                                         | Use Meter (2311)                        |

| CONSOLE PROCEDURES                                      | 036 Meter (2511)                        |

|                                                         | IBM 2540 CARD READ-PUNCH AND            |

| System Initialization 21                                | INTEGRATED 2540 ATTACHMENTS             |

|                                                         | INTEGRATED 2940 ATTACIMENTS             |

| SPECIAL AND OPTIONAL FEATURES 23                        | Special Features                        |

|                                                         | Keys, Switches, and Indicators 112      |

| INTEGRATED INPUT/OUTPUT                                 | Reader Operation                        |

| CHARACTERISTICS                                         | Punch Operation                         |

| CHARACIERISTICS                                         | Punch-Feed-Read Operation               |

| Integrated Device Addressing 25                         | Termination Operations                  |

| Integrated Device Addressing 25                         | Operation Commands                      |

| CONCOLE DELNMED KENDOLDD 20                             | Unit-Status Bytes                       |

| CONSOLE PRINTER-KEYBOARD                                |                                         |

| Your and Table stand                                    | Sense Bytes                             |

| Keys and Indicators                                     | Programming Timing Information          |

| Addressing                                              | Status-Byte Bit Combinations            |

| Program-Controlled Operations 29                        | Possible Combinations of Sense Bits135  |

| Status Byte                                             | Suggested Operating and Restart         |

| Channel-Status Byte                                     | Procedures                              |

| Sense Byte                                              | Use Meter (2540)                        |

| Manual Alter/Display                                    |                                         |

| Logout                                                  | INPUT/OUTPUT CHANNEL CHARACTERISTICS140 |

| Suggested Restart Procedures 37                         |                                         |

|                                                         | Standard I/O Interface                  |

|                                                         | Channel Device Addressing               |

| INTEGRATED 1403 PRINTER ATTACHMENT 39                   | Input/Output Devices for Channel 141    |

|                                                         | Multiplexer Channel                     |

| Special Features                                        | Selector Channel                        |

| Description 40                                          |                                         |

| Printer Keys and Indicators 47                          | APPENDIX A: AUXILIARY STORAGE MAPS146   |

| Addressing                                              |                                         |

| Commands                                                | APPENDIX B: CODES                       |

| Status Byte                                             |                                         |

| Sense Byte                                              | APPENDIX C: TIMINGS                     |

| Printing Speeds                                         |                                         |

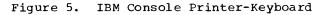

| Programming Timing Information 55                       | System/360 Model 25 Instruction         |

| Halt I/O to Integrated 1403 56                          | Timings                                 |

| Possible Status-Byte Bit Combinations . 57              | I/O Timing Tables                       |

| Suggested Restart Procedures 59                         |                                         |

| Use Meter (1403) 62                                     | INDEX                                   |

| Resets                                                  |                                         |

|                                                         |                                         |

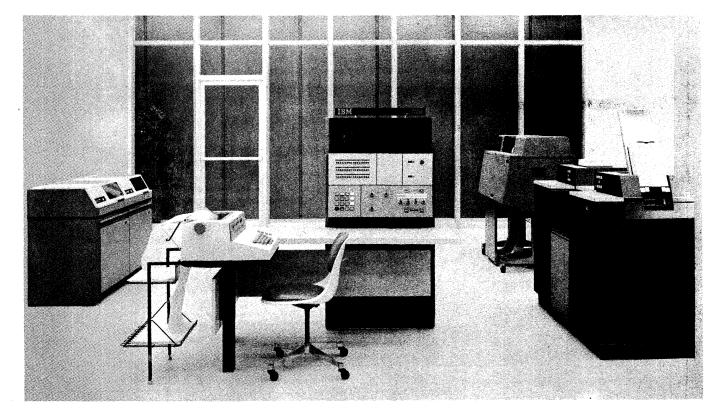

The various models and input/output configurations of the IBM System/360 series of data processing systems cover the entire range of commercial and scientific data handling requirements. Within the storage capacity, processing speed, and types of I/O devices that can be attached, compatibility is maintained throughout the System/360 line.

The operating performance of the System/360 Model 25 lies in a range between the Model 20 and the Model 30. Some overlapping of system capabilities (within the storage and input/output facilities of the Model 25) allows for expansion of your computing system to match your company's growth.

The console printer-keyboard, which is required on all models, provides for low-speed, low-volume input/output. Considerable job flexibility is provided with the integrated attachment features for the IBM 1403 Printer, IBM 2540 Card Read-Punch, and up to four IBM 2311 Disk Storage Drives. With program storage of 16K, 24K, 32K, or 48K, and the wide choice of I/O equipment that can be attached, the Model 25 provides data handling capabilities for diversified applications in virtually all data processing fields.

Several programming support systems are available for the Model 25. Refer to the <u>IBM System/360 Bibliography</u>, Form A22-6822, for abstracts of the IBM publications that apply to the Model 25.

Additional special and optional features are available for specialized tasks such as emulation of the IBM 1401, 1440, and 1460 data processing systems, program-controlled communications between CPU's, etc.

This publication is intended as a reference for users of the System/360 Model 25: only items that are unique to the Model 25 are discussed in detail. For this reason, a comprehensive knowledge of the System/360 series is necessary. This information can be found in the <u>IBM</u> <u>System/360 Principles of Operation</u>, Form A22-6821.

## SYSTEM FEATURES

ED25

The System/360 Model 25 central processing unit (CPU) is available in four program-storage sizes.

| System/360<br>Model | Progran<br>Capacit |       | ıge   |

|---------------------|--------------------|-------|-------|

| D25                 | 16,384             | bytes | (16K) |

| DC25                | 24,576             | bytes | (24K) |

| E25                 | 32,768             | bytes | (32K) |

Each model of the System/360 Model 25 is equipped with the following standard or required features.

49,152 bytes (48K)

System Control Panel IBM 1052 Printer-Keyboard (Model 7) Standard Instruction Set (fixed-point operations) Commercial Instruction Set (decimal operations).

Optional and special features available for the Model 25, which are described in detail later in this publication and/or in the <u>System/360 Principles of Operation</u>, include:

Scientific Instruction Set (floating-point operations) Universal Instruction Set (standard, commercial, and scientific instruction sets, plus the storage protection feature) 1403 Attachment Feature 2311 Attachment Feature 2540 Attachment Feature Multiplexer Channel (32 subchannels) Selector Channel 1401/1460 Compatibility 1440 Compatibility Direct Control External Interrupt Interval Timer Storage Protection

Some of these features are mutually exclusive: the installation of one precludes the use of another. This is the case, for example, with the multiplexer and selector channels. Some options require the presence of other features (i.e., storage protection feature is necessary for the universal instruction set). Still other features have subfeatures, etc. Information that clarifies these various features is in applicable sections of this publication. Also, refer to the <u>IBM</u> System/360 Model 25 Configurator, Form A24-3511, for an overall view of system features. The <u>IBM System/360 Input/Output</u> <u>Configurator</u>, Form A22-6823, lists the control units and input/output devices that can be attached to the Model 25 through the multiplexer or selector channel interface.

## INPUT/OUTPUT ATTACHMENTS

The System/360 Model 25 provides for integrated attachment of a group of commonly used I/O devices. An <u>integrated</u> <u>attachment</u> is an I/O control unit that is incorporated within the processing unit. It provides for the control and the data transfer for a specific I/O device.

These attachments do not connect to a standard I/O channel, but they are program-controlled as if they were. The devices are addressed using channel and device addresses, and they respond with the same status conditions.

System/360 input/output multiplexer or selector channel special features are also available to handle a wide range of additional I/O devices.

The following are the specific devices for which integrated attachments are provided. These features are described in detail in the <u>Integrated I/O</u> <u>Characteristics</u> section.

- 1. IBM 1052 Printer-Keyboard (Model 7): This device and its integrated attachment in the processing unit are required features on the Model 25.

- 2. <u>IBM 1403 Model 2 or 7 Printer</u>: The Model 2 provides a print line with 132 print positions; the Model 7 has 120 print positions. The <u>maximum</u> printing speed for the Model 2 is 750 lines per minute. The maximum printing rate for the Model 7 is 600 lines per minute. Refer to the <u>Printing Speeds</u> section for determination of various printing rates. The integrated attachment for this device is a special feature.

- 3. <u>IBM 2311 Model 1 Disk Storage Drive</u>: Up to four 2311s can be attached to the system through a single integrated attachment special feature.

- 4. <u>IBM 2540 Model 1 Card Read-Punch</u>: The card-reader portion of this device reads cards at a maximum rate of 1000 card per minute; the card punch operates at a maximum rate of 300 cards per minute. The integrated attachment for this device is a special feature.

The Console Printer-Keyboard, the 1403, the 2540 Reader, and the 2540 Punch are assigned to channel 0 and operate in multiplex mode. The 2311s are assigned to channel 1 and operate in burst mode as if on a selector channel.

Note: The console printer-keyboard and the integrated 1403 and 2540 attachment features are not attached via the multiplexer channel but appear to the program to be on this channel. The integrated 2311 attachment feature <u>does not</u> require a selector channel feature, although it appears to the program to be on the selector channel. Thus, the presence or absence of selector or multiplexer channel features is completely independent of the integrated I/O attachment features.

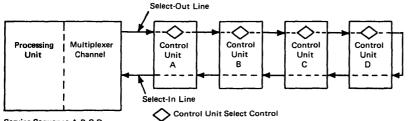

#### INPUT/OUTPUT CHANNEL

In addition to the integrated I/O devices, the Model 25 can also have a standard I/O interface channel for connecting additional I/O devices. The channel special feature may be installed as channel 0 and function as a multiplexer channel, or as channel 1 and function as a selector channel. The two types of channel cannot be installed simultaneously. With either type of channel installed, the integrated Console Printer-Keyboard, 1403, and 2540 are addressed as if they were on channel 0, and the integrated 2311s are addressed as if they were on channel 1. Up to eight control-unit positions are provided for connecting I/O devices on the installed channel. Either of the following maximum configurations is possible.

- Channel 0 with eight control-unit positions, plus all of the integrated devices assigned to that channel, and the maximum of four 2311s attached to channel 1 through the integrated attachment.

- Channel 1 with eight control-unit positions, plus a maximum of four 2311s connected to channel 1 through the integrated attachment, and all of the other integrated devices assigned to channel 0.

With the multiplexer channel, 32 unit control word positions (UCWs) are provided to address up to 152 devices: eight UCWs can address up to 16 devices each; 24 UCWs can address one I/O device each.

When the selector channel feature is installed, up to 256 I/O device addresses can be used.

## Channel Interface

When the multiplexer or selector channel special feature is present, a standard I/O interface is provided for attaching a wide variety of I/O devices to System/360. The <u>interface</u> is a standard set of electrical connections through which signals are sent that allow for exchange of data and control information between the CPU and attached I/O devices. The interface is called <u>standard</u> because any present or future device can be attached to the system as long as it complies with the specifications of the interface.

Control of I/O functions, determined by instructions in the CPU program, and the transfer of data between CPU and I/O devices, are handled through channels. These channels coordinate the operation of I/O devices through program control.

The selector channel is usually used for high-speed data rate I/O devices because although operations are initiated by the CPU (which also reads data into or out of core storage), selector-channel data-transfer operations <u>overlap</u> CPU operations. CPU facilities are <u>used</u> for multiplexer Channel data-transfer operations.

The maximum data rate for either channel feature is 30,000 bytes per second (30KB).

## Selector Channel

A selector channel is used to sustain operation of one device at a time. A variety of devices can be attached to a selector channel, but it is most useful when used with high-speed I/O devices.

## Multiplexer Channel

The data-handling capability of the multiplexer channel is <u>normally</u> lower than that of the selector channel, although the multiplexer channel can handle nearly the same data rates of I/O devices attached to the selector channel when operating in <u>burst mode</u>. In this mode, the channel is temporarily assigned to a single device. The advantage of the multiplexer channel is that it can service the data flow and control requirements of several slow-speed I/O devices at one time. This kind of operation is accomplished in <u>multiplex mode</u> (sometimes called data interleaved mode). For example, the data sent from two serial card readers to the CPU can be handled at one time in multiplex mode by the multiplexer channel.

#### IBM 2025 PROCESSING UNIT

The IBM 2025 Processing Unit (CPU) contains core storage and facilities necessary to perform arithmetic and logical processing of data and to control communications and data transfers between the CPU and external devices.

Major internal components of the 2025 processing unit are:

Core Storage Local Storage Arithmetic-Logic Unit Addressing Registers Data Registers Error-Detection Circuits

#### Core Storage

Core Storage consists of three distinct areas: program storage, control storage, and auxiliary storage. Provisions are made to store or read out one or two bytes during a single storage access cycle. Although the core storage read/write cycle time is 900 nanoseconds, two cycles are required to read or store a byte or halfword (2 bytes) in either program or auxiliary storage. The first of these two cycles is necessary to obtain information needed to control the data access. Thus, the total time required per access is 1800 nanoseconds or 1.8 microseconds. This is not true, however, for sequential processing of microprogram steps in control The address for the next control storage. word to be executed is retained or appropriately updated as a function of the access. Therefore, the time necessary to read out a control word (2 bytes) is always 900 nanoseconds.

<u>Program Storage</u>: This area of core storage is accessible by the user's programs. It contains from 16,384 to 49,152 byte locations, depending upon the model. This storage is used to contain the instructions and data areas required for problem programs. These positions are addressed from location 0 up through the highest installed program storage address.

Certain locations of program storage are permanently assigned as follows to ensure program compatibility within System/360 as

## described in <u>System/360 Principles of</u> Operation, Form A22-6821.

| Decimal<br><u>Address</u> | Length     | Purpose                                                   |

|---------------------------|------------|-----------------------------------------------------------|

| 0                         | Doubleword | Initial program-loading<br>PSW                            |

| 8                         | Doubleword | Initial program-loading<br>CCW1                           |

| 16                        | Doubleword | Initial program-loading<br>CCW2                           |

| 24                        | Doubleword | External old PSW                                          |

| 32                        |            | Supervisor-call old PSW                                   |

| 40                        |            | Program old PSW                                           |

| 48                        | Doubleword | Machine-check old PSW                                     |

| 56                        | Doubleword | Input/output old PSW                                      |

| 64                        | Doubleword | Channel-status word                                       |

| 72                        | Word       | Channel-address word                                      |

| 76                        | Word       | Not used                                                  |

| 80                        | Word       | Timer                                                     |

| 84                        | Word       | Not used                                                  |

| 88                        |            | External new PSW                                          |

| 96                        |            | Supervisor-call new PSW                                   |

| 104                       |            | Program new PSW                                           |

| 112                       |            | Machine-check new PSW                                     |

| 120                       | Doubleword |                                                           |

| 128-159                   |            | Diagnostic scan-out<br>area, beginning at<br>address 128. |

The remaining byte locations of program storage can be used for programming functions as outlined in the <u>IBM System/360</u> <u>Principles of Operation</u>.

<u>Control Storage</u>: This core storage area is used exclusively to contain the microprogram routines necessary to interpret problem-program instructions, and to control all system functions for the mode of operation being executed. This area is reserved for control-program purposes and is not available to the problem programmer. Refer to the <u>System</u> <u>Control</u> section.

Auxiliary Storage: This core storage section is used for the general registers and floating-point registers, temporary work areas for various CPU functions, storage for unit control words (UCWs) for channel and I/O attachment features, etc. This area ranges from 2,048 to 4,096 bytes, depending upon the program-storage capacity of the system. Of these auxiliary-storage areas, only the general and floating-point registers are addressable by the problem program. As in other System/360 models, the 16 general registers have a capacity of one word (four bytes) each. The four floating-point registers are doubleword registers.

## Local Storage

The Model 25 utilizes a high-speed (180-nanosecond) unit for local storage. This system component is used for intermediate storage of the data being operated upon by the current control program step. It also holds addresses and other information required for internal processing and input/output operations. Generally, information is transferred from core storage, placed in local storage, used in some arithmetic, logic, or addressing function by the ALU or other data-flow component, and then returned to local storage. Depending upon the operation, the information may be retained in local storage, transferred back to core storage, or directed to an input/output device or some other point in the system data flow.

During the execution of microprogram (control-program) steps, local storage can accept or read out a byte of information as many as four times within the primary system cycle of 900 nanoseconds. A serial-by-byte capability permits the local storage to accept halfwords from core storage, and buffer the core-storage address into the ALU as specified by the microprogram step.

## Arithmetic-Logic Unit (ALU)

The arithmetic-logic unit in the Model 25 is used to produce both arithmetic and logical combinations from input data from a variety of sources within the system. The data path through the ALU is one byte wide. The ALU inputs, the destination of the result, and the control of the ALU are determined by the control-program step being executed.

Associated with the ALU is an arithmetic modifier that effectively doubles the data width through the ALU circuitry for some operations.

#### Addressing Registers

Core storage (program, control, and auxiliary areas) are all accessed by a common set of storage-address registers. The address used depends upon the function being performed. In some instances, it is derived from the contents of the preceding control word and the contents of an address-backup register. For other functions, the core-storage address is obtained from a local storage area. For sequential control-word processing, the core-storage address is developed from the address of the previous control-program step.

Because only the program storage section of core storage may be accessed directly by the programmer, and because the control-program area (and certain auxiliary-storage locations) must not be violated, provision is made to prevent inadvertent accesses to these areas.

## Data Registers and External Facilities

Several special registers and other facilities that are external to local storage are used as sources and destinations for data and control information. These registers contain CPU status information, the settings of switches A, B, C, and D on the system control panel, status and data being transferred between the CPU and the channel or attachment devices, status and data associated with various special features, and similar data. These registers are not addressable by the problem programmer.

## Error-Detection Circuitry

Tests are made for core-storage address validity, data parity (both within the CPU and during I/O data transfers), and other system malfunctions during system operation. Error-recovery microprogram routines included in the control program attempt to correct the error condition when this is possible. If the error-recovery attempt is unsuccessful, the system operation in progress is terminated. In many instances, the problem program or supervisor program also includes error-test routines, but these routines are application dependent and are not considered part of the computing system.

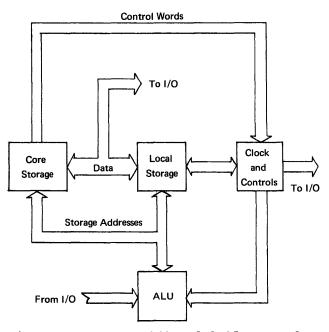

## SYSTEM/360 MODEL 25 DATA FLOW

Figure 2 is a simplified schematic of the Model 25 data flow. The manner in which the various elements of the data flow are used for a given application depends upon the control-program step being executed.

Figure 2. System/360 Model 25 Data Flow

## SYSTEM CONTROL

As in other System/360 models, this system performs internal data manipulations and input/output operations by executing <u>microprogram</u> routines. In the Model 25, 16,384 bytes of core storage are reserved as microprogram (or control) storage. This section of core storage is standard on all models and is in addition to the program-storage area for a particular model. This area cannot be used for application-program purposes.

Control programs for the Model 25 can be easily reloaded into control storage (see the <u>System Initialization</u> section). These microprograms are prepared by IBM so that engineering changes can be implemented quickly and with minimum inconvenience to users of the Model 25. This also ensures problem-program compatibility between System/360 models within storage and input/output capabilities.

The control program for a mode of operation, System/360 mode for example, is especially written to:

- 1. Interpret problem-program instructions

- 2. Perform arithmetic and data-handling functions within the CPU

- Initiate I/O operations and control any code translations required for the device

- 4. Handle data errors and other exceptional conditions

5. Perform other data manipulations required for efficient completion of the job.

## Priority of System Operations

The Model 25 is designed to take advantage of the possibility of overlap between CPU operations and input/output functions. Also, the priority of operations within the CPU are ordered so that functions having the highest urgency are given the highest priority. This method of handling data and control requirements allows for maximum system throughput while reducing the likelyhood of data overruns. (A <u>data</u> <u>overrun</u> is a condition where information is presented to the CPU from, for example, a magnetic tape unit, but because of other higher-priority system requirements, the information is lost.)

The highest priority (level 4) is given to the functions of System Reset, Initial Program Load (IPL), and Control Storage Load (CSL). These operations are allowed to immediately interrupt any other system function.

Priority level 3 is used for high-speed data transfers between the CPU and I/O devices attached to the channel, such as magnetic tape. This level is allowed to interrupt any operation having a lower priority.

Priority level 2 is reserved for data chaining operations for the integrated 2311 disk attachment feature.

Priority level 1 handles such medium-priority system functions as channel-status transfers and data chaining, and input/output transfers for the integrated 2540 attachment feature.

The lowest priority, level 0, is used to handle system operations that are either buffered or are not subject to data overruns. Among these are 1403 and 2540 status and chaining, and CPU instruction processing.

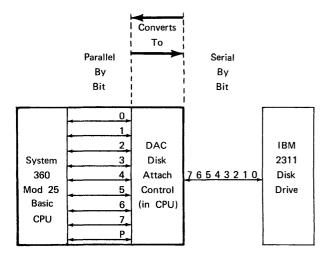

Because of the high data rate of the 2311 devices, a special share-cycle priority is assigned to handle data transfers between core storage and the integrated 2311 disk attachment feature. This priority is allowed to interrupt any other level of operation except level 4 (System Reset, IPL, or CSL). Each interruption to handle a byte of disk-file data requires only two cycles out of every seven. This permits operation of a 2311 unit in conjunction with any I/O device attached to the channel (except magnetic tape or other high-speed unbuffered devices).

When the priority level assigned for a feature or operation is either not active or not included with the system (absence of the integrated 2311 attachment feature, for example), that level is bypassed.

The priority structure in the Model 25 is organized so that coincident or pending requests for status or data-handling service are queued: stacked up in order of their occurrence and/or significance until they can be accepted by the CPU.

## MODEL-DEPENDENT IMPLEMENTATION OF SYSTEM/360 FUNCTIONS

The concept of compatibility between System/360 models is not applied for some detail functions. Neither the frequency of occurrence nor the usefulness of results warrants identical action on all models. These functions are concerned with the handling of invalid programs and machine malfunctions. They are identified in the System/360 Principles of Operation under Functions that may Differ Among Models. Wherever model dependency exists, the System/360 definition allows choice of implementation, or specifies that the outcome of the operation is unpredictable. The intent is that the user should ignore results that are defined to be unpredictable, and should not base his programs on any function where choice of implementation is permitted.

Considering any particular installation and operation, the results are not truly unpredictable: the action and result may depend upon system components or the input data.

However, writing a program based on the information contained in this section is in violation of the rules of compatibility of System/360. If the program depends on a function that is model-dependent, it may not produce the same results on another model of System/360. Even if a program allows for the model-dependent implementation of all other models, difficulties may be encountered if and when new System/360 models are introduced. Furthermore, a mandatory engineering change may in some instances require changes in a program that makes use of such model-dependent information.

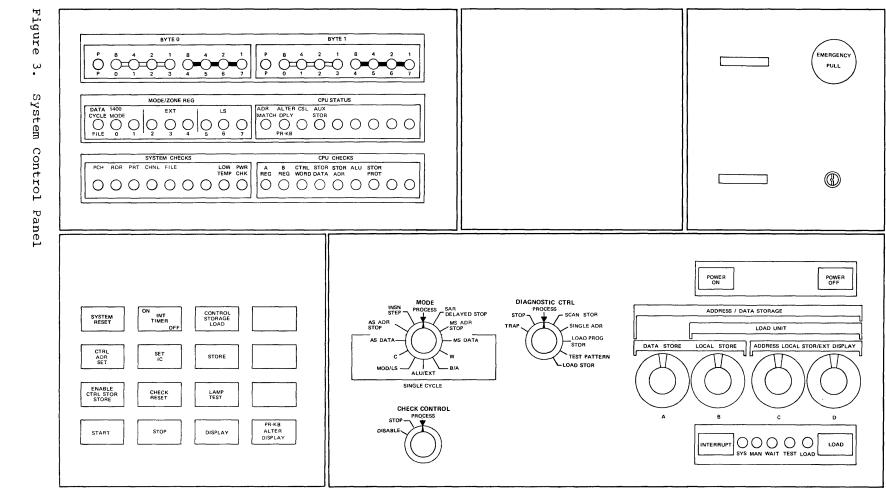

#### SYSTEM CONTROL PANEL

The system control panel contains the switches, indicators, and other manual controls necessary for operation and control of the system. Other device-dependent controls are located on certain input/output units. The system control panel is made up of four sections (Figure 3).

- 1. Displays

- 2. Operator Control Section

- 3. Operator Intervention Section

- 4. Customer Engineering controls

The system is manually controlled with pushbutton switches and rotary switches. Two of the rotary switches control the mode of operation and check-control. Four hex-coded switches are used for addressing and for entering manual data. One rotary switch is used for diagnostic control.

#### INDICATORS OR DISPLAYS

Several indicators are available for displaying data and status information. The remaining lights are used as multipurpose indicators to display the Storage Address Register and other manually selected registers and locations.

## Byte-0 and Byte-1 Indicators

The byte-0 and byte-1 indicators are used to display a variety of data and address information, depending on the operation in progress. Refer to the descriptions of the keys and switches on the system control panel.

#### Mode/Zone Register\_Indicators

Data Cycle, File: This light is on during a file-share cycle. This means a byte of information is being transferred between main storage and a 2311 device through the integrated 2311 disk attachment feature.

<u>Bit 0:</u> Indicates operation in 1400 emulator mode.

Bit 1: Not used.

<u>Bits 2, 3, and 4:</u> Show the current mode of operation for addressing incoming and outgoing external lines and registers.

<u>Bits 5, 6, and 7:</u> Indicate the bit structure that is decoded as the zone location for local-storage addressing.

#### CPU STATUS INDICATORS

Address Match: This light turns on when the address set up in switches A, B, C, and D matches the address being used to access core storage, and the Mode switch is in the SAR delayed stop position.

Alter/Display Printer-Keyboard (PR-KB): Turns on to indicate that the console printer-keyboard is executing an alter/display routine.

<u>CSL:</u> Pressing the CSL switch turns on this light and starts the control storage load (CSL) routine. The indicator resets when the control-program load routine is completed.

## System Checks

<u>PWR CHK (Power Check):</u> Should any dc supply fall below its sensed output level (and/or circuit-breaker or thermal sensor trip), the machine sequences down to its normal power-off status and the power-check light turns on.

Power restart cannot be activated until the power-check light is reset by pressing the power-off switch and/or resetting the tripped circuit breaker or manually operating the thermal-reset switch.

<u>PCH (Punch):</u> Turns on for any punch condition in the integrated 2540 attachment feature that requires operator attention.

<u>RDR (Reader):</u> Turns on for any reader condition in the integrated 2540 attachment feature that requires operator attention.

<u>CHNL (Channel):</u> A microprogram-detected channel error or a bus-in parity error turns this light on.

12 IBM System/360 Model 25

FILE: This indicates that an error has been detected during operation of a 2311 device through the integrated 2311 disk attachment feature.

LOW TEMP (Low Temperature): When power is turned on initially, this light comes on and remains on until the array is at proper operating temperature (about 2 minutes, depending upon room temperature). The purpose of this light is to indicate to the operator that the system is not yet up to optimum operating temperature.

## CPU Checks

<u>Parity Indicators:</u> These lights, when on, indicate that incorrect parity was detected at the data-flow component named. The parity indicators are:

| A REG     | A-register      |

|-----------|-----------------|

| B REG     | B-register      |

| CTRL WORD | Control word    |

| STOR DATA | Storage data    |

| STOR ADDR | Storage address |

<u>ALU:</u> Turns on when an error is detected in the arithmetic-logic unit (ALU) circuits during an ALU cycle. The ALU check is not a parity check but an actual bit check.

Storage Protect: Turns on to indicate that data read out of the storage-protect buffer had incorrect parity.

#### OPERATOR CONTROL SECTION

This section of the system control panel contains the controls required by the operator when the CPU is operating under control of the supervisor portion of the programming environment being used [Disk Operating System (DOS), Tape Operating System (TOS), etc.]. Under supervisor program control, a minimum of direct manual intervention is required because the supervisor program performs operations such as store and display.

The main functions provided by the operator control panel (OCP) are the control and indication of system status (wait, manual, etc.), operator-to-machine communication (primarily via the console printer-keyboard), and initial program loading.

The switches and indicators in the OCP section of the system control panel are present on all System/360 models. On the Model 25, they have the following functions.

## Switches

<u>Emergency-Pull Switch:</u> Pulling this switch turns off all power beyond the primary power box except EPO (Emergency Power-Off) control voltage on every unit that is part of the system or that can be switched onto the system. Therefore, the switch controls the system proper and all off-line and shared control units and I/O devices. The contents of core storage can be affected when this switch is operated.

The switch latches in the <u>out</u> position and can be restored to its <u>in</u> position by maintenance personnel only.

When the emergency-pull switch is in the out position, the power-on key is ineffective.

<u>Power-On Key:</u> This key is pressed to initiate the power-on sequence of the system.

As part of the power-on sequence, the system is reset in such a manner that the system performs no instructions or I/O operations until explicitly directed. The contents of core storage are preserved.

The power-on key is backlighted to indicate when the power-on sequence is completed. The key is effective only when the emergency pull switch is in.

If the power-on light glows pink, the power-on sequence for the system cannot be completed because of a malfunction in a power supply or an I/O device.

<u>Power-Off Key:</u> The power-off key is pressed to initiate the power-off sequence of the system.

The contents of core storage are preserved. The key is effective only while power is on the system, and it overrides the power-on key.

<u>Interrupt Key:</u> The interruption key is pressed to request an external interruption.

The interruption is taken when not masked off and when the CPU is not in the stopped state. Otherwise, the interruption request remains pending. Bit 25 in the interruption-code portion of the current PSW is made 1 to indicate that the interrupt key is the source of the external interruption. The key is effective only while power is on the system.

<u>Load Key:</u> The load key is pressed to start initial program loading. The key is

System Control Panel 13

effective only while power is on the system.

When the load key is operated, the following functions occur.

- 1. An automatic system reset is performed.

- 2. The CPU clock is started.

- 3. The basic test microprogram is

- performed. 4. The clear UCW microprogram is run to reset all the flag bytes in the UCW

- area of auxiliary storage. 5. The load microprogram is begun. This routine analyzes switches B, C, and D to determine the address of the program-loading I/O device (load-unit address). When this routine is completed, the Initial Program Load (IPL) PSW has been successfully set up, and the load light is turned off.

Note that the system mask is reset when the load key is pressed. The system mask in the IPL PSW is then effective as soon as the IPL PSW is set up.

The load key does not change the system operating mode already determined by the CSL function and the contents of control storage.

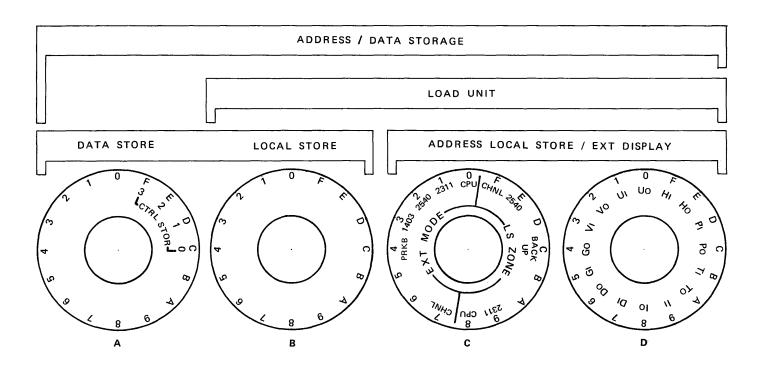

Load Unit Switches: Three rotary switches (B, C, and D) provide the I/O address bits used for initial program loading (see Figure 4).

All three are 16-position rotary switches labeled with the hexadecimal characters 0-F. The channel address (0 or 1) is loaded from switch B, and the unit addresses from switches C and D.

These switches have other functions, as described under <u>Operator Intervention</u> <u>Section</u>.

## <u>Indicators</u>

<u>System:</u> This indicator is on whenever the customer or CE use-meter is recording time.

Manual: Whenever the CPU clock is stopped or the CPU is in a soft-stop loop, this indicator is on. The soft-stop loop is a microprogram routine used to handle all exceptional conditions and interruptions in the CPU. The first time through the loop, all pending interruptions are handled. After this, only the integrated I/O devices, the interval timer, instruction step, and certain console functions are handled. Pressing the stop key is one way to enter the soft-stop loop. <u>Wait:</u> This light is on when the CPU is in the wait state (i.e., CPU clock is running but instruction execution is not taking place). If an interruption occurs, the CPU is taken out of the wait state and processing occurs, depending on the program being executed.

<u>Test:</u> This light is on when either the mode switch, the diagnostic-control switch, or the check-control switch is <u>not</u> in the process position.

Load: Whenever an initial program load (IPL) microprogram is in progress, this indicator is on. It turns on after the load key has been pressed and released, and turns off when the initial PSW is successfully loaded.

#### OPERATOR INTERVENTION SECTION

This section of the system control panel contains the controls required for the operator to intervene in normal programmed operation.

Many of these keys are described as being intended for customer engineering use only. Indiscriminate operation of these controls will seriously affect or terminate the problem-program application in progress.

## Pushbutton Keys

System Reset Key: This key resets the CPU clock and the various registers and controls in the CPU and I/O units necessary to prepare the system for another job. In addition, a system-reset microprogram is initiated when the CPU clock is started upon release of the switch.

It is not necessary to press this key when the load key is operated because the load key also initiates a system reset.

Control Address Set Key: This key is effective only when the CPU clock is stopped. When the switch is pressed, the contents of the four address switches (A, B, C, and D) are used as the address for the next storage-access cycle. For 16K systems, this address is from 4000-7FFF (switch-A positions 4-7); for 24K or 32K systems, this address is 8000-BFFF (switch-A set to 8-B); and for 48K systems, it is C000-FFFF (switch-A positions C-F). This key is for customer engineer use only. Enable Control Storage Store Key: This key must be pressed and held during a store into the control-storage area of core storage (refer to <u>Store Operation</u>). The store operation is successfully completed when the new data is displayed in the byte-0 and byte-1 indicators. This key is for customer engineering use only.

Start Key: Pressing the start key generates a clock-start signal to start the machine. The processor continues to operate in the mode selected by the setting of the mode switch.

CSL key: Pressing this key causes a system reset, and initiates a microprogram used to load the control-storage and auxiliary storage areas of core storage with new information to change system operating modes (from System/360 mode to 1400 emulator mode). The data source for a CSL function is the input device specified by switches A, B, C, and The CSL light (CPU status) is on while D. in the CSL routine, and is reset upon CSL completion. Refer to the System Initialization section for further information.

Set IC Key: This switch is effective when the CPU is in either a soft-stop or a hard-stop state. The Set-IC (instruction counter) key causes a branch to the soft-stop routine that gates the contents of switches A, B, C, and D into the instruction counters. This address must be valid for the installed program storage area. At the end of the Set-IC routine, the system enters a soft-stop state.

<u>Check Reset Key:</u> Pressing this button resets the check latches in the processing unit to the no-error state.

Stop Key: Pressing the stop key with the system in process mode causes a branch into the soft-stop routine at the end of the current instruction, and turns on the manual light.

When this key is pressed, the system enters the stopped state when:

- 1. The instruction being processed has been completed,

- 2. All pending interruptions have been serviced, and

3. Any I/O operation in progress has been finished.

Note: Any time the system enters the soft-stopped state (such as when the stop key is pressed), the hexadecimal address for the next System/360 instruction (problem program instruction) is printed on the console printer-keyboard. This notation is also printed when the system-reset key is pressed. This provides a permanent record of each occurrence of a stop.

If data or command chaining is involved, it is completed before the CPU clock is stopped. The system light stays on as long as any I/O unit is engaged in an I/O operation; that is, until device-end is accepted for the last command in a chain for that I/O device.

Note that the machine environment is not destroyed when the stop key is pressed, and the program that was in progress can be restarted (by pressing the start key). The address of the next instruction is displayed in the byte-0 and byte-1 indicators.

When the system is stopped by pressing the stop key, the multiplexer channel is allowed to accept share-request traps (microprogram branches), and the selector channel is allowed to accept data cycles. This provision permits input-terminal and multisystem operations even though the 2025 program in progress has been manually interrupted.

<u>Interval Timer Switch</u>: This switch is present only if the interval-timer feature is installed. The switch activates the interval timer.

Display Key: This key is operative only when the CPU is in the stopped state. When the mode switch is in the MS-data or AS-data position, the display pushbutton causes the address in switches A, B, C, and D to access storage, read out the two data bytes, and display them in the byte-0 and byte-1 display indicators. The halfword accessed is then available on the core-storage bus-out lines (R0 and R1). R0 displays in byte-0 and R1 in byte-1. Refer to the Mode Switch and Console Procedures sections for a detailed description of display operations.

## Note:

The Full View of Switch A Shows Control Storage Positions For 48K Systems, The Partial Views of Switch A Are Used For 16K, 24K, and 32K Systems.

Switch A For 16K Systems

Switch A for 24K and 32K Systems

Figure 4. Control Panel Switches A, B, C, and D

Lamp Test Key: When this key is pressed, all console indicators (except PWR CHK and LOW TEMP) should light. The lamp-test key can be pressed at any time with no effect on system operation.

Store Key: Any core storage or local storage location can be altered from the console. The store switch is effective when the mode-control switch is in any of three positions:

MS Data

AS Data

Mod/LS

The detailed store operation is described in the <u>Mode Switch</u> and <u>Console Procedures</u> sections.

<u>PR-KB Alter/Display Key:</u> Pressing this key causes a console printer-keyboard request. When the request is honored, the console printer-keyboard unlocks, the PR-KB alter/display indicator and the proceed light turn on. The console printer-keyboard is then used for alter/display. (See <u>Manual Alter/Display</u>.)

## Address/Data Switches

These four switches (A, B, C, and D) are used to address a location in any storage area and can be manipulated without disrupting CPU operation (Figure 4). For specific functions, they specify the data to be stored in the location designated by the mode switch. Refer to <u>Mode Switch</u> and <u>Console Procedures</u> for more information.

#### CUSTOMER ENGINEERING CONTROLS

The Mode switch, Check Control Switch, and the Diagnostic Control switch are intended primarily for customer engineering use. When processing problem programs, these switches should all be set to the Process position.

MODE SWITCH

The mode of system operation is controlled by the setting of this switch. The positions of the switch put the machine into either an operating mode or a single-cycle mode.

## Operating Mode Positions

<u>MS Address Stop:</u> The machine is in a normal operating mode. When the address in switches A, B, C, D matches the address of the core-storage location being accessed, the machine stops at the completion of the microword in progress. The address-match indicator is turned on. The byte-0 and byte-1 indicators display the address of the <u>next microprogram step</u> to be executed. The match occurs for addresses that specify either program or control storage.

<u>Process</u>: This is the normal operating position for the system. If the clock stops with the switch in this position, byte-0 and byte-1 display the contents of the storage-address register.

<u>Instruction Step:</u> In this position, the machine performs one instruction for each operation of the start button. At the conclusion of the instruction, the machine goes to a soft-stop routine. In single-instruction operation, the console printer-keyboard prints out the next instruction address after each instruction is executed. If the clock stops (for some other reason) with the switch in this position, the storage address register is displayed in byte 0 and byte 1. Except for a machine check, I/O overruns do not occur when the switch is in this position.

<u>AS-Address Stop:</u> The machine is in normal operating mode. When the address in switches A, C, and D matches the auxiliary-storage address present in bits 0-3 and 8-15 of the storage-address register (MO-register bits 0-3 and M1-register bits 0-7), the machine stops at the completion of the microword in progress. The address-match indicator is turned on. The byte-0 and byte-1 indicators display the address of the next microprogram step to be executed. The auxiliary-storage area of core storage is addressed by the four high-order bits and the eight low-order bits of the storage-address register; the second of the four normal hexadecimal digits is not relevant.

SAR Delayed Stop: At this switch setting, the machine operates normally in run mode until the address in switches A, B, C, D compares to the address in the storage-address register. The machine completes the macro instruction in progress. It then goes to a soft-stop routine, similar to single-cycle and/or instruction-step operation. The address-match indicator turns on. If the clock stops with the switch in this position, the storage-address register is displayed in the byte-0 and byte-1 indicators

The mode switch can be switched between these first five positions during system operation, with no effect on normal machine operation except as described for the switch settings.

Single-Cycle Mode Positions

When the mode switch is in any of the remaining positions, pressing the start key causes the CPU to operate for only one cycle (overruns occur for operations involving nonbuffered devices). During this cycle, the CPU performs the function specified by the control word being executed. At the end of the cycle, the display in byte-0 and byte-1 is the storage-address register, except for the alter/display storage and auxiliary-storage positions.

<u>Alter/Display Functions, Mode Switch:</u> The <u>store</u> pushbutton is effective only when the mode switch is in one of the following positions (see <u>Store Operation</u>). MS Data AS Data MOD/LS

The <u>display</u> pushbutton is effective only when the mode switch is in one of the following single-cycle positions (see <u>Display Operation</u>).

B/A C ALU/EXT MOD/LS AS Data MS Data.

W

All of the preceding single-cycle positions except AS-data and MS-data display the storage-address register in the byte-0 and byte-1 indicators unless the display key is pressed. When the display key is held pressed, the byte-0 and byte-1 indicators display the contents of the data-flow component addressed by the Mode switch, as follows.

Mode Switch Operations Position Information Displayed Possible

W Storage-address back- Single cycle up registers (W0 and or display W1 registers)

- C Contents of the Single cycle control-word register or display (C0 and C1 registers)

- B/A B-register and A- Single cycle register (components or display that feed the ALU)

- MOD/LS ALU modifier and the Single byte of local storage cycle, selected by switches store, or C, D display

- ALU/EXT Output of the arith- Single cycle metic/logic unit, and or display the external location selected by switches C, D.

Note: These functions are more fully detailed in the Console Procedures section.

CHECK-CONTROL SWITCH

This 3-position rotary switch provides a stop-on-error function for the CPU. It is used for customer engineering purposes. The switch positions and the action taken are as follows.

Switch Position Action

Process This is the normal operating position.

- Disable In this position, all machine checks are ignored, but the appropriate check latch is set.

- Stop A machine check detected while the switch is in this position causes a hard stop (clock stop) at the completion of the control word in progress.

## DIAGNOSTIC CONTROL SWITCH

<u>Process</u>: This is the normal position when the machine is operating, or when no scan-diagnostic functions are being performed. When the switch is taken out of the Process position, the system is put into a test status.

18 IBM System/360 Model 25

#### Scan and Load Positions

The circuitry scan and load operations are started by pressing System Reset, then Start. This starts the scan or load operation at address 0000. The scan continues until the system-reset key is pressed, or the diagnostic control switch is moved to the single-cycle position. If the scan or load operation is to be started at an address other than 0000, switches A, B, C, and D are set to the desired address. Pressing control-address set key places the address into the storage-address register. Pressing the start key initiates a clock-start, and the operation continues until terminated as indicated.

<u>Scan Storage:</u> Every position of storage is read and regenerated in sequence. A parity error on storage data or a storage address causes a hard stop. The check-control switch must be in the stop position.

Load Program Storage: The data in switches A, B, C, and D is loaded into every position of program storage. When the control storage area is addressed, the locations are accessed in sequence, but the store lines are not activated. A storage scan should follow the load program to determine if the data is stored properly.

Single Address: When the switch is in this position, the storage address specified by switches A, B, C, and D (set into the storage-address register by the control-address set key) is used each cycle to address a single storage location. As with the other scan or load positions of this switch, the start key must be pressed to initiate the function.

Test Pattern: A test pattern of 1's and 0's is loaded into every position of program, auxiliary, and control storage (except the CSL area). The program continues to loop until the system-reset key is pressed. Load Storage: Operation with the switch in this position is similar to Load Program Storage except that program, control, and auxiliary storage are loaded from the contents of switches A, B, C, and D. The CSL area is not affected.

<u>Stop:</u> This position is used by the Customer Engineer for diagnostic purposes.

<u>Trap:</u> This position is used by the Customer Engineer for diagnostic purposes.

## USE METER (CPU)

The 2025 system control panel has two separate meters that record time whenever the system is in operation (i.e., initiating, executing, or completing instructions or commands, including those to I/O or assignable units). The position of a key switch determines whether the customer meter or the customer engineering (CE) meter operates. The Customer Engineer sets this switch to cause the CE meter to record time spent during system maintenance.

The system light is on when the system is in operation. It indicates that one of the CPU meters is running. When the stop key is pressed, this light stays on (and the CPU meter continues recording elapsed time) until any previously initiated operation involving an I/O or assignable unit has been completed; that is, until device-end occurs for the last command in a chain for that device. Thus, the CPU customer meter stops (as do other use meters that depend upon it) when there are no further operations in progress, or after the system has been stopped.

The CPU use meter operates for a minimum of approximately one second each time it is started.

## Display Operations

Any core-storage location can be displayed from the system control panel. Several address and data registers can also be displayed. The position of the Mode switch specifies the source of the information to be displayed, as follows.

- MS Data Core storage (program storage or control storage, depending upon the address being used)

- AS Data Auxiliary storage

- C C-register (control register)

- MOD/LS Arithmetic modifier and local storage

- ALU/EXT Arithmetic-logic unit and external facilities

- B/A B-register and A-register (the inputs to ALU and core storage)

- W W-register (storage-address register backup register)

Only those data-flow components the user may need to display are discussed in this section. Other functions of the Mode switch (C, B/A, and W) are used by the Customer Engineer.

Display Program Storage: Set the Mode switch to the MS-Data position. Set switches A, B, C, and D to the program-storage address to be displayed: for 16K systems, this address is from hexadecimal 0000 through 3FFF; for 24K systems, this is 0000-5FFF; for 32K systems, use 0000 through 7FFF; and for 48K systems, use 0000-BFFF. When the display key is pressed, the addressed halfword is displayed in the byte-0 and byte-1 indicators.

Display Control Storage: This procedure is identical to the display of program storage except that switches A, B, C, and D are used to address a control-storage location. For 16K systems, this is hexadecimal 4000-7FFF; for 24K or 32K systems, use 8000-BFFF; and for 48K systems, use C000 through FFFF.

The procedure for displaying control storage is intended for customer engineering use only.

Display Auxiliary Storage: Set the Mode switch to the AS-Data position. Set switches A, C, and D to the auxiliary storage address to be displayed (switch B is not used). This address is from 0x00 through 7xFF for 16K systems; 0x00-BxFF for 24K or 32K systems; and 0x00-FxFF for 48K systems.

Normally, only the general and floating-point registers, and the MPX UCW areas of auxiliary storage, can be displayed by the user. These areas are shown in <u>Appendix A</u>.

## Local Storage Alter/Display

To perform either of these operations, the mode-control switch must be set to the modifier/alter-display local-store position (MOD/LS).

Any position in local storage can be displayed and/or altered from the system control panel. The location to be accessed is selected by switches C and D. Switches A and B supply the byte of data for an alter-local-store operation. The multiple labeling on the knob of switch C is to enable selection of core-storage addresses, local-storage zones, or the external-mode address for the various manual operations. Multiple labeling on the switch-D knob is for selection of bytes U0, U1, V0, V1, etc. in local storage.

Switch C, bits 1, 2, and 3, supplies three bits for zone selection that are the equivalent of mode-register bits 5, 6, and 7. These are gated into the mode-register bit circuits.

Switch D, bits 0, 1, 2, and 3, supplies the bits that are decoded to select the actual byte.

Display Local Storage: After switches C (zone) and D (byte) have been set to select the desired local-storage location, and the Mode switch is set to the MOD/LS position, press the display key. The byte-0 lights indicate the contents of the arithmetic modifier, and the byte-1 indicators show the contents of the addressed LS location

<u>Store Local Storage:</u> Set the mode switch to the MOD/LS position. Set switches C (zone) and D (byte) for the desired local-storage location. Set switches A and B to the new data to be entered. The newly entered information is displayed in the byte-1 indicators. (The arithmetic modifier cannot be altered.)

<u>Note</u>: Except for customer engineering diagnostic purposes, the contents of local storage must not be disturbed.

## ALU/External Display

The data displayed in byte-0 and byte-1 is the M0 and M1 registers whenever the mode switch is turned to this position, or when single-cycling the machine in this mode.

During the operation of the display switch, the ALU output is gated through the LS assembler and is displayed in the byte-0 indicators. The byte-1 indicators display the contents of the external address specified by switches C and D.

Switch C, bits 1, 2, and 3, correspond to the information normally set up in the mode-zone register in positions 2, 3, and 4. Switch D, bits 0-3, are decoded for actual byte addressing within any mode.

The store switch is ineffective in this mode position. Upon release of the display switch, byte-0 and byte-1 indicators again display the M0 and M1 register.

## Store Operations

Information can be manually stored into any core-storage location. A halfword (two bytes) is always affected. If a single byte is to be changed, the remainder of the halfword must be reentered. Information can be stored in the program or auxiliary-storage areas by using the procedure given in the following. If a change is to be made to the control-storage section of core storage (for customer engineering use only), the Enable Control Storage Store key must be held pressed during the store operation. The store operation must be preceded by a display operation of the location to be altered.

It is advisable to display any location (in which data is manually stored) so that the store operation can be verified.

Program-Storage Store Operation: To alter the contents of a halfword in the program-storage area:

Set the Mode switch to MS-Data

Turn switches A, B, C, and D to the

location to be altered.

- 3. Press the display key. The byte-0 and byte-1 indicators show the present contents of this halfword location.

- 4. Set the data halfword into switches A, B, C, and D. If only part of the halfword is to be changed, the unchanged portion must be included as part of the two bytes.

- 5. Press the store key. The byte-0 and byte-1 lights indicate the new information that has been entered into the location specified in Step 2.

- Steps 2 through 5 must be repeated for each halfword to be changed.

Auxiliary-Storage Store Operation: The procedure to alter auxiliary storage is similar to the steps given in the <u>Program-Storage Store Operation</u> section. A halfword in auxiliary storage can be altered as follows.

- 1. Set the Mode switch to AS-Data.

- Set switches A, C, and D (switch B is not used) to the address of the location.

- 3. Press the display key.

- 4. Enter the new data into switches A, B, C, and D.

- 5. Press the store key.

- Steps 2 through 5 must be repeated for each halfword to be changed.

Note: Except for changes to the general and floating-point registers, and customer engineering diagnostic purposes, the auxiliary-storage area must remain undisturbed after it has been initialized using the control storage load (CSL) procedure.

<u>Control Storage Store Operation:</u> Control storage can be altered as shown for program storage, except that the Enable Control Storage Store key must be held while the Store key is pressed.

Note: Except for customer engineering diagnostic purposes, the control storage area must remain undisturbed after it has been initialized using the control storage load (CSL) procedure.

#### SYSTEM INITIALIZATION

There are two classes of initialization for the Model 25. First, control storage load initialization is required when modes of operation are changed (System/360 mode to 1400 emulator mode). This is called Control Storage Load (CSL). The second type of initialization is Initial Program Load (IPL), used to prepare the system for another job in the current system operating mode.

Control Storage Load (CSL)

All Model 25 computing and input/output operations are controlled by microprogram routines stored in the control-storage area of core storage. Whenever system maintenance is performed (depending upon the cause and service steps involved), the system should be reinitialized by using the CSL procedure. Similarly, when operating modes are changed, the CSL procedure must be used.

A small portion of control storage is reserved for a routine to read control-program and auxiliary-storage information from an input device. If this special microprogram is disturbed, a limited amount of manual data must be entered by the Customer Engineer. Then, the normal CSL procedure can be used to complete system initialization.

CSL for System/360 Mode (Using Integrated  $\frac{2540}{100}$ : When the system has been initialized to 1400 mode, the following prodedure is used.

- 1. Press the system reset key.

- 2. Set switches A and B to 0.

- 3. Set switches C and D to the 2540 reader unit address.

- 4. Press the Control Storage Load (CSL) key.

- 5. Place the CSL card deck in the 2540 reader and press the reader start key. The CSL indicator remains on until the CSL routine is completed.

<u>CSL for System/360 Mode (Using a Channel</u> <u>Input Device):</u> If the CSL records are located on a device attached to the multiplexer or selector channel, the following procedure is used.

- 1. Set switch A to 0.

- 2. Set Switch B to 2.

- 3. Set switches C and D to the unit address of the channel input device being used.

- Place the CSL records (cards, tape, etc.) in the input device, and make the device ready.

- 5. Press the CSL key. The CSL indicator remains on until the CSL routine is completed.

CSL for 1400 Emulator Mode: This procedure is given in the <u>System/360 Model 25,</u> 1401/1460 and 1440 Compatibility Features publication, Form A24-3512.

## Initial Program Load (IPL)

This procedure is used after a successful CSL operation. Initial program loading is discussed in detail in the <u>System/360</u> <u>Principles of Operation</u>. The step-by-step method of starting system operation is given here for the Model 25.

- 1. Set switches A, B, C, and D to the hexadecimal representation of the unit address for the input device.

- Place the object-program records (disk, cards, etc.) in the input device, and make the device ready.

- 3. Press the IPL key.

An automatic system reset is generated as a function of the IPL operation. After the object problem program has been entered into core storage, system operation is under control of the application being executed. This section describes the function and operation of the special and optional features that are available for this system. Features are also shown on the <u>IBM</u> <u>System/360 Model 25 Configurator</u>, Form A24-3511. Consult the <u>IBM System/360</u> <u>Principles of Operation</u> for uses and programming considerations of these special features.

Because of the complexity of some major special features, they are described in separate sections.

INSTRUCTION SETS

The <u>standard</u> and <u>commercial</u> instruction sets are provided on all models to perform fixed-point and decimal arithmetic operations. Refer to the <u>IBM System/360</u> <u>Principles of Operation</u> for a description of the various instructions.

## Scientific Instruction Set

This feature provides 44 additional instructions used for floating-point calculations. With this feature, the four floating-point registers in auxiliary storage can be accessed.

#### Universal Instruction Set

When the standard, commercial, and scientific instruction set features are combined with the storage protection feature, the universal instruction set is obtained. The storage protection feature provides two additional instructions.

## DIRECT CONTROL

Control of a variety of special equipment (including another processing unit or non-IBM devices) is possible with this feature. Two instructions: Read Direct and Write Direct, and six distinct interruption lines are included with this feature. Direct control is used to pass controlling and synchronizing information between the CPU and special external devices. Data transfers are normally handled over the multiplexer or selector channel facilities.

If this feature is installed, the external interruption special feature cannot be installed.

#### EXTERNAL INTERRUPTION

This feature provides fast program response for time-dependent operations for which the data-transfer function is already provided. This feature has six distinct interruption lines.

If the direct control feature is installed, this feature cannot be installed.

#### INTERVAL TIMER

This feature provides the ability to decrement a program-controlled count at a fixed rate. Automatic program interruption occurs when the count passes from positive to negative through zero.

A value placed in a fixed core-storage location by the programmer is decremented by one, 300 times per second. when the value goes from positive to negative, a timer interruption occurs. For example, for a hex value of 004650 (18,000 in decimal), an interval timer interruption occurs at the end of one minute of CPU running time (18,000/300 = 60 seconds).

The storage locations used to store the value to be decremented are at hex address 50-53, although the Model 25 (consistent with other System/360 models) uses only the high-order 24 bits of this word (hex locations 50-52). The maximum interval timer cycle is 15.5 hours. Because the ac line frequency is used as the basis for the decrement, timer accuracy resolution is 16.66ms for 60 Hz systems (20ms for 50Hz systems).

This feature can be used for job accounting by measuring the duration of time for each job, for an interruption to prevent a runaway job from gaining control of the system, for time stamping, and for polling particular operations on a regular basis (for example, every minute, every half hour, etc.).

STORAGE PROTECTION

This feature provides the facility to protect against inadvertent alteration to blocks of 2,048 bytes of storage specified by the programmer. With this feature, a programmed protection key prevents writing data into a protected area of core storage, thereby preventing one program from destroying another. Protection against reading data from an input/output device into a protected area is also provided. This applies to channel operations as well as to operations involving the integrated I/O attachment features. Protection keys and patterns are established in the supervisor mode.

Storage protection is not effective for manual display and alter functions initiated from the system control panel.

Fetch protection (against undesired accesses to core storage) is not available on the Model 25.

The two additional instructions provided with this feature are Set Storage Key and Insert Storage Key. These instructions are used to assign and inspect the keys, respectively. The Console Printer-Keyboard, the 1403, the 2540 Reader, and the 2540 Punch attached through their integrated attachments can operate in overlap or time-share fashion with each other and with devices attached through the standard interface on channel 0. At the same time one of the 2311s attached through the integrated attachment on channel 1 can be operating. If the standard I/O interface is assigned to channel 1, one of the 2311s or one of the devices attached to the standard interface can operate with the integrated devices on channel 0. (The limitation with channel 1 is due to its function as a selector channel.)

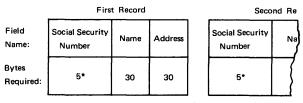

## INTEGRATED DEVICE ADDRESSING

Each I/O device connected to the system must have an address that is unique to the device. The same address must not be assigned to more than one device and the device cannot respond to more than one address. Sixteen bits of the address developed from the I/O instruction define address of the device as four hex digits. The high-order eight bits define the channel (00 and 01 hex define channels 0 and 1, respectively, for the Model 25). The remaining two hex digits define the device address. On channel 0, the integrated devices may be assigned addresses from 00 to FF.

For purposes of System/360 standardization, the integrated devices are assigned addresses at the factory but these may be changed by the Customer Engineer when required. These addresses are defined under the respective device headings.

The addressing for the integrated attachment 2311s on channel 1 is limited to 90 through 93 for the four devices. The 9 defines the control unit in this case and must be the same for all of the devices. If less than four 2311 devices are installed, any of the four low-order digit addresses (0 through 3) may be used. The standard interface, if used on channel 1, can use any address except the 9X series. The Console Printer-Keyboard (PR-KB) is a Model 25 required feature and is physically attached to the processing unit frame as an integral unit. The keyboard allows entry of information into the processing unit for either initiation or alteration. The printer allows the production of a visual record of information from the processing unit. It may serve as an output unit, a record of operation, or as a logout of error conditions. The keyboard and the printer are controlled by the attachment built into the processing unit.

To the programmer the printer-keyboard appears to be attached to channel 0, but it is not physically connected to the standard interface and need not be included in the count of control units attached. For program-controlled operations, the printer-keyboard is controlled with the normal channel instructions. After the operation is initiated, other programmed instructions are handled in the normal manner. Data is transferred as required with multiplex share cycles. For manually initiated operations, normal programmed instructions are suspended until the operation is completed.

When the attachment requires a share cycle for the transfer of data or status, the share cycle is executed upon completing processing for the current instruction and all higher priority requests. If <u>simultaneous</u> requests for <u>data</u> service occur for the printer-keyboard and any other I/O unit on channel 0, the request for the other unit is honored <u>first</u>.

In addition to program-controlled operations, the printer-keyboard can perform alter/display and logout functions. The alter/display function is initiated when the Alter/Display key is operated (CPU console). The primary function of the alter/display operation is to alter and subsequently display the contents of a storage address or group of sequential addresses. The display feature can be used without alteration when it is necessary to examine stored information. In this case, the stored information is not changed. During the alter/display operations, all I/O operations in progress and trapping functions are allowed in the normal manner.

The logout function provides a hard copy printed output of CPU machine errors that may occur. The logout function is initiated through the machine-check trap. Status or sense information is not applicable to the logout and alter/display functions. These functions are not executed until any current printer-keyboard program-controlled operation is completed to the point of device-end status. The status and sense conditions for the operation must remain in the attachment UCW until after the manual operation is completed.

If an alter/display (or logout) operation is started, CPU instruction execution is delayed until after the operation is completed.

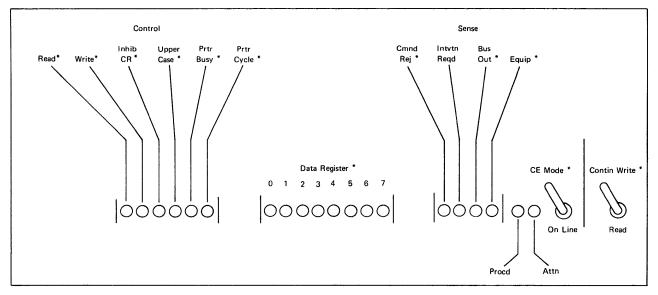

#### KEYS AND INDICATORS

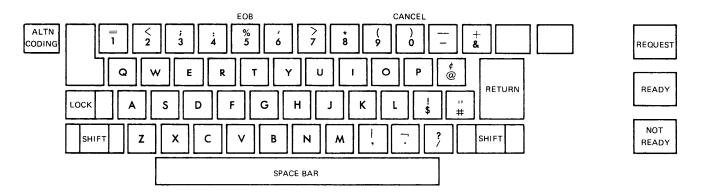

Certain keys and indicators are not used when the PR-KB is attached to the System/360 Model 25. These unused items are all on the upper portion of the console and are indicated by an asterisk (\*) in Figure 5.

INDICATORS (FIGURE 5)

## INTVTN REQD (Intervention Required)

This indicator is on when:

- 1. The forms switch indicates that the printer is out of forms, or

- 2. The printer not-ready switch is operated.

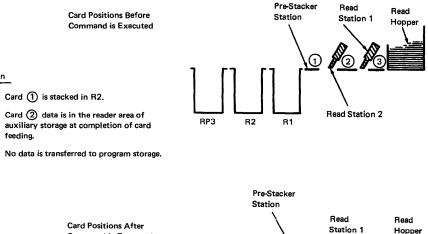

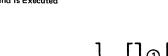

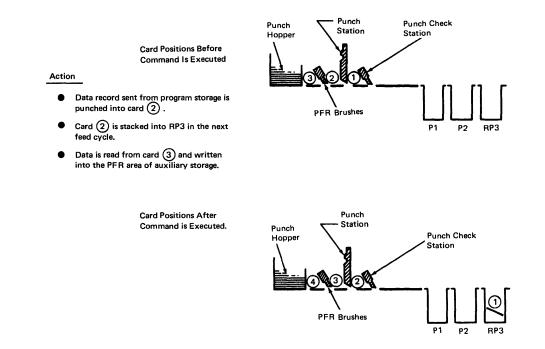

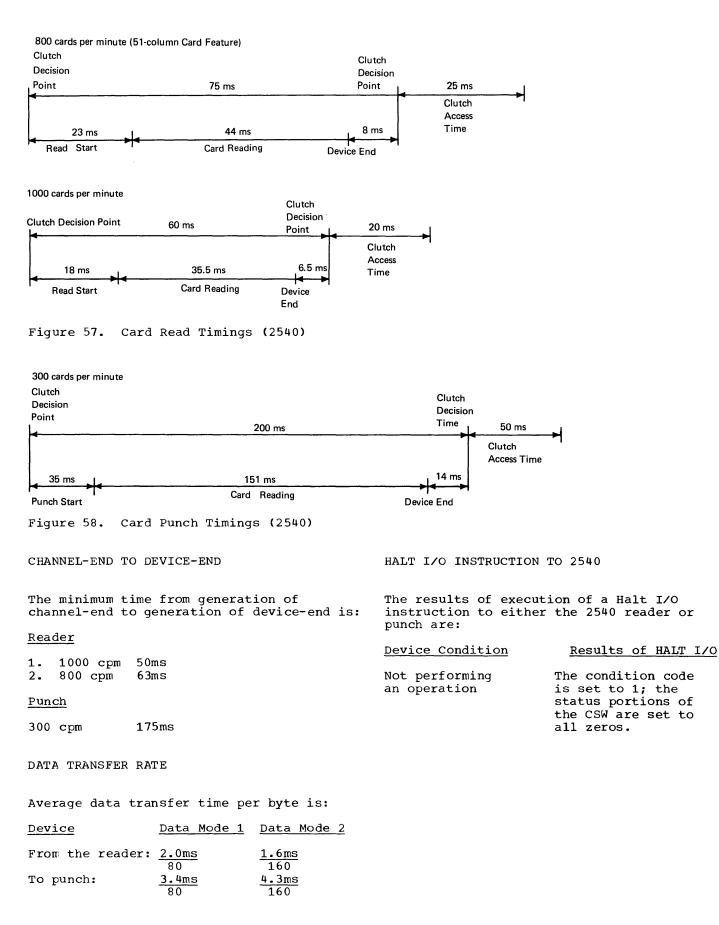

Note that the PR-KB enters the not-ready state when the forms switch indicates that an out-of-forms condition exists.