# Field Engineering Manual of Instruction

System/360 Model 40 Functional Units

#### **Preface**

This manual describes functional units of the IBM 2040 Processing Unit. Storage and functional units that control data flow are explained in detail. An explanation of the control and documentation for microprogramming is also contained in this manual.

A knowledge of computer fundamentals, System/360 philosophy, and the Model 40 data paths are useful in understanding this manual. The following manuals supply this information:

- 1. System/360 Model 40 Comprehensive Introduction, Field Engineering Manual of Instruction, Order Number 223-2840-0

- 2. System/360 Model 40 Theory of Operation, Field Engineering Manual of Instruction, Order Number 223-2844-0.

- 3. System/360 Model 40 Power Supplies, Features, and Appendix, Field Engineering Manual of Instruction, Order Number 223-2845-0

- 4. System/360 Model 40, 2040 Processing Unit, Field Engineering Maintenance Manual, Order Number 223-2841-0

- 5. System/360 Model 40, 2040 Processing Unit, Field Engineering Diagrams Manual, Order Number 223-2842-0

This manual is written to engineering change level 254814 for ALD's and CLD level 255263.

All three-digit figure references in this publication refer to figures in the Diagrams Manual.

The words "memory" and "storage" may be used interchangeably between this publication and the machine ALD's.

Fifth Edition (March, 1970)

This edition, Order Number SY22-2843-1, is a reprint of Form Y22-2843-0 incorporating changes released in the following FE supplement:

FES Number Y22-6784

Date

January 30, 1969

Changes are periodically made to the specifications herein; any such change will be reported in subsequent revisions or FE Supplements.

This manual has been prepared by the IBM Systems Development Division, Product Publications, Dept. B96, PO Box 390, Poughkeepsie, N.Y. 12602

A form is provided at the back of this publication for readers' comments. If the form has been removed, comments may be sent to the above address.

| Clock Purpose and Function of Clock A Gate Clock Generation B Gate Clock Generation T Clock Start-Stop                                                                                                                                     | 7<br>7<br>9                            | Connect Box Carry Box XOR Box Decimal Correction ALU Output Parity ALU Extended Carry                                                                                       | 48<br>48<br>49<br>49             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Registers A Register B Register C Register D Register R Register (R Bus) ALU Registers ALU Control Register                                                                                                                                | 11<br>14<br>14<br>14<br>15<br>18       | Compress ALU Output Checking ALU Input Checks ALU Internal Checks ALU Output Checks ALU Timing Glossary for ALU                                                             | 51<br>51<br>51<br>51<br>51       |

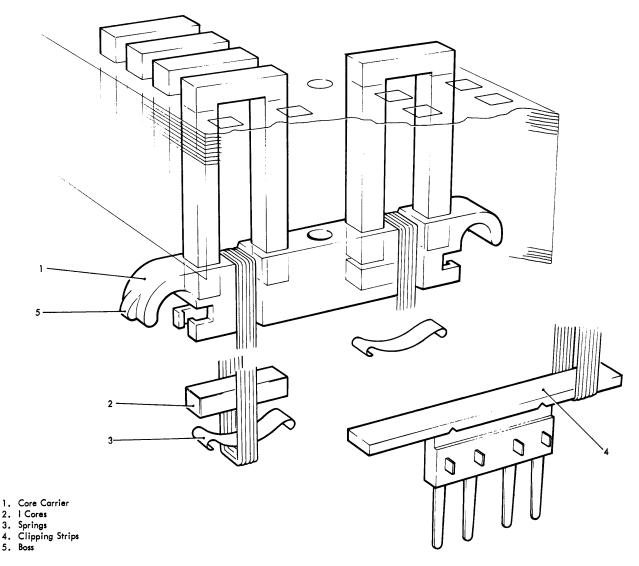

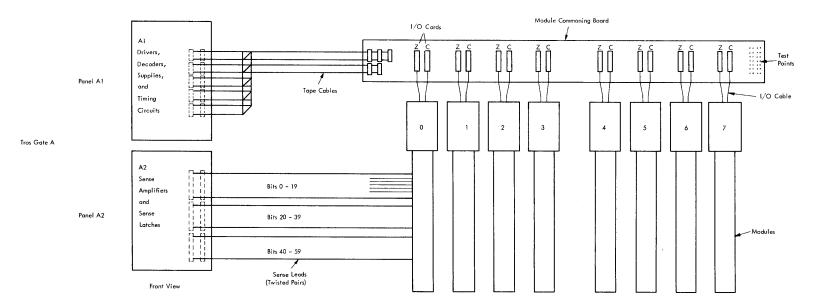

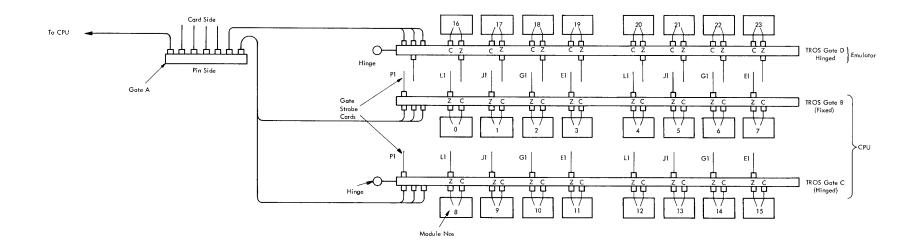

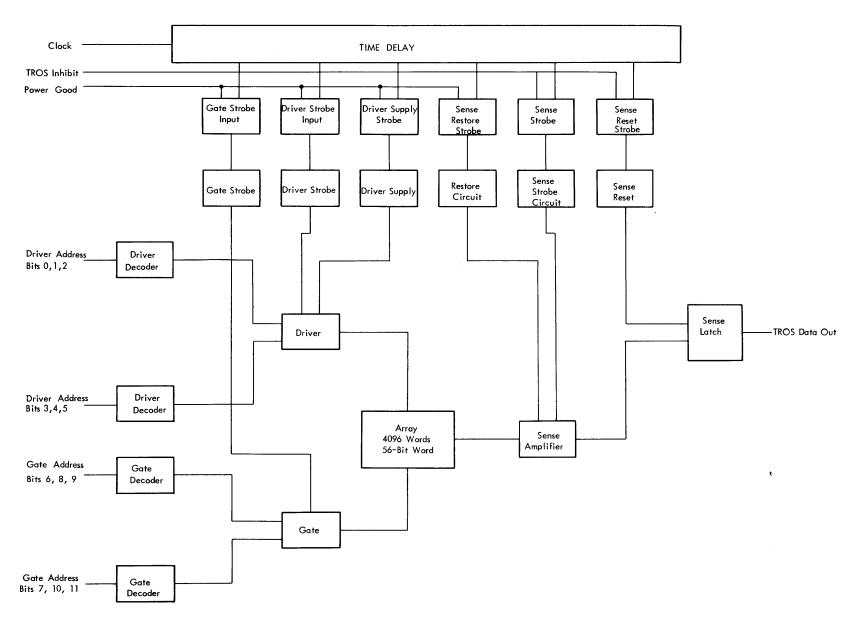

| ALU Function Register P Register (P Bus) Q Register (Q Bus) Extension Register Skew Select Register and Skew Buffer Storage Protect Registers Storage Protect Data Register                                                                | 18<br>18<br>19<br>19<br>19             | Transformer Read Only Storage (TROS)  Principles of Operation  Physical Description  The Transformer (Figure 34)  Tapes (Figure 35)  The Module  Core-Carrier Assembly      | 52<br>53<br>53<br>53<br>54       |

| Storage Protect Key Register Multiplex or Channel Registers Multiplex Data Register Multiplex Error Register Selector Channel Registers S Register T Register Channel Flags Register                                                       | 19<br>19<br>19<br>20<br>20<br>20       | Laminar Bus The Array Functional Description TROS Timing TROS Addressing TROS Drive Scheme Decoding of ROSAB (See Figure 43)                                                | 58<br>58<br>58<br>58<br>58<br>62 |

| Channel Checks and Status Register Channel Key Register W Registers (Byte Buffers) TROS Address Registers ROAR (Read Only Address Register) ROSCAR (Read Only Storage Channel Address Register) ROBAR (Read Only Back-up Address Register) | 20<br>20<br>20<br>20<br>20<br>20<br>20 | TROS Control Word and Data Flow Data Registers Emit Circuits TROS Control Word Parity Bits Control Latches Examples for Data Flow Control Determining the Next TROS Address | 64<br>66<br>66<br>66<br>66       |

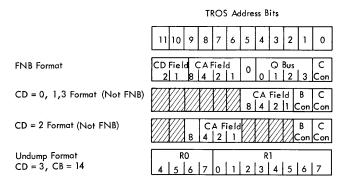

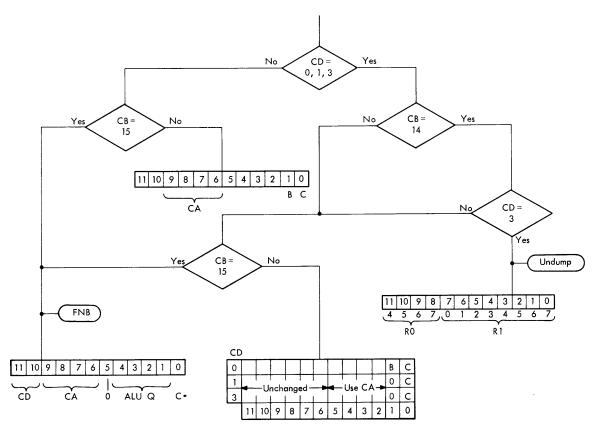

| Staticizer's (Stats)                                                                                                                                                                                                                       |                                        | FNB Format CD = 0, 1, 3 Format CD = 2 Format Undump Format                                                                                                                  | 67<br>67<br>67                   |

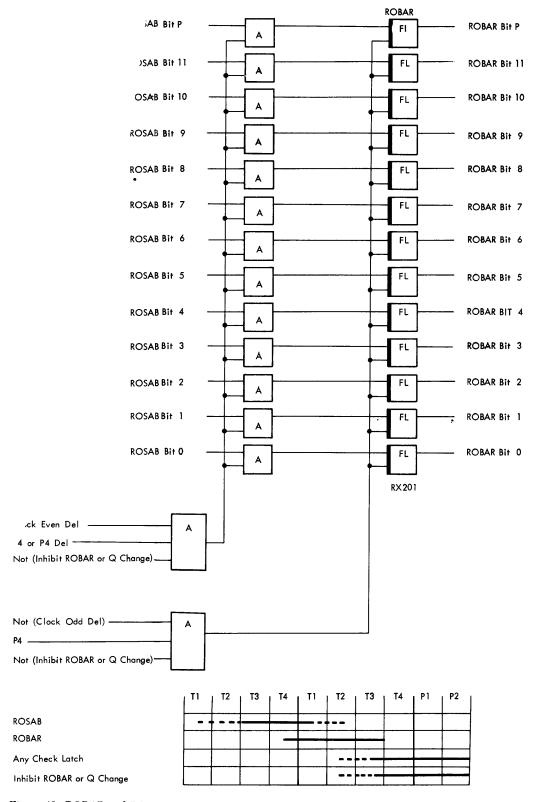

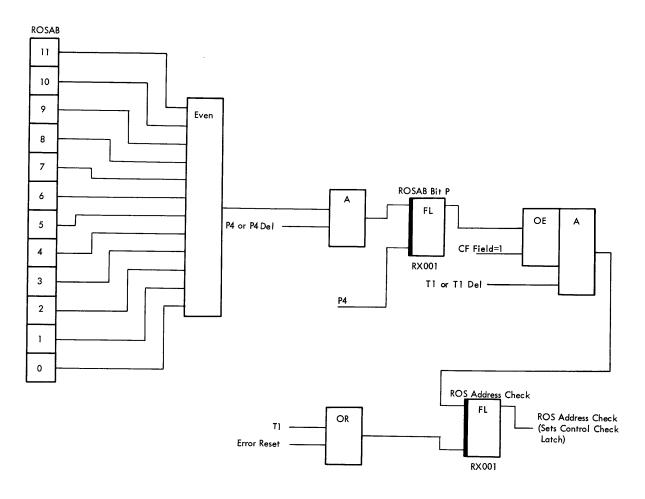

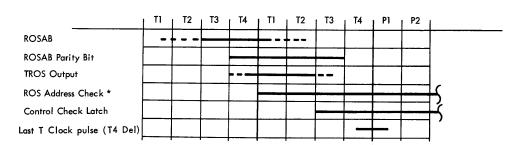

| Arithmetic and Logical Unit (ALU) ALU control TROS Control Function Control Arithmetic Binary Arithmetic                                                                                                                                   | 30<br>32<br>36<br>39                   | Special Formats Forced Addresses Examples for Generating Next TROS Address TROS Checking ROBAR (Figure 48) TROS Address Check (Figure 49)                                   | 67<br>68<br>69<br>69<br>69       |

| Decimal Arithmetic — True Add Decimal Arithmetic — Complement Add Treatment of Negative Decimal Numbers ALU Operations Logical Operations                                                                                                  | 39<br>40<br>40<br>40                   | TROS Word Data Check (Figure 50)  Control Field Decoder Checks  ROAR Format Checks (Figure 51)                                                                              | 69                               |

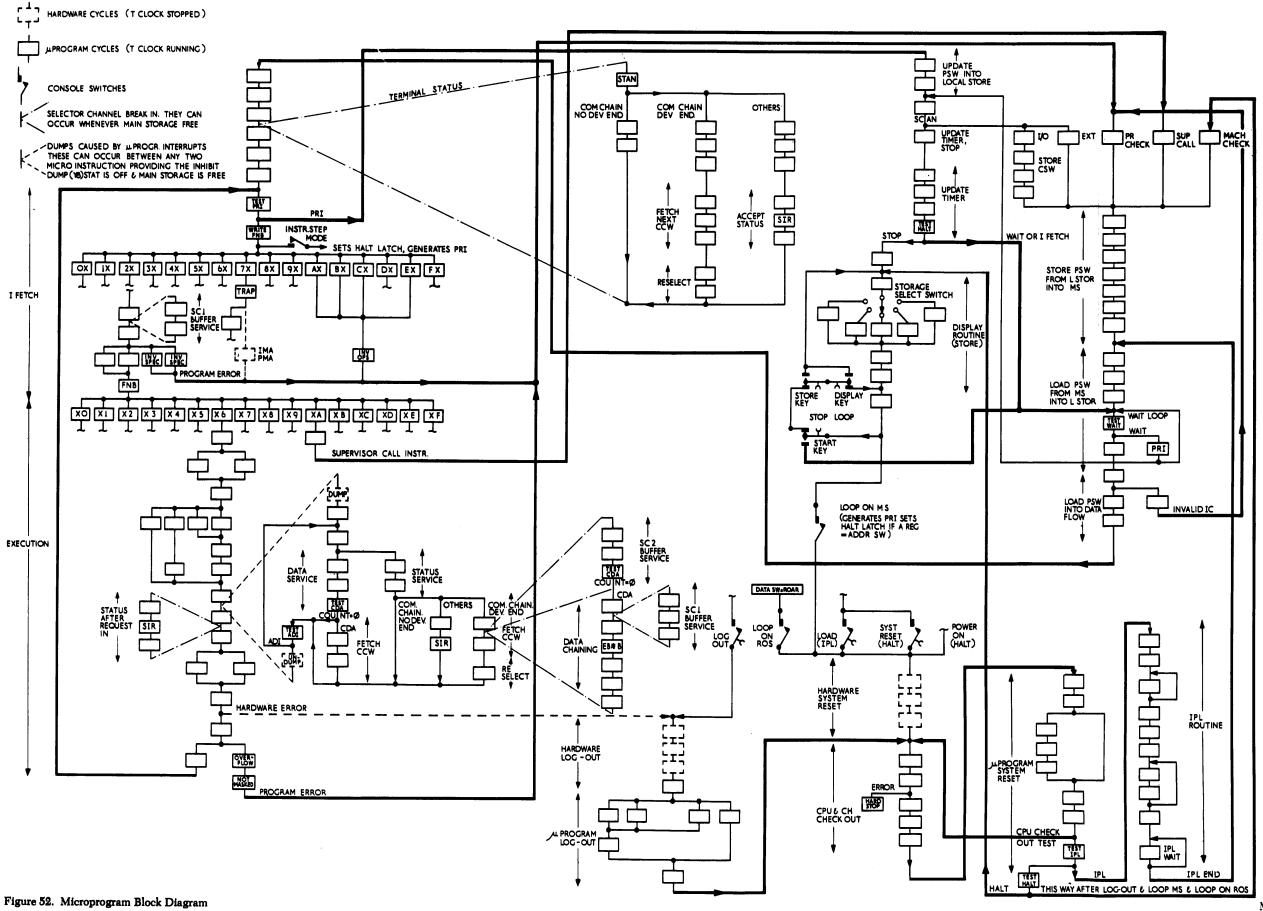

| Shifts Arithmetic Operations Carry Control Carry Latches YCI and YCD Tests and Conditions                                                                                                                                                  | 40<br>40<br>42<br>42<br>43             | Microprogram Overall Microprogram Block Diagram Individual Microroutines Circuit Functions System Operation                                                                 | 74<br>74<br>76<br>76             |

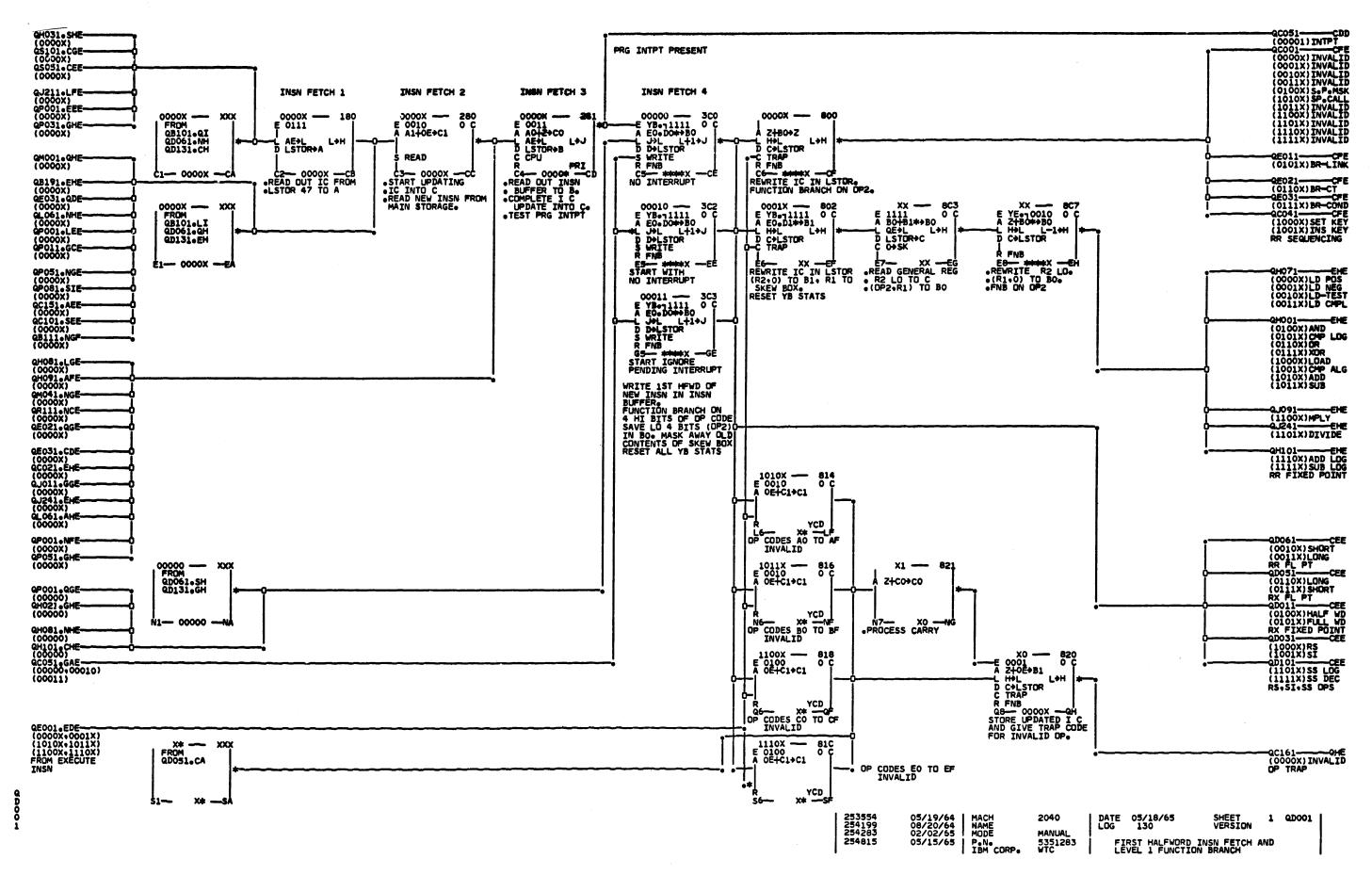

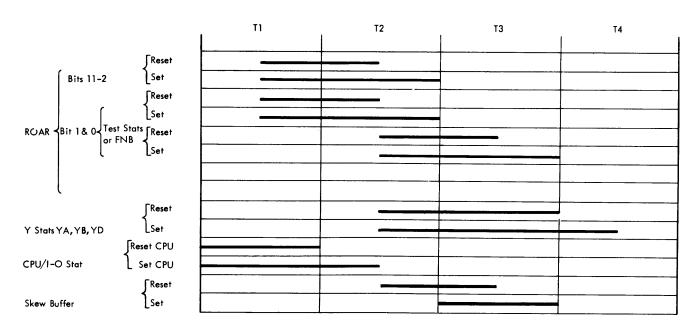

| B Condition Tests, CPU State and CD = 0 or 2 C Condition Tests, CPU State Additional Conditions Summary of ALU Conditions ALU Circuits Two Wire Logic                                                                                      | 43<br>43<br>45<br>45                   | Error Handling Manual Operations CAS Logic Diagrams Interpretation of a Single CAS Block Determination of Microinstruction Sequence                                         | 76<br>77<br>77<br>78<br>79       |

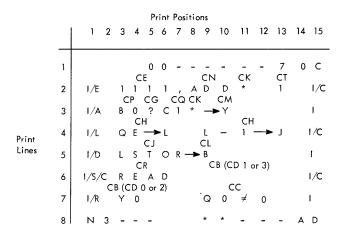

| Two-Wire Logic P and Q Input Latches Skew Feature Decimal Filler Right Shift Unit                                                                                                                                                          | 45<br>46<br>46                         | Additional Information on CLD's  CLD Example of I-Fetch Entry to I-Fetch Exits of I-Fetch First Halfword I-Fetch (Figure 54)                                                | 84<br>85<br>85                   |

| Sequence of I-Fetch Using CLD Example                                             | Protect Storage Address (PSA) Detection            | . 127 |

|-----------------------------------------------------------------------------------|----------------------------------------------------|-------|

| Other Microinstructions on Figure 54                                              | Invalid Storage Address (ISA) Detection            | .131  |

| Machine Instructions – CLFC's                                                     | Storage Address Tests (SAT and TRAP)               |       |

| Instruction Fetch Microprogram 87                                                 | Storage Protect Local Storage                      | . 131 |

| Second-Level Instruction Fetch: RX Half and                                       | General Write Scheme                               | . 133 |

| Full Word Fixed Point 87                                                          | Reading Out a Location                             |       |

| Second-Level Instruction Fetch: RX Floating Point 88                              | Addressing                                         |       |

| Second-Level Instruction Fetch: RS and SI Operations 88                           | X-Y Drive                                          |       |

| Second-Level Instruction Fetch: SS Logical 88                                     | Sense                                              |       |

| Second-Level Instruction Fetch: SS Decimal 89                                     | Inhibit                                            |       |

| Branch and Link 89                                                                | Read and Write Controls                            |       |

| Branch on Count 90                                                                | Timing Logic                                       |       |

| Branch on Condition                                                               | Storage Protect Block Diagram                      |       |

| Convert to Binary90Convert to Decimal91                                           | Circuit Description                                | .142  |

| Fixed-Point Halfword Add and Subtract 92                                          | •                                                  |       |

| Fixed-Point Multiply 93                                                           | Main Storage                                       | . 143 |

| Floating-Point Multiply 94                                                        | Capacity                                           |       |

| Shift Instructions 95                                                             | Speed                                              |       |

| omit instructions                                                                 | Storage Cycle                                      |       |

| The same of Manager Construction Construction                                     | 64K Halfword Main Storage                          | 145   |

| Theory of Magnetic Core Storage 97                                                | Address Registers                                  |       |

| Ferrite Cores 97                                                                  | Addressing                                         |       |

| Magnetic Properties 97                                                            | Drive Scheme                                       |       |

| Hysteresis Loop 98 Controlling the Core 98                                        | Common Sense/Inhibit Line                          |       |

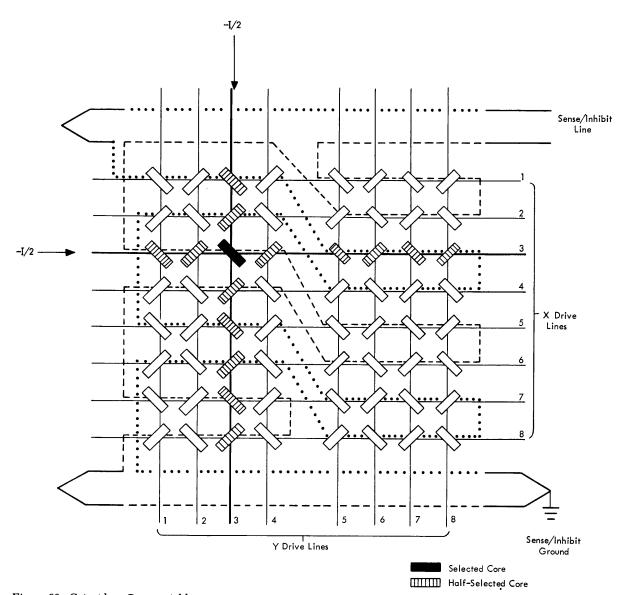

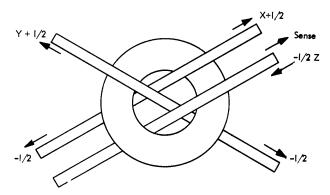

| Coincident Current Addressing 100                                                 | Control and Timing Logic Block Diagram             |       |

| Split Cycle Operation 100                                                         | Timing                                             |       |

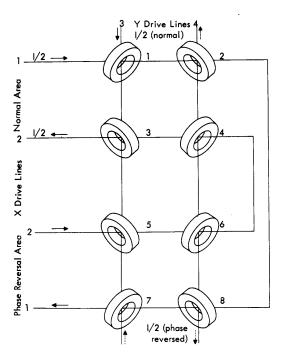

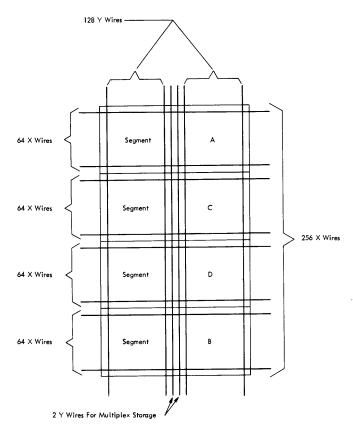

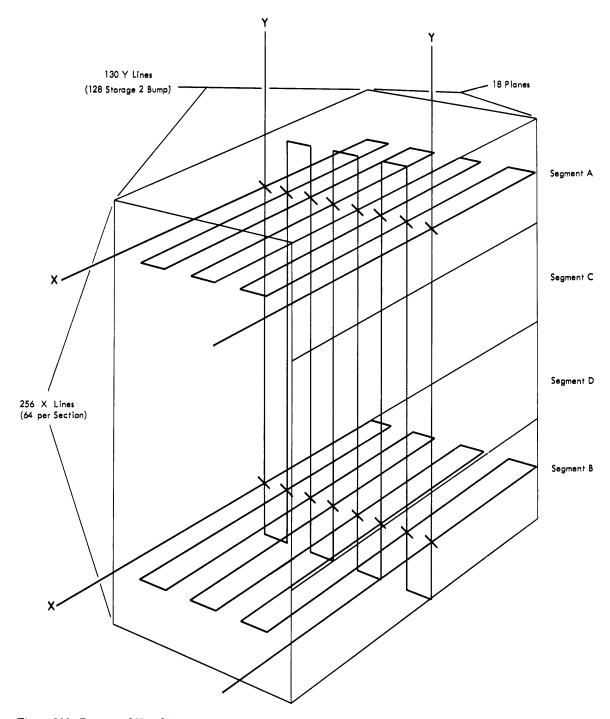

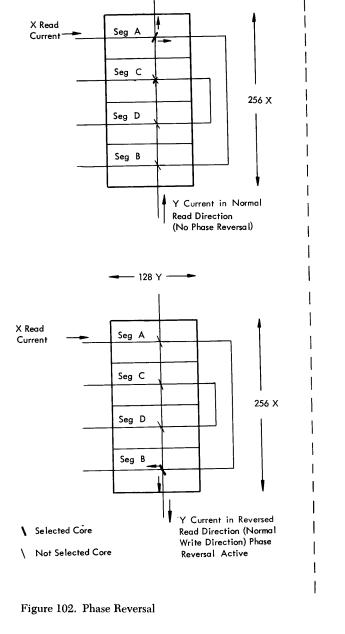

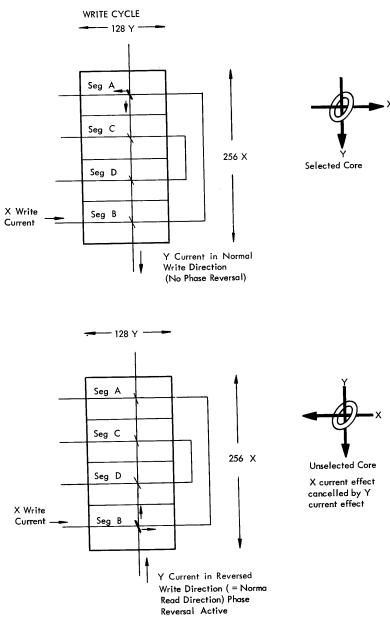

| Phase Reversal 102                                                                | External Controls                                  |       |

| 11436 1(6)61341                                                                   | Power On Reset                                     |       |

| Land Co.                                                                          | Data Register (D Register)                         |       |

| Local Storage                                                                     | Checking Storage Address Bus                       | 167   |

| External Machine Circuitry                                                        | Checking D Register                                |       |

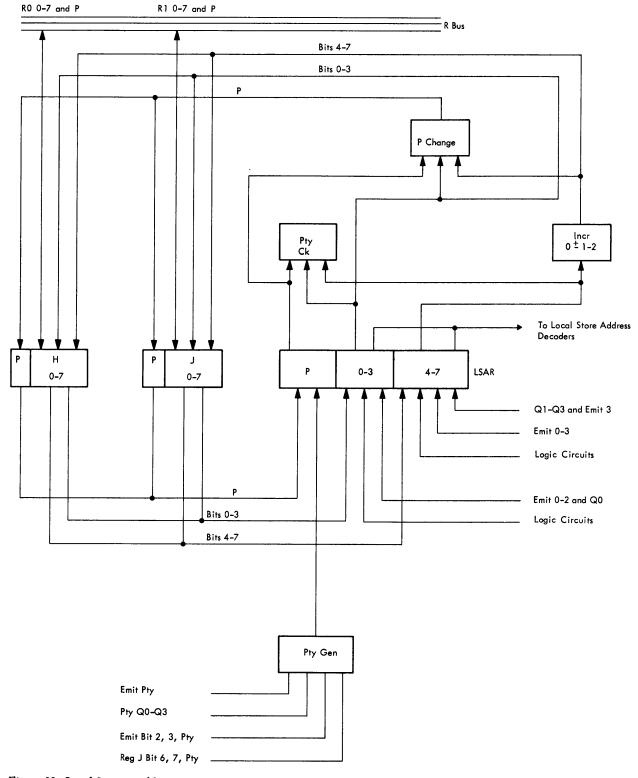

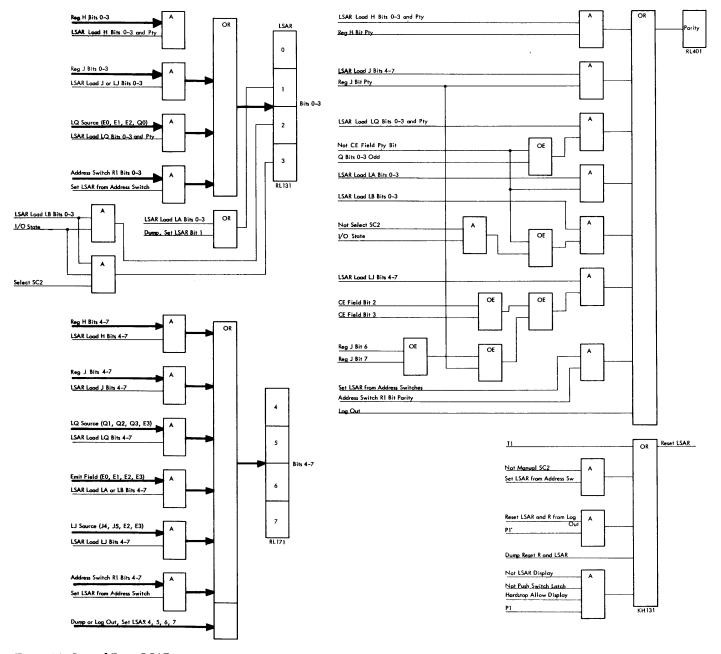

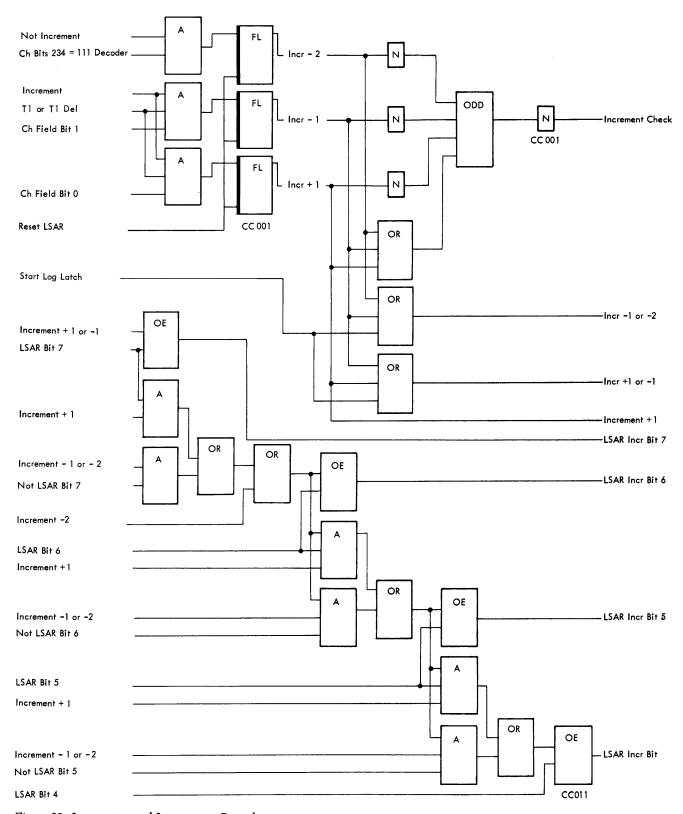

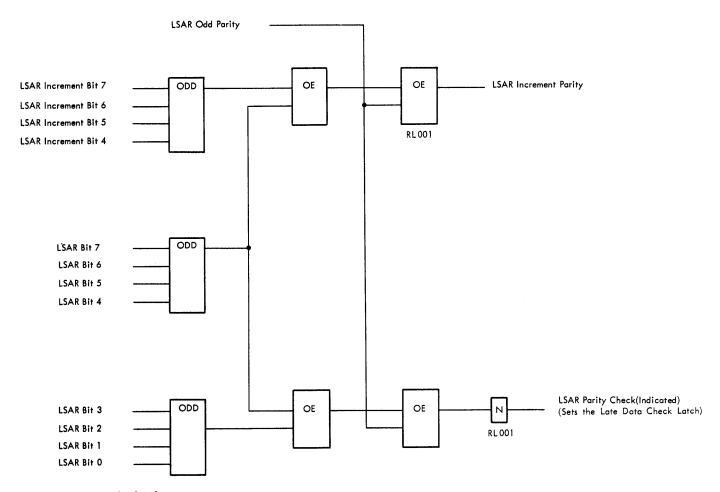

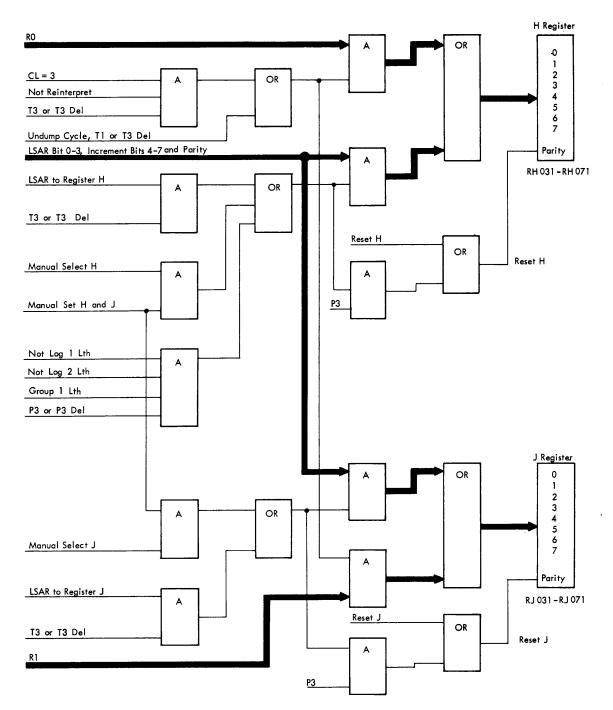

| Local Storage Address Register (LSAR)103Local Storage Address Loop (Figure 62)103 | Circuit Description                                | .167  |

| Registers in the Address Loop (Figure 62) 103                                     | 1024K Halfword Multiplex Storage                   |       |

| Incrementer 103                                                                   | Multiplex Storage Address                          | . 168 |

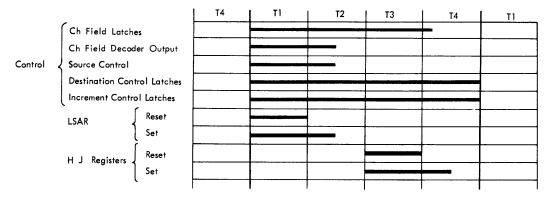

| Address Loop Controls 103                                                         | Circuit Description                                | . 169 |

| Address Loop Checking                                                             | Main Storage Power Supplies                        | . 169 |

| Timing 108                                                                        | Physical Structure of Main Storage                 | . 170 |

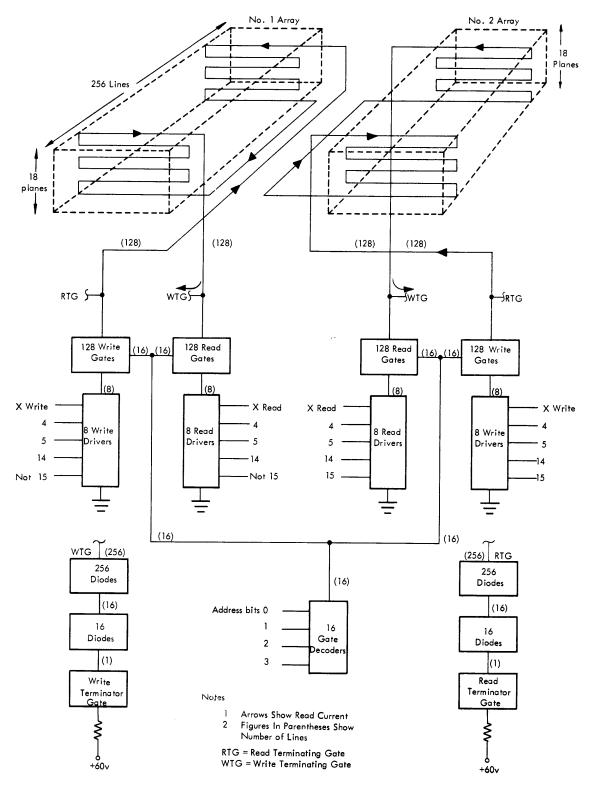

| Local Storage Data Register 108                                                   | Arrays                                             | .172  |

| Local Storage Unit                                                                | Core Planes                                        | .172  |

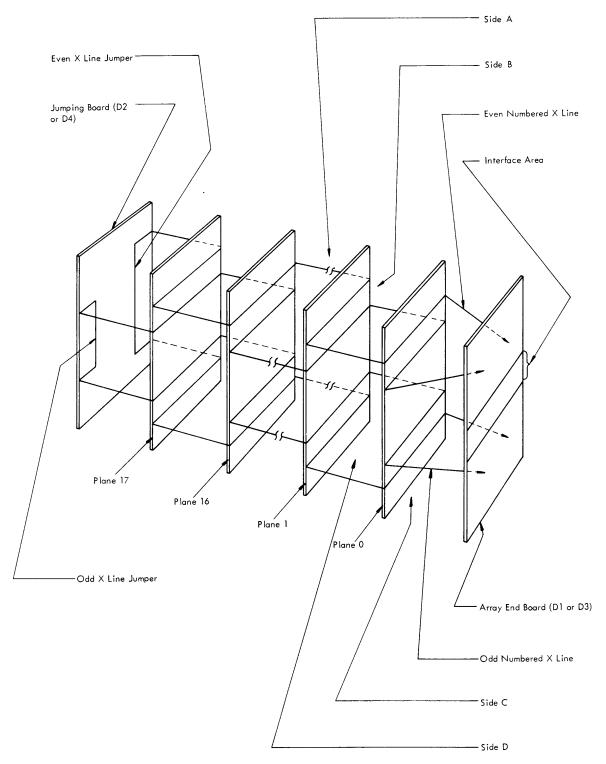

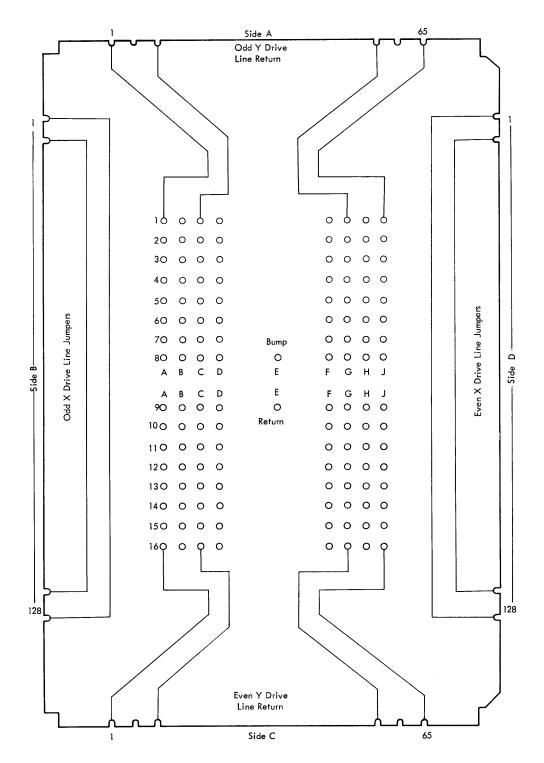

| Read Operation                                                                    | X Drive Line Routing                               | .176  |

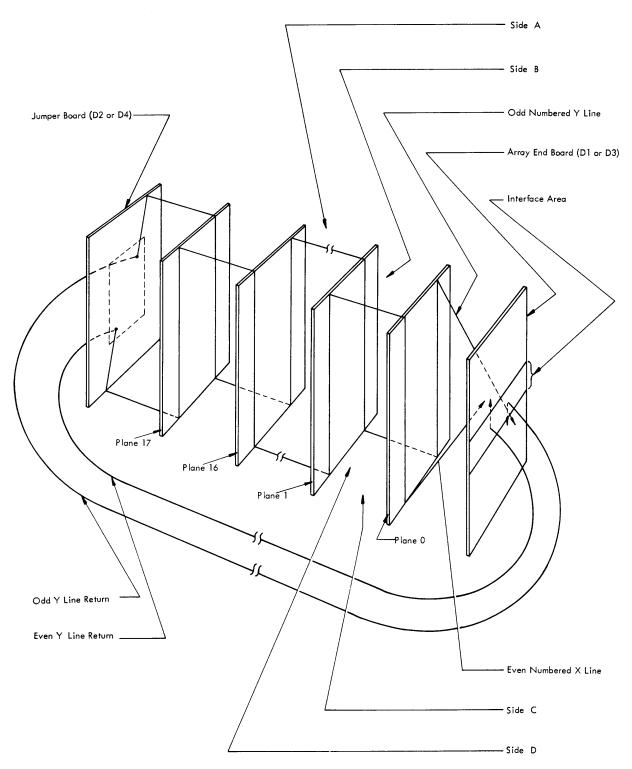

| Write Operation 112                                                               | Y Drive Line Routing                               |       |

| Addressing                                                                        | Sense/Inhibit Line Connections                     | 176   |

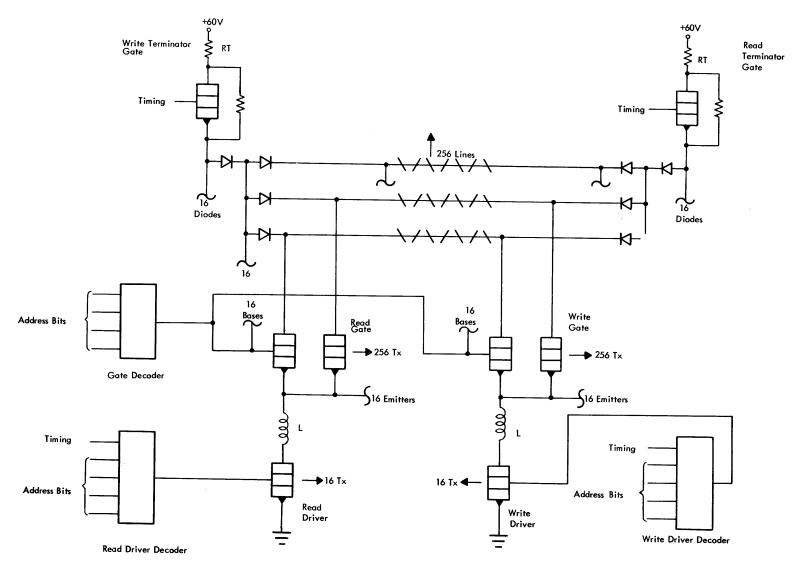

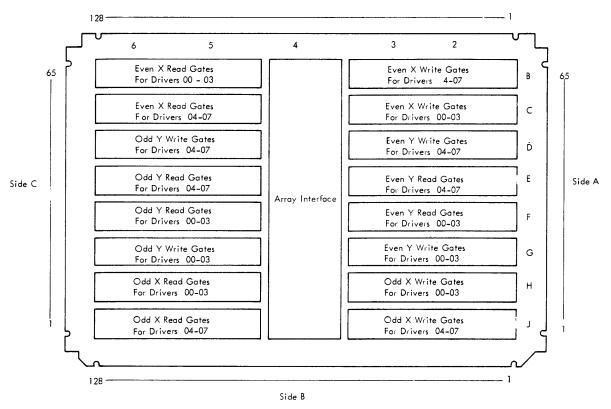

| Drive Scheme                                                                      | Array End Boards D1 and D3 Jumper Boards D2 and D4 | 176   |

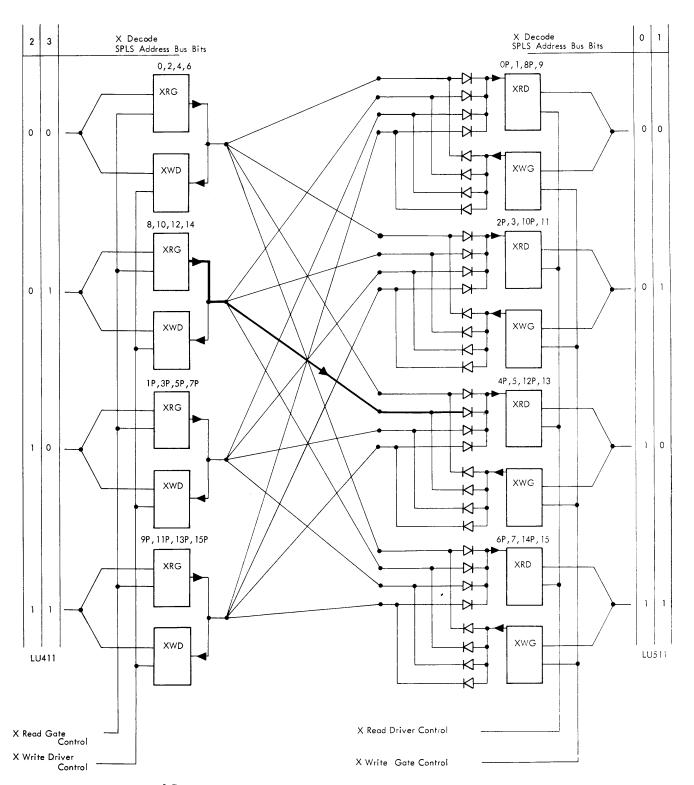

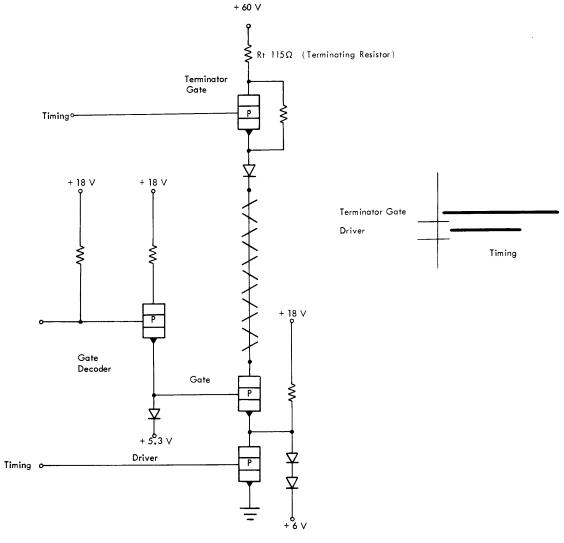

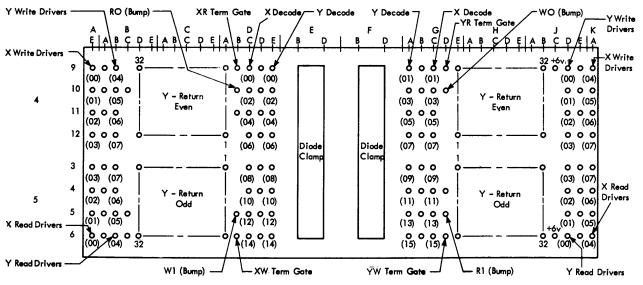

| X Line Driving and Gating                                                         | Socket Panel C1                                    | 100   |

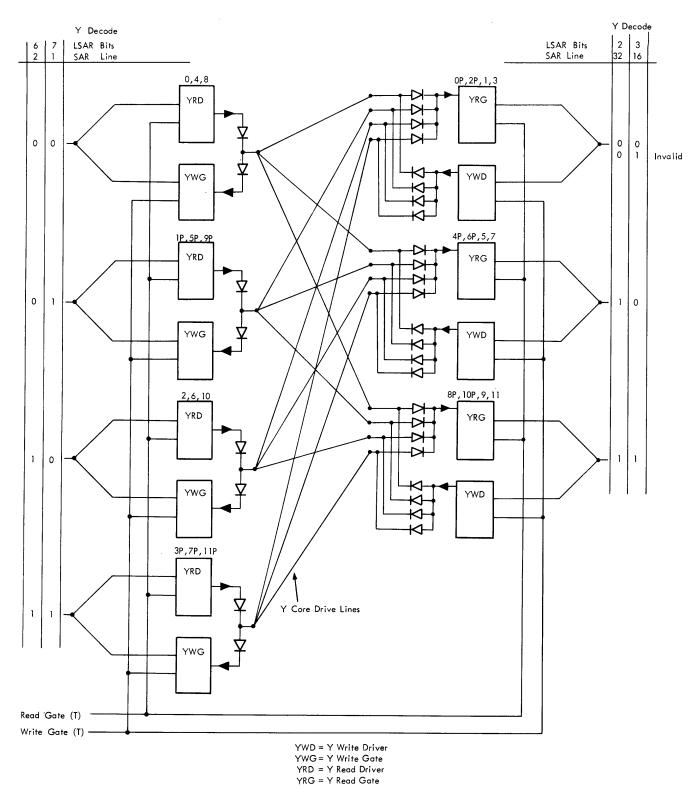

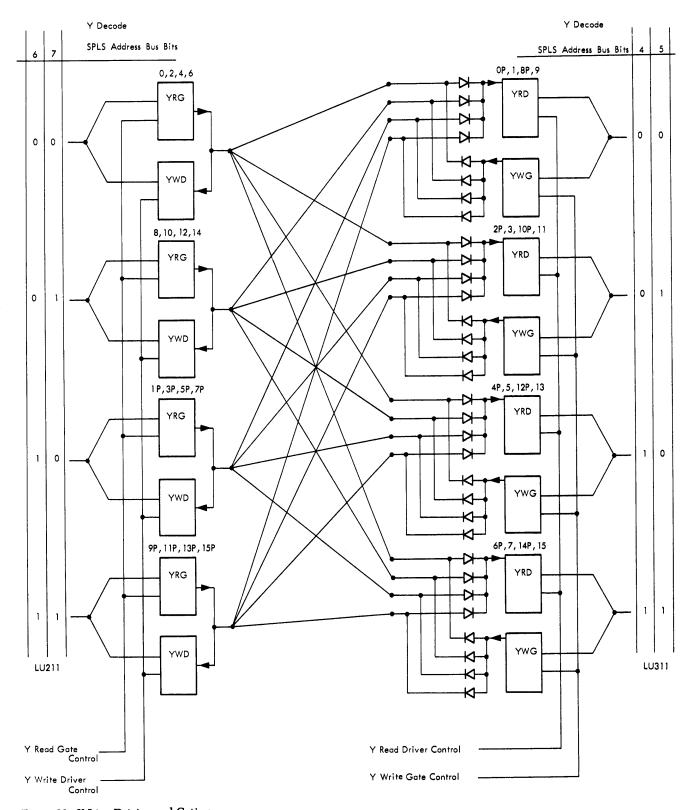

| Y Line Driving and Gating 115                                                     | Board Al                                           |       |

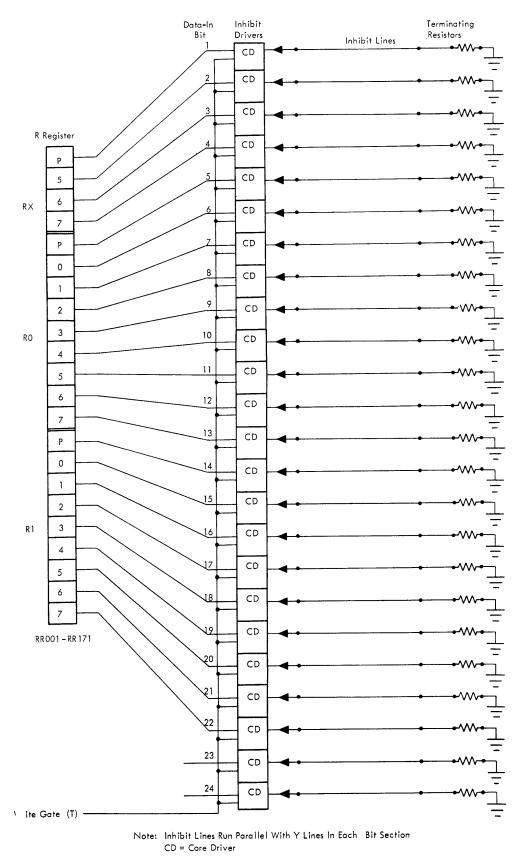

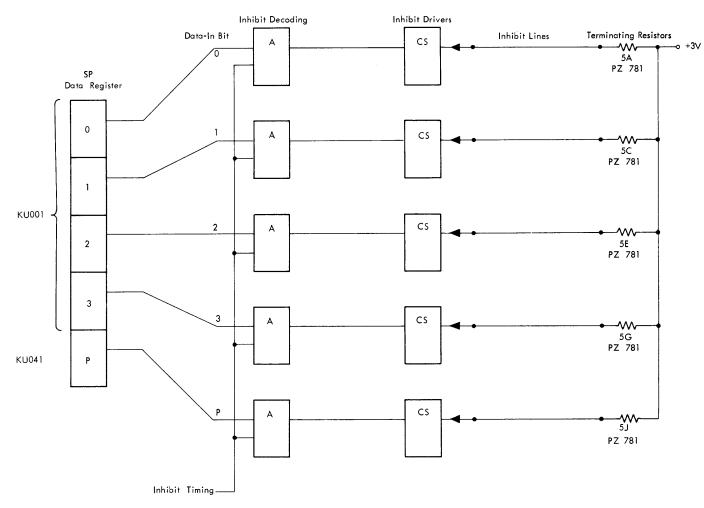

| Inhibit                                                                           | Board B1                                           |       |

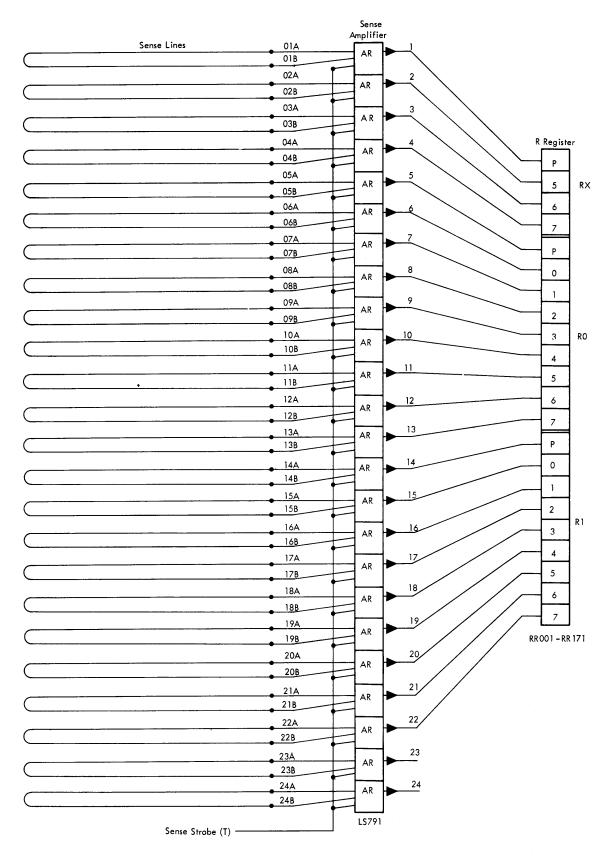

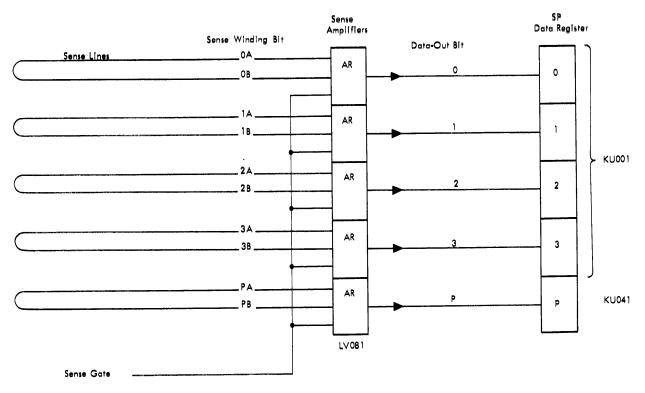

| Sense 115                                                                         |                                                    | .180  |

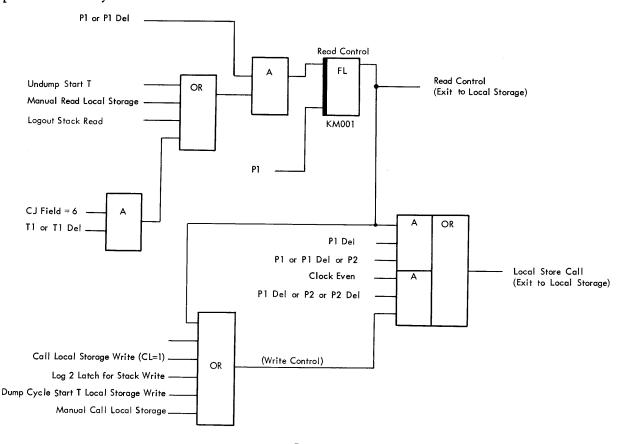

| Read and Write Controls                                                           |                                                    | . 100 |

| Timing 120                                                                        | Charling                                           | 100   |

| Read Cycle 122<br>Write Cycle 122                                                 | Checking                                           |       |

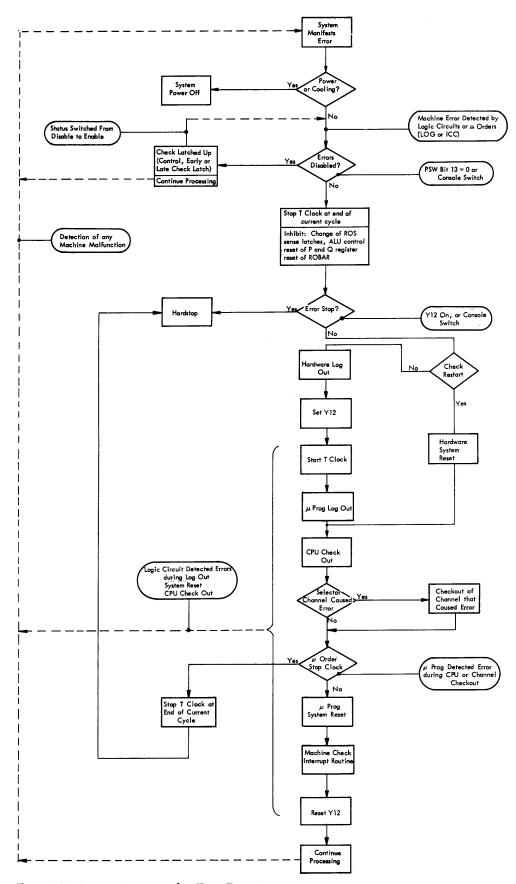

| Write Gycle 122<br>Circuit Description 122                                        | Error Detection Logic Detected Errors              | 186   |

| Circuit Bescription                                                               | Microprogram Detected Errors                       | 100   |

| · · · · · · · · · · · · · · · · · · ·                                             | Start Log Out                                      |       |

| Storage Protect 123                                                               | Stop T Clock                                       | 186   |

| Functional Unit Circuits 123                                                      | Set Interface Control Check                        | 186   |

| Storage Protect Address Bus 123                                                   | System Operation After Error Detection             |       |

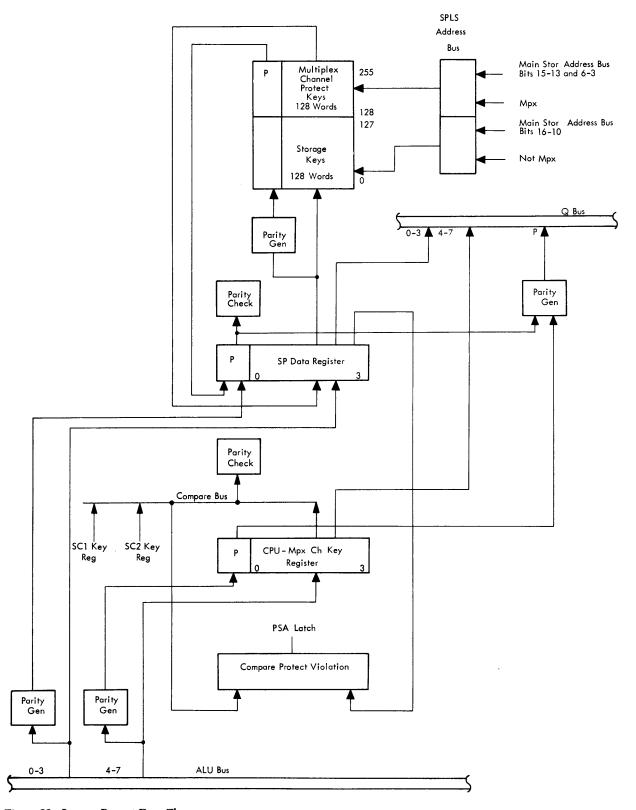

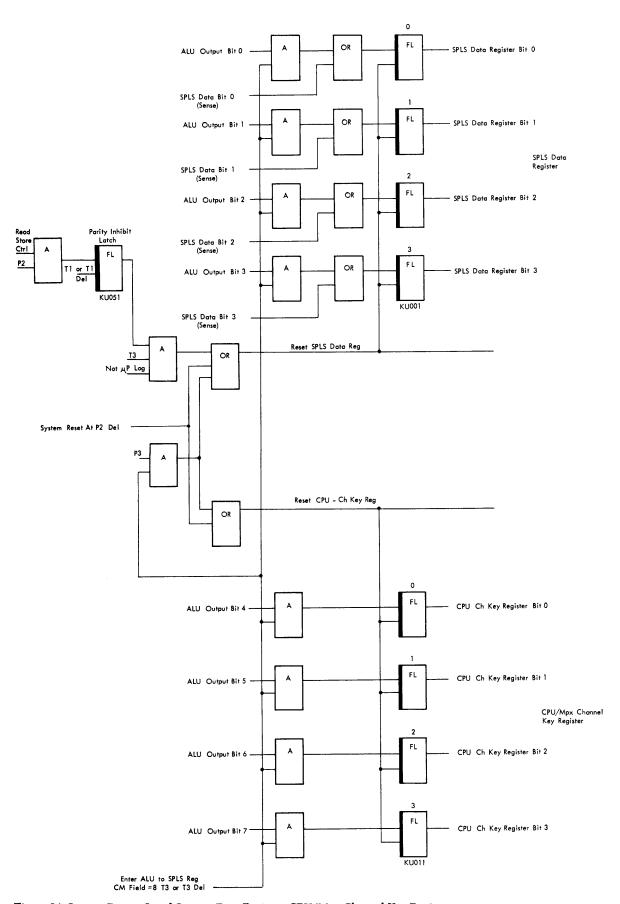

| SPLS Data Register 125                                                            | Normal Processing Mode, Errors Enabled             |       |

| CPU/Mpx Channel Key Register 125                                                  | Normal Processing Mode, Errors Disabled            | 187   |

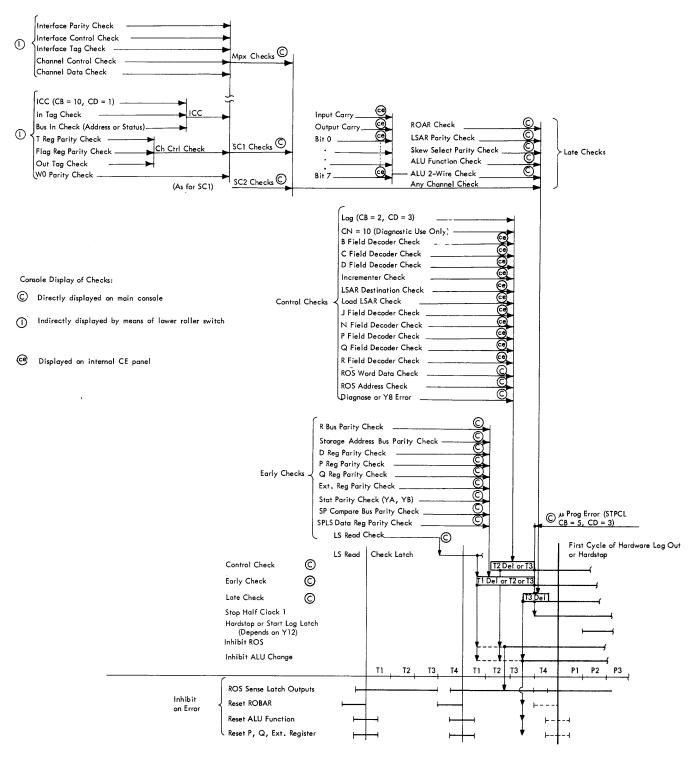

| Selector Channel Key Registers 125                                                | Checks in Relation to Timing (Figure 135)          | 187   |

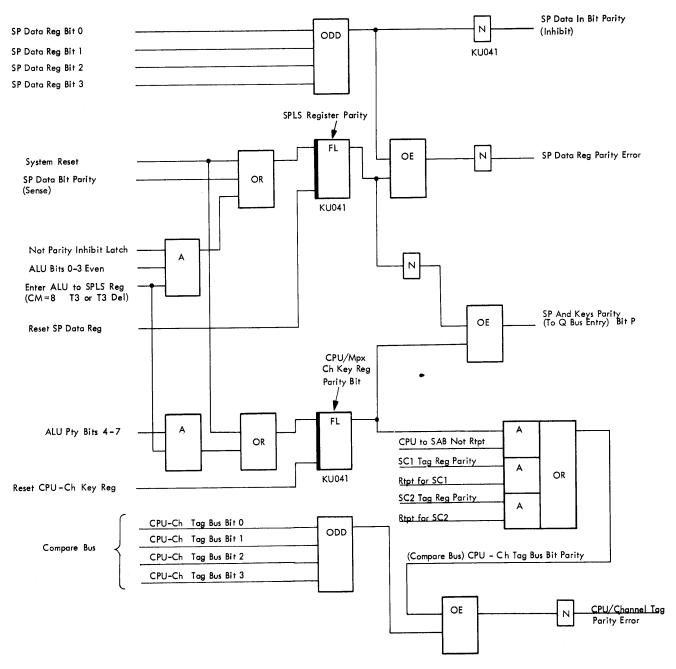

| Parity Checking 125<br>Assignment of Storage 125                                  | Other Machine Malfunctions                         | 190   |

| Examining the Storage Keys in SPLS 125                                            | Microprogram Looping                               | 190   |

| Storage Protect for CPU Operation 125                                             | Machine Malfunctions Indicated as Program Check    | . 190 |

| Storage Protect for Selector Channel 125                                          | •                                                  |       |

| Storage Protect for Multiplex Channel 127                                         | Index                                              | 191   |

| G                                                                                 |                                                    | ・エリエ  |

# Illustrations

| FIGURE           | TITLE                                            | PAGE | FIGURE         | TITLE                                           | PAGE  |

|------------------|--------------------------------------------------|------|----------------|-------------------------------------------------|-------|

| Clock            |                                                  |      | Microp         | program                                         |       |

| 1                | Basic Clock Pulses                               | 7    | 52             | Microprogram Block Diagram                      | 75    |

| $\overset{1}{2}$ | Clock System                                     |      | 53             | CAS Block Frame                                 |       |

| 3                | Clock Start/Stop Circuit for A Gate              |      | 54             | CLD Sample                                      |       |

| 4                | T Clock Start/Stop Controls                      |      | 55             | Essential Timings for Interpretation of CLD's   |       |

| 5                | Start/Stop for B Gate Clocks                     |      | 00             | Essential Timings for Interpretation of CED's   | . 00  |

|                  | <u>-</u>                                         |      | Theory         | of Magnetic Core Storage                        |       |

|                  |                                                  |      | 56             | Two Stable States of Magnetic Core              | . 97  |

| Registe          | ers                                              |      | 57             | 1 Changing to 0                                 | . 97  |

| 6                | Registers                                        | 19   | 58             | Core Field While Changing States                |       |

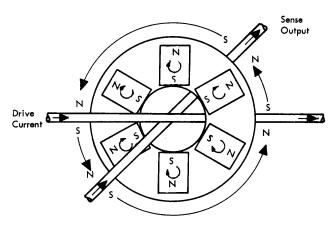

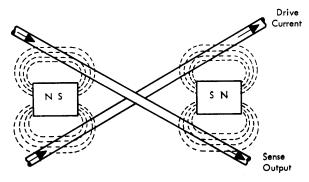

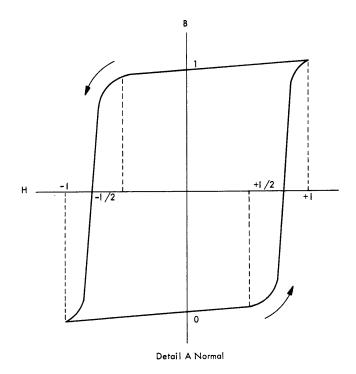

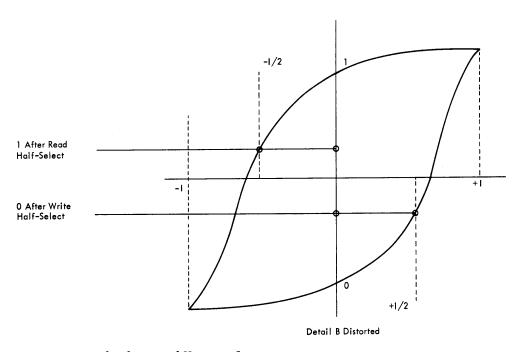

| 7                | A Register Circuits                              |      | 59             | Normal and Distorted Hysteresis Loops           |       |

| 8                | D Register Set (Only D0 Shown)                   |      | 60             | Coincident Current Addressing                   |       |

| 9                | R Bus Entry                                      |      | 61             | Cores Involved in Phase Reversal                | . 102 |

| 10               | Hardware Entry to Q Bus                          |      | 1 1 6          | •                                               |       |

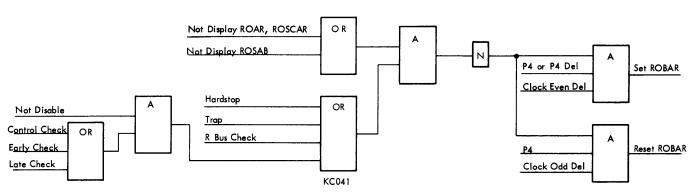

| 11               | Set and Reset of ROBAR                           |      | Local S        | _                                               |       |

|                  |                                                  |      | 62             | Local Storage Address Loop                      |       |

| c                |                                                  |      | 63             | CH Field Control Chart                          |       |

| Staticiz         | zers                                             |      | 64             | Set and Reset LSAR                              |       |

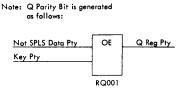

| 12               | Staticizer Parity Bit Generation                 | 23   | 65             | LSAR Bits                                       |       |

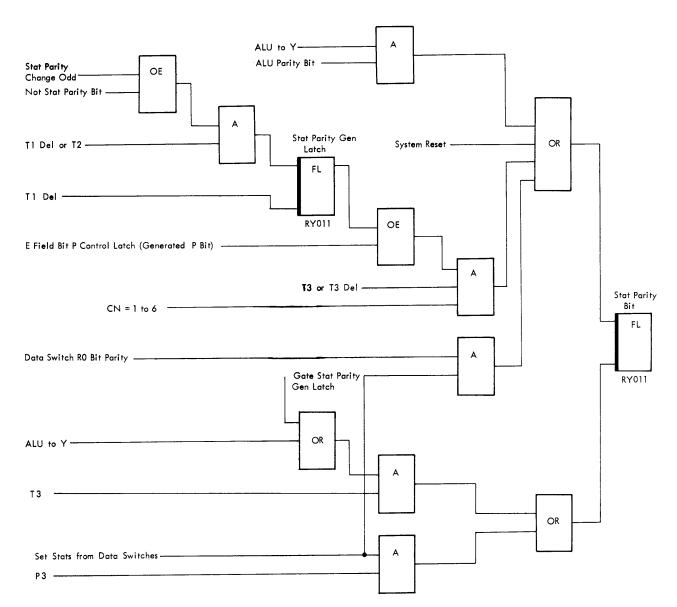

| 13               | YA and YB Parity Change                          | 24   | 66             | Incrementer and Incrementer Control             |       |

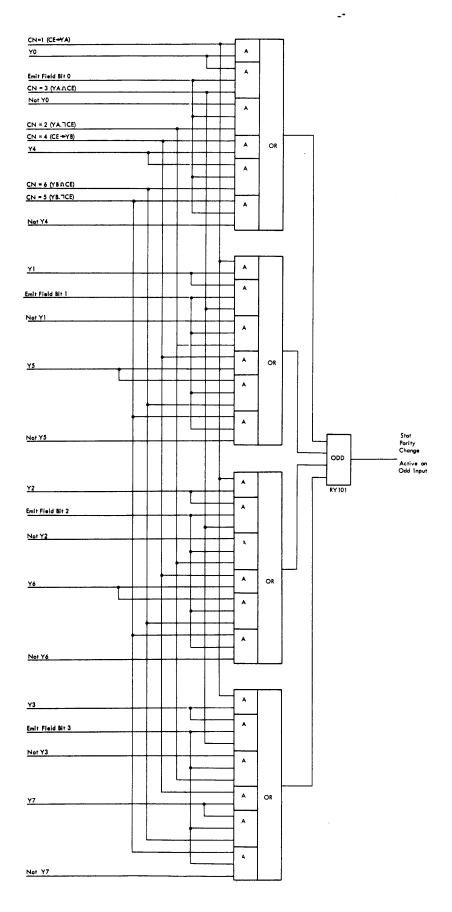

| 14               | Y Stats, Function and Control                    | 25   | 67             | Parity Check/Change                             |       |

| 15               | YA Stats                                         |      | 68             | LSAR Destination, H and J Register              |       |

| 16               | YD Stats                                         | 27   | 69             | Local Storage Address Loop Timing               |       |

| 17               | YE Stats                                         | 28   | 70             | Local Storage Block Diagram                     |       |

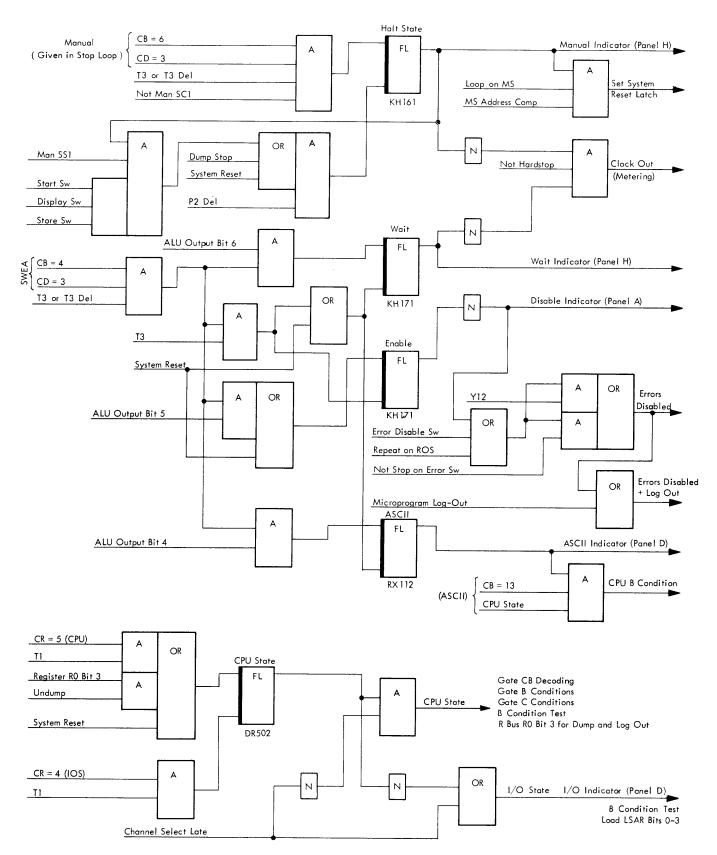

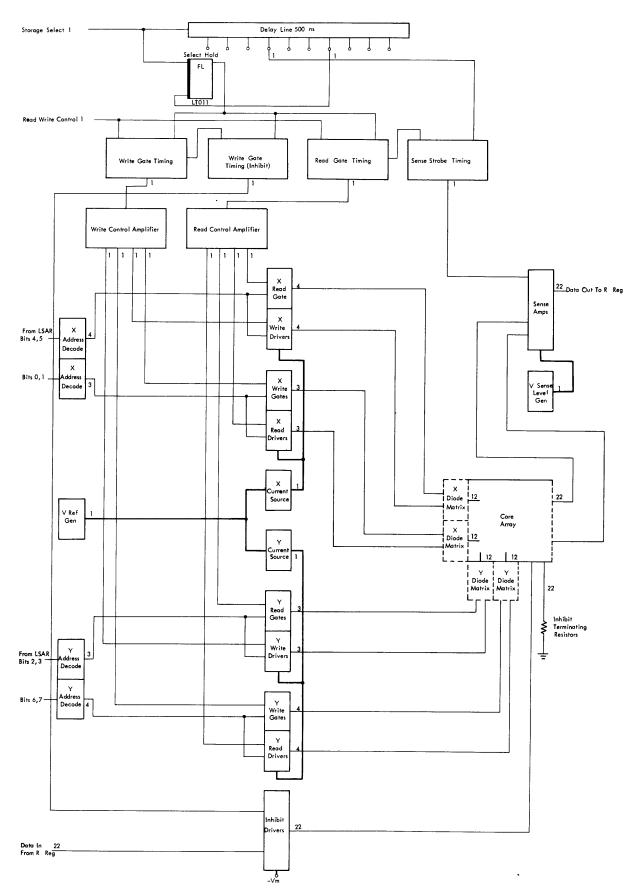

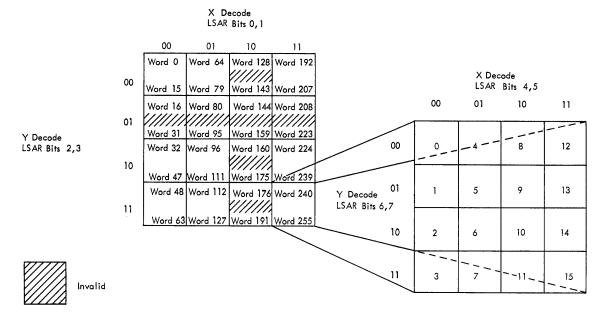

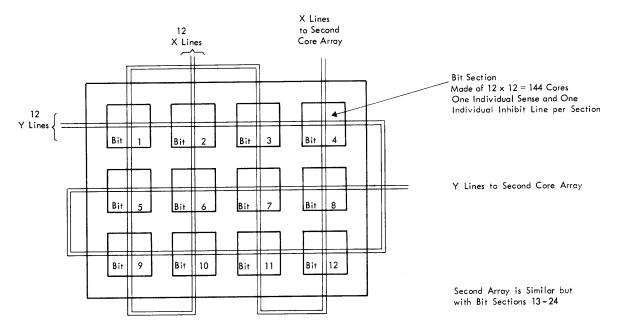

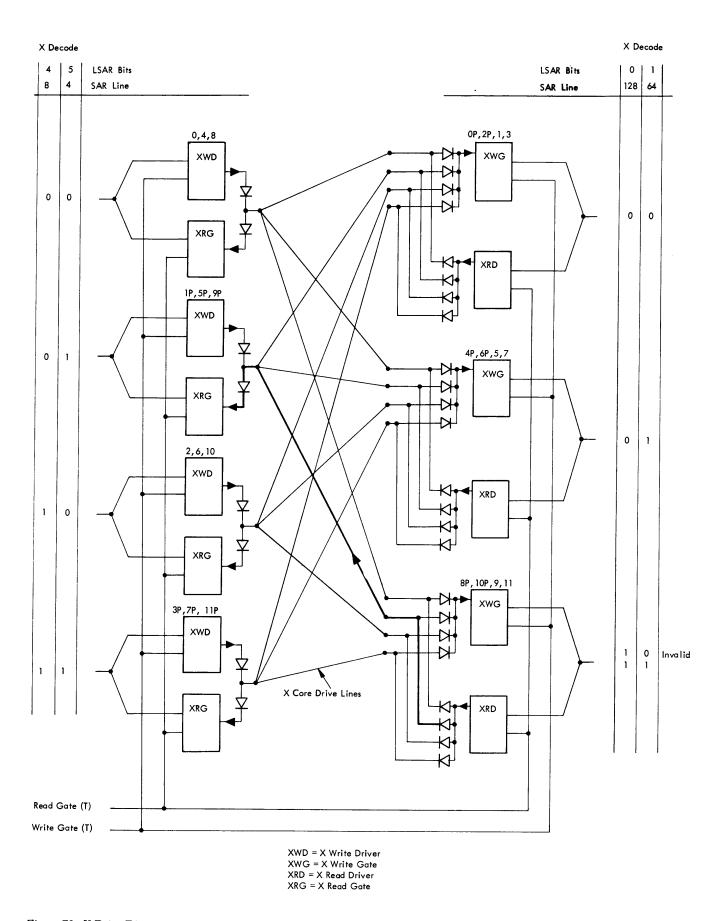

| 18               | Stats (Halt State, Wait, Enable, ASCII, I/O)     | 29   | $\frac{71}{2}$ | Address Decode Diagram                          |       |

|                  |                                                  |      | <b>72</b>      | Layout of One Core Plane                        |       |

| Arithm           | etic and Logical Unit (ALU)                      |      | 73             | X Drive Diagram                                 |       |

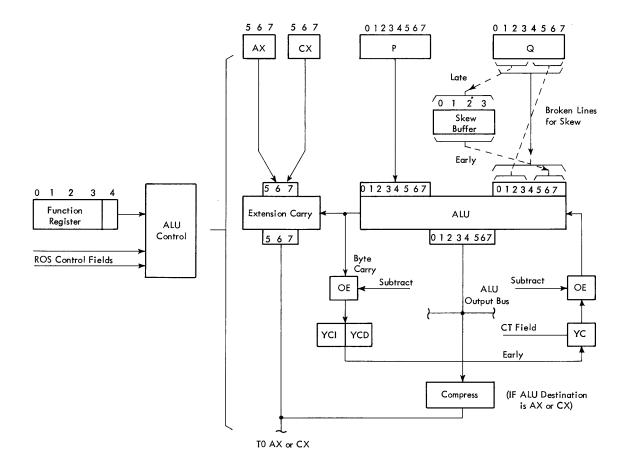

| 19               | ALU Schematic                                    | 31   | 74             | Y Drive Diagram                                 |       |

| 20               | ALU Control Signals and Functions                |      | 75<br>76       | Inhibit Drive Diagram                           |       |

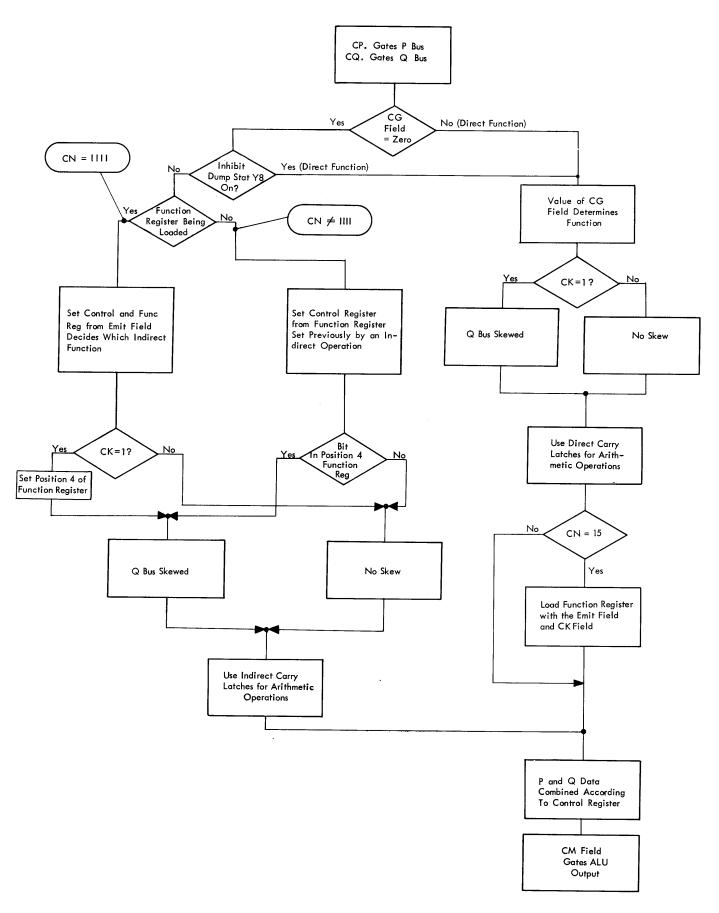

| 21               | Effects of ROS Fields on ALU                     |      | 76             | Sense Diagram                                   |       |

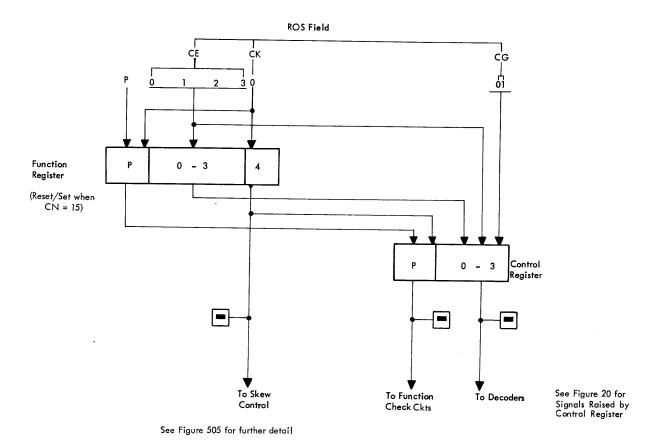

| $\frac{21}{22}$  | Function and Control Registers                   |      | <b>77</b>      | Local Storage Read and Write Controls           |       |

| 23               | Function Check Signals                           |      | <b>78</b>      | Local Storage Timing Circuit                    |       |

| 24               | Examples of Fixed-Point Binary Subtraction       |      | 79             | Local Storage Timing Diagram                    | . 121 |

| 2 <del>5</del>   | ALU Work Sheet (2 Sheets)                        |      | C4             | a Durata et                                     |       |

| 26               | ALU Carry Latches                                |      | Storage        | e Protect                                       |       |

| 27               | ALU Timing Chart                                 |      | 80             | Storage Protection Symbolically                 | . 124 |

| 28               | Skew Select Schematic                            |      | 81             | SPLS Addressing Scheme                          | . 125 |

| 29               | Right Shift Box (Example Right Shift)            |      | 82             | Storage Protect Data Flow                       | . 126 |

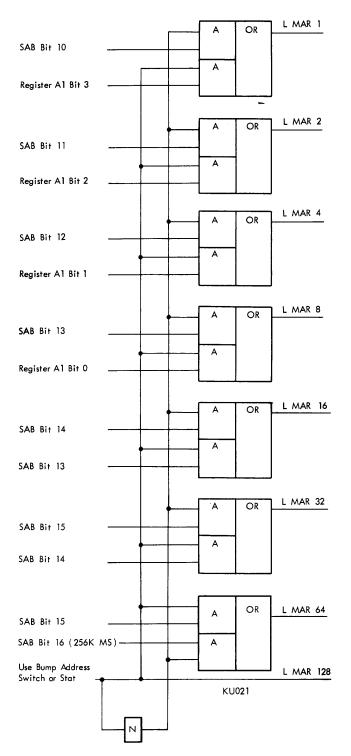

| 30               | ALU Sum Generator                                |      | 83             | Storage Protect Address Bus                     | . 127 |

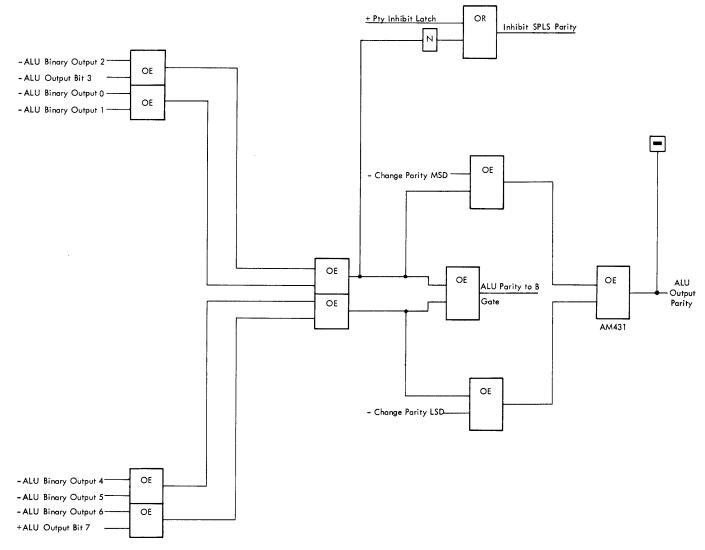

| 32               | ALU Parity Generation                            |      | 84             | Storage Protect Local Storage Data Register,    |       |

|                  |                                                  | 00   |                | CPU/Mpx Channel Key Register                    |       |

| Transfe          | ormer Read Only Storage (TROS)                   |      | 85             | Parity Inhibit, Parity Generation, Parity Check |       |

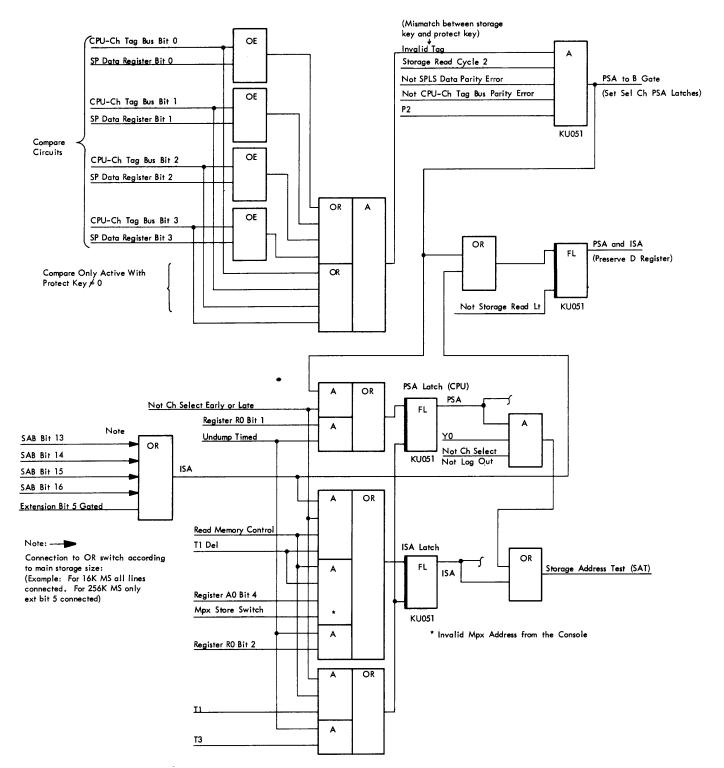

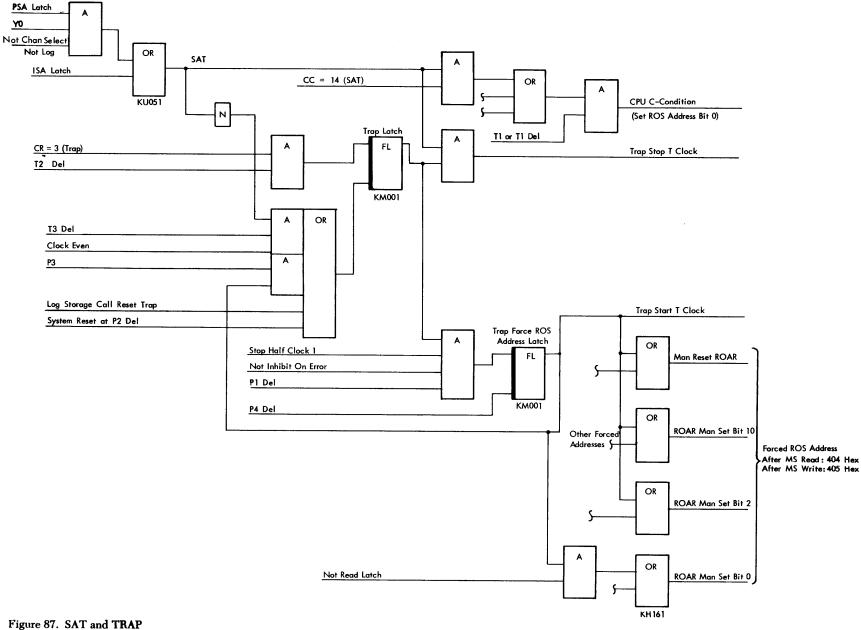

|                  |                                                  |      | 86             | PSA and ISA Detection                           |       |

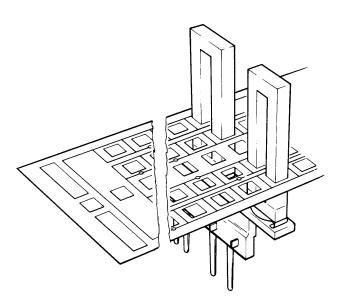

| 33               | Principle of TROS                                | oz   | 87             | SAT and TRAP                                    |       |

| 34               |                                                  |      | 88             | Storage Protect Core Plane Bit Sections         |       |

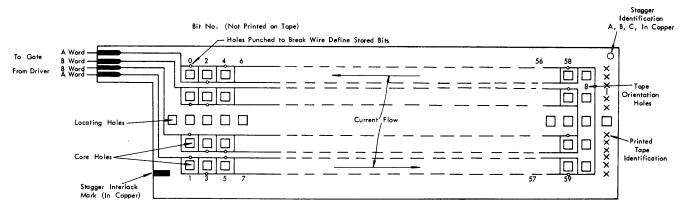

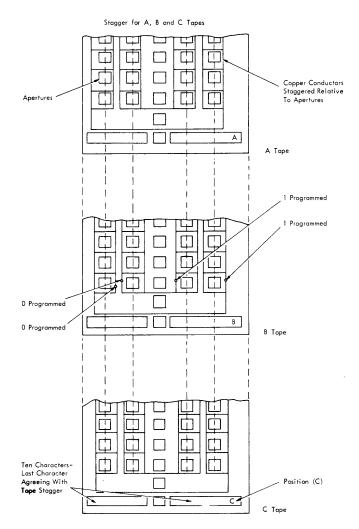

| 35               | Tape Layout                                      |      | 89             | Storage Protect Address Decode                  | . 134 |

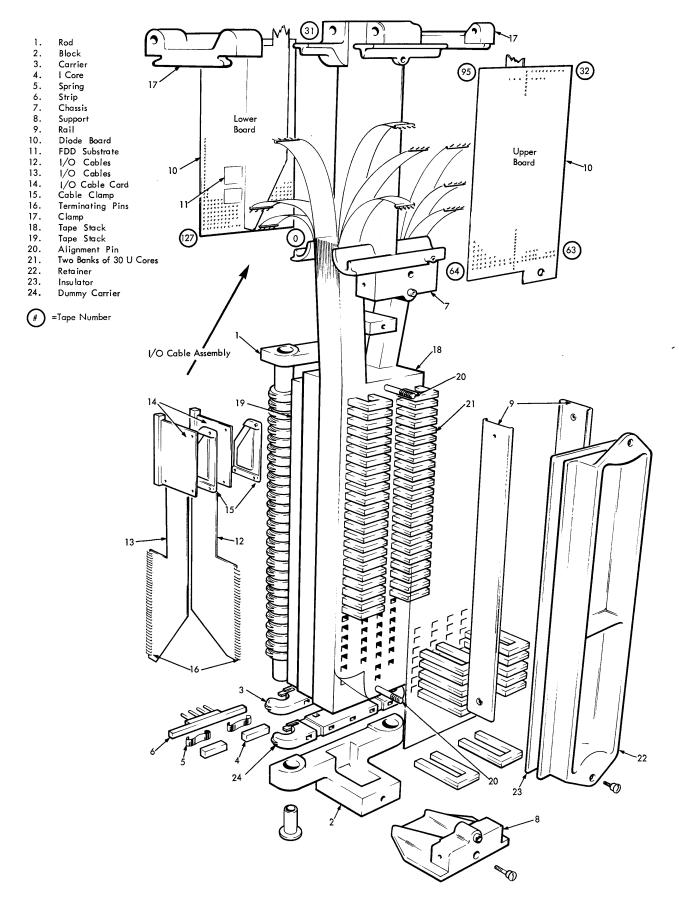

| 36               | Tape Stagger TROS Module (Exploded View)         |      | 90             | X Line Driving and Gating                       |       |

| 37               |                                                  |      | 91             | Y Line Driving and Gating                       |       |

| 38               | Core-carrier Assembly                            |      | 92             | Sense Schematic                                 |       |

| 39               | General Arrangement of TROS Hardware             |      | 93             | Inhibit Drive Schematic                         |       |

| 40               | 4K TROS Block Diagram                            |      | 94             | Storage Protect Timing Circuit                  |       |

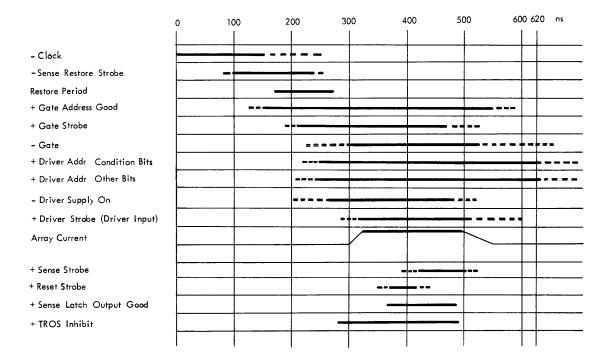

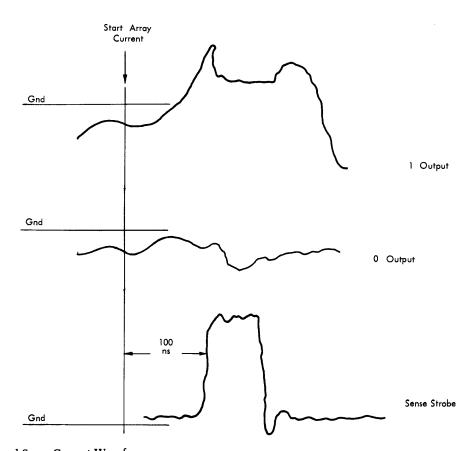

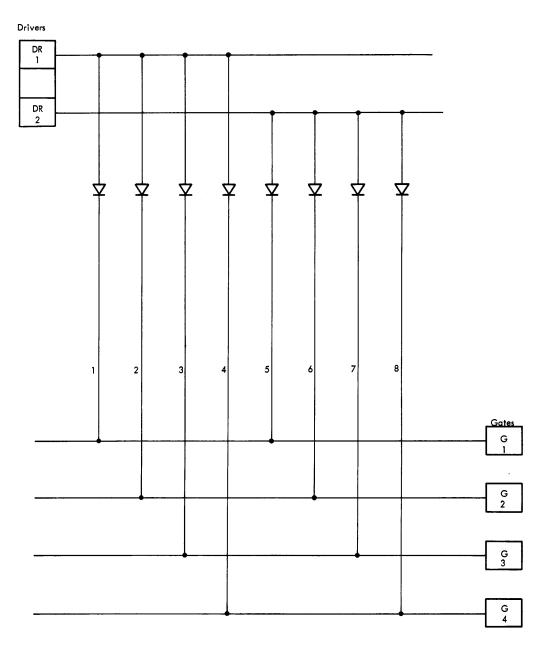

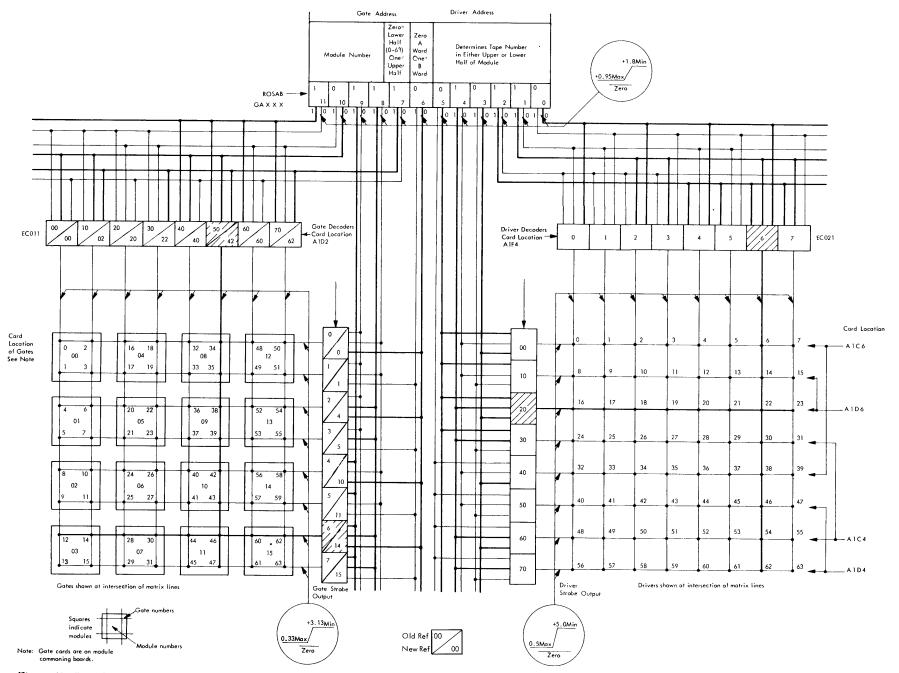

| 41               | TROS Timing and Sense Current Waveforms          |      | 95             | Storage Protect                                 | . 141 |

| 42<br>43         | Principle of Driving and Gating Decoding of ROAR |      |                |                                                 |       |

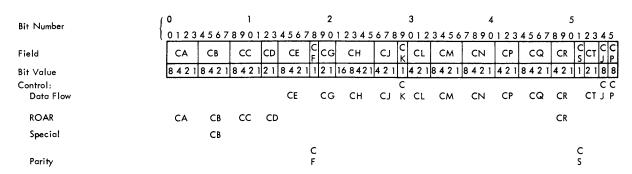

| 43<br>44         | TROS Control Word and Basic Functions            |      | Main S         | torage                                          |       |

| 44<br>45         | IBM System/360 Model 40 Data Flow                |      | 96             | Core Storage Locations                          | . 144 |

| 45<br>46         | Basic TROS Address Bit Generation                |      | 97             | Phase Reversal Control                          |       |

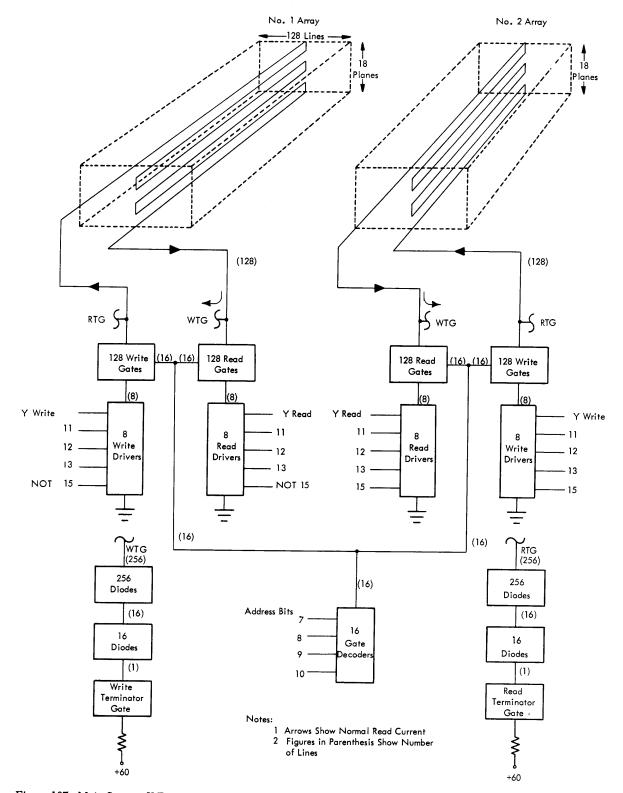

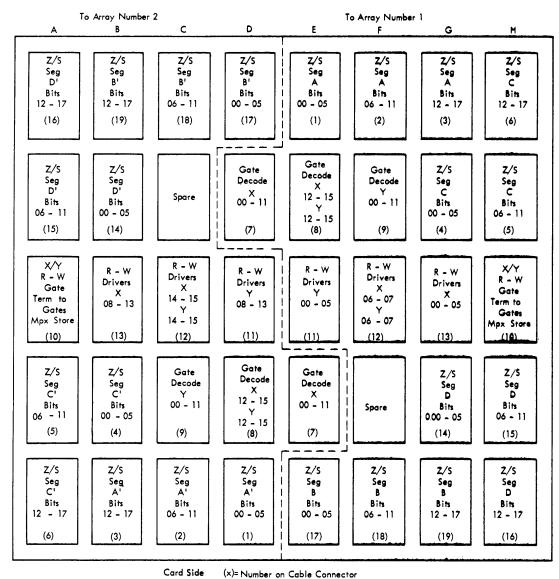

| 40<br>47         | Determining Next TROS Address                    |      | 98             | Main Storage Arrays                             | .147  |

| 48               | ROBAR and ROBAR Timing (4K TROS)                 |      | 99             | Plane Layout                                    |       |

| 40<br>49         | TROS Parity Bit Generation and TROS Parity       | 10   | 100            | Routing of X and Y Wires                        |       |

| 70               | Check (4K TROS)                                  | 71   | 101            | Routing of X Lines                              |       |

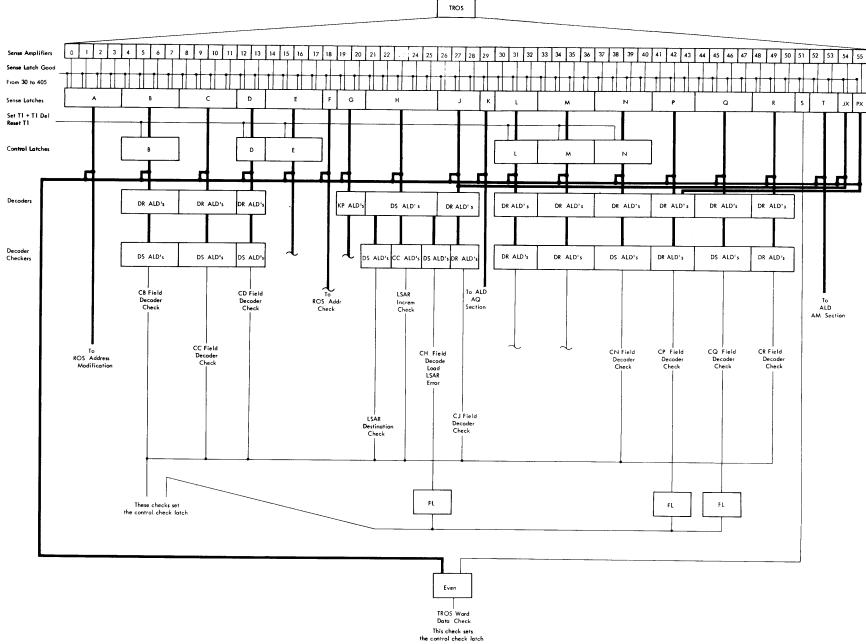

| 50               | Data Check and Control Field Decoder Checks      |      | 101            | Phase Reversal                                  |       |

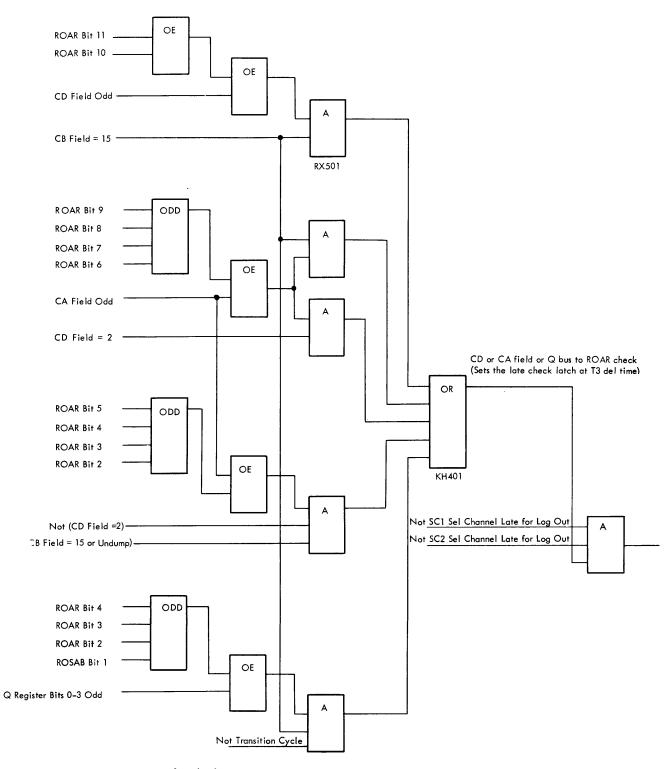

| 50<br>51         | DAOX to BOAR Transfer Check                      | 73   | 102            |                                                 | 152   |

| FIGURE | TITLE P.                                       | AGE | FIGURE | TITLE PAGE                                          |

|--------|------------------------------------------------|-----|--------|-----------------------------------------------------|

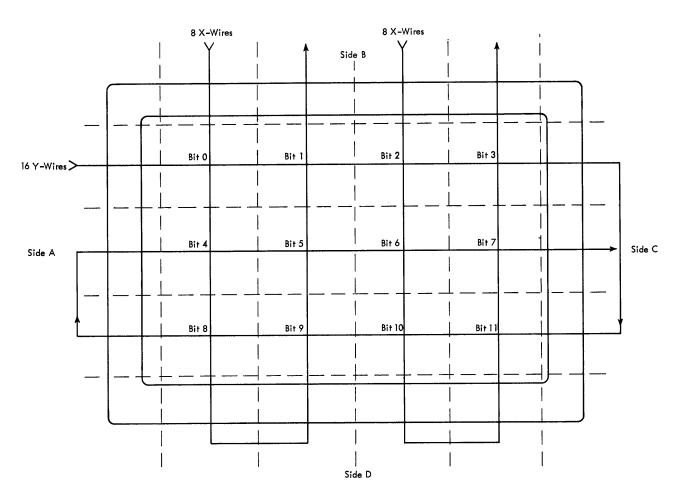

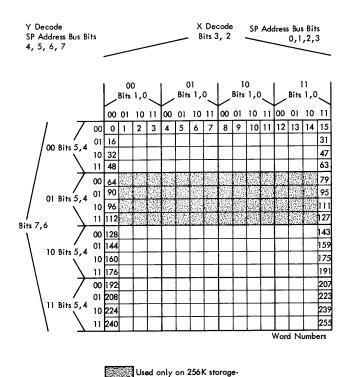

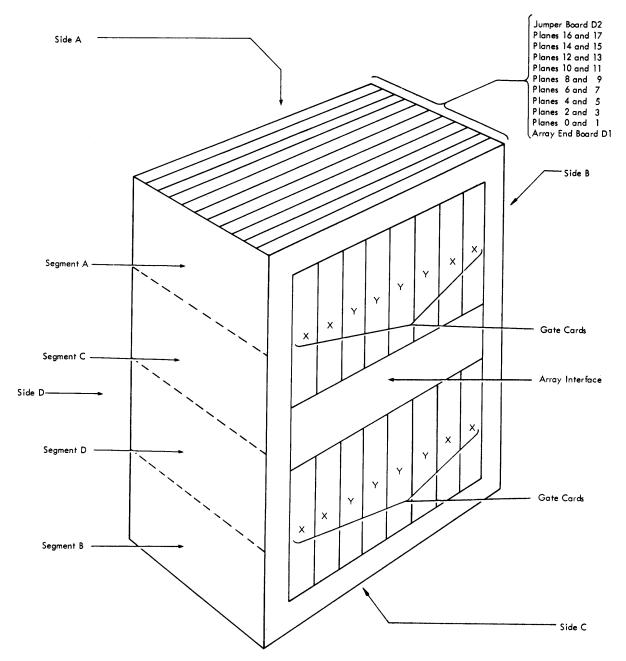

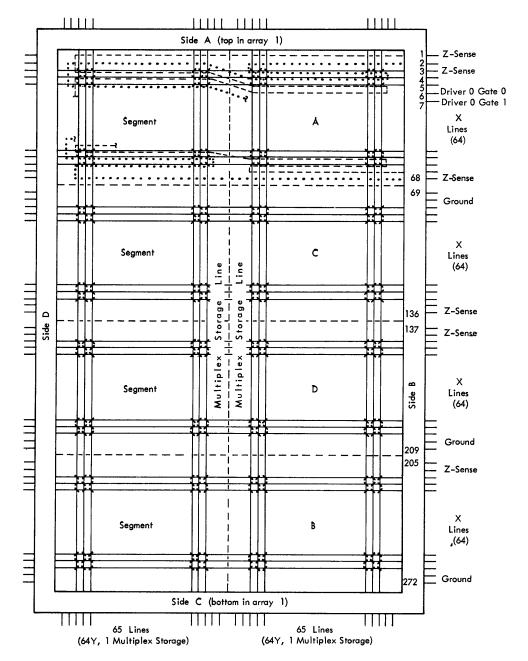

| 104    | Connection of Four Basic Drive Circuits        | 152 | 121    | Array No. 1                                         |

| 105    | Main Storage Unit Drive                        | 153 | 122    | Plane Arrangement (Array 1, Invert for Array 2) 174 |

| 106    | Storage X Dimension Drive                      | 155 | 123    | Sense/Inhibit Wire Routing                          |

| 107    | Main Storage Y Dimension Drive                 |     | 124    | Core Winding Three Wire                             |

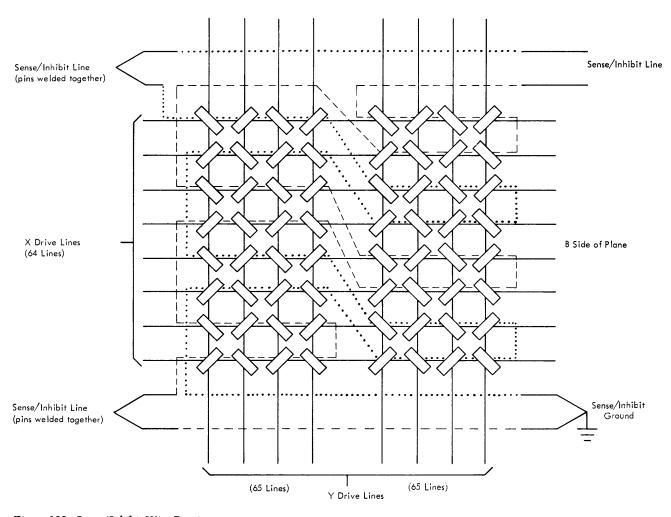

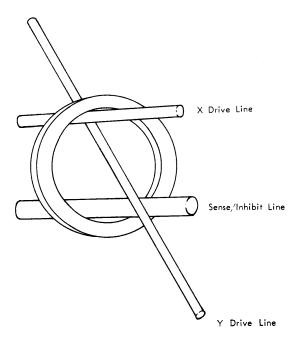

| 108    | Core Wires (Three Wire System)                 |     | 125    | X Line Routing177                                   |

| 109    | Main Storage Sense Amplifier and Inhibit       |     | 126    | Y Line Routing                                      |

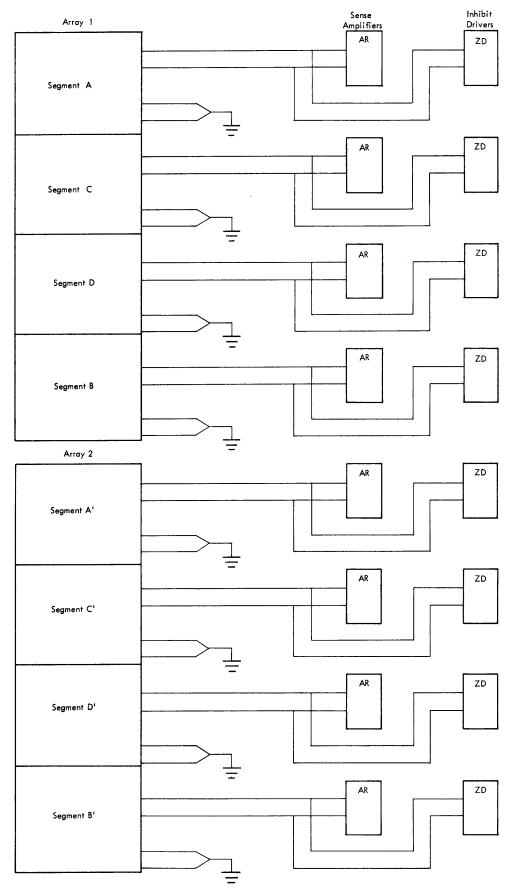

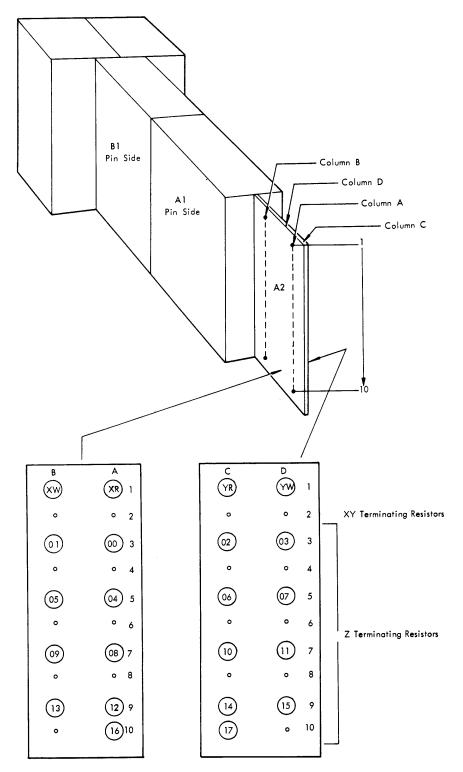

|        | Driver Allocation                              | 158 | 127    | Array End Board D1                                  |

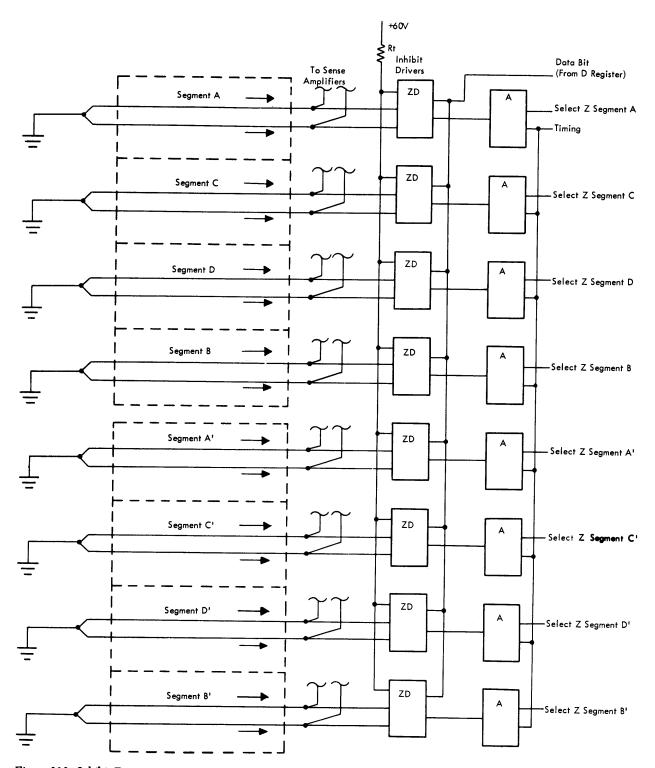

| 110    | Inhibit Drive                                  |     | 128    | Interface Area of Board D1                          |

| 111    | Principle of Inhibit Drive                     |     | 129    | Jumper Board D2                                     |

| 112    | Main Storage Sense                             |     | 130    | Socket Panel C1                                     |

| 113    | Storage Select and Gate Select Pulses          |     | 131    | Board A1                                            |

| 114    | Main Storage Timing Chart                      |     | 132    | Board B1 Layout                                     |

| 115    | Main Storage Addressing Parity                 |     | 133    | Board A2 Layout                                     |

| 116    | 2 riegister zumit, demonstrati mite - mity -   | 168 |        | •                                                   |

| 117    | Storage Address Bit Allocation for Mpx Storage | 169 | Checki | ng                                                  |

| 118    | Multiplex Y Drive                              |     |        | System Operation After Error Detection              |

| 119    | Multiplex Storage Y Dimension                  |     | 134    |                                                     |

| 120    | 64K Halfword Storage Unit                      | 172 | 135    | Checks in Relation to Timing                        |

.

# **Purpose and Function of Clock**

- Provides timed pulses to the system

- Three types of clock pulses are generated: P, T, and gated T

- Separate clock systems for A and B logic gates

The purpose of the clock is to provide timing pulses. Two separate timing systems are generated, one for each logic gate. The A gate system synchronizes the B gate system. The A gate system has two sets of pulses: the continuously running P clock and the T clock. The P clock pulses control main storage and TROS. T clock pulses can be started and stopped by CPU controls.

The B gate system has a T clock, which runs in synchronism with the A gate T clock, and a modified clock called gated T clock, which is used in selector channel operations.

#### A Gate Clock Generation

- Free running oscillator 3.2 mc

- Paraphase amplifier produces clock odd and clock even

- Gate generator

- P and T pulse generator

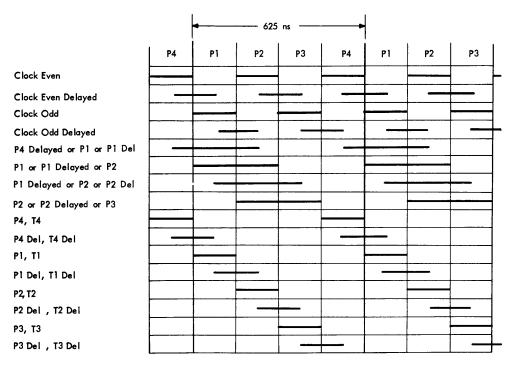

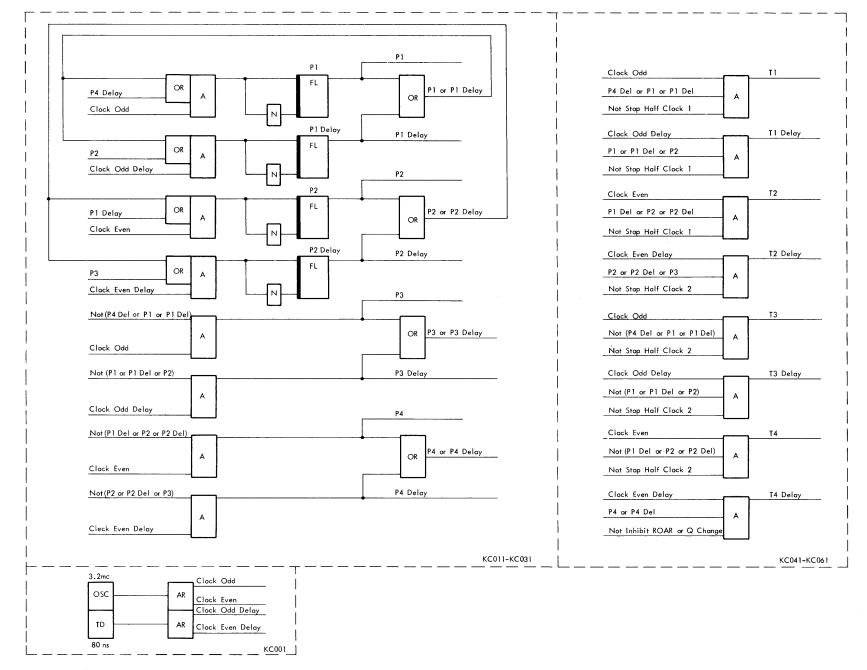

For basic clock pulse timing see Figure 1. A diagram of the clock system is shown in Figure 2. Circuits are on ALD pages KC001 through KC081.

The basic clock time is derived from an oscillator and delay card which produces control pulses at a frequency of 3.2mc (megacycles,  $10^6$  cycles/second) with a tolerance of + or -1 kilocycle ( $10^3$  cycles/second). The delay on the card produces a pulse called delayed clock, which occurs 80 nanoseconds after clock.

The clock pulse is fed into a paraphase amplifier and emitter follower stage which produces the pulses clock odd and clock even. Clock odd and clock even are 180 degrees out of phase.

Figure 1. Basic Clock Pulses

Figure 2. Clock System

The delayed clock pulse is fed into a second identical stage, which produces delayed clock odd and delayed clock even.

The gate generator gates the clock signals in the P pulse and T pulse generators to produce the individual timing pulses (P1, P2, T1, T2, etc.) used throughout the machine.

Gate generator circuits are built with AND and OR circuits gated by the P pulse generator output. All circuits are designed so that the proper pulse sequence is established automatically after power is brought up.

The P pulse and T pulse generators are also combinations of AND and OR circuits, fed by the clock signals and the gates provided by the gate generator. The stop clock, when active, blocks the T clock and controls the T pulse generator.

#### **B** Gate Clock Generation

- Controlled by A gate oscillator

- Paraphase amplifier produces clock odd and clock even

- Gate generator uses latches and is synchronized by the A gate P clock

- T pulse generator and gated T pulse generator

Basic clock pulses and a block diagram are shown in Figures 1 and 2. Circuits are on ALD pages GX501.

The basic timing is derived from the oscillator of the A gate system. As a result of the time delay in the wiring from A to B gate, the B gate timing system is approximately 10 nanoseconds later than the A gate.

A set of paraphase amplifiers identical to the A gate system, produces clock odd and clock even and the corresponding delayed clock signals.

The gate generator consists of two pairs of interconnected latches supplied with the paraphase amplifier outputs. Each of the four latches is set and reset alternately at periods of approximately 310 nanoseconds, equal to two consecutive P pulses. The set times of the latches are spaced at half P pulse intervals and are staggered by half a P pulse, producing identical gates as used in the A gate.

A synchronizing signal, synch B gate clock, is supplied from the A gate to ensure that A gate P1 is coincident with B gate P1.

The gate generator waveforms in conjunction with the clock signals are combined in logic circuits to provide the B gate T clock and gated T clock.

The B gate clocks are stopped and started in parallel with the A gate T clock. The gated T clock is:

- 1. Stopped during logout microprogram to prevent selector channel interference.

- 2. Running during hardware system reset.

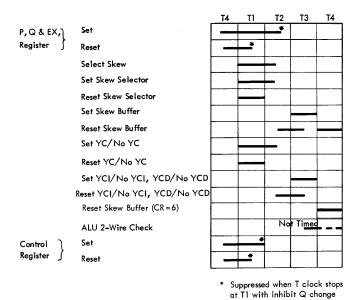

# T Clock Start-Stop

- Clocks always stop after T4 del (delayed)

- The clock for A gate is controlled by stop half clock lines

- B gate clocks controlled by A gate T clock

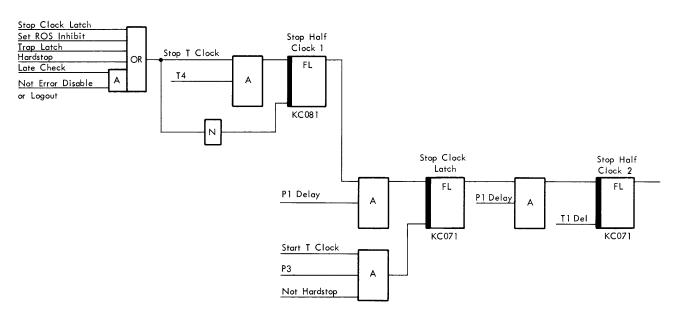

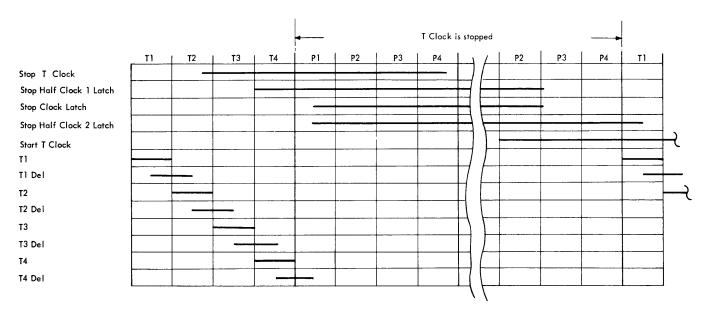

Figure 3 shows the simplified circuits for developing the two signals, stop half clock 1 and stop half clock

Figure 3. Clock Start/Stop Circuit for A Gate

2, which are responsible for blocking the A gate T clock generator.

Stop half clock 1 blocks T1 and T2, stop half clock 2 blocks T2 del to T4. The line labelled stop T clock becomes active for all possible conditions that stop the clock and can come on at any time during the cycle. In practice, only errors detected before T4 del can generate this signal and can stop the clock at the end of the cycle in which they are detected. Example: Local storage read check cannot stop in the same cycle. Similarly the line start T clock is the or condition of all signals that resume T clock operation.

In Figure 4 the last pulse generated after stop T clock is present is T4 del; the first pulse blocked is T1.

To restart the T clock, start T clock resets the stop clock latch and the first timing pulse generated is T1.

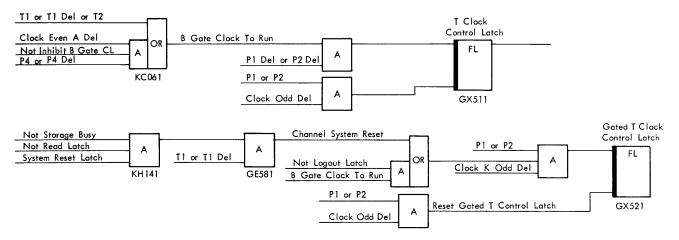

The B gate clocks are directly controlled by the A gate clock. The signal, B gate clock to run, is essentially T1 and T2 of the A gate clock. (Figure 5).

For the B gate T clock, this signal is directly latched to provide gating of the T clock generator. Not logout is needed for gated T clock pulses to be active. Channel system reset, in addition, allows the gated T clock to run.

The gated T pulses and T pulses will be present together, except in the following circumstances:

- 1. No gated T pulses during microprogram logout.

- 2. Gated T pulses during hardware system reset.

Figure 4. T Clock Start/Stop Controls

Figure 5. Start/Stop for B Gate Clocks

- Latch-type circuits which temporarily hold several bits of data or control information are called registers

- Relationship of the various registers is shown on the over-all data flow

- Registers can store information for any number of machine cycles until new information is read in

- A register that is reset in every cycle is also referred to as a data bus

A group of latches which is used temporarily to store data or control information is called a register. If a certain latch of the group is on, the position is considered to contain a "one" bit (1). When the position is reset or off, it contains a "zero" bit (0).

Read-in and read-out of registers is normally under control of the microprogram, but some of the registers have special logic controls incorporated. This section gives the characteristics of every register in the machine.

Registers will normally hold their contents until new information is read into them, which may be after one or any number of machine cycles. Some specific registers, however, are reset at the beginning of every cycle. The purpose of these registers is to buffer information during data transfers (either on the 16-bit or 8-bit data flow) where the source register may be changed during the present cycle, but the old contents may be used for the entire duration of the cycle.

This type of register is often referred to as a data bus. (Examples: R bus, P bus, Q bus.) Figure 6 shows the basic controls and purposes of the registers.

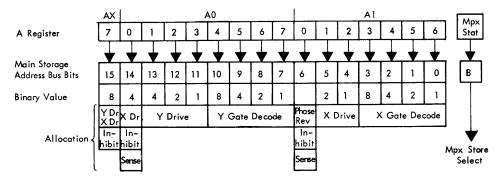

#### A Register

- Two bytes (A0, A1) plus extension (AX) each with parity bit

- Temporary work register

- Main storage address register for CPU operations

- Set from R bus and ALU output

- Output to main storage address bus (sab), R bus, and P bus

- Register is not parity checked, but during CPU operations is always gated to SAB which is checked

Figure 7 shows the A register circuits.

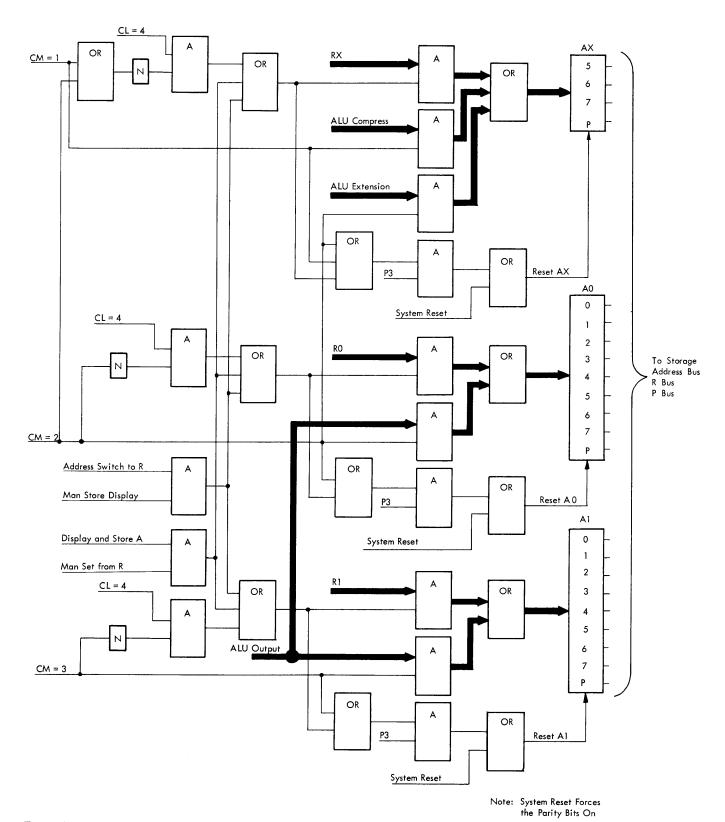

The capacity of the A register is two bytes plus extension, each part having its own parity bit. The A register may be used as a temporary work register, but its main purpose is to address main storage during CPU or multiplexor channel operations.

The A register is read in under microprogram control from either the R bus or the ALU output. Logic circuit controls are included for manual console operations. When the register is read in, the old content of the register is reset (all bit latches turned off).

During system reset all latches are turned off, but a special entry to the parity latches becomes active which insures that system reset forces "good zeros" (all latches off, parity on) into the register.

The output of the A register can be gated to one or more of the following units: storage address bus (sab), R bus, or P bus. When the system is not working as a selector channel the output is gated to the sab.

In accordance with main storage addressing, bit 7 of A1 is not gated to SAB. Connection of A register to SAB also depends on the multiplexor (Mpx) stat, which provides a changed data path for addressing multiplex store.

The A register itself is not parity checked, but parity checking exists on the SAB which is almost continuously fed by the A register. Additionally, the other destinations of A register information are parity checked (R bus, P bus).

The source of A register data can be specified from the R bus and the ALU output in the same microinstruction. In this case, the ALU output should override R bus data.

R bus gating is blocked for the register part which is intended to receive the ALU output:

- 1. Manually loading the A register from the console data switches (which are fed to the R bus) is controlled by the AND switch, display and store A, AND'ed with manual set from R.

- 2. For display and store of main storage, the console address switches are fed to the R bus and gated into A by the switch, address switches to R, AND'ed with manual store-display.

| Register                     | Set                                                      | Reset                                            | Length    | Main function                                                                          | Special controls                                                                                      | ALD's   |

|------------------------------|----------------------------------------------------------|--------------------------------------------------|-----------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|---------|

| A Reg                        | R bus, ALU                                               | On read in                                       | 19 bits   | Main storage addressing                                                                |                                                                                                       | RA001   |

| B Reg                        | R bus, ALU                                               | On read in                                       | 16 bits   | Temporary data storage                                                                 |                                                                                                       | RB001   |

| C Reg                        | R bus, ALU                                               | On read in                                       | 19 bits   | Temporary storage only;<br>source to Mpx data reg                                      |                                                                                                       | RC 001  |

| D Reg                        | R bus, ALU,<br>MS data out                               | On read in                                       | 16 bits   | Temporary storage, MS<br>data register                                                 | Coincidence circuitry<br>controls priority of<br>incoming data: ALU,<br>R bus output, MS<br>read data | RD021   |

| R Reg (Bus)                  | From source<br>specified in<br>CJ field                  | Every mach-<br>ine cycle                         | 19 bits   | Buffer register for two-<br>byte data flow. Data reg-<br>ister for local storage       |                                                                                                       | RR 00 1 |

| ALU Control                  | From ALU<br>function reg-<br>ister or CE or<br>CG fields | Every mach-<br>ine cycle                         | 4 bits    | Determines the ALU function to be performed                                            |                                                                                                       | KP023   |

| ALU Function                 | From CE field if CN = 15                                 | On read in                                       | 5 bits    | Stores ALU function for indirect operations                                            |                                                                                                       | KP001   |

| P Reg (Bus)                  | From source<br>specified in<br>CP field                  | Every mach-<br>ine cycle                         | 8 bits    | ALU entry for one operand                                                              |                                                                                                       | RP001   |

| Q Reg (Bus)                  | From source<br>specified in<br>CQ field                  | Every mach-<br>ine cycle                         | 8 bits    | ALU entry for one operand                                                              |                                                                                                       | RQ001   |

| Extension                    | By microprogram                                          | Every mach-<br>ine cycle                         | 3 bits    | Contains the entry to ALU if<br>a register with an extension is<br>gated to P or Q bus | If both P and Q<br>specify an extension,<br>P blocks Q                                                | REO01   |

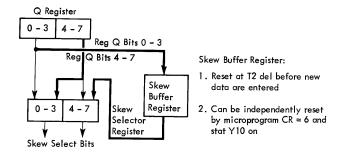

| Skew Select                  | From CK=1                                                | Every mach-<br>ine cycle                         | 8 bits    | Provides a four-bit left shift of the Q bus data                                       | Controlled by ALU function register                                                                   | AQ011   |

| Skew Buffer                  | From CK=1                                                | On read in or micro-<br>program (CR = 6)         | 4 bits    | Holds the skewed data                                                                  | Controlled by ALU function register                                                                   | AQ011   |

| Storage Prot-<br>ect         | Logic or<br>microprogram                                 | Logic or<br>microprogram                         | 4 bits    | Holds the storage key when<br>MS is accessed                                           |                                                                                                       | KU011   |

| Mpx Data                     | Data (C reg)                                             | On read in                                       | 8 bits    | Holds data to bus out                                                                  |                                                                                                       | FA023   |

| Mpx Error                    | Channel conditions                                       | I/O mode,<br>CB=7                                | 6 latches | Set by error conditions in channel, can be displayed                                   |                                                                                                       | FN011   |

| S Reg                        | R bus, ALU                                               | On read in                                       | 19 bits   | Addresses MS during channel operations                                                 |                                                                                                       | HS501   |

| T Reg                        | ALU output                                               | On read in                                       | 16 bits   | Records the number of<br>bytes transmitted by the<br>channel                           |                                                                                                       | HT501   |

| Chan Flags                   | ALU, ROS,<br>logic circuits                              | I/O mode,<br>clear channel                       | 8 bits    | Holds channel control flags                                                            |                                                                                                       | GF501   |

| Chan Checks<br>and Stat Regs | From channel logic circuits                              | Clear SC errors                                  | 8 bits    | Holds channel checks and status bits                                                   |                                                                                                       | GG543   |

| Chan Key                     | Microprogram                                             | On read in                                       | 4 bits    | Holds the protect key during selector channel operations                               |                                                                                                       | GU501   |

| W Regs                       | Interface, ALU,<br>R bus                                 | Every mach-<br>ine cycle                         | 5 bytes   | Data buffer between MS and interface                                                   |                                                                                                       | HW501   |

| ROAR                         | Logic or<br>microprogram                                 | Every mach-<br>ine cycle                         | 12 bits   | Used to address read only storage                                                      |                                                                                                       | RX 00 1 |

| ROSCAR                       | Logic or<br>microprogram                                 | Microprogram                                     | 13 bits   | Used to address read only storage during selector channel operation                    |                                                                                                       | GC501   |

| ROBAR                        | ROSAB                                                    | Every cycle<br>unless inhibit ROBAR<br>is active | 13 bits   | Holds the ROS address used in th<br>previous cycle                                     | е                                                                                                     | RX 201  |

Figure 6. Registers

Figure 7. A Register Circuits

**Registers** 12/65 13

# **B** Register

- Two bytes (BO and BI) each with a parity bit

- B register is microprogram controlled to serve as a work area and temporary storage

- Set from R bus and ALU output

- Output to R bus, P bus, Q bus

- Register is not parity checked

The B register is used as temporary storage for two bytes of data. It is under control of the microprogram when handling data between registers and the ALU, etc.

B register circuits are similar to the circuits shown for the A register (Figure 7).

TROS field values control the gating and the coincidence circuits.

The B register is not parity checked; however, its contents are eventually checked when the data are moved to the R, P, or Q registers.

# **C** Register

- Two bytes (C0 and C1) plus an extension (CX) each with a parity bit

- Temporary work register, can hold an updated A register address

- Set from R bus and ALU output

- Output to R bus and Q bus

- Byte C1 is the source of all output data of the multiplex channel

- Not parity checked

The C register, used as a temporary storage, contains two bytes (co and c1) and an extension (cx). All parts have separate parity bits, although the register is not parity checked. Invalid parity is eventually detected when the C register data are moved to either the R or Q registers.

C register circuits are similar to those shown for the A register. The extension cx is provided for more efficient access to main storage. During a main storage cycle, the A register may not be changed. This would mean that address updating could be done only after the MS cycle. With CX available, updating is done during the MS cycle, and the modified address is stored in C.

Byte C1 is the only source which is fed to the multiplex data register. All output information of the multiplexor channel, therefore, has to be transferred to C1.

# **D** Register

- Two bytes (DO, D1) each with parity bit

- Temporary work register

- ms data register

- Set from R bus, ALU output or Ms output (sense)

- Output to R bus, O bus, or Ms entry (inhibit)

- Parity checked

- For output to MS, good parity is always generated

- D register is directly displayed on the console

- D register assigns priority to system data flow

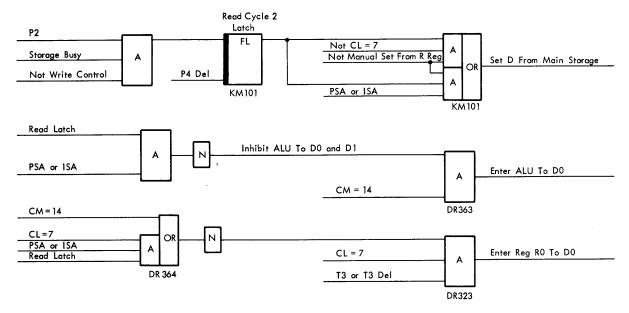

The D register can be used as temporary storage for two bytes of data, but its principal function is to act as the main storage data register.

During the second machine cycle of a main storage read operation, the Ms sense amplifier output is gated by logic circuits to the D register. Entry of R bus and ALU is under microprogram control.

Circuitry is provided which assigns highest priority to the ALU output, second highest priority to R bus output and lowest priority to main storage read data.

Main storage read data are completely lost if the microinstruction following a Ms read call specifies R bus to D register.

No provisions are made to override one byte of main storage data by an ALU output. Specification of ALU output to D in the second read cycle of main storage is an invalid microprogram statement.

In case a Ms read call is given for an invalid storage address, or if the storage protection is violated, R and ALU entries to the D register are blocked to ensure that storage data are not destroyed. (Figure 8 shows the entry gates for DO).

The D register output to the main storage inhibit drivers is always in good parity, i.e. the parity bits to main storage are generated according to the contents of bits 0-7. The D register parity bits are not used in this circuit.

The D register is parity checked, incorrect parity sets the early check latch.

Figure 8. D Register Set (Only D0 Shown)

#### R Register (R Bus)

- Two bytes (R0, R1) plus extension (RX) each with parity bit

- Buffer register for the two-byte data flow (R bus);

special purpose: data register for local storage and buffer register for display

- Set by microprogram from the sources specified in the cj field. Set by logic circuits during logout, manual store-display and dump from various other sources

- Output to destinations specified in the CL field and by logic circuits

- Parity checked

The capacity of the R register is two bytes plus extension, each part having its own parity bit. The R register is reset in every machine cycle and is therefore also referred to as R bus.

The main purpose of this register is to provide a buffer for data transfer between various parts of the system. Special purposes of the R register are:

- 1. Data register for local storage

- 2. Display buffer for the console lights associated with the roller switches.

During microprogram cycles the R bus is fed from the various sources specified in the cJ field; during hardware cycles or manual store-display operations various other sources are gated to the R bus.

Example: During logout or display the P and Q bus can be gated directly to R. R bus entries for machine check conditions are also provided.

Figure 9 shows the various possibilities for R bus entries and the corresponding gates responsible. The main timings for reset and set are also indicated. The figure may be used as a starting point before entering the ALD's.

The output of the R bus is again distributed throughout the machine during microprogram cycles to the destinations specified in the CL field.

In the undump hardware cycle R is gated to ROAR. During hardware logout R is stored in local storage.

In manual store-display operations, R is gated by logic circuits to various parts of the system. Hardstop display with the upper roller switch in positions other than 1 (R bus display) gates the R bus to two sets of

15

| MICROPROGRAM | CONTROLLED | ENTRY | то | R BUS |

|--------------|------------|-------|----|-------|

|              |            |       |    |       |

|               |                                                   | ,    |                                             |                                             |                                             | Y10 C                                       |                                            | iickoi k                                                  | OGRAM CON                                                              | IKOLLEL          |                                                                    |                                         |                                         |                                             |                                             |                                        |                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                        |                                                                                                      |                                                                                                               |                                                                |

|---------------|---------------------------------------------------|------|---------------------------------------------|---------------------------------------------|---------------------------------------------|---------------------------------------------|--------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------------------|------------------|--------------------------------------------------------------------|-----------------------------------------|-----------------------------------------|---------------------------------------------|---------------------------------------------|----------------------------------------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| CJ =<br>Symbo | CJ = 0 1 2 3 4 5 6 7 88 9 10 11 12 13 1 2 3 4 5 5 |      |                                             |                                             |                                             |                                             |                                            |                                                           | CIC<br>or Log Out)                                                     | 6<br>LSTOR       |                                                                    |                                         |                                         |                                             |                                             |                                        |                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                        |                                                                                                      |                                                                                                               |                                                                |

| Gate          |                                                   | None | A Reg to R Reg                              | B Reg to R Reg                              | C Reg to R Reg                              | D Reg to R Reg                              | H Reg to RO Reg<br>J Reg to RO Reg         | None                                                      | Enter Data and<br>Checks to Channel<br>Bus Mpx                         | Clock Timer to R | Channel Flags<br>Boundary Flags to R                               | Enter S Reg to R Bus                    | Enter T Reg to R Bus                    | W0 to R0 and<br>W1 to R1                    | W2 and Channel<br>Protect Key to R          | Enter W34 to R Bus                     | Man Addr Switches<br>to R Register | IPL Unit Address<br>and Store Select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Man Data Switches<br>to R Register     | Enter IF Controls to R                                                                               | Channel Status<br>and Checks to R<br>(SC only)                                                                | one<br>Z                                                       |

|               |                                                   |      |                                             |                                             |                                             |                                             | <u> </u>                                   |                                                           |                                                                        |                  | Cho                                                                | annel F                                 | R Bus                                   |                                             |                                             |                                        |                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                        | Chan                                                                                                 | nel R Bus                                                                                                     |                                                                |

| RX            | P<br>5<br>6<br>7                                  |      | AXP<br>5<br>6<br>7                          | PG                                          | CXP<br>5<br>6<br>7                          | PG                                          | PG                                         | 1<br>2<br>3<br>4                                          | PG                                                                     | PG               | PG                                                                 | SXP<br>5<br>6<br>7                      | PG                                      | PG                                          | PG                                          | PG                                     | (P)<br>6<br>7                      | PG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | (P)<br>6<br>7                          | PG                                                                                                   | PG                                                                                                            | 1<br>2<br>3                                                    |

| RO            | P<br>0<br>1<br>2<br>3<br>4<br>5<br>6              | PG   | AOP<br>0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | BOP<br>0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | COP<br>0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | DOP<br>0<br>1<br>2<br>3<br>4<br>5<br>6      | HP<br>0<br>1<br>2<br>3<br>4<br>5<br>6      | 21 Data Out Bit 6 2 8 8 9 9 9 9 9 9 9 9 9 9 9 9 9 9 9 9 9 | PG IF Parity Ck IF Tag Ck  Mpx I/O Mc Ch Data Ck Ch Ctrl Ck IF Ctrl Ck | PG<br>ode        | Channel Flags CHAO CHAO CHAO CHAO CHAO CHAO CHAO CHAO              | SOP<br>0<br>1<br>2<br>3<br>4<br>5<br>6  | TOP<br>0<br>1<br>2<br>3<br>4<br>5<br>6  | WOP<br>0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | W2P<br>0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | W3P<br>0<br>1<br>2<br>3<br>4<br>5<br>6 | Iress Switches                     | ) (P) (S lost Sel 2 lo | Binary Data Switches                   | Sel & Hold Out<br>Sel In<br>Addr Out<br>Addr In<br>Com Out<br>Status In<br>Service Out<br>Service In | P PCI WLR Programmer State Ck STATE PROGRAMMER STATE CH Ch Ch Ch Ch Ck PC Ch Chain Ck Ch Chain Ck             | Data Out B 8 9 10 11 12 13 13 13 13 13 13 13 13 13 13 13 13 13 |

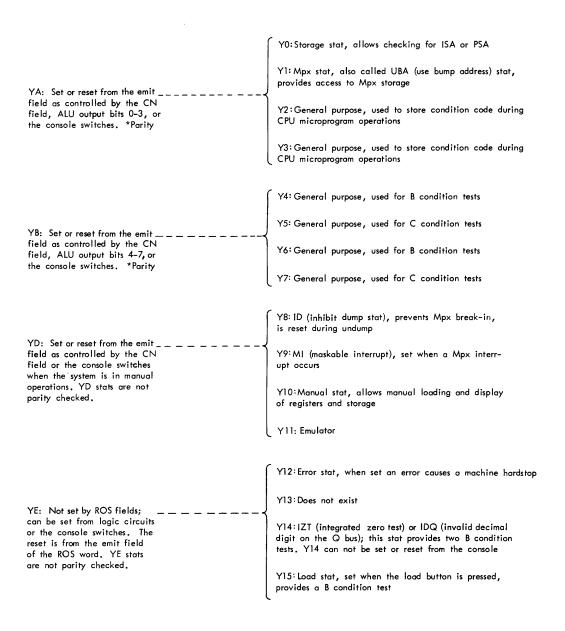

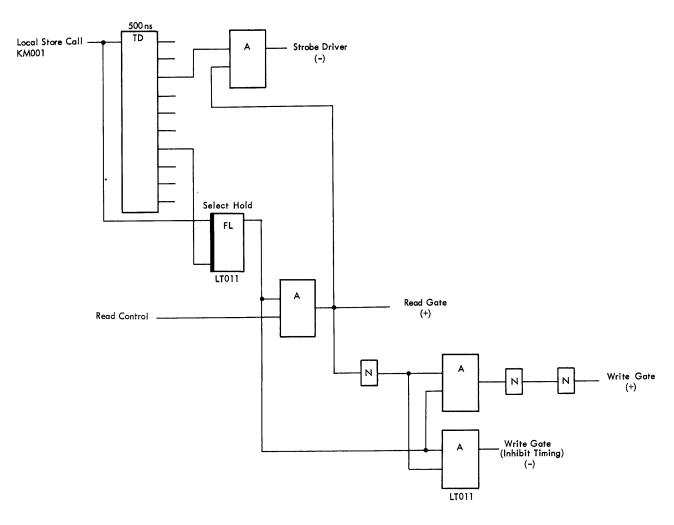

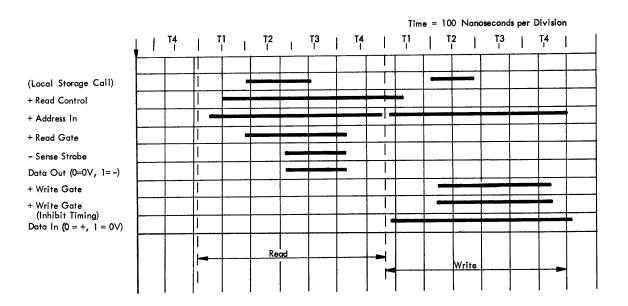

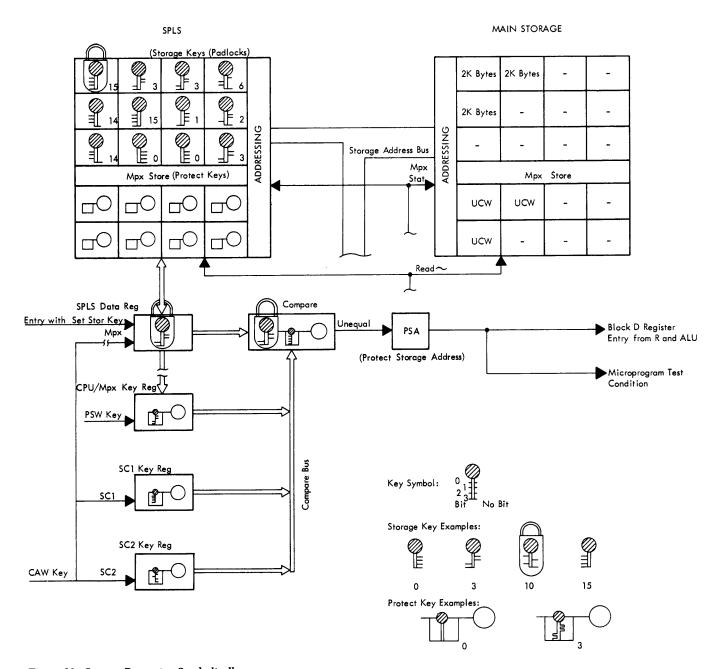

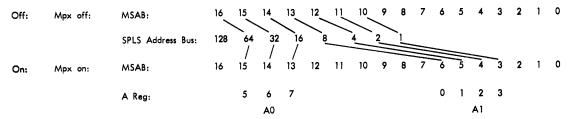

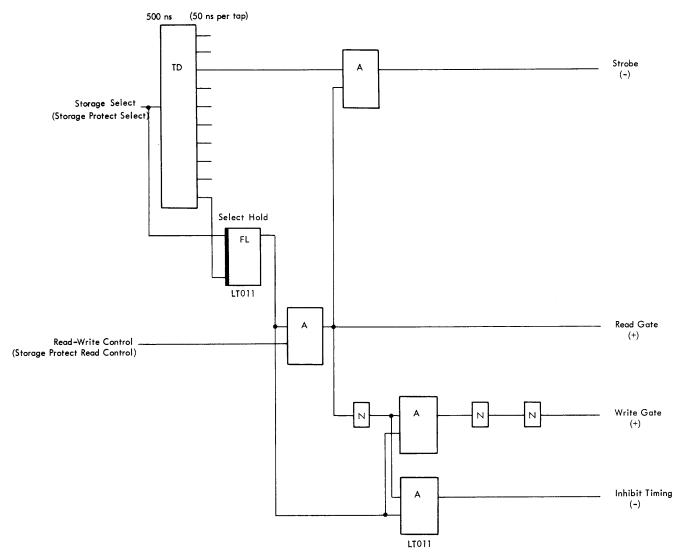

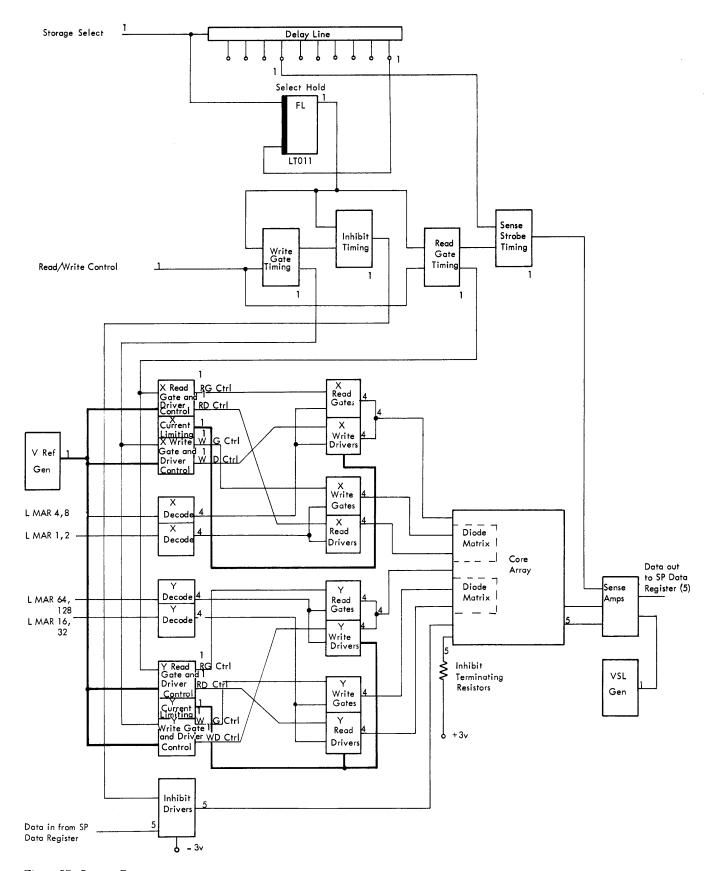

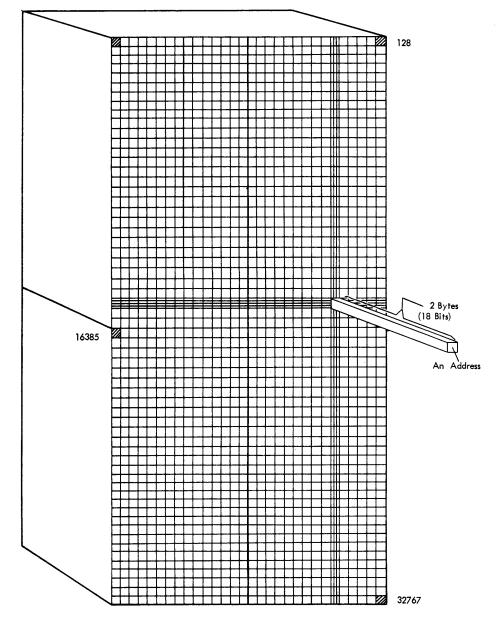

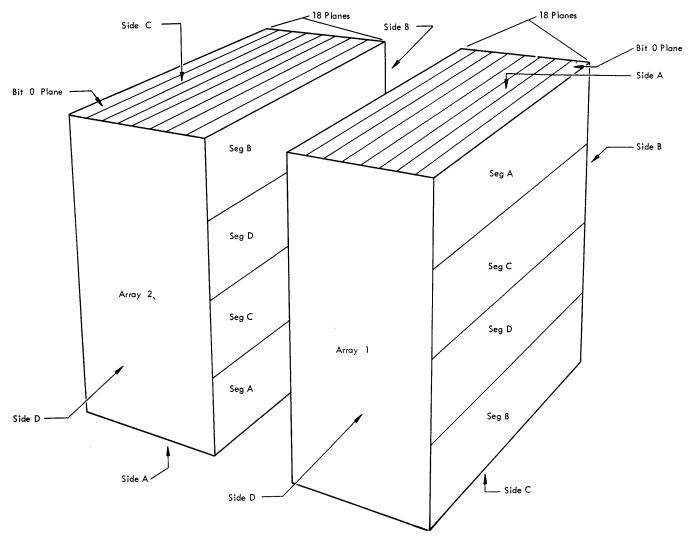

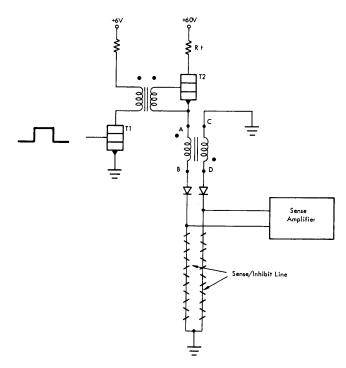

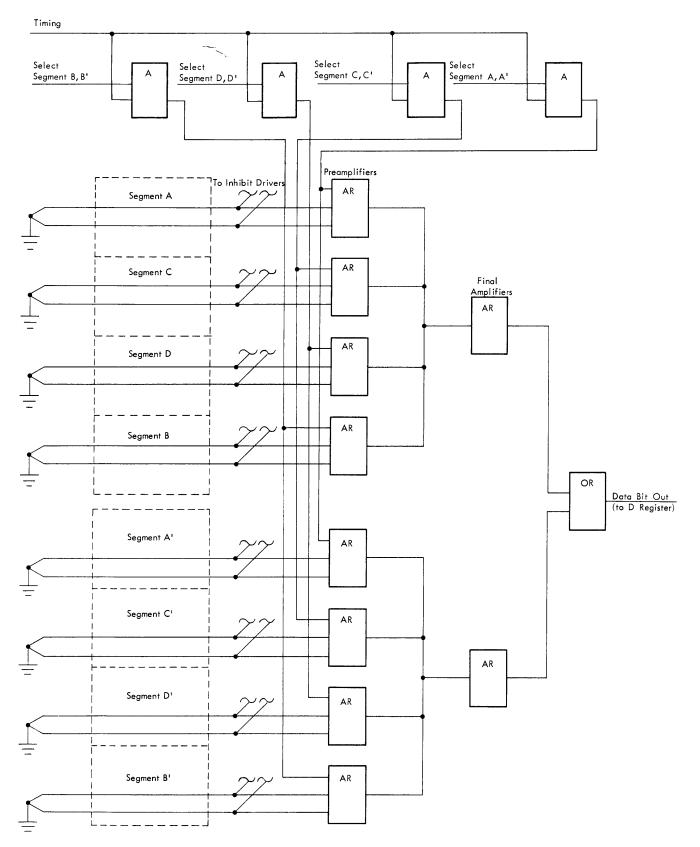

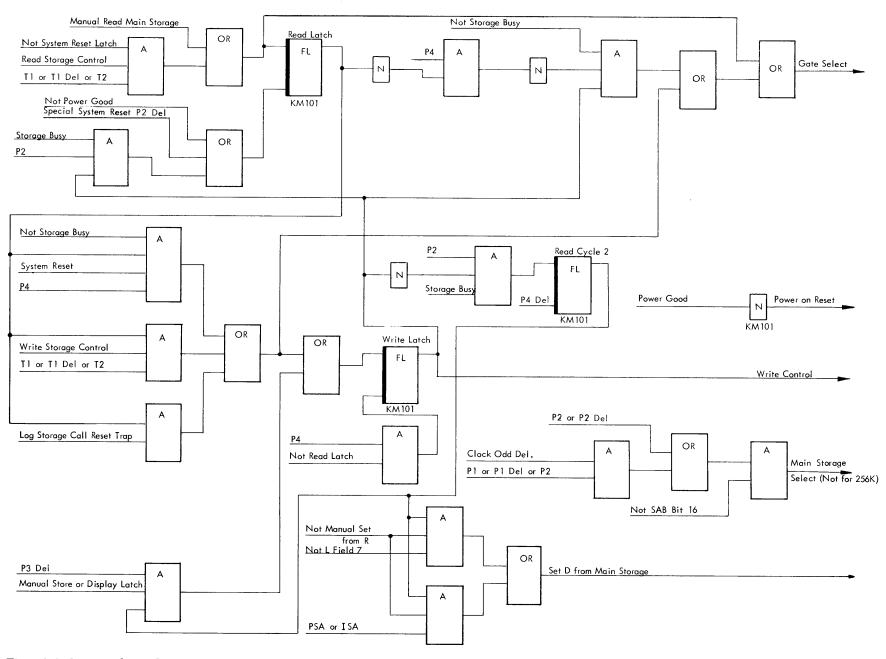

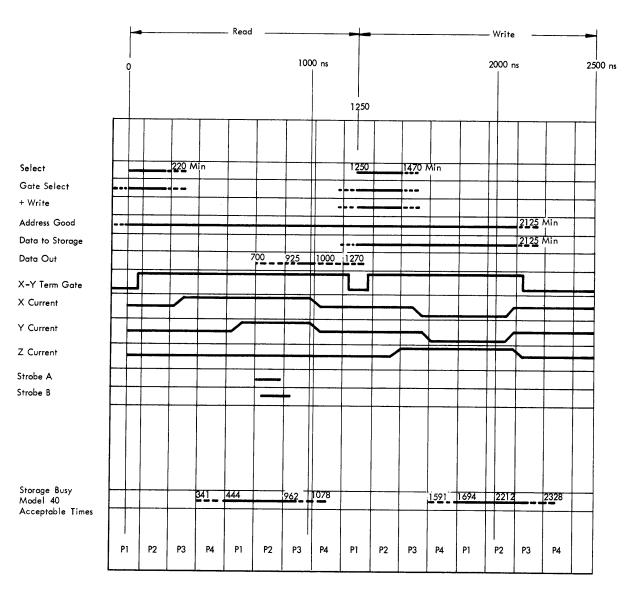

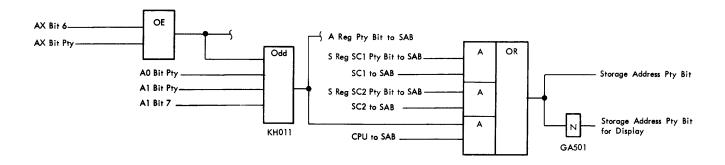

| R1            | P 0 1 2 3 4 5 6 7                                 | PG   | A1P<br>0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | B1P<br>0<br>1<br>2<br>3<br>4<br>5<br>6      | C1P<br>0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | D1P<br>0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | JP<br>0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | 14<br>15<br>16<br>17<br>18<br>19<br>20<br>21<br>22        | Note 2 PG<br>0<br>                                                     | PG 1 2 3         | W0 Flog W1 Flog W2 Flog W3 Flog W4 Flog Count=0 Count=1 Bytes in W | S1 P<br>0<br>1<br>2<br>3<br>4<br>5<br>6 | T1 P<br>0<br>1<br>2<br>3<br>4<br>5<br>6 | WI P 0 1 2 3 4 5 6 7                        | Ch Key P  Ch Key 0 1 2 3                    | W4P<br>0<br>1<br>2<br>3<br>4<br>5<br>6 | (P)                                | 2 2 Load Unit Switches 2 4 2 6 2 1 0 3 4 2 6 2 1 0 2 9 2 4 2 9 2 9 2 9 2 9 2 9 2 9 2 9 2 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | (P)<br>0<br>1<br>2<br>3<br>4<br>5<br>6 | Op Out Op In Sup Out Req In Select Inh Sel Out Unit Unobt Halt I-O                                   | Ript for ALU<br>Ch Sel Late<br>TO Pry Ck<br>T1 Pry Ck<br>W0 Pry Ck<br>Bus In Ck<br>Ch Flag Ck<br>Multi Tag Ck | 14<br>15<br>16<br>17<br>18<br>19<br>20<br>21                   |