# Field Engineering Theory of Operation (Manual of Instruction)

Restricted Distribution

This manual is intended for internal use only and may not be used by other than IBM personnel without IBM's written permission.

Specifications contained herein are subject to change without notice. Revisions and/or supplements to this publication will be issued periodically.

**Restricted Distribution**

This manual is intended for internal use only and may not be used by other than IBM personnel without IBM's written permission.

Specifications contained herein are subject to change without notice. Revisions and/or supplements to this publication will be issued periodically.

# PREFACE

This manual provides detailed descriptions of the functions and operations of the IBM 2415 Models 1-3 Tape Control, in addition to a general introduction to magnetic tape devices and tape control units. A theory of operation manual is intended primarily for instruction and as a classroom aid, not to provide maintenance and troubleshooting information. Complete servicing information is contained in the maintenance manual.

All figures in Chapters 2 and 3 are released as systems reference pages and are in the maintenance diagram volume shipped with each system. I/Ooperation (IOP) diagrams, referred to in Chapter 3, are contained in the diagram manual. Some figures in Chapter 4 are also released as systems reference pages. Refer to the preface of the diagram manual for a complete explanation of the type of diagrams available and how each group is released for the 2415 tape system.

It is assumed that the reader of this manual is familiar with the following texts, or has had equivalent experience: Basic Computer System Principles -- Course Code 41077

Oscilloscope Operations -- Course Code 43014

SMS Component Circuits and Logic -- 1440 Preschool Part 3, Form R25-4967

System/360 I/O Interface -- Course Code 43140 Manuals that contain information relating directly to 2415 operations are:

- Field Engineering Theory of Operation, <u>IBM 2415</u> <u>Models 1-6 Magnetic Tape Unit</u>, Form <u>Y22-2915</u>

- Field Engineering Maintenance Manual, <u>IBM 2415</u> <u>Models 1-6 Magnetic Tape Unit and Control</u>, Form Y22-2916

- Field Engineering Diagram Manual, <u>IBM 2415</u> <u>Models 1-6 Magnetic Tape Unit and Control</u>, Form Y22-2917

Recent changes in terminology should be noted. The terms "block" and "interblock gap" (IBG) used in this manual are synonymous with the terms "record" and "inter-record gap" (IRG).

#### First Edition

This publication, Form Y22-2918-0, obsoletes Form Z22-2918-0. Major technical changes have been made in this publication, and it should be reviewed in its entirety.

Significant changes and additions to the specifications contained in this publication will be reported in subsequent revisions or FE Supplements.

This manual has been prepared by the IBM Systems Development Division, Product Publications, Dept. B95, PO Box 390, Poughkeepsie, N.Y. 12602. A form is provided at the back of this publication for the reader's comments. If the form has been removed, comments may be sent to the above address.

© International Business Machines Corporation 1966

# CONTENTS

| CHAPTER 1. INTRODUCTION                                                                                                     | • | • | • | • | 1-1        |

|-----------------------------------------------------------------------------------------------------------------------------|---|---|---|---|------------|

| Input/Output Devices                                                                                                        | • | • |   |   | 1-1        |

| Magnetic Tape                                                                                                               | • | • |   |   | 1-1        |

| Magnetic Tape Device                                                                                                        | • |   |   |   | 1-1        |

| Control Unit                                                                                                                | • | • |   |   | 1-2        |

| $Channel \cdot \cdot$ | • |   |   |   | 1-2        |

|                                                                                                                             |   |   |   |   | 1-3        |

| Bit                                                                                                                         |   |   |   |   | 1-3        |

| Byte                                                                                                                        |   |   |   |   | 1-3        |

| Character                                                                                                                   |   | • |   |   | 1-3        |

| Parity Bit                                                                                                                  |   | · |   |   | 1-3        |

| Block                                                                                                                       |   |   |   |   | 1-3<br>1-4 |

| Interblock Gaps (IBG)                                                                                                       | • | · |   |   | 1-4        |

| File                                                                                                                        |   | · | • |   | 1-4        |

|                                                                                                                             |   |   |   |   | 1-4        |

|                                                                                                                             |   | • |   |   | 1-5        |

| Check Character Parity                                                                                                      |   | • |   |   | 1-7        |

| Control Unit Priority                                                                                                       |   | : |   |   | 1-7        |

| 2415 Models 1, 2, and 3 Tape Control                                                                                        |   |   |   |   | 1-7        |

| NRZI System of Recording                                                                                                    |   |   |   |   | 1-9        |

| Command Operations.                                                                                                         |   |   |   |   | 1-10       |

| Initial Selection                                                                                                           |   |   |   |   | 1-10       |

| Begin Operation or Stack Status                                                                                             |   |   |   |   | 1-11       |

| Test I/O Operation                                                                                                          |   |   |   | Ż | 1-12       |

| Short or Long Busy.                                                                                                         | • |   |   |   | 1-12       |

| Sense Operation                                                                                                             |   |   |   |   | 1-13       |

| Tape Motion Control Commands                                                                                                |   |   |   |   | 1-15       |

| Write Operation                                                                                                             |   |   |   |   | 1-16       |

| Read Operation                                                                                                              |   |   |   |   | 1-17       |

| Read Backward Operation                                                                                                     | • |   |   |   | 1-17       |

| End Status Burst Mode                                                                                                       |   |   |   |   | 1-17       |

| End Status Request In Interrupt                                                                                             |   |   |   |   | 1-18       |

| Status Bits                                                                                                                 |   | • |   |   | 1-18       |

| Turnaround                                                                                                                  |   |   |   |   | 1-19       |

| Error Checking                                                                                                              |   |   |   |   | 1-19       |

| CE Panel                                                                                                                    | • | • |   |   | 1-21       |

| Power Supply                                                                                                                |   | • |   |   | 1-21       |

| Metering                                                                                                                    | • | • |   |   | 1-21       |

|                                                                                                                             |   |   |   |   |            |

| CHAPTER 2. FUNCTIONAL UNITS                                                                                                 |   |   |   |   |            |

| Metering and On-Line Gating                                                                                                 |   |   |   |   | 2-1        |

| Metering Interface Lines                                                                                                    |   |   |   |   |            |

| On-Line Latch                                                                                                               | • | • | • |   |            |

| Select Signal Switching and Gating                                                                                          | • | • | • |   | 2-1        |

| Select Reed Relay (RR1)                                                                                                     | • | • | • |   | 2-2        |

| Select Out Circuits                                                                                                         | • | • | · |   | 2-2        |

| Addressing                                                                                                                  | • | • | • |   | 2-2        |

| Address Decoder                                                                                                             | • | • | • | - | 2-2        |

| Address Generator                                                                                                           | • | • | • |   | 2-3        |

| Tape Unit Decoding and Unit Free Gating                                                                                     | • | · | • |   | 2-3        |

| TU Address Compare                                                                                                          | · | • | • |   | 2-4        |

| Device Register and Device End Scanner                                                                                      | • | • | • |   | 2-4        |

| Device (TU Address) Register                                                                                                | • | • | • |   | 2-5        |

| Device End (Unit Free) Scanner                                                                                              | • | • | • |   | 2-5        |

| Stop Scan                                                                                                                   | · | · | • |   | 2-5<br>2-6 |

|                                                                                                                             | • | • | • |   | 2-0<br>2-6 |

|                                                                                                                             | • | • | • |   | 2-0<br>2-6 |

|                                                                                                                             | • | • | • |   | 2-0        |

| Selective Reset                                                                                                             |   |   | : |   | 2-7        |

| Later , e and otop Later)                                                                                                   | • | • | • | • |            |

| Resets (Tape Control)                             | •    | •    | •   | •  | • | • |   |   |     | • | 2-7  |

|---------------------------------------------------|------|------|-----|----|---|---|---|---|-----|---|------|

| Machine Reset                                     | •    | •    | •   | •  | • | • | • | • | •   | • | 2-7  |

| Sense Reset                                       | •    | •    | •   | •  | • | • | • | • | •   | • | 2-8  |

| Status Reset and Reset Arm.                       |      |      |     |    |   |   |   |   |     |   | 2-8  |

| Early Reset                                       |      |      |     |    |   |   |   |   |     |   | 2-9  |

| Idle Reset, and Green and Go                      | •    | •    | •   | •  | • | • | • |   |     |   |      |

| TAU Reset                                         | •    | •    | •   | •  | • | • | • | • | •   | • | 2-9  |

| Force Burst Mode (FBM) and O                      | pera | atio | nal | In | • | • | • | • | •   | • | 2-10 |

| Command Register, Decoding, and                   | nd ( | Gat  | ing | •  | • | • | • | • | • , | • | 2-11 |

| Command Busy Latch                                | •    | •    | •   | •  | • | • | • | • | •   | • | 2-11 |

| Command Gate Latch                                | •    | •    | •   | •  | • | • |   | • | •   | • | 2-11 |

| Data Register (DR)                                | •    | •    | •   | •  | • | • | • | • | •   | • | 2-12 |

| Data Register Parity Circuits                     |      | •    | •   |    | • |   | • | • | •   |   | 2-12 |

| Data Register Inputs Outbound                     |      | •    | •   |    | • | • |   | • |     | • | 2-13 |

| Data Register Inputs Inbound                      |      |      |     |    |   |   |   |   |     |   | 2-13 |

| Data Register Outputs                             |      | •    |     |    |   |   |   |   |     |   | 2-14 |

|                                                   |      |      |     |    |   |   |   |   |     |   | 2-14 |

| Status Latches                                    |      |      |     |    |   |   |   |   |     |   | 2-14 |

| Status Bytes                                      |      |      |     |    |   |   |   |   |     |   |      |

| Status Latch Inputs                               |      |      |     |    |   |   |   |   |     |   | 2-15 |

| Delay Counter, Write Clock, and                   |      |      |     |    |   |   |   |   |     |   |      |

| Microsecond Mode                                  |      |      |     |    |   |   |   |   |     |   | 2-15 |

|                                                   |      |      |     | •  |   |   |   |   |     |   | 2-16 |

| Sense Counter                                     |      |      |     |    |   |   |   |   |     |   | 2-16 |

| Counter Oscillators                               |      |      |     |    |   |   |   |   |     |   | 2-16 |

| Write Triggers and Deskewing .                    |      |      |     |    |   |   |   |   |     |   |      |

| Writing a Bit on Tape (NRZI)                      |      |      |     |    |   |   |   |   |     |   | 2-16 |

| Deskewing Delay Counter .                         |      |      |     |    |   |   |   |   |     |   | 2-17 |

| Writing Check Characters .                        |      |      |     |    |   |   |   |   |     |   |      |

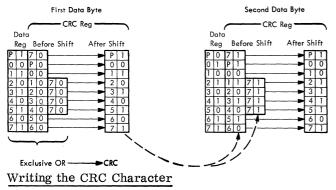

| Cyclic Redundancy Check Regist                    |      |      |     | :  |   |   |   |   |     |   | 2-17 |

| CRC Character Generation .                        |      |      |     | •  |   |   |   | • | •   | • | 2-17 |

| Writing the CRC Character .                       |      |      |     |    |   |   |   |   |     |   |      |

| Read Clock and Drive                              |      | :    |     |    |   |   |   | • | •   | • | 2-18 |

| First Bit Latch                                   |      |      |     | •  |   |   | • |   |     |   | 2-19 |

|                                                   |      |      |     |    |   |   | • | • | •   | • | 2-19 |

| Read Register                                     |      |      |     | •  |   |   |   | • | •   | • | 2-19 |

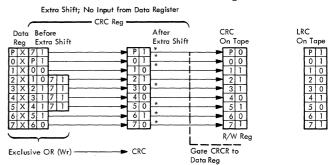

| Register Outputs<br>Longitudinal Redundancy Check |      |      |     |    |   |   |   | • | •   | • | 2 10 |

|                                                   |      |      |     |    |   |   |   |   |     |   |      |

| Write LRCC                                        |      |      |     |    |   |   |   |   |     |   |      |

| Read LRCC                                         |      |      |     |    |   |   | • | • | •   | • | 2-20 |

| Tape Mark Recognition                             |      |      |     |    |   |   |   |   |     |   | 2-20 |

| Seven-or Nine-Track Forward                       |      |      |     |    |   |   |   |   |     |   |      |

| Nine-Track Backward                               | •    | ·    | ·   | ·  | • | • | • | • | •   | • | 2-21 |

| Seven-Track Backward                              |      |      |     |    |   |   |   |   |     |   |      |

| Error Detection                                   | -    | •    | •   | •  | • | • | • | • |     |   |      |

| Data or Equipment Check .                         | •    | •    | •   | •  | • | • | • | • |     |   | 2-22 |

| Read Parity Check                                 | •    |      | •   | •  | • | · | • | • |     |   | 2-22 |

| Write Parity Check                                | •    | •    | •   | •  | • | ٠ |   | • |     |   | 2-22 |

| Command Reject                                    |      | •    | •   | •  | • | • | • | ٠ | •   |   | 2-23 |

| Bus Out Check                                     | •    | •    | •   | •  | • | • | • | • | •   |   | 2-23 |

| Skew Error                                        | •    | •    | •   | •  | • | • | • | • |     |   | 2-23 |

| Word Count 0                                      | •    | •    | •   | •  | • | • | • | • | •   | • | 2-23 |

| Counter Check                                     |      | •    | •   | •  | • | • | • | • |     |   | 2-23 |

| Interblock Gap Noise                              |      | •    | •   | •  | • | • | • | • |     |   | 2-24 |

| Ready Drop                                        |      | •    | •   | •  | • | • | • | • |     |   | 2-24 |

| Overrun                                           |      | •    | •   | •  | • | • | • | • | •   |   | 2-24 |

| Data Register VRC                                 | •    | •    | •   | •  | • | • | • | • | •   |   | 2-24 |

| Read Register VRC                                 |      |      | •   |    | • |   |   | • |     |   | 2-24 |

| Longitudinal Redundancy Che                       |      |      |     |    |   |   |   |   |     |   |      |

| C-Compare Error                                   |      |      |     |    |   |   |   |   |     |   |      |

|                                                   |      |      |     |    |   |   |   |   |     |   |      |

| CHAPTER 3. PRINCIPLES OF OPE     |         |      |   |     |   |   |   |   |              |

|----------------------------------|---------|------|---|-----|---|---|---|---|--------------|

| Initial Selection Sequence       |         | •••  | • | •   | • | • | • | • | 3-1          |

| Channel Addresses Tape Control   | 1.      |      |   | •   | • | • | • | • | 3-1          |

| Address Selection                |         |      |   |     | • |   | • | • | 3-2          |

| Command Set                      |         |      |   |     |   |   |   |   |              |

| Initial Status Byte              |         |      |   |     |   |   |   |   | 3-3          |

| Begin Operation or Stack Status  |         |      |   | •   |   |   |   |   | 3-3          |

| Initial Status Bits and TAU Rese |         |      |   |     |   |   |   |   | 3-4          |

| Sense Operation                  |         |      |   |     |   |   |   |   | 3-5          |

|                                  |         |      |   |     |   |   |   |   | 3-5          |

|                                  |         |      |   |     |   |   |   |   | 3-6          |

| Time Read Delay                  |         |      |   |     |   |   |   |   |              |

| Read Data Block                  |         | •••  |   |     |   |   |   |   | 3-6          |

| Stop Read                        |         |      |   |     |   |   |   |   |              |

| Read Tape Mark                   |         |      |   |     |   |   |   |   | 3-6          |

| End of Block (EOB) Search        |         |      |   |     |   |   |   |   | 3-6          |

| Read Backward Operation          |         |      |   |     |   |   |   |   | 3-7          |

| -                                |         |      |   |     |   |   |   |   | 3 <b>-</b> 7 |

| Start Tape Motion                |         |      |   |     |   |   |   |   |              |

|                                  |         | •••  |   |     |   |   |   |   | 3-7          |

| Read Check Characters and/or     | 1 ape   | Mark | • | •   |   |   |   |   |              |

| Backward at Load Point           |         |      |   |     |   |   |   |   | 3-7          |

| Read Data Block                  |         |      |   |     |   |   |   |   | 3-8          |

| Stop Read                        |         | •••  |   |     |   | • |   |   | 3-8          |

| EOB Search                       |         |      |   |     | • | • | • | • | 3-8          |

| Space or Space File Operations.  |         |      |   |     |   |   |   |   | 3-8          |

| Forward Space or Space File      |         |      |   |     |   |   |   |   | 3-9          |

| End Forward Space                | ••      | • •  | • | •   |   | • |   |   | 3-9          |

| End Forward Space File           |         |      |   |     | • | • |   |   | 3-9          |

| Backspace or Backspace File      |         |      |   |     |   | • |   |   | 3-10         |

| End Backspace                    |         |      |   | •   | • | • | • |   | 3-10         |

| End Backspace File               |         |      | • | •   | • | • |   |   |              |

| Write Operation                  |         |      | • | • . | • |   | • | • | 3-11         |

| Start Tape Motion                |         |      |   |     |   |   |   | • | 3-11         |

| Time Write Delay Request l       | First D | ata. | • |     | • |   |   |   | 3-11         |

| Write Data Block                 |         |      |   |     |   |   |   |   |              |

| Stop Write                       |         |      |   |     |   |   |   |   | 3-11         |

| End of Block (EOB) Search .      |         |      |   |     |   |   |   |   | 3-12         |

| Write Tape Mark or Erase Gap.    |         |      |   |     |   |   |   |   | 3-12         |

| Begin Tape Motion and Time L     |         |      |   |     |   |   |   |   | 3-12         |

| End Erase Gap                    |         |      |   |     |   |   |   |   | 3-12         |

| Write the Tape Mark              |         |      |   |     |   |   |   |   | 3-12         |

|                                  |         | •••  |   |     |   | : |   |   | 3-13         |

| Rewind and Rewind-Unload.        |         |      |   |     |   |   |   |   |              |

|                                  |         |      |   |     |   |   |   |   |              |

|                                  |         |      |   |     |   |   |   |   | 3-13         |

|                                  | •••     |      |   | •   | • | • | • | • | 3-13         |

| Unit Free Device End             |         |      |   |     |   |   |   |   | 3-13         |

| Rewind at LP                     |         |      |   |     |   | • |   |   | 3-14         |

| Rewind-Unload                    |         |      |   |     |   |   |   |   | 3-14         |

| Unit Free after Rewind-Unload    | ι.      | • •  | • | •   | • | ٠ | • | ٠ | 3-14         |

| End Status Burst Mode            | • •     | • •  | ٠ | •   | • |   |   | • | 3-14         |

| Operation                        | •••     |      | • | •   | • | • | • | • | 3-14         |

| End Status Request In                         | In   | teri | upt  |      |     |      |     |      |    |    |    |   |   | 3-15        |

|-----------------------------------------------|------|------|------|------|-----|------|-----|------|----|----|----|---|---|-------------|

| Status Pending                                |      |      |      | •    | •   |      | •   |      | •  | •  |    |   |   | 3-15        |

| Request In                                    |      |      |      |      |     |      |     |      |    |    |    |   |   |             |

| Interrupt Address In                          |      |      |      |      |     |      |     |      |    |    | •  |   |   | 3-16        |

| Interrupt Status In .                         |      |      |      |      |     |      |     |      |    |    |    |   |   |             |

| Turnaround                                    |      |      |      |      |     |      |     |      |    |    |    |   |   |             |

| Operation                                     |      |      |      |      |     |      |     |      |    |    |    |   |   |             |

| Erase before Turnaro                          | und  | ÷    |      | Ī    |     |      | ÷   |      |    | ÷  |    | · | ļ | 3-16        |

|                                               |      | ·    | •    | ·    | •   | ·    | •   | •    | •  | ·  | •  | · | · | 0 10        |

| CHAPTER 4. FEATURE                            | S    |      |      |      |     |      |     |      |    |    |    |   |   | 4 <b>-1</b> |

| Seven-Track Operation                         |      |      |      |      |     |      |     |      |    |    |    |   |   |             |

| Data Conversion .                             |      |      |      |      |     |      |     |      |    |    |    |   |   | 4-1         |

| Data Conversion .<br>Feature Functional Units | 5    | •    | •    | •    |     | •    |     | •    | •  | •  |    |   | • | 4-2         |

| Mode Register                                 |      | •    |      |      |     |      |     |      |    | •  |    |   |   | 4-2         |

| Translators                                   |      |      |      |      |     |      |     |      |    |    |    |   |   |             |

| Byte Counter and Cha                          | irac | ter  | Co   | unt  | er  |      |     |      |    |    |    |   |   | 4-4         |

| Data Convert Theory of                        |      |      |      |      |     |      |     |      |    |    |    |   |   |             |

| Write Data Convert                            |      |      |      |      |     |      |     |      |    |    |    |   |   |             |

| Read Data Convert                             |      |      |      |      |     |      |     |      |    |    |    |   |   |             |

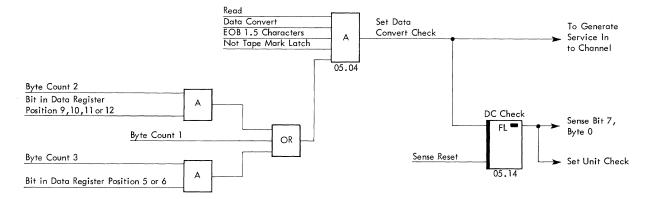

| Data Convert Check                            |      |      |      |      |     |      |     |      |    |    |    |   |   |             |

| Data Convert Check                            | •    | •    | •    | •    | •   | •    | •   | •    | •  | •  | •  | • | • | 4-/         |

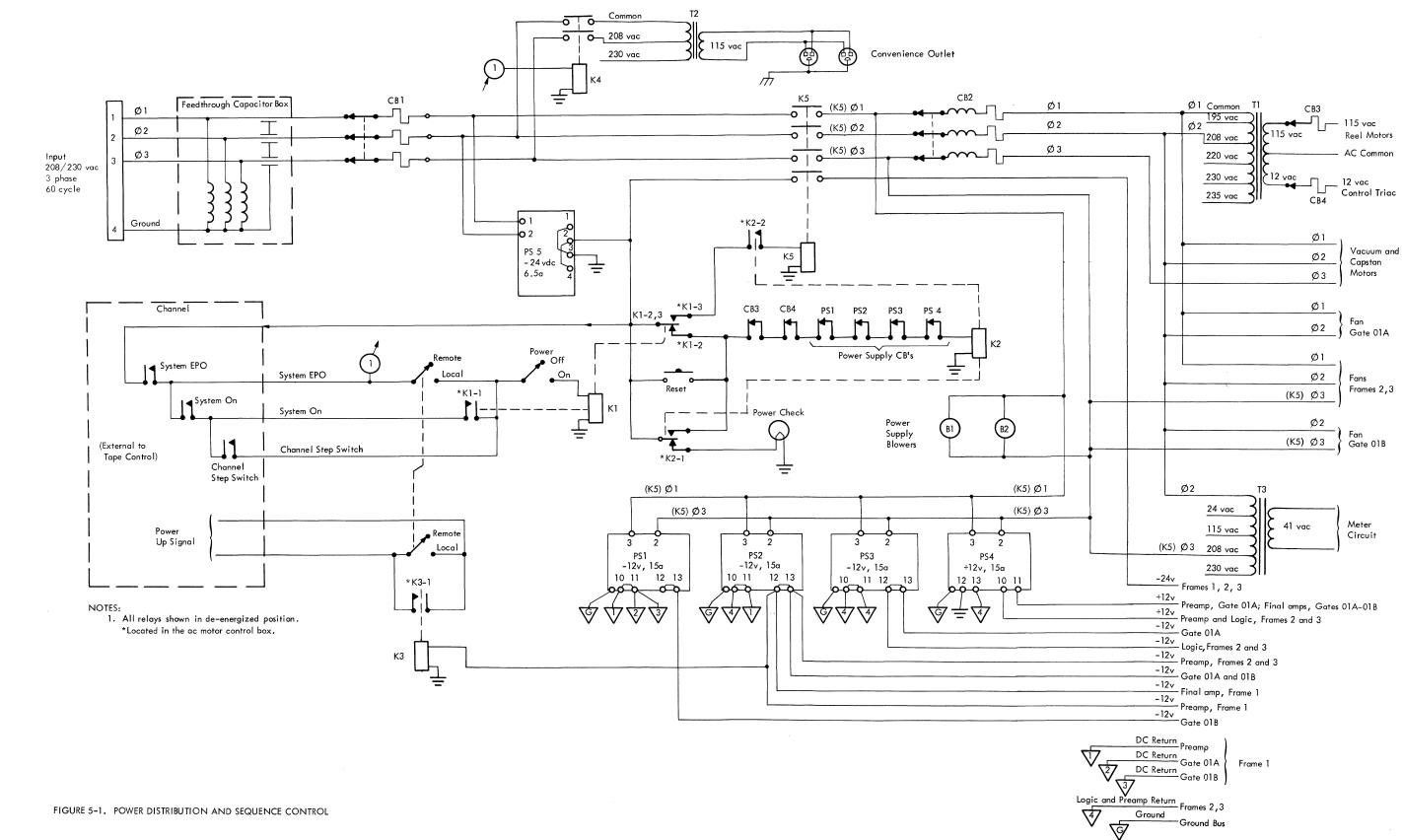

| CHAPTER 5. POWER S                            | IIPF | ии   | S 4  | NT   | ۰ c | ON   | TR  | OT   |    |    |    |   |   | 5_1         |

| Power-On Sequence, Re                         |      |      |      |      |     |      |     |      |    |    |    |   |   |             |

| Overload Control .                            |      |      |      |      |     |      |     |      |    |    |    |   |   |             |

| Power Controls                                |      |      |      |      |     |      |     |      |    |    |    |   |   |             |

| rower controls                                | •    | •    | •    | •    | •   | •    | •   | •    | •  | •  | •  | • | • | 3-2         |

| CHAPTER 6. CONSOLE                            | A1   | ٧D   | МА   | IN   | TEN | JAN  | VCE | E FE | AI | UR | ES |   |   | 6-1         |

| Section 1. Console .                          |      |      |      |      |     |      |     |      |    |    |    |   |   |             |

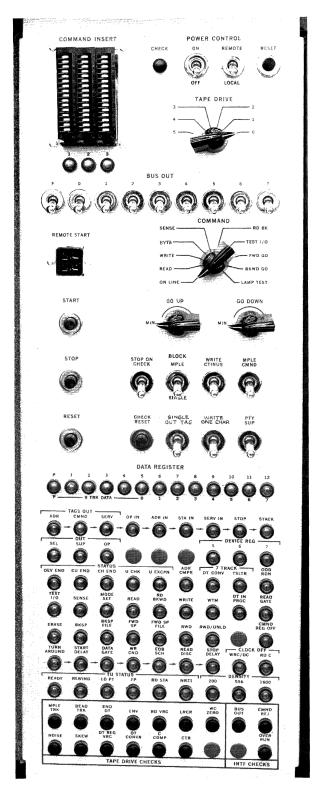

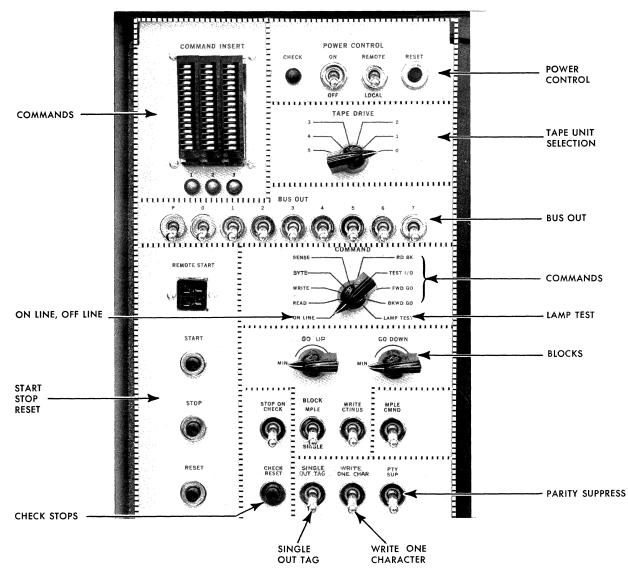

| CE Panel Operation .                          |      |      |      |      |     |      |     |      |    |    |    |   |   | 6-1         |

| Power Controls                                |      |      |      |      |     |      |     |      |    |    |    |   |   |             |

| Start, Stop, and Rese                         |      |      |      |      |     |      |     |      |    |    |    |   |   |             |

|                                               |      |      |      |      |     |      |     |      |    |    |    |   |   |             |

| On-Line and Off-Line                          |      |      |      |      |     |      |     |      |    |    |    |   |   |             |

| Tape Unit Selection                           |      |      |      |      |     |      |     |      |    |    |    |   |   |             |

| Commands                                      |      |      |      |      |     |      |     |      |    |    |    |   |   |             |

| Lamp Test                                     |      |      |      |      |     |      |     |      |    |    |    |   |   |             |

| Bus Out                                       |      |      |      |      |     |      |     |      |    |    |    |   |   |             |

| Check Stops                                   |      |      |      |      |     |      |     |      |    |    |    |   |   |             |

| Blocks                                        |      |      |      |      |     |      |     |      |    |    |    |   |   |             |

| Single Out Tag .                              | •    | •    | •    | •    | •   | •    | •   | •    | •  | •  | •  | • | • | 6-4         |

| Write Single Charact                          | er   | •    |      | •    |     | •    |     |      | •  | •  | •  | • |   | 6-4         |

| Parity Suppress                               |      | •    |      |      |     |      |     |      |    |    | •  | • |   | 6-4         |

| Section 2. Maintenance                        |      |      |      |      |     |      |     |      |    |    |    |   |   |             |

|                                               |      |      |      |      |     |      |     |      |    |    |    |   |   | -           |

| APPENDIX A. UNIT CH                           | IAR  | AC   | те   | RIS  | STI | CS   |     |      |    |    |    |   |   | A-1         |

|                                               |      |      |      |      |     |      |     |      |    |    |    |   |   |             |

| APPENDIX B. SPECIAL                           | CII  | RCI  | JIT  | S    | •   | •    | •   | •    | •  | •  | •  | • |   | B <b>-1</b> |

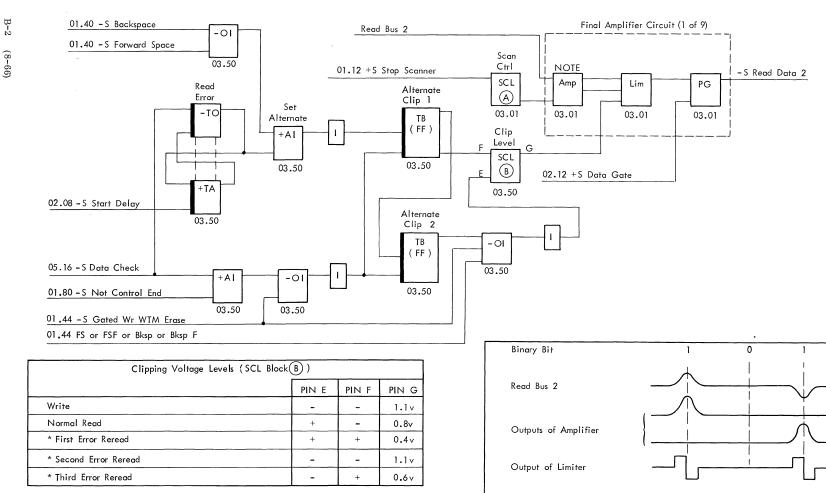

| Final Amplifier and Clip                      | opir | ıg l | Leve | el C | Con | tro] | ι.  | •    | •  | •  |    |   | • | B-1         |

| Pulse Generation .                            | •    |      |      |      |     |      |     |      |    |    |    | • |   | B-1         |

| Clipping Voltage Lev                          | els  |      |      |      |     |      |     |      |    |    |    |   |   | B-1         |

|                                               |      | •    |      | •    |     |      |     |      |    |    |    |   |   | B-1         |

|                                               |      |      |      |      |     |      |     |      |    |    |    |   |   |             |

| INDEX                                         |      |      |      |      |     | •    | •   | •    |    |    |    | • |   | X-1         |

|                                               |      |      |      |      |     |      |     |      |    |    |    |   |   |             |

# ILLUSTRATIONS

|        |       | Manual |

|--------|-------|--------|

| Figure | Title | Page   |

# CHAPTER 1. INTRODUCTION

| 1-1  | Control Unit System Relationship 1-2         |

|------|----------------------------------------------|

| 1-2  | Blocks and Gaps 1-4                          |

| 1-3  | Write Skew (Exaggerated) 1-5                 |

| 1-4  | Tape Data Format 1-6                         |

| 1-5  | Input/Output Interface Lines, System/360 1-8 |

| 1-6  | Control Unit Priority Wiring 1-9             |

| 1-7  | IBM 2415 Tape System 1-10                    |

| 1-8  | NRZI Method of Recording 1-10                |

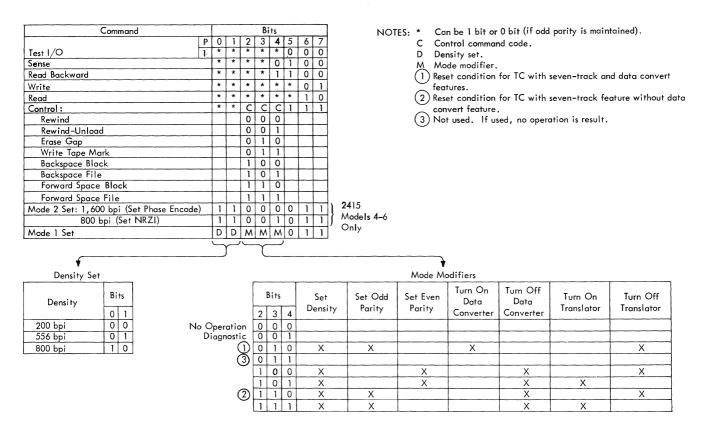

| 1-9  | Command Codes 1-11                           |

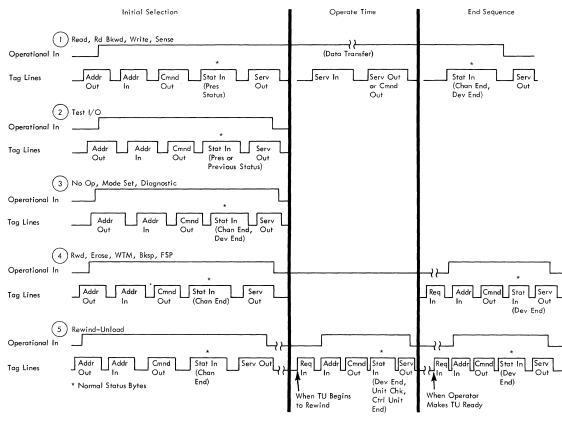

| 1-10 | Channel Interface Tag Line Sequences 1-12    |

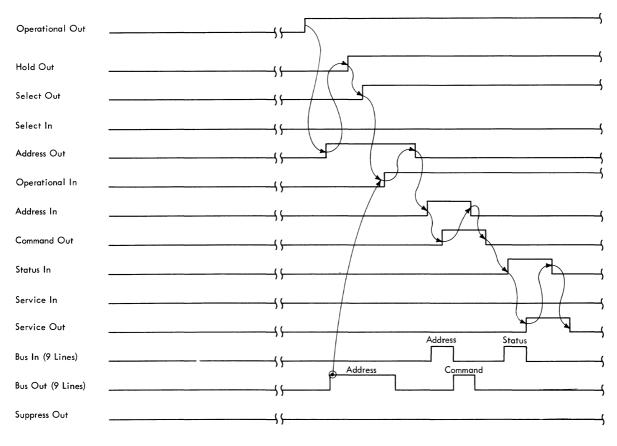

| 1-11 | Initial Selection Interface Sequence 1-13    |

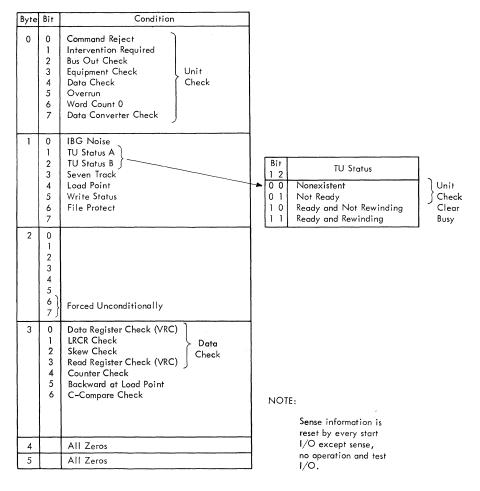

| 1-12 | Sense Bytes 1-14                             |

| 1-13 | Status Bits 1-18                             |

| 1-14 | Error Conditions (NRZI Operation) 1-19       |

|      |                                              |

# CHAPTER 2. FUNCTIONAL UNITS

| CHAFI  | ER 2. FUNCTIONAL UNITS                     |            |

|--------|--------------------------------------------|------------|

|        |                                            | Systems*   |

| Figure | Title                                      | Page       |

| 2-1    | Metering and On-Line Controls              | 00.21.01.1 |

| 2-2    | Select Signal Gating, Delay, and Wiring .  | 00.21.02.1 |

| 2-3    | Address Decoder and Generator              | 00.21.03.1 |

| 2-4    | Tape Unit Address Decode, Selection, and   |            |

|        | Unit Free Gating • • • • • • • •           | 00.21.04.1 |

| 2-5    | Device Register and Device End Scanner .   | 00.21:05.1 |

| 2-6    | Resets General, Selective, Machine,        |            |

|        | Sense, and Status                          | 00.21.06.1 |

| 2-7    | Stop Latch and Halt I/O                    | 00.21.07.1 |

| 2-8    | Early Reset                                | 00.21.07.1 |

| 2-9    | Idle Reset (Green and Go)                  | 00.21.07.1 |

| 2-10   | TAU Reset                                  | 00.21.08.1 |

| 2-11   | Force Burst Mode and Operational In        | 00.21.09.1 |

| 2-12   | Command Register, Decoder, and Gating .    | 00.21.10.1 |

| 2-13   | Bus Out Parity Check and Bus In P-Bit      |            |

|        | Injection                                  | 00.21.09.1 |

| 2-14   | Data Register Position 7, Input/Output     |            |

|        | Gating                                     | 00.21.11.1 |

| 2-15   | Data Register Resets                       | 00.21.12.1 |

| 2-16   | Status Latches                             | 00.21.13.1 |

| 2-17   | Delay Counter, Write Clock, Sense Counter, |            |

|        | and Drive                                  | 00.21.14.1 |

| 2-18   | Write Deskewing and Write Triggers         | 00.21.15.1 |

| 2-19   | Cyclic Redundancy Check Register (CRCR).   | 00.21.16.1 |

| 2-20   | Read Clock, Drive, and First-Bit Latch     | 00.21.17.1 |

| 2-21   | Data Time and Tape Mark Detection          | 00.21.18.1 |

| 2-22   | Command Reject                             | 00.31.01.1 |

| 2-23   | Bus Out Check                              | 00.31.01.1 |

| 2-24   | Skew Error                                 | 00.31.01.1 |

| 2-25   | Word Count 0                               | 00.31.02.1 |

| 2-26   | Counter Check                              | 00.31.02.1 |

| 2-27   | IBG Noise                                  | 00.31.02.1 |

| 2-28   | Ready Drop                                 | 00.31.03.1 |

| 2-29   |                                            | 00.31.03.1 |

| 2-30   | Det D tet MDO                              | 00.31.04.1 |

| 2-30   |                                            | 00.31.05.1 |

| 2-31   | Read Register VRC                          | 00.31.06.1 |

| 2-32   |                                            | 00.31.00.1 |

| 2-33   |                                            | 00.31.07.1 |

| 2-34   | C-Compare Error • • • • • • • • •          | 00.31.0/.1 |

# CHAPTER 3. PRINCIPLES OF OPERATION

|        |                                              | Systems*   |

|--------|----------------------------------------------|------------|

| Figure | Title                                        | Page       |

| 3-1    | Short Busy or Bypass Select (Flow)           | 00.40.01.1 |

| 3-2    | Initial Selection-Address Selection (Flow) . | 00.40.02.1 |

| 3-3    | Initial Selection-Command Set,               |            |

|        | Status In (Flow)                             | 00.40.03.1 |

| 3-4    | Initial Selection Sequence (Timing)          | 00.40.04.1 |

| 3-5    | Sense Operation (Flow)                       | 00.40.10.1 |

| 3-6    | Read Forward Operation (Flow)                | 00.41.01.1 |

| 3-7    | Read Forward Sequence (Timing)               | 00.41.02.1 |

| 3-8    | Read Backward Operation (Flow)               | 00.41.10.1 |

| 3-9    | Read Backward Sequence (Timing)              | 00.41.11.1 |

| 3-10   | Write Operation (Flow)                       | 00.41.20.1 |

| 3-11   | Write Sequence (Timing)                      | 00.41.21.1 |

| 3-12   | Forward Space Block/File (Flow)              | 00.41.30.1 |

| 3-13   | Backspace Block/File (Flow)                  | 00.41.40.1 |

| 3-14   | Write Tape Mark or Erase Gap (Flow)          | 00.41.50.1 |

| 3-15   | WTM and Erase Gap Sequence (Timing).         | 00.41.51.1 |

| 3-16   | Rewind or Rewind-Unload (Flow)               | 00.40.20.1 |

| 3-17   | End Status Burst Mode (Flow)                 | 00.40.30.1 |

| 3-18   | End Status Burst Mode (Timing)               | 00.40.31.1 |

| 3-19   | End Status Request In Interrupt (Flow) .     | 00.40.40.1 |

| 3-20   | End Status Request In Interrupt (Timing).    | 00.40.41.1 |

| 3-21   | Turnaround (Flow).                           | 00.40.50.1 |

|        |                                              |            |

| CHAPTI | ER 4. FEATURES                        | Systems*   |

|--------|---------------------------------------|------------|

|        |                                       | or Manual  |

| Figure | Title                                 | Page       |

| 4-1    | Mode Register                         | 00.27.01.1 |

| 4-2    | Translators                           | 00.27.02.1 |

| 4-3    | Eight-Bit Code BCD Relationship • • • | • • 4-3    |

| 4-4    | Byte and Character Counter            | 00.27.04.1 |

| 4-5    | Data Convert Check (DCC)              | • • 4-7    |

#### CHAPTER 5. POWER SUPPLIES AND CONTROL

|        |                                         |   |   |   | Manual |

|--------|-----------------------------------------|---|---|---|--------|

| Figure | Title                                   |   |   |   | Page   |

| 5-1    | Power Distribution and Sequence Control | • | • | • | 5-3    |

## CHAPTER 6. CONSOLE AND MAINTENANCE FEATURES

| -      |                                          |   | Manual |

|--------|------------------------------------------|---|--------|

| Figure | Title                                    |   | _Page  |

| 6-1    | IBM 2415 CE Panel                        | • | 6-1    |

| 6-2    | Functional Grouping of CE Panel Controls | • | 6-2    |

| 6-3    | Command Card Wiring • • • • • • • •      | • | 6-3    |

# APPENDIX B. SPECIAL CIRCUITS

|        |                                        |   | Manual |

|--------|----------------------------------------|---|--------|

| Figure | Title                                  |   | Page   |

| B-1    | Final Amplifier and Clip Level Control | • | • B-2  |

\* These figures are released as reference pages in the systems maintenance diagram volume that is shipped with each tape system.

# ABBREVIATIONS

| А    | AND Circuit                             | ms      | Millisecond                      |

|------|-----------------------------------------|---------|----------------------------------|

| ALD  | Automated Logic Diagram                 | mv      | Millivolt                        |

| AND  | AND Circuit                             |         |                                  |

| AR   | Amplifier Circuit                       | N       | Inverter                         |

|      |                                         | NRZI    | Non–Return to Zero IBM           |

| BOB  | Beginning of Block                      |         |                                  |

| BOT  | Beginning of Tape (Load Point)          | 0       | OR Circuit                       |

| bpi  | Bytes per Inch                          | OE      | Exclusive OR Circuit             |

|      |                                         | OR      | OR Circuit                       |

| CCW  | Counterclockwise                        |         |                                  |

| CE   | Customer Engineer                       | P (bit) | Parity Bit                       |

| CRCC | Cyclic Redundancy Check Character       | PE      | Phase Encode                     |

| CRCR | Cyclic Redundancy Check Register        |         |                                  |

| CU   | Control Unit                            | RC      | Read Clock                       |

| CW   | Clockwise                               | RIC     | Read In Clock                    |

|      |                                         | ROC     | Read Out Control                 |

| DC   | Data Converter or Delay Counter         | RR      | Read Register                    |

| DR   | Data Register                           | R/W     | Read/Write                       |

|      |                                         |         |                                  |

| EOB  | End of Block                            | SKB     | Skew Buffer                      |

| EOT  | End of Tape (Tape Indicate)             | SLD     | Simplified Logic Diagram         |

|      |                                         |         |                                  |

| FF   | Flip-Flop Circuit                       | TAU     | Tape Adapter Unit                |

| FL   | Flip-Latch Circuit                      | TB      | Binary Trigger                   |

| FP   | File Protect                            | TC      | Tape Control                     |

|      |                                         | TL      | Tape Indicate                    |

| I    | Inverter                                | TM      | Tape Mark                        |

| IBG  | Interblock Gap                          | Triac   | Triode AC Switch (Semiconductor) |

| 1/0  | Input/Output                            | TU      | Tape Unit                        |

| ips  | Inches per Second                       |         |                                  |

|      |                                         | usec    | Microsecond                      |

| LP   | Load Point                              |         |                                  |

| LRCC | Longitudinal Redundancy Check Character | v       | Volt                             |

| LRCR | Longitudinal Redundancy Check Register  | VRC     | Vertical Redundancy Check        |

| _    | 1 (11)                                  | WC      | Write Cleak                      |

| ma   | Milliampere                             | WC      | Write Clock                      |

| mill | 1/1000 Inch                             | WTM     | Write Tape Mark                  |

|      |                                         |         |                                  |

IBM 2415 MODEL 1 OR 4 MAGNETIC TAPE UNIT AND CONTROL

# INPUT/OUTPUT DEVICES

IBM Data Processing Systems include input/output devices, control units, channels, storage units, and central processors, although they vary widely in size, complexity, speed, and application. Input/ output devices enter information into the system (input) and record information generated by the system (output).

Typical input devices sense or read data information stored on media such as punch cards, magnetic tape, paper tape, printed forms, or printed copy. The same types of media are used in typical output devices to record or write data information. Some devices operate as either an input or output device.

Magnetic tape is used extensively as an input/ output medium because it rapidly stores large amounts of data in compact, easily handled form. Data stored (written) on magnetic tape may be retained as permanent recordings that can be reread repeatedly without destroying the recorded information, or as temporary recordings that are erased automatically as new data is written on tape.

# Magnetic Tape

- Magnetic tape consists of a long plastic strip coated with a ferromagnetic material.

- Some types of tape are designed to provide superior wear characteristics and greater reliability.

- The width and thickness of tape are generally determined by the type of magnetic tape device on which the tape is used.

- Magnetic tape is supplied on reels for ease of handling.

Magnetic tape consists of a long, flexible, and continuous strip of plastic (the base) coated with a layer of ferromagnetic material dispersed in a suitable binder (the coating). There are two kinds of 1/2inch wide magnetic tape in general use: IBM DYNEXCEL tape (formerly heavy duty (HD) tape) and Mylar\* tape. DYNEXCEL tape provides greater reliability of performance as an input/output medium. Both kinds of tape use a polyethelene plastic base. The composition of the ferromagentic coating determines the color and wear characteristics of the tape. Due to the materials used in the coating, heavy duty tape wears better than Mylar tape and withstands higher temperature during storage. For ease of handling, magnetic tape is wound on reels similar to those used with conventional home tape recorders. Reel sizes vary according to the type of tape and magnetic tape device on which it is used.

Each reel of magnetic tape contains physical markers to designate the useful or data area portion. The extreme ends of the tape are not usable because some tape must remain on the reels during use. Tape markers that are sensed photoelectrically by the magnetic tape device usually consist of reflective foil stickers. (Refer to Chapter 1 of Field Engineering Theory of Operation, <u>IBM 2415 Models 1-6</u> <u>Magnetic Tape Unit</u>, Form Y22-2915 for a detailed description of magnetic tape and the method of recording.

# Magnetic Tape Device

- A magnetic tape device is the means by which data is actually written on and read from magnetic tape.

- Data is written on tape in separate longitudinal rows called tracks.

- A separate read and write head reads and writes data in each track.

- All read and write heads are packaged in one read/write head assembly.

- Other essential functions of a magnetic tape device, referred to as a tape unit, are tape and reel motion control.

- Most tape unit operations are timed and controlled externally.

A magnetic tape device is the machine that is used as an input device to read data from magnetic tape and as an output device to write data on magnetic tape. A magnetic tape device is most commonly referred to as a tape unit.

Data is recorded on magnetic tape in longitudinal rows called tracks. These tracks are similar to the rows on a punched card. A tape unit has one write head and one read head for each tape track. The read and write heads for all tracks are in a single unit called a read/write head assembly. When reading (input), the tape unit moves tape across the read/write head assembly so that the read heads sense information, previously written on the coated

<sup>\*</sup> Trademark of E.I. DuPont deNemours & Co., Inc.

surface of the tape, as a series of pulses. When writing (output), the tape unit moves tape across the read/write head assembly so that the write heads record new data on the coated surface of the tape by magnetizing the surface coating of each track.

In addition to reading and writing data and moving tape at a fixed speed, a tape unit must also sense tape limits, rewind tape, and control the motion of tape reels. Due to the physical nature of tape movement and control, a magnetic tape unit is, of necessity, an electromechanical device that operates slower than an electronic device. Before data can be written on tape, for example, the tape unit requires a period of delay from the time it is ordered to write, while the tape builds up speed. Tape requires hundreds of microseconds to attain operating speed; whereas, electronic devices, such as a central processor, operate in the nanosecond (thousandths of a microsecond) range.

## Control Unit

- Central control of the operation of more than one input/output (I/O) device is more efficient and economical.

- A tape control unit is an all-electronic device that controls several tape units.

- The tape control is entirely responsible for the proper control of all system operations on any attached tape unit.

- The tape control must select a unit, control its movement, time its operations, and monitor conditions such as status and errors.

- A tape control is the only communications link between a tape unit and the external system.

- Control units communicate with the computer system through I/O channels.

A few tape unit functions are controlled automatically by essential circuitry within the device, but most unit functions are controlled externally. One set of timing and control circuits, operating several tape units, is more economical than duplicate control circuitry in each tape unit. A single set of electronic control circuits, used to control multiple I/O devices of the same type, is packaged in a device called a control unit.

A magnetic tape control unit is referred to as a tape control; some of the major functions of a tape control are:

1. Selecting (addressing) a specific tape unit.

2. Initiating the proper status conditions for specific operations.

3. Timing delays before and after writing or reading.

4. Timing of data transfer to and from the computer system input/output control.

5. Controlling the beginning and end of tape motion.

6. Monitoring of tape limit signals, error conditions, tape unit malfunctions, etc.

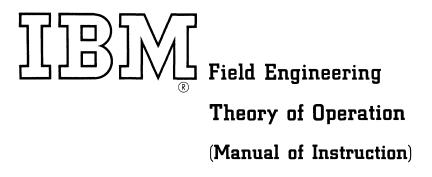

All system communications with a tape unit, including the flow of data, pass through the tape control (Figure 1-1). However, if the computer system has to communicate directly with all of its control units, system operation is delayed needlessly. A central control, called a channel, usually external to the system central processor, directs all I/O operations.

# Channel

- The channel is a separate electronic device that frees the processor from the task of controlling I/O operations.

- The control program in the computer system initiates all I/O operations by issuing instructions to the channel.

- The channel initiates operations by issuing commands to a control unit.

A channel is designed to free the computer system from the time-consuming task of controlling I/O operations; this includes selecting specific control units and I/O devices, initiating operations, and the buffering of data flow to and from the system main storage. (Buffering is the accumulation and temporary storage of groups of data to reduce the number of data transfers required of the system storage.) By relieving the central processor from the task of direct control of I/O, data processing can proceed concurrently with I/O operations.

FIGURE 1-1. CONTROL UNIT -- SYSTEM RELATIONSHIP

# DATA FORMAT

# <u>Bit</u>

- A bit is the smallest unit of information.

- A bit is a binary 1 when it represents an active condition.

- A bit is a binary 0 when it represents an inactive condition.

The smallest unit of information in a data processing system is called a bit. Each bit represents either an active or inactive condition, such as the on or off state of a bistable device (latch). A bit becomes a binary 1 when it represents the on or active condition. A bit becomes a binary 0 when it represents the off or inactive condition.

# Byte

- Bits are combined into groups called bytes.

- A byte contains 8 data bits.

- A ninth bit is added for parity checking.

Serial transmission of individual bits between devices, and within devices, is time consuming and inefficient, so groups of eight bits are combined to form bytes. An eight-bit byte can represent a special code, character, letter, or number, whose configuration is determined by the CPU.

Bits or bit positions in a register are designated 0-7.

If a particular character or code is represented by the active state of the four- and seven-bit positions of a byte, the byte would have a 1 bit in positions 4 and 7, and 0 bits in the other six positions. The four- and seven-bit signal lines have active levels; whereas, the remaining lines have inactive levels (on voltage or current signal lines).

A ninth bit is added to a byte for parity checking as the byte is moved from one set of circuits to another. See "Parity Bit."

# Character

- A character is a group of six data bits.

- A seventh bit (check bit) is added for parity checking.

- Characters are used for seven-track feature operations only.

Basic 2415 operations utilize the byte on nine-track tape units. When installed as a feature, seven-track tape units can be used to provide compatibility with the tape format of earlier model tape systems. A smaller group of bits for feature operation, called a character, contains six data bits. A seventh bit, called a check (C) bit, is added for parity checking. Refer to Chapter 4 for feature data flow.

# Parity Bit

- A parity (P) bit is added to each byte as a means of error checking.

- The total number of binary 1 bits in a byte (data bits and parity bit combined) is always odd for odd parity.

- A character also contains a parity (check) bit.

- The total number of binary 1 bits in a character (data and C bits) is always odd or even, depending on the format designated by the system program.

A parity bit is an additional bit that is added to each byte, or character, as a means of error checking the data. For odd parity, the binary state of the parity bit (1 or 0) is such that there is always an odd number of 1 bits in each byte, or character, <u>including</u> the parity bit.

For example, if a byte contains bits 01101001(0-7), the parity bit is 1 to give a total of five 1 bits 101101001 (P, 0-7). If a character contains the bits 101100, the check bit is 0 for a total of three 1 bits 0101100. For an even parity character, the binary state of the check bit is such that there is always an even number of 1 bits in each character, including the check bit.

# Block

- A group of bytes (or characters) is called a block.

- The amount of data in a tape block (number of bytes or characters) is variable.

- Byte spacing in a block is determined by tape control oscillators and tape speed.

- Tape blocks are separated by gaps of erased tape.

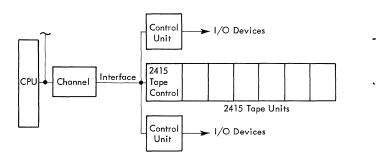

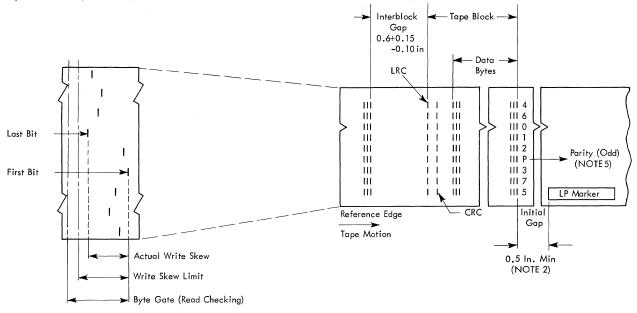

All bits in a byte (or character) are transferred in parallel to the selected tape unit. When data bytes are written on magnetic tape, each byte is written perpendicular to the horizontal edge of tape. Each bit of a byte is written simultaneously (ideal condition) in separate tracks on tape. A separate group of related bytes, such as all of the information punched in an 80-column card, is called a block. Refer to Field Engineering Theory of Operation, <u>IBM 2415</u> <u>Models 1-6 Magnetic Tape Unit</u>, Form Y22-2915, for a detailed description of writing on tape. Tape blocks are separated by erased areas of tape (Figure 1-2).

FIGURE 1-2. BLOCKS AND GAPS

#### Interblock Gaps (IBG)

- An interblock gap is the erased area between two blocks.

- The gap between blocks is generated by tape unit mechanical inertia and tape control and tape unit delay timings.

- A start delay is timed before writing or reading.

- A stop delay is timed after writing or reading.

- Write start and stop delays create the interblock gaps between blocks.

- Groups of related blocks are usually separated by a tape mark.

The gap or blank area of erased tape between blocks is the result of mechanical limitations in the tape unit. Because tape cannot start or stop instantaneously, a period of time (in milliseconds) is required to accelerate tape to full speed or to stop tape after the end of a block.

When end of block is reached, the tape unit "go" signal is dropped to stop movement. However, inertia moves the tape well past the write heads before motion stops. The tape control must make allowance for tape unit limitations by appropriate delay timings, although the tape unit times most of the stop delay.

A command to write another data block starts tape motion again. Bytes are written too close together unless tape is at full speed, so the tape control unit delays transmission of bytes to the tape unit. The start delay time for write operations (while the tape accelerates) is called write delay (or read delay for read type operations).

A gap between blocks on tape represents the total length of tape movement created by the write stop time of one block and the write (start) delay time of the following block. Start-stop times (mechanical), which are adjustable in the tape unit, have a direct bearing on the length of the gap. If tape unit mechanical start and stop times are changed, the length of the resulting gaps are also changed.

Short stop times tend to create shorter gaps. Quick acceleration tends to create longer gaps. When a tape unit gets up to full speed quicker, tape travels a greater distance during write delay time. The normal gap between blocks (Figure 1-2) is 0.6 inch long for nine-track tape units and 0.73 inch long for seven-track tape units. The blocks can be closer in nine-track because nine-track tape unit read/write heads are constructed with a closer spacing between the read and write heads.

# File

- A file is a group of blocks.

- Files are separated by tape marks.

- The number of blocks in a file is determined by the CPU program.

A file, as recorded on the tape, is a group of blocks separated by a special block called a tape mark. The number of blocks in a file is variable and is determined by the CPU program. By using tape marks between groups of related blocks, programs can determine when files begin and end.

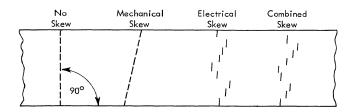

# Skew

- Skew is the misalignment of bits within a byte.

- Bits can be skewed during the writing and/or the reading process.

- Skew is generally mechanical or electrical.

- Mechanical skew is minimized by proper read/ write head adjustment.

- Electrical write skew is minimized by adjustable delay taps in the tape control for each tape unit.

- Electrical read skew is minimized by adjustable delay taps in each tape unit.

During a write operation, pulses that comprise a byte are delayed (by preset adjustable delay taps)

to align bits, and these pulses are sent to the tape unit. Ideally, all bits of a byte should be perfectly aligned and should be detected (read) at the same instant as the byte passes over the read heads during a subsequent read operation. Unfortunately, this ideal condition is difficult to achieve due to write and read head manufacturing tolerances, small differences in head assembly adjustments between tape drives, and slight variations in circuit delays between bit tracks. These factors are further aggravated if a tape swerves slightly as it passes over the heads during the write operation or any subsequent read operation.

In the misalignment of bits within a byte, skew can mean a slanting or staggering of bits relative to the horizontal edge of tape. If skew is excessive, bits of adjacent bytes might mix and cause read errors. Figure 1-3 shows an exaggerated example of write skew. The example is called write skew because the bytes are actually written on tape with the bits misaligned. However, bits written on tape in perfect alignment can be skewed during the read operation. Read heads and/or read circuits can cause the bits to be misaligned electrically; that is, some bits are delayed longer than others.

Skew is generally mechanical or electrical. Mechanical skew is usually caused by misadjustment of the write head assembly on the write drive and/or the read head assembly on the read drive. Electrical skew is caused by head manufacturing tolerances and/or circuit delays. Mechanical skew is corrected by adjustment of the head assemblies on the tape unit on which a tape is written and the unit on which the same tape is read. Electrical skew is minimized by adjustable tape control write delay taps or tape unit read delay taps during maintenance.

FIGURE 1-3. WRITE SKEW (EXAGGERATED)

# Check Characters

- The standard nine-track format contains data followed by two check characters: a CRCC and an LRCC.

- The seven-track format contains data followed by one check character, an LRCC.

The standard nine-track format writes two check characters at the end of each block (Figure 1-4). The first check character is the cyclic redundancy check character (CRCC), and the second check character is a longitudinal redundancy check character (LRCC).

The CRCC is a character developed in the CRC register in the tape control. This character, during each nine-track write operation, represents an accumulation of all the bits in the block. The CRCC is written on tape four byte spaces after the last data byte. (The CRCC is written to create compatible tapes for 2400-series tape systems, which use the CRCC for single bit read error correction.)

The second check character (LRCC) is an odd/even parity count of all the bits in each track of a block. The total number of bits in any track of a block is made an even number by placing a 1 or 0 in the LRCC position. The second check character is written four byte spaces after the CRCC, or a total of eight spaces from the last data byte. The nine-track LRCC represents the same odd/even bit count as the LRCC used in seven-track operations. Since the CRCC is written before the LRCC, the CRCC bits are included in the odd/even LRCC count. Each track must have an even number of bits in each block. For a seven-track operation, only one check character (the LRCC) is written.

The LRCC in a seven-track operation is written four character spaces after the last data character (Figure 1-4). The seven-track format meets the same specifications as the format used on other IBM tape systems, such as the IBM 729 or 7330 Magnetic Tape Units.

# Check Character Parity

- Nine-track LRC character is always odd parity.

- Seven-track LRC character and nine-track CRC character can be odd or even parity.

- CRC character contains an odd number of bits if there is an even number of data characters.

- CRC character contains an even number of bits if there is an odd number of data characters.

During nine-track operations, the LRCC always contains an odd number of bits. Thus, the vertical redundancy of a nine-track LRCC is always odd. However, the vertical redundancy (number of bits in the character) of the nine-track CRCC can be an odd or even number. As a general rule, the vertical redundancy of the CRCC is an even number if the total number of data bytes in the entire block is an odd number. Likewise, if the total amount of data bytes

Tape Data Format (Nine Track)

- NOTES: 1. Tape is shown with oxide side down. NRZI recording. Bit produced by reversal of flux polarity. Tape fully saturated in each direction.

- Tape to be fully saturated in the erased direction in the initial gap and the inter-record gap. Erasure such that an N seeking end of compass will point to start of tape.

- CRC Cyclic redundancy check character. Parity of CRC character is determined by the number of data characters in record. Odd number of data characters-even CRC character, etc. CRC used only in System/360 800 bpi. CRC character spaced four bits from data characters.

- 4. LRC Longitudinal redundancy check character always odd parity. Spaced four bits from CRC.

- 5. Parity Bit A vertical parity bit is written for each character containing an even number of bits.

Tape Data Format (Seven Track)

- NOTES: 1. Tape is shown with oxide side down. NRZI recording. Bit produced by reversal of flux polarity. Tape fully saturated in each direction.

- Tape to be fully saturated in the erased direction in the initial gap and the inter-record gap. Erasure such that an N seeking end of compass will point to start of tape.

- 3. LRC Longitudinal redundancy check character odd or even-spaced four bits from data character.

- 4. Parity Bit A vertical parity bit is written for each character.

FIGURE 1-4. TAPE DATA FORMAT

in the block is an even number, the vertical redundancy of the CRCC is odd. A nine-track LRCC always contains an odd number of bits; the CRCC may be odd or even, depending on the number of data bytes within the block. The seven-track data format may contain either an odd or even number of bits in the LRC character. This is possible because seventrack operations may employ odd or even redundancy when handling data bytes. The following considerations apply to the redundancy of the seven-track LRCC:

1. Using even redundancy mode always produces an LRCC that contains an even number of bits, regardless of the number of data bytes in the block.

2. When using odd redundancy mode, the number of bits in the LRCC is odd if there is an odd number of data bytes, or the number of bits in the LRCC is even if there is an even number of data bytes in the block.

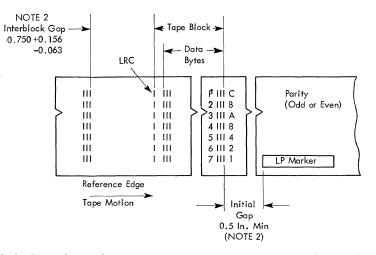

# I/O INTERFACE

- The I/O interface establishes requirements for communication between the channel and control units.

- The I/O interface uses 34 lines.

- The I/O interface specifies the function of the interface lines and the sequence in which the lines are used.

The I/O interface is a set of established requirements for uniform signal transfers between a channel and all control units. The interface uses 34 lines and specifies the signal sequence and information format transferred on the lines. (The reader should be familiar with the contents of Systems Reference Library, <u>IBM System/360 I/O Interface -- Channel</u> to Control Unit, Original Equipment Manufacturers' <u>Information (OEMI)</u>, Form A22-6843.) Interface lines are grouped by function (Figure 1-5). The following is a brief review of the functions of each group.

Bus Out Lines transmit information (data, I/O device address, commands, and control orders) from the channel to the control unit.

Bus In Lines transmit information (data, selected  $\overline{I/O}$  device identification, status information, and sense data) from the control unit to the channel.

<u>Tag Lines</u> interlock and control information on the buses and are used for special sequences.

<u>Selection Controls</u> are used for the selection and scanning of I/O control units and attached I/O devices.

$\underline{Metering\ Controls\ }$  condition usage meters in the various attached control units and I/O devices.

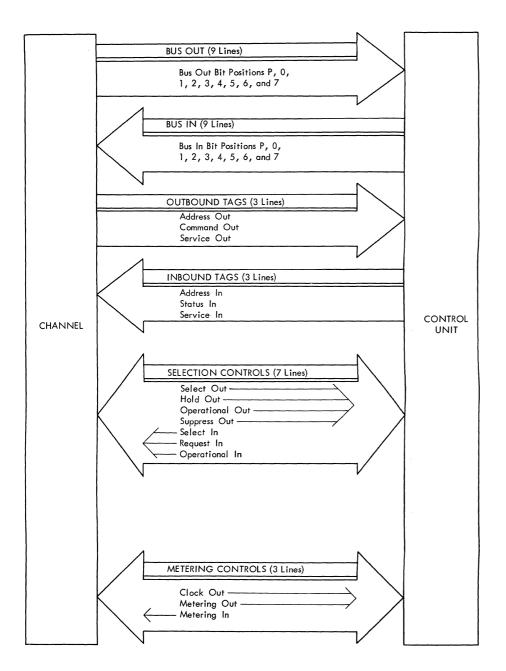

# CONTROL UNIT PRIORITY

- Control unit priority is determined by internal select signal wiring and physical connections to the interface signal cables.

- Interface priority is the order in which control units are selected if more than one unit requires channel service.

- The select signal leaves the channel as select out, but it may reach some control units as select in.

- When the select signal reaches a control unit for which the signal is <u>not</u> intended, the signal must be propagated to the next lower priority control unit.

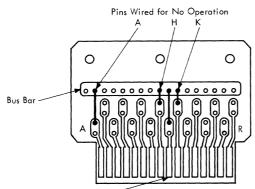

The select out and select in lines form a series loop from and to the channel through all attached control units (Figure 1-6). The select out line is jumpered to the select in line in the terminator block located at the tail gate of the control unit which is physically the farthest unit from the channel on the interface cable hookup. Electrical priority is established by wiring within each control unit when the system is installed.

The higher priority control units are wired in series with the select out line from the channel; the lower priority units are wired in series with the select in return line to the channel. The highest priority unit is the first unit which receives the select (out) signal; the lowest priority unit returns the select (in) signal directly to the channel.

The select signal sequence is such that a control unit must propagate the select signal to the next lower priority unit, when selection is not required. That is, when a control unit that does not need service (or is not addressed) receives the select signal, it must regenerate and pass on the select signal to the next control unit physically attached to the select out or select in line.

2415 MODELS 1, 2, AND 3 TAPE CONTROL

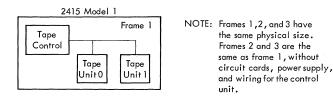

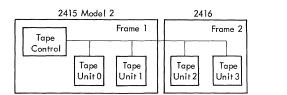

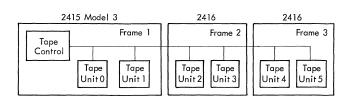

The IBM 2415 Tape Control is a control unit that operates as many as six tape units. The difference between Models 1, 2, and 3 is the number of tape units connected to the tape control (Figure 1-7). The

FIGURE 1-5. INPUT/OUTPUT INTERFACE LINES, SYSTEM/360

\* Not Always Required

FIGURE 1-6. CONTROL UNIT PRIORITY WIRING

Models 4, 5, and 6 tape control differs from Models 1, 2, and 3 in that it uses a method of coding called phase encode; while Models 1, 2, and 3 use the NRZI system.)

# NRZI System of Recording

- Polarity of tape is changed in either direction at a given time to record a 1 bit.

- Polarity of tape is not changed at a given time to record a 0 bit.

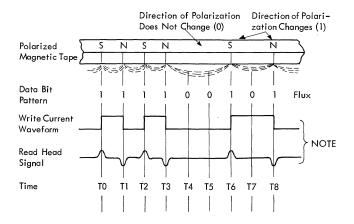

The NRZI system of recording information continuously polarizes magnetic tape; a logical 1 is recorded by changing the direction of polarization. A logical 1, then, is indicated by a change in the direction of polarization at a given time, while a logical 0 is indicated by no change in the direction of polarization at a given time. Refer to Chapter 4 of Field Engineering Theory of Operation, <u>IBM 2415 Models</u> <u>1-6 Magnetic Tape Unit</u>, Form Y22-2915 for a description of how the magnetic pattern is created on tape.

#### Writing on Tape

The write current waveform, shown in Figure 1-8, is an example of the signal sent to a tape unit write head over the write bus; it represents the information in one recording track. The tape control generates a write current waveform for each track according to the byte information sent by the channel. (The bit pattern in Figure 1-8 represents single track information for nine successive bytes.) Note that a write current polarity change occurs <u>only</u> when a 1 bit is indicated, and the tape is magnetized accordingly.

# Reading from Tape

When tape passes over the read heads during read or write operations, the magnetic flux patterns on tape cause read waveforms similar to the single read head signal shown in Figure 1–8. A pulse is generated only when a change in tape magnetic polarity passes the read head. (The write and read waveforms are shown together for a comparison of the results for the same bit pattern.)

FIGURE 1-7. IBM 2415 TAPE SYSTEM

NOTE: Waveforms shown are for comparison only; these waveforms would be difficult to view together on an oscilloscope.

FIGURE 1-8. NRZI METHOD OF RECORDING

## COMMAND OPERATIONS

All command operations are initiated by the channel with an initial selection sequence. During initial selection, a tape control and one tape unit are addressed, and a command is sent to the tape control. The tape control then responds with information about its status, indicating its ability to perform the command. The command (Figure 1-9) specifies which operation is to be performed.

Test I/O and non-motion control command (mode set) operations are completed during initial selection. All other operations are initiated when initial selection is completed. See Figure 1-10. A sense operation transfers information to the channel, but does not use the tape unit. Eight motion control command operations use the tape unit, but there is no data transfer between the tape control and the channel. Read, read backward, and write operations transfer data between the tape unit and the channel.

A detailed block diagram of over-all data flow and controls, Figure UDC-1, is contained in the diagram manual. Refer to Figure UDC-1 in conjunction with the following descriptions.

# **Initial Selection**

- Initial selection is performed in three basic steps: address selection, command set, and status response.

- When the tape control decodes its address, it then decodes the tape unit address and selects one tape unit.

- Tape control traps the select out signal and sends the tape control-tape unit coded address byte back to the channel.

- Channel sends a command to the tape control.

- Tape control decodes the command and sends status information back to the channel to complete the initial selection sequence.

#### Address Selection

Address selection is initiated by the channel, which sends a coded address byte on bus out and the address out tag (Figure 1-11) to all tape controls in parallel. All attached control units attempt to decode the address. The channel then sends select out to the tape controls in series.

When a tape control decodes its own address, it then sets the tape unit address in the device register and decodes the address to select one of the tape units.

When the tape control address is decoded, the tape control traps the select out signal when it arrives (does not pass it on to the next tape control). The selected tape control now activates the operational in line to interlock itself to the channel. The complete address (tape control and tape unit) is then sent

FIGURE 1-9. COMMAND CODES

back to the channel on the bus in lines for verification, and the complete address activates the address in tag to identify the information on the bus. Address selection is completed at this point.

# Command Set

When the channel receives the combined address byte of the tape control and tape unit it has selected, it responds by sending a coded command on bus out and activates the command out tag.

The tape control checks the coded command for correct parity in the data register. If parity is good (odd), the byte is set in the command register and the command is decoded. See Figure UDC-1. The tape control now inspects the decoded command to determine whether or not the designated command can be performed.

# Initial Status Response

The tape control completes the initial selection sequence by sending a status byte of information to the channel: tape control and tape unit status information is sent to the channel on bus in, and a status in tag is sent to the channel. The purpose of the initial status byte is to indicate to the channel the operational condition of the tape control and tape unit. If the tape control is not able to perform the command, the status byte indicates why the operation cannot be performed.

The initial status byte is normally empty (except for the P bit) for a read, write, or sense command. The byte contains a channel end status bit for a control command. Because a test I/O command is initiated to relieve the TC of pending status, it is not unusual for any particular status bits to be active during test I/O.

# Begin Operation or Stack Status

- Channel response to status in allows the tape control to begin operation or causes the tape control to stack status.

- Service out response signals that the status byte is accepted; proceed with the command.

- Command out response signals that the status byte is rejected; store (stack) status byte and block initiation of any operation that requires channel use.

FIGURE 1-10. CHANNEL INTERFACE TAG LINE SEQUENCES

• Prohibitive status conditions in control or tape unit cause tape control to block performance of command at end of initial selection.

At the end of initial selection, the channel response to status in mainly determines tape control procedure. The channel can either accept or reject the status byte. However, in either case, the operation is not executed by the tape control if prohibitive status conditions exist (such as tape unit is busy) as determined by the tape control.