# Field Engineering Theory Of Operation

**Restricted Distribution**

This manual is intended for internal use only and may not be used by other than IBM personnel without IBM's written permission.

2260 Display Station, Models 1 and 2

2848 Display Control, Models 1, 2, and 3 (Serial No. 60,000 Series)

#### PREFACE

This manual presents the detailed theory of operation of the IBM 2260 Display Station Models 1 and 2, and IBM 2848 Display Control Unit, Models 1, 2, and 3. However, the description of the 2848 Display Control pertains only to those units whose serial numbers are 60,000 or above.

The following publications can be used to supplement the information provided in this manual:

IBM System/360 I/O Interface - Channel to Control Unit - Original Equipment Manufacturers Information (Form A22-6843-3) This is a reprint of Y27-2046-2 incorporating changes released in the following F. E. Supplements:

| Form Number<br>Y27-2165-0 | Pages Affected<br>4-10, 4-11 and<br>4-18                                                                                                                                                     | $\frac{\text{Date}}{\text{Sept}}$ . | 11, 1967 |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|----------|

| ¥27-2171-0                | v through vii,<br>1-3 through 1-6,<br>1-21, 1-22, 2-97,<br>2-98, 2-123,<br>2-124, 2-125,<br>2-126, 6-1 through<br>6-4, B-1 through<br>B-3, X-1 through<br>X-8 add pages<br>2-124A and 2-124B | l                                   | 1, 1967  |

|                           |                                                                                                                                                                                              |                                     |          |

Definition

#### ABBREVIATIONS LIST

The abbreviations used in this manual, together with their definitions, are as follows:

|              |                             | EPO            | Emergency Power Off           |

|--------------|-----------------------------|----------------|-------------------------------|

| Abbreviation | Definition                  | ETX            | End of Text                   |

|              |                             | FC             | Feature Code                  |

| ACK          | Acknowledge                 | $\mathbf{LF}$  | Line Feed                     |

| ASCII        | American Standard Code for  | LRC            | Longitudinal Redundancy Check |

|              | Information Interchange     | MI             | Manual Input                  |

| CAN          | Cancel                      | NAK            | Not Acknowledge               |

| CRT          | Cathode-Ray Tube            | NDC            | Nondestructive Cursor         |

| DAU          | Data Adapter Unit           | $\mathbf{NL}$  | New Line                      |

| DC           | Display Control             | OLSA           | Off Line Selectric Analyzer   |

| DS           | Display Station             | SMS            | Standard Modular System       |

| EBCDIC       | Expanded Binary Coded Deci- | SOH            | Start of Heading              |

|              | mal Interchange Code        | $\mathbf{STX}$ | Start of Text                 |

| EOM          | End of Message              | VRC            | Vertical Redundancy Check     |

| EOT          | End of Transmission         | XA             | Transmit Adapter              |

|              |                             |                |                               |

Abbreviation

This manual has been prepared by the IBM Systems Development Division Product Publications, Dept. 520, CPO Box 120, Kingston, N.Y., 12401. Address comments concerning the manual to this address.

(C) International Business Machines Corporation 1967

#### CONTENTS

| CHAPTER 1 INTRODUCTION                   | •     | •  | •   | • | • | 1-1          |

|------------------------------------------|-------|----|-----|---|---|--------------|

| Scope of Manual                          | •     | •  | •   | • | • | 1-1          |

| IBM 2848 Display Control, General Descri | iptio | on | •   | • | • | 1-1          |

| IBM 2848 Display Control, Model 1 .      | •     | •  | •   | • | • | 1-2          |

| IBM 2848 Display Control, Model 2 .      | •     | •  | •   | • | • | 1-2          |

| IBM 2848 Display Control, Model 3 .      | •     | •  | •   | • | • | 1-3          |

| IBM 2848 Model Summary                   | •     | •  | •   | • | • | 1-3          |

| Special 2848 Features                    | •     | •  | •   | • | • | 1-3          |

| Operator Controls and Indicators         | •     | •  | •   | • | • | 1-3          |

| CE Panel                                 | •     | •  | •   | • | • | 1-3          |

| IBM 2260 Display Station, General Descri | ptic  | n  | •   | • | • | 1-3          |

| Special Features • • • • • • •           | •     | •  | •   | • | • | 1-6          |

| Feature 4766 Alphanumeric Keyboa         | rd    | •  | •   | • | • | 1-6          |

| Feature 4767 Numeric Keyboard .          | •     | •  | •   | • | • | 1-6          |

| Control Key Functions • • • • •          | •     | •  | •   | • | • | 1-6          |

| Functional Description                   | •     | •  | •   | • | • | 1-6          |

| IBM 2848-2260 Display Complex • •        | •     | •  | •   | • | • | 1-6          |

| IBM 2848 Display Control • • • •         | •     | •  | •   | • | • | 1-8          |

| Channel Adapter • • • • • •              | •     | •  | •   | • | • | 1-8          |

| IBM 2848 Common • • • • •                | •     | •  | •   | • | • | 1-11         |

| 1053 Printer Adapter • • • • •           | •     | •  | •   | • | • | 1-12         |

| Control and Timing • • • • •             | •     | •  | •   | • | • | 1-13         |

| IBM 2260 Display Station                 | •     | •  | •   | • | • | 1-13         |

| System/360 - Channel Adapter Interface   |       |    |     | • | • | 1-14         |

| General                                  | •     | •  |     | • | • | 1-14         |

| Line Description                         | •     |    |     | • | • | 1-14         |

| Bus Out                                  | •     |    |     | • | • | 1-14         |

| Bus In                                   |       | •  |     |   |   | 1-17         |

| Operational Out                          | •     |    |     | • | • | 1-17         |

| Request In                               |       |    |     |   | • | 1-18         |

| Address Out                              |       |    |     |   | • | 1-18         |

| Select Out • • • • • • • •               |       | •  | •   | • |   | 1-18         |

| Hold Out                                 | •     |    |     |   |   | 1-18         |

| Sele <b>ct</b> In                        |       |    |     |   |   | 1-19         |

| Operational In                           |       |    |     |   |   | 1-19         |

| Address In                               |       |    |     |   |   | 1-19         |

| Command Out                              |       | •  |     |   |   | 1-19         |

| Status In                                | •     |    |     | • |   | 1-19         |

| Service Out                              | •     | •  | •   | • |   | 1-20         |

| Service In                               | •     |    |     | • |   | 1-20         |

| Suppress Out                             |       |    |     |   | • | 1-20         |

| Clock Out                                |       |    |     |   | • | 1-20         |

| Metering In                              | •     | •  | •   | • | • | 1-21         |

| Metering Out                             | •     | •  | •   | • | • | 1-21         |

| Addressing                               | •     | •  | •   | • | • | 1-21         |

| Commands and Command Operation           | •     | •  | •   | • | • | 1-21         |

| Write DS Buffer Storage Command .        | •     | •  | •   | • | • | 1-21         |

| Write 1053 Buffer Storage Command        | •     | •  | •   | • | • | 1-22         |

| Write DS Line Address Command            | •     | •  | •   | • | • | 1-22         |

|                                          | •     | •  | • . | • | • |              |

| Read DS MI (Manual Input) Command        | •     | •  | •   | • | • | 1-23<br>1-24 |

| Short Read DS MI Command                 | •     | •  | •   | • | • | 1-24<br>1-25 |

| Read Full DS Buffer Command              | •     | •  | •   | • | • |              |

| No Op (No Operation) Command             | •     | •  | •   | • | • | 1-25         |

| Erase DS Buffer Storage Command .        | •     | •  | •   | • | • | 1-25         |

| Sense Command                            | •     | •  | •   | • | • | 1-25         |

| Test I/O Command        | •    | •    | •    | •    | •  | •     | •   | •    | •   | •    | • | 1-25 |

|-------------------------|------|------|------|------|----|-------|-----|------|-----|------|---|------|

| Interleave Read .       | •    | •    | •    | •    | •  | •     | •   | •    | •   | •    | • | 1-25 |

| Channel-Display Compl   | ex   | - 5  | lequ | enc  | ce | and   | Re  | espc | nse | es   | • | 1-26 |

| Stop Sequence           | •    | •    | •    | •    | •  | •     | •   | •    | •   | •    | • | 1-26 |

| Interface Disconnect    | Se   | que  | ence |      | •  | •     | •   | •    | •   | •    | • | 1-26 |

| Selective Reset Sequ    | en   | ce   | •    | •    | •  | •     | •   | •    | •   | •    | • | 1-26 |

| Read Operation          | •    | •    | •    | •    | •  | •     | •   | •    | •   | •    | • | 1-26 |

| Write Operation         | •    | •    | •    | •    | •  | •     | •   | •    | •   | •    | • | 1-26 |

| System Reset Sequen     | ce   |      | •    | •    | •  | •     | •   | •    | •   | •    | • | 1-26 |

| Short Control Unit Bu   | ısy  | See  | quei | ıce  | •  |       | •   | •    | •   | •    | • | 1-27 |

| Sense and Status Bytes  | •    |      |      |      | •  |       |     |      | •   | •    | • | 1-27 |

| Sense Byte              |      | •    |      | •    | •  | •     | •   | •    |     | •    |   | 1-27 |

| Status Byte 🛛 🔒 🔸       | •    |      |      | •    | •  | •     | •   | •    |     | •    | • | 1-27 |

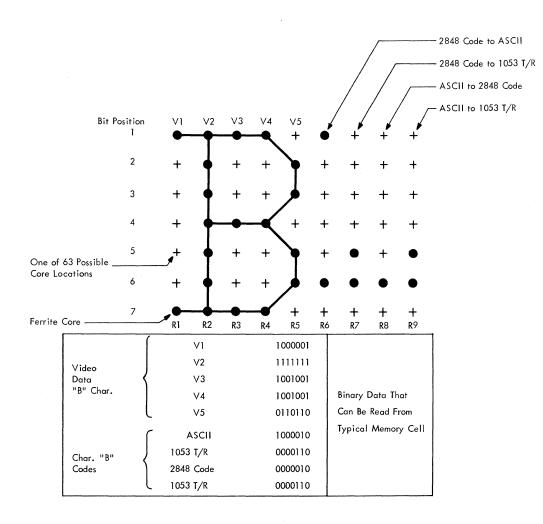

| Character Codes and Dis | spla | iya  | ble  | Syı  | nb | ols   | •   | •    | •   | •    | • | 1-28 |

| Displayable Symbols     |      | •    |      | •    |    |       |     |      |     |      |   | 1-28 |

| EBCDIC Code             | •    |      |      |      | •  |       |     |      |     |      | • | 1-29 |

| Keyboard Code .         |      |      |      |      |    |       |     |      |     |      | • | 1-30 |

| Internal 2848 Six-Bit   | вс   | D    | Cod  | e    |    |       |     |      |     |      | • | 1-30 |

| 1053 Printer Code .     |      |      |      |      |    |       |     |      |     |      |   | 1-31 |

| Terms and Definitions   |      |      |      |      |    |       |     |      |     |      |   | 1-31 |

|                         |      |      |      |      |    |       |     |      |     |      |   |      |

| CHAPTER 2 FUNCTION      |      |      | NUI  |      | •  | •     | •   | •    | •   | •    | • | 2-1  |

| Introduction            |      | •    | •    | •    | •  | •     | •   | •    | •   | •    | • | 2-1  |

| IBM 2260 Display Statio |      | •    | •    | •    | •  | •     | •   | •    | •   | •    | • | 2-1  |

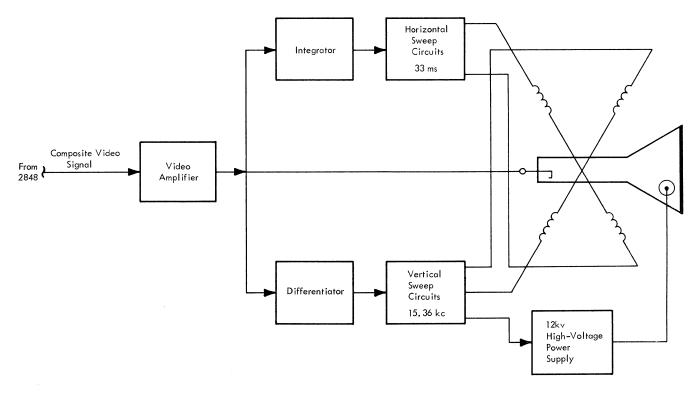

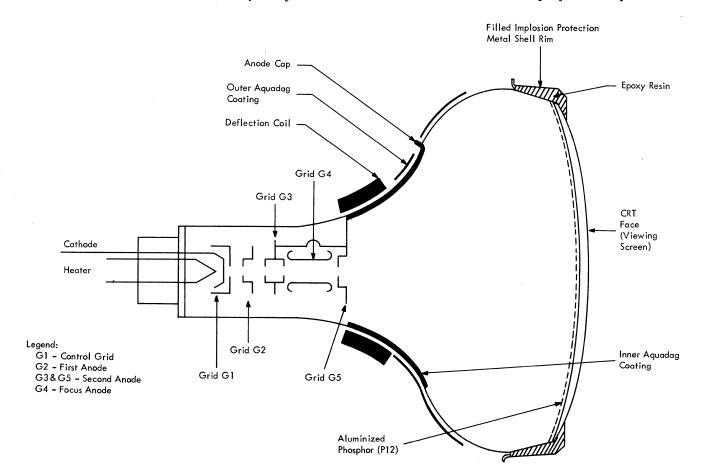

| Cathode-Ray Tube        |      | •    | •    | •    | •  | •     | •   | •    | •   | •    | • | 2-3  |

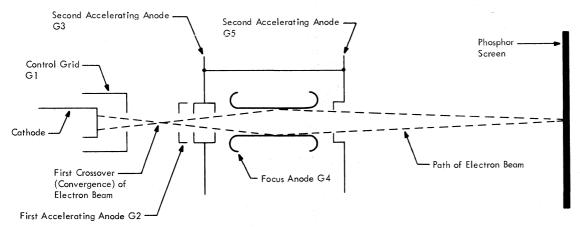

| Eelctron Gun            | •    | •    | •    | •    | •  | •     | •   | •    | •   | •    | • | 2-4  |

| Beam Focusing           | •    | •    | •    | •    | •  | •     | •   | •    | •   | •    | • | 2-4  |

| Deflection Yoke A       | Ass  | eml  | oly  | •    | •  | •     | •   | •    | •   | •    | • | 2-5  |

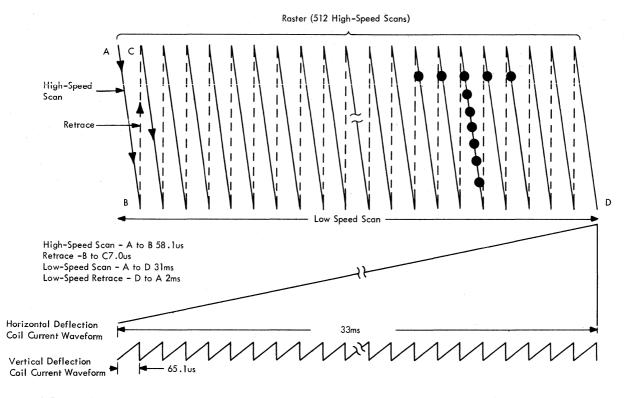

| Raster                  | •    | •    | •    | •    | •  | •     | •   | •    | •   | •    | • | 2-5  |

| Correction Mag          | -    | ets  | •    | •    | •  | •     | •   | •    | •   | •    | • | 2-5  |

| Centering Ring          | -    | •    | •    | •    | •  | •     | •   | •    | •   | •    | • | 2-5  |

| Tilting                 |      | •    | •    | •    | •  | •     | •   | •    | •   | •    | • | 2-5  |

| Aquadag Coating         |      | ٠    |      | •    | •  | •     | •   | •    | •   | •    | • | 2-6  |

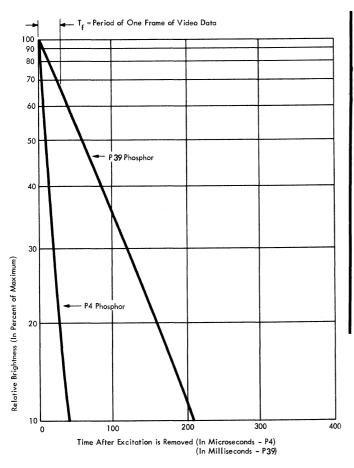

| Screen Phosphors        | •    | ٠    |      |      |    | •     | •   | •    | •   |      | • | 2-6  |

| CRT Electrode Po        |      |      |      | •    | •  |       | •   | •    |     |      | • | 2-7  |

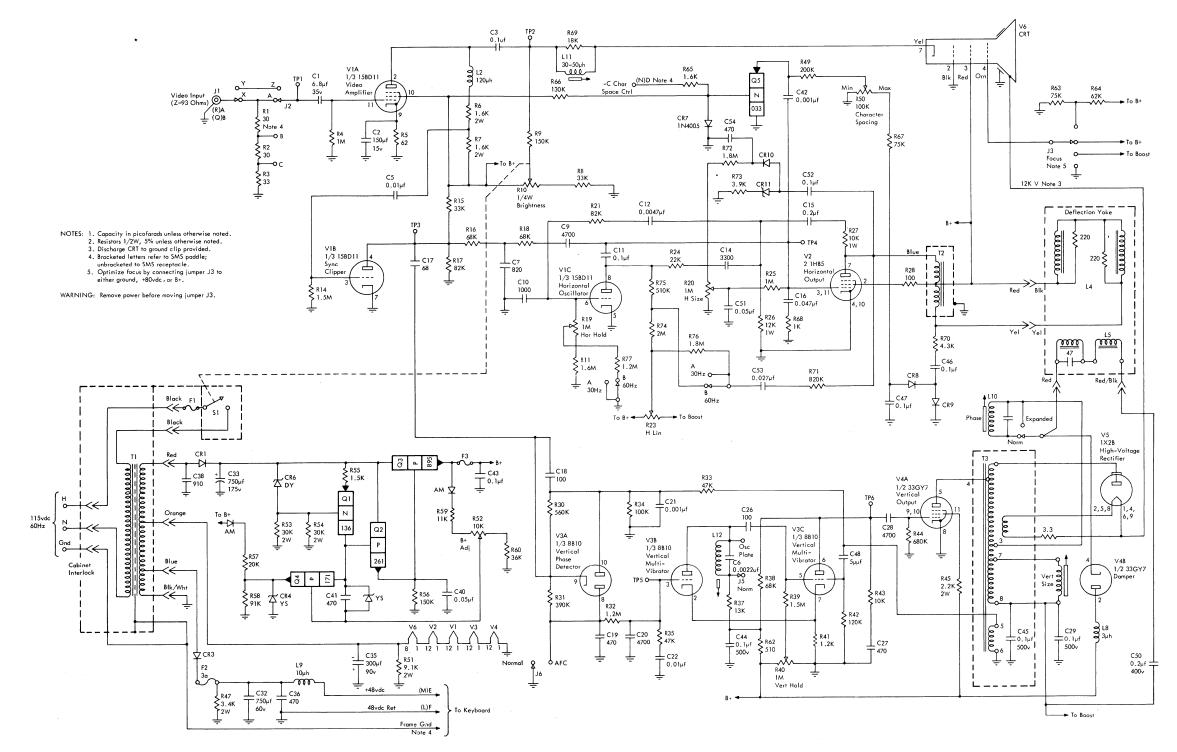

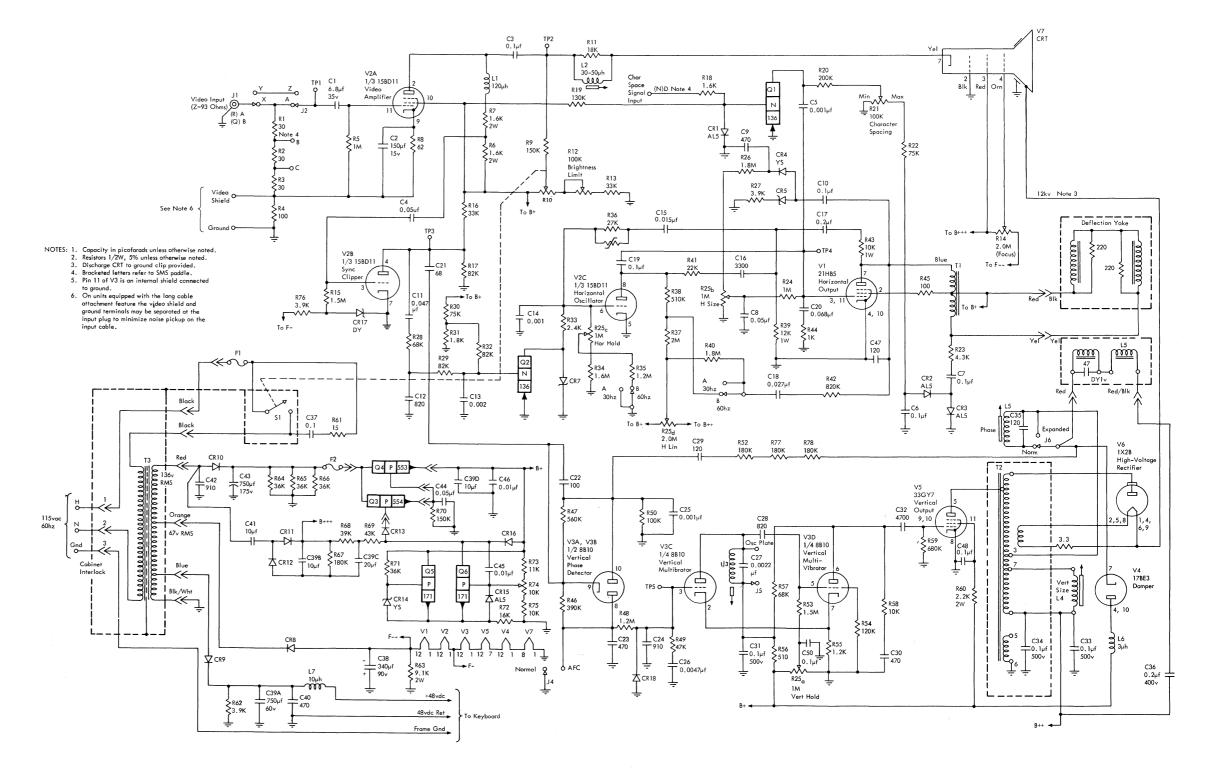

| Display Station Elect   | ror  |      |      | D2   | U  | sing  | 01  | .aer | Le  | ever |   | 2-7  |

| Circuit Boards • •      | •    | •    |      | •    | •  | •     | •   | ·    | •   | •    | • | 2-7  |

| Video Amplifier         |      | •    |      | •    | •  | •     | •   | •    | :   | •    | • | 2-7  |

| Sync Clipper .          |      | •    | •    | •    | •  | •     | •   | •    | •   | •    | • |      |

| Horizontal Multivi      |      |      |      | •    | •  | •     | •   | •    | •   | •    | • | 2-8  |

| Vertical Phase De       |      |      |      | •    | •  | •     | •   | •    | •   | •    | • | 2-11 |

| Vertical Multivib       |      |      | •    | •    | •  | •     | •   | •    | •   | •    | • | 2-11 |

| Vertical Output C       |      |      |      | •    | •  | •     | •   | •    | •   | •    | • | 2-12 |

| High-Voltage Rec        | ctif | ier  |      | •    | •  | •     | •   | •    | •   | •    | • | 2-12 |

| Damper Circuit          | •    | •    | •    | •    | •  | •     | •   | :    | •   | •    | • | 2-12 |

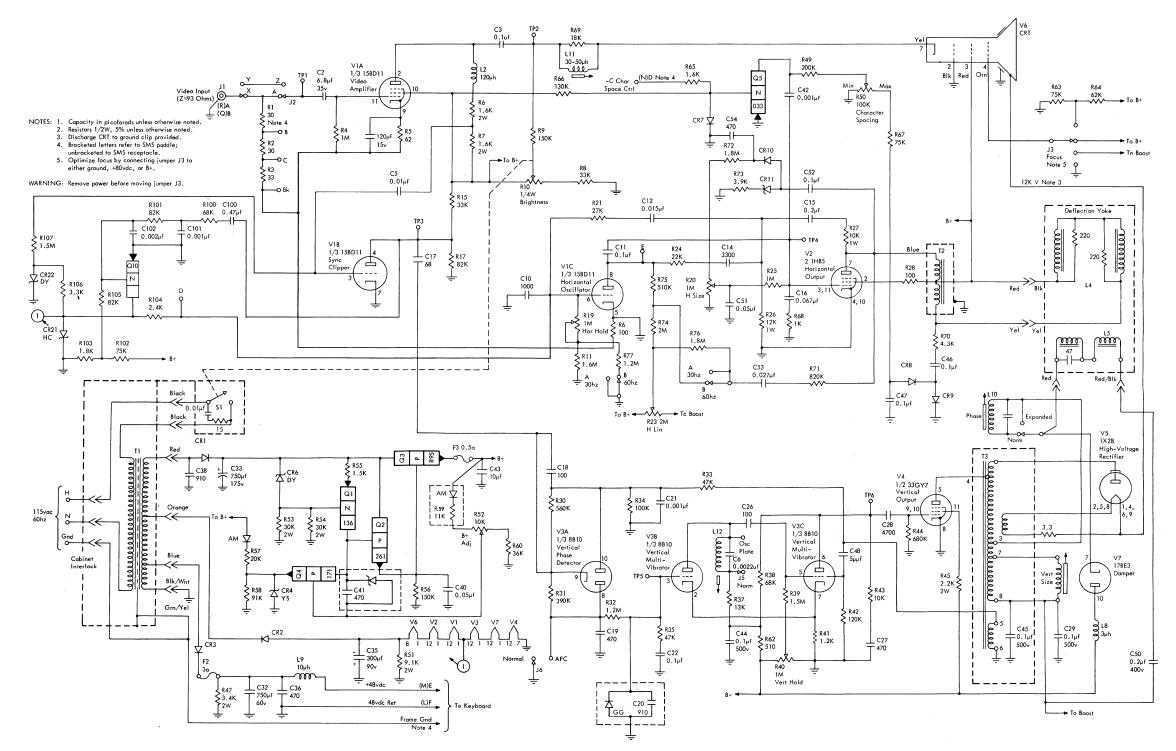

| Display Station Elect   | ror  | nics | for  | DS   | υ  | sing  | Ti  | ube  |     |      |   |      |

| Adapters                | •    | •    | •    | •    | •  | •     | •   | •    | •   | •    | • | 2-13 |

| Display Station Elect   | ror  | nics | for  | DS   | υ  | sing  | N   | ewe  | r   |      |   |      |

| Level Circuit Boards    |      | •    | •    | •    | •  | •     | •   | •    | •   | •    | • | 2-13 |

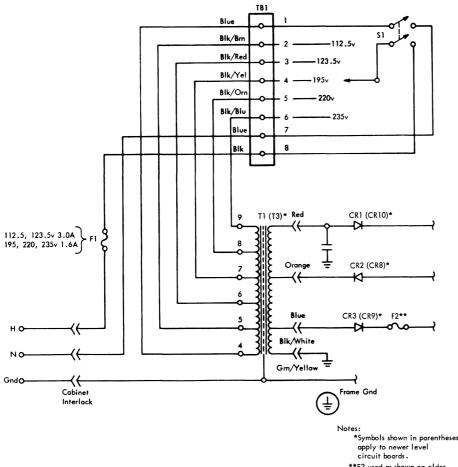

| Display Station Powe    |      |      | •    |      | •  | ·     | •   | •    | •   | •    | • | 2-13 |

| B+ Supply for DS        | Usi  | ng   | Old  | er I | Le | vel ( | Cir | cuit | t   |      |   |      |

| Boards                  | •    | •    | •    | •    | ·  | •_    | •   | •    | •   | •    | • | 2-14 |

| B+ Supply for DS        | Usi  | ng   | Nev  | ver  | Le | evel  | Ci  | rcui | lt  |      |   | 0.44 |

| Boards                  | •    | •    | ·    | •    | ٠  | • 1   | •   | •    | •   | • 1  | • | 2-14 |

| -84VDC Supply           |      | •    | •    | •    | •  | •     | •   | •    | •   | •    | • | 2-14 |

| +48VDC Supply           | •    | •    | •    | •    | •  | •     | •   | •.   | •   | •    | • | 2-14 |

|                         |      |      |      |      |    |       |     |      |     |      |   |      |

2260/2848 - 60,000S FETOM (3/68) i

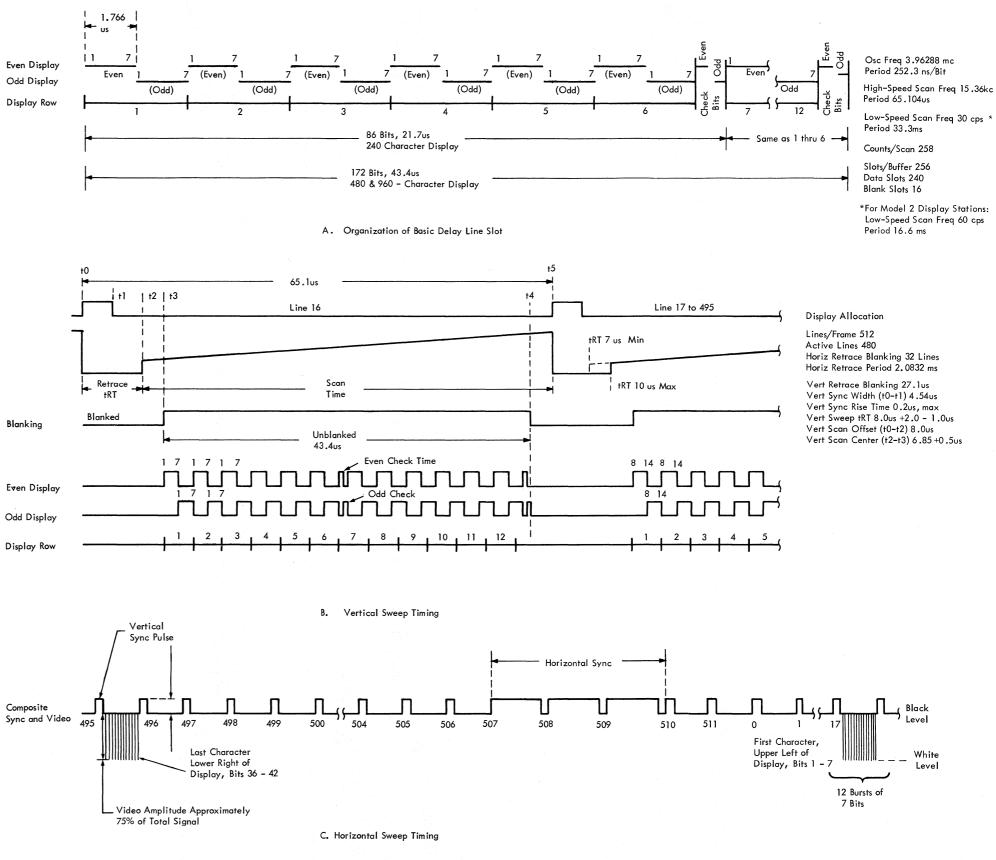

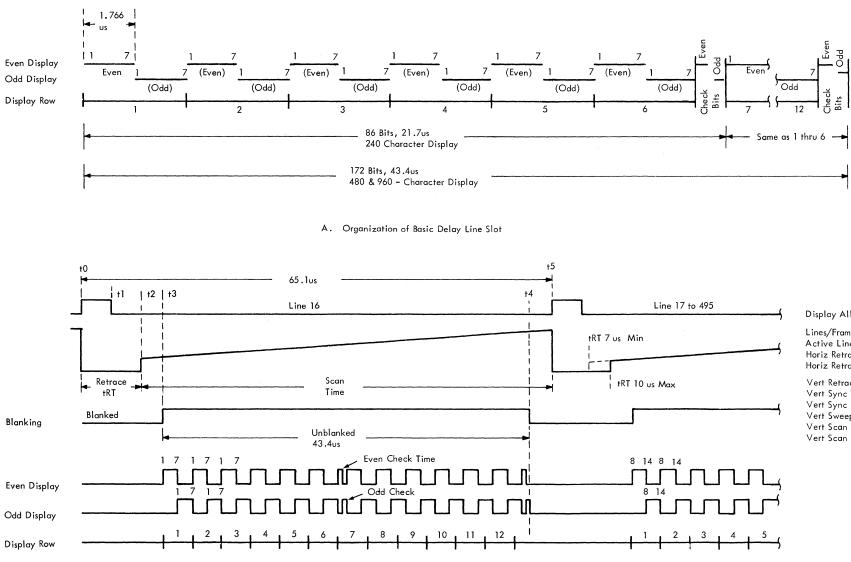

| Display Station Timing                    | •   | •           | 2-14E |

|-------------------------------------------|-----|-------------|-------|

| Organization of Basic Delay Line Slot     | •   | •           | 2-14  |

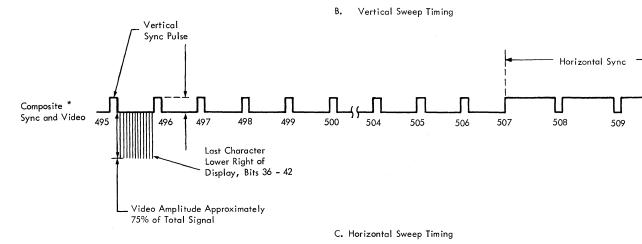

| Vertical Sweep Timing                     | •   | •           | 2-17  |

| Horizontal Sweep Timing                   | •   | •           | 2-17  |

| Manual Input Keyboard                     |     | ." <b>.</b> | 2-17  |

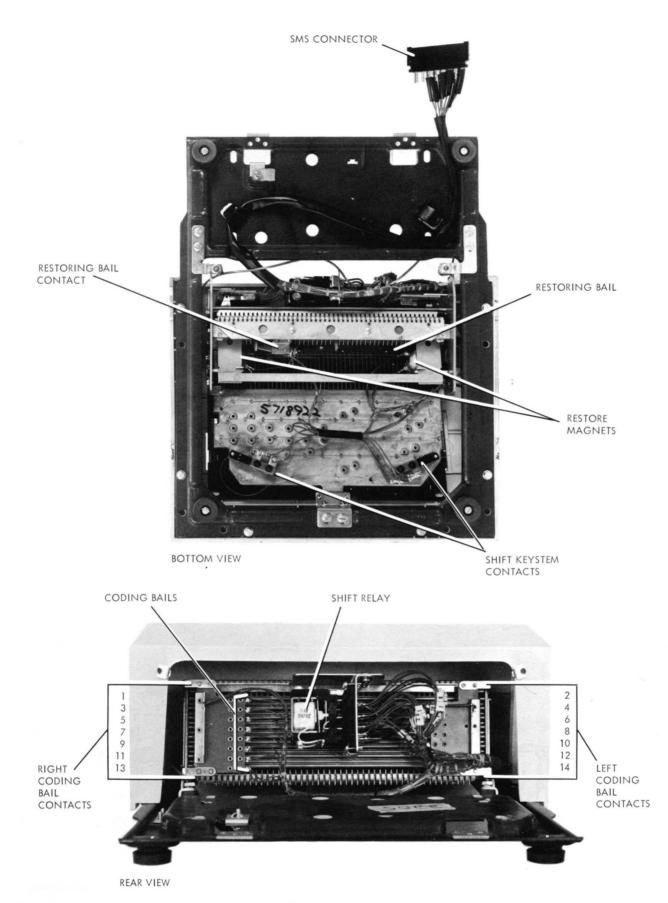

| Description                               | •   | •           | 2-18  |

| Keyboard Mechanics                        | •   | •           | 2-18  |

| Bail Contacts                             | •   | •           | 2-18  |

| Keystem Contacts                          | •   | •           | 2-24  |

| Keyboard Restoring Components             | •   | •           | 2-24  |

| Keyboard Interlocks                       | • ' | •           | 2-25  |

| Keyboard Electronics                      |     |             | 2-25  |

| IBM 2848 Display Control                  | •   | •           | 2-27  |

| Display Adapter                           |     |             | 2-29  |

| Delay Line Theory                         |     | •           | 2-29  |

| Description                               |     |             | 2-29  |

| Operation                                 |     |             | 2-29  |

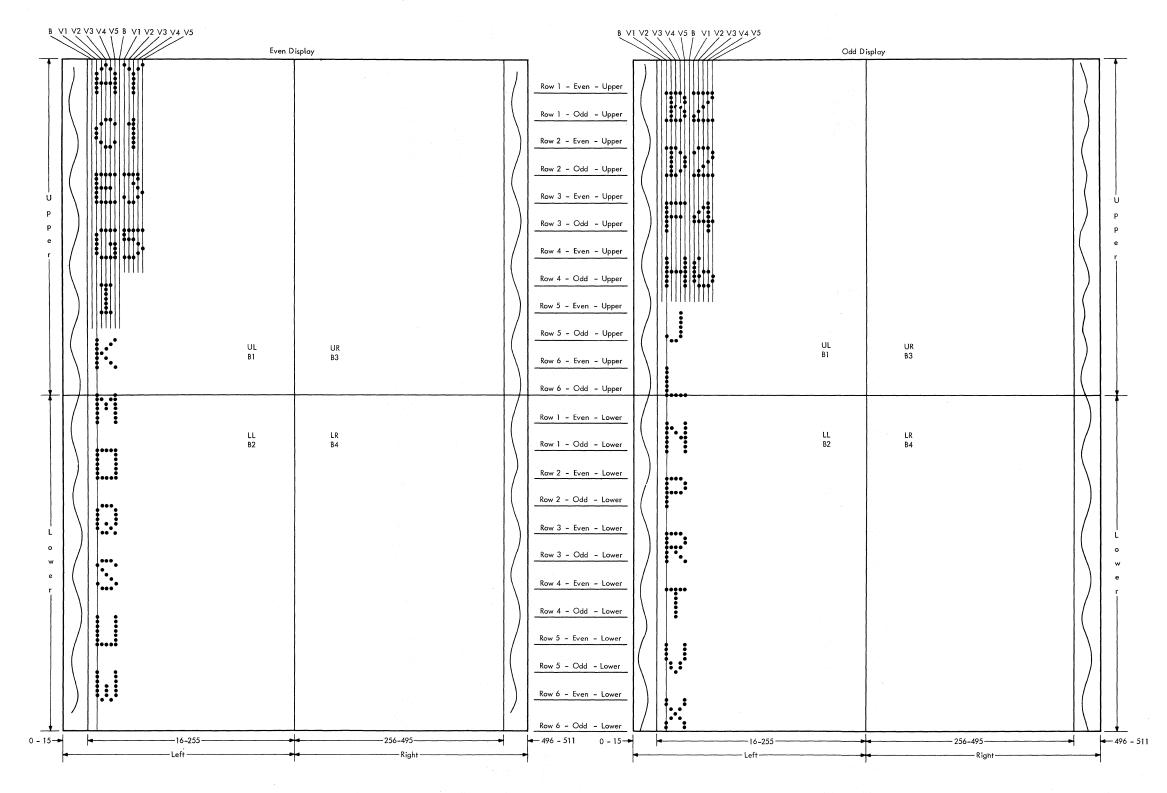

| Delay Line Bit Organization               |     |             | 2-30  |

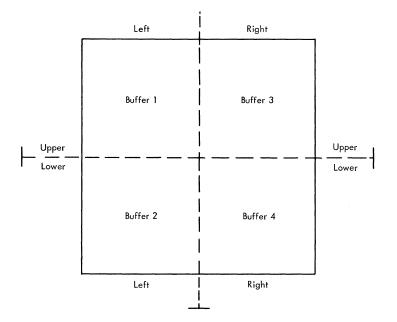

| Buffer Slot Layout                        |     |             | 2-31  |

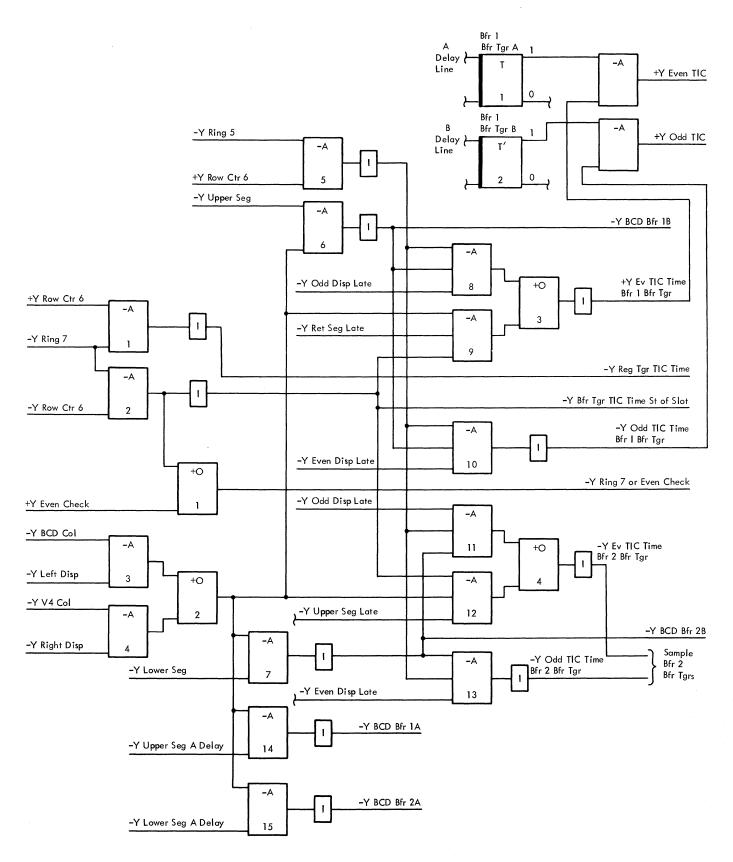

| Delay Line Controls                       |     |             | 2-35  |

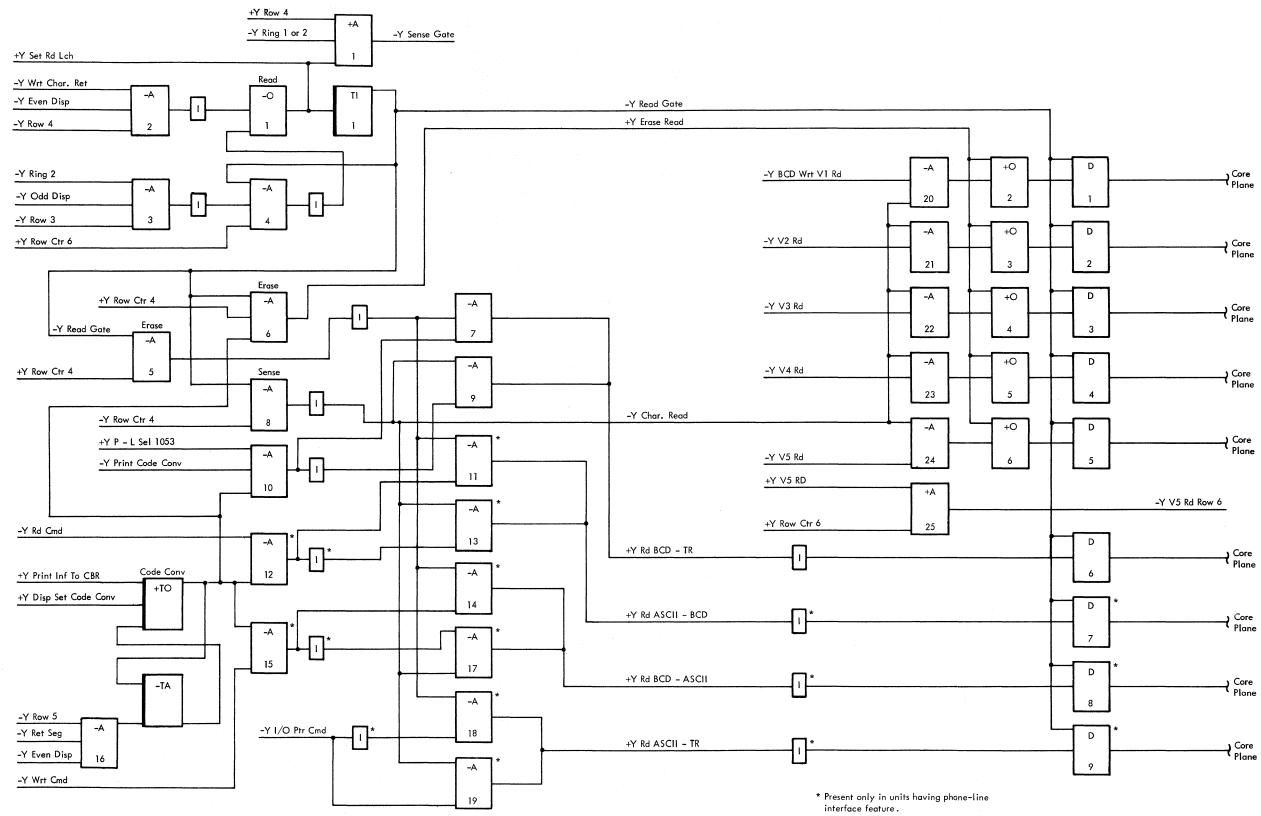

| BCD Data Gating                           |     |             | 2-35  |

|                                           |     |             | 2-35  |

| -                                         | •   | •           | 2-36  |

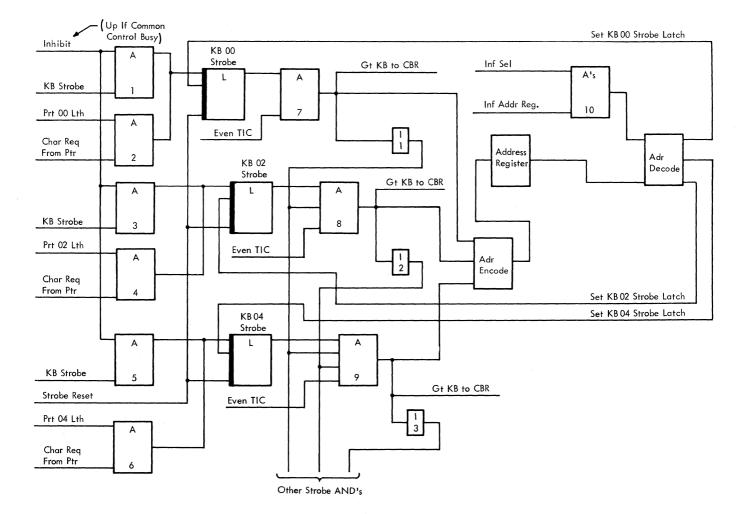

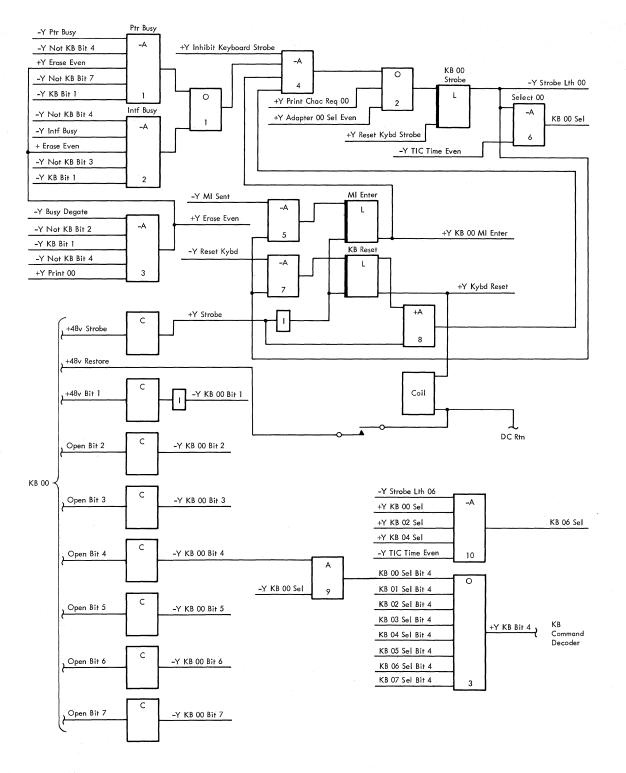

| Keyboard Operation                        | •   | •           | 2-36  |

| Keyboard Priority                         | •   | •           | 2-30  |

| Keyboard Controls                         | •   | •           |       |

| Keyboard Data Bit Conversion and Gating   | •   | •           | 2-40  |

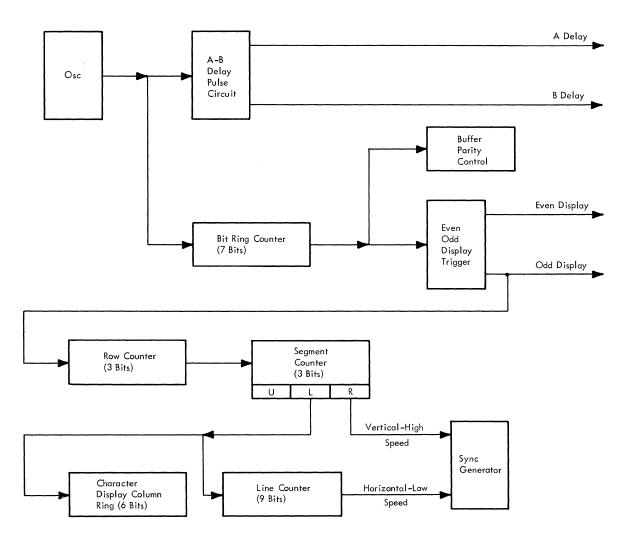

| Timing and Clock Circuits                 | •   | •           | 2-40  |

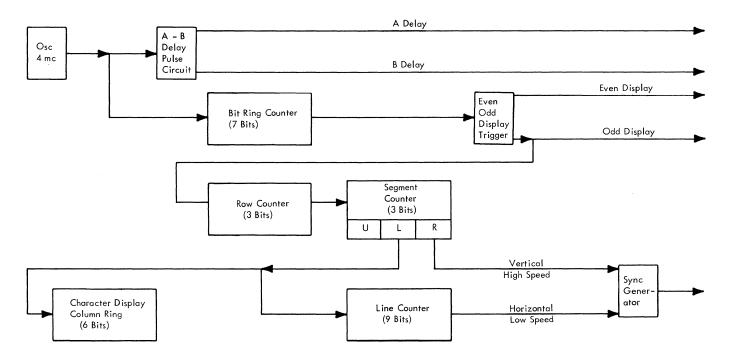

| Oscillator                                | •   | •           | 2-43  |

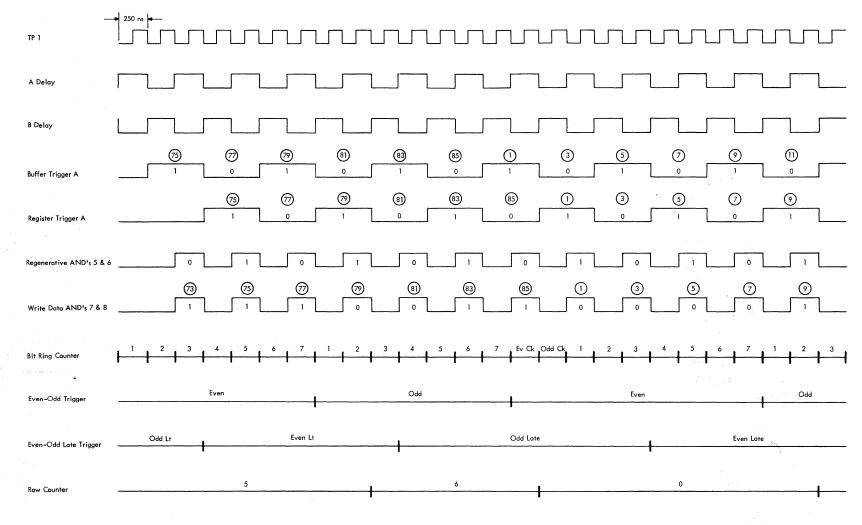

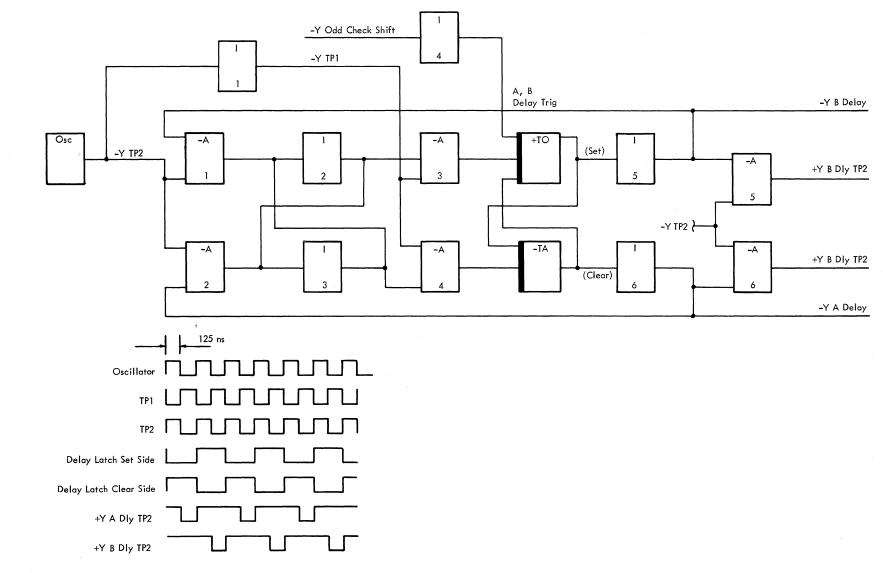

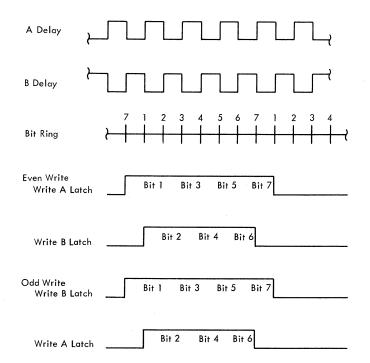

| A and B Delay Pulse Circuit               | •   | •           | 2-45  |

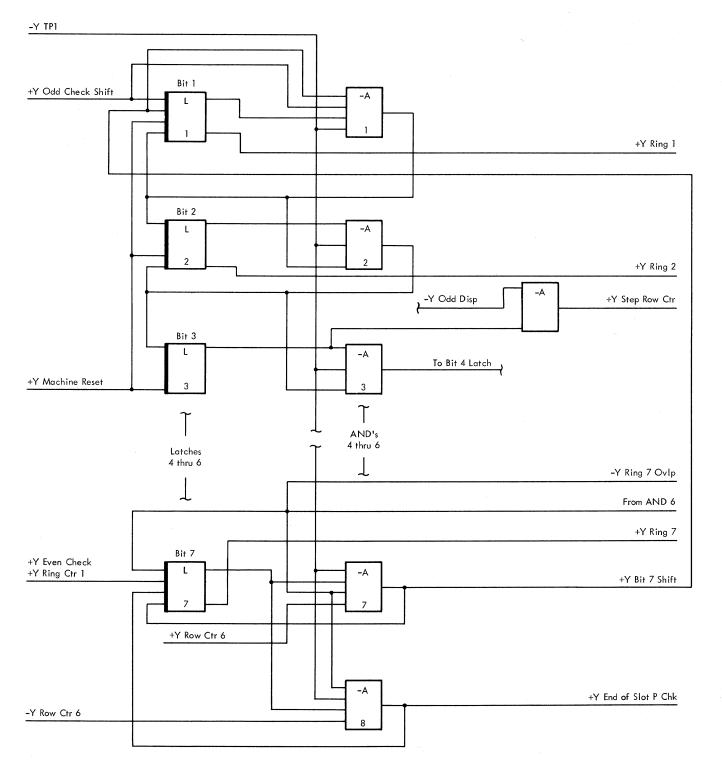

| Bit Ring Counter • • • • • • • •          | •   | •           | 2-45  |

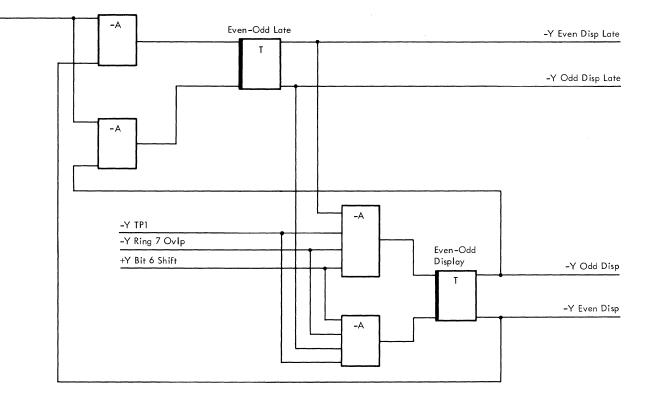

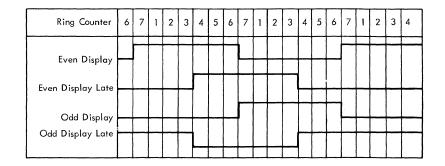

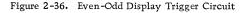

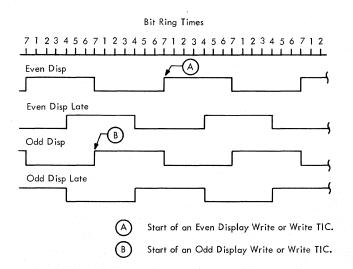

| Even-Odd Display and Late Triggers        | •   | •           | 2-47  |

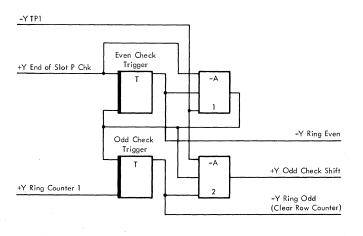

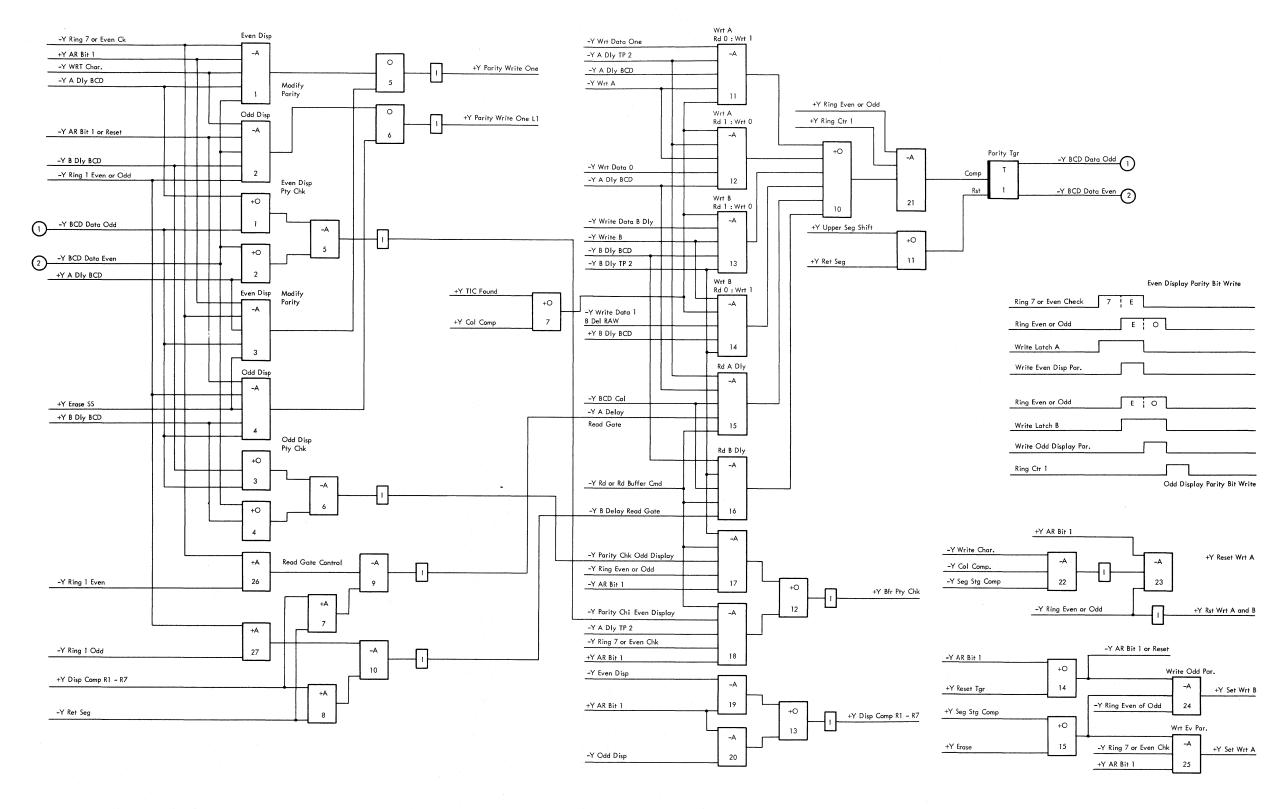

| Buffer Parity Control Circuit             | •   | •           | 2-47  |

| Row Counter • • • • • • • • • •           | •   | •           | 2-50  |

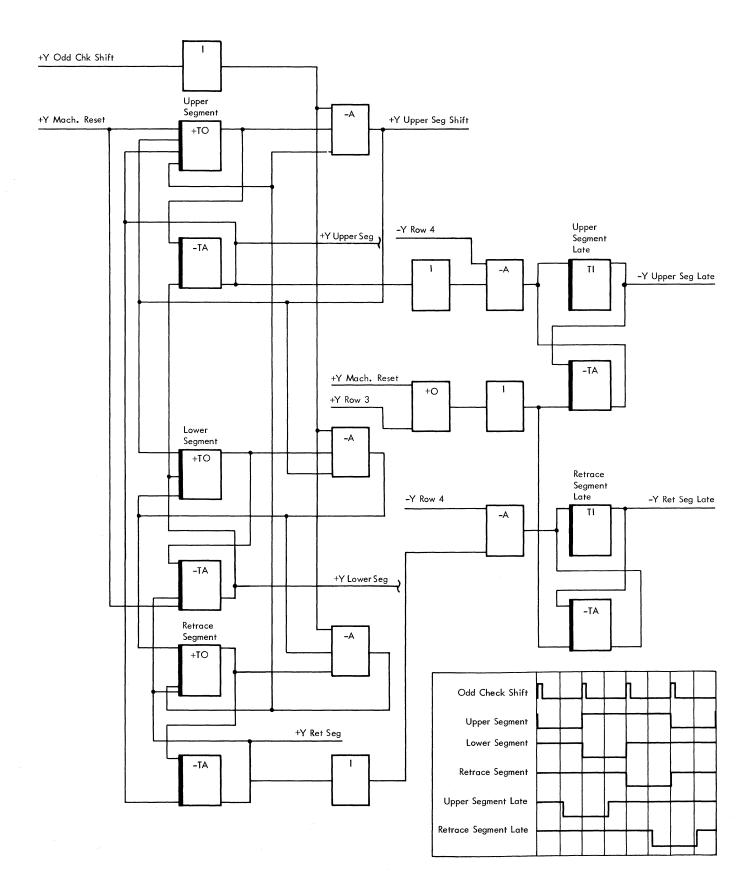

| Segment Counter                           | •   | •           | 2-50  |

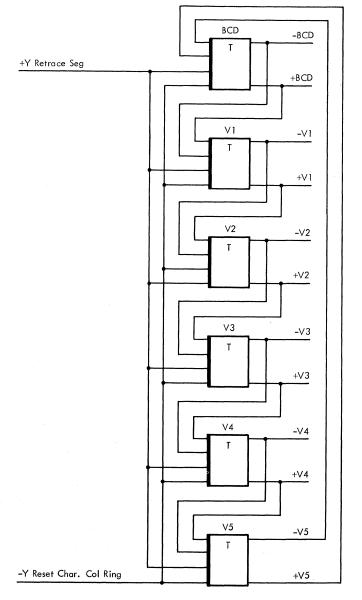

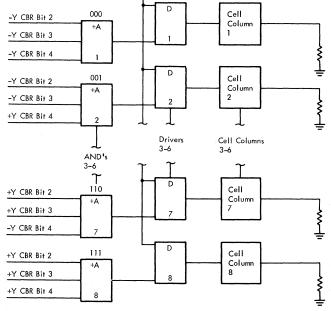

| Character Display Column Ring Counter .   | •   | •           | 2-52  |

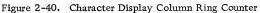

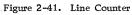

| Line Counter • • • • • • • • •            | •   | •           | 2-52  |

| Sync Generator                            | •   | •           | 2-54  |

| Vertical Sync Generation                  | •   | •           | 2-54  |

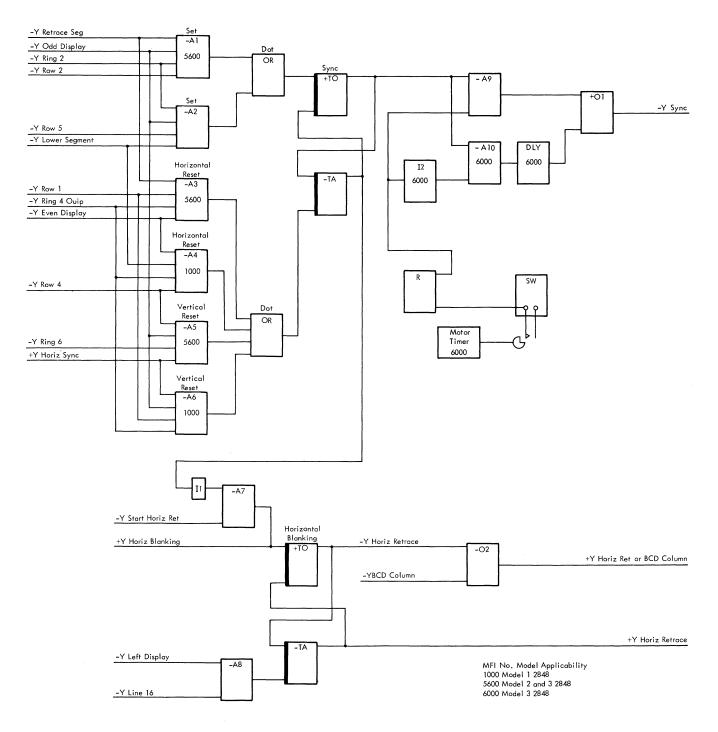

| Horizontal Sync Generation                | •   | •           | 2-56  |

| Horizontal Blanking                       | •   | •           | 2-56  |

| Sync Pulse Delay Circuit                  |     | •           | 2-56  |

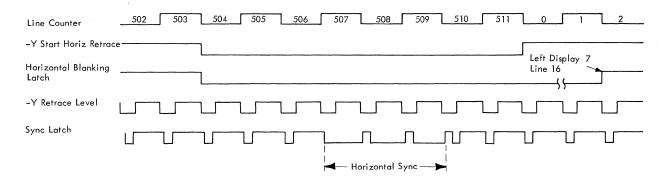

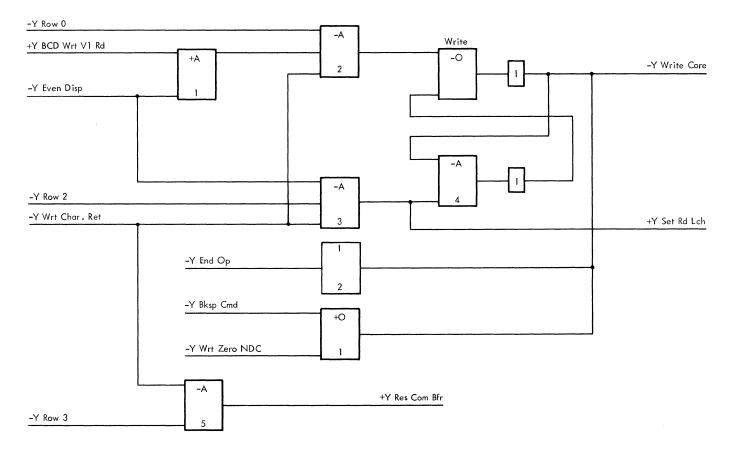

| Reset Controls                            | •   | •           | 2-57  |

| TIC Sample Decoder                        | •   |             | 2-57  |

| General                                   | •   |             | 2-57  |

| Circuit Operation                         | •   | •           | 2-60  |

| BCD Gating Outputs                        | •   |             | 2-62  |

| Character Generator Read Gate Generation. |     | •           | 2-62  |

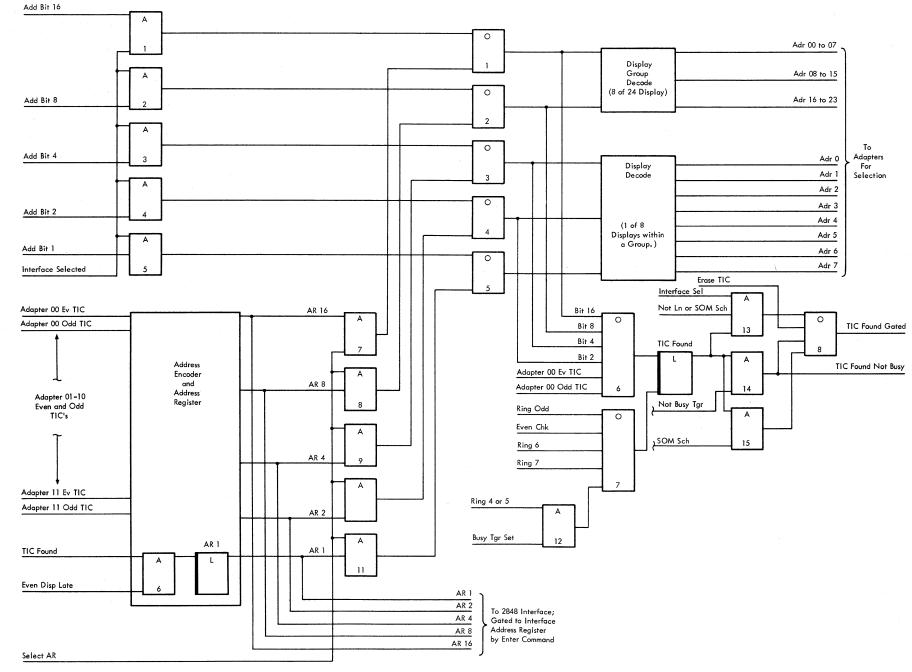

| Display Addressing                        |     |             | 2-62  |

| General                                   |     |             | 2-62  |

| Address Encoder and Address Register      | ·   |             | 2-63  |

| Display Group Decoder                     | •   | •           | 2-63  |

|                                           | •   | •           | 2-65  |

| Display Address Decoder                   | •   | •           |       |

| TIC Found Latch                           | •   | • •         | 2-65  |

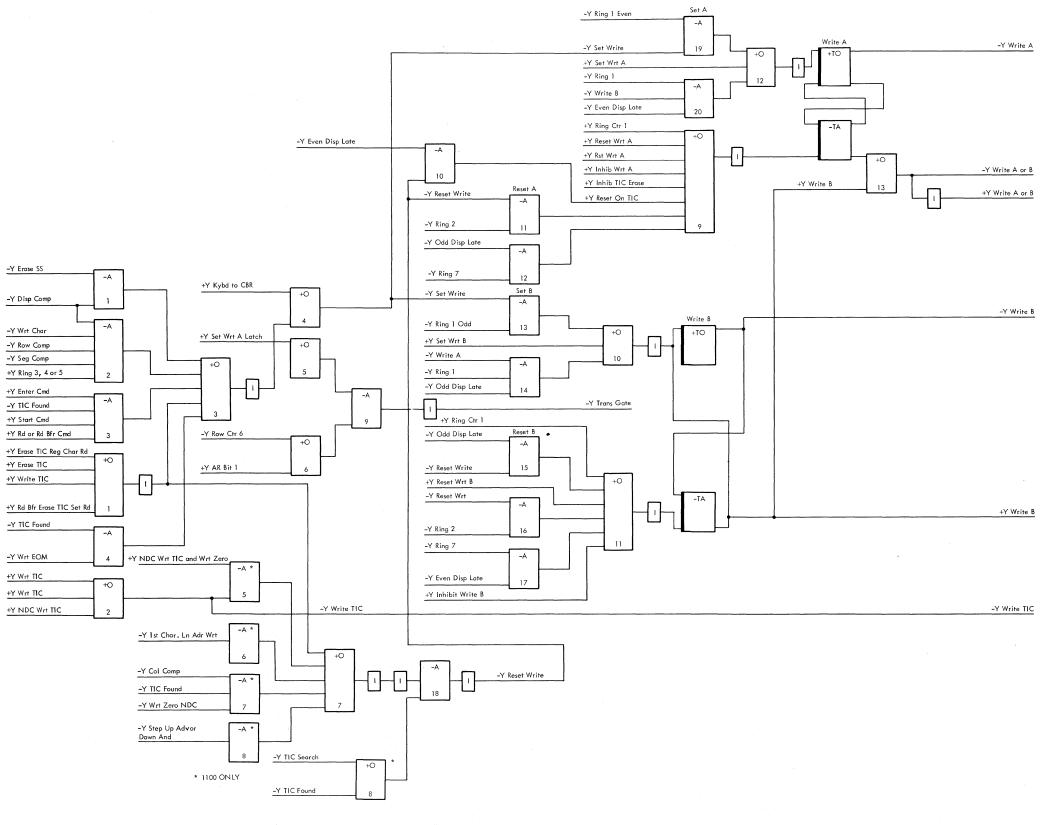

| Write A and Write B Latches               | •   | •           | 2-65  |

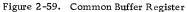

| Keyboard Write Operation                  | •   | •           | 2-66  |

| Erase Operation                           | •   | •           | 2-66  |

| Interface Write Operation                 | •   | •••         | 2-69  |

| TIC Write and Erase Operation • • • •     | •   | •           | 2-69  |

| Write EOM (NDC Only)                   | • |   | 2-69         |

|----------------------------------------|---|---|--------------|

| Other Write Latch Control Signals      |   | • | 2-69         |

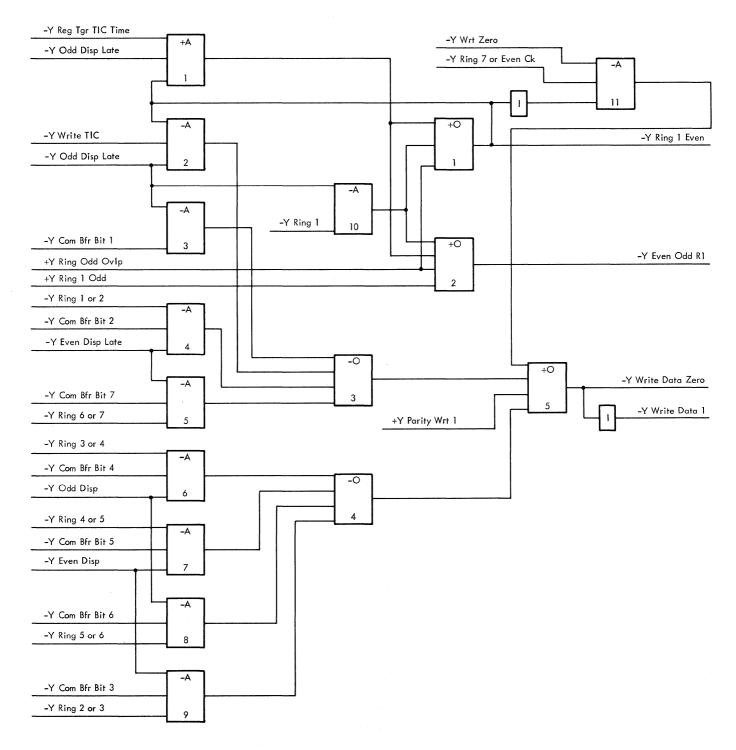

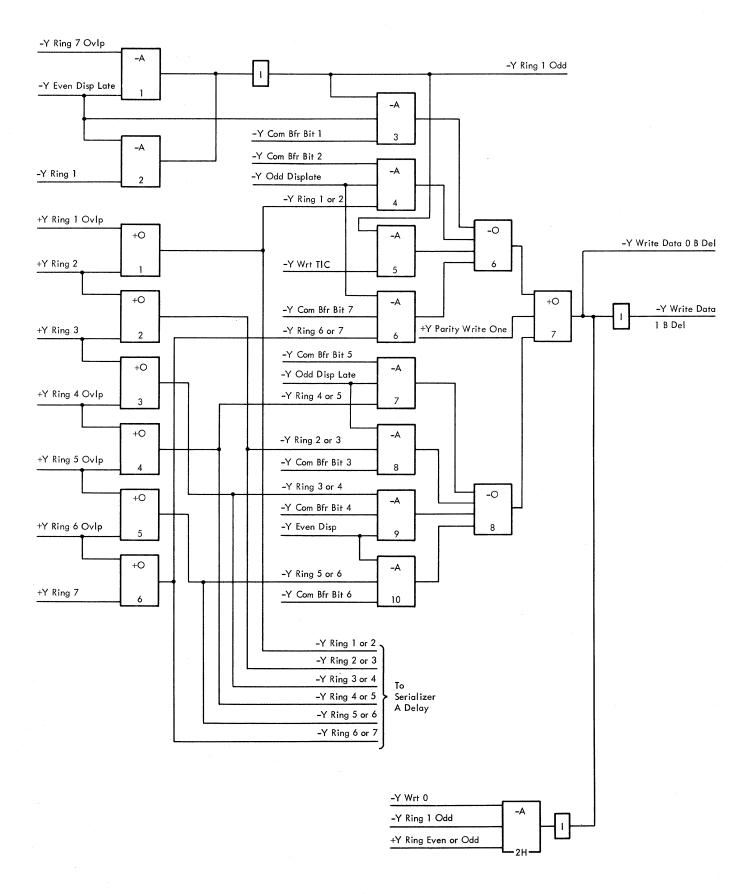

| Serializer                             |   |   | 2-69         |

| Write Data Operation                   |   |   | 2-70         |

| Write TIC Operation                    |   |   | 2-73         |

| Other Write Operations                 | - |   | 2-73         |

| Deserializer                           | • |   | 2-73         |

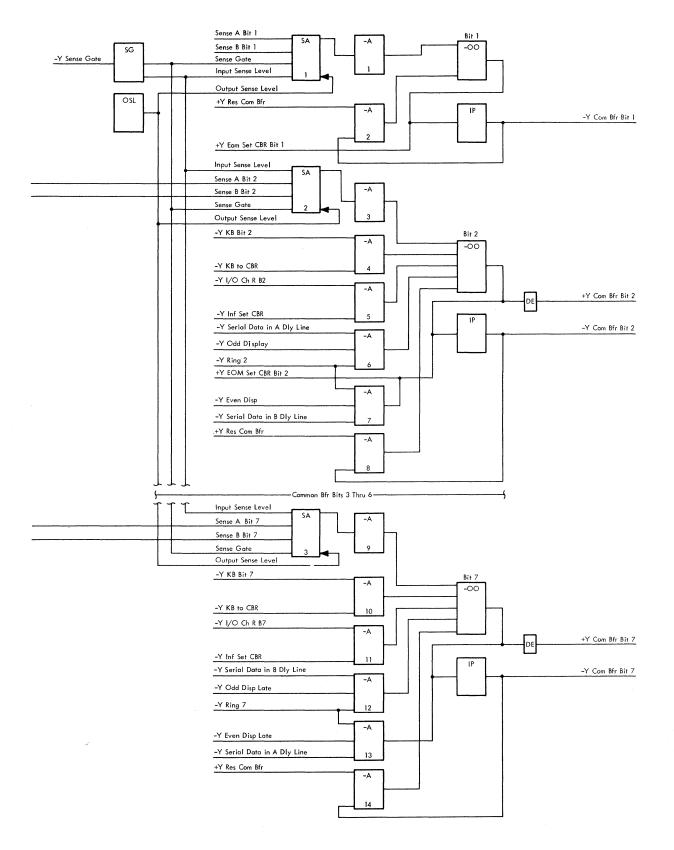

| Common Buffer Register • • • • • • •   | • | • | 2-74         |

| Common Buffer Register Inputs          | • |   | 2-74         |

| Sense Amplifier Inputs                 |   | • | 2-76         |

| End of Message Inputs                  |   | • | 2-76         |

| Keyboard Inputs                        | • | • | 2-76         |

| Interface Inputs                       |   | • | 2-76         |

| Delay Line Inputs                      |   |   | 2-76         |

| Reset Inputs                           |   |   | 2-76         |

| Common Buffer Register Outputs         |   |   | 2-76         |

| Register Control                       |   |   | 2-76         |

| Set EOM                                |   |   | 2-79         |

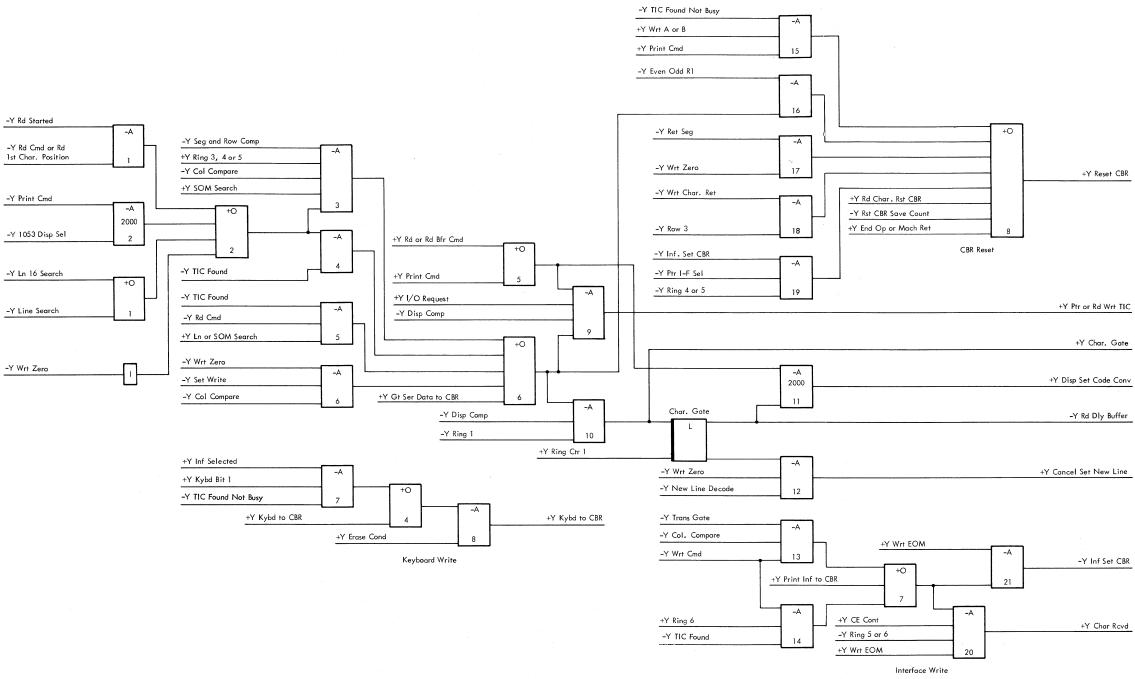

| SOM, New Line, and EOM Decode          | • | • | 2-79         |

| 01                                     | • | • | 2-80         |

| Core Plane                             | • | • | 2-80<br>2-81 |

| Cell Selection                         | • | • | 2-81         |

|                                        | • | • |              |

| Read Winding Connection and Operation  | • | • | 2-82         |

| Sense Winding Connection and Operation | • | • | 2-82         |

| Binary Data Outputs • • • • • • •      | • | • | 2-84         |

| Decoders.                              | • | • | 2-84         |

| Write Control                          | • | • | 2-84         |

| Read Control                           | • | • | 2-84         |

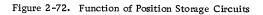

| Position Storage and Compare Logic     | • | • | 2-86         |

| General                                | • | • | 2-86         |

| Counter Storage Control                | • | • | 2-86         |

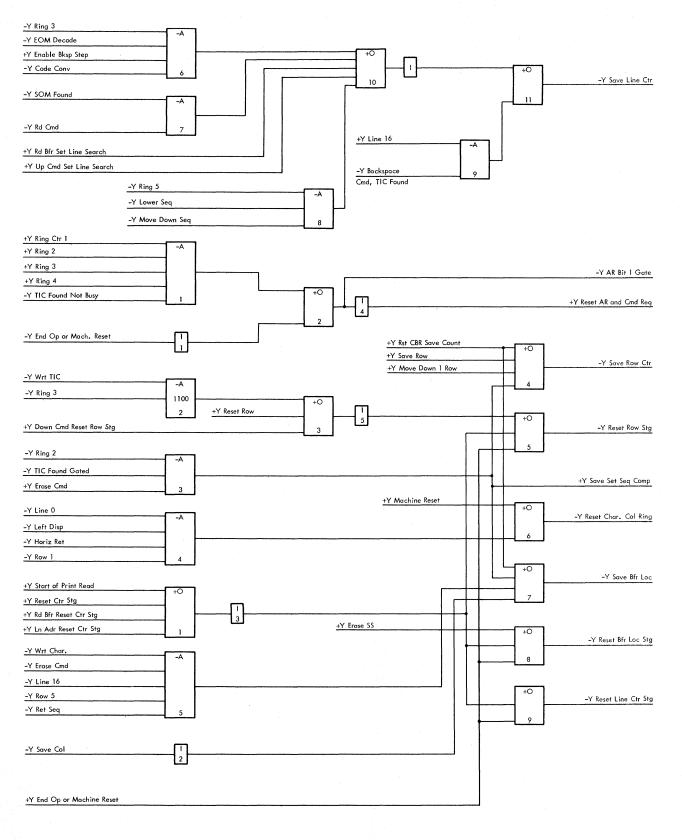

| Row Counter Storage and Compare        | • | • | 2-92         |

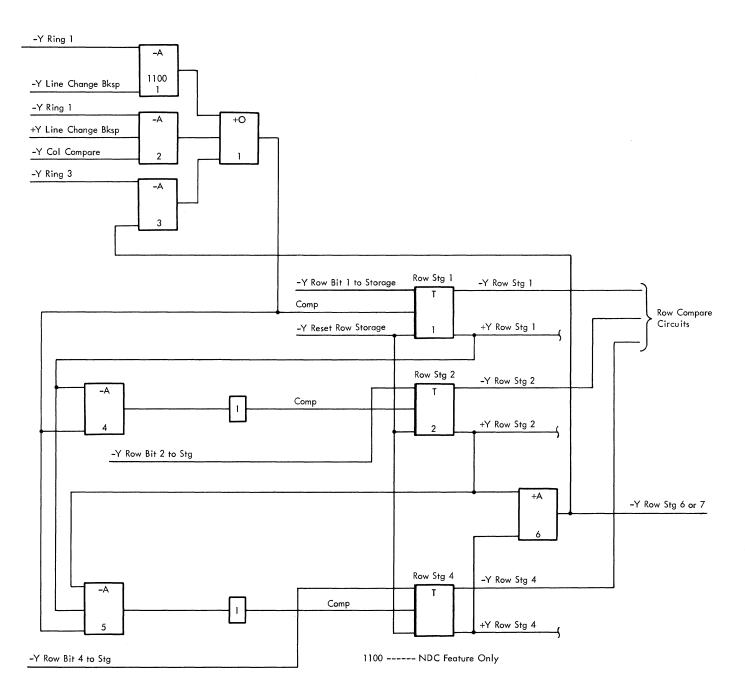

| Segment Storage and Compare • • • •    | • | • | 2-92         |

| Column Storage and Compare             | • | • | 2-92         |

| Line Counter Storage and Compare       | • | • | 2-94         |

| Display Compare                        | • | • | 2-97         |

| Left/Right Storage                     | • | • | 2-97         |

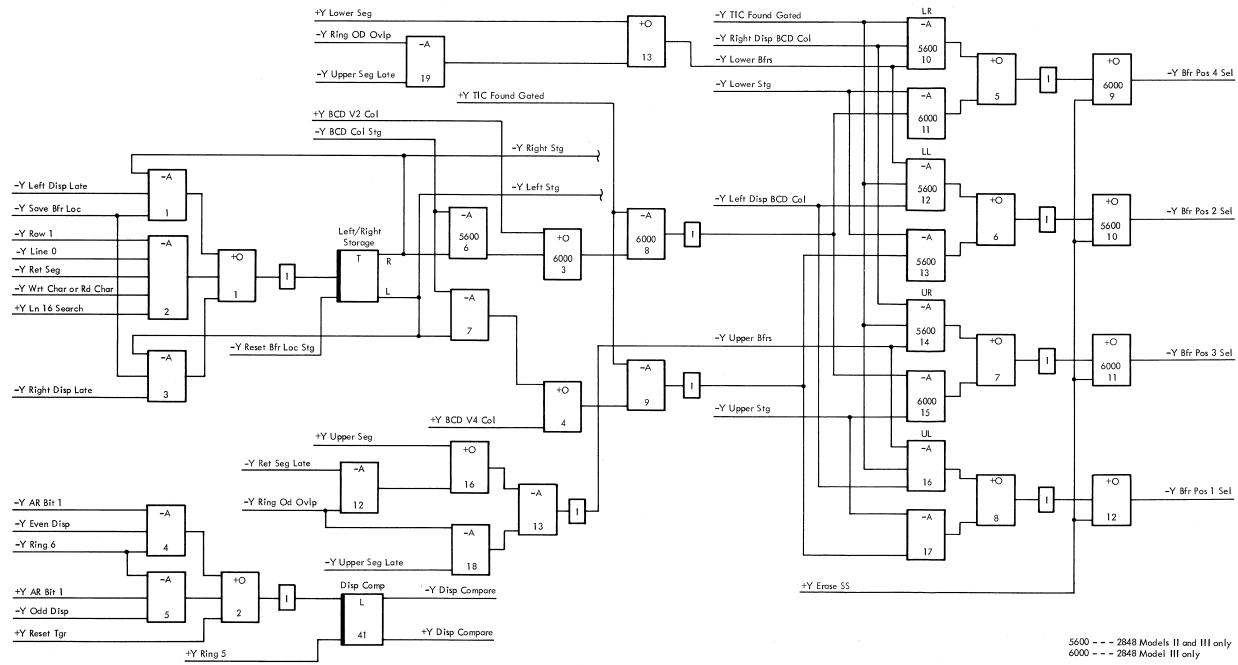

| Buffer Selection Circuits              | • | • | 2-97         |

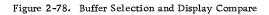

| Video Buffer Selection                 | • | • | 2-98         |

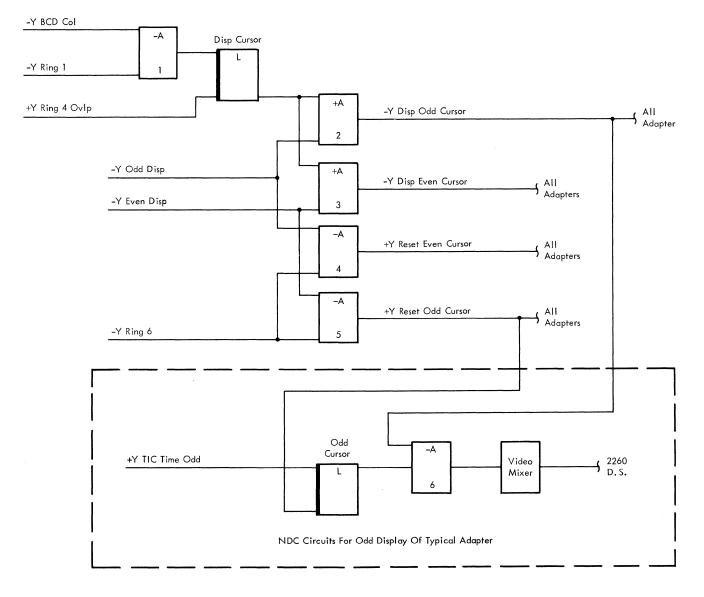

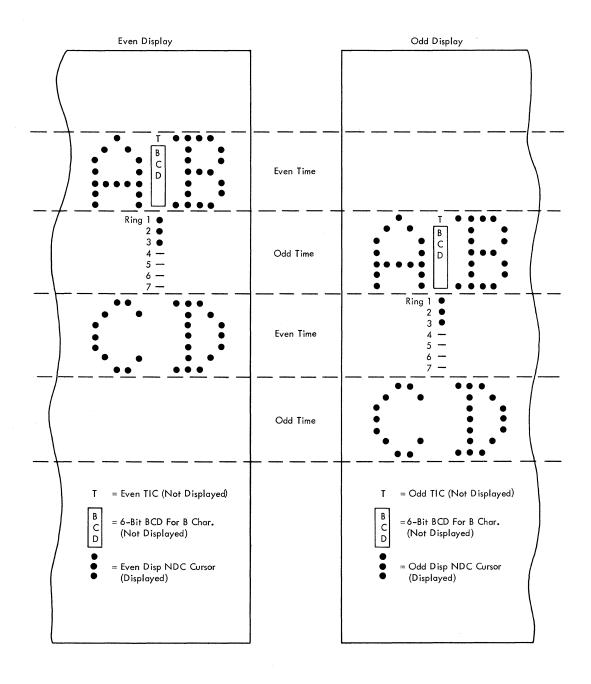

| Nondestructive Cursor Generation       | • | • | 2-101        |

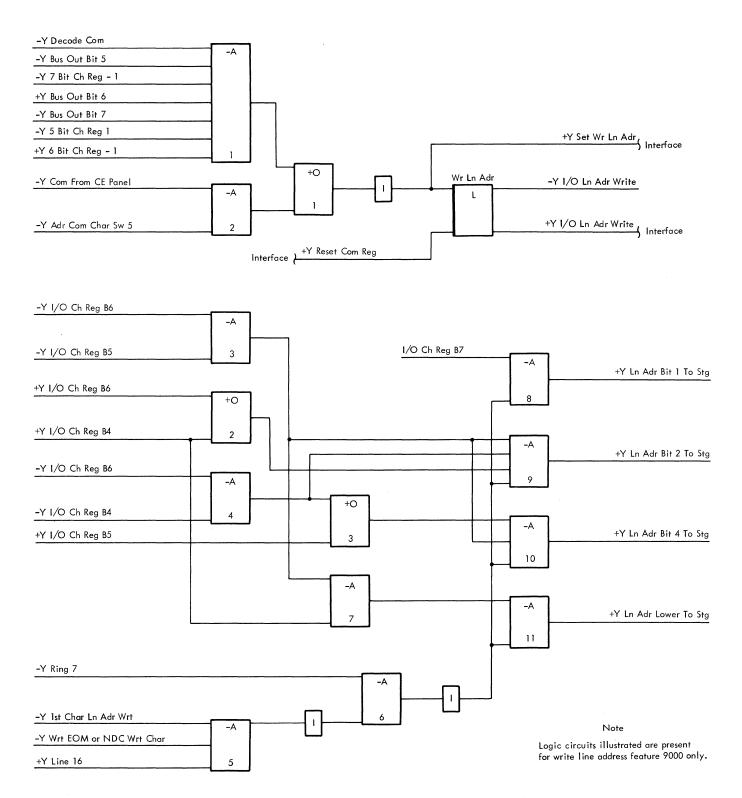

| Write Line Address                     | • | • | 2-102        |

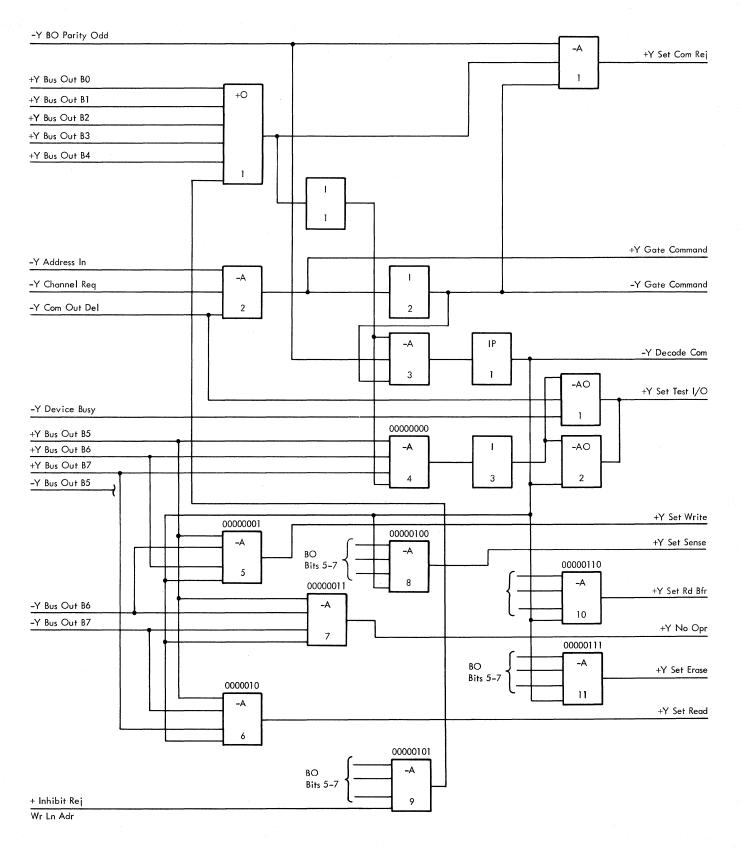

| Command Decode                         | • | • | 2-102        |

| Decoder Operation • • • • • • • • •    |   | • | 2-102        |

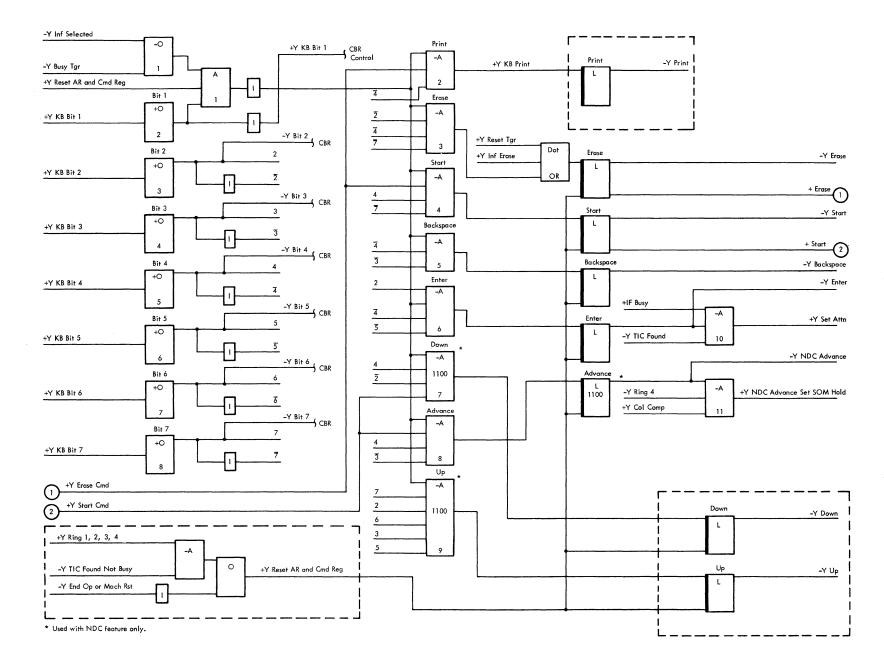

| Keyboard Command Decode                |   | • | 2-103        |

| Parity Control                         |   |   | 2-106        |

| Parity Assignment                      | • | • | 2-106        |

| Parity Update                          | • | • | 2-108        |

| Parity Check                           |   |   | 2-108        |

| Parity Write Control                   |   | • | 2-108        |

| Parity Read Gate Control               | • |   | 2-111        |

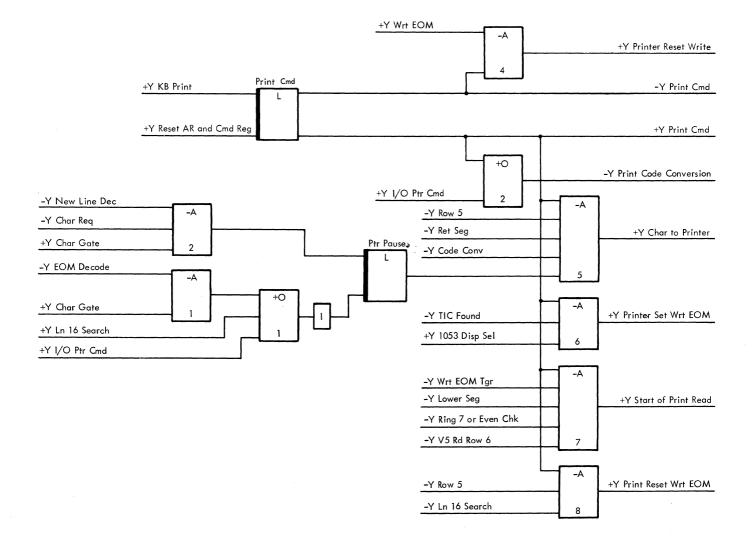

| Printer Adapter Controls               | • | • | 2-111        |

| Control Latches and Triggers           | • |   | 2-112        |

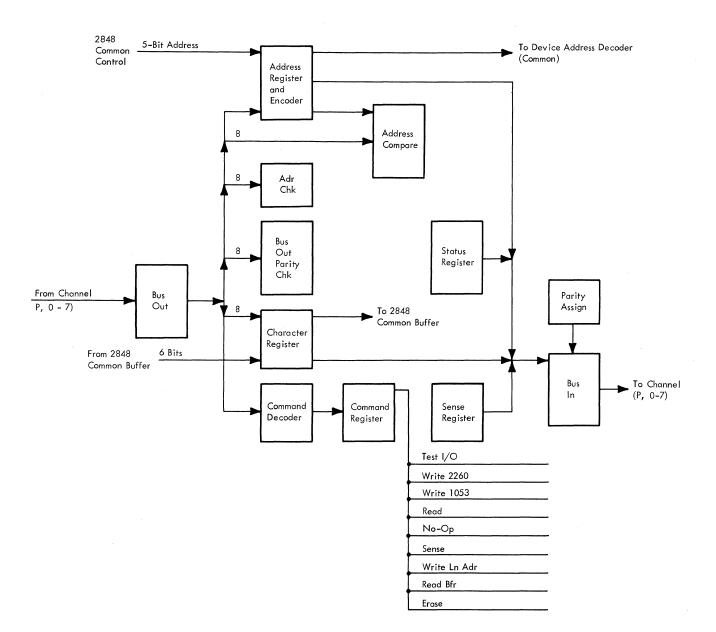

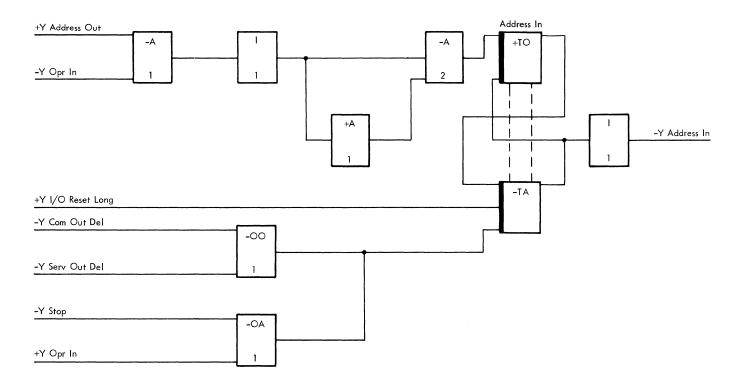

| Channel Adapter                        | • | • | 2-112        |

| Block Diagram Analysis                 |   |   | 2-112        |

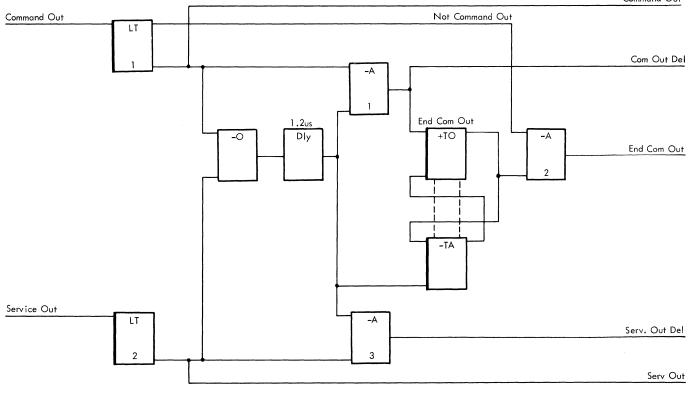

| Out Tag Delays                         |   | • | 2-115        |

| Command Out Delayed                    |   | • | 2-115        |

| Service Out Delayed                    |   | • | 2-116        |

| Control Latches                        | • |   | 2-116        |

|                                        |   |   | - 1 - E      |

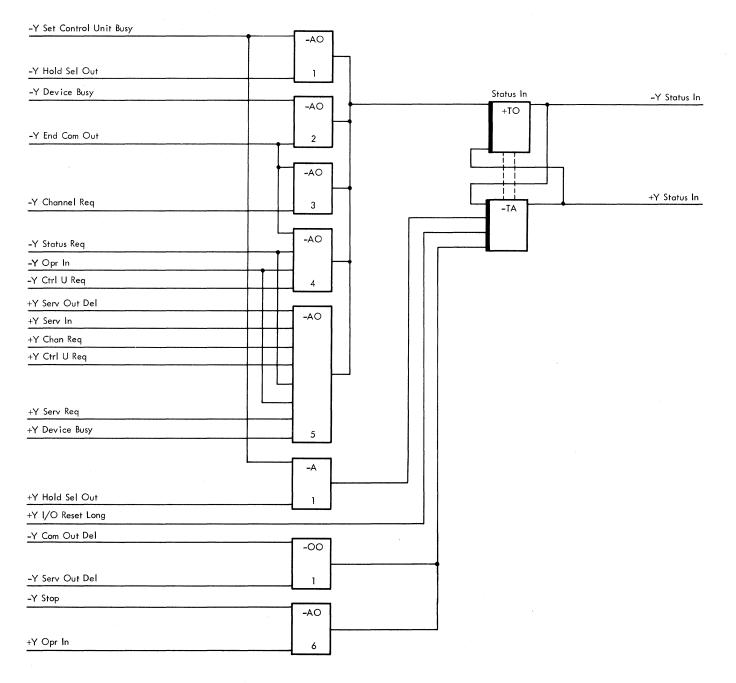

| Channel Request                                | . 2-117         |  |

|------------------------------------------------|-----------------|--|

| Control Unit Request                           | . 2-117         |  |

| Status Request                                 | . 2-117         |  |

| Service Request                                | . 2-117         |  |

| Operational In Latch                           | . 2-117         |  |

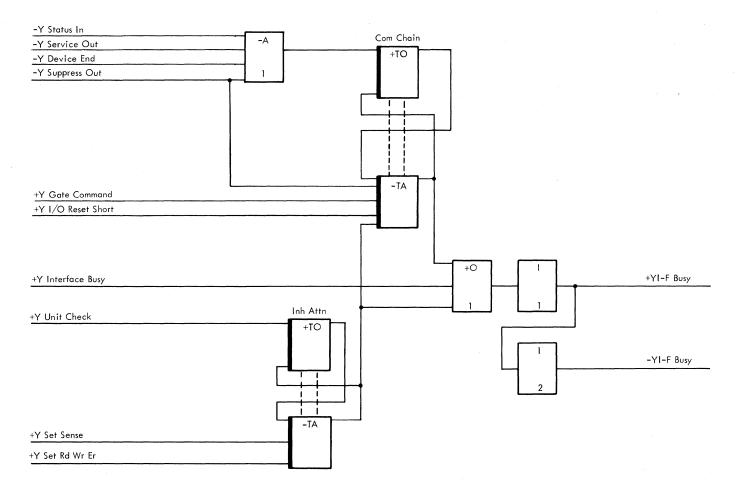

| Busy Latches                                   | . 2-118         |  |

| Interface Busy                                 | . 2-118         |  |

| Device Busy                                    | . 2-118         |  |

| Address In                                     | . 2-118         |  |

| Status In                                      | . 2-118         |  |

| Service In                                     | . 2-119         |  |

| Stack Status Latch                             | . 2-119         |  |

| Stop Latch                                     | . 2-119         |  |

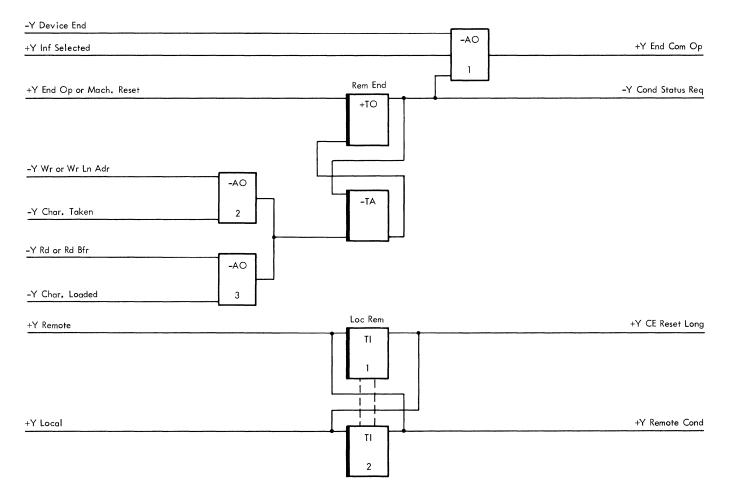

| Remember End and Local-Remote Latches .        | . 2-119         |  |

| Command Chaining and Inhibit Attention Latches | s. 2-121        |  |

| Command Chaining                               | . 2-121         |  |

| Inhibit Attention                              | . 2-122         |  |

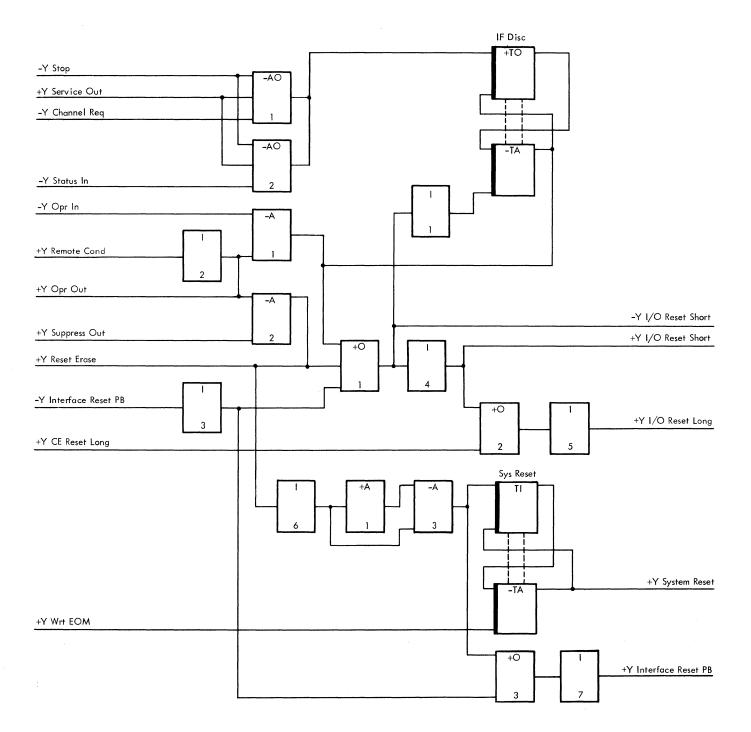

| Disconnect and Reset Circuits                  | . 2-122         |  |

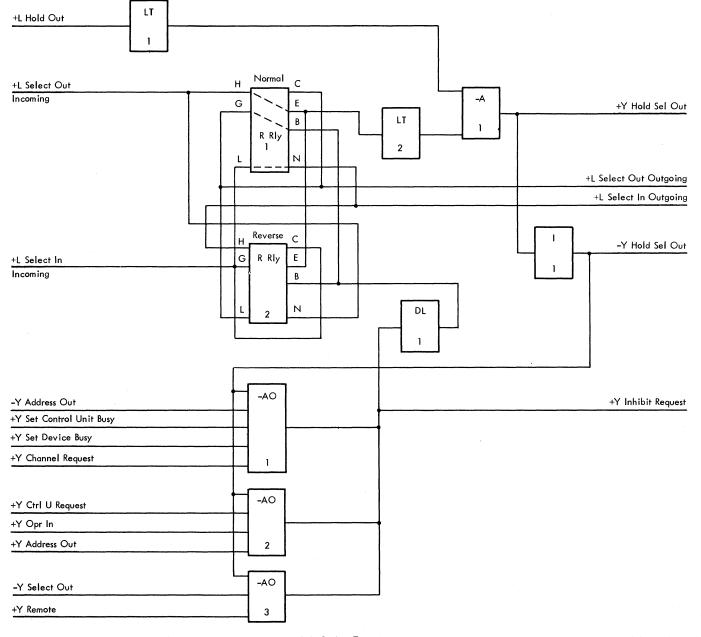

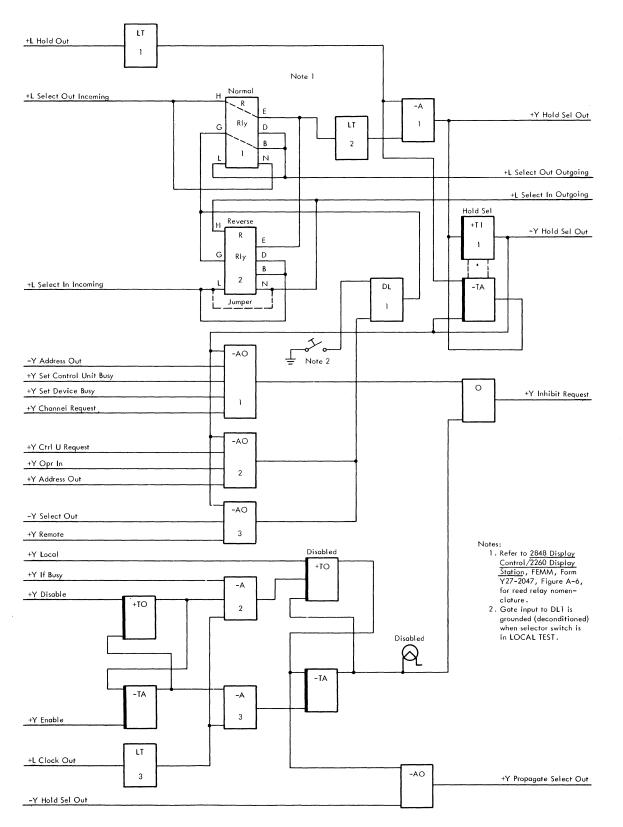

| Hold Select Circuits                           | . 2-122         |  |

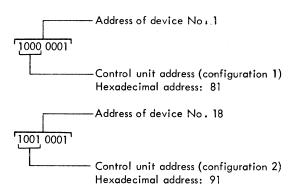

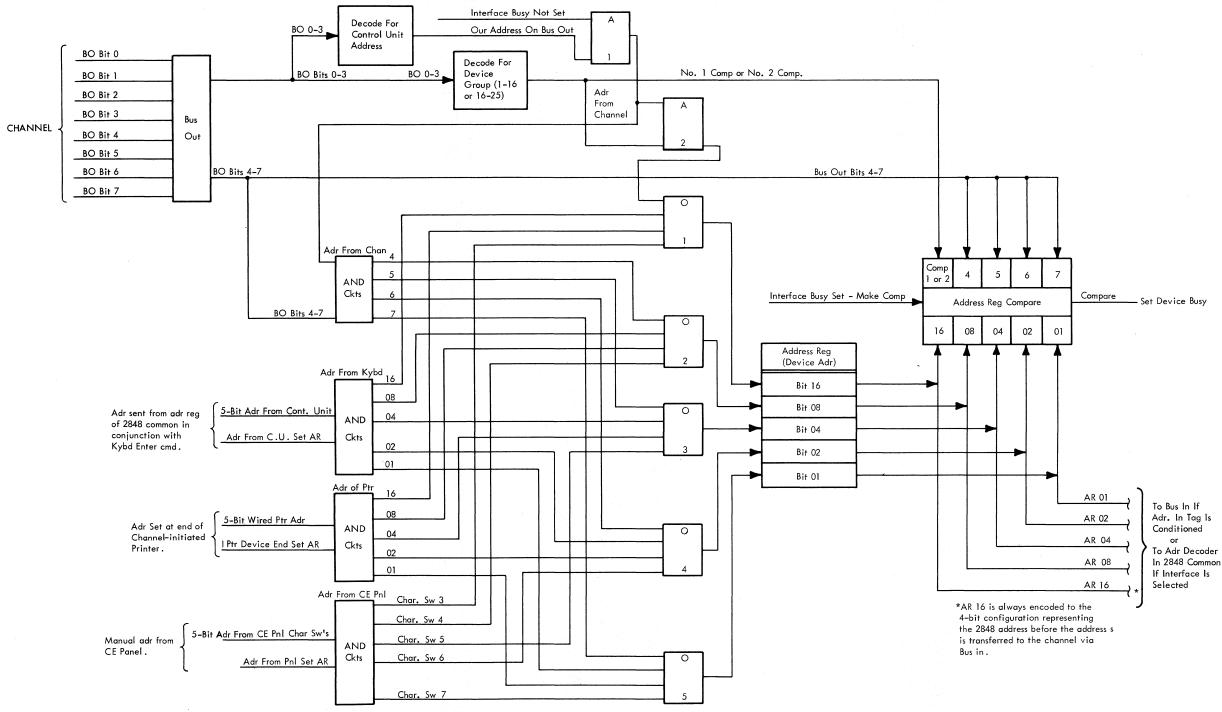

| Control Unit and Device Addressing             | . 2-125         |  |

|                                                | 0 405           |  |

|                                                | 0.400           |  |

| Control Unit-Originated Address                | · 2-126         |  |

|                                                | . 2-126         |  |

|                                                | · 2-120         |  |

|                                                | · 2-120         |  |

| Sense and Status Registers                     |                 |  |

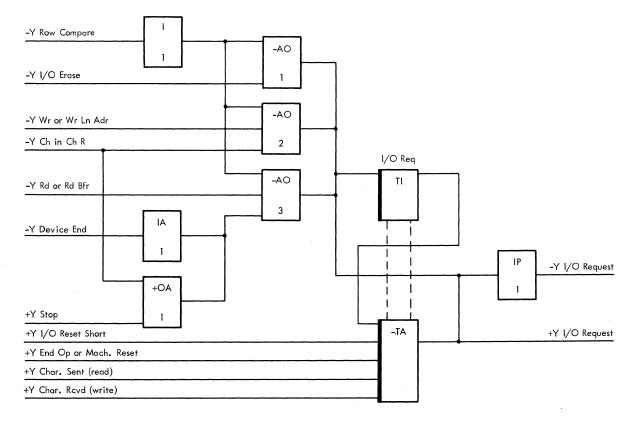

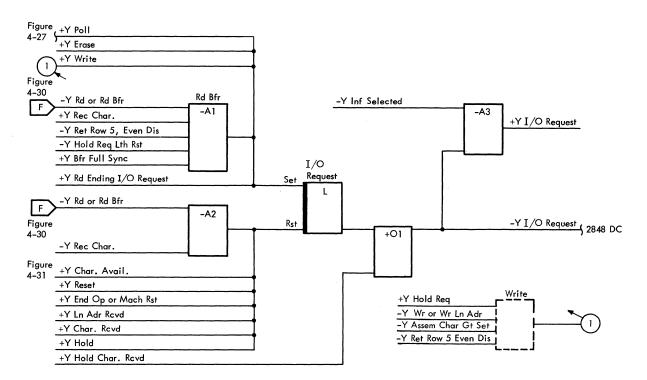

| I/O Request and Character Register Control     | . 2-131         |  |

| I/O Request                                    | . 2-131         |  |

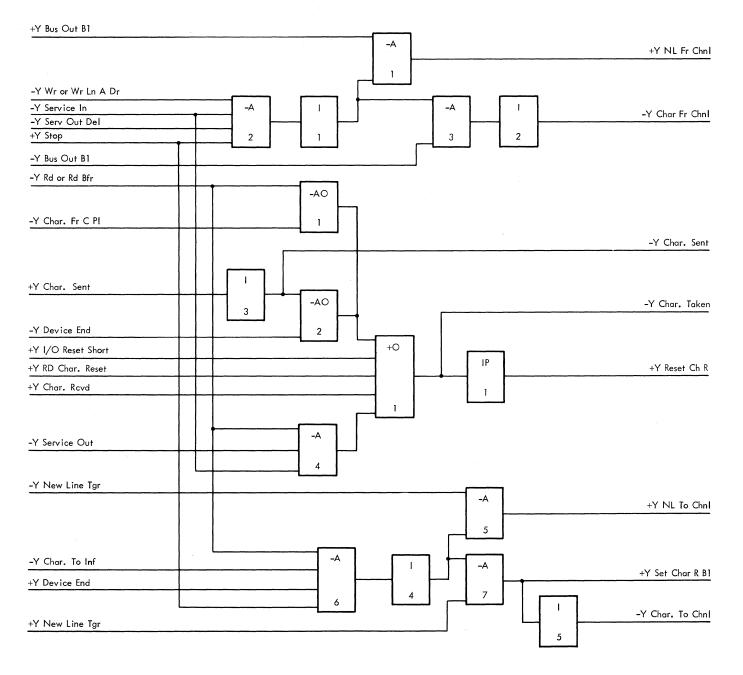

| Character Register Control                     | . 2-131         |  |

| Character Register and Code Converter          | . 2-132         |  |

| Character Formats                              | · 2-132         |  |

|                                                | · 2-133         |  |

|                                                | · 2-133         |  |

|                                                |                 |  |

| Circuit Description                            | • 2-133         |  |

| Channel Adapter Operational Sequences          | . 2-133         |  |

| Chamel-Initiated Sequences                     | . 2-133         |  |

| Sense                                          | . 2-137         |  |

|                                                | . 2-138         |  |

| No Operation                                   | . 2-138         |  |

| Test I/O                                       | . 2-138         |  |

| Command-to-Busy Device • • • • • •             | . 2-139         |  |

| Control Unit Busy • • • • • • • •              | . 2-140         |  |

| Control-Unit-Initiated Sequences               | . 2-141         |  |

| Data Transfer                                  | . 2-141         |  |

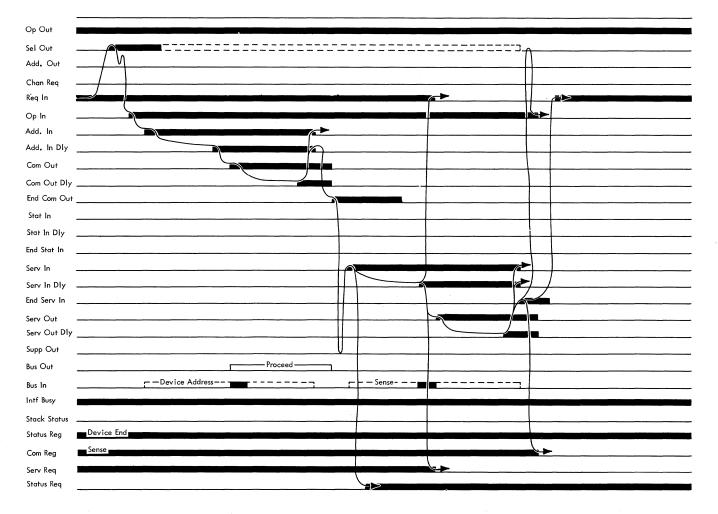

| Sense Transfer                                 | . 2-143         |  |

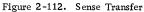

| Status Transfer                                | . 2-145         |  |

| Special Sequences                              | . 2-146         |  |

| Stack Status                                   | . 2-146         |  |

| Stop                                           | • 2-146         |  |

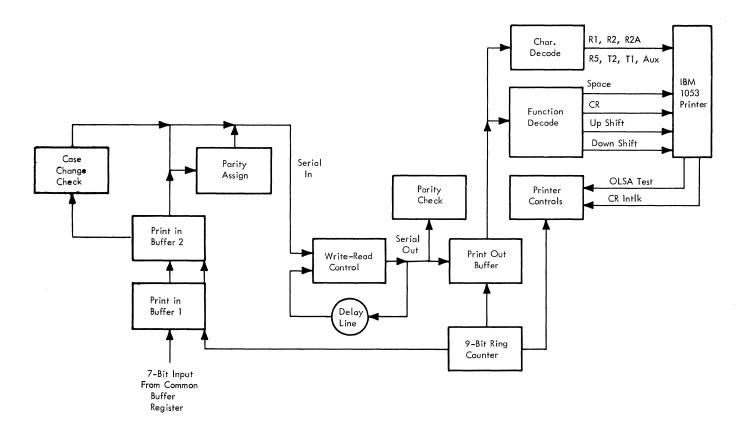

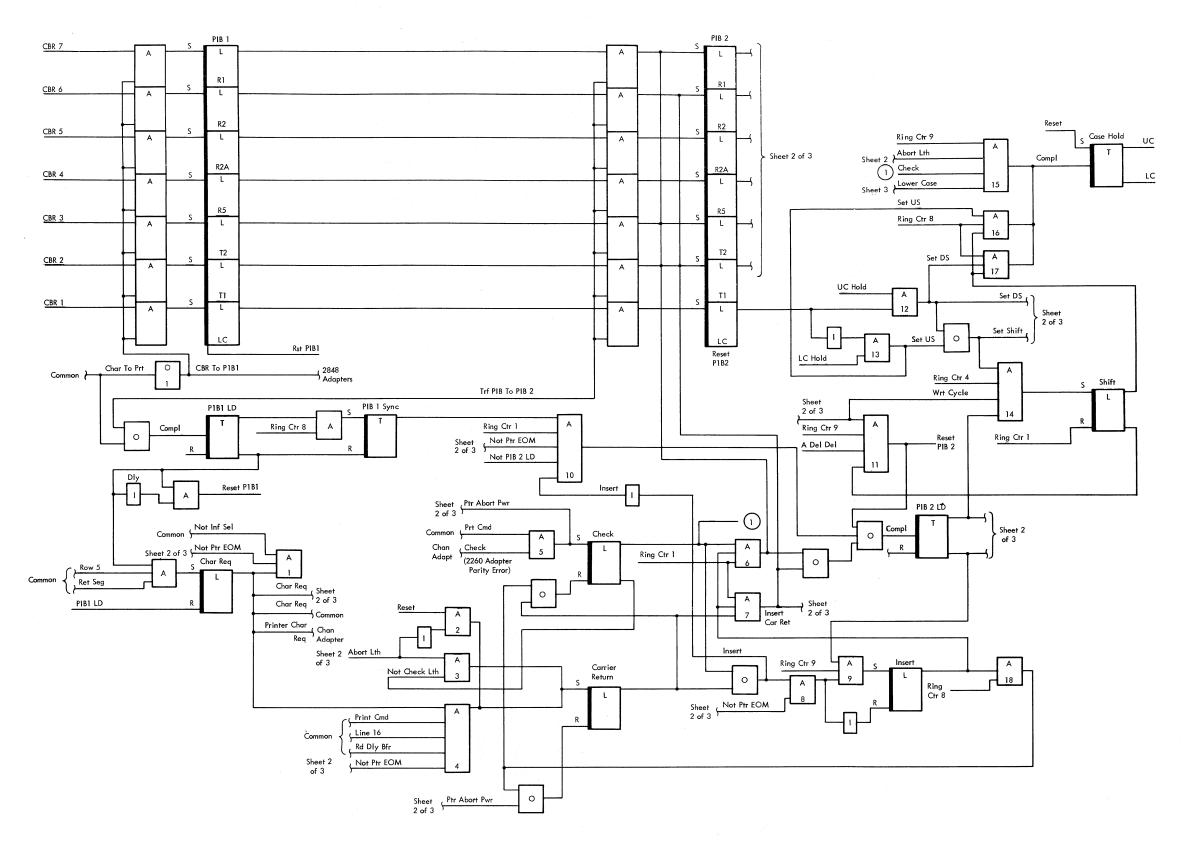

| Printer Adapter                                | . 2-147         |  |

| Printer Adapter Circuit Description            | . 2-148         |  |

| Ring Counter                                   | . 2-148         |  |

| Print In Buffers • • • • • • • • • •           | • <b>2-</b> 149 |  |

| Print In Buffer 1                              | . 2-149         |  |

| Print In Buffer 2                              | . 2-149         |  |

| Case Change Check                              | . 2-150         |  |

| Parity Assignment                              | . 2-150         |  |

| Delay Line                                     | . 2-150         |  |

| 7      | Parity Check Circuit 2-15                           |

|--------|-----------------------------------------------------|

| 7      | Print Out Buffer                                    |

| 7      | Function Decoder 2-15                               |

| 7      | Keyboard Print Operation 2-15                       |

| 7      | Printer Adapter Input Operation 2-15                |

| 8      | Printer Operation, Case Change Not Required 2-15    |

| 8      | Printer Operation, Case Change Required 2-15        |

| 8      | EOM and Display Adapter Parity Check 2-15           |

| 8      | Print Cycle Operations                              |

| 8      | Print Cycle and No Parity Check 2-15                |

| 9      | Print Cycle with Parity Check 2-15                  |

| 9      | Print Cycle with EOM and Chk Chac Latch On 2-15!    |

| 9      | Print Cycle with EOM Set and Chk Chac Latch         |

| 9      | Off                                                 |

| 1      | Write 1053 Buffer Storage                           |

| 1      |                                                     |

| 2      | CHAPTER 3 PRINCIPLES OF OPERATION 3-1               |

| 2      | General                                             |

| 2      | Channel Adapter Operational Sequences 3-1           |

| 5      | Channel-Initiated Sequences 3-1                     |

| 5      | Read or Write Selection                             |

| 6      | Sense                                               |

| 6      | Erase                                               |

| 6      | No Operation                                        |

| 6      | Test $I/O$                                          |

| 9      |                                                     |

| 1      |                                                     |

|        | -                                                   |

| 1      |                                                     |

| 1      | Data Transfer                                       |

| 2      | Sense Transfer                                      |

| 2<br>3 | Status Transfer                                     |

| 3      | Special Sequences                                   |

|        | Stack Status                                        |

| 3      | Stop 3-5                                            |

| 3      | Keyboard Operations 3-6                             |

| 3      | Alphanumeric Key 3-6                                |

| 3      | New Line Key                                        |

| 7      | Up and Down Keys                                    |

| 8      | Advance Key (NDC Feature) 3-8                       |

| 8      | Advance Key (Destructive Cursor Feature) 3-8        |

| 8      | Start Key                                           |

| 9      | Enter Key                                           |

| 0      | Backspace Key                                       |

| 1      | Erase Key                                           |

| 1      | Print Key                                           |

| 3      |                                                     |

| 5      | CHAPTER 4 FEATURES 4-1                              |

| 6      |                                                     |

| 6      |                                                     |

| 6      | Remote Interface Adapter                            |

| 7      | General                                             |

| 8      | ASCII Code Set 4-2                                  |

| 8      | IBM 2701 Data Adapter Unit 4-2                      |

| 9      | Data Sets 4-2                                       |

| 9      | ASCII Communications Control Characters 4-4         |

| 9      | 2848 Display Control Modes of Operation • • • • 4-4 |

| 0      | Control Mode                                        |

| 0      | Text Mode 4-4                                       |

| 0      | 2848 Display Control Status 4-5                     |

|        |                                                     |

FES Y27-2190

|     | Transmit Status • • • • •          | •     | •    | •    | •,  | •    | • | •   | 4-5           |

|-----|------------------------------------|-------|------|------|-----|------|---|-----|---------------|

|     | Selected Status • • • •            | •     | •    | •    | •   | •    | ٠ | •   | 4-5           |

|     | Nonselected Status • • • •         |       | •    | •    | •   | •    | • | •   | 4-5           |

|     | Receive Status • • • •             |       | •    | • ,  | •   | •    | • | • . | 4-5           |

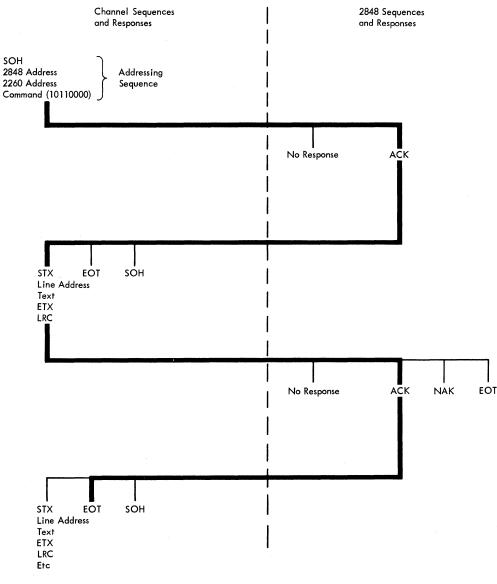

|     | Addressing Sequence                |       | •    | •    | •   | •    | • | •   | 4-5           |

|     | Commands and Command Operation     | on    |      | •    | •   | •    | • | •   | 4-6           |

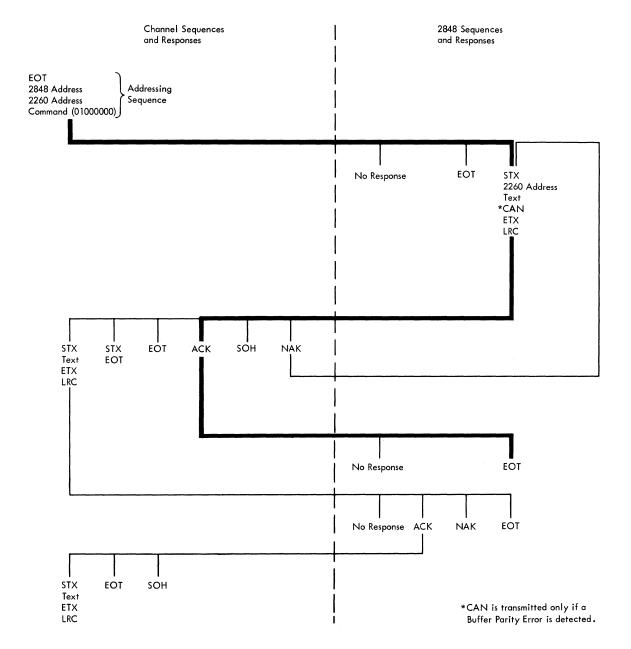

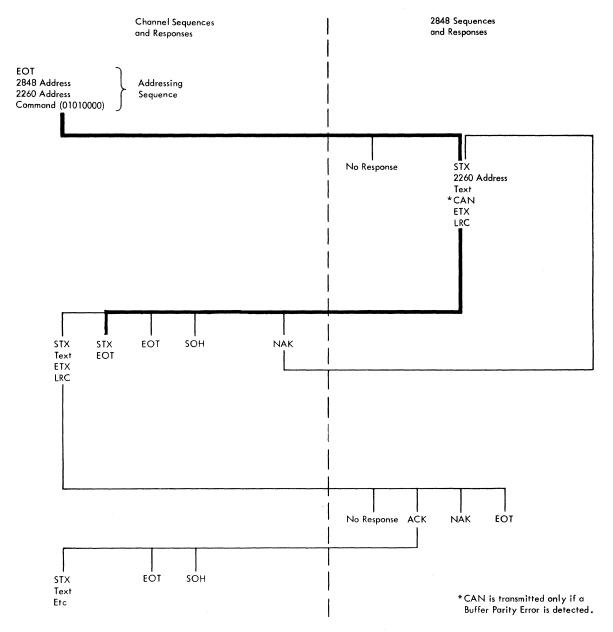

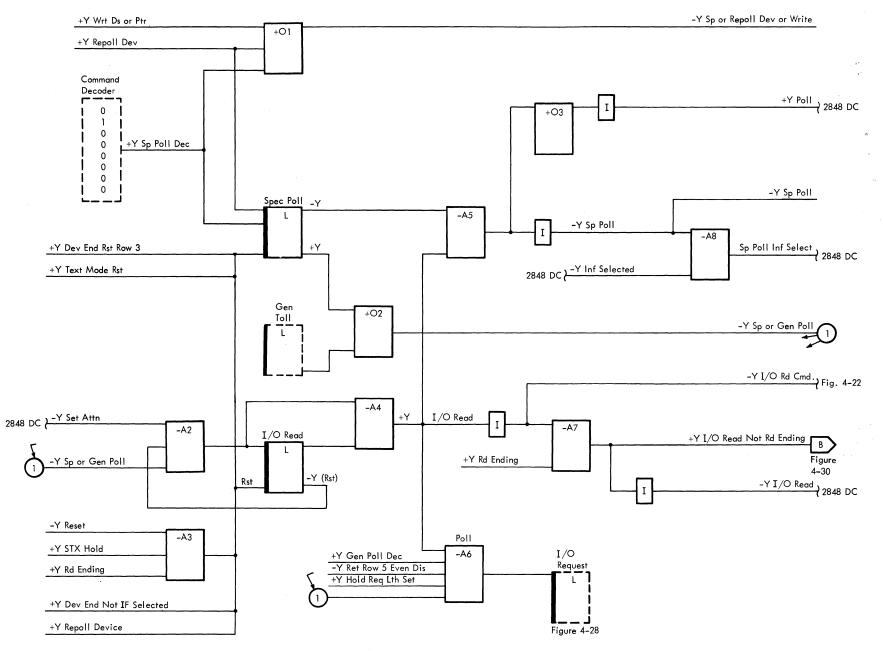

|     | Specific Poll to a 2260 Display    | Sta   | atio | n    | •   | •    | • | •   | 4-6           |

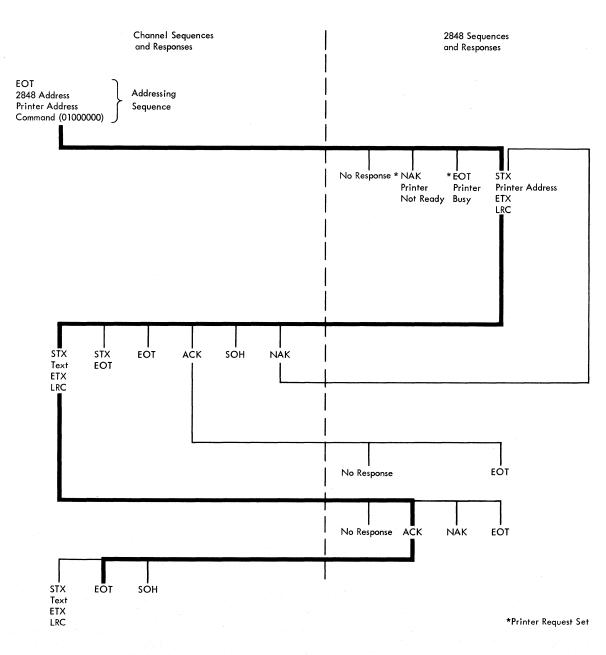

|     | Specific Poll to the 1053 Printer  | r     | •    | •    | •   | •    | • | •   | 4-8           |

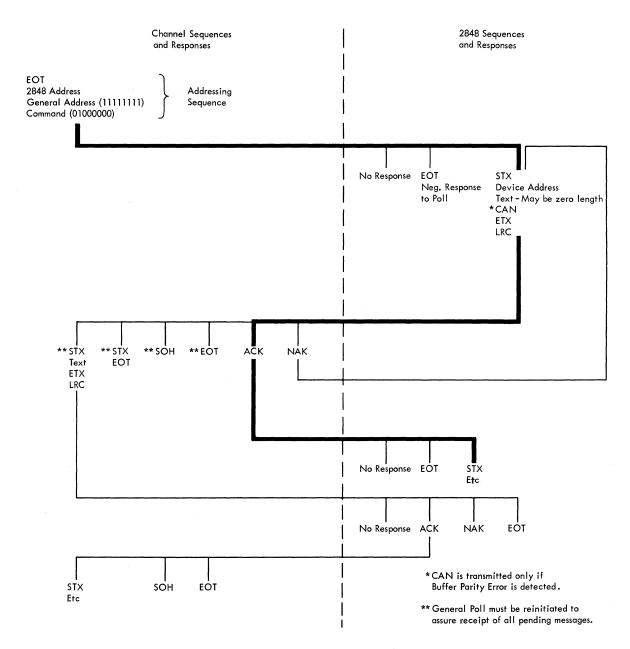

|     | General Poll                       |       | •    | •    | •   | •    | • | •   | 4-10          |

|     | Read Addressed Full DS Buffer .    |       | •    | •    | •   | •    | • | •   | 4-10          |

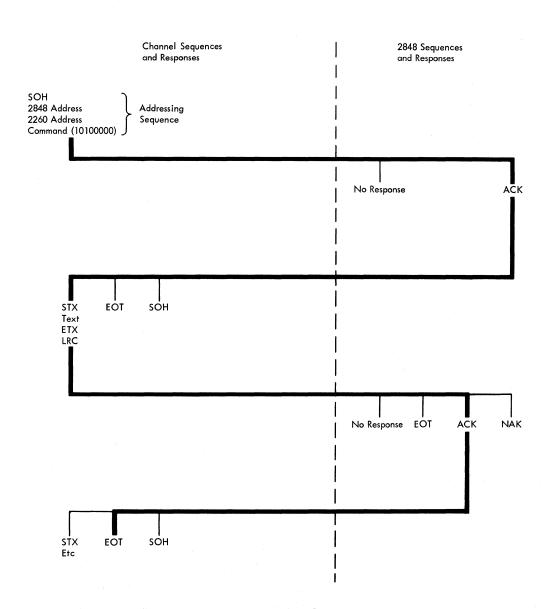

|     | Write Addressed DS                 |       | •    | •    | •   | •    | • | •   | 4-12          |

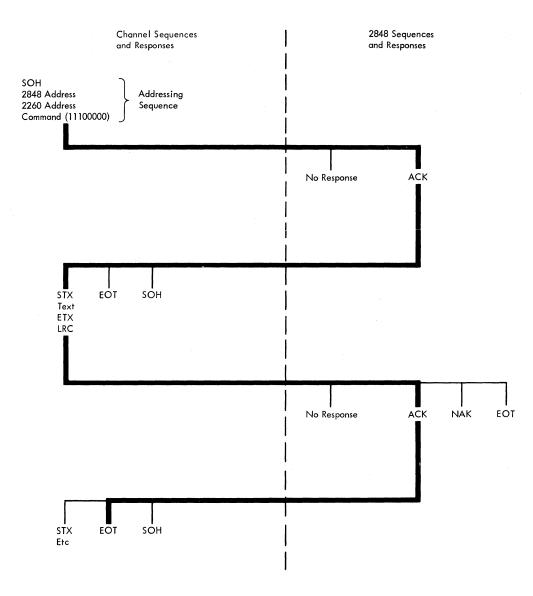

|     | Erase/Write Addressed DS           |       | •    | •    | •   | •    | • | •   | 4-13          |

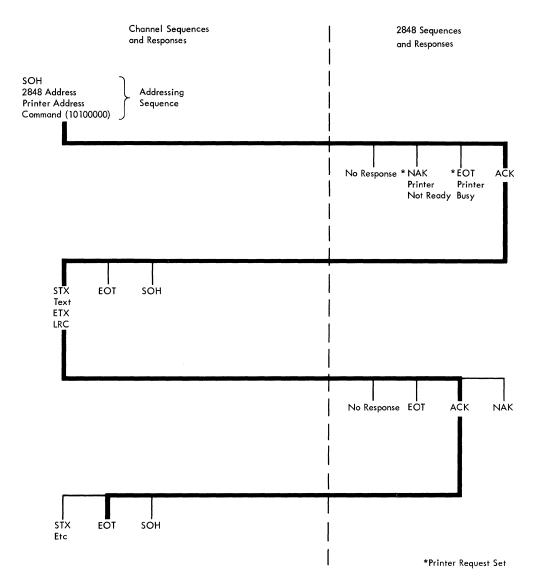

|     | Write Printer                      |       | •    | •    | •   | •    | • | •   | 4-13          |

|     | Printer Request Condition          |       | •    | •    | •   | •    | • | •   | 4-14          |

|     | Write DS Line Address              |       | •    | •    | •   | •    | • | •   | 4-15          |

|     | Summary of Sequences and Res       | po    | nse  | s    | •   | •    | • | •   | 4-16          |

|     | 2848 Display Control Sequences     | a     | nd   | Res  | po  | nses | 5 | •   | 4-17          |

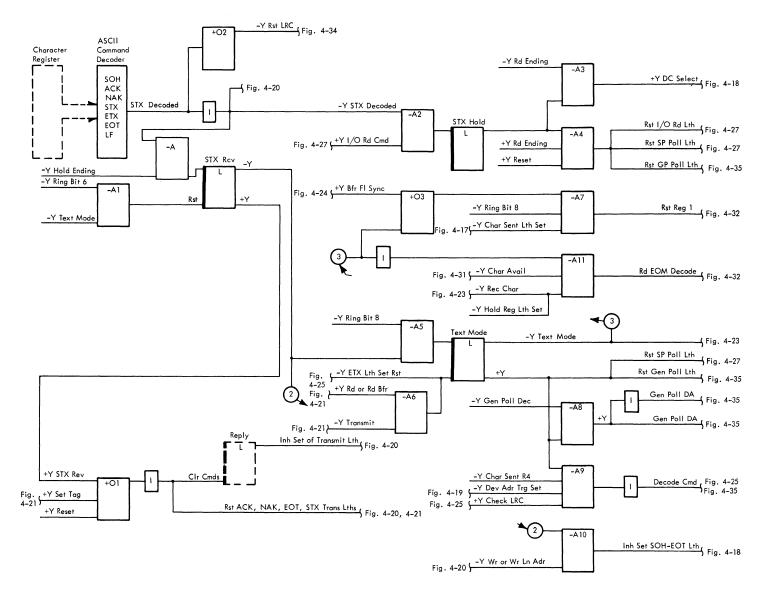

|     | Channel Sequences and Respons      | ses   |      | •    |     |      |   | •   | 4-18          |

| Fun | ctional Units                      |       | •    | •    |     |      |   |     | 4-19          |

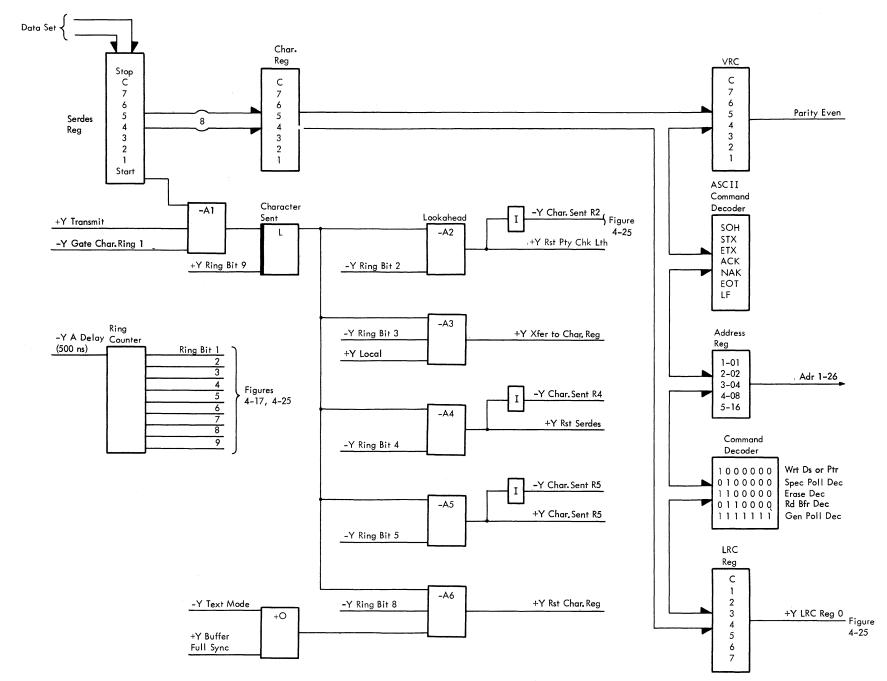

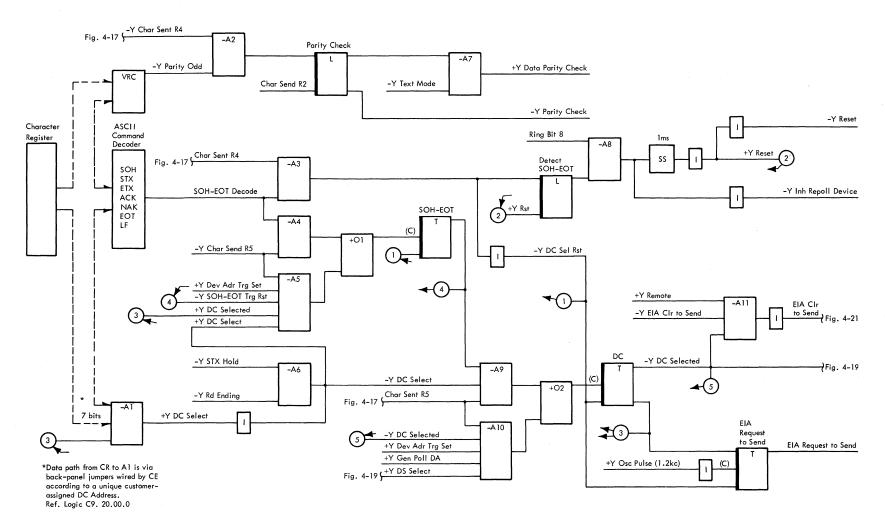

|     | Adapter Data Flow • • • • •        | ,     | •    | •    |     |      |   | •   | 4-19          |

| -   | Write Operation                    |       | •    |      |     |      |   |     | 4-19          |

|     | Read Operation                     |       | •    |      |     |      |   |     | 4-21          |

|     | Ring Counter                       |       |      | Ż    |     |      |   |     | 4-21          |

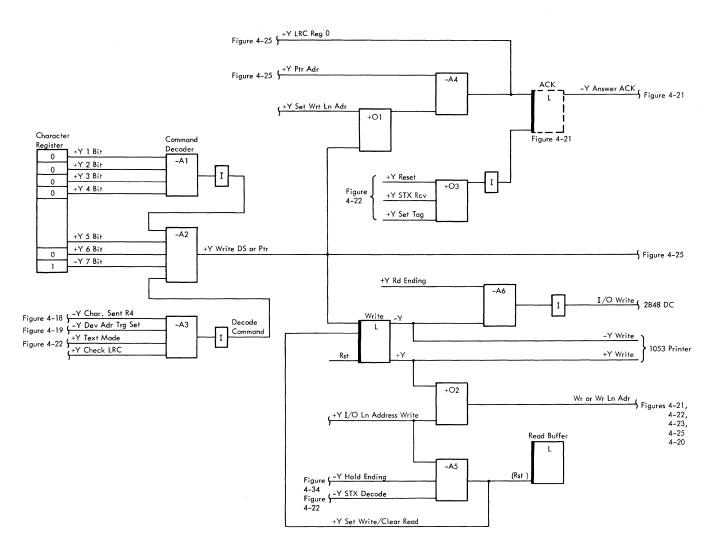

|     | 1.2-kc Clock and Serdes Control.   |       |      |      |     |      | • |     | 4-21          |

|     | Serializer-Deserializer Register.  |       |      |      |     |      |   | •   | 4-21          |

|     | 0                                  |       |      |      |     | •    | • | •   | 4-22          |

|     | Serdes Data Inputs                 |       | •    | •    | •   | •    | • | •   | 4-22          |

|     | Serdes Data Outputs                |       | •    | •    | •   | •    | • | •   | 4-22          |

|     | Special Serdes Outputs             |       | •    | •    | •   | •    | • | •   |               |

|     | Register Operation                 |       | •    | •    | •   | •    | • | •   | 4-22          |

| ,   | Character Register                 |       | •    | •    | •   | •    | • | •   | 4-22          |

|     | Control Mode Operation             |       | •    | •    | •   | •    | • | •   | 4-23          |

|     | Write Operation                    |       | •    | •    | •   | •    | • | •   | 4-23          |

|     | Read Operation                     |       |      |      | •   | •    | • | •   | 4-23          |

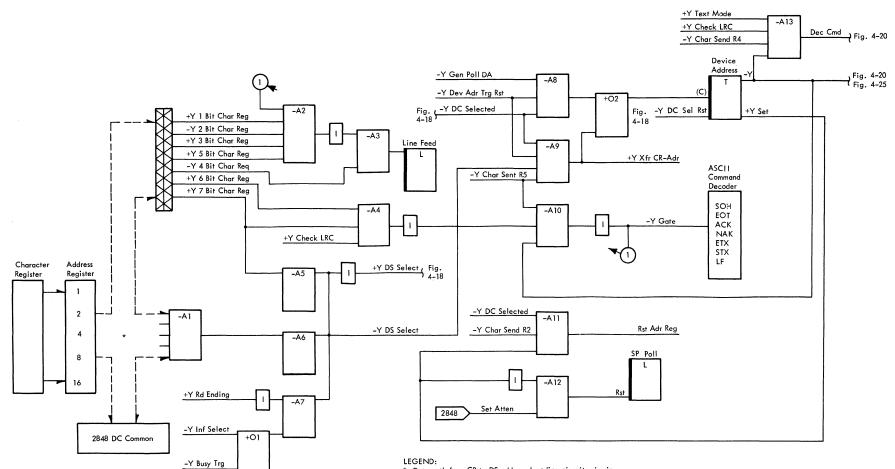

|     | Address Register • • • • •         |       |      |      | •   | •    | • | •   | 4-23          |

|     | Write/Channel Initiated Read C     | •     | era  | tion | 1   | •    | • | •   | 4-23          |

|     | Read Manual Input Operation .      | •     | •    | •    | •   | •    | • | •   | 4-23          |

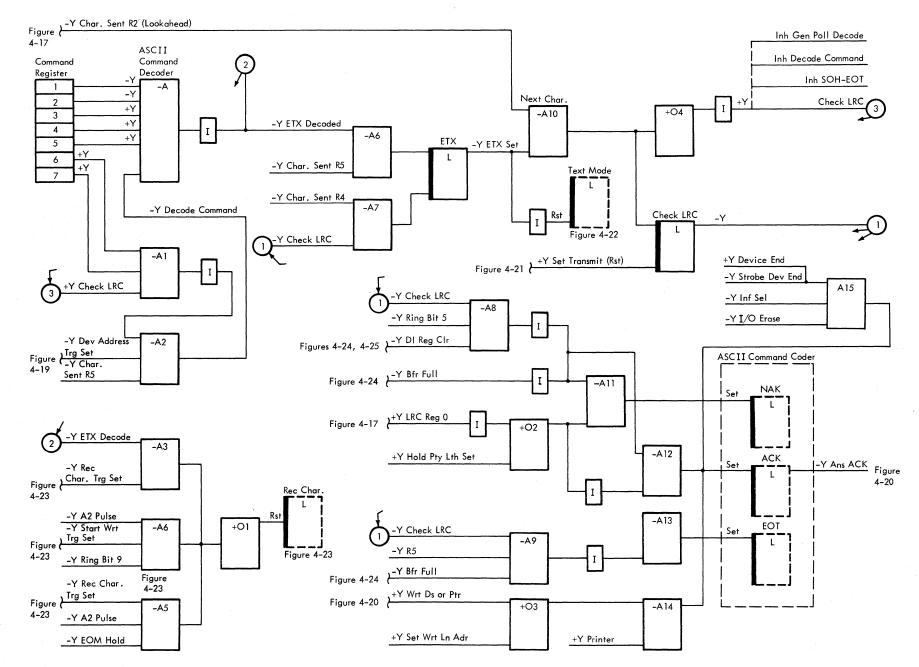

|     | Command Decoder • • • •            | •     | •    | •    | •   | •    | • | •   | 4-24          |

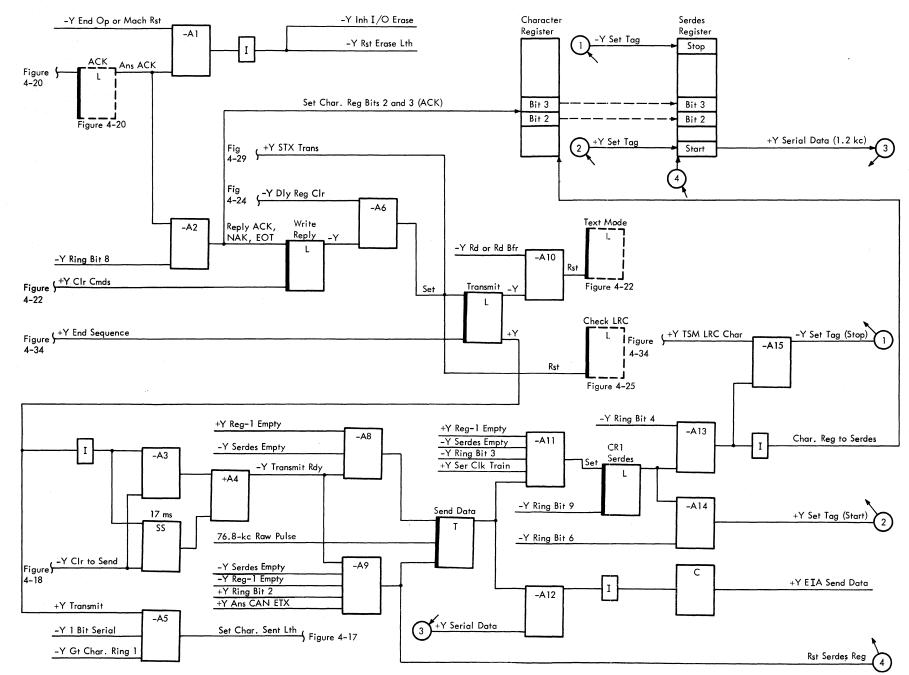

|     | ASCII Command Decoder • •          | •     | •    | •    | •   | •    | • | •   | 4-24          |

|     | ASCII Command Coder • • •          | •     | •    | •    | •   | •    | • | •   | 4-24          |

|     | LRC Register • • • • • •           | •     | •    | •    | •   | •    | • | •   | 4-25          |

|     | LRC Operation During Write         | •     | •    | •    | • • | •    | • | •   | 4-25          |

|     | LRC Operation During Read          | •     | •    | • ,  | •   | • •  | • | •   | 4 <b>-</b> 25 |

|     | Parity Check and Assignment .      | •     | •    | •    | •   | •    | • | •   | 4-26          |

|     | Parity Assignment                  | •     | • .  | •    | •   | •    | • | •   | 4-26          |

|     | Parity Check • • • • •             | •     | •    | •    | •   | •    | • | •   | 4-26          |

|     | Serializer and 7-to-6-Bit Code Con | nve   | erte | er   | •   | • •  | • | •   | 4-26          |

|     | Character Register Inputs .        | •     | •    | •    | •   | •    | • | •   | 4-26          |

|     | Common Buffer Register Inputs      |       | •    | •    | •   | •    |   | •   | 4-27          |

|     | Special Character Inputs           | •     | •    |      | •   | •    |   | •   | 4-27          |

|     | Read and Write Mark Inputs         | •     |      | •    |     |      |   | •   | 4-28          |

|     | Delay Line                         |       |      |      |     | •    |   | •   | 4-28          |

|     | Deserializer and Output Register   | • . • | •    | •    | •   | •    |   |     | 4-28          |

|     |                                    | •     |      | •    | •   |      |   | •   | 4-28          |

|     | Address Transfers to Output Reg    |       |      | •    | •   |      | • |     | 4-29          |

|     | Output Register Empty Latch        |       | •    | •    | •   | •    | • | •   | 4-29          |

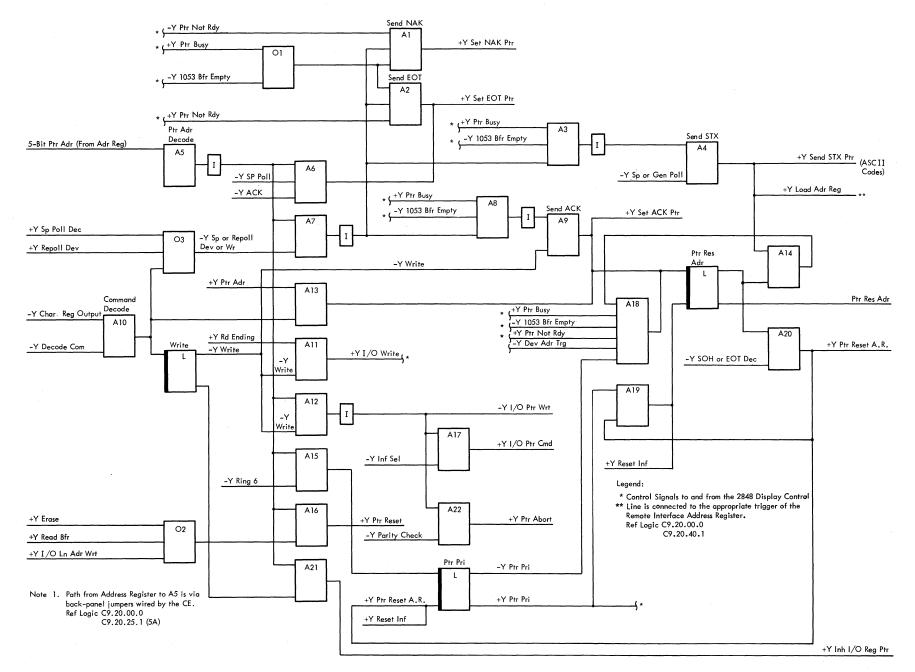

|     | Write and Write Command Control    |       |      |      |     | •    |   |     | 4-29          |

|     | Read and Read Command Controls     |       |      |      |     |      |   | •   | 4-29          |

|     | 1053 Printer Controls              |       |      |      |     |      |   | •   | 4-29          |

|     |                                    | •     | •    | •    | •   | •    | • | •   |               |

| Theory of Operation                                                                                                 | 4-29         |

|---------------------------------------------------------------------------------------------------------------------|--------------|

| General                                                                                                             | 4-29         |

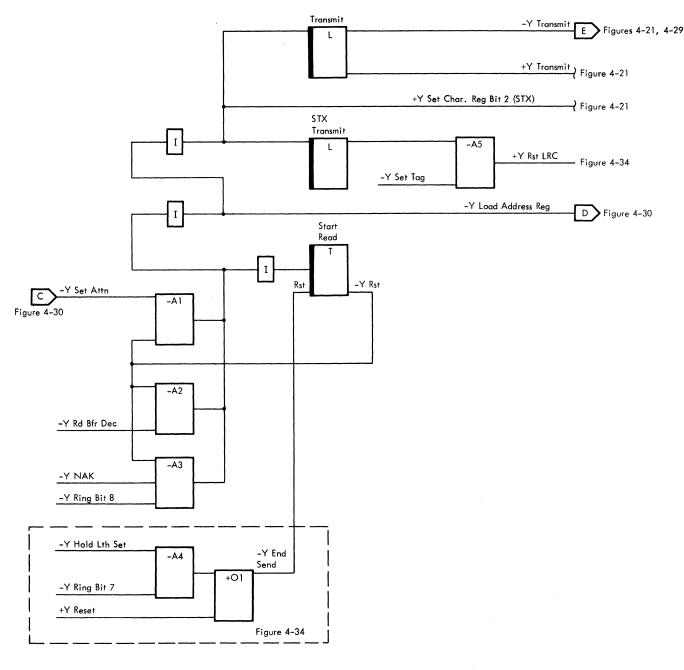

| Addressing Sequence - Write Operation                                                                               | 4-30         |

| Channel Response - SOH, EOT Character                                                                               | 4-30         |

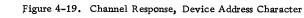

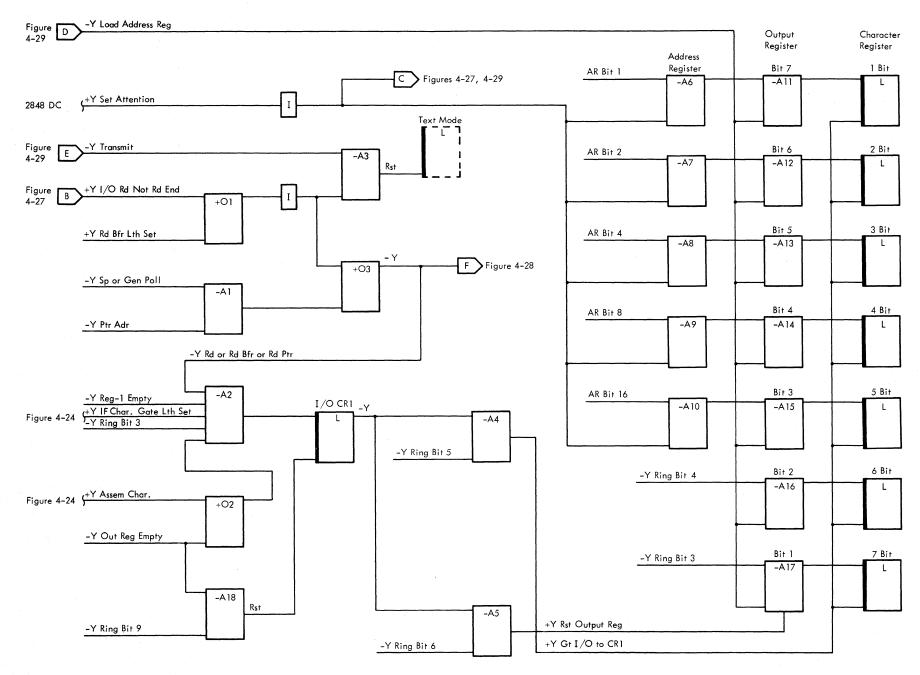

| Channel Response - DC Address                                                                                       | 4-30         |

| Channel Response - 2260 DS Address                                                                                  | 4-30         |

| Command - Write Addressed DS                                                                                        | 4-34         |

| Remote Interface Response - ACK Character • •                                                                       | 4-34         |

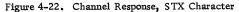

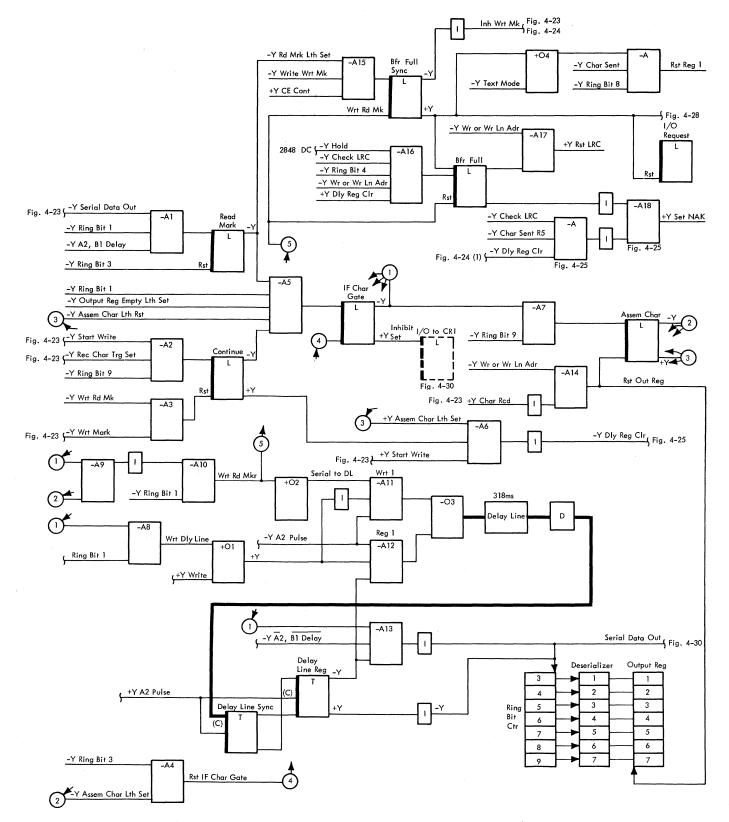

| Channel Response - STX Character                                                                                    | 4-35         |

| Channel Response - Text Character                                                                                   |              |

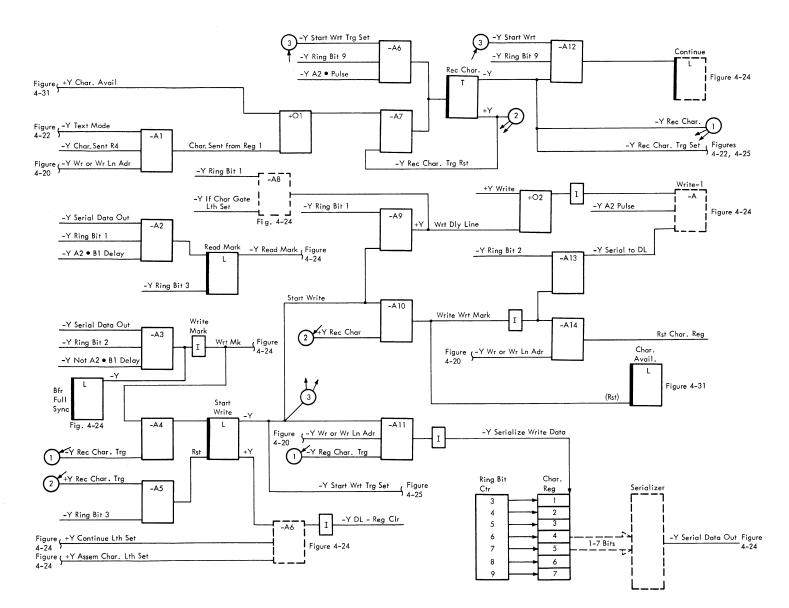

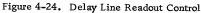

| Delay Line Readout - Write Operation                                                                                | . 4-41       |

| Deserializer and Output Register Transfer - Write                                                                   |              |

| Operation                                                                                                           |              |

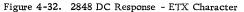

| Channel Response - ETX Character                                                                                    | 4-41         |

| Channel Response - LRC Character                                                                                    | 4-43         |

| Channel Response - EOT Character                                                                                    | 4-43         |

| Command - Write Printer                                                                                             | 4-45         |

| Address Sequence                                                                                                    | 4-45         |

| Initial Adapter Response                                                                                            | 4-45         |

| Printer Ready and Not Busy                                                                                          | 4-45         |

| Printer Busy                                                                                                        | 4-46<br>4-46 |

|                                                                                                                     |              |

| Address Sequence - Read Operation                                                                                   | 4-46<br>4-46 |

|                                                                                                                     | 4-40<br>4-46 |

|                                                                                                                     |              |

| 2848 DC Response - 2260 DS Address                                                                                  |              |

|                                                                                                                     |              |

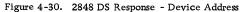

| Delay Line Readout - Read Operation<br>Deserializer and Output Register Transfer - Read                             | 4-01         |

| Operation                                                                                                           | 4-51         |

| Output Register to Character Register Transfer                                                                      | 4-51         |

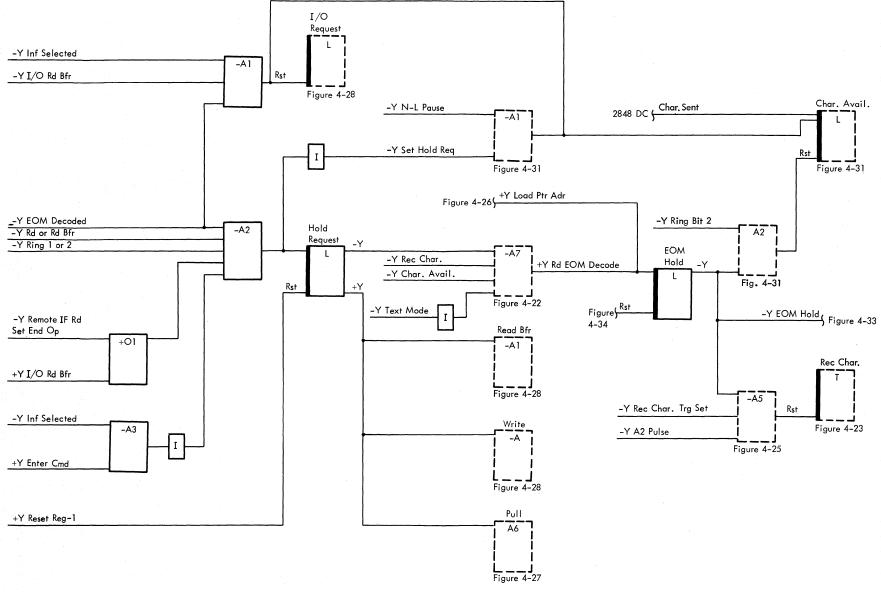

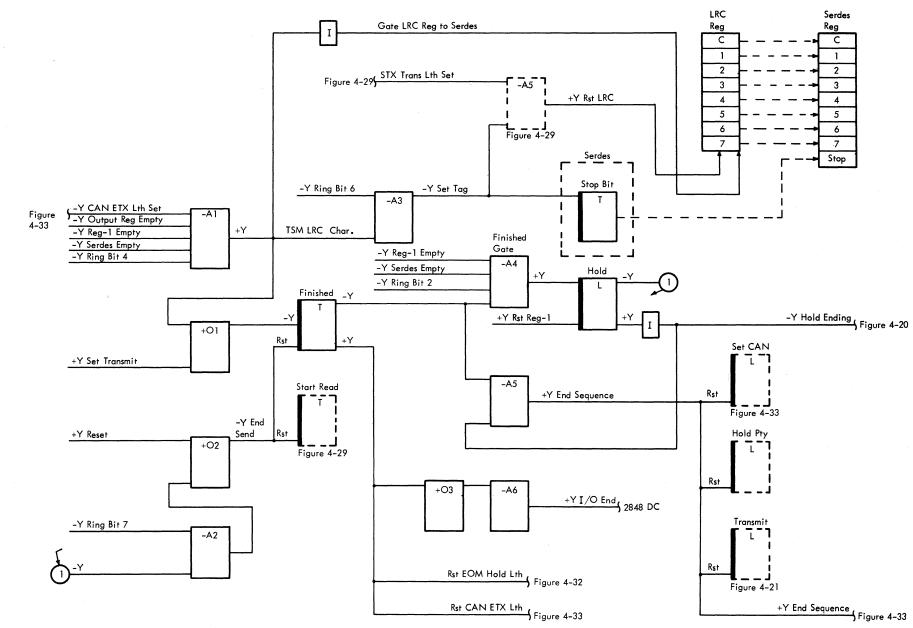

| 2848 DC Response - ETX Character                                                                                    | 4-53         |

| Buffer Parity Check - Read Operation                                                                                | 4-53         |

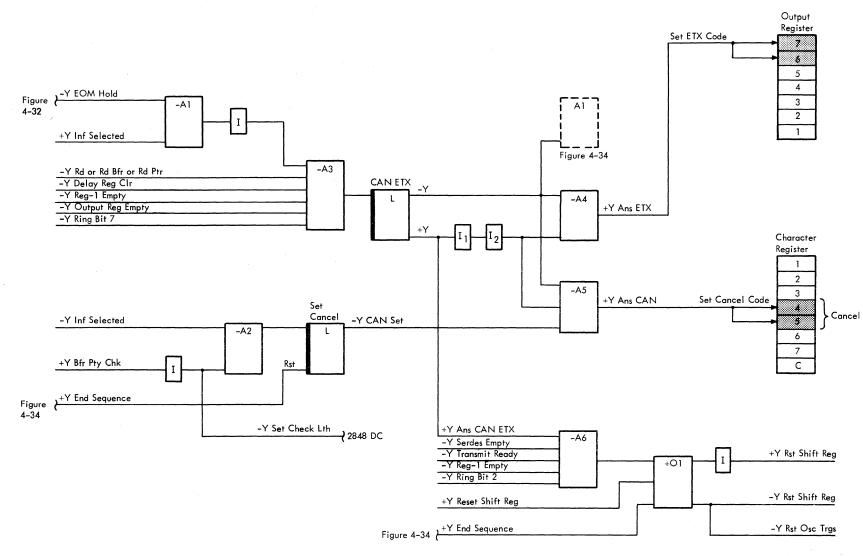

| 2848 DC Response - LRC Character                                                                                    | 4-53         |

| Channel Response - STX to Read End Sequence                                                                         | 4-57         |

| Write DS Line Address                                                                                               | 4-57         |

| Write/Erase Command                                                                                                 | 4-57         |

| Write Erase Command - Channel Response (STX).                                                                       | 4-59         |

| General Poll                                                                                                        | 4-59         |

|                                                                                                                     | <b>F</b> 1   |

| CHAPTER 5 POWER SUPPLIES AND CONTROL                                                                                | 5-1<br>5-1   |

| Introduction                                                                                                        | 5-1<br>5-1   |

| 60-Cycle Power System                                                                                               | 5-1<br>5-1   |

| Power Control Sequences                                                                                             | 5-1          |

|                                                                                                                     | 5-1          |

| Power On - Remote $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ Power On - Local $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 5-1          |

| Power Off - Remote                                                                                                  | 5-1          |

| Power Off - Local                                                                                                   | 5-4          |

| Emergency Power Off                                                                                                 | 5-4          |

| Fault Condition Operation                                                                                           | 5-4          |

| Circuit Breaker Open During Local Operation .                                                                       | 5-4          |

| Circuit Breaker Open During Remote                                                                                  |              |

| Operation                                                                                                           | 5-4          |

| Overtemperature Conditions                                                                                          | 5-4          |

| DC Power Supply                                                                                                     | 5-4          |

| 50-Cycle Power System                                                                                               | 5-4          |

| Initial Power Distribution                                                                                          | 5-4          |

| Power Control Sequences                                                                                             | 5-8          |

|                                                                                                                     |              |

|         | Power   | On -   | Re   | emo  | te   |      | •    | •             | •    | •             |      | •   | •    | •  | • | 5-8          |

|---------|---------|--------|------|------|------|------|------|---------------|------|---------------|------|-----|------|----|---|--------------|

|         | Power   | On -   | Lo   | cal  |      |      | •    | •             | •    | •             |      | •   | •    | •  | • | 5-8          |

| :       | Power   | Off -  | Re   | emo  | ote  | •    | •    | •             | •    | •             | •    | •   | •    | •  |   | 5-8          |

| :       | Power   | Off -  | Lc   | cal  |      |      | •    | •             | •    | •             |      | •   | •    | •  | • | 5-8          |

|         | Emerg   | ency   | Pov  | wer  | Of   | f    |      |               |      |               | •    | •   |      |    |   | 5-8          |

| :       | Fault ( | Condi  | tio  | n O  | per  | ati  | on   | •             | •    |               | •    | •   | •    | •  | • | 5-8          |

|         | Cir     | cuit I | Brea | ake  | r Oj | pen  | Dı   | ı <b>ri</b> r | ıg I | .o <b>c</b> a | al ( | Dpe | rati | on | • | 5-8          |

|         | Cir     | cuit I | Brea | ike  | r 0  | pen  | Dı   | ırir          | ig F | Ren           | not  | e   |      |    |   |              |

|         | Op      | eratio | n    | •    | •    |      | •    | •             | •    | •             | •    | •   | •    | •  | • | 5-8          |

|         | Co      | ntacto | or P | 'K1  | Ov   | erl  | oad  | l Co          | onta | icts          | 0    | pen | in   |    |   |              |

|         | Loc     | al     | •    | •    | •    |      | •    | •             | •    | •             | •    | •   |      | •  | • | 5-8          |

|         | Co      | ntacto | or F | K1   | Ov   | erl  | oad  | l Co          | onta | acts          | s 0  | pen | in   |    |   |              |

|         | Re      | mote   | •    | •    | •    | •    | •    |               | •    |               | •    | •   | •    |    | • | 5-9          |

|         | Re      | set of | PK   | 1 C  | ve   | rloa | ad ( | Cor           | ntac | ts            |      | •   |      |    |   | 5-9          |

|         | Ov      | ertem  | per  | ratu | re   | Cor  | ndit | ion           | IS   |               | •    | •   |      |    | • | 5-9          |

|         | The     | ermal  | l Ci | ircu | it l | Res  | et   |               | •    | •             | •    | •   |      | •  | • | 5-9          |

|         | DC Po   | wer S  | up   | plie | s    |      |      |               |      | •             |      |     |      | •  | • | 5-9          |

|         |         |        |      |      |      |      |      |               |      |               |      |     |      |    |   |              |

| CHAP    | FER 6   | CON    | ISO  | LE   | AN   | DN   | MA)  | INT           | EN   | AN            | CE   |     |      |    |   |              |

|         |         | FEA    | TU   | RES  | 5    | •    | •    | •             | •    | •             | •    | •   | ٠    | •  | • | 6 <b>-</b> 1 |

| Introdu | otion   |        |      |      |      |      |      |               |      |               |      |     |      |    |   | 6-1          |

| 6-1 |

|-----|

| 6-1 |

| 6-1 |

| 6-1 |

| 6-1 |

| 6-2 |

|     |

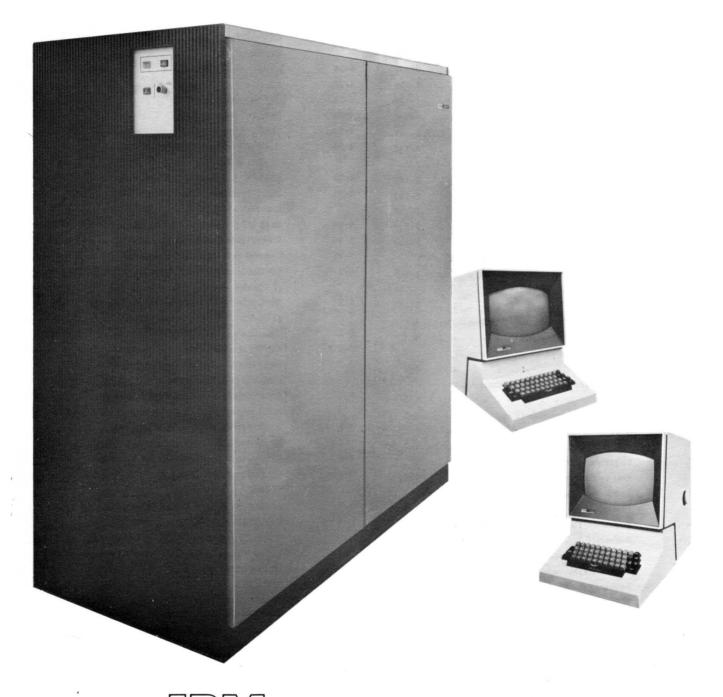

| Frontispiece | IBM 2260 Display Station - 2848 Display  |

|--------------|------------------------------------------|

|              | Control viii                             |

| 1-1          | Summary of IBM 2848 Display Control      |

|              | Models 1-3                               |

| 1-2          | IBM 2848 Display Control Features        |

|              | (2 Sheets) 1-4                           |

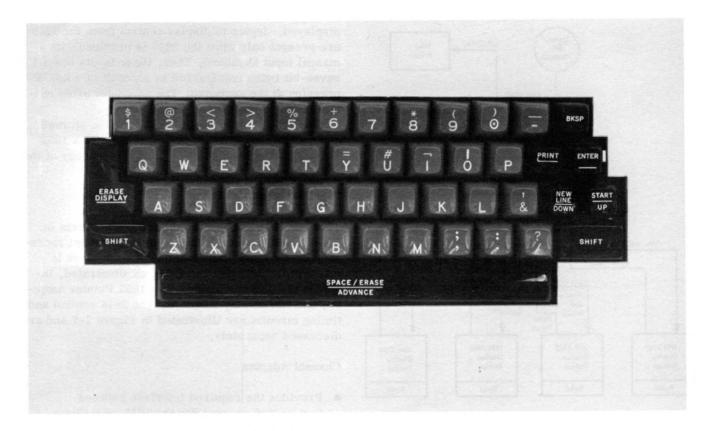

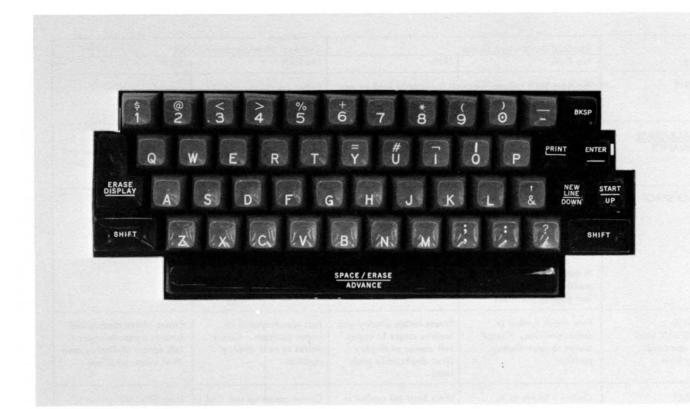

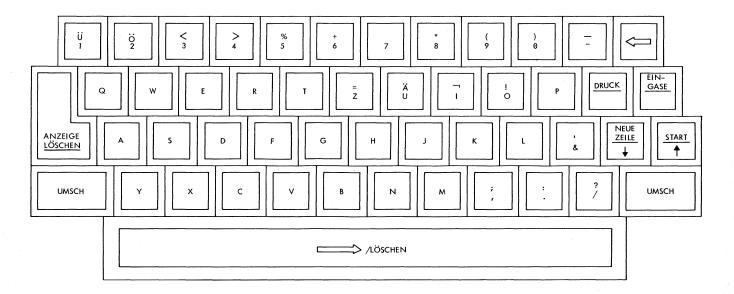

| 1-3          | Optional Alphanumeric Keyboard for       |

|              | 2260 DS 1-7                              |

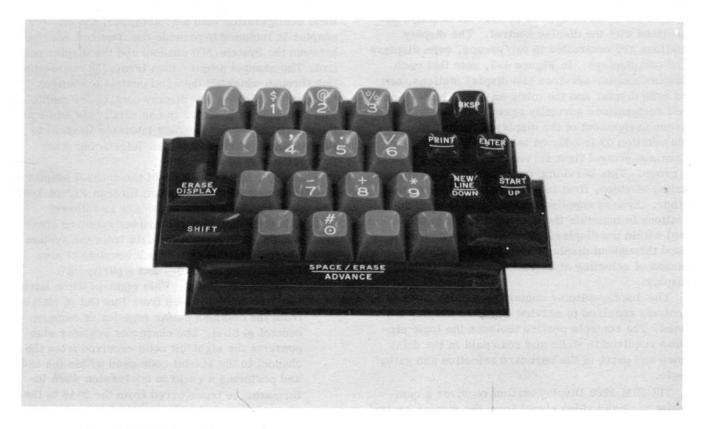

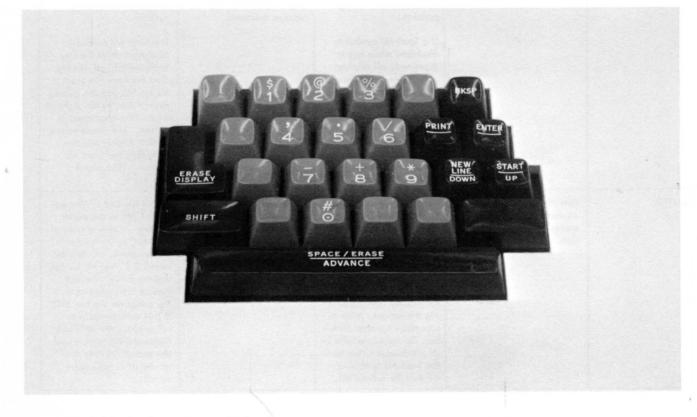

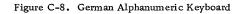

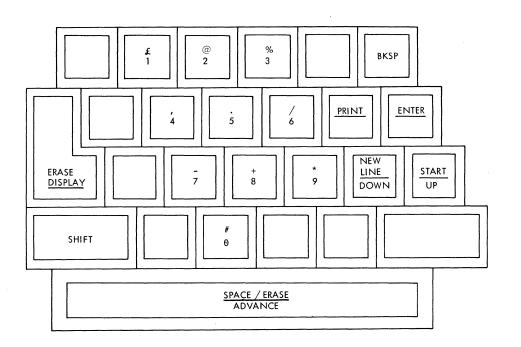

| 1-4          | Optional Numeric Keyboard for 2260       |

|              | DS 1-7                                   |

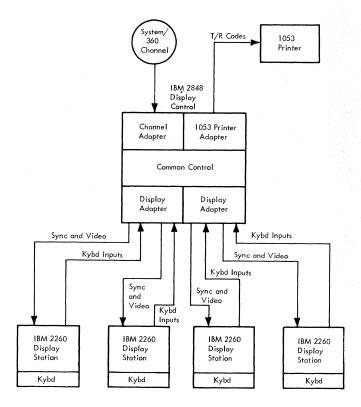

| 1-5          | IBM 2848 - IBM 2260 Display Complex,     |

|              | Block Diagram 1-8                        |

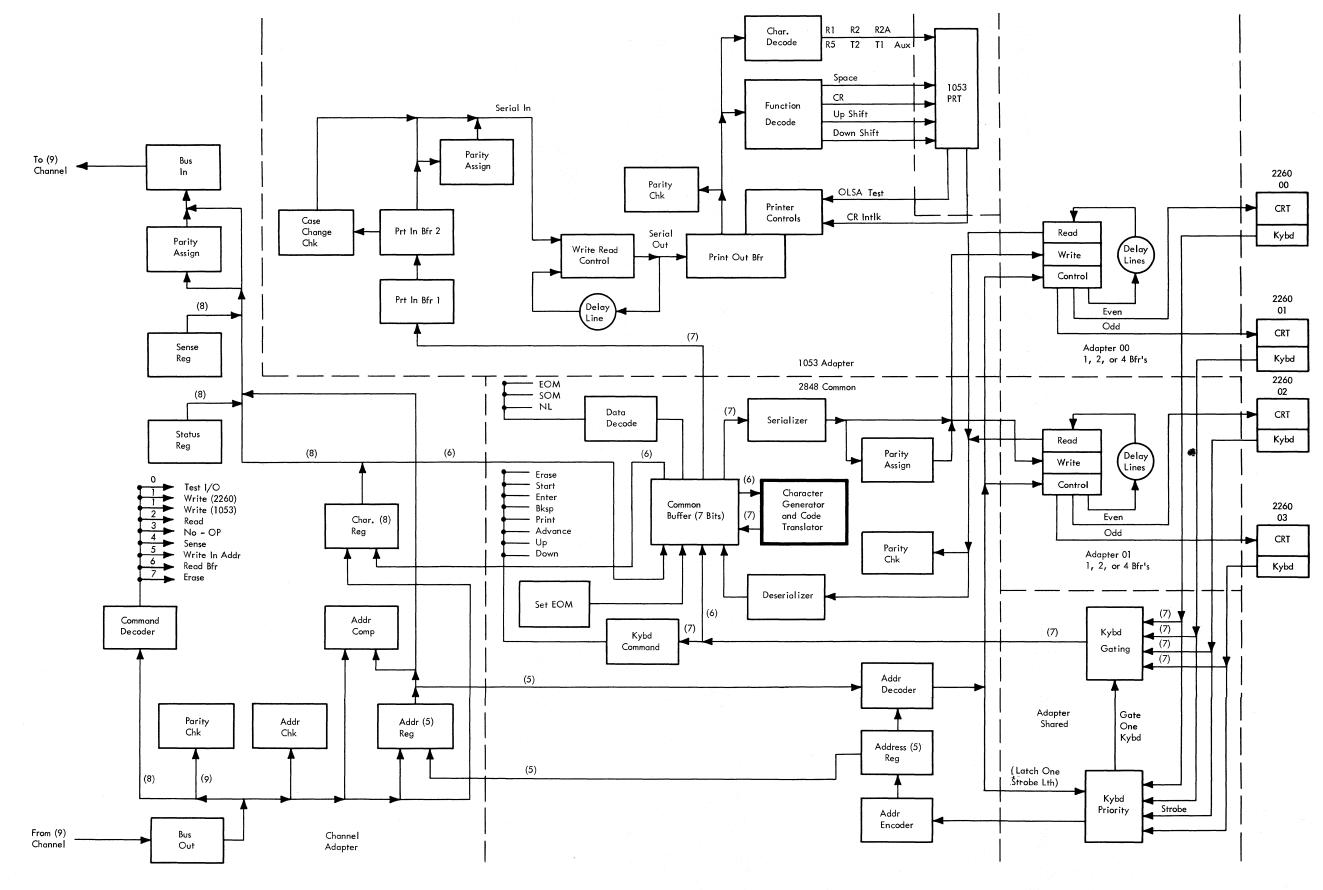

| 1-6          | IBM 2848 - IBM 2260 Block Diagram . 1-9  |

| 1-7          | Timing and Clock Circuits, Simplified    |

|              | Block Diagram 1-11                       |

| 1-8          | CRT Display Organization 1-15            |

| 1-9          | 2260 Display Station, Block Diagram 1-17 |

| 1-10         | Typical Address Assignments, Model 1     |

|              | 2848 DC 1-21                             |

| 1-11         | Commands and Their Code Structure 1-22   |

| 1-12         | Displayable Symbols 1-28                 |

| 1-13         | EBCDIC Code Used for 2848-System/360     |

|              | Channel Transfers 1-29                   |

| 1-14         | Keyboard Code 1-30                       |

| 1-15         | Internal 2848 Six-Bit BCD Code 1-31      |

| 1-16         | 1053 Printer Tilt-Rotate Codes and Their |

|              | 2848 Six-Bit BCD Code Equivalents 1-32   |

| 1-17         | Terms and Definitions (2 Sheets) 1-33    |

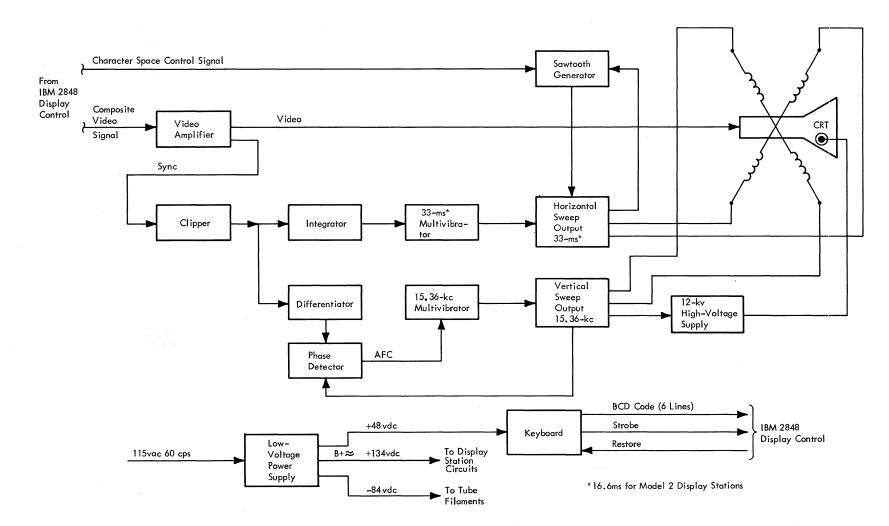

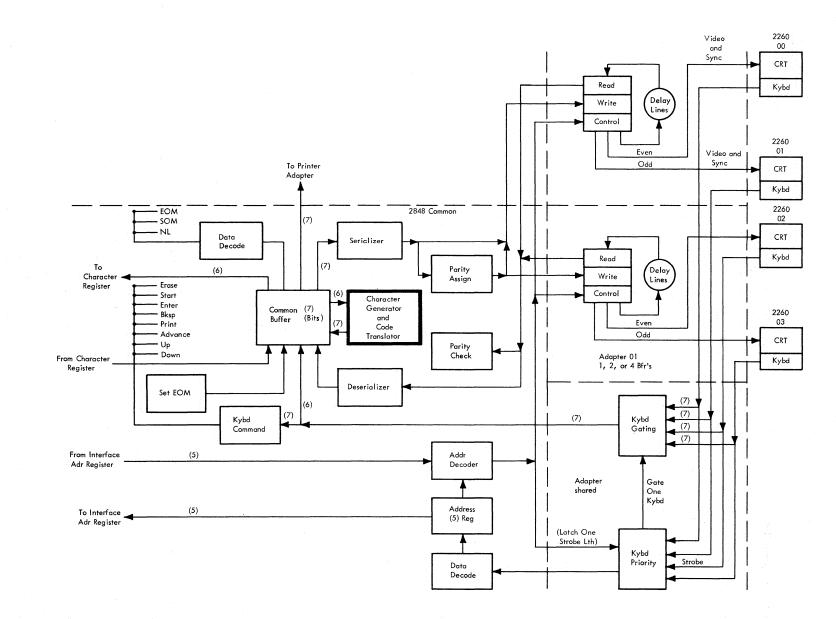

| 2-1          | Display Station Block Diagram 2-2        |

| Numeric Keyboard                                | • | 6-2 |

|-------------------------------------------------|---|-----|

| Control Key Functions                           |   | 6-2 |

|                                                 |   |     |

| APPENDIX A MACHINE CHARACTERISTICS              | • | A-1 |

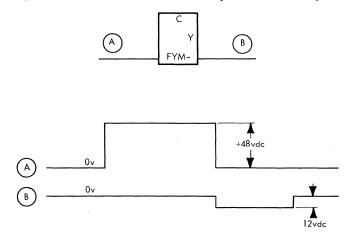

| APPENDIX B SPECIAL CIRCUITS                     | • | B-1 |

| Introduction                                    | • | B-1 |

| Integrator Card A, Type FYM                     | • | B-1 |

| Integrator Card B, Type FYN                     | • | B-1 |

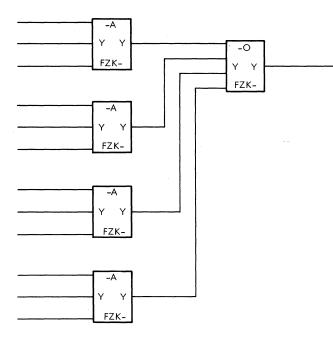

| Four Diode-Coupled 3-Way AND Circuit, Type FZK. | • | B-1 |

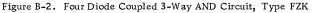

| Video Mixer, Type EFY                           |   | B-1 |

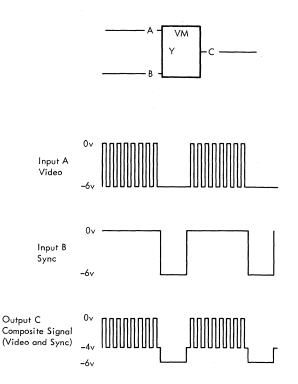

| Sense Gate and Output Sense Level, Type FYZ     |   | B-2 |

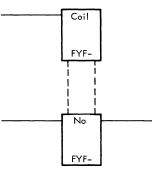

| Reed Relay, Type FYF                            | • | B-3 |

| Reed Relay, Type YPM                            | • | B-3 |

| APPENDIX C LANGUAGE FEATURES                    |   | C-1 |

| Feature Description                             |   | C-1 |

| Identification and Instruction Label Changes    |   | C-1 |

| Character Codes                                 |   | C-1 |

| Character Generator Modification                |   | C-1 |

| 1053 Printer Print Element                      |   | C-1 |

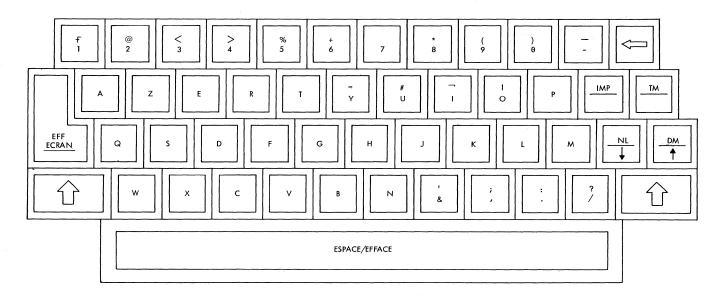

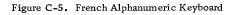

| Keyboard Changes                                |   | C-1 |

| French Keyboard                                 |   | C-1 |

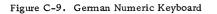

| German Keyboard                                 |   | C-1 |

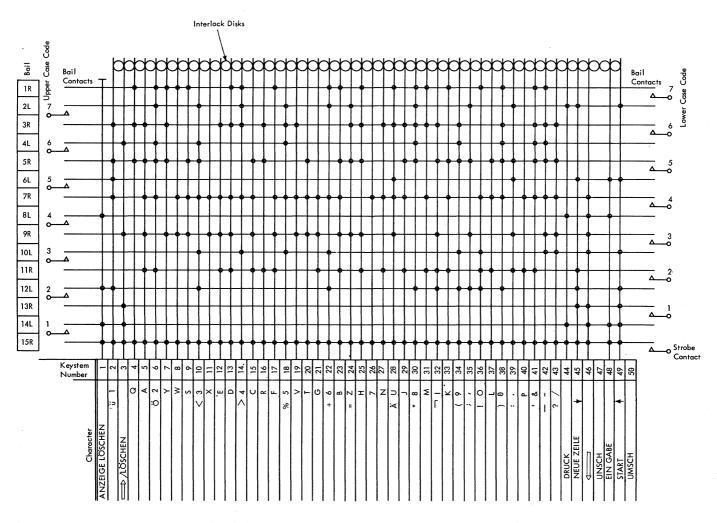

| United Kingdom Keyboard                         |   | C-2 |

|                                                 | • | 0-2 |

| INDEX                                           | • | X-1 |

#### ILLUSTRATIONS

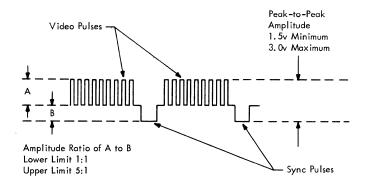

|   | 2-2  | Composite Video Signal (One Vertical      |       |  |

|---|------|-------------------------------------------|-------|--|

|   |      | Scan)                                     | 2-3   |  |

|   | 2-3  | Cathode-Ray Tube                          | 2-3   |  |

|   | 2-4  | CRT Electron Gun                          | 2-4   |  |

|   | 2-5  | Deflection Coil Currents and Raster       |       |  |

|   |      | Relationship                              | 2-6   |  |

|   | 2-6  | Persistence Characteristics of P4 and P39 |       |  |

|   |      | Phosphors                                 | 2-7   |  |

| I | 2-7  | Display Station, Electrical Schematic     |       |  |

| I |      | Diagram for DS Using Older Level          |       |  |

|   |      | Circuit Boards                            | 2-9   |  |

|   | 2-7A | Display Station Electrical Schematic      |       |  |

| I |      | Diagram for DS Using Tube Adapters        | 2-14A |  |

| l | 2-7B | Display Station Electrical Schematic      |       |  |

| I |      | Diagram for DS Using Newer Level          |       |  |

| ł |      | Circuit Boards                            | 2-14C |  |

|   | 2-8  | Display Station, Power Supply For 50-     |       |  |

|   |      | Cycle Operation                           | 2-14E |  |

|   | 2-9  | Display Station Timing                    | 2-15  |  |

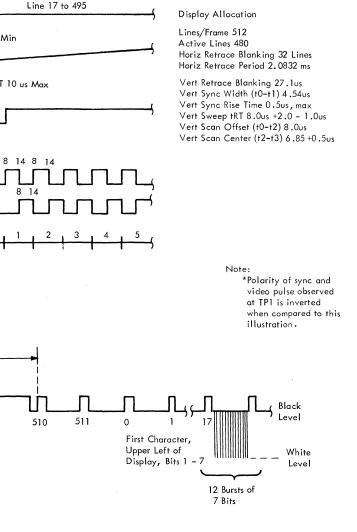

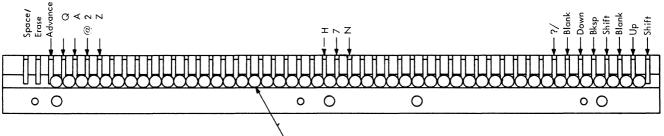

|   | 2-10 | Alphanumeric Keyboard, Bottom and         |       |  |

|   |      | Rear Views                                | 2-19  |  |

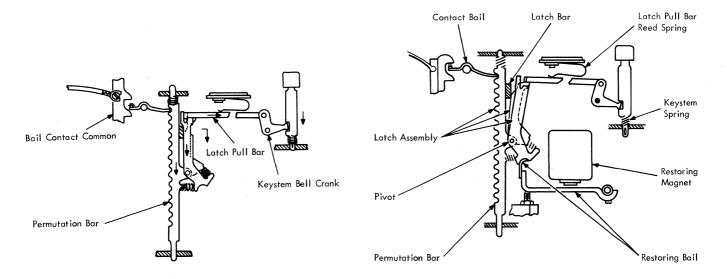

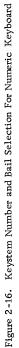

|   | 2-11 | Key Position                              | 2-20  |  |

|   | 2-12 | Permutation Bar and Keyboard Latch        |       |  |

|   |      | (Normal)                                  | 2-20  |  |

|   | 2-13 | Permutation Bar and Keyboard Latch        |       |  |

|   |      | (Tripped)                                 | 2-20  |  |

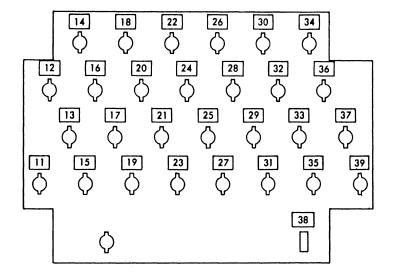

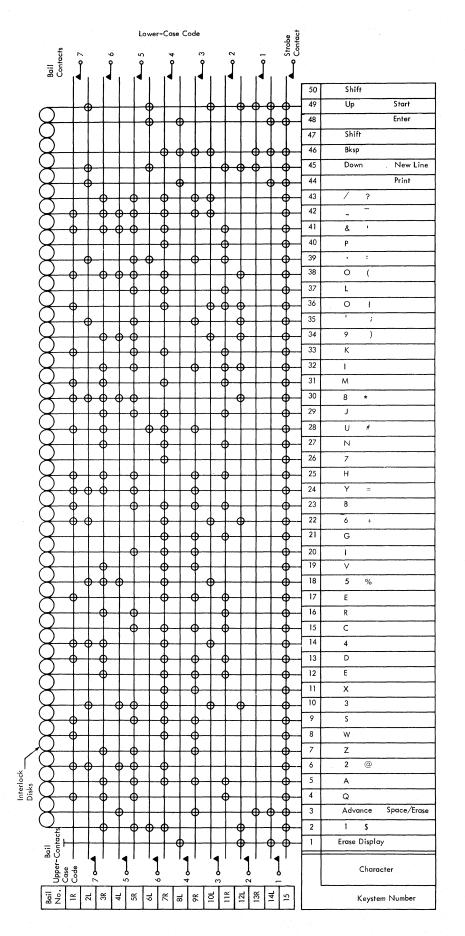

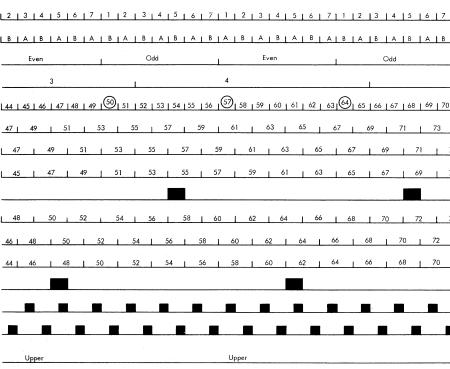

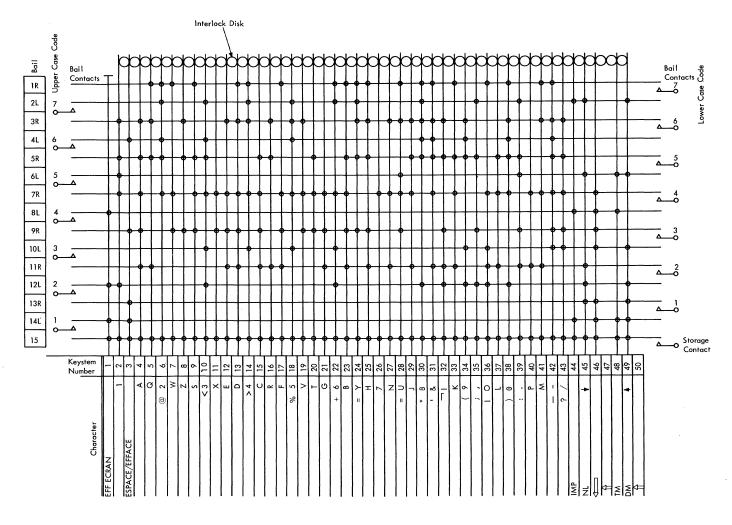

|   | 2-14 | Keystem Numbering Chart                   | 2-21  |  |

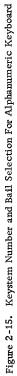

|   | 2-15 | Keystem Number and Bail Selection For     |       |  |

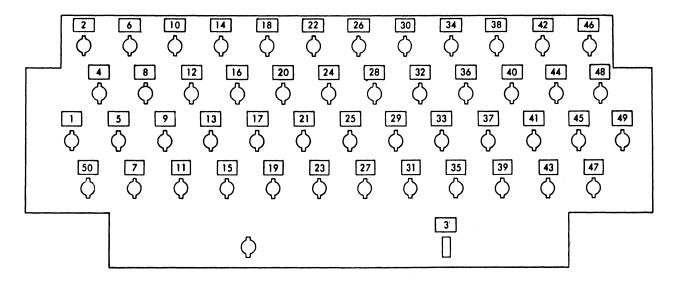

|   |      | Alphanumeric Keyboard                     | 2-22  |  |

|   |      |                                           |       |  |

2260/2848 - 60,000S FETOM (3/68) v

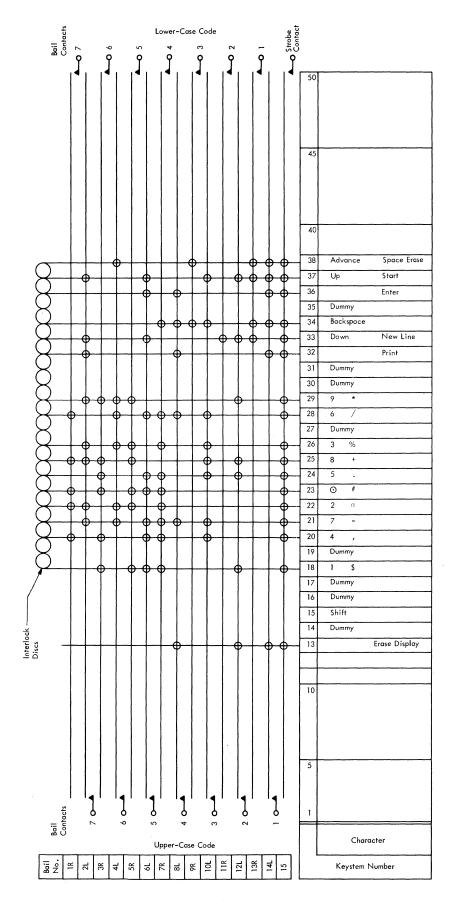

| 2-16         | Keystem Number and Bail Selection for       |              | 2-59           | Common Buffer Register • • • •                                               | 2-75                  |

|--------------|---------------------------------------------|--------------|----------------|------------------------------------------------------------------------------|-----------------------|

|              | Numeric Keyboard                            | 2-23         | 2-60           | Common Buffer Register Input Signals .                                       | 2-76                  |

| 2-17         | Key Position (Latched and Tripped)          | 2-24         | 2-61           | Common Buffer Register Controls                                              | 2-77                  |

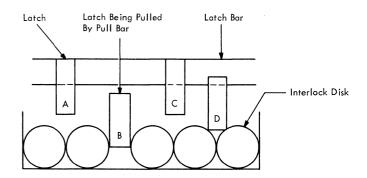

| 2-18         | Interlock Disks                             | 2-25         | 2-62           | SOM, New Line, and EOM Decode                                                |                       |

| 2-19         | Interlock Disks (Partial)                   | 2-25         | 0.62           | Circuit                                                                      | 2-79                  |

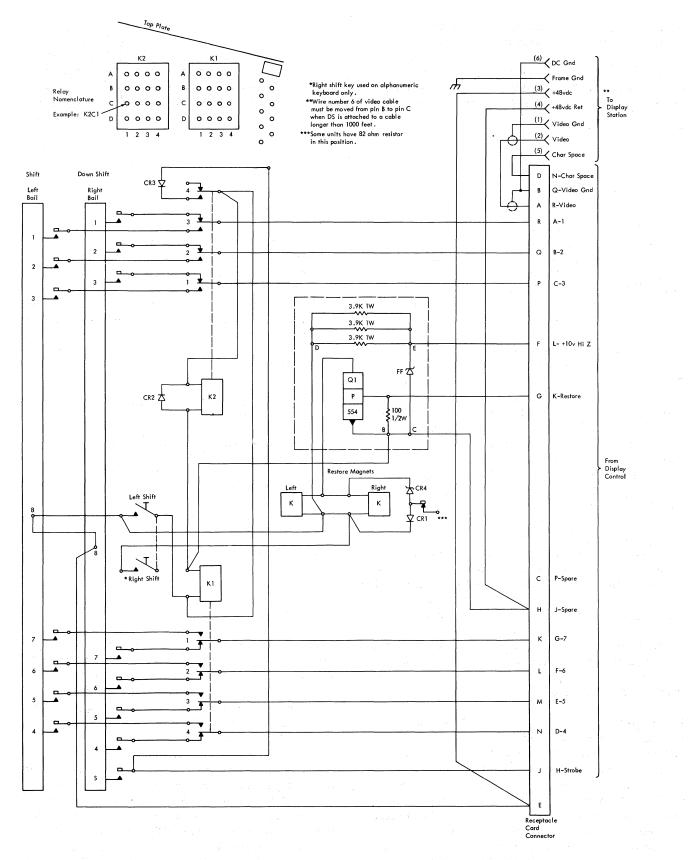

| 2-20         | Keyboard Electronics                        | 2-26         | 2-63<br>2-64   | Common Buffer Register Control Codes .                                       | 2-80                  |

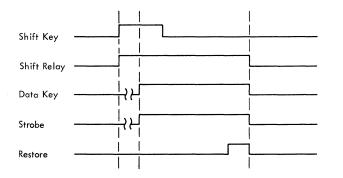

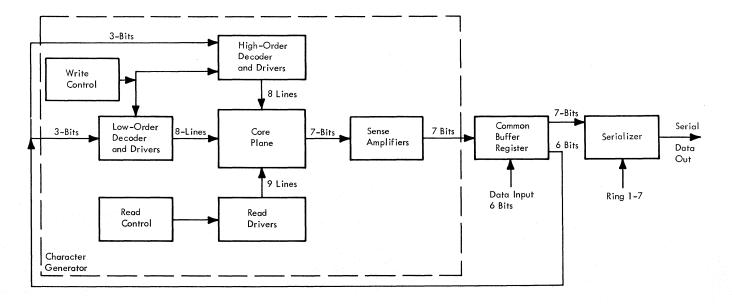

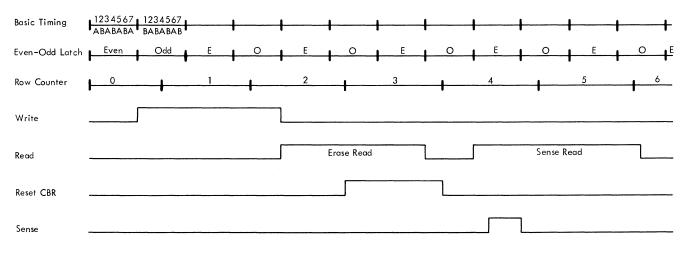

| 2-21         | Keyboard Data Transfer Timing               | 2-27         | 2-64           | Character Generator, Block Diagram.                                          | 2-80                  |

| 2-22         | Display Control, Simplified Block           | <b>a a a</b> | 2-66           | Character Generator Timing                                                   | 2-81                  |

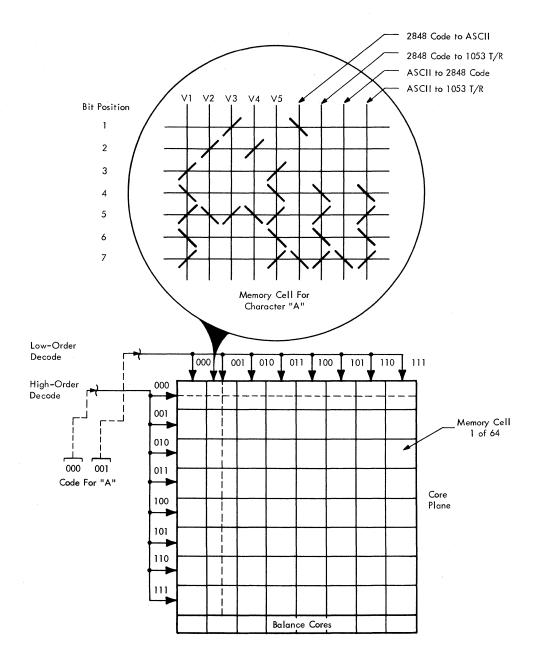

| 0.00         | Diagram                                     | 2-28         | 2-67           | Core Plane Layout and Cell Selection .<br>Selection, Read, and Sense Winding | 2-82                  |

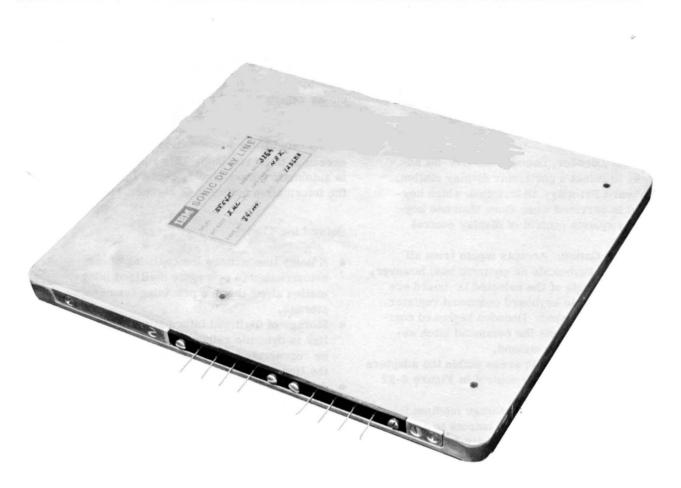

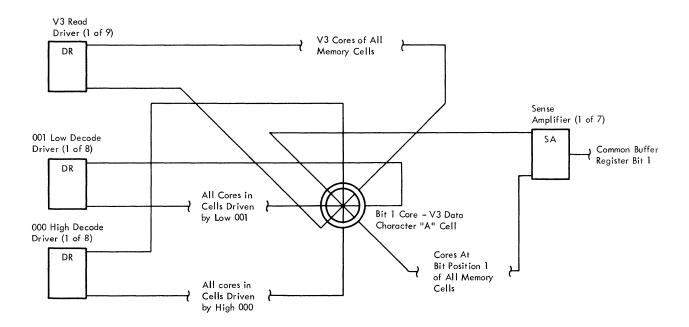

| 2-23         | Delay Line Module                           | 2-30         | 2-07           | Connections                                                                  | 2-83                  |

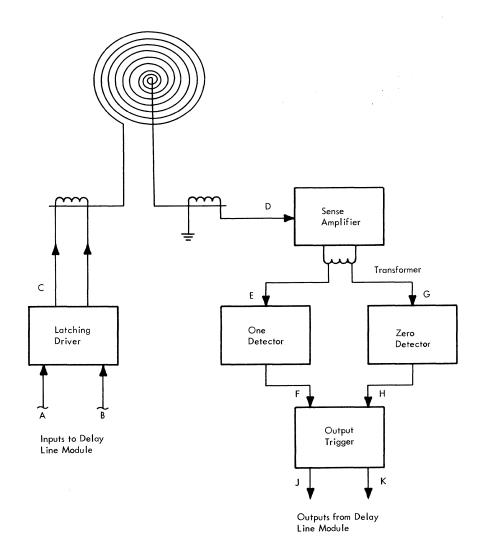

| 2-24         | Delay Line Module, Simplified Block         | 2-31         | 2-68           | Generation of Binary Data from Memory                                        | 2-05                  |

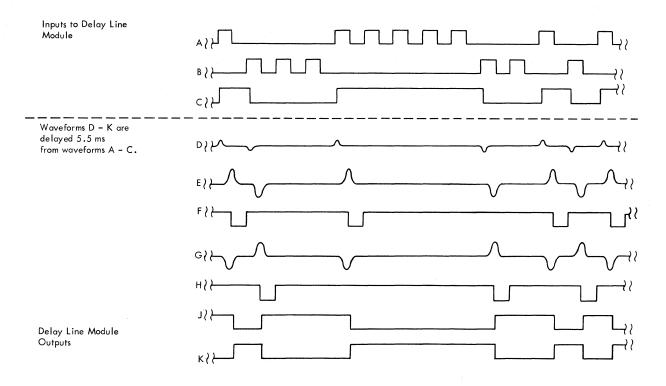

| 0.05         | Diagram                                     |              | 2 00           | Cell                                                                         | 2-83                  |

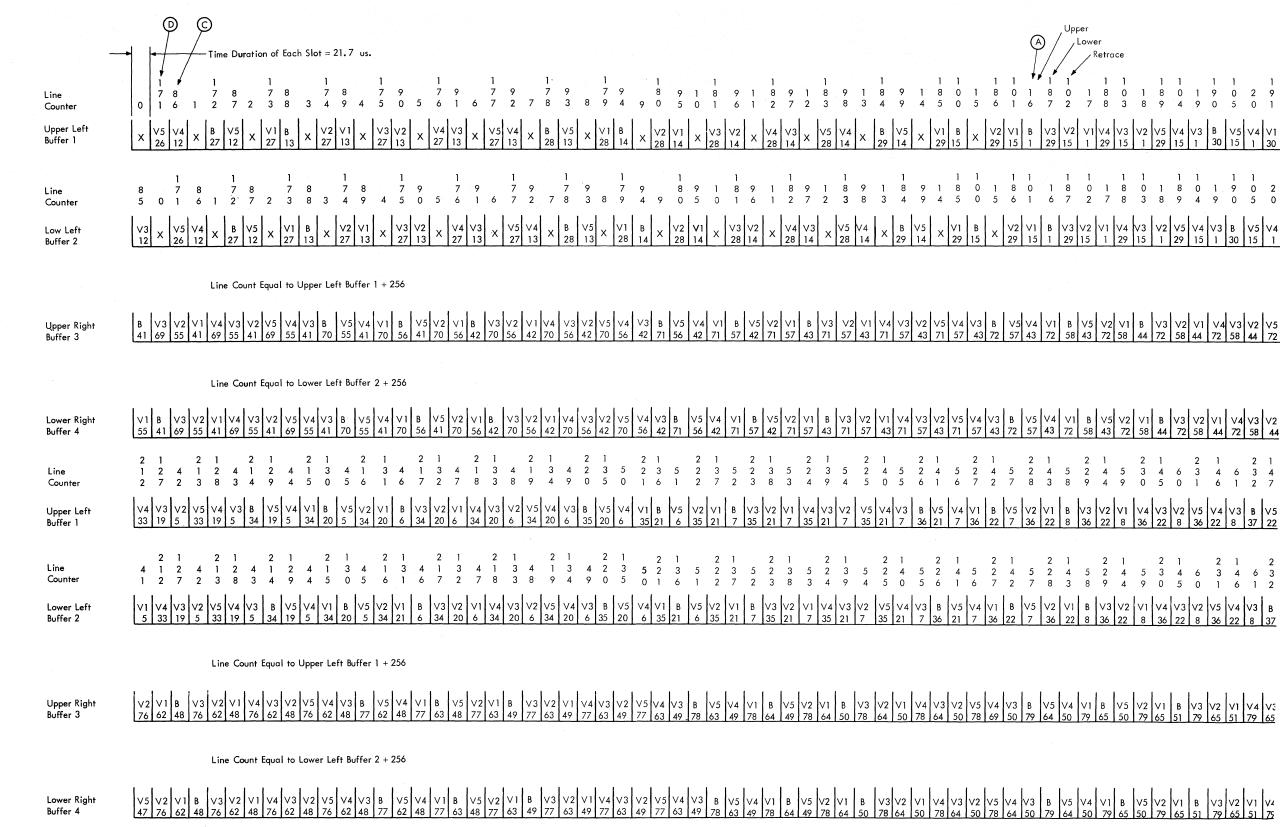

| 2-25<br>2-26 | Delay Line Timing                           | 2-32<br>2-33 | 2-69           | Low Order Decoder and Driver                                                 | 2-83<br>2 <b>-</b> 84 |

| 2-20         | Buffer Slot Layout                          | 2-35         | 2-70           | Character Generator Write Control                                            | 2-85                  |

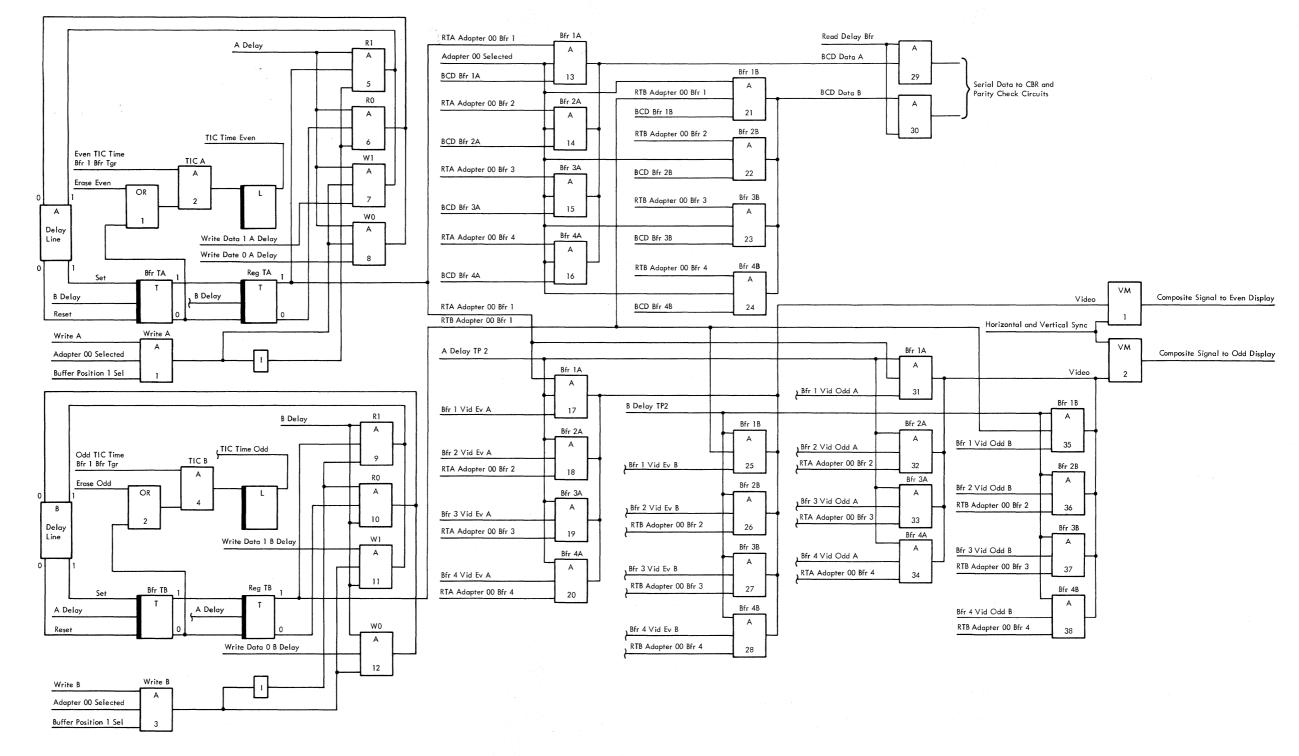

| 2-21         | Delay Line Controls and BCD-Video<br>Gating | 2-37         | 2-71           | Character Generator Read Control                                             | 2 00                  |

| 2-28         | Delay Line Control Timing                   | 2-37         |                | Circuits                                                                     | 2-87                  |

| 2-29         | Delay Line Timing, One Slot                 | 2-39<br>2-41 | 2-72           | Function of Position Storage Circuits                                        | 2-89                  |

| 2-20         | Keyboard Assignments for Model 3            | 6-41         | 2-73           | Counter Storage Control                                                      | 2-90                  |

| 2-30         | Machines                                    | 2-43         | 2-74           | Counter Storage Control Outputs                                              | 2-91                  |

| 2-31         | Keyboard Priority                           | 2-43         | 2-75           | Row Counter Storage                                                          | 2-93                  |

| 2-32         | Keyboard Controls and Keyboard Data         | 2-45         | 2-76           | Vertical Segment and Column Storage on                                       |                       |

| 2 32         | Bit Conversion and Gating                   | 2-44         |                | Compare                                                                      | 2-95                  |

| 2-33         | Timing and Clock Circuits, Simplified       |              | 2-77           | Generation and Purpose of Save Line                                          |                       |

| 2 33         | Block Diagram                               | 2-45         |                | Counter Signals                                                              | 2-97                  |

| 2-34         | Oscillator and A-B Delay Pulse Circuit .    | 2-46         | 2-78           | Buffer Selection and Display Compare .                                       | 2-99                  |

| 2-35         | Bit Ring Counter                            | 2-48         | 2-79           | Video Buffer Selection, A delay                                              | 2-101                 |

| 2-36         | Even-Odd Display Trigger Circuit            | 2-49         | 2-80           | Video Buffer Selections for A Delays                                         | 2-102                 |

| 2-37         | Buffer Parity Control Circuit               | 2-49         | 2-81           | Nondestructive Cursor Generation                                             | 2-103                 |

| 2-38         | Row Counter                                 | 2-50         | 2-82           | Display of NDC Cursor - Even and Odd .                                       | 2-104                 |

| 2-39         | Segment Counter                             | 2-51         | 2-83           | Write DS Line Address Decode and                                             |                       |

| 2-40         | Character Display Column Ring Counter.      | 2-52         |                | Gating                                                                       | 2-105                 |

| 2-41         | Line Counter                                | 2-53         | 2-84           | Write Line Address Decoder Operation $\bullet$                               | 2-106                 |

| 2-42         | Sync Generator                              | 2-55         | 2-85           | Keyboard Command Decoder and                                                 |                       |

| 2-43         | Sync Generator Timing                       | 2-56         |                | Command Latches • • • • • • •                                                | 2-107                 |

| 2-44         | Sync Pulse Widths                           | 2-56         | 2-86           | Parity Circuits                                                              | 2-109                 |

| 2-45         | Reset Controls                              | 2-58         | 2-87           | Printer Adapter Controls                                                     | 2-111                 |

| 2-46         | TIC Sample Time Decoding                    | 2-59         | 2-88           | Control Latches and Trigger Functions                                        |                       |

| 2-47         | TIC Sample Decoding, Buffer 1 and 2 .       | 2-61         |                | (3 Sheets)                                                                   | 2-113                 |

| 2-48         | Function of TIC Sample Decoder Circuit      |              | 2-89           | Channel Interface Controls                                                   | 2-116                 |

|              | Groups                                      | 2-62         | 2-90           | Out Tag Delays                                                               | 2-117                 |

| 2-49         | Use of Character Column Outputs as          |              | 2-91           | Address In Latch                                                             | 2-119                 |

|              | Character Generator Read Gates              | 2-63         | 2-92           | Status In Latch                                                              | 2-120                 |

| 2-50         | Display Addressing                          | 2-64         | 2-93           | Remote End, Local-Remote                                                     | 2-121                 |

| 2-51         | Address Encoder Outputs                     | 2-65         | 2-94           | Command Chaining, Inhibit Attention .                                        | 2-122                 |

| 2-52         | Write A and Write B Latches, Timing         |              | 2-95           | Disconnect and Reset                                                         | 2-123                 |

|              | Chart                                       | 2-66         | 2-96           | Hold-Select Circuit for Units not Equipped                                   |                       |

| 2-53         | Write A and Write B Latches                 | 2-67         |                | with Isolation Feature                                                       | 2-124                 |

| 2-54         | Even and Odd Display Signals, Timing        |              | 2 <b>-</b> 96A | Hold-Select Circuit for Units Equipped                                       | 1                     |

|              | Chart                                       | 2-70         |                | with Isolation Feature                                                       | 2 <b>-</b> 124A       |

| 2-55         | Serializer, A Delay                         | 2-71         | 2-97           | Control Unit and Device Addressing                                           | 2-127                 |

| 2-56         | Serializer, B Delay                         | 2-72         | 2-98           | Command Byte Format                                                          | 2-129                 |

| 2-57         | Serializer Data and Inputs and Even-Odd     |              | 2-99           | Command Decode                                                               | 2-130                 |

|              | Bit Sequences                               | 2-73         | 2-100          | I/O Request                                                                  | 2-131                 |

| 2-58         | Deserialization of Delay Line Data at       |              | 2-101          | Character Register Control                                                   | 2-132                 |

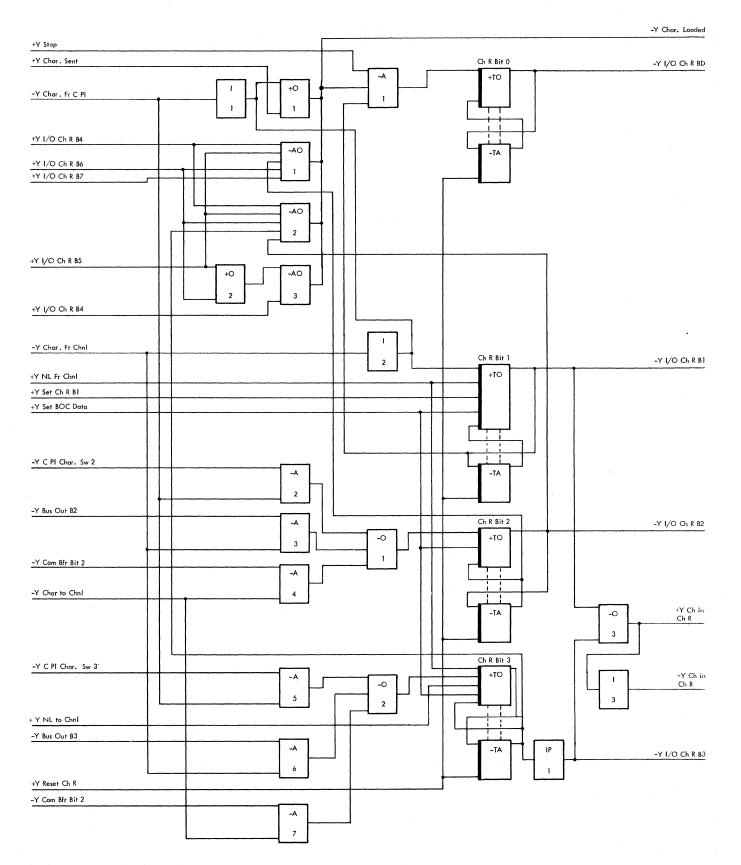

|              | CBR Inputs • • • • • • • • •                | 2-74         | 2-102          | Character Register Bits 0-3                                                  | 2-134                 |

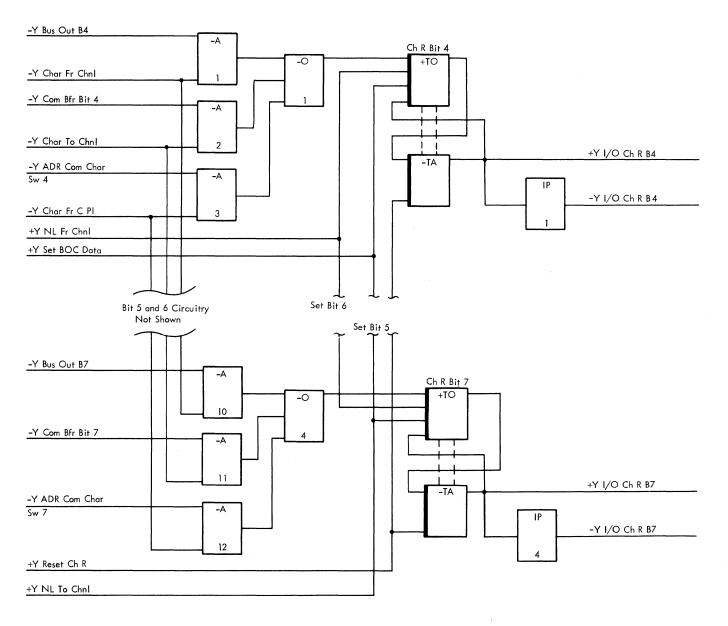

|              |                                             |              | 2-103          | Character Register Bits 4-7                                                  | 2-135                 |

|              |                                             |              |                |                                                                              |                       |

.

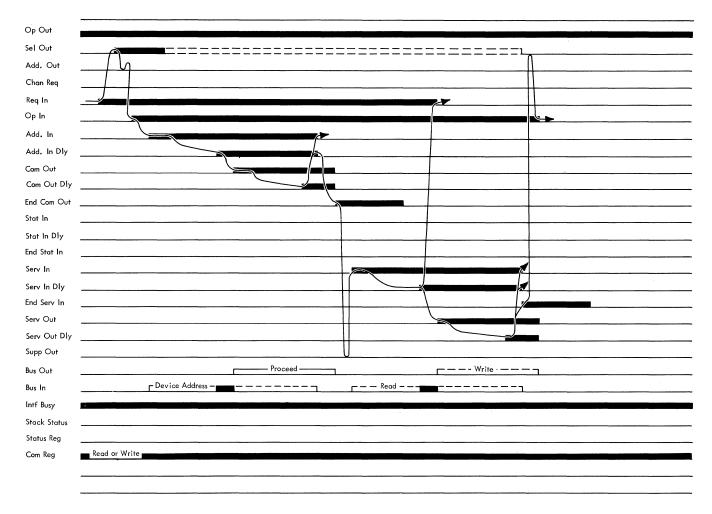

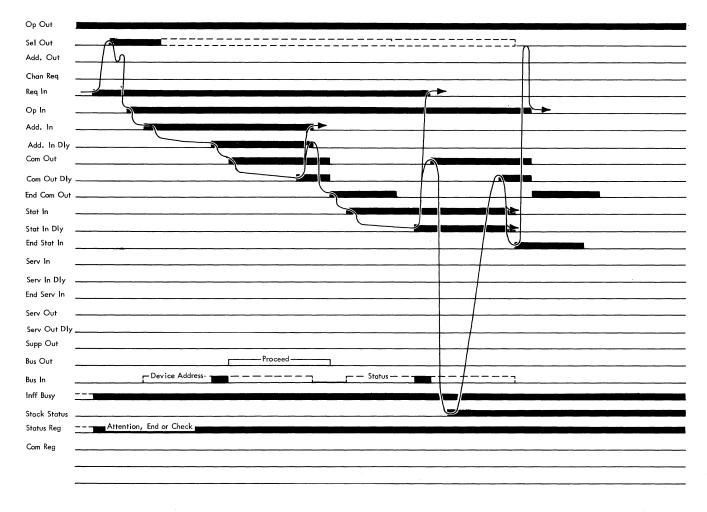

| 2-104      | Channel-Initiated Selection (Read or  |               |

|------------|---------------------------------------|---------------|

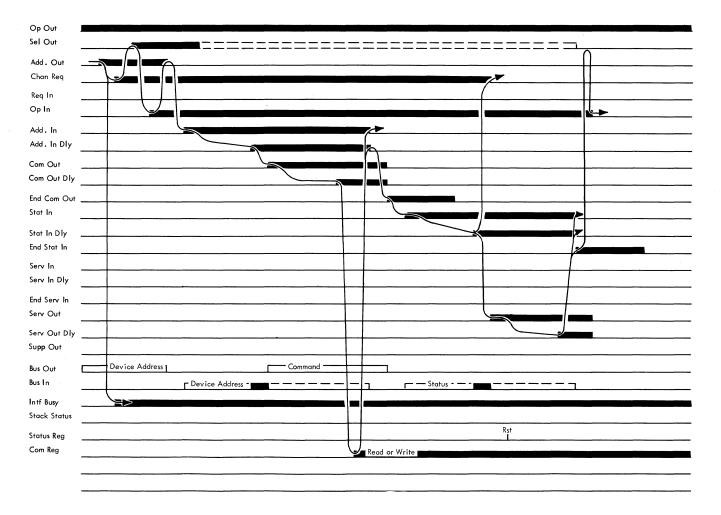

| 2-104      | Write)                                | 2-136         |

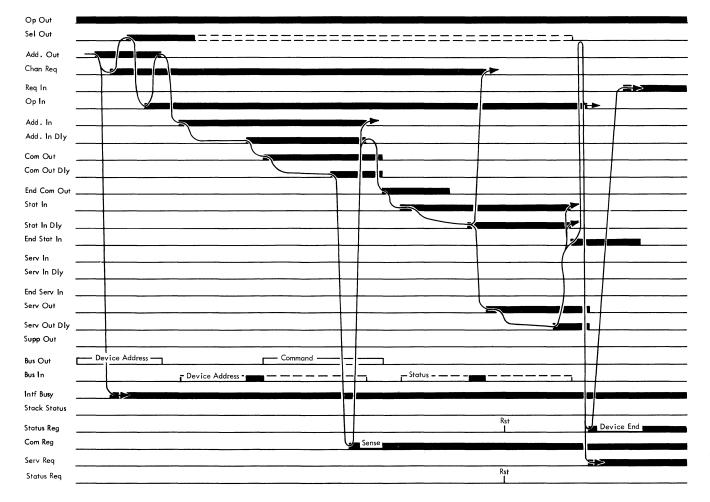

| 2-105      | Sense Operation                       | 2-137         |

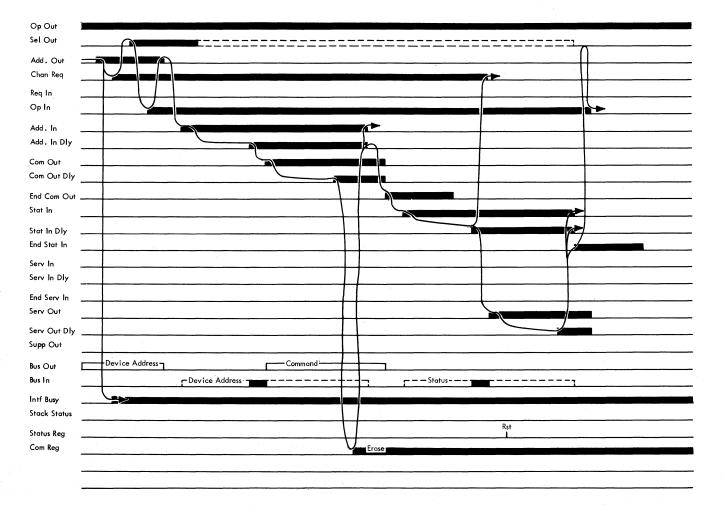

| 2-106      | Erase Operation                       | 2-138         |

| 2-107      | No Op Operation • • • • • • • •       | 2-139         |

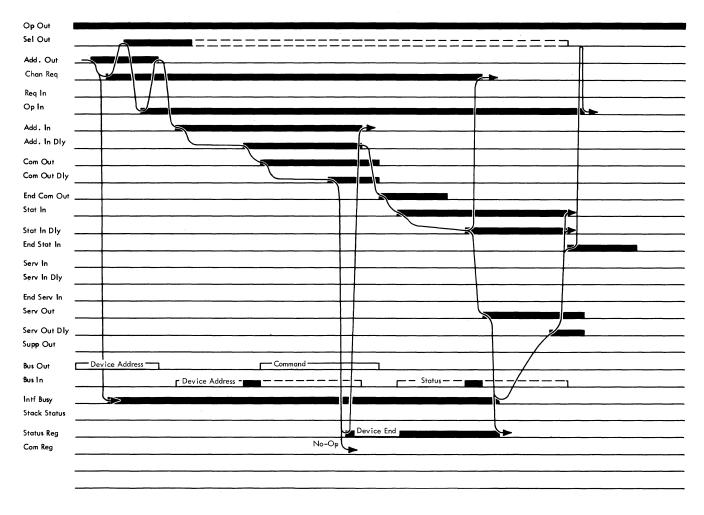

| 2-108      | Test I/O Operation                    | 2-140         |

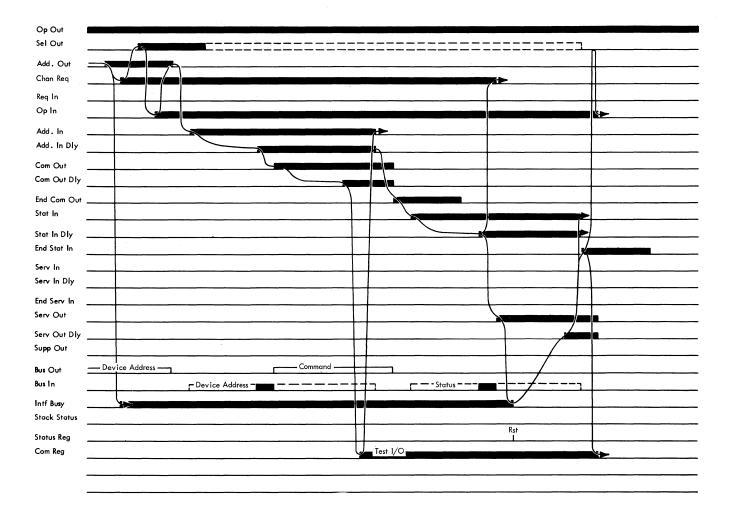

| 2-103      | Test I/O To Busy Device               | 2-141         |

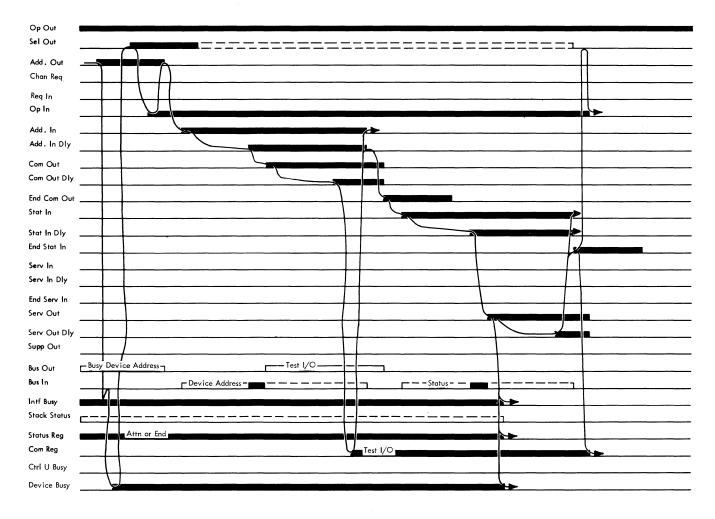

| 2-110      | Control Unit Busy Sequence            | 2-142         |

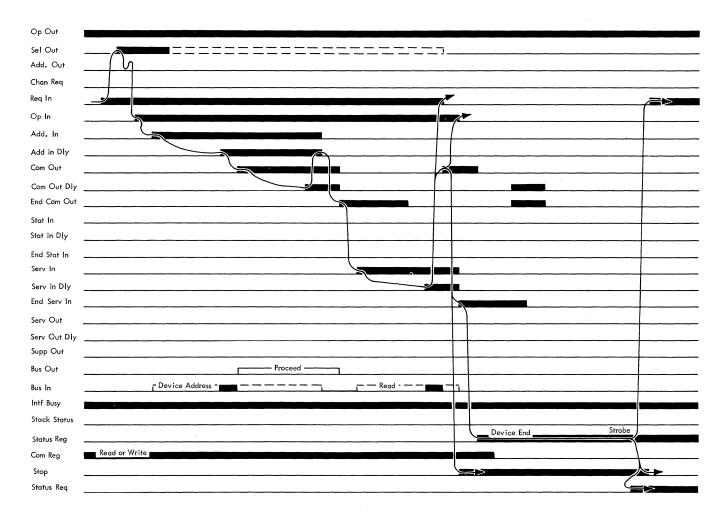

| 2-111      | Control Unit Initiated Data Transfer  | 6 116         |

| 2          | (Read or Write)                       | 2-143         |

| 2-112      | Sense Transfer                        | 2-144         |

| 2-112      | Status Transfer                       | 2-145         |

| 2-114      | Stack Status Sequence                 | 2-143         |

| 2-115      | Stop Sequence                         |               |

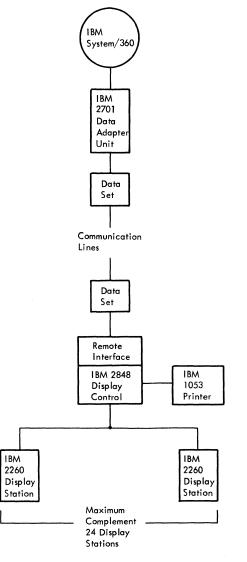

| 2-115      | Printer Adapter, Simplified Block     | 2-140         |

| 2-110      | Diagram                               | 2-149         |

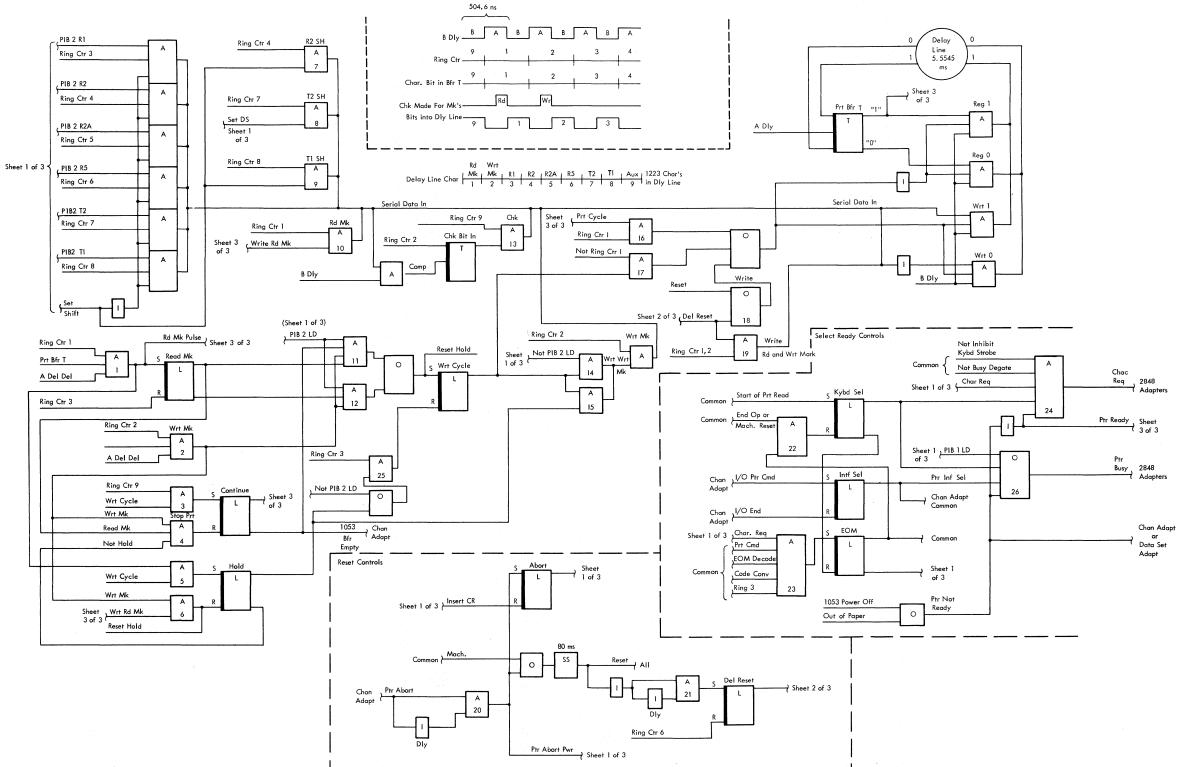

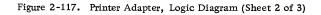

| 2-117      | Printer Adapter, Logic Diagram        | 2-149         |

| 2-117      | (3 Sheets)                            | 2-153         |

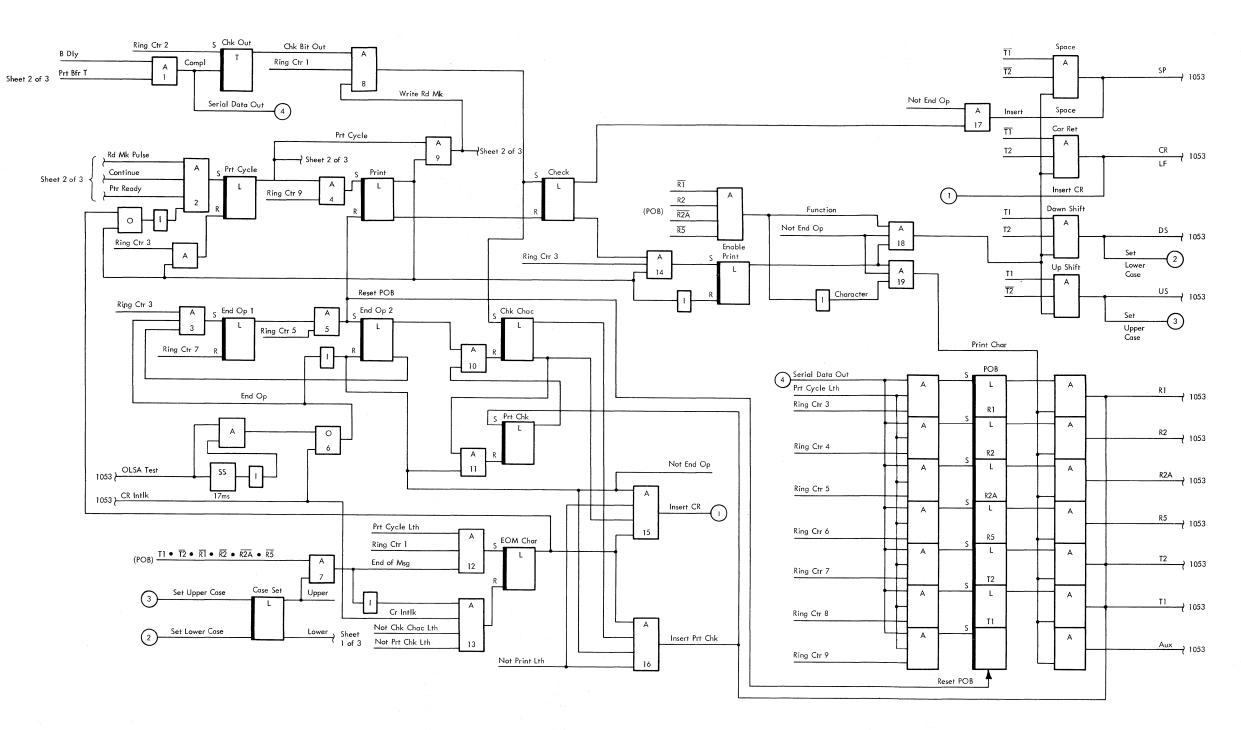

| 4-1        | Remote Display Complex Configuration. | 2-155<br>4-1  |

| 4-1<br>4-2 | ASCII-8 Code Set                      | 4-3           |

| 4-2        | Ten-Bit Format of Transmitted ASCII   | 4-3           |

| 4-3        | Characters                            | 4-4           |

| 4-4        | Typical Remote Device Address Assign- | 4-4           |

| 4-4        | ments                                 | 4-5           |

| 4-5        | 2848-2260 Commands (Remote)           | 4-5<br>4-6    |

| 4-5<br>4-6 | Sequence/Response Diagram - Specific  | 4-0           |

| 4-0        | Poll to 2260 DS                       | 4-7           |

| 4-7        | Sequence/Response Diagram - Specific  | 4-7           |

| 4-7        | Poll to Printer                       | 4-8           |

| 4-8        | Sequence/Response Diagram - General   | 4-0           |

| 4-0        | Poll                                  | 4-9           |

| 4-9        | Sequence/Response Diagram – Read      | - <b>-</b> -9 |

| 4-9        | Addressed Full DS Buffer              | 4-11          |

| 4-10       | Sequence/Response Diagram - Write     | 4-11          |

| 4-10       | Addressed DS                          | 4-12          |

| 4-11       | Sequence/Response Diagram - Erase/    | L             |

|            | Write                                 | 4-14          |

| 4-12       | Sequence/Response Diagram - Write     | 1 11          |

| 4-12       | Printer                               | 4-15          |

| 4-13       | Sequence/Response Diagram - Line      | - 10          |

| 1 10       | Address Write                         | 4-16          |

| 4-14       | Display Line Addresses (Remote)       | 4-17          |

| 4-15       | Remote Interface Adapter, Data Flow   | 1 -1          |

| 1 10       | Diagram                               | 4-20          |

| 4-16       | Command Decoder Function Codes        | 4-24          |

| 4-17       | Character Register Control            | 4-31          |

| 4-18       | Channel Response - SOH-EOT and DC     | 1 01          |

| ~ ~~       | Address Characters                    | 4-32          |

| 4-19       | Channel Response - Device Address     | 1 02          |

|            | Character                             | 4-33          |

| 4-20       | Channel Response - Command Character  | 1 00          |

|            |                                       | 4-35          |

| 4-21       | Remote Interface Response – ACK       |               |

|            | Character                             | 4-36          |

| 4-22       | Channel Response - STX Character      | 4-37          |

| 4-23       | Channel Response - Text Character     | 4-39          |

| 4-24       | Delay Line Readout Control (2 Sheets) | 4-40          |

|            |                                       |               |

|            |                                       |               |

|   | Channel Deserves FTTY and IDC               |      |    |              |

|---|---------------------------------------------|------|----|--------------|

|   | Channel Response - ETX and LRC<br>Character |      |    | 4-42         |

|   |                                             | •    | •  | 4-42<br>4-44 |

|   | Write Printer Control                       | •    | •  | 4-44<br>4-47 |

|   | I/O Request Control                         |      | •  | 4-48         |

|   | 2848 DC Response - STX Character            | :    | •  | 4-49         |

|   | 2848 DS Response - Device Address           |      |    | 4-50         |

|   | Read Operation - Common Buffer to           |      | •  |              |

|   | Serializer Transfer                         |      |    | 4-52         |

|   | 2848 DC Response - ETX Character            |      |    | 4-54         |

|   | Read Operation - Buffer Parity Chec         |      |    |              |

|   | Control                                     |      |    | 4-55         |

|   | 2848 DC Response - LRC Character            |      | •  | 4-56         |

|   | Write/Erase Command                         |      | •  | 4-58         |

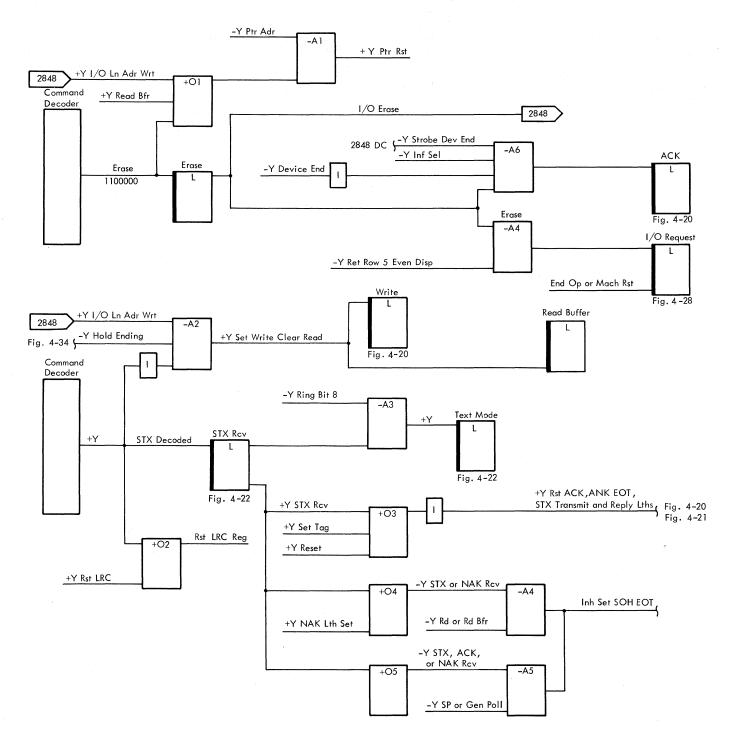

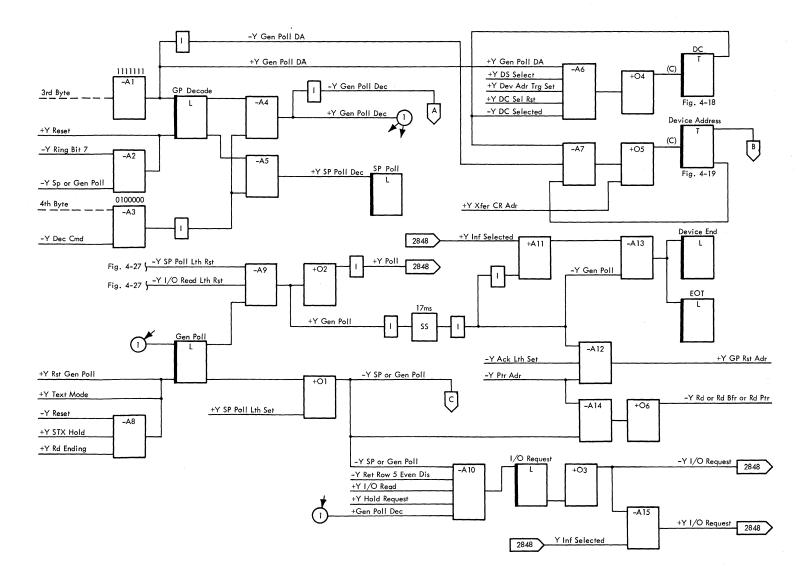

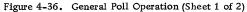

|   | General Poll Operation (2 Sheets).          |      | •  | 4-60         |

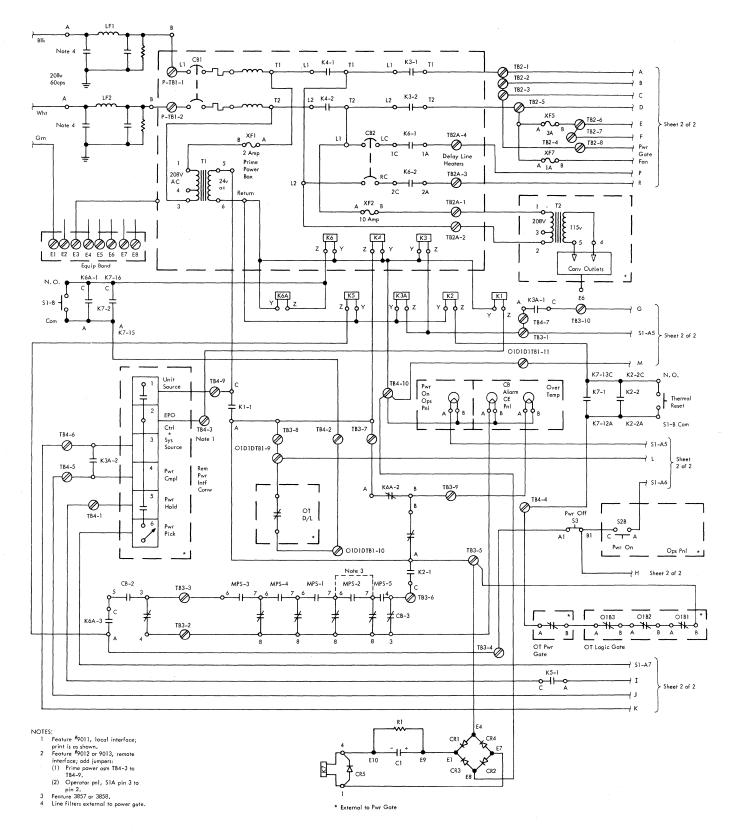

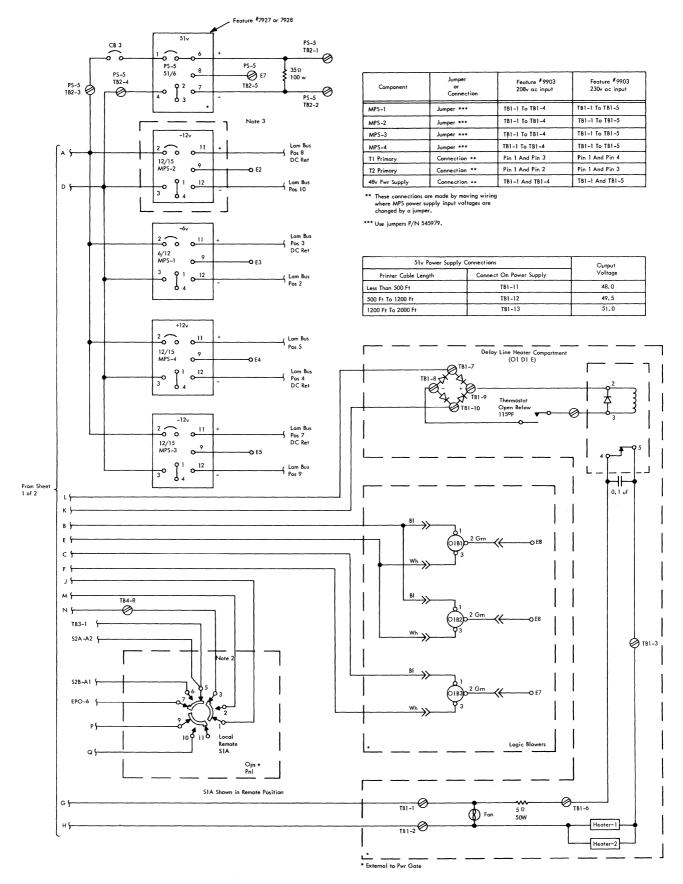

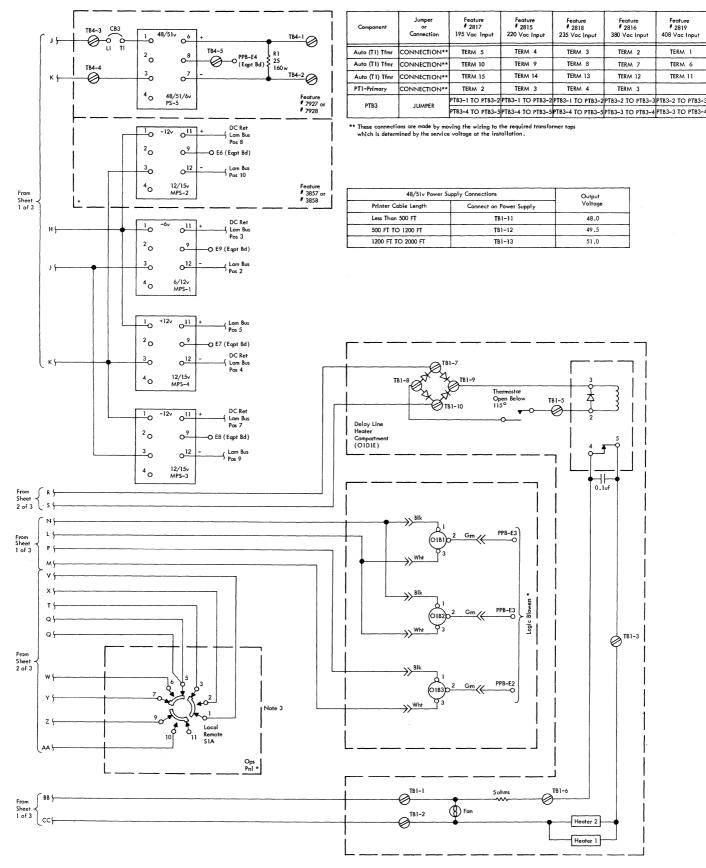

|   | 60-Cycle Power Distribution and Co          | ntro | 51 |              |

|   | (2 Sheets)                                  |      |    | 5-2          |

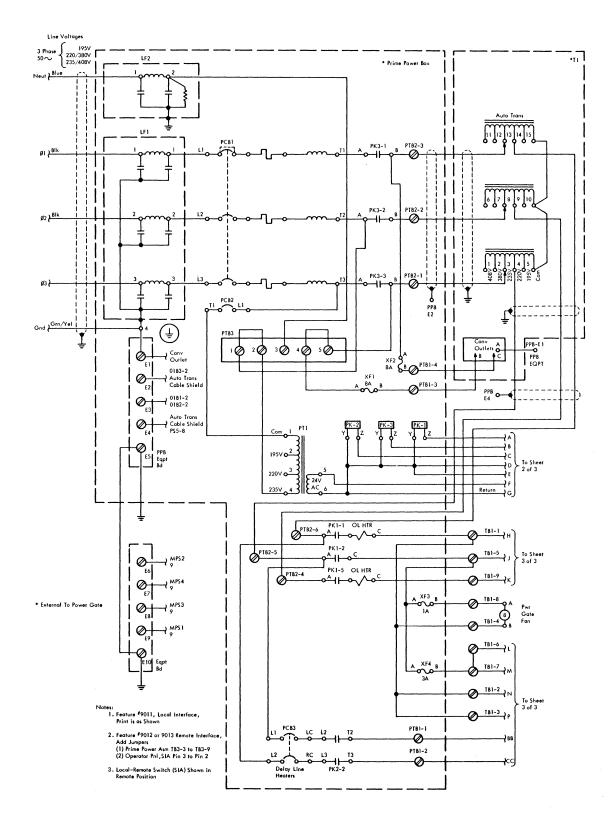

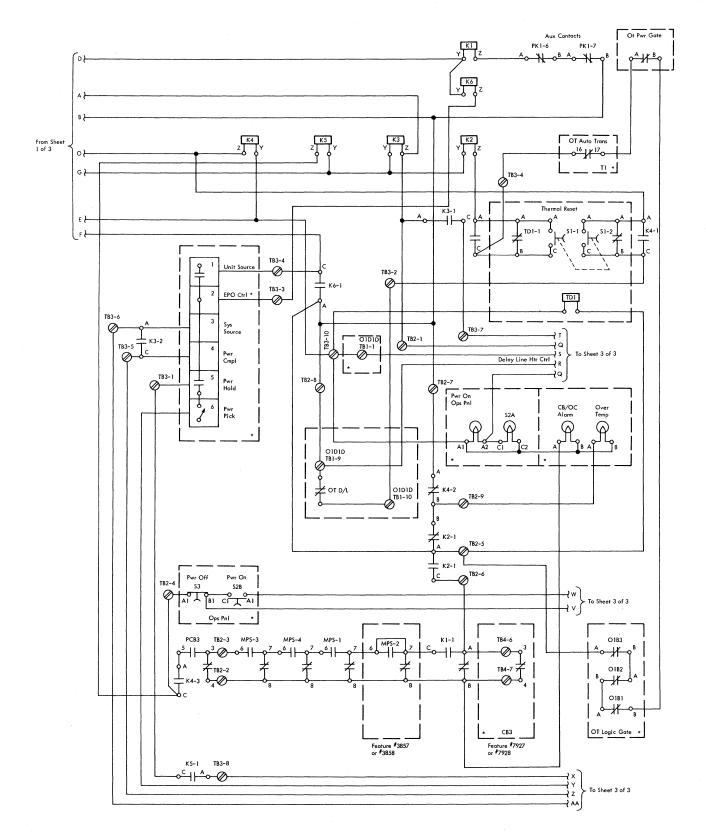

|   | 50-Cycle Power Distribution and Con         | ntro | ol |              |

|   | (3 Sheets)                                  |      | •  | 5-5          |

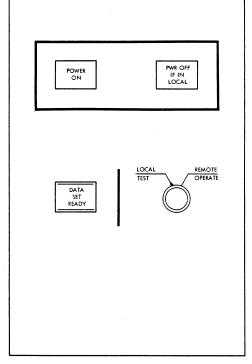

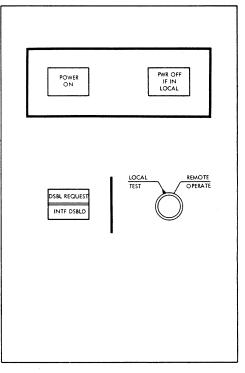

|   | Operator's Panel - IBM 2848                 |      | •  | 6-1          |

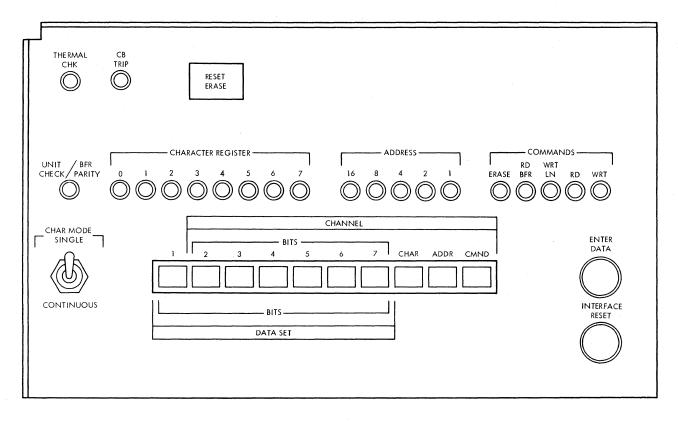

|   | CE Panel - IBM 2848                         |      | •  | 6-2          |

|   | 2848 Display Control Operator's Pan         | el   |    |              |

|   | Controls and Indicators                     | •    | •  | 6-3          |

|   | 2848 Display Control CE Panel Control       | rols |    |              |

|   | and Indicators                              | •    | •  | 6-4          |

|   | 2260 Display Station Alphanumeric           |      |    |              |

| - | Keyboard                                    | •    | •  | 6 <b>-</b> 5 |

|   | 2260 Display Station Numeric Keybo          | oard | 1. | 6-5          |

|   | Function of 2260 DS Control Keys (2         |      |    |              |

|   | Sheets)                                     | •    | •  | 6-6          |

|   | Integrator Card A, Type FYM                 | •    | •  | B-1          |

|   | Four Diode Coupled 3-Way AND Cir            | cui  | t, |              |

|   | Туре FZК                                    | •    | •  | B-2          |

|   | Video Mixer, Type EFY                       | •    | •  | B-2          |

|   | Output Sense Level and Sense Gate,          |      |    |              |

|   | Туре FYZ                                    | •    | •  | B-3          |

|   | Reed Relay, Type FYF                        | •    | •  | B-3          |

|   | Reed Relay, Type YPM                        | ٠    | •  | B <b>-3</b>  |

|   | Identification and Instruction Label        |      |    |              |

|   | Summary                                     | •    | •  | C-2          |

|   | Language Feature Character Codes            | •    | •  | C-3          |

|   | 1053 Printer Typehead, Language Sy          | mb   | ol |              |

|   | and Character Variations                    | •    | •  | C-3          |

|   | Graphic Character and Function Key          |      |    |              |

|   | Change Summary                              | •    | •  | C-3          |

|   | French Alphanumeric Keyboard .              | •    | •  | C-4          |

|   | French Numeric Keyboard                     | •    | •  | C-4          |

|   | Keystem Number and Bail Selection           | 1,   |    |              |

|   | French Alphanumeric Keyboard .              | •    | •  | C-5          |

|   | German Alphanumeric Keyboard .              | •    | •  | C-5          |