# Systems Reference Library

# IBM 1801 and 1802 Processor-Controllers Original Equipment Manufacturers' Information

This Original Equipment Manufacturers' Information (OEMI) manual provides the definitions and functional descriptions of the interface lines for the IBM 1801/1802 I/O Interface. In addition, it contains electrical, mechanical, and cabling considerations and specifications of this interface. It is assumed that the reader of this manual is engineering oriented and understands computer engineering techniques and terminology.

# Preface

This document provides information of interest to designers and manufacturers of equipment to be attached to the IBM 1801/1802 Processor-Controllers. The responsibility of IBM resulting from such an attachment is defined in the *Multiple Supplier System Bulletin*, Order No. G120-6648.

The 1801/1802 I/O interface is a communication link between channel elements and I/O adapters in the IBM 1800 System. It provides an information format and control signal sequence capability as well as a uniform means of attaching and controlling various types of I/O devices.

Information in the form of data, status and sense information, control signals and I/O device addresses, is transmitted in both directions over the signal control lines of this interface. All transmissions are interlocked with corresponding response signals permitting the processorcontroller (independent of the I/O transfer) to continue execution of other instructions.

The design of this interface provides these important features:

Ease of input/output programming over a wide range of ... control units.

- Ready connection of both IBM and non-IBM designed control units to the IBM 1800 System.

- Ability to accommodate all future control units designed with the parameters of this interface.

- An interlocked interface operation that is not timedependent; this permits broad ranges of control unit attachments.

- An operation uniformly applicable to both multiplex and data channel operations as well as to channel-tochannel transmission and control operations.

This Original Equipment Manufacturers' Information (OEMI) manual provides a functional description of these lines together with the electrical, mechanical and cabling considerations, and specifications of the interface. It defines the interfaces between the I/O adapters in the 1801/ 1802 and the I/O devices.

All descriptions and data in this manual are subject to modification as a result of engineering developments.

#### **Related Literature**

The *IBM 1800 Data Acquisition and Control System Bibliography*, Order No. GA26-5921 lists the available reference publications for the 1800 System and associated I/O devices. The *IBM 1800 Installation Manual-Physical Planning*, Order No. GA26-5922 contains additional information and descriptions concerning process I/O interfaces.

#### Fourth Edition (March 1970)

This publication Order No. GA26-3591-3 is a major revision, replacing and making obsolete GA26-3591-2. This revision covers additional features added to the 1800 system. This publication has been completely revised and should be reviewed for changes.

Significant changes or additions to the specifications contained in this publication are continually being made. When using this publication in connection with the operation of IBM equipment, check the latest SRL Newsletter for revisions or contact the local IBM branch office.

Manuals referred to in this publication that have an Order No. with a four character prefix are identical in content to the same manual without the initial prefix character. (e.g., GA26-xxxx-Y is the same in content as A26-xxxx-Y.)

The illustrations in this manual have a code number in the lower corner. This is a publishing control number and is not related to the subject matter.

Copies of this and other IBM publications can be obtained through IBM Branch Offices.

A form for reader's comments is provided at the back of this publication. If the form has been removed, send your comments to the address below.

This manual was prepared by the IBM Systems Development Division, Product Publications, Department G24, San Jose, California 95114. Send comments concerning the contents of this manual to this address.

© Copyright International Business Machines Corporation 1966

# Contents

| INTRODUCTION.                                              | 1        |

|------------------------------------------------------------|----------|

| IBM 1803 Core Storage Unit                                 | 1        |

| I/O Channel                                                | 1        |

| INTERRUPT                                                  | 1        |

| OPERATIONS MONITOR                                         | 1        |

| Process I/O                                                | 1        |

| ANALOG INPUT<br>DIGITAL INPUT                              | 1<br>3   |

| External Synchronization                                   | 3        |

| DIGITAL OUTPUT                                             | 4        |

| ANALOG OUTPUT                                              | 4        |

| External Synchronization                                   | 4        |

| Data Processing Input/Output                               | 4        |

| OPERATIONS                                                 | 5        |

| Machine Language                                           | 5        |

| DATA FORMAT.                                               | 5        |

| INSTRUCTION FORMAT                                         | 5        |

| INSTRUCTION SET                                            | 7<br>7   |

| Addressing                                                 | 7        |

| Indexing                                                   | 8        |

| Registers                                                  | 8        |

| INDEX REGISTERS                                            | 8        |

| MACHINE REGISTERS                                          | 8<br>9   |

| CONTROL REGISTERS                                          | 9        |

| Basic Processor-Controller Data Flow.                      | 9        |

| Machine Cycles                                             | 11       |

| CLOCK                                                      | 11       |

| CHANNEL TIMING PULSES                                      | 11       |

| I                                                          | 11       |

| II                                                         | 11<br>11 |

| IA                                                         | 14       |

| Ε                                                          | 14       |

| E1, E2, and E3                                             | 15       |

| XIO Control and XIO Data Cycles                            | 15       |

| Execute I/O I/O CONTROL COMMANDS                           | 16<br>16 |

| Address                                                    | 16       |

| Area                                                       | 16       |

| Function                                                   | 16       |

| Modifier                                                   | 17       |

| XIO INSTRUCTION EXECUTION                                  | 17       |

| DIRECT PROGRAM CONTROLLED OPERATION<br>Read/Write Function | 17<br>17 |

| Control Function                                           | 18       |

| Sense Interrupt                                            | 18       |

| Sense Device                                               | 18       |

| Interrupt                                                  | 18       |

| Interrupt Level Masking<br>External Interrupt Polling      | 19<br>20 |

| Programmed Interrupts                                      | 20       |

| Status Words                                               | 20       |

| Interrupt Level Status Word                                | 21       |

| Programmed Operations                                      | 21       |

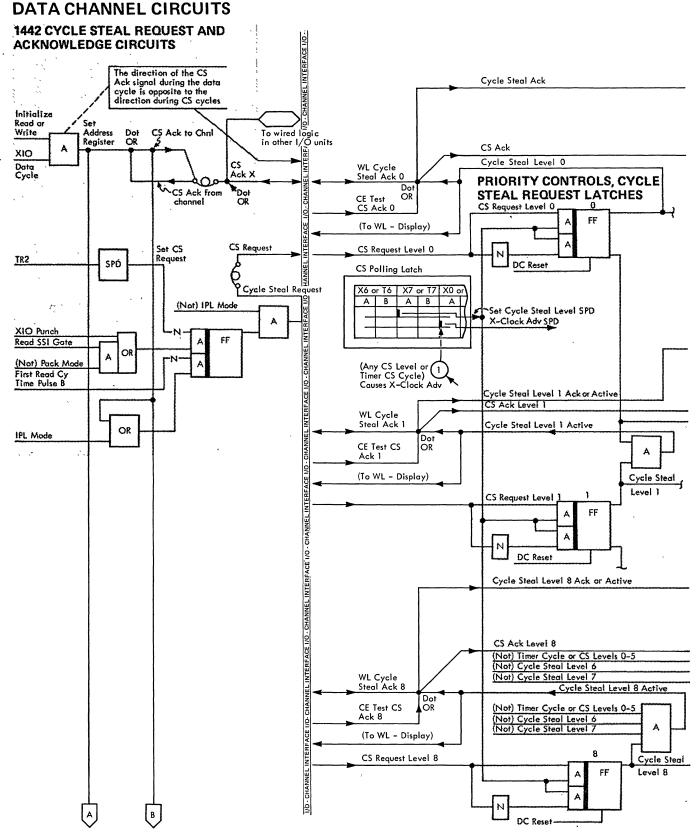

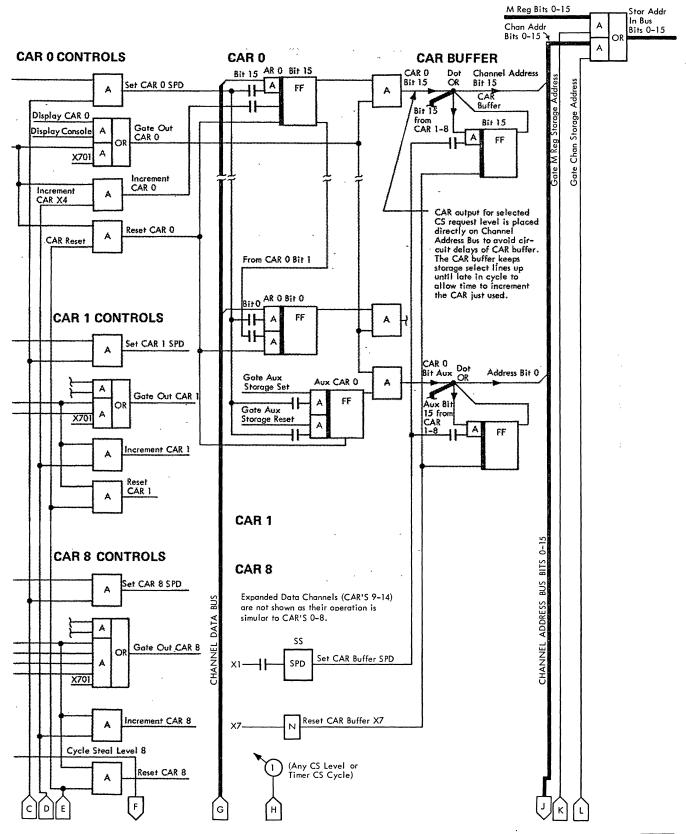

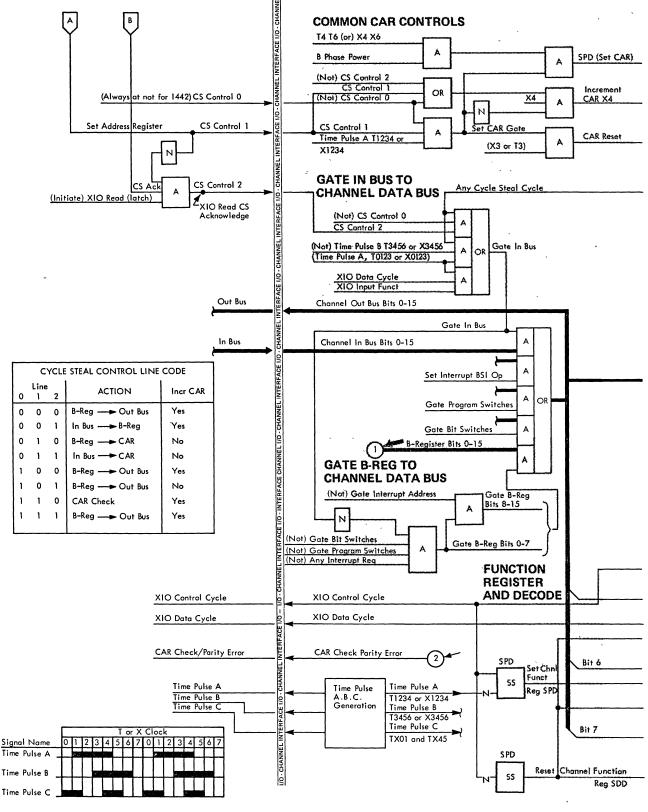

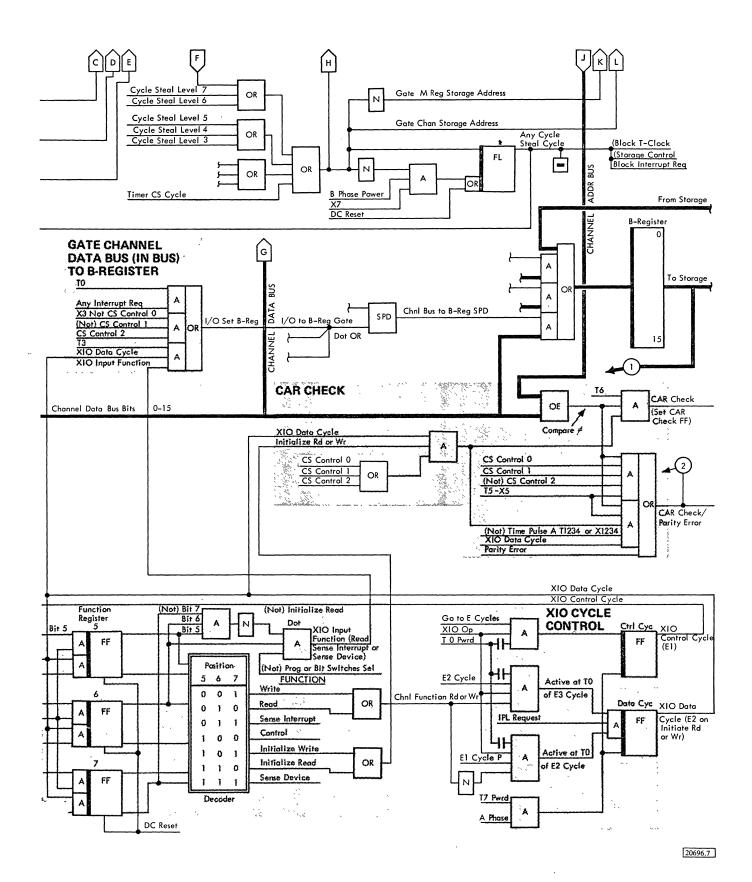

| DATA CHANNEL CONTROLLED OPERATION                          | 21<br>23 |

| Priority Controls                                          | 23       |

| Operational Sequence                                       | 25       |

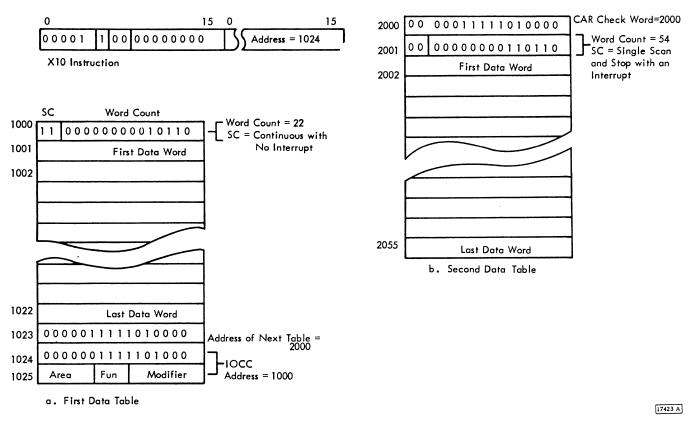

| Data Chaining                                              | 26       |

| Data Channel Operation                                     | 27       |

| Data Table                                                 | 27<br>27 |

| Cycle Steal Cycle                                          | 21       |

.

.

| ENVIRONMENTAL CONDITIONS                                                                                                                                                                                                                                                                                  | 29                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Temperature and Relative Humidity Limits                                                                                                                                                                                                                                                                  | 29                                                 |

| AIR CONDITIONING                                                                                                                                                                                                                                                                                          | 29                                                 |

| Room Pressurization                                                                                                                                                                                                                                                                                       | 29                                                 |

| Air Filtration                                                                                                                                                                                                                                                                                            | 29                                                 |

| Atmospheric Contaminants                                                                                                                                                                                                                                                                                  | 29                                                 |

| Recorders and Indicators                                                                                                                                                                                                                                                                                  | 30                                                 |

| LIGHTING                                                                                                                                                                                                                                                                                                  | 30                                                 |

| VIBRATION                                                                                                                                                                                                                                                                                                 | 30                                                 |

| HAZARDOUS LOCATIONS                                                                                                                                                                                                                                                                                       | 30                                                 |

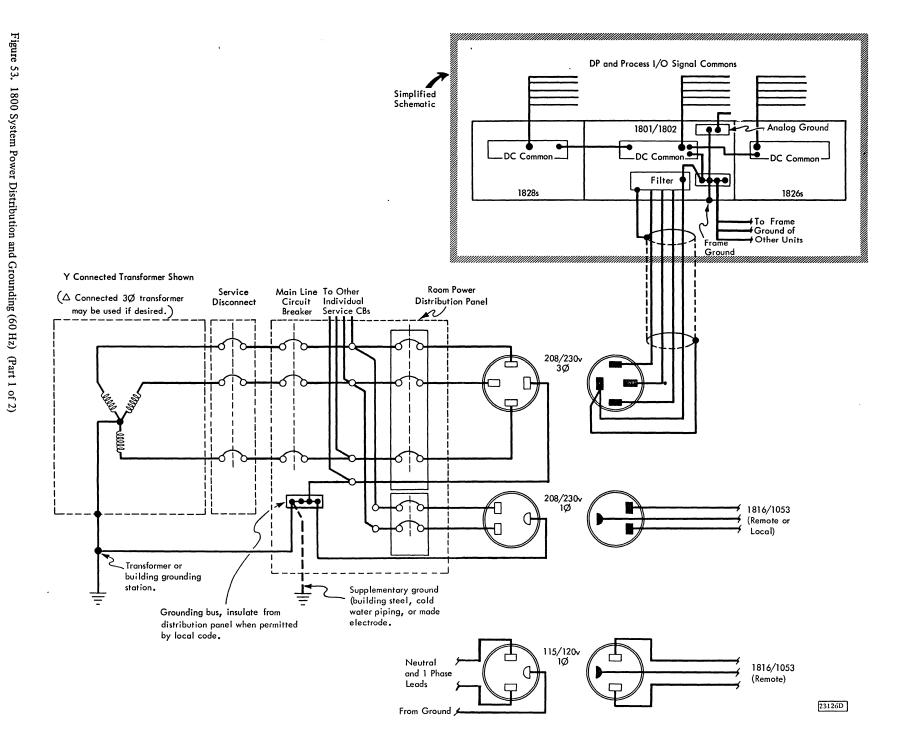

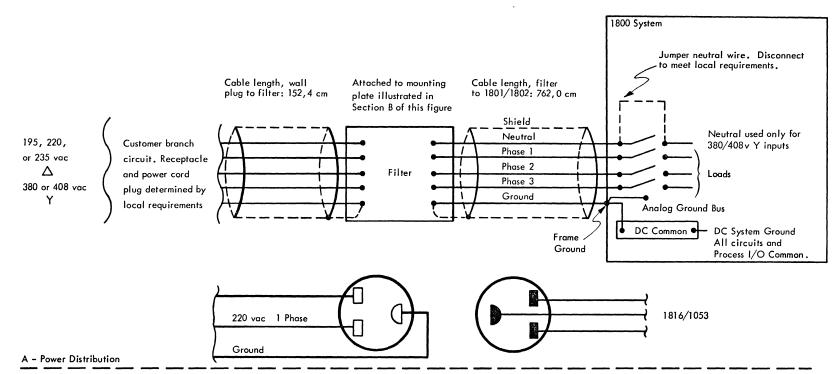

| Primary Electrical Power Requirements                                                                                                                                                                                                                                                                     | 30                                                 |

| SPECIFICATIONS                                                                                                                                                                                                                                                                                            | 30                                                 |

| POWER DISTRIBUTION                                                                                                                                                                                                                                                                                        | 30                                                 |

| GROUNDING.                                                                                                                                                                                                                                                                                                | 31                                                 |

| Grounding Electrode Types                                                                                                                                                                                                                                                                                 | 31                                                 |

| Internal System DC Grounding                                                                                                                                                                                                                                                                              | 31                                                 |

| PHASE ROTATION                                                                                                                                                                                                                                                                                            | 32                                                 |

| LIGHTNING PROTECTION                                                                                                                                                                                                                                                                                      | 32                                                 |

| CONVENIENCE OUTLETS                                                                                                                                                                                                                                                                                       | 32                                                 |

| Unit Specifications                                                                                                                                                                                                                                                                                       | 32                                                 |

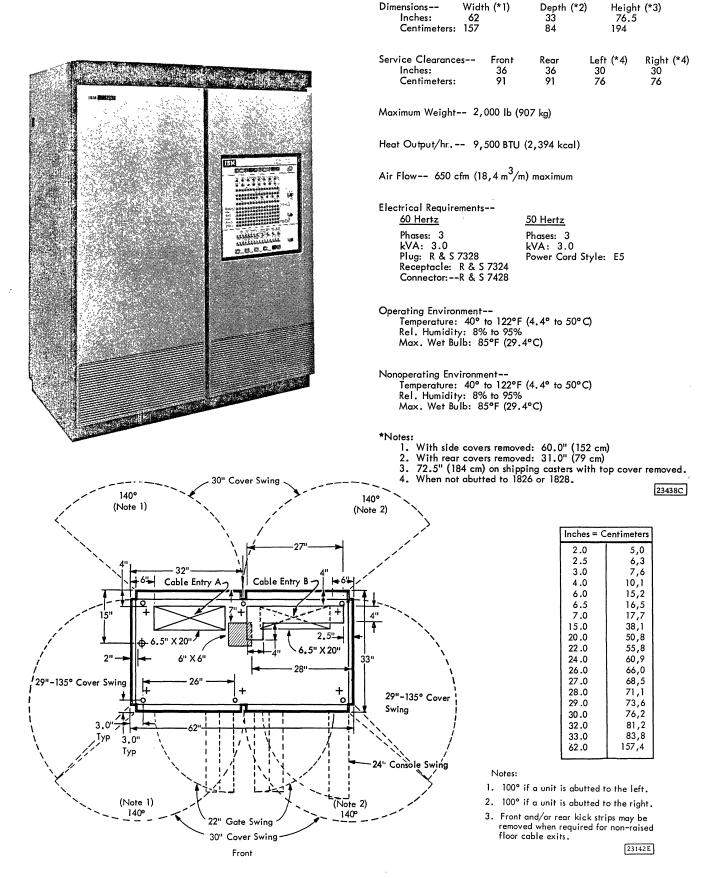

| IBM 1801 and 1802 Processor-Controller                                                                                                                                                                                                                                                                    | 33                                                 |

|                                                                                                                                                                                                                                                                                                           |                                                    |

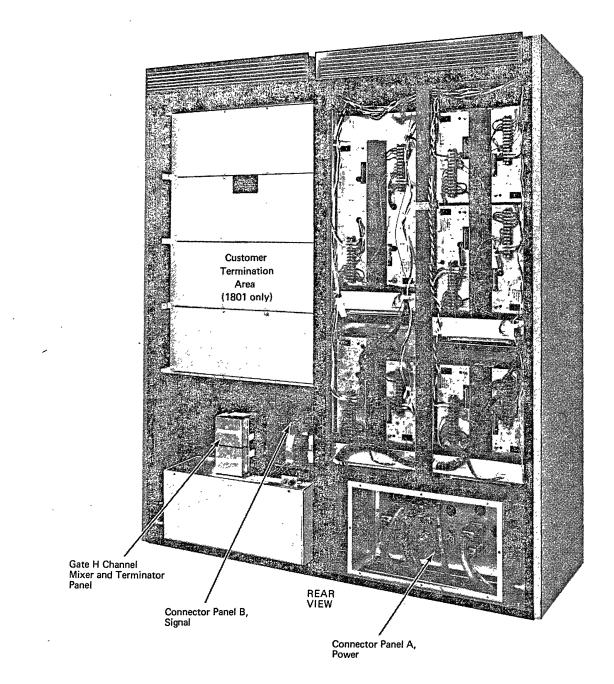

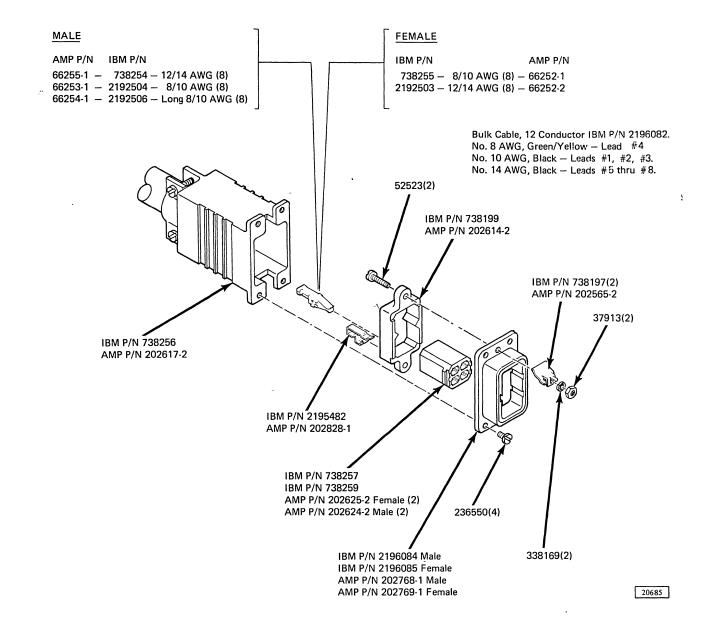

| POWER AND SIGNAL INTERFACES                                                                                                                                                                                                                                                                               | 36                                                 |

| Cables                                                                                                                                                                                                                                                                                                    | 36                                                 |

| Power Cabling                                                                                                                                                                                                                                                                                             | 36                                                 |

| 1801/1802 POWER                                                                                                                                                                                                                                                                                           | 36                                                 |

| 1803, 1810, 1826, AND 1828 POWER CONNECTORS                                                                                                                                                                                                                                                               | 36                                                 |

| 2401/2402 POWER CONNECTOR                                                                                                                                                                                                                                                                                 | 36                                                 |

| 1442 POWER CONNECTOR                                                                                                                                                                                                                                                                                      | 36                                                 |

| EMERGENCY POWER OFF AND POWER                                                                                                                                                                                                                                                                             |                                                    |

| CONNECTORS TO THE 1443<br>POWER CONNECTORS TO THE 1054, 1055, AND 1627                                                                                                                                                                                                                                    | 36                                                 |

|                                                                                                                                                                                                                                                                                                           | 36                                                 |

| 1053 CABLES                                                                                                                                                                                                                                                                                               | 36                                                 |

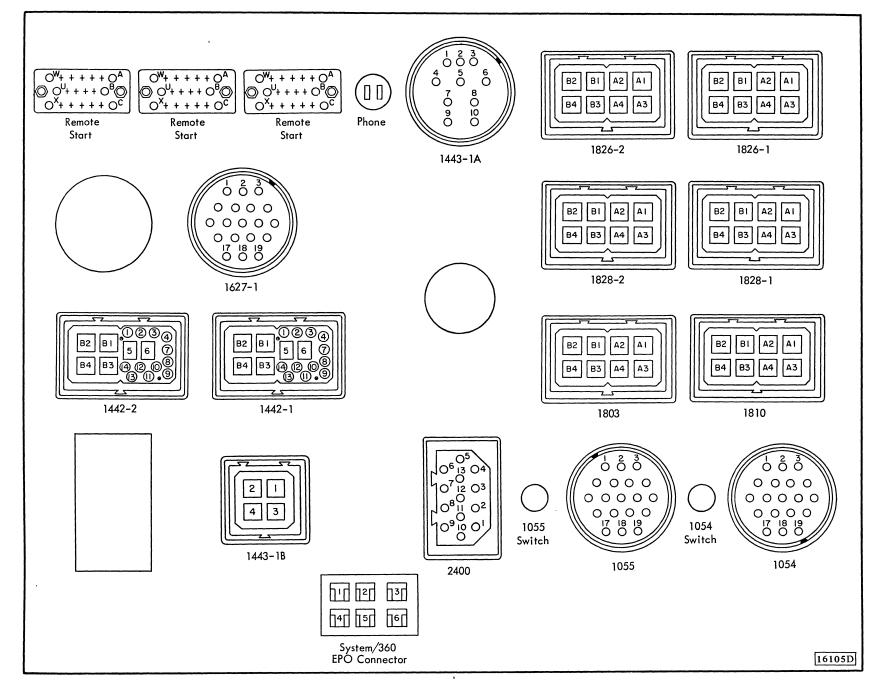

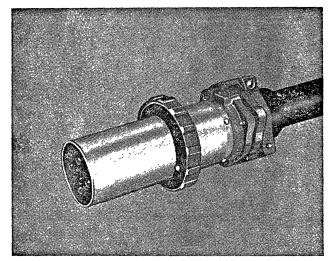

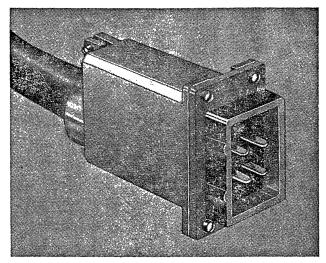

| CABLE CONNECTORS                                                                                                                                                                                                                                                                                          | 36                                                 |

| FLOOR TO FRAME CLEARANCE                                                                                                                                                                                                                                                                                  | 45                                                 |

| Signal Cabling                                                                                                                                                                                                                                                                                            | 45                                                 |

|                                                                                                                                                                                                                                                                                                           | <i>с 1</i>                                         |

| INPUT/OUTPUT CHANNEL INTERFACE                                                                                                                                                                                                                                                                            | 54                                                 |

| I/O CHANNEL INTERFACE LINES                                                                                                                                                                                                                                                                               | 54<br>54                                           |

| Out Bus                                                                                                                                                                                                                                                                                                   | 54                                                 |

| In Bus                                                                                                                                                                                                                                                                                                    | 54                                                 |

| Parity Bits.                                                                                                                                                                                                                                                                                              | 54                                                 |

| CPU Stop Clock                                                                                                                                                                                                                                                                                            | 54                                                 |

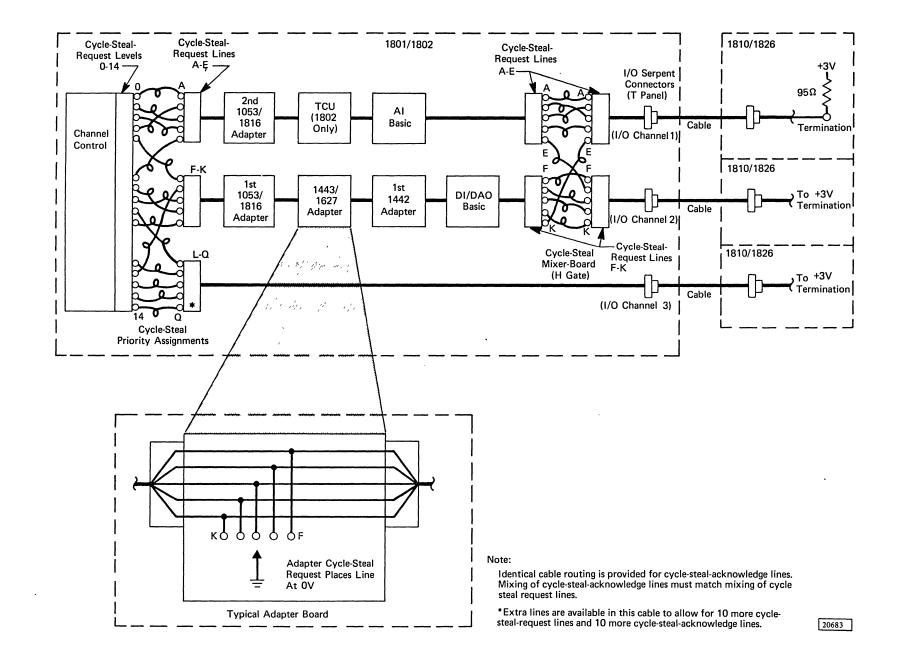

| Cycle-Steal Request                                                                                                                                                                                                                                                                                       | 54                                                 |

| Cycle-Steal Acknowledge                                                                                                                                                                                                                                                                                   | 54                                                 |

| Cycle-Steal Control                                                                                                                                                                                                                                                                                       | 58                                                 |

| Interrupt Poll A and B                                                                                                                                                                                                                                                                                    | 58                                                 |

| IPL Mode                                                                                                                                                                                                                                                                                                  | 58                                                 |

| Metering                                                                                                                                                                                                                                                                                                  | 58                                                 |

| Time Pulse A, B, and C                                                                                                                                                                                                                                                                                    | 58                                                 |

| Parity Error                                                                                                                                                                                                                                                                                              | 58                                                 |

| XIO Data Cycle                                                                                                                                                                                                                                                                                            | 20                                                 |

| XIO Control Cycle                                                                                                                                                                                                                                                                                         | 50                                                 |

|                                                                                                                                                                                                                                                                                                           | 59<br>50                                           |

| Storage Protect Violation                                                                                                                                                                                                                                                                                 | 59                                                 |

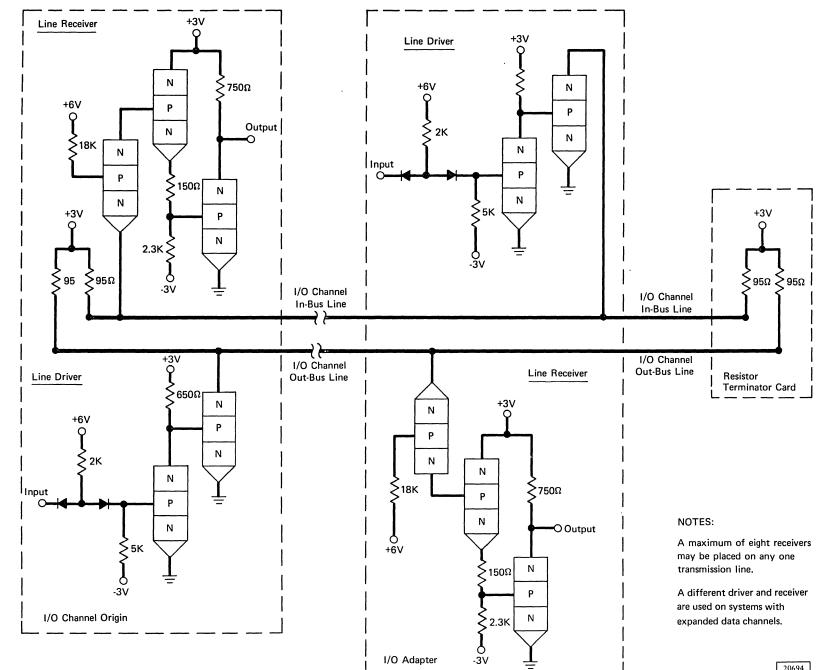

| SIGNAL CABLE TERMINATION                                                                                                                                                                                                                                                                                  | 59<br>60                                           |

| SIGNAL CABLE TERMINATION                                                                                                                                                                                                                                                                                  | 59<br>60<br>60                                     |

| SIGNAL CABLE TERMINATION<br>I/O CHANNEL TIMING<br>Electrical Specifications                                                                                                                                                                                                                               | 59<br>60<br>60<br>60                               |

| SIGNAL CABLE TERMINATION<br>I/O CHANNEL TIMING<br>Electrical Specifications<br>PHYSICAL CONSIDERATIONS                                                                                                                                                                                                    | 59<br>60<br>60<br>60<br>60                         |

| SIGNAL CABLE TERMINATION<br>I/O CHANNEL TIMING<br>Electrical Specifications<br>PHYSICAL CONSIDERATIONS<br>Single Driver and Receiver                                                                                                                                                                      | 59<br>60<br>60<br>60<br>60                         |

| SIGNAL CABLE TERMINATION.         I/O CHANNEL TIMING         Electrical Specifications         PHYSICAL CONSIDERATIONS         Single Driver and Receiver         Multiple Drivers and Receivers                                                                                                          | 59<br>60<br>60<br>60<br>60<br>60                   |

| SIGNAL CABLE TERMINATION.<br>I/O CHANNEL TIMING<br>Electrical Specifications<br>PHYSICAL CONSIDERATIONS<br>Single Driver and Receiver.<br>Multiple Drivers and Receivers.<br>GENERAL ELECTRICAL CONSIDERATIONS.                                                                                           | 59<br>60<br>60<br>60<br>60<br>60<br>60             |

| SIGNAL CABLE TERMINATION.<br>I/O CHANNEL TIMING<br>Electrical Specifications .<br>PHYSICAL CONSIDERATIONS<br>Single Driver and Receiver .<br>Multiple Drivers and Receivers.<br>GENERAL ELECTRICAL CONSIDERATIONS.<br>Current Flow                                                                        | 59<br>60<br>60<br>60<br>60<br>60<br>60<br>60       |

| SIGNAL CABLE TERMINATION.         I/O CHANNEL TIMING         Electrical Specifications         PHYSICAL CONSIDERATIONS         Single Driver and Receiver         Multiple Drivers and Receivers.         GENERAL ELECTRICAL CONSIDERATIONS         Current Flow         Voltage Levels                   | 59<br>60<br>60<br>60<br>60<br>60<br>60<br>60<br>60 |

| SIGNAL CABLE TERMINATION.         I/O CHANNEL TIMING         Electrical Specifications         PHYSICAL CONSIDERATIONS         Single Driver and Receiver         Multiple Drivers and Receivers.         GENERAL ELECTRICAL CONSIDERATIONS         Current Flow         Voltage Levels         Impedance | 59<br>60<br>60<br>60<br>60<br>60<br>60<br>60<br>60 |

| SIGNAL CABLE TERMINATION.         I/O CHANNEL TIMING         Electrical Specifications         PHYSICAL CONSIDERATIONS         Single Driver and Receiver         Multiple Drivers and Receivers.         GENERAL ELECTRICAL CONSIDERATIONS         Current Flow         Voltage Levels                   | 59<br>60<br>60<br>60<br>60<br>60<br>60<br>60<br>60 |

This Page Intentionally Left Blank.

11

.

| SPECIFIC ELECTRICAL REQUIREMENTS |    |

|----------------------------------|----|

| Receiver                         | 60 |

| Terminator                       | 65 |

| Driver                           | 65 |

| Cable                            | 65 |

| Connectors                       | 65 |

| ALTERATIONS AND ATTACHMENTS      | 66 |

| POWER SUPPLIES AND CONTROL       | 67 |

| POWER-ON SEQUENCE                |    |

| ×                                |    |

|                                  |    |

,

| s | 60 | POWER-OF   | F S  | SEQUENCE          |           |         | 67 |

|---|----|------------|------|-------------------|-----------|---------|----|

|   | 60 | POWER FA   | ILU  | JRE PROTECT CI    | RCUIT     |         | 67 |

|   | 65 | EMERGENO   | CY   | POWER OFF         |           |         | 70 |

|   | 65 |            |      |                   |           |         |    |

|   | 65 | APPENDIX A | . (  | GLOSSARY          |           |         | 73 |

|   | 65 | APPENDIX B | . I  | O CHANNEL, SI     | MPLIFIED  | DATA    |    |

|   |    |            |      | CHANNEL (CYC      |           |         |    |

|   | 66 |            |      | OPERATION         |           |         | 76 |

|   |    |            |      | DEVICE STATUS     |           |         |    |

|   | 67 | APPENDIX D | ). 1 | 1801/1802 I/O ADA | APTER INT | ERFACES | 85 |

|   | 67 | APPENDIX E | . I  | ANALOG INPUT I    | NTERFAC   | Е       | 98 |

|   |    |            |      |                   |           |         |    |

-

-

•

.

IBM 1801/1802 Processor-Controller

The 1801 and 1802 Processor-Controllers (P-C) are available in several models, depending upon the core storage capacity and cycle time desired. Five core storage sizes are available in the 1801 or 1802 — 4096; 8192; 16,384; 24,576; 32,768 words — with storage cycle times of 2 or 4 microseconds (2.25 microseconds with the additional storage feature).

Additional storage is available in the 1803 core storage unit in increments of 8192 words, with a combined system maximum of 65,536 words. With the additional storage feature, the 1801 or 1802 contains 24,576 words, and the additional 16,384 to 40,960 words are located in the 1803.

In addition to the many special features available, the standard features include: three data channels, three index registers, three interval timers, 12 levels of interrupt, operations monitor, storage protection, power failure protection, parity, double precision arithmetic, multiply-divide, and an operator's console. The IBM 1802 provides magnetic tape control in addition to the above mentioned features.

# **IBM 1803 CORE STORAGE UNIT**

The IBM 1803 Core Storage Unit is a free standing unit designed to allow for expansion of core storage size above the 32,768 words available in the 1801 or 1802 Processor-Controller. With the additional storage feature, 24,576 core storage words are contained in the 1801 or 1802 with the additional storage in the 1803. The 1803 is available with 16,384 to 40,960 core storage words, in increments of 8192 words, for a maximum system core storage capacity of 65,536 words.

# **I/O CHANNEL**

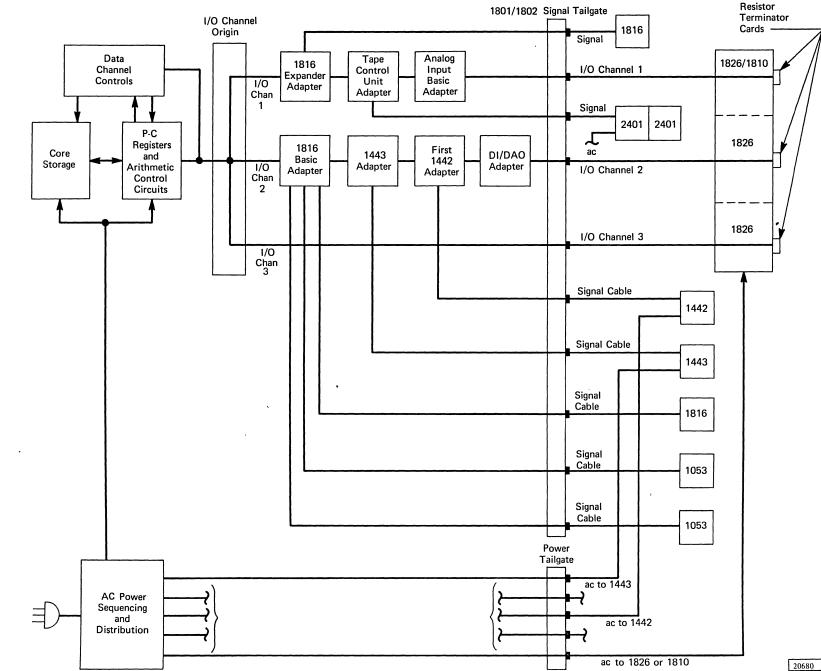

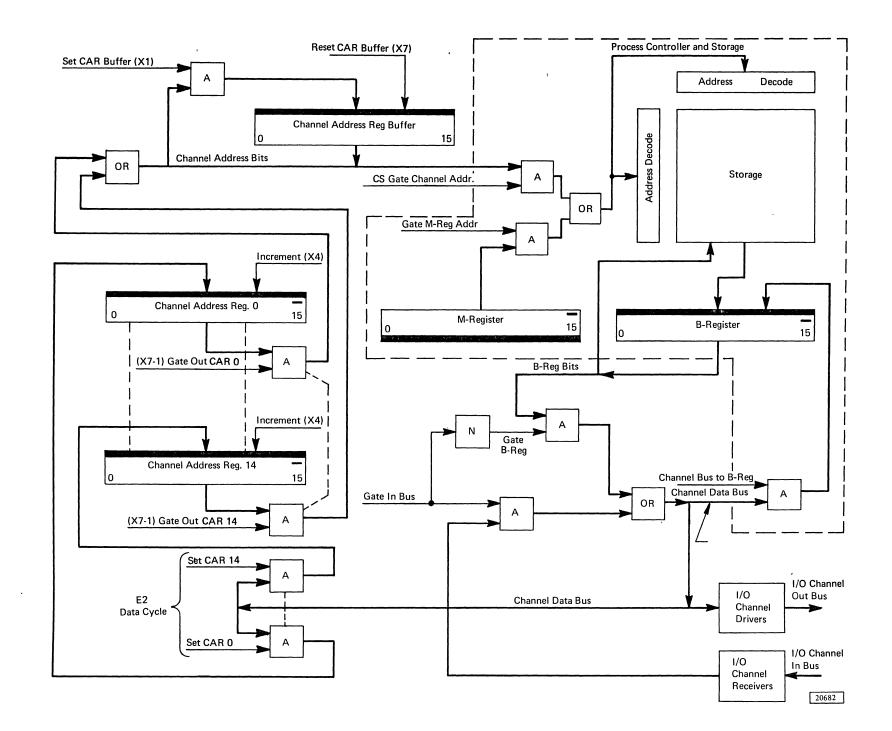

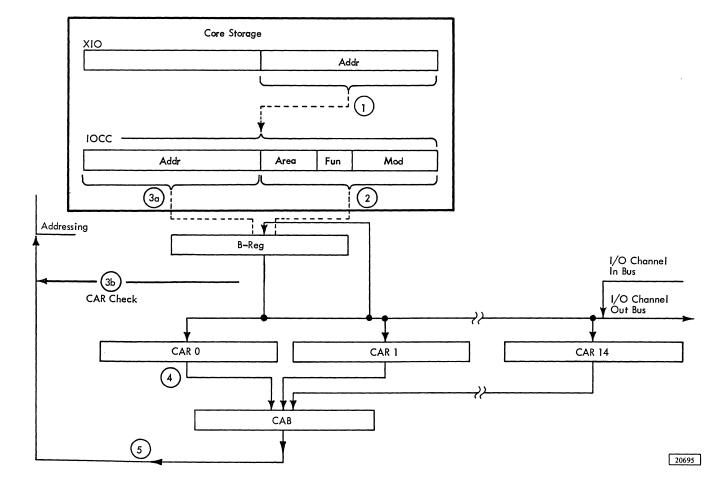

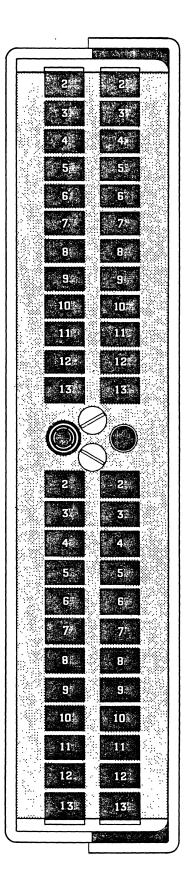

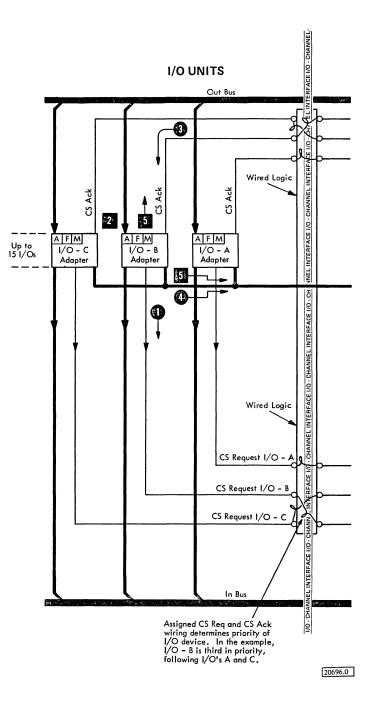

Input/output devices are attached to the I/O channel via I/O adapters which interface to the I/O channel (Figure 1). The adapters, which can be located physically within the I/O device or the P-C, provide the logical capability necessary to operate and control the devices, and adapt the characteristics of the device to the standard controls provided by the I/O channel. Usage of the I/O channel is on an assigned priority basis, with the P-C having the lowest priority.

The processor-controller I/O channel provides for communication between the P-C and the I/O adapters. All data transfers between the P-C core storage and the I/O devices require the use of the I/O channel.

# Data Channel

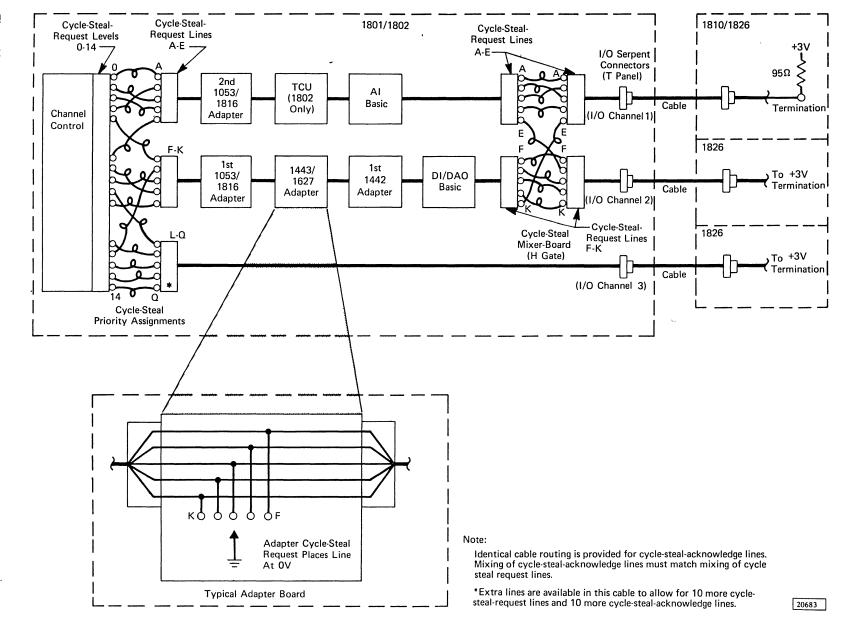

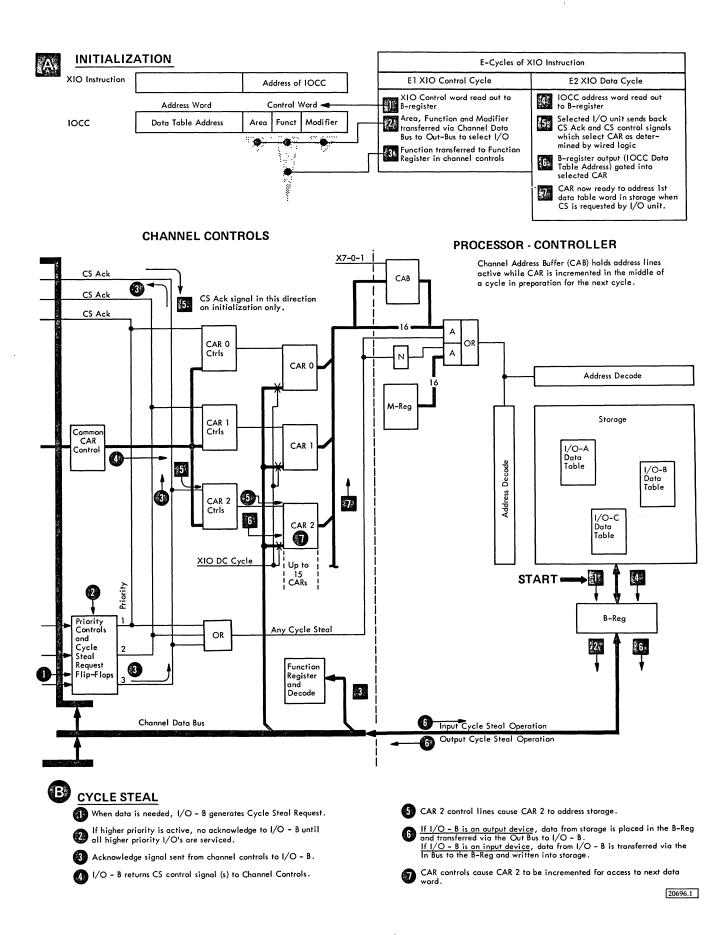

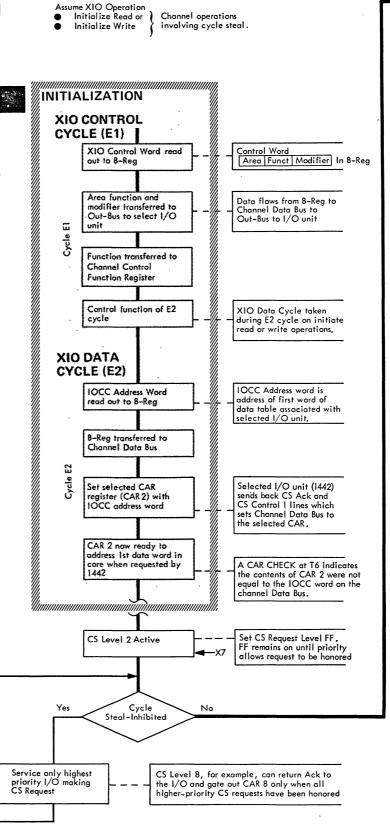

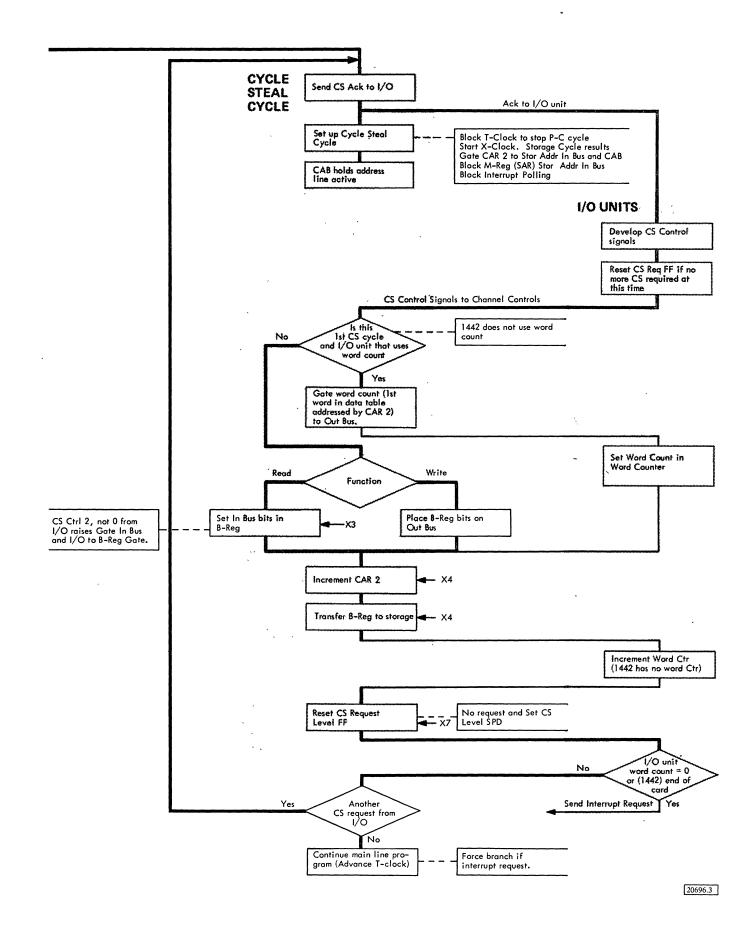

Data channels control high speed data transfer, via the I/O channel, between I/O devices and core storage by a method called cycle-stealing. Each data channel has a fixed priority for usage of the I/O channel.

Assignment of an I/O device to a data channel assigns the priority level (for usage of the I/O channel) of the I/O device. Three data channels are standard and 12 additional are optional.

# Interrupt

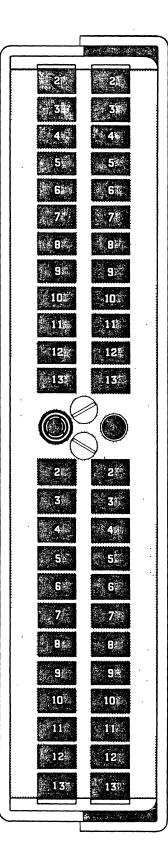

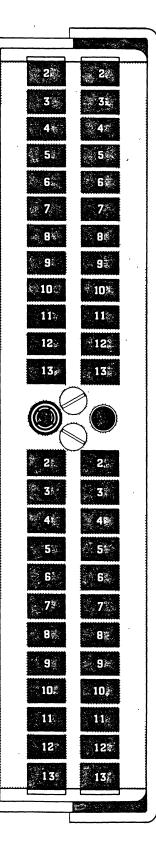

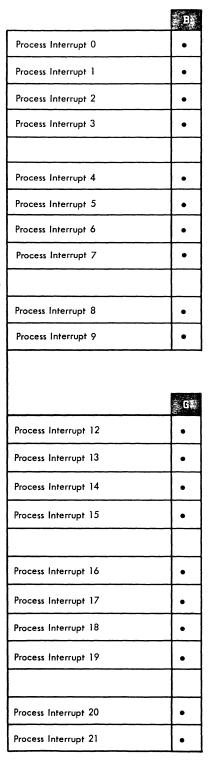

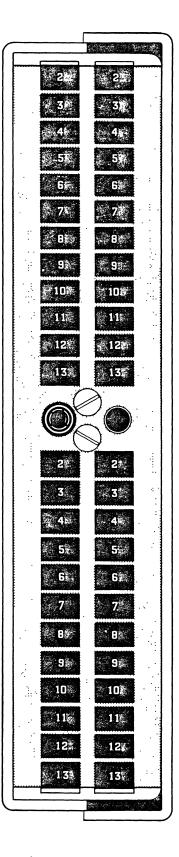

Twelve levels of interrupt are standard in the 1801 or 1802. Twelve additional levels are available in groups of six. Sixteen separate interrupts can be assigned to each level. These interrupts are generated by programmed instruction; the data processing I/O units, process I/O units and features, and the attachment circuitry. The customer can assign interrupts to any priority level, thus determining the priority of interrupts of the I/O device on the system. Interrupt levels are wired by IBM according to the information supplied on the Interrupt Level Assignment Form.

#### **Operations Monitor**

The operations monitor is a device which causes a contact to close upon completion of a preset timeout period (selectable between 5 and 30 seconds  $\pm 10\%$ ), or in event of an 1801/1802 power failure. It notifies the process operator when the processor-controller is not executing a predetermined sequence of instructions. The customer is to furnish the alarm device and its power. Power is limited to 30 volts (ac or dc) and 1 ampere maximum. Two wire terminations (external "sync" terminals 14 and 15), using number 8 barrier type terminals, are provided in a customer accessible location in the machine.

# **PROCESS I/O**

The process I/O is divided into four general categories: analog input, digital input, digital output, and analog output. (For additional process I/O information refer to *IBM 1800 Installation Manual-Physical Planning*, Order No. GA26-5922.)

#### Analog Input

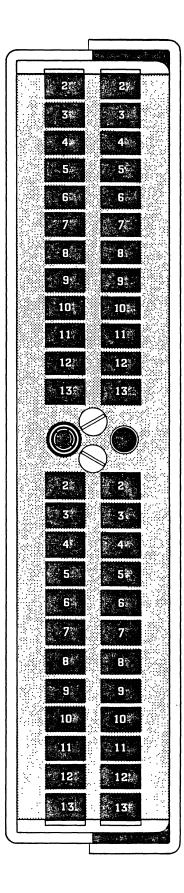

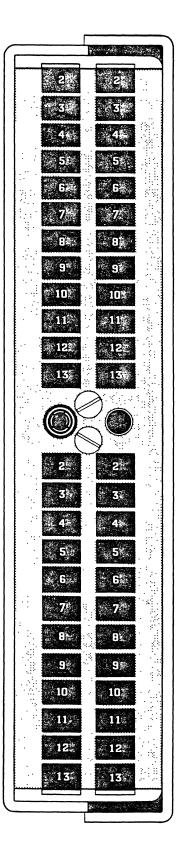

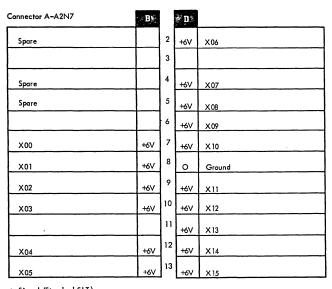

The following features associated with analog input are installed in the 1801 or 1802. Customer terminations for analog input are made to the 1851 terminals mounted in 1828 enclosures.

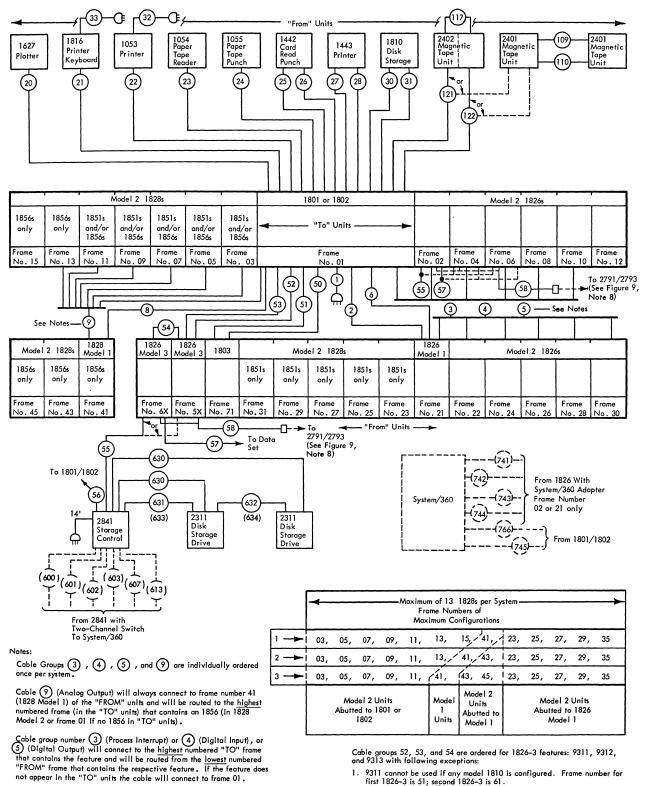

Figure 1. Input/Output Channel, Signal and Power Paths

Ν

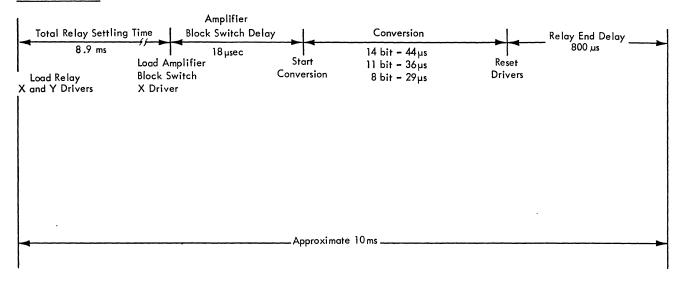

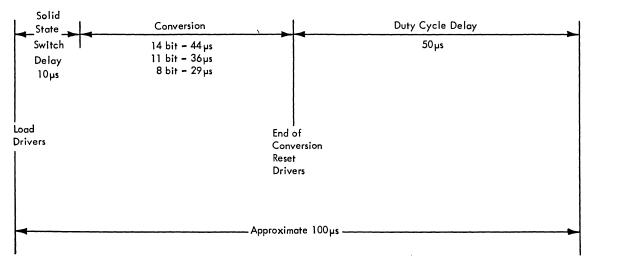

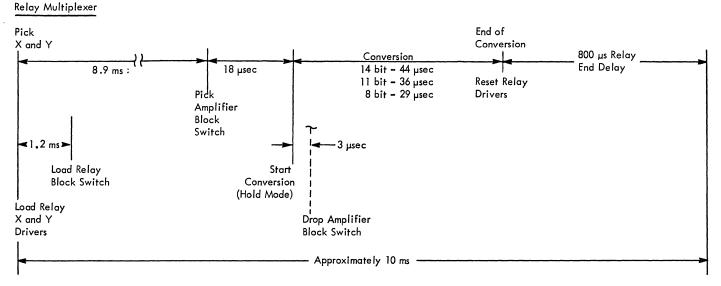

Analog-Digital Converter, Mod 1. This feature converts analog signals to digital values with the following characteristics:

| Input Type      | Voltage, bipolar           |

|-----------------|----------------------------|

| Input Level     | 0 to ±5 volts              |

| Input Impedance | 10 megohms or greater      |

| Output Value    | 8, 11 or 14 bits plus sign |

| ADC Conversion  | 29, 36 or 44 microseconds  |

| Time            |                            |

The number of output bits is program selected. The ADC includes a buffer amplifier.

Conversions can be synchronized from an external signal. After a point is addressed, a "ready" condition is transmitted to an external customer device; this device provides a "sync" pulse which either starts conversion for relay points or starts multiplexing for solid state points. Sync and ready signal termination are in the 1801, 1802, 1826 with AI Expander, or 1827.

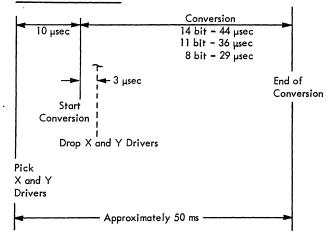

Analog-Digital Converter, Mod 2. This feature converts analog signals to digital values with the following characteristics:

| Input Type      | Voltage, bipolar            |

|-----------------|-----------------------------|

| Input Level     | 0 to $\pm 5$ volts          |

| Input Impedance | 100K ohms                   |

| Output Value    | 8, 11, or 14 bits plus sign |

| ADC Conversion  | 29, 36, or 44 microseconds  |

| Time            |                             |

The program selects the number of output bits. The ADC includes a sample and hold amplifier to allow higher conversion rates, and can be synchronized from an external signal.

After a point is addressed, a "ready" condition is transmitted to an external customer device. This device provides a "sync" pulse which starts conversion for relay points or starts multiplexing for solid state points.

*Comparator*: This feature performs automatic range checking on digital values developed by the Analog-Digital Converter Mod 1 or Mod 2. High and low limits are obtained from the processor-controller core storage via the data channel that transmits their addresses for the analog input operation (random mode only). An out-of-limits condition alerts the processor-controller with an interrupt that permits the address of that input signal to be obtained under direct program control. *Multiplexer Overlap*: Provides for overlap (simultaneous selection) of multiplexer/R (relay) and multiplexer/S (solid state) analog input multiplexer points. This allows high speed scanning and conversion of the multiplexer/S points to occur while the slower multiplexer/R points are being selected.

*Multiplexer/R Control*: This feature provides the necessary circuitry to operate up to 16 multiplexer/R groups.

*Multiplexer/S Control*: Multiplexer/S control provides circuitry to operate up to 16 multiplexer/S high-level singleended groups.

# **Digital Input**

The following digital input features may be installed in the 1801 or 1826. The number of each of the following available in an 1801 is dependent on the particular combination of features ordered and/or the termination capacity. When an 1802 is used on a system these features are located exclusively in the 1826.

Digital Input – Contact: Each group provides the status sensing circuitry and the terminals for up to 16 customer isolated, dry contacts.

Digital Input – Voltage: Each group provides the status sensing circuitry and the terminals for up to 16 customer voltage levels. A high speed option with unfiltered inputs allows switching rates up to 100 kc.

Pulse Counter (8-bit or 16-bit): Each pulse counter group provides two 8-bit or one 16-bit counter for counting pulse inputs.

#### External Synchronization

Digital input and pulse counter reading can be synchronized from an external signal. Digital input addressing can generate a "ready" signal which is transmitted to an external customer device. This device provides a "sync" pulse which initiates entry of digital input data into the processorcontroller. Synchronization terminals are located in the 1801, 1802, or 1827.

**Process Interrupt** – Contact: Each group provides terminals for the customer and the latching circuits for sensing and interrupting when a change occurs in the status of up to 16 customer isolated, dry contacts.

**Process Interrupt** – Voltage: Each group provides the customer with terminals and the latching circuits for sensing and interrupting when a change occurs in the status of up to 16 voltage level inputs.

# **Digital Output**

The following digital output features may be installed in either the 1801 or the 1826. The number of groups of each that are available for the 1801 is dependent on the particular combination of features ordered and/or the termination capacity. When an 1802 is used on a system these features are located exclusively in the 1826.

*Electronic "Contact" Operate*: Each group provides terminals for the customer and circuits for the electronic switching and latching of 16 customer lines carrying customer-supplied power up to 48 vdc at 0.45 amps.

**Pulse Output:** Each group provides terminals and circuits for momentary electronic switching of 16 customer lines, each carrying customer-supplied power up to 48 vdc at 0.45 amps with a duration of 3 milliseconds.

*Register Output*: Each register output group provides terminals and the circuitry for transmitting 16-bit words of binary data at repetitive speeds up to 500,000 words per second to customer registers. Voltage outputs are +3 volts for binary 1 and 0 volts for binary 0.

# Analog Output

The 1801 or 1802 can provide the adaptation circuitry and cabling attachment for analog output features which are housed in 1856 terminals mounted in 1828 enclosures.

# External Synchronization

A digital or analog output function can be synchronized from an external signal. Addressing of DAO can generate a "ready" signal which is transmitted to an external customer device. This device generates a "sync" pulse which initiates the output function. Termination is in the 1801, 1802, or 1827.

# DATA PROCESSING INPUT/OUTPUT

The following DP I/O units can be attached to the 1801 or 1802:

- 2 1816 Printer-Keyboard

- 8 1053 Output Printer (6 with 2 1816s installed)

- 1 1054 Paper Tape Reader

- 1 1055 Paper Tape Punch

- 2 1442 Card Read-Punch, Model 6 or 7 (1 1442 if 1054 or 1055 or Data Channel Expander in system)

- 1 1627 Plotter, Model 1 or 2

- 1 1443 Printer, Model 1 or 2

- 1 1810 Disk Storage, Model A1, A2, A3, B1, B2, or B3

- 8 2311 Disk Storage Drives with one 2841 Storage Control

- 4 Communication Adapters (2 Line Adapters per CA)

- 2-2790 Adapters

In addition, the 1802 will accommodate either:

1 or 2 - 2401 Magnetic Tape Units, Model 1, 2, or 3 or 1 - 2402 Magnetic Tape Unit, Model 1, 2 or 3

# Operations

# MACHINE LANGUAGE

The binary system enables the representation of numbers by any bi-stable means such as the on or off state of a flipflop, the up or down level of a signal line, or the direction of the field about a magnetic device. In core storage, each bit value is stored in a magnetic core; in data registers each bit value is stored as the on/off condition of a flip-flop or flip-latch.

The binary representation of data best facilitates the parallel manipulation of fixed-length words and is the most efficient method of processing scientific data.

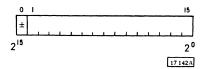

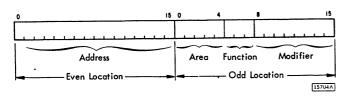

#### Data Format

In the 1800 system, the standard, or single-precision data word (Figure 2) is 16 bits in length. Bit positions 0 through 15 represent decimal values of  $2^{15}$  through  $2^{0}$  respectively.

Figure 2. Single Precision Data Word

Positive numbers are represented in true binary form, whereas negative numbers are in two's complement form. The sign bit (position 0) is always 0 for positive numbers and 1 for negative numbers. The two's complement of a binary number is defined as its one's complement increased by one. The one's complement of a binary number is that number that results by replacing each 1 in the number with a 0, and each 0 with a 1.

The largest single-precision positive number that can be represented is  $2^{15}-1$ , or 32,767 (a sign bit of 0, and 1's in all other bit positions). The largest negative number is  $-2^{15}$  or -32,768 (a sign bit of 1, and 0's in all bit positions). The number 0 is represented by all bits being 0; there is no negative 0.

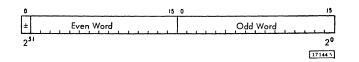

A double-precision number of 32 bits can be used to give a number range from +2,147,483,647 to -2,147,483,648 $(2^{31}-1 \text{ to } -2^{31})$ . Two adjacent words must be used in storage with the high-order word at an even address, and the low-order word at the next higher odd address (Figure 3).

Figure 3. Double Precision Data Word

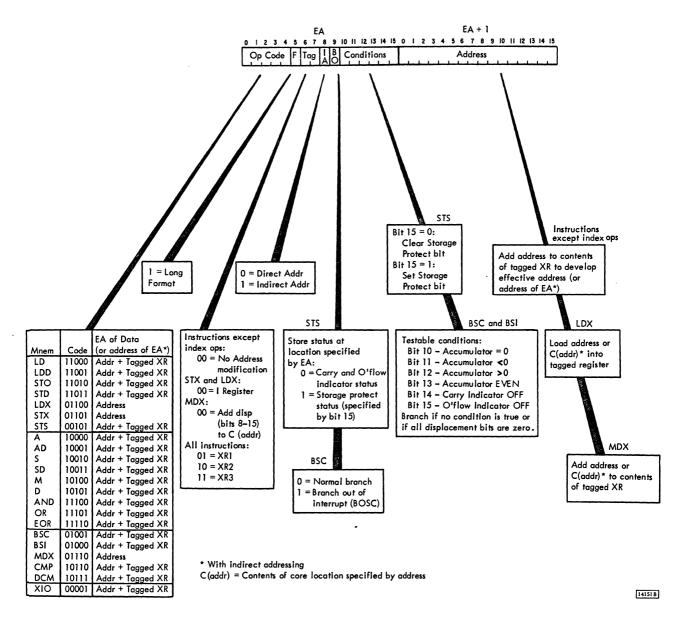

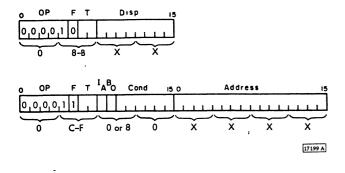

#### Instruction Format

The instruction defines the basic operation to be performed and contains the factors necessary for developing a core storage address. This core storage address is called the effective address (EA).

Two basic instruction formats are used: a single-word instruction (Figure 4) and a two-word instruction (Figure 5). The two-word instruction contains the full core storage address in the 16 bits of the low order word. The single-word instruction is used when it is not necessary to furnish the full core storage address, but only to modify (displace) a base address already existing in a designated 16-bit register. The displacement bits, 8 through 15, can be used to address a range of core storage locations from 127 addresses above the base address to 128 addresses below the base address.

The address portion of a two-word instruction can also be modified by adding to the contents of a designated 16-bit index register.

The bits within the instruction are used in the following manner:

*Op Code*: The operation to be performed by the instruction is defined by these five bits. There are 26 valid op codes.

Format (F): This bit selects the instruction format. A "0" indicates a single-word instruction and a "1" indicates a two-word instruction.

Tag (T): These are the index tag bits used to select a register for address modification.

Displacement: These eight bits define the displacement value and are added to the register specified by the tag bits to develop the effective address (EA).

Displacement may be in either a positive or negative direction as determined by the sign of the displacement value. A negative displacement value will be in two's complement form with a bit in position 8.

Indirect Address (IA): This is the indirect address bit in the two-word instruction format except in the modify-indexand-skip instruction with a tag 00 specified. If "0", addressing is direct. If "1", addressing is indirect.

Figure 4. Single-Word Instruction Format

Figure 5. Double-Word Instruction Format

*Branch Out (BO)*: This bit is used to specify that the branch-or-skip-on-condition instruction is to be interpreted as "branch-out-of-interrupt routine."

*Conditions*: These six bits specify the indicators to be tested on a branch-or-skip-on-condition instruction.

Address: These 16 bits usually specify a core storage address in a two-word instruction. The address can be modified by the contents of an index register or used as an indirect address if the IA bit is on.

# Instruction Set

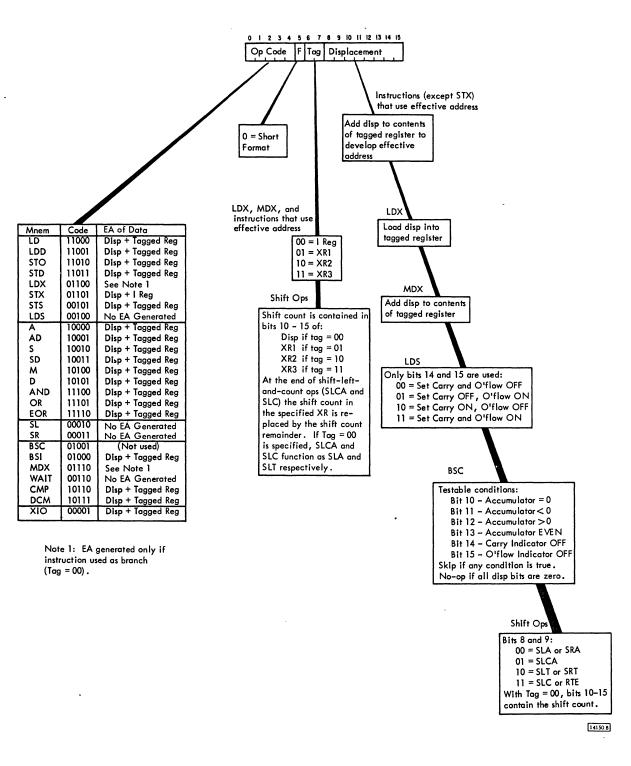

The 1800 instruction set is shown in Figure 6. Each instruction falls into one of five classes. Note that the instructions which may be modified with indirect addressing are indicated in the indirect addressing column. Some instructions perform multiple uses as specified by their control bits.

# ADDRESSING

# Indirect Addressing

Indirect addressing is used only in double-word instructions (F=1). The direct address can be generally defined as the

| Class      | Instruction                      | Indirect<br>Addressing | Mnemonic  |

|------------|----------------------------------|------------------------|-----------|

| Load and   | Load Accumulator                 | Yes                    | LD        |

| Store      | Double Load                      | Yes                    | LDD       |

|            | Store Accumulator                | Yes                    | STO       |

|            | Double Store                     | Yes                    | STD       |

|            | Load Index                       | **                     | LDX       |

|            | Store Index                      | Yes                    | STX       |

|            | Load Status                      | No                     | LDS       |

|            | Store Status                     | Yes                    | STS       |

| Arithmetic | Add                              | Yes                    | A         |

|            | Double Add                       | Yes                    | AD        |

|            | Subtract                         | Yes                    | S         |

|            | Double Subtract                  | Yes                    | SD        |

|            | Multiply                         | Yes                    | м         |

| 1          | Divide                           | Yes                    | D         |

|            | And                              | Yes                    | AND       |

|            | Or                               | Yes                    | OR        |

|            | Exclusive Or                     | Yes                    | EOR       |

| Shift      | Shift Left Instructions          |                        |           |

|            | Shift Left Logical (A) *         | No                     | S LA      |

|            | Shift Left Logical (AQ)*         | No                     | SLT       |

|            | Shift Left and Count (AQ)*       | No                     | SLC       |

|            | Shift Left and Count (A) *       | No                     | SLCA      |

|            | Shift Right Instructions         |                        |           |

|            | Shift Right Logical (A)*         | No                     | SRA       |

|            | Shift Right Arithmetically (AQ)* | No                     | SRT       |

|            | Rotate Right (AQ)*               | No                     | RTE       |

| Branch     | Branch and Store I               | Yes                    | BSI       |

|            | Branch or Skip on Condition      | Yes                    | BSC(BOSC) |

|            | Modify Index and Skip            | **                     | MDX       |

|            | Wait                             | No                     | WAIT      |

| <b>I</b>   | Compare                          | Yes                    | СМР       |

|            | Double Compare                   | Yes                    | DCM       |

| 1/0        | Execute I/O                      | Yes                    | XIO       |

\* Letters in parentheses indicate registers involved in shift operations.

\*\* See the section for the individual instruction (MDX and LDX)

17151 D

Figure 6. Instruction Set

location of data in core storage. An indirect address can then be defined as the address of a direct address. For most instructions, the effective address that is generated during I1 and I2 cycles is a direct address.

However, the presence of a "1" in the bit-8 position of a long format instruction indicates that the effective address is really an indirect address. This indirect address is the core storage location of a direct address.

Only one level of indirect addressing is available in the 1800 system. This means that the indirect address of an instruction always selects a direct address, never another indirect address.

Indirect addressing requires an additional I cycle, called the IA cycle. The IA cycle reads the direct address from the core storage location specified by the indirect address and places the direct address in the accumulator.

# Indexing

Indexing enables the use of one instruction to operate on data stored in various core storage locations without altering the instruction word itself. When specified by the instruction word tag bits, the contents of the specified index register are added to the instruction address during the instruction cycle. Therefore, at the beginning of the execute cycle, the effective address that is in the accumulator has been modified by the index register.

There are instructions that load, store, and modify any of the three index registers.

# REGISTERS

## Index Registers (XR)

There are three 16-position index registers. They are used to index an instruction causing the contents of the specified index register to be added to the instruction address to form the desired effective address for that instruction.

### **Machine Registers**

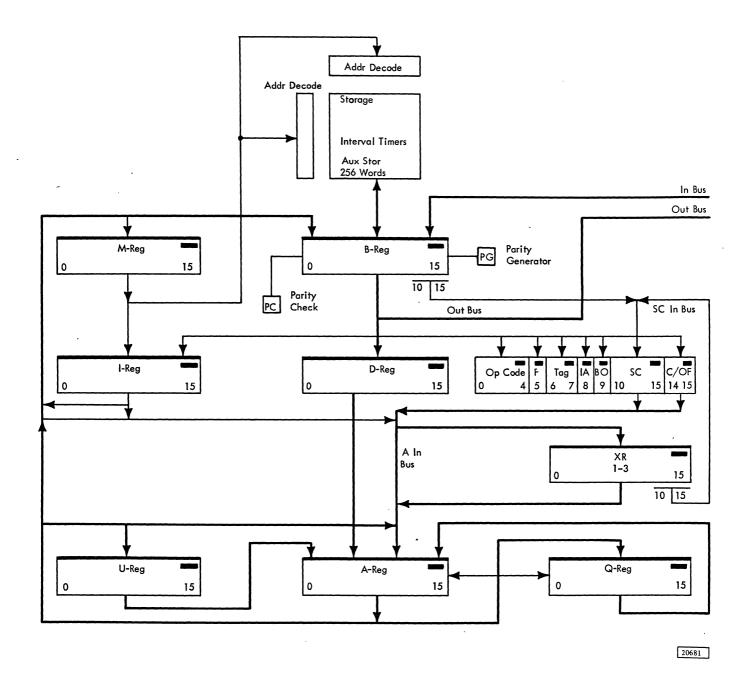

There are seven basic machine registers which are used by the CPU to provide the results specified by the program.

A (Accumulator Register): The accumulator is a 16-position register with unique connections that enable arithmetic and shift operations. It is used to store one factor of an arithmetic or logical operation; the D register contains the other factor. The result of any arithmetic operation is contained in the accumulator. The contents can be shifted to the right or left.

The accumulator can be loaded from core storage by a load accumulator instruction. This operation is executed to set up a data word to be shifted.

An XIO instruction with a sense command can load the accumulator with a sense word from an I/O adapter. The program can then analyze the sense word by a shift operation.

The accumulator contents can be stored into core storage by a store accumulator instruction.

*B* (Storage Buffer Register): The B register is a 16-position register. It is used to buffer all instruction and data words read from or written into core storage.

D (Arithmetic Factor Register): The D register is a 16position register. It is used to store one factor for arithmetic and logical operations; the other factor is in the accumulator (A register). The D register and the accumulator have unique interconnections that implement arithmetic and logical operations. I (Instruction Address Register): This 16-position register is a counter to maintain the address of the next instruction. The contents are transferred to the M register to address core storage. The contents of the I register are then increased by one for the next sequential address. The contents are transferred to the accumulator for effective address generation during each one-word instruction cycle.

M (Storage Address Register): This 16-position register is used to address core storage. It is loaded from the I register or the accumulator. The output of position 15 is forced on during double precision instructions or for fetching an Input Output Control Command (IOCC).

Q (Accumulator Extension Register): This 16-position register is used as an extension of the accumulator for arithmetic operations.

U (Temporary Accumulator Register): This 16-position register is used for temporary storage of the contents of the accumulator. It does not contain the ability to perform arithmetic operations. It is used to store the contents of the accumulator while the accumulator is being used by another operation such as generating an effective address.

#### **Control Registers**

*Op Code (Operation Code Register)*: This five-position register decodes the operation code and controls the gating of information from the B register to other registers.

F (Format Register): This one-position register defines the operation as a one or two word instruction.

Tag Register: This two-position register specifies if one of the three index registers is to be used during this instruction.

SC (Shift Counting): This six-position counter is loaded at the beginning of every cycle to control the number of cycles to be taken. It is loaded at the beginning of a shift instruction to control the number of positions to be shifted. It is decremented each execute cycle and when the shift count = 0 the operation is ended.

C/OF (Carry and Overflow Registers): This two-bit register is set to indicate either a carry or overflow condition of the accumulator.

# Modifier Registers

IA (Indirect Addressing Register): This one-position register specifies (if a "1") and controls indirect addressing for this instruction.

BO (Branch Out Register): This one-position register controls the branch-or-skip-on-condition instruction to cause it to be interpreted as a "branch-out-of-interrupt routine".

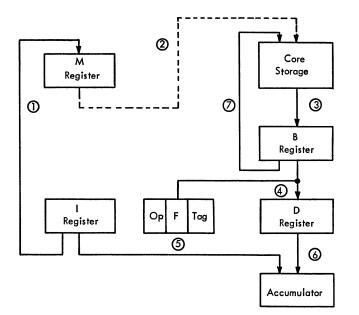

# BASIC PROCESSOR-CONTROLLER DATA FLOW

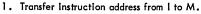

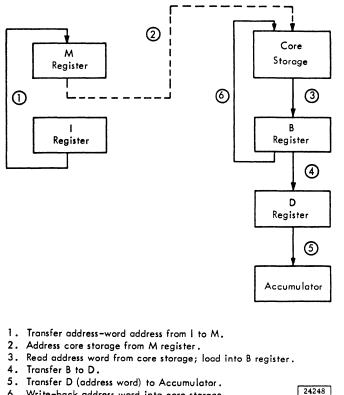

The first machine cycle of an operation or after a reset is an instruction cycle. The purpose of the first instruction cycle of any operation is to analyze the instruction word to determine the operation to be performed and to set up the registers that control the operation. These control registers are loaded with the contents of the B register during the first half of the cycle (Figure 7).

The control registers include the operation register, the format and tag registers, the shift counter, and the modifier register. A decode of the operation code activates the lines that gate information from the B register to other registers. The format register defines the operation as a one word or two word instruction. The tag register specifies one of the three index registers or the I register to be used during this instruction.

The shift counter is a dual-purpose register. For most instructions, it is loaded by hardware means, rather than from the B register, to indicate the number of cycles necessary for the specified operation. For shift operations, it is loaded from the B register or from an index register to control the number of shifts to be performed. It is decremented with each cycle or with each shift to accomplish its function.

The modifier register (bit 8-IA and bit 9-BO) is used by some operations to specify various functions to be performed by one op code.

Being a stored-program system, the 1800 system must execute instructions, stored in core storage, in a prescribed sequence. A register must be provided to keep track of the address of the next instruction to be performed. This register is the instruction register (I register). At the beginning of each instruction cycle, when an instruction word must be read from core storage, the contents of the I register are transferred to the M register. Immediately after I is transferred to M, the I register is incremented one address, so that it always contains the address of the next instruction to be performed.

If the address that is to be used to address core storage, the effective address, is to be generated during one I cycle, it is generated by adding part of the instruction word contained in the B register to the contents of the I register, or to the contents of one of the three index registers. An adder of some sort is therefore required. All additions are made to the accumulator. An additional register is required to contain the other factor of an add operation. This arithmetic factor register is called the D register.

Unique circuit connections and controls between the D register and the accumulator enable add and subtract operations.

To generate an effective address in one I cycle for a short format instruction, the CPU must be able to transfer the contents of the I register or one of the index registers to the accumulator. The other factor of the addition is a part of the instruction word contained in the B register, therefore,

Figure 7. Processor-Controller Data Flow

the D register is located between the B register and the accumulator. The contents of the D register are then added to the contents of the accumulator and the result (effective address) remains in the accumulator at the end of the I cycle.

At the beginning of the cycle which uses this effective address, the contents of the accumulator are transferred to the M register to address core storage.

Some instructions require that more than 16 bits be operated upon during the E cycles of one instruction. Therefore, another 16-bit register is connected to the accumulator. This register is called the accumulator extension register or Q register. Binary bits in the accumulator can be shifted from the low order position of the accumulator into the Q register, or the entire 16-bit word can be transferred from the accumulator to the Q register, or from the Q register to the accumulator.

The objectives of some operations are to modify a data word that has been previously loaded into the accumulator. Because the accumulator is used to generate an effective address during the I cycle, a temporary storage is needed for the accumulator word. This temporary storage register is called the U register. Sixteen-bit words can be transferred from the accumulator to the U register, and from the U register to the accumulator.

The basic data flow for internal CPU operations consists of the 16 data bits that are sensed in core storage and set into the B register and into the Op, format, tag, and modifier registers during the instruction cycle. The contents of these registers determine what will happen during succeeding cycles.

During execution cycles, data is manipulated between the B, D, A, Q, and U registers and then written into a predetermined core storage location, or left in the accumulator.

The next instruction, specified by the I register, is addressed by the M register and read from core storage and the program continues.

Some instructions require only one I cycle to perform the complete operation. For example, the load status instruction sets the condition of the carry and overflow indicators according to the information contained in two positions of the B register. The second half of the I cycle merely gates positions 14 and 15 of the B register into the carry and overflow indicators and the operation is complete.

Other instructions require an instruction cycle followed by an execution cycle. For example, the load accumulator instruction generates an effective address during the I cycle and reads a data word from core storage and places that word in the 16-bit accumulator during the E cycle.

#### MACHINE CYCLES

#### Clock

There are two clocks furnishing all timings in the 1800 system. Only one clock is running at any time. The two clocks are; the T clock which furnishes all timings to control CPU operations and direct program controlled I/O operations, and the X clock which controls the data channel operations.

The clocks generate timing pulses T0, T1, T2, through T7 or X0, X1, X2, etc., depending on which clock is running. The timing pulses are grouped into machine cycles. One machine cycle is from T0 through T7 or X0 through X7. The time for one machine cycle is 2, 2.25, or 4  $\mu$ sec depending on the 1800 configuration.

When certain arithmetic and shift operations require more steps than one cycle provides, the clock is stepped to T7 and then clock advances are prevented, extending T7 while the phase flip-flop output provides timing pulses for the operation. Advancement from T7 requires the absence of any of the clock extending conditions.

# **Channel Timing Pulses**

The clock timing pulses T0 through T7 or X0 through X7 are ANDed together to generate three basic timing pulses which are sent to the I/O adapters via the I/O channel

interface. The three timing pulses are; timing pulse A, timing pulse B, and timing pulse C. The three timing pulses, A, B, and C can be combined in the I/O adapter to generate all eight timing pulses.

#### I (Instruction Cycles)

In the performance of stored program instruction operations, the computer proceeds through instruction time (I-cycles), and generally through execution time (E cycles) for each operation. The functions of instruction time are to read the instruction from core storage, store the instruction in the control registers, decode the registers to set up the necessary controls for the operation, and to develop an effective address.

Six types of instructions and the machine cycles required for each type are:

|                                                                                                                                                                                   | Cycl            | es Req      | uired |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------|-------|

| Type of Instruction                                                                                                                                                               | 11              | 12          | IA    |

| Single–Word<br>Single–Word with Indexing<br>Double–Word<br>Double–Word with Indexing<br>Double–Word with Indirect Addressing<br>Double–Word with Indexing and Indirect Addressing | × × × × × × × × | ×<br>×<br>× | ×××   |

24035A

#### 11 (Instruction Cycle)

This cycle is used by all instructions. It reads the instruction data from core storage at the address specified by the instruction (I) address register. The core storage word is read into the B register, distributed to the various control registers, and decoded to indicate the operation to be performed.

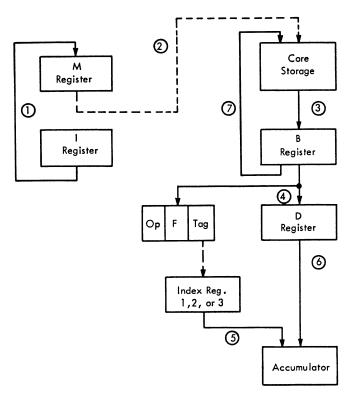

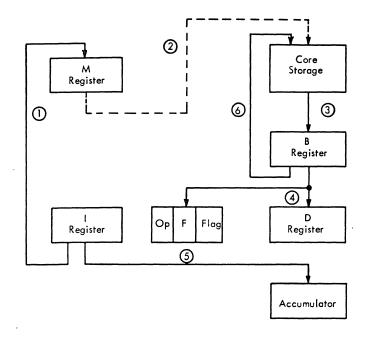

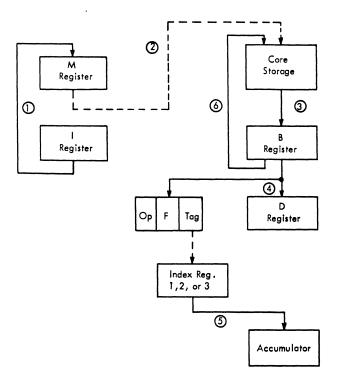

There are four types of I1 cycles. Each type performs specific functions to generate or help generate the effective address. The four types of I1 cycles and their functions are shown in Figures 8, 9, 10, and 11.

## 12 (Instruction Cycle)

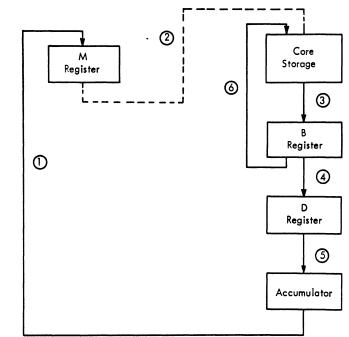

This cycle is used by all long format instructions. It is used to read the second word of the instruction and load it into the accumulator (Figure 12). The second word in a long format instruction is the effective address unless it is modified by indexing or indirect addressing. The I register contents, loaded into the accumulator during the I1 cycle, are not used.

If the instruction specifies an index register, the contents of that index register were loaded into the accumulator during the I1 cycle. The I2 cycle then reads the address word from core storage and adds it to the index register contents in the accumulator.

Figure 8. I1 Cycle, Single Word, Without Indexing

- 2. Address core storage from M register.

- 3. Read instruction word from core storage; load into B register.

- 4. Load operation, format, and tag registers with B register bits 0-7. Load D register with B register bits 8-15. Extend displacement sign (bit 8) in D register.

- 5.

- Transfer I register to Accumulator. Add D register to Accumulator. Effective address is now in 6. Accumulator. 7. Write-back instruction word into core storage.

- 1. Transfer instruction address from 1 to M.

- 2. Address core storage from M register.

- 3. Read instruction word from core storage; load into B register.

- 4. Load operation, format, and tag registers with B register bits 0-7. Load D register with B register bits 8-15. Extend displacement sign (bit 8) in D register.

- 5. Transfer Index register, selected by Tag bits, to Accumulator.

- 6. Add D register to Accumulator. Effective pddress is now in

- Accumulator.

- 7. Write-back instruction word into core storage.

24245

Figure 10. I1 Cycle, Double Word, Without Indexing

- 1. Transfer instruction address from I to M.

- 2. Address core storage from M register.

- 3. Read instruction word from core storage; load into B register.

- Load operation, format, and tag registers with B register bits 0-7. Load D register with B register bits 8-15. Extend displacement 4. sign (bit 8) in D register.

- 5. Transfer I register to Accumulator.

- 6. Write-back instruction word into core storage.

D register and Accumulator Contents will not be used. 12 cycle will read address word from core storage and place it in the Accumulator.

24246

- 1. Transfer instruction address from 1 to M.

- 2. Address core storage from M register.

- 3. Read instruction word from core storage; load into B register.

- 4. Load operation, format, and tag registers with B register bits 0-7. Load D register with B register bits 8-15. Extend displacement sign (bit 8) in D register.

- 5. Transfer Index register, selected by Tag bits, to Accumulator.

- 6. Write-back instruction word into core storage.

D register contents will not be used. 12 cycle will read the address word into the D register and add it to the index word in the accumulator.

24247

Figure 11. I1 Cycle, Double Word, With Indexing

6. Write-back address word into core storage.

Figure 12. I2 Cycle, Double Word, Without Indexing

#### IA (Indirect Addressing Cycle)

This cycle is used only by double word instructions. A direct address can be generally defined as the location of data in core storage. An indirect address can then be defined as the address of a direct address. For most instructions, the effective address that is generated during I1 and I2 cycles is a direct address.

However, the presence of a "one" in the bit 8 position of the instruction indicates that the effective address is really an "indirect" address.

This "indirect" address is the core storage location of a "direct" address.

The preceding I2 cycle loaded the indirect address into the accumulator. This indirect address may be the address word (Figure 11) or the address word plus the contents of an index register (Figure 12). The IA cycle loads the indirect address into the M register, reads the direct address from the core storage location specified by M, and transfers the direct address to the accumulator via B and D registers (Figure 13).

Only one level of indirect addressing is available in the 1800 system. This means that the indirect address of an instruction always selects a direct address, never another indirect address.

## E (Execution Cycle)

The performance of a computer operation is normally divided into two parts, instruction time (I cycles) and execution time (E cycles).

Each execution time is preceded by its associated instruction time during which the instruction is read from core storage and interpreted.

The function of execution time is to accomplish the objectives of the particular operation specified by the instruction. The required number of machine cycles depends upon the specific operation to be performed (Figure 14).

- 1. Transfer indirect address, loaded into accumulator during 12 cycle, to M register.

- Address core storage from M register.

- 3. Read direct address from core storage; load into B register.

24249

- 4. Transfer B to D.

- 5. Transfer D to A.

- 6. Write-back direct address into core storage.

Figure 13. IA Cycle

The following instructions are complete at the end of their instruction time and require no execution cycles.

- Wait. 1.

- Shift right/left. 2.

- 3. Load status.

- Branch or skip on condition. 4.

- Load index if no index register is specified. 5.

| OP               | CYCLE |                                |    |       |    |          |

|------------------|-------|--------------------------------|----|-------|----|----------|

|                  | 11    | 12                             | IA | El    | E2 | E3       |

| WAIT             | х     | -                              | -  | -     | -  | _        |

| XIO,             | Х     | 1                              | /  | х     | Х  | /        |

| SLA              | Х     | -                              | -  | -     | -  | -        |

| SRA              | Х     | -                              | -  | -     | -  | -        |

| LDS              | Х     | -                              | -  | -     | -  | -        |

| STS              | Х     | /                              | /  | х     | -  | -        |

| BSI              | Х     | 1                              | /  | Х     | -  | -        |

| BSC              | Х     | 1                              | /  | -     | -  | -        |

| LDX              | Х     | 1                              | /  | -     | -  | -        |

| STX              | Х     | 1                              | /  | Х     | -  | -        |

| MDX              | Х     | 1                              | 1  | 1     | /  | -        |

| A                | Х     | 1                              | /  | Х     | -  | -        |

| AD               | Х     | 1                              | /  | Х     | Х  | -        |

| S                | Х     | 1                              | /  | Х     | -  | -        |

| SD               | Х     | 1                              | /  | х     | X  | -        |

| м                | Х     | 1                              | /  | х     | -  | -        |

| D                | Х     | 1                              | /  | Х     | X  | -        |

| СМР              | Х     | 1                              | 1  | Х     | -  | -        |

| DCM              | Х     | 1                              | /  | X     | X  | -        |

| LD               | Х     | 1                              | 1  | Х     | -  | -        |

| LDD              | Х     | /                              | /  | X     | X  | -        |

| sto              | Х     | /                              | /  | X     | -  | -        |

| STD              | Х     | 1                              | 1  | X     | X  | -        |

| AND              | Х     | 1                              | /  | X     | -  | -        |

| OR               | Х     | /                              | /  | X     | -  | -        |

| EOR              | Х     | /                              | /  | Х     | -  | -        |

| - C <sub>3</sub> |       | used.<br>not used.<br>y or may |    | used. |    | <b>4</b> |

| L                |       |                                |    |       |    | 24037C   |

Figure 14. Instruction Usage of I and E Cycles

When the execution time for an operation is complete, the computer is directed to enter the instruction time for the next instruction in sequence.

# E1, E2, and E3 (Execution Cycles)

The functions of individual E-cycles are described as they are used to accomplish the objectives of the various operations. However, each has normal functions and objectives. These normal functions and objectives are performed each E-cycle except during the cycles that they are specifically blocked. These normal functions objectives are:

*T0*: Transfer the effective address that was generated during I-cycles from the accumulator to the M register and read core storage. Load core storage word into B register.

*T1:*

- 1. Transfer the contents of the temporary accumulator storage register (U) to the accumulator (A). (The contents of A are placed in U at the beginning of instruction time, and are returned to A at the beginning of the first E cycle of an instruction.)

- 2. Decrement the shift counter. The shift counter is set during instruction time for the number of cycles required to complete the operation.

- T2: Transfer B to D.

- T3: Set arith ctrl and add flip-flops if required.

T4:

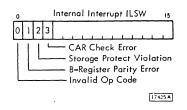

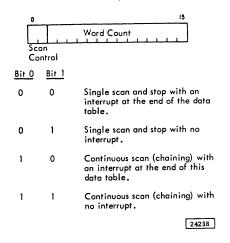

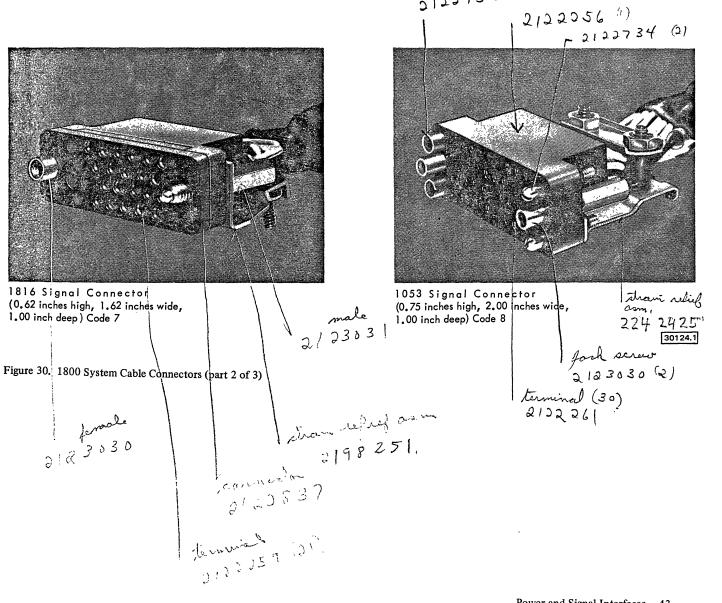

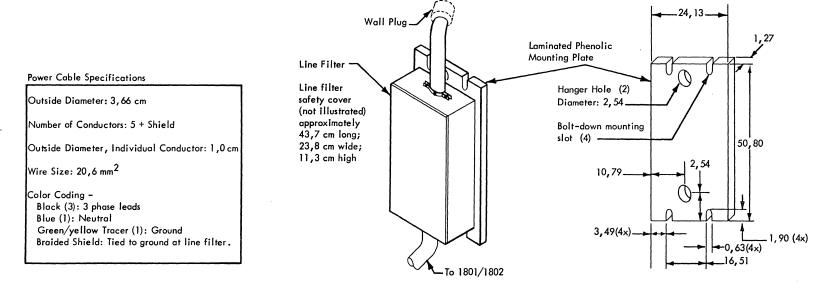

- <sup>1</sup> 1. Store the contents of B back into the core storage location specified by M.