#### THEORY OF OPERATION

09826-66514 CPU BOARD & 09826-66515

This document assumes that the reader is familiar with the operation and requirements of the Motorola MC68000 Microprocessor.

When reading this Theory of Operation, the schematic([(HPDd\*aiming 09826-90300-4), Timing diagrams (HP Drawing 09826-90300-7), Block diagram (HP Drawing 09826-90300-6,) and the Motorola MC68000 Data Manual are useful references.

#### **GENERAL DESCRIPTION:**

The CPU Board contains the CPU chip (68000), control circuitry, Boot Roms, and 64K of Auto-Located RAM. In addition to the standard 68000 control signals, the CPU Board also supplies two special purpose control signals, IOR and IOW. These two signals are used by sub-systems which utilize Intel compatible peripheral chips for controlling reads and writes.

| _] |                   |              | ana amin'ny fisiana amin'ny fisiana amin'ny fisiana amin'ny fisiana amin'ny fisiana amin'ny fisiana amin'ny fis  | MODEL     | 9826A         | STK NO |          |                 |        |     |

|----|-------------------|--------------|------------------------------------------------------------------------------------------------------------------|-----------|---------------|--------|----------|-----------------|--------|-----|

|    |                   |              | and the second |           | THEORY OF OPE | RATION |          |                 |        |     |

| Ĵ  |                   |              |                                                                                                                  | BY        | Carl Anderson |        | DATE     | May 29,         | 1981   |     |

| TR | See page<br>PC NO | 1 for Rev.'s | DATE                                                                                                             |           | Jul           |        | SHEET NO | <sup>2</sup> -2 | OF     | 26  |

|    |                   | REVISIONS    | In a scall with the second standard stands                                                                       | SUPERSEDE | ES            |        | OWG NO   | A-09820         | 5-0032 | Ĵ-Ĵ |

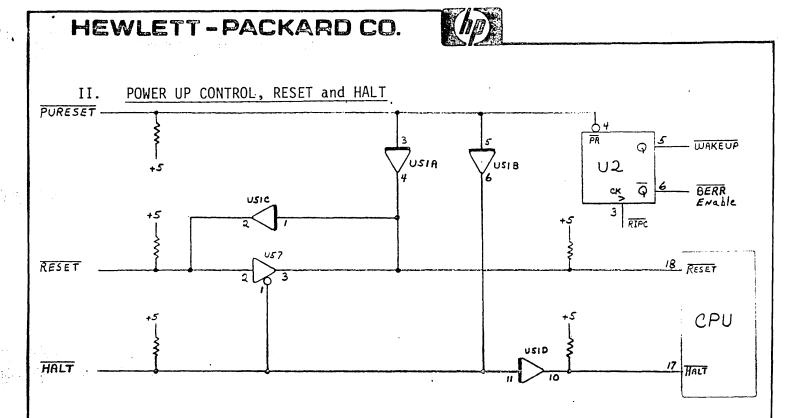

During power-up,  $\overrightarrow{PURESET}$  is asserted by the power supply board. This asserts RESET and HALT to the system bus and the processor through U5, A + B + C and presets U2.  $\overrightarrow{WAKEUP}$  from U2 is negated, inhibiting chip select (See RAM Access section).  $\overrightarrow{BERR}$  Enable is negated allowing suppression of the first  $\overrightarrow{BERR}$ . (See RAM Auto Locate section). After voltages stabilize,  $\overrightarrow{PURESET}$  is negated.

To the CPU, RESET and HALT are both inputs and Outputs. If the CPU is generating a reset due to a RESET instruction, RESET is gated through U51 C to the system bus. This resets all external devices while the state of the processor is not affected. CPU HALT output is not used, and is prevented from being applied to the bus by U51 D.

If  $\overline{\text{RESET}}$  and  $\overline{\text{HALT}}$  are both asserted by an external device,  $\overline{\text{HALT}}$  enables U57 so that  $\overline{\text{RESET}}$  is applied to the CPU along with  $\overline{\text{HALT}}$ . This initiates a total system reset of the CPU and external devices.

A RESET from the system will reset the external devices but not the processor because U57 is not enabled since HALT is not asserted.

|     |                   |             |       | MODEL   | 9826A            | STK NO |                     |       |        |            |    |

|-----|-------------------|-------------|-------|---------|------------------|--------|---------------------|-------|--------|------------|----|

|     |                   |             |       |         | THEORY OF OPERAT | ION    |                     |       |        |            |    |

|     |                   |             |       | BY      | Carl Anderson    |        | <sub>date</sub> Ma  | y 29, | 1981   |            |    |

| LTR | See Dage<br>PC NO | 1 for Rev.' | SDATE | APPD    | EAL              |        | SHEET NO            | 3     | OF     | :          | 26 |

|     |                   | REVISIONS   |       | SUPERSE | DES              |        | <sub>dwg no</sub> A | -0982 | 5-9002 | <u>0-9</u> |    |

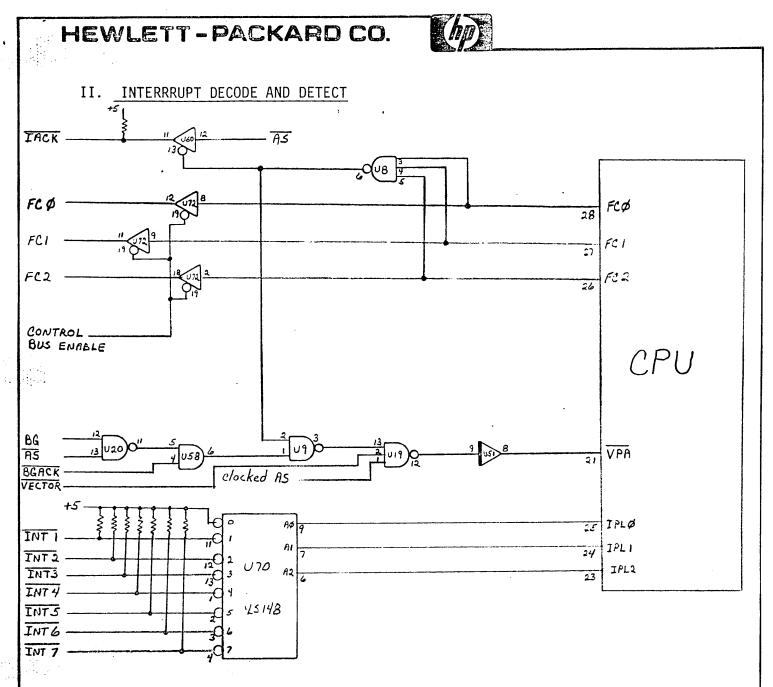

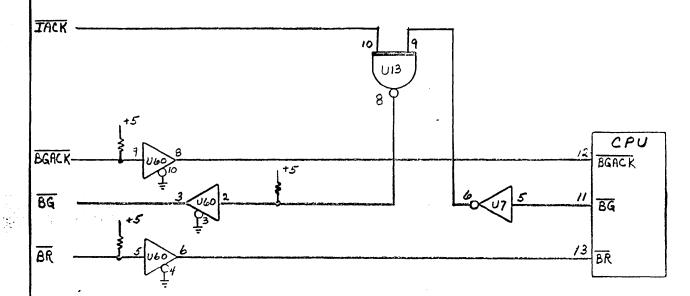

Seven levels of interrupt are decoded into a 3 line binary by U70. Interrupt level 7 is the highest priority, level 0 is no interrupt. Internal circuitry in the CPU inhibits all interrrupts with priority levels less than or equal to the current processor priority.

FCO - FC2 outputs indicate the type of cycle being executed by the processor. During an interrupt cycle, all three outputs are high. These are gated through U8, enabling U60. When AS is asserted, it is gated through U60, asserting TACK (Interrupt Acknowledge) to the interrupting device.

|     |                   |                                                                                                                 |           | MODEL    | 9826A             | STK NO |                         |           |          |    |

|-----|-------------------|-----------------------------------------------------------------------------------------------------------------|-----------|----------|-------------------|--------|-------------------------|-----------|----------|----|

|     |                   | La characterization de la constance de la const |           |          | THEORY OF OPERATI | ON     | generations and the sec | x <b></b> |          |    |

|     |                   |                                                                                                                 |           | 8)<br>8) | Carl Anderson     |        | DATE M                  | ay 29,    | 1981     |    |

| LTR | See page<br>PC NO | <u>1 for Rev.</u>                                                                                               | S<br>DATE | APPD     | enh               |        | SHEET NO                | -4        | OF       | 26 |

|     | REVISIONS         |                                                                                                                 |           | SUPERSE  | DES               |        | dwg no A                | -09826-   | -90320-9 | )  |

7830-00E-L

An interrupt requires that the processor go to some exception handling routine. The addresses of these routines are in memory locations called EXCEPTION VECOTRS. The vector numbers can be generated internally by the CPU or externally.

If the VPA input is asserted, it tells the CPU to generate the vector number internally, based upon the interrupt level (Auto-Vector). If VPA is not asserted, the interrupting device must supply the vector number on DO- D7. Control of the VPA input is accomplished through the VECTOR input. During the interrupt, U19 is enabled by the interrupt detect circuitry explained above (U8), U9 and the clocked AS. If VECTOR is high VPA is asserted indicating auto-vector. If VECTOR is asserted, the interrupting device must supply the vector number.

See the 68000 manual for more detailed information concerning exception processing.

|     |                 |                    |      | MODEL      | 9826A            | STK NO |                                    |       |                  |        |

|-----|-----------------|--------------------|------|------------|------------------|--------|------------------------------------|-------|------------------|--------|

|     |                 |                    |      | -          | THEORY OF OPERAT | ION    |                                    |       |                  |        |

|     |                 |                    |      | BY (       | Carl Anderson    |        | <sub>DATE</sub> May                | ·29,  | 1981             |        |

|     | <u>See page</u> | <u>l for Rev.'</u> | S    | C          |                  | ĺ      |                                    | ĥ     |                  | 26     |

| LTR | PC NO           | APPROVED           | DATE | APPD       | 21mm             |        | SHEET NO                           |       | OF               | ······ |

|     | REVISIONS       |                    |      | SUPERSEDES | s                |        | DWG NO A-                          | 09826 | i <i>—</i> 90320 | -9     |

|     |                 |                    |      |            |                  |        | والمراجع والمطور والمطور ومستغمتها |       |                  |        |

#### M6800 PERIPHERAL CONTROL

The 68000 CPU has three control signals called E (enable), VPA (Valid peripheral address), and VMA (Valid memory address), used for interfacing synchronous M6800 peripheral devices with the asynchronous MC68000.

The E output is the standard enable signal common to all M6300 peripheral devices.

The VPA input indicates that the device addressed is a M6800 family device and it also tells the processor to use automatic vectoring for an interrupt (See interrupt decode and defect).

The VMA output tell M6800 peripheral devices that there is a valid address on the address bus and the processor is synchronized to enable.

|      | a de regenerate a del desensita de la desensita |             |                                                                  | MODEL 9826A      | STK NO                 |

|------|-----------------------------------------------------------------------------------------------------------------|-------------|------------------------------------------------------------------|------------------|------------------------|

|      |                                                                                                                 |             |                                                                  | THEORY OF OPEN   | RATION                 |

|      |                                                                                                                 |             | alandar milita garge garger geförsta hand militärike af 2012 for | BY Carl Andreson | DATE May 29, 1981      |

| LTR  | See page                                                                                                        | 1 for Rev's | DATE                                                             | APPO DA          |                        |

|      |                                                                                                                 | REVISIONS   |                                                                  | SUPERSEDES       | DWG NO A-09826-90320-9 |

| 7830 | )-006-L                                                                                                         |             |                                                                  |                  |                        |

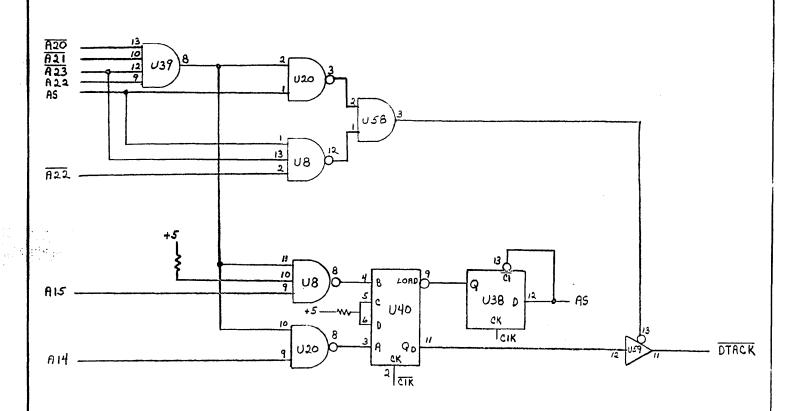

DTACK signals the CPU that a transfer is complete. Auto DTACK is generated on the CPU board and is used to supply the DTACK for the ROM address space and for internal synchronous I/O devices.

The states of A20 through A23 determine the use of Auto DTACK in the following manner:

A20 = synchronous (if internal) A21 = internal A22 and A23 = I/0

U39 and U20 and U8 decode A20 through A23. If an internal, synchronous I/O device is addressed, the output of U58 is low, enabling the transfer of  $\overline{\text{DTACK}}$  through U59.

|     |                      |             |                                                                                                                 | MODEL    | 9826A         | STK NO |                   |        |

|-----|----------------------|-------------|-----------------------------------------------------------------------------------------------------------------|----------|---------------|--------|-------------------|--------|

|     | CHING MALL IN COMMON | <u></u>     | an and a second seco |          | THEORY OF OPE | RATION |                   |        |

|     |                      |             | A NAME AND A NAME AND A NAME AND A DATA AND A | BY       | Carl Anderson |        | DATE May 29, 1981 |        |

| LTR | See page             | 1 for Rev's | DATE                                                                                                            |          | STUL          |        | SHEET NO 67       | of 226 |

|     | REVISIONS            |             |                                                                                                                 | SUPERSED | ES            |        | DWG NO A-09826-90 | 320-9  |

Since different devices require different access times, A14 and A15 are used to determine the number of wait states after AS before U40 enables DTACK as shown in the following truth table:

| <u>A15</u> | <u>A14</u> | <u>Wait (cycles)</u> | Access time (clock cycles) |

|------------|------------|----------------------|----------------------------|

| 0          | 0          | 0                    | 5                          |

| 0          | 1          | 1                    | 6                          |

| 1          | 0          | 2                    | 7                          |

| 1          | 1          | 3                    | 8                          |

AS and DATA STROBES are negated by the processor after it sees DTACK asserted when AS is negated, U38 is cleared, allowing U40 to load and dissabling the count and U59 is inhibited negating DTACK.

The following examples show how the auto DTACK wait states correspond with the processor access cycle:

Access cycle with 0 wait states (5 cycle access) Cycle 1 Place address on bus Cycle 2 Assert AS and Data strobes Cycle 3 Assert DTACK Cycle 4 Transfer data Cycle 5 Terminate access by negating AS, Data strobes, and DTACK

Access cycle with 3 wait states (8 cycle access)

| Cycle 1 | Place address on bus                                               |

|---------|--------------------------------------------------------------------|

| Cycle 2 | Assert $\overline{\text{AS}}$ and $\overline{\text{Data strobes}}$ |

| Cycle 3 | Wait                                                               |

| Cycle 4 | Wait                                                               |

| Cycle 5 | Wait                                                               |

|     |          |             | an a                                                  | MODEL 98         | 26A      | STK NO    |          |        |          |             |  |

|-----|----------|-------------|-------------------------------------------------------------------------------------------|------------------|----------|-----------|----------|--------|----------|-------------|--|

|     | ĺ        |             |                                                                                           | T۲               | EORY OF  | OPERATION |          |        |          |             |  |

|     |          |             | n an                                                  | <sub>вү</sub> Са | rl Ander | rson      | DATE     | May 29 | , 1981   |             |  |

| LTR | See page | 1 for Rev.' | DATE                                                                                      |                  | Thil     |           | SHEET NO | 78     | OF       | _ <b>26</b> |  |

|     |          | REVISIONS   | an an a' le company ann an Crubban (1988) a' le sa an | SUPERSEDES       | 7        |           | DWG NO   | A-0982 | 6-190321 | 0-9         |  |

( **)**

.

,

(h)

|               |           | Cycle 6<br>Cycle 7 | Assert DTACK<br>Transfer data            |                      |

|---------------|-----------|--------------------|------------------------------------------|----------------------|

|               |           | Cycle 8            | Terminate access by negat<br>and DTACK   | ing AS, Data Strobes |

|               |           |                    |                                          |                      |

|               |           |                    |                                          |                      |

|               |           |                    |                                          |                      |

|               |           |                    |                                          |                      |

|               |           |                    |                                          |                      |

|               |           |                    |                                          |                      |

|               |           |                    |                                          |                      |

|               |           |                    |                                          |                      |

|               |           |                    |                                          |                      |

|               | · · · - · |                    |                                          |                      |

|               |           |                    |                                          |                      |

|               |           |                    |                                          |                      |

|               |           |                    |                                          |                      |

|               |           |                    |                                          |                      |

|               |           |                    |                                          |                      |

| 1             |           |                    |                                          |                      |

|               |           |                    | MODEL 9826A STK NO<br>THEORY OF OPERATIO |                      |

|               |           |                    | Garl Anderson                            | May 29, 1981         |

|               | bage 1 fc | or Rev.'s          | DATE APPD ESTA                           | SHEET NO 9 OF 2      |

| See r<br>pc n |           | APPROVED           |                                          |                      |

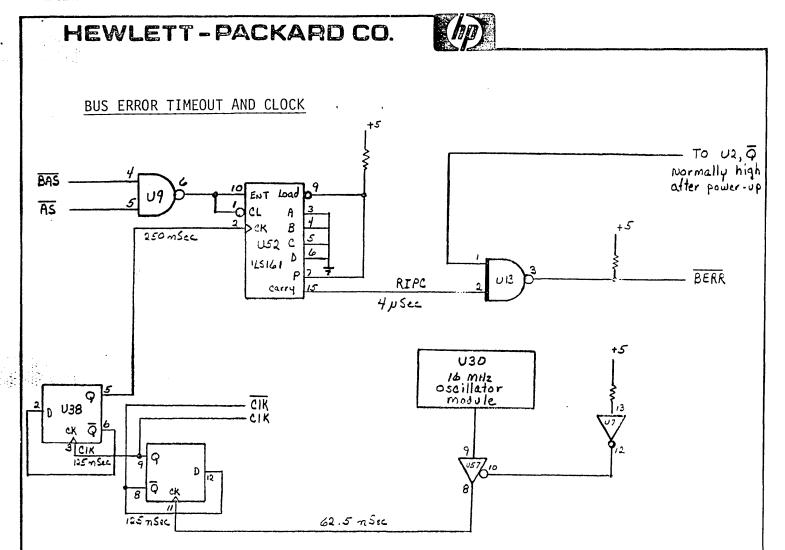

DTACK signals the processor that a data transfer is complete so that the CPU can terminate the cycle. BERR tells the CPU that DTACK has not occured during a pre-determined amount of time and it should initiate an exception processing cycle.

U30 generates a 16 MHZ clock. This is divided by 2 by U28 to produce the 8 MHZ ClK and  $\overline{ClK}$  system clocks. ClK is again dividied by 2 by U38 to produce a 4MHZ clock to the bus error timeout counter, U52.

When  $\overline{AS}$  and  $\overline{BAS}$  are negated the clear and enable T inputs of U52 are held low, disabling the counter. When  $\overline{AS}$  and/or  $\overline{BAS}$  are asserted, enable T and clear go high allowing U52 to count. Since U52 is clocked

|     |                                           |              |                                       | MODEL | 9826A    | ST         | K NO |                     |         |        |    |

|-----|-------------------------------------------|--------------|---------------------------------------|-------|----------|------------|------|---------------------|---------|--------|----|

|     | U-12-24-1-2-1-2-1-2-1-2-1-2-1-2-1-2-1-2-1 |              | · · · · · · · · · · · · · · · · · · · |       | THEORY O | F OPERATIO | DN   |                     |         |        |    |

|     |                                           | 1 fan Day l  |                                       | вү    | Carl And | erson      |      | DATE                | May 29  | , 1981 | -  |

| LTR | See page                                  | 1 for Rev.'s | DATE                                  | APPD  | PAL      |            |      | SHEET NO            | .10     | OF     | 26 |

|     | REVISIONS                                 |              |                                       |       | DES      |            |      | <sub>dwg no</sub> A | -09826- | 90320  | -9 |

at a 250 nS rate, it takes 4  $\mu$ S until RIPC is asserted. If  $\overline{AS}$  and  $\overline{BAS}$  are negated during this time, indicating a data transfer acknowledge has been asserted, U52 will be cleared and inhibited preventing RIPC. If  $\overline{DTACK}$  is not asserted during the 4  $\mu$ S that U52 is counting, RIPC is asserted and, except at power-up (see RAM Auto Locate section), is gated through U13 to produce  $\overline{BERR}$ . Upon seeing  $\overline{BERR}$ , the microprocessor goes into an exception processing sequence.

|     |          |                 | y de serie de contra constante en la serie de la s<br>Serie de la serie | MODEL 9826A           | STK NO                                         |          |          |       |    |

|-----|----------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------------------------------------|----------|----------|-------|----|

|     |          |                 |                                                                                                                                                                                                                                     | THEORY                | OF OPERATION                                   |          |          |       |    |

|     |          |                 |                                                                                                                                                                                                                                     | <sub>By</sub> Carl Ar | nderson                                        | DATE May | 29, 198  | 1     |    |

| LTR | See page | <u>APPROVED</u> | S                                                                                                                                                                                                                                   | APPO DEM              | тран. — на | SHEET NO | 11       | OF    | 26 |

|     |          | REVISIONS       | Anna anna an Anna an Armainn a' Marainn an Ar                                                                                                                                                                                       | SUPERSEDES            |                                                | DWG NO A | -09826-9 | 0320- | 9  |

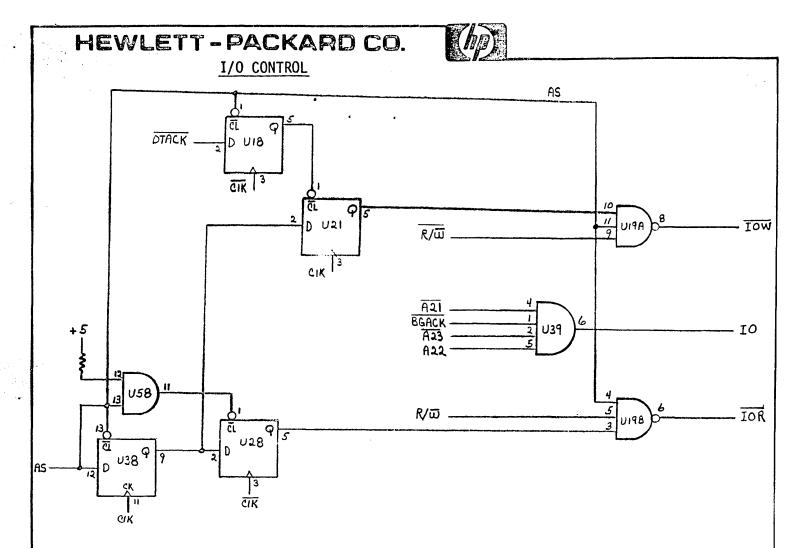

The two control signals  $\overline{IOW}$  and  $\overline{IOR}$  are used as control signals for Intel compatable peripheral chips. The signal IO is used to aid in internal chip select decoding.

U39 decodes A23, A22, and A21 to determine an I/O address. If the CPU has control of the bus, indicated by the negation of  $\overline{BGACK}$ , IO is asserted.

Before  $\overline{AS}$  is asserted, U38, U28, U18, and U21 are cleared by AS low. When  $\overline{AS}$  is asserted, either U19A or U19B is enabled depending upon the state of R/W. The first rising edge of the clock after AS is asserted clocks AS through U38. On the falling edge it is clocked through U28. If the operation is an I/O read,  $\overline{IOR}$  is asserted at this

|    |          |             |      | MODEL  | 9826A             | STK NO |          |         |         |     |

|----|----------|-------------|------|--------|-------------------|--------|----------|---------|---------|-----|

|    |          |             |      |        | THEORY OF OPERATI | (ON    |          |         |         |     |

|    |          |             |      | BY     | Carl Anderson     |        | DATE     | May 29, | 1981    |     |

|    | See page | 1 for Rev.' | 5    |        | $ \sim 0 $        |        |          | 112     |         | 26  |

| TR | PC NO    | APPROVED    | DATE | APPD   | tome              |        | SHEET NO | - 12    | OF      | 20  |

|    |          | REVISIONS   |      | SUPERS | EDES              |        | DWG NO   | A-09826 | 5-90320 | )-9 |

time. The next rising edge of the clock, U21 transfers AS to U19. If the operation is an I/O write,  $\overline{IOW}$  is asserted.  $\overline{IOW}$  is negated by  $\overline{DTACK}$  being clocked through U18, clearing U21.  $\overline{IOR}$  is negated by the negation of AS at U19.

|     |          |              | ne an ann an tha ann an tha ann an tha a<br>An ann an tha ann an tha an | MODEL     | 9826A           | STK NO |          |         |        |           |

|-----|----------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------------|--------|----------|---------|--------|-----------|

|     |          |              |                                                                                                                                                                                                                                   |           | THEORY OF OPERA | TION   |          |         |        |           |

|     |          |              |                                                                                                                                                                                                                                   | BY        | Carl Anderson   |        | DATE     | May 29, | 1981   |           |

| LTR | See page | 1 for Rev.'s | DATE                                                                                                                                                                                                                              |           | Inh             |        | SHEET NO | 13      | OF     | <b>26</b> |

|     |          | REVISIONS    |                                                                                                                                                                                                                                   | SUPERSEDE | <u>s</u>        |        | DWG NO   | A-0982  | 26-903 | 20-9      |

EXTERNAL BUS CONTROL

An external device capable of controlling the bus requests the bus by asserting  $\overline{BR}$  (Bus Request). When the processor sees  $\overline{BR}$ , it asserts  $\overline{BG}$  indicating that it will release bus control at the end of the current bus cycle.

U13 is enabled by TACK negated so that a bus request cannot be honored until after the processing of an interrupt. When the requesting device receives the BG and sees the negation of AS, indicating the termination of the current processor cycle, it asserts BGACK (Bus Grant Acknowledge). The external device then has control of the bus until it negates BGACK.

|                |                   |              |        | MODEL     | 9826A           | STK NO | . <u> </u>        |

|----------------|-------------------|--------------|--------|-----------|-----------------|--------|-------------------|

| and the second |                   |              |        |           | THEORY OF OPERA | TION   |                   |

|                |                   |              |        | ВҮ        | Carl Anderson   |        | May 29, 1981      |

| LTR            | See page<br>PC NO | 1 for Rev. ' | S DATE | APPD F    | Inch            |        | SHEET NO 14 OF 26 |

|                | 0.000             | REVISIONS    |        | SUPERSEDE | S               |        | A-09826-90320-9   |

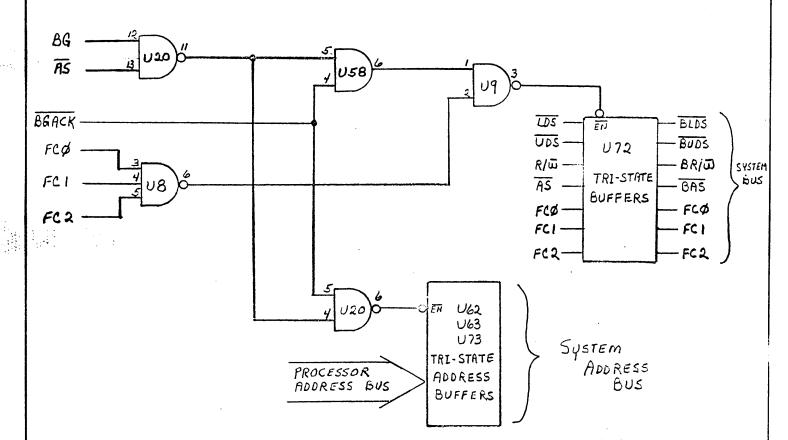

BUS CONTROL, CPU STATUS, AND ADDRESS BUFFERS

During a DMA cycle the CPU gives up control to an external device. The system address bus and control bus must be tri-stated to that the controlling device can apply signals to them. This is accomplished by decoding  $\overline{BG}$ ,  $\overline{BGACK}$ , and  $\overline{AS}$  with U20, U58, and U9. If the states of  $\overline{BG}$ ,  $\overline{BGACK}$ , and  $\overline{AS}$  indicate that an external device has control, U72 and the address buffers are tri-stated by bringing their enable inputs high.

During an interrupt cycle, the CPU is active during vector number acquisition (see Interrupt Decode and Detect), but the control signals are isolated from the system control bus, so that the I/O card responds to the IACK access not the RAM in the top of memory. U8 and U9 decode the states of FCO-FC2 (all high during interrupt) and tri-state U72.

|             |          |                       | n a sa an | MODEL            | 9826A           | STK NO                             |          |         |         |    |

|-------------|----------|-----------------------|-----------------------------------------------|------------------|-----------------|------------------------------------|----------|---------|---------|----|

|             | 1000.000 |                       |                                               |                  | THEORY OF OPERA | TION                               |          |         |         |    |

|             |          |                       |                                               | BY               | Carl Anderson   |                                    | DATE     | May 29, | 1981    |    |

| Ballet Mart | See page | 1 for Rev.'s          | - MANAGARI DI TIMUN MANY MILANDI DI TIMUN     | 1000 9           | EAD V           |                                    |          | 15      |         | 26 |

| LTR         | PC NO    | APPROVED<br>REVISIONS | DATE                                          | APPD<br>SUPERSED | DES .           | 4 Million (1998), Said Marines and | SHEET NO | A-09826 | -90320- | .9 |

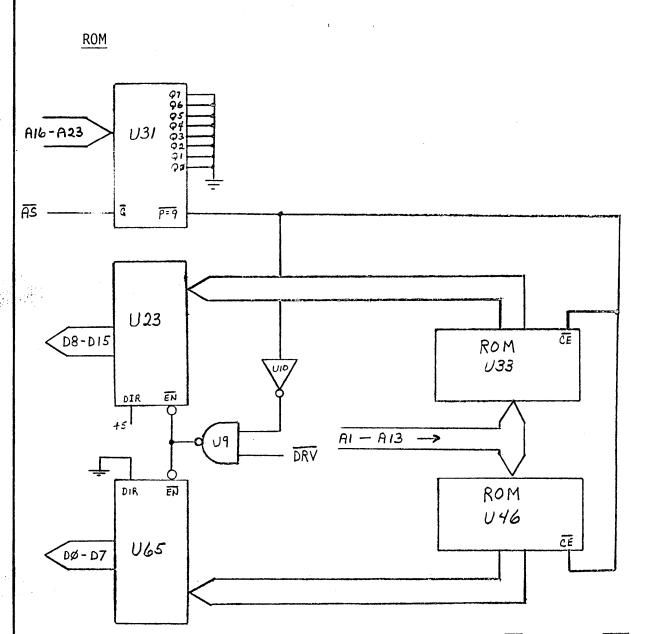

U31 decodes a low on A16 through A23 to enable  $\overline{CE}$  to ROM.  $\overline{DRV}$  is normally high so  $\overline{p=q}$  is gated through U9 to enable the data buffer U23 and U65. Data at the location addressed by the address bus is transferred through the buffers onto the processor data bus.

$\overline{\text{DRV}}$  is used to isolate the ROM data output from the CPU data bus for test purposes. If  $\overline{\text{DRV}}$  is asserted, the data buffers are never enabled.

|     |                         | REVISIONS                                |                                                                                                                 | SUPERSEDES | -            |        | DWG NO | A-098  | 26-9032 | <u>j-9</u> |

|-----|-------------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------|------------|--------------|--------|--------|--------|---------|------------|

| LTR | <u>See pag</u><br>рс NO | APPROVED                                 | DATE                                                                                                            |            | ml           |        |        | 16     | OF      | 26         |

|     |                         |                                          |                                                                                                                 | BY         | Carl Anderso | n      | DATE M | ay 29, | 1981    |            |

|     |                         | an a | y animites and all all the first standard spaces and an and a standard standard standard standard standard stan |            | THEORY OF OP | ERATIO | N      |        |         |            |

|     |                         |                                          |                                                                                                                 | MODEL      | 9826A        | STK NO |        |        |         |            |

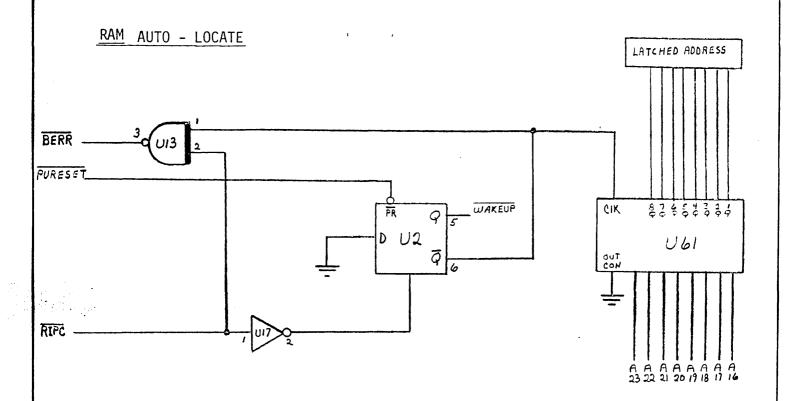

The on beard RAM locates itself at the bottom of RAM memory. This auto-locate feature eliminates the need for user set switches on an internal board.

U2 is preset by PURESET at turn on. The low Q output inhibits U13. During wake up, the processor writes to and reads from each block of memory to determine how much memory is available. When there is no response from a memory card indicating end of memory, RIPC is asserted by the Bus Error Timeout circuit. Since U13 is inhibited, BERR is not asserted. Instead, U2 is clocked by RIPC. This enables U13 so that subsquent Bus Errors will be asserted, and clocks the address that is present when this first RIPC accurs into latch U61. Because the D input

|     |                                           | n a salangan ku saka sa a sa |                                                      | MODEL    | 9826A      |      | STK NO |          |         |         |            |

|-----|-------------------------------------------|------------------------------------------------------------|------------------------------------------------------|----------|------------|------|--------|----------|---------|---------|------------|

|     |                                           |                                                            |                                                      |          | THEORY OF  | OPER | ATION  |          |         |         |            |

|     |                                           |                                                            |                                                      | BY       | Carl Ander | son  |        | DATE     | May 29, | 1981    |            |

| LTR | See page                                  | 1 for Rev.'                                                | S<br>DATE                                            | APPD <   | BML        |      |        | SHEET NO | 117     | ÛF      | <b>226</b> |

|     | 2. 300 A 10 | REVISIONS                                                  | AND THE SHOW AND THE TAXABLE IN COMPANY OF THE PARTY | SUPERSED | ES         |      |        | DWG NO   | A-0982  | 6-90320 | i-9        |

of U2 is tied low, U2 and U61 outputs will remain in this state until power is cycled.

The latched address from U61 is used by the RAM Location Decoder to provide chip select to the RAM.

|     |                                                                                                                |                                                                                                                 |                                                                                                                 | MODEL 9826A | STK NO       |               |                    |

|-----|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------------|--------------|---------------|--------------------|

|     |                                                                                                                | and a subservery of the contract of the second of the s | . Man and the design of the second | THEORY      | OF OPERATION |               |                    |

|     | a a construction of the second se |                                                                                                                 |                                                                                                                 | BY Carl Ar  | nderson      | DATE May 29,  | 1981               |

| LTR | See page                                                                                                       | 1 for Rev.                                                                                                      | S.<br>DATE                                                                                                      | APPD ETA    |              | SHEET NO 18   | <sub>of</sub> 26   |

|     |                                                                                                                | REVISIONS                                                                                                       | Contraction and the second  | SUPERSEDES  |              | DWG NO A-0982 | 6-9032 <b>0-</b> 9 |

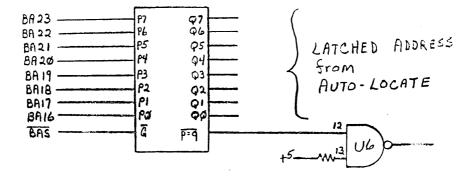

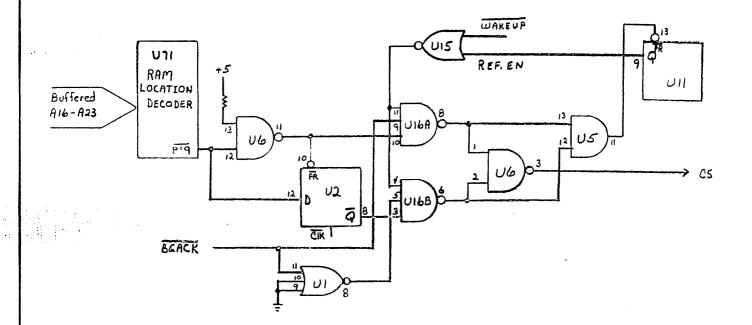

#### RAM LOCATION DECODER

The outputs of the RAM Auto Locate circuit (U61) are tied to Q inputs of comparator U71. When the address on BA16 through BA23 matches the latched address from Auto Locate and when U71 is enabled by  $\overline{\text{BAS}}$ , the output of U71 is asserted. If Ram is not being refreshed this output is gated to become chip select.

| L        |          |                   |                                                                                                                 |            |         |         |        |                      |          |     |

|----------|----------|-------------------|-----------------------------------------------------------------------------------------------------------------|------------|---------|---------|--------|----------------------|----------|-----|

|          |          |                   |                                                                                                                 | MODEL      | 9826A   |         | STK NO |                      |          |     |

| <u> </u> |          |                   | and a second construction of the second s |            | THEORY  | OF OPER | ATION  |                      |          |     |

|          |          |                   |                                                                                                                 | BX         | Carl Ar | nderson | DATE   | May 29               | , 1981   |     |

| LTR      | See page | <u>1 for Rev.</u> | S<br>DATE                                                                                                       | APPD E     | The     |         | SHEE   | TNO 19               | OF       | .26 |

|          |          | REVISIONS         | C ADM. NY TA TOMOTOR AND                                                    | SUPERSEDES |         |         | DWG    | <sub>No</sub> A-0982 | 26-90320 | -9  |

(hp)

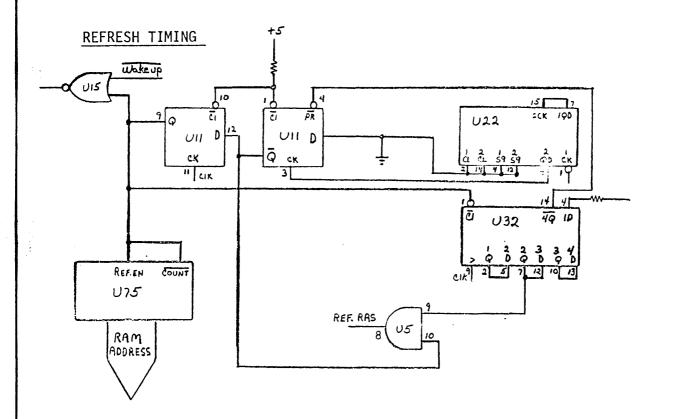

The 2118-4 RAM requires that each of the 128 rows be refreshed at least every 2 mS. This is accomplished by the dual decade counter, U22. The  $\overline{\text{CLK}}$  input is 125 nS. U22 divides this by 100 producing an output which clocks U11 pin 3 at a 12.5  $\mu$ S rate. Because the D input (pin 2) of U11 is tied low, when it is clocked by U22 it's  $\overline{Q}$  output (pin 6) goes high. On the next rising edge of the clock Ref. en (U11 pin 9) is asserted. This occurance of Ref. en every 12.5  $\mu$ S enables each row to be refreshed every 1.6 mS.

When Ref. en is asserted the internal counter of U75 supplies the refresh address to RAM, the output of U15 goes low disabling chip select, and the clear input of U32 is brought high allowing it to start counting.

| <b>2</b> |          |                                                                                                                 |      | MODEL 9826A                  |           | STK NO |         |          |                 |

|----------|----------|-----------------------------------------------------------------------------------------------------------------|------|------------------------------|-----------|--------|---------|----------|-----------------|

|          |          | 979-979 (* 1994) (* 1995) (* 1995) (* 1995) (* 1995) (* 1995) (* 1995) (* 1995) (* 1995) (* 1995) (* 1995) (* 1 |      | THEOR                        | Y OF OPER | ATION  |         |          |                 |

|          |          |                                                                                                                 |      | <sub>BY</sub> Carl           | Anderson  | DATE   | May 29, | 1981     |                 |

| menune.  | See page | 1 for Rev.'                                                                                                     |      | APPD STA                     | L         | SHEET  | 20      | OF.      | 26              |

| LTR      | PC NO    | APPROVED                                                                                                        | DATE | and the second states of the |           |        | A-09826 | 5-903P0- | -9 <sup>-</sup> |

|          |          | REVISIONS                                                                                                       |      | SUPERSEDES                   |           | DWG NC |         |          |                 |

(hp)

250 nS (2 clocks) later, 2Q of U32 (pin 7) goes high. At this time, both inputs of U5 are high, asserting the Ras for Refresh. After another 250 nS,  $U3^{\circ}$ 's  $\overline{40}$  output (pin 14) goes low. This negates the refresh Ras by reseting U11 bringing U5 pin 10 low. The next rising edge of the clock negates ref.en,U15's output (pin 10) goes high enabling chip select, U32 is cleared, and the internal counter of U75 is advanced by asserting count.

|              |                                      |             | aused an of allowing production (see, etc., and production (see allowing)) (2000)                                | MODEL      | 9826A       | STK     | K NO |         |        |         |      |  |

|--------------|--------------------------------------|-------------|------------------------------------------------------------------------------------------------------------------|------------|-------------|---------|------|---------|--------|---------|------|--|

| _            | AND A REAL PROPERTY OF A DESCRIPTION |             | and the second |            | THEORY OF ( | OPERATI | ION  |         |        |         |      |  |

|              |                                      |             | A NEW YORK AND                                                               | BA         | Carl Anders | son     | D    | ATE     | May 29 | , 1981  |      |  |

| LTR          | See page                             | 1 for Rev.' | DATE                                                                                                             | APPD E     | ml          |         | s    | HEET NO | 21     | . 01    | 26   |  |

| an constants |                                      | REVISIONS   | AN ADDRESS OF THE REAL POINT OF THE POINT OF T  | SUPERSEDES |             |         | D    | WG NO   | A-098  | 26-9032 | 20-9 |  |

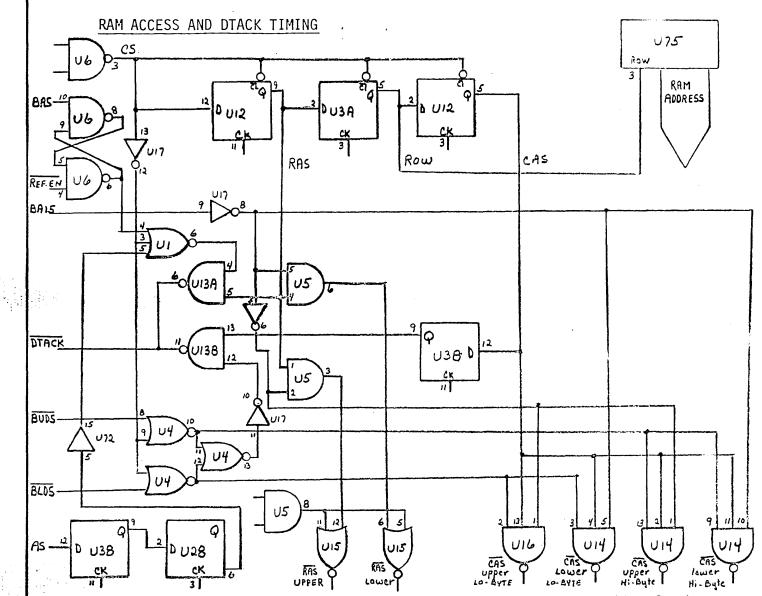

RAM ACCESS

If RAM is being refreshed, the Ref.en input to U15 is high. The output of U15 is low inhibiting both gates of U16. This causes CS to remain low. When the refresh is complete, Ref.en is negated. The output of U15 then enables both gates of U16.

If RAM is being accessed by the CPU,  $\overrightarrow{BGACK}$  is high,  $\overrightarrow{p=q}$  is inverted by U6 and fed to U16 pin 10. Since this gate is enabled by  $\overrightarrow{BGACK}$  high and Ref.en low, U16 pin 8 goes low allowing U6 to assert CS. At the same time, U5 is inhibited causing its output to go low. This presets the Ref.en flip-flop (U11) preventing refresh from occuring during a memory access.

Because DMA is asynchronous with the clock and RAM control is synchronous, a means must be provided to synchronize a DMA access of RAM to prevent possible timing problems. This is accomplished with

| $\square$ |                   |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | MODEL 9826A      | STK NO   |                |        |     |

|-----------|-------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------|----------------|--------|-----|

|           |                   |             | an a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | THEORY OF OPERAT | LION     |                |        |     |

|           |                   | 1           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | BY Carl Anderson | DATE     | <u>May 29,</u> | 1981   |     |

| LTR       | See page<br>PC NO | 1 for Rev.' | DATE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | APPD ATTL        | SHEET NO | 22             | OF     | -26 |

|           |                   | REVISIONS   | and an existing a structure of distance of the second structure of the second | SUPERSEDES       | DWG NO   | A-09826        | -90320 | )-9 |

| 7830      | -006-L            |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                  |          |                |        |     |

U2 and U16B.

During DMA  $\overrightarrow{BGACK}$  is asserted. This inhibits U16A. U1 inverts  $\overrightarrow{BGACK}$  and enables U16B. When  $\overrightarrow{p=q}$  is asserted, it is clocked through U2 by  $\overrightarrow{clk}$  and inverted, gated through U16B and U6, asserting CS. At the same time, U5 is inhibited presetting U11 to prevent refresh.

$\overline{WAKEUP}$  is normally low except during power-up. At power-up, on board RAM could be located anywhere, depending upon the state of the RAM location decoder. If  $\overline{WAKEUP}$  is high, CS is negated and stays that way until the first bus error. (See RAM Auto-Locate).

|      |          |             |                                                     | MODEL 9826A | STK NO       |             |                  |  |

|------|----------|-------------|-----------------------------------------------------|-------------|--------------|-------------|------------------|--|

|      |          |             | a a canadam a sa s | THEORY      | OF OPERATION |             |                  |  |

|      |          |             |                                                     | BY Carl Ar  | derson       | DATE May 29 | 9, 1981          |  |

| LTR  | See page | 1 for Rev.' | DATE                                                | APPO FORL   | 999          | SHEET NO 23 | <sub>0F</sub> 26 |  |

|      |          | REVISIONS   | 2                                                   | SUPERSEDES  |              | A-0982      | 26-90320-9       |  |

| 7830 | D-006-L  |             |                                                     |             |              |             |                  |  |

A normal CPU access of RAM is a 5 cycle access. However, if Refresh occurs during the access, time must be allowed for the refresh before the transfer of data can occur. This is accomplished by controlling the time at which DTACK occurs. During a normal access, ENDT is gated to provide DTACK. When RAM is accessed during a refresh cycle, ENDT is ignored, and since CAS won't occur until after refresh, it is gated to provide DTACK.

|     |                   |              | n an                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | MODEL      | 9826A<br>THEORY OF OPI | STK NO<br>ERATION | V                 |  |  |

|-----|-------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------------------|-------------------|-------------------|--|--|

|     |                   |              | ) and the former, as a sense of the form of the set of | Вү         | Carl Anderson          | n                 | May 29, 1981      |  |  |

| LTR | See page<br>pc NO | 1 for Rev.'s | DATE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | APPD D     | hele ,                 |                   | SHEET NO 24 OF 26 |  |  |

|     | REVISIONS         |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | SUPERSEDES |                        |                   | A-09826-90320-9   |  |  |

### Hewlett-Packard Co.

#### RAM Access with no Refresh

While CS is negated, U12 and U3 are cleared negating RAS, enabling row address to RAM by pulling the row input to U75 low, and negating CAS. When CS is asserted, it is clocked through U12 asserting RAS. RAS is gated to U5 pin 6 or pin 3 depending upon the state of BA15. If BA15 is high, RAS is gated to U15 pin 12 asserting RAS upper. If BA15 is low, it is gated to U15 pin 6 asserting RAS lower. At the same time, RAS enables U13A (EDTACK) and AS has been clocked through U38. The next clock falling edge clocks RAS through U3 asserting Row which enables the column address to RAM through U75, and AS is clocked through U28 asserting ENDT. ENDT is inverted by U1 and applied to U13A, asserting DTACK. The next clock transition clocks Row through U12 asserting CAS. CAS is gated to RAM through U14 and U16 depending upon the states of UDS, LDS, and BA15. BA15 determines high or low address, UDS and LDS determine high or low byte or both.

#### RAM Access with a Refresh

During a refresh cylce Ref.en is asserted, inverted and latched by U6, CS is inhibited and RAS remains low. These signals combine to inhibit U13A. When Ref.en is negated, indicating end of refresh, CS is asserted, CS goes low and BUDS and/or BLDS have already been asserted. These are gated through U4 and U17 enabling U13B (LDTACK). RAS, ROW, and CAS are clocked through U12 and U3 in the manner described above. CAS is clocked through U3B asserting LDTACK which is gated through U13 asserting DTACK.

|                      |                                                                                                                                                                                                                                    |                                          | The submitted states in the submitted states and the                                                                                                                                                                                | 1                   | and a second |  |  |  |  |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                      | ARE STORE AND ADDRESS OF A THE STORE                                                                                                                                                                                               |                                          |                                                                                                                                                                                                                                     | MODEL 9826A STK NC  | 0                                                                                                              |  |  |  |  |

| <b>B</b> alence      | NEW COMPANY AND AND AND                                                                                                                                                                                                            | an a |                                                                                                                                                                                                                                     | THEORY OF OPERATION |                                                                                                                |  |  |  |  |

|                      | A CARGONING STOLEN AND A CARGONING                                                                                                                                                                                                 |                                          | a na pra na prantski kalendar na prantski prantski prantski prantski prantski prantski prantski prantski prants<br>V se prantski | By Carl Anderson    | May 29, 1981                                                                                                   |  |  |  |  |

| LTR                  | See page                                                                                                                                                                                                                           | 1 for Rev.                               | S                                                                                                                                                                                                                                   | APPO SML            | SHEET NO 25 OF 286                                                                                             |  |  |  |  |

| 2003-207<br>2003-207 | a de ser antigen de la calculation de la constant de ser de ser de ser antigen de ser a la ser de ser de ser de<br>La constant de la calculation de la constant de la constant de ser de |                                          |                                                                                                                                                                                                                                     | SUPERSEDES          | A-09826-90320-9                                                                                                |  |  |  |  |

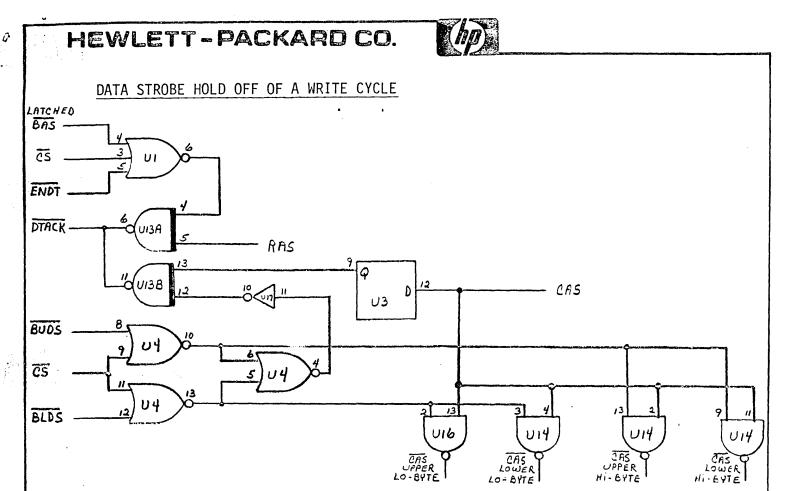

During a DMA write to RAM, the amount of time necessary to set up data to RAM is unknown. Because of this the DMA controller starts the RAM access by placing the RAM address on the bus and asserting  $\overline{\text{BAS}}$ . While data is being set up, the DMA controller holds off the data strobes until data is valid.  $\overline{\text{ENDT}}$  is inhibited because the control bus is tristated when the CPU gives up control, so U13A (EDTACK) is inhibited.

RAS, ROW, and CAS are asserted in the normal manner, but  $\overline{CAS}$  is not applied to RAM, because U16 and U14 are inhibited by the negation of the data strobes.

Once data is valid, the DMA controller asserts  $\overline{\text{BUDS}}$  and/or  $\overline{\text{BLDS}}$ , which are gated through U4 and U16 or U14 to assert  $\overline{\text{CAS}}$ , and through U4, U17, and U13 to assert  $\overline{\text{DTACK}}$ .