#### THONE WELL PROBRIETARY SENSITIVE

HANFYWELL PRADBLETARY \_ CONFITURE

#### PROPRIETARY NOTICE

The information and design of the system described herein ware originated by and are the property of Electronic Data Processing Division, Honeywell, Inc. The content of this document is <u>Honeywell Proprietary -</u> <u>Sensitive</u> and is for internal use only. Such information may not be reproduced, disclosed to others, or used by others for any purpose without written permission from an authorized Honeywell official.

#### NOTE

The demands of expediency in publishing this preliminary document have precluded the editorial attention usually given to such documents. The reader should consider this if inconsistencies, redundancies, or errors become evident herein.

## TABLE OF CONTENTS

## Paragraph

## Title

Page

SECTION II - FORMAT REPRESENTATIONS AND DESCRIPTIONS

| 2.1     | DATA REPRESENTATIONS AND DATA CONTROL DESCRIPTION | DNS 2-1  |

|---------|---------------------------------------------------|----------|

| 2.2     | DATA REPRESENTATIONS                              | 2-2      |

| 2.2.1   | Variable - Length Data Representations            | Loui I   |

| 2.2.2   | Fixed - Length Tagged Data Representations        | 2-6      |

| 2.3     | DATA DESCRIPTION                                  | A. mar S |

| 2.3.1   | Structors                                         | 2 - 25   |

| 2.3.1.1 | Implicit - Length Structor                        | 2-5      |

| 2.3.1.2 | Explicit - Length Structor                        | 1-10     |

| Ż.3.2   | Ministructors                                     | 1. 1.    |

| 2.3.2.1 | Singular Ministructor                             | 1        |

| 2.3.2.2 | Dual Ministructor                                 | 2        |

| 2.3.2.3 | Array Ministructor                                | 2、24     |

| 2.3.2.4 | String Ministructor                               | 2-20     |

| 2.3.3   | Microstructors                                    | 2-22     |

| 2.3.3.1 | Bit/Binary String Microstructor                   | 2-23     |

| 2.3.3.2 | Byte String Microstructor                         | 2-23     |

| 2.3.3.3 | Implicit Microstructos                            | 2-24     |

| 2.4     | CONTROL INFORMATION REPRESENTATION                | 2-25     |

| 2.4.1   | System Convrol Structors                          | 2-25     |

| 2.4.1.1 | Procedure Index                                   | 2-27     |

| 2.4.1.2 | TSB Identifiers                                   | 228      |

| 2.4.1.3 | Protected Elementa                                | 228      |

| 2.4.1.4 | Trap Effectors                                    | 2-29     |

| 2.4.2   | System Base                                       | 2-29     |

| 2.4.3   | Task Status Block                                 | 2-31     |

| 2.4.4   | Task Priority Array                               | 2-35     |

| 2.4.5   | I/O Start Array                                   | 2-35     |

| 2.4.6   | External Start Array                              | 2-36     |

| 2.4.7   | Processor Status Array                            | 2-37     |

| 2.5     | I/O INFORMATION REPRESENTATION                    | 2-38     |

| 2,5.1   | I/O Structors                                     | 2-38     |

|         |                                                   |          |

#### TABLE OF CONTENTS (Cont.)

#### Paragraph Title Page 2-39 2.5.1.1 Device Identifier Structor 2-39 2.5.1.2 I/O Command Structor 1/0 Control Command Specifier 2.5.1.3 2-40 2.5.2 2-40 I/O Operands 2.5.3 2-42 Device Specification Table 2-42 2.5.4 Traffic Registers 2.5.5 Simultaneity Table 2-43 < 2.5.6 Input/Output Status Word 2-43

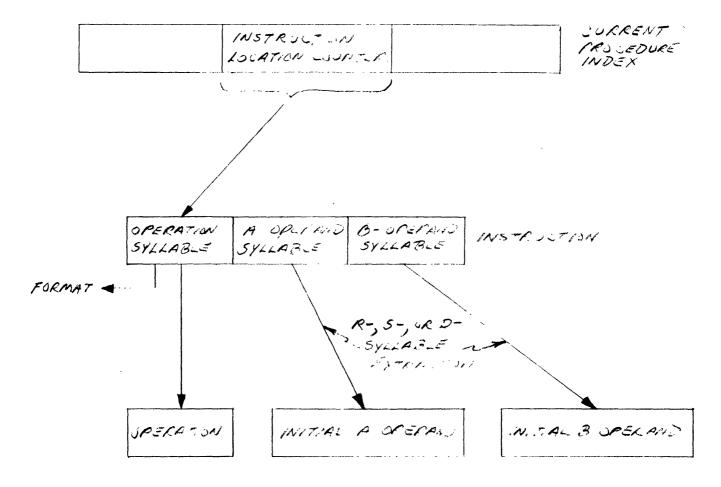

#### SECTION III - INSTRUCTION FORMATS AND INSTRUCTION EXTRACTION

| 3.1     | GENERAL                                                                         | 3-1        |

|---------|---------------------------------------------------------------------------------|------------|

| 3.2     | INSTRUCTION FORMATS                                                             | 3-3        |

| 3.2.1   | Register-Register (RR) Format                                                   | 3-3        |

| 3.2.2   | Register-Selector (RS and RL) and Selector-<br>Register (SR and LR) Formats     |            |

| 3.2.3   | Selector-Selector (SS, SL, LS, LL) Formats                                      | 3-4        |

| 3.2.4   | Relative Displacement (RD) Format                                               | it and the |

| 3.2.5   | Control Variant (CV) Format                                                     | 3-6        |

| 3.3     | INSTRUCTION EXTRACTION                                                          | 3-6        |

| 3.3.1   | Register-Register (RR) Format Extraction                                        | 3-6        |

| 3.3.2   | Register-Selector (RS, RL) and Selector-<br>Register (SR, LR) Format Extraction | 3-8        |

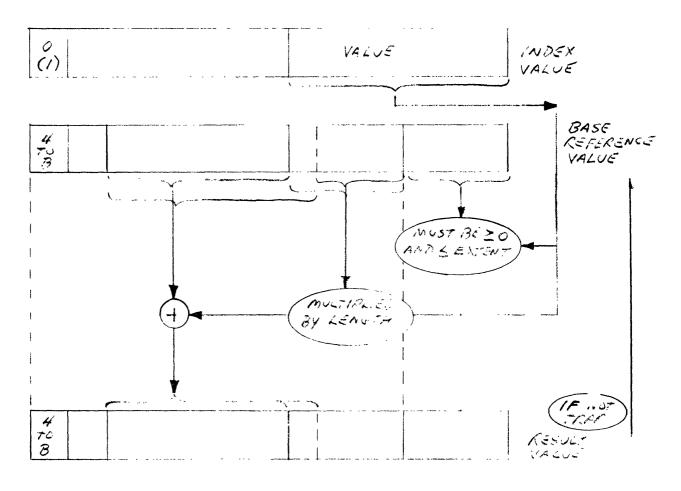

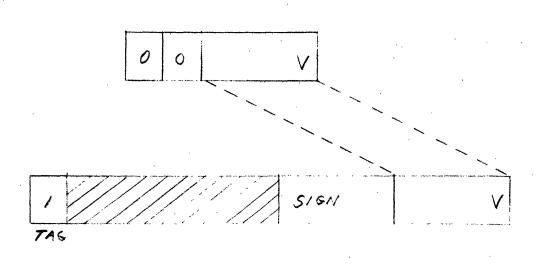

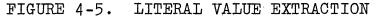

| 3.3.2.1 | Literal Value Case                                                              | 3-8        |

| 3.3.2.2 | Implicit-Length Base Reference Case                                             | 3-8        |

| 3.3.2.3 | Explicit-Length Base Reference Case                                             | 3-9        |

| 3.3.2.4 | Indexed Implicit-Length Base Reference Case                                     | 3-11       |

| 3.3.2.5 | Indexed Explicit-Length Base Reference Case                                     | 3-13       |

| 3.3.2.6 | Auto-indexed Implicit-Length Base<br>Reference Case                             | 3-16       |

| 3.3.2.7 | Auto-indexed Explicit-Length Base<br>Reference Case                             | 3-17       |

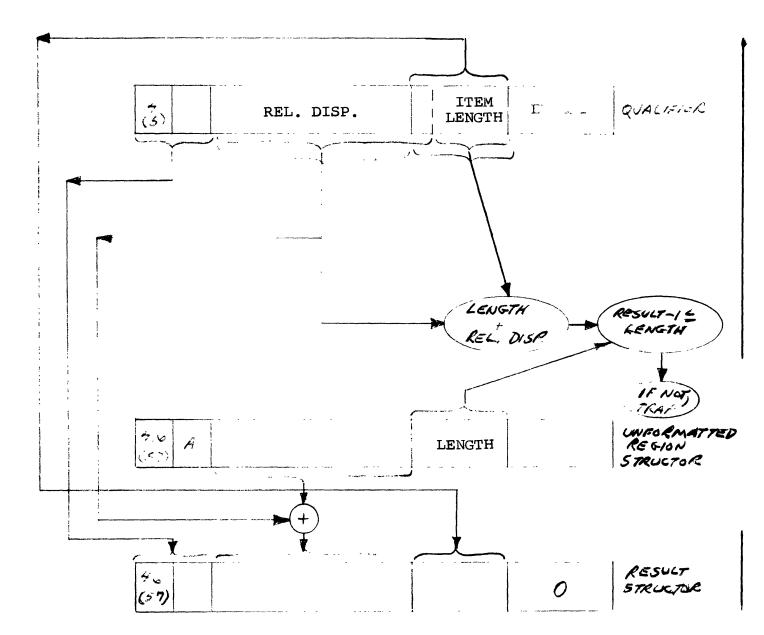

| 3.3.2.8 | Auto-Qualified Base Reference Case                                              | 3-21       |

| 3.3.2.9 | Multiple Selection Case                                                         | 3-23       |

· · · ·

TABLE OF CONTENTS (Cont.)

| Paragraph | Title                                                              | Page          |

|-----------|--------------------------------------------------------------------|---------------|

| 3.3.3     | Selector-Selector (SS, SL, LS, LL)<br>Format Extraction            | 3-30          |

| 3.3.4     | Relative Displacement (RD) Format Extraction                       | 3-30          |

| 3.3.5     | Control Variant (CV) Format Extraction                             | 3-35          |

|           |                                                                    |               |

|           | SECTION IV - AUTOFETCH/AUTOSTORE                                   |               |

| 4.1       | GENERAL                                                            | 4-1           |

| 4.2       | AUTOFETCH/AUTOSTORE CONVERSION                                     | 4-1           |

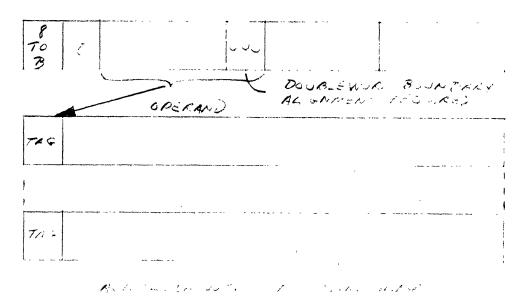

| 4.2.1     | Autofetch/Autostore Conversion For<br>Tagged Doublewords           | 4-2           |

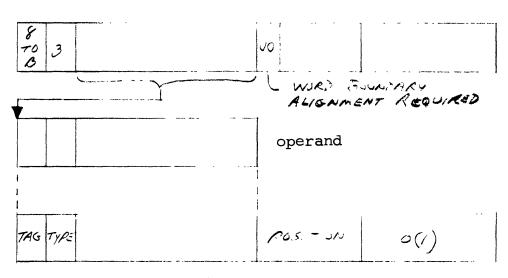

| 4.2.2     | Autofetch/Autostore Conversion For<br>Ministructors                | 4-2           |

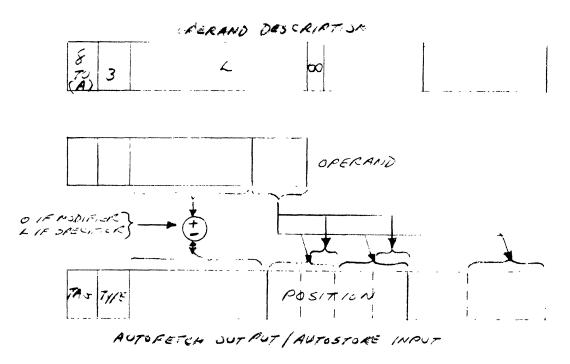

| 4.2.2.1   | Autofetch of Ministructor Operands                                 | 4-3           |

| 4.2.2.2   | Autostore Into Ministructor Operands                               | 4-5           |

| 4.2.3     | Autofetch Conversion For Microstructure                            | 49            |

| 4.2.3.1   | Autofetch of Microstructor Operands                                | 4-9           |

| 4.2.4     | Autofetch/Autostore Conversion for Deferred<br>Selection Structors | 4-11          |

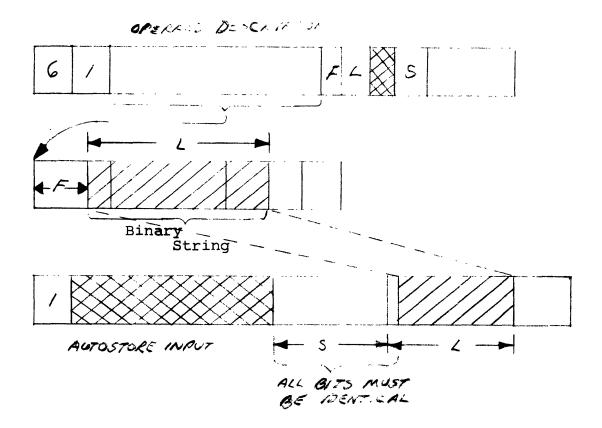

| 4.2.5     | Autofetch/Autostore Conversion for Bit Strings                     | 4-12          |

| 4.2.6     | Autofetch/Autostore Conversion for<br>Binary Strings               | 4-14          |

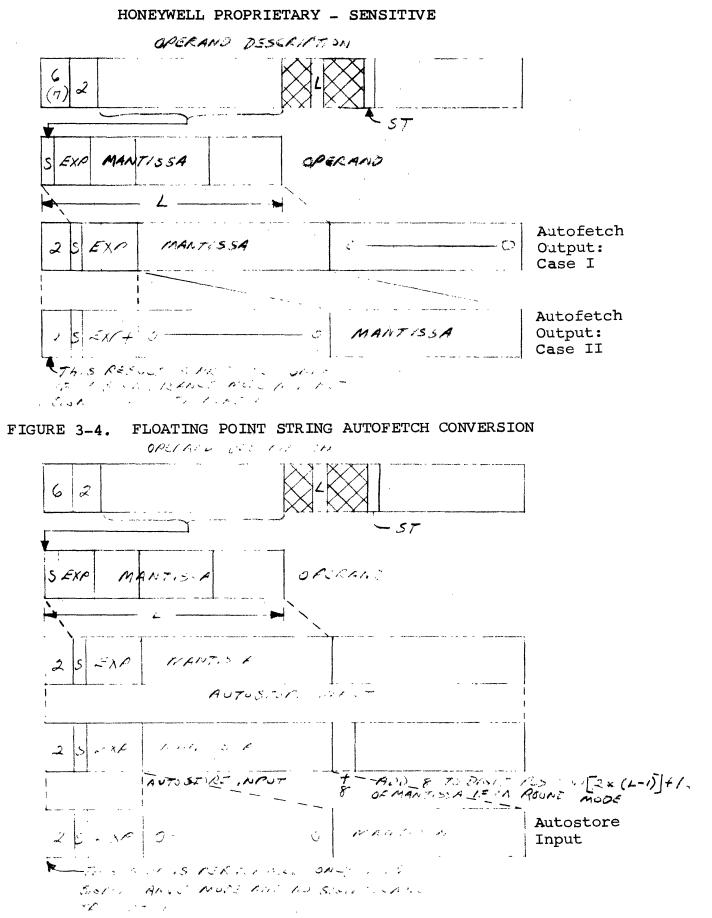

| 4.2.7     | Autofetch/Autostore Conversion for Floating<br>Point Strings       | 4-16          |

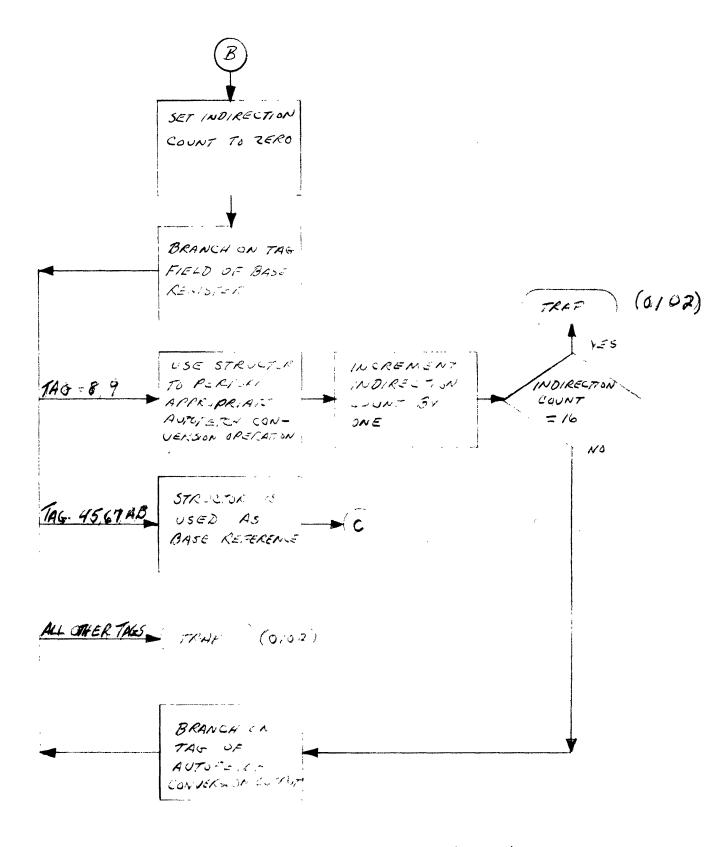

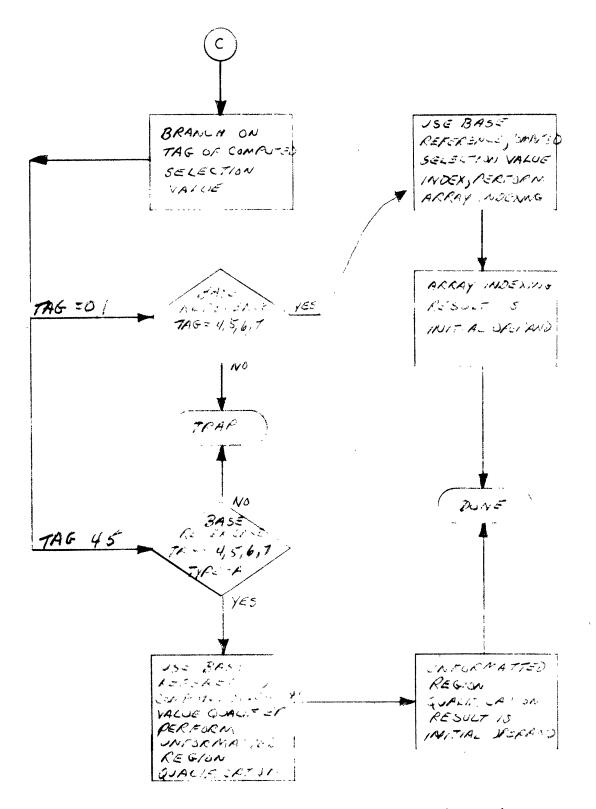

| 4.3       | AUTOFETCH EVALUATOR                                                | 4-18          |

| 4.4       | AUTOSTORE EVALUATOR                                                | 4-21          |

|           | SECTION V - AUTOCONVERSION                                         |               |

| 5.1       | INTRODUCTION                                                       | 51            |

| 5.2       | CONVERSION CONVENTIONS                                             | 5-2           |

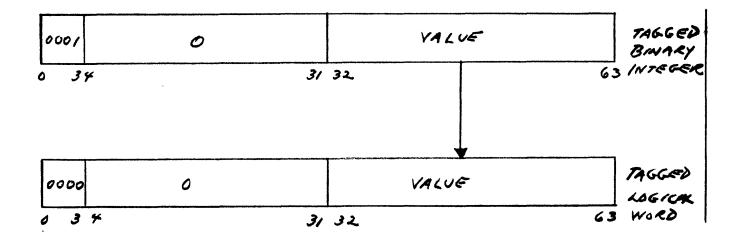

| 5.2.1     | Tagged Logical Word to Tagged Binary Integer                       | 5-2           |

| 5.2.2     | Tagged Binary Integer to Tagged Floating<br>Point Number           | 5 <b>-3</b> 1 |

| 5.2.3     | Tagged Floating Point to Decimal String                            | 5-4           |

5.2.4 Decimal String to Tagged Floating Point 5-6

¥

HONEYWELL PROPRIETARY - SENSITIVE

TABLE OF CONTENTS (Cont.)

,

| Paragraph | Title                                           | Page         |

|-----------|-------------------------------------------------|--------------|

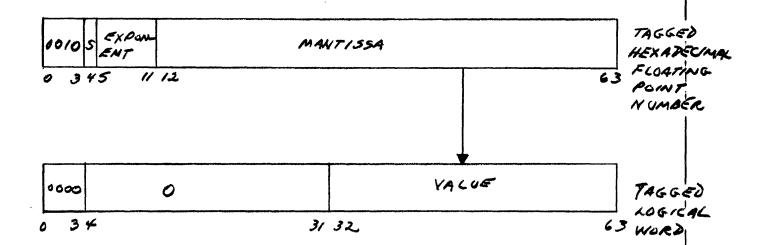

| 5.2.5     | Floating Point Number to Tagged Binary Integer  | 5-7          |

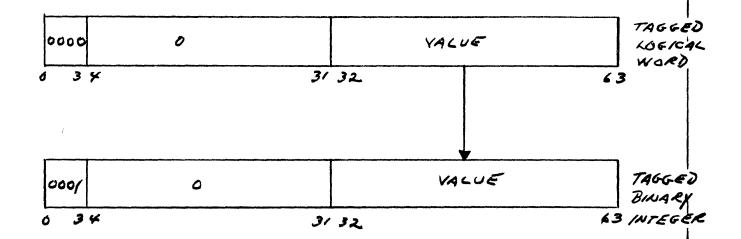

| 5.2.6     | Tagged Binary Integer to Tagged Logical Word    | 5-8          |

|           | SECTION VI - INSTRUCTIONS                       |              |

| 6.1       | DATA MANIPULATION ISTRUCTIONS                   | 6-1          |

| 6.1.1     | Add/Subtract                                    | 6-2          |

| 6.1.1.1   | Logical Binary Addition/Subtraction             | 6-3          |

| 6.1.1.2   | Twos Complement Binary Addition/Subtraction     | 6-4          |

| 6.1.1.3   | Herndecimal Floating Point Addition/Subtraction | 6-4          |

| 6.1.1.4   | Decimal String Addition/Subtraction             | 6-6          |

| 6.1.2     | Multiply                                        | 6-10         |

| 6.1.2.1   | Logical Binary Multiplication                   | 6-11         |

| 6.1.2.2   | Twos Complement Binary Multiplication           | 6-12         |

| 6.1.2.3   | Hexadecimal Floating Point Multiplication       | 6-13         |

| 6.1.2.4   | Decimal String Multiplication                   | 6-16         |

| 6.1.3     | Divide                                          | 6-18         |

| 6.1.3.1   | Logical Binary Division                         | 6 <b>-19</b> |

| 6.1.3.2   | Twos Complement Binary Division                 | 6-20         |

| 6.1.3.3   | Hexadecimal Floating Point Division             | 5-21         |

| 6.1.3.4   | Decimal String Division                         | 6-24         |

| 5.1.4     | Compare                                         | 6-27         |

| 6.1.4.1   | Logical Binary Comparision                      | 6-27         |

| 6.1.4.2   | Twos Complement Binary Comparison               | 6-28         |

| 5.1.4.3   | Hexadecimal Floating Point Comparison           | 6-28         |

| 6.1.4.4   | Decimal String Comparison                       | 6-28         |

| 6.1.4.5   | Byte String/Translated Byte String Comparison   | 6-29         |

| 6.1.5     | Move                                            | 6-31         |

| 6.1.5.1   | Byte String/Translated Byte String Move         | 6-31         |

| 6.1.5.2   | Decimal String to Decimal String Move           | 6-32         |

| 6.1.5.3   | Autostore Moves                                 | 6-33         |

| 6.1.6     | And/Or/Exclusive OR                             | 6-33         |

| 6.1.6.1   | Logical Word And/Or/Exclusive OR                | 6-33         |

. \*

HONEYWELL PROPRIETARY - SENSITIVE

TABLE OF CONTENTS (Cont.)

,÷

| Paragraph     | Title                                                    | Page                    |

|---------------|----------------------------------------------------------|-------------------------|

| 6.1.6.2       | Byte String/Translated Byte String AND, OR, EXCLUSIVE OR | 5-34                    |

| 6.1.7         | Shift                                                    | 6 <b>~35</b>            |

| 6.1.7.1       | Single Precision Logical Left Shift                      | 6-36                    |

| 6.1.7.2       | Single Precision Logical Right Shift                     | 6 <b>~36</b>            |

| 6.1.7.3       | Single Precision Arithmetic Left Shift                   | <del>6</del> <b>3</b> 7 |

| 6.1.7.4       | Single Precision Arithmetic Right Shift                  | 637                     |

| 6.1.7.5       | Double Precision Logical Left Shift                      | 638                     |

| 6.1.7.6       | Double Precision Legical Right Shift                     | 6- 38                   |

| 6.1.7.7       | Double Precision Arithmetic Left Shift                   | 6-39                    |

| 6.1.7.8       | Double Precision Arithmetic Right Shift                  | 6-39                    |

| 6.1.7.9       | Single Precision Rotational Shift                        | 640                     |

| 6.1.8         | Load Positive/Load Negative                              | 6-40                    |

| 6,1.8,1       | Twos Complement Binary Loading                           | 6-40                    |

| 6.1.8.2       | Hexadecimal Floating Point Loading                       | 6-41                    |

| 6.1.9         | Load Complement                                          | 6-41                    |

| 6.1.9.1       | Logical Binary Negation                                  | 6-42                    |

| 6.1.9.2       | Twos Complement Binary Negation                          | 6-42                    |

| 6.1.9.3       | Hexadecimal Floating Point Negation                      | 6-42                    |

| 6.1.10        | Load and Test                                            | 6-42                    |

| 6.1.10.1      | Logical Binary Testing                                   | 6-43                    |

| 6.1.10.2      | Twos Complement Binary Testing                           | 6-43                    |

| 6.1.11        | Edit                                                     | 6-43                    |

| 6.2           | GENERAL REGISTER LOADING/STORING INSTRUCTIONS            | 6-43                    |

| 6.2.1         | Сору                                                     | 6-44                    |

| 6.2.2         | Load                                                     | 6-44                    |

| 6.2.3         | Fetch                                                    | 6-44                    |

| 6.2.4         | Convert to Logical                                       | 6-45                    |

| 6.2.5         | Convert to Binary                                        | 6-45                    |

| 6.2.6         | Convert to Floating                                      | 6-46                    |

| 6.2.7         | Dump Multiple                                            | 6-46                    |

| 6.2.8         | Undump Multiple                                          | 6-48                    |

| 6.2 <b>.9</b> | Dump                                                     | 6-49                    |

## vli

HONEYWELL PROPRIETARY - SENSITIVE

.

## TABLE OF CONTENTS (Cont.)

| Paragraph | Title                                                      | Page              |

|-----------|------------------------------------------------------------|-------------------|

| 6.2.10    | Dump                                                       | 6-50              |

| 6.2,11    | Store                                                      | 6-50              |

| 6.2.12    | Deposit                                                    | 6-50              |

| 6.3       | BRANCHING INSTRUCTIONS                                     | 6-51              |

| 6.3.1     | Test and Branch                                            | 6-51              |

| 6.3.2     | Conditional Branch                                         | 652               |

| 6.3.3     | Branch and Link                                            | 653               |

| 6.3.4     | Branch On Incremented Count/Branch On<br>Decremented Count | 6 <sub>2</sub> 53 |

| 5.4       | STRUCTOR MANIPULATION INSTRUCTIONS                         | 6-54              |

| 6.4.1     | Solect                                                     | 6-34              |

| 6.4.2     | Lower Subarray                                             | 6-55              |

| 6.4.3     | Upper Subarray                                             | 6-55              |

| 6.4.4     | Point                                                      | 655               |

| 5.4.5     | Initial Substring                                          | 6-54              |

| 5.4.6     | Terminal Substring                                         | 6-57              |

| ÷. 5      | TASK CONTROL INSTRUCTIONS                                  | 6-58              |

| 6.5.1     | Stop                                                       | 6-59              |

| 6,5.2     | Start                                                      | 6-5)              |

| 6.3.3     | Suspend                                                    | 6-6)              |

|           | Conditional Stop                                           | 6-61              |

| 6.5.5     | I/O External Conditional Stop                              | 6-6.1             |

| 6.5.6     | Load Status                                                | 6-64              |

| 6.5.7     | Test and Set                                               | 6-65              |

| 6.5.8     | Set Mode - Reset Mode                                      | 666               |

| 6.5.9     | Field Extract                                              | 6-67              |

| 6.5.10    | Field Substitute                                           | 6-68              |

| 6.6       | INPUT/OUTPUT INSTRUCTIONS                                  | 6-70              |

| 6.6.1     | Initial Device Operation                                   | 6-70              |

| 6.6.2     | Halt Device Operation                                      | 6-70              |

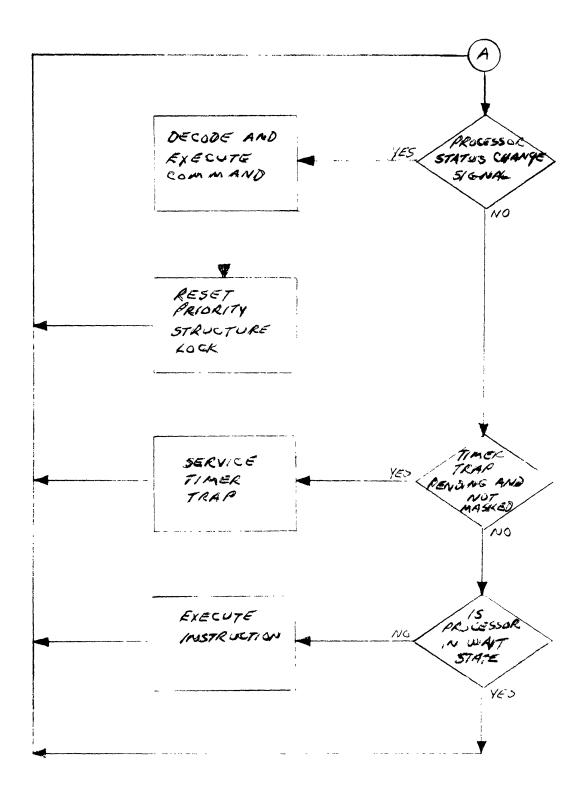

### SECTION VII - TASK MULTIPLEXING

1.1 INTRO

INTRODUCTION

7-1

HONEYWELL PROPRIETARY - SENSITIVE

1

. . . . .

TABLE OF CONTENTS (Cont.)

| Paragraph                | Title                               | Page |

|--------------------------|-------------------------------------|------|

| 7.2                      | LOCK AND UNLOCK FUNCTIONS           | 7-1  |

| 7.3                      | DISPATCH OPERATION                  | 7-2  |

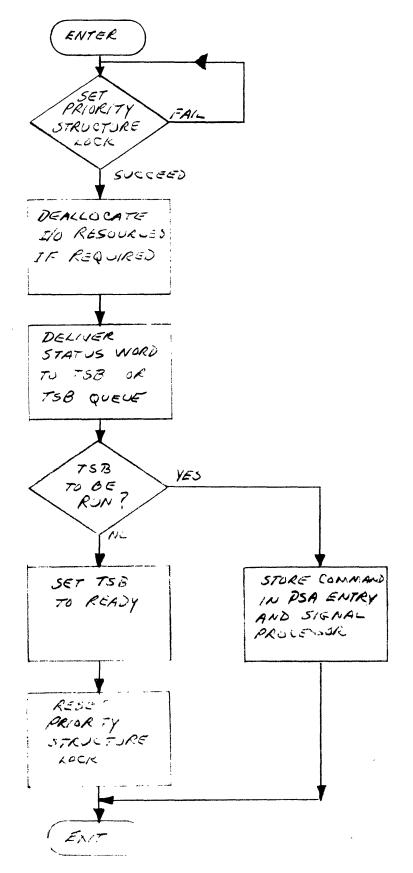

| 7.4                      | I/O INITIATED STARTS                | 7-4  |

| 7,5                      | EXTERNALLY INITIATED STARTS         | 7-5  |

|                          | SECTION VIII - TRAPPING             |      |

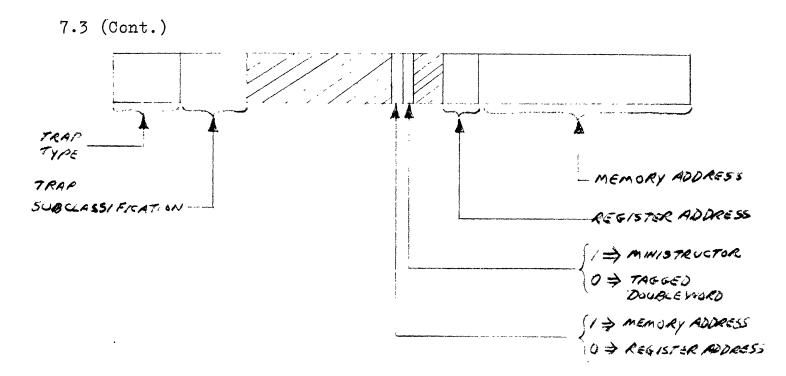

| 8.1                      | INTRODUCTION                        | 8-1  |

| 8.2                      | TRAPPING IFORMATION STRUCTURE       | 8-1  |

| 8.3                      | TRAP CAUSES                         | 8-1  |

| 8.4                      | TRAP MECHANIZATION                  | 8-4  |

|                          | SECTION IX - TIMING FACILITIES      |      |

| 9.1                      | SYSTEM CLOCK                        | 3-1  |

| 9.2                      | SYSTEM TIMER                        | 9-1  |

| مهم معار<br>محمد مع آر خ | TASK TIMER                          | · 🚡  |

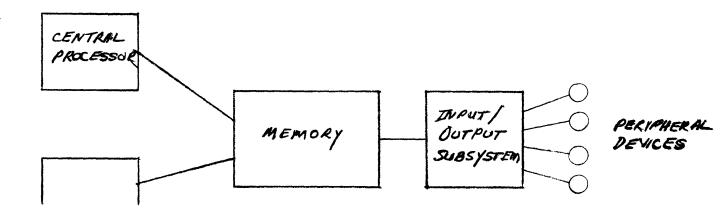

|                          | SECTION X - INPUT/OUTPUT FACILITIES |      |

| 10.1                     | INPUT/OUTPUT OPERATIONS             | 10-1 |

| 30.2                     | CENTRAL PROCESSOR I/O INSTRUCTIONS  | 10-3 |

| 3V - 2   | UEMIRAL PROCESSOR 1/0 INSTRUCTIONS                              | 10-3  |

|----------|-----------------------------------------------------------------|-------|

| 10.2.1   | Initiate Device Operation Instruction                           | 10-4  |

| <b>.</b> | Extraction of IDO Orders Specifying<br>Command Array            | 10-9  |

| 10.2.1.2 | Extraction of INO Orders Specifying<br>A Single Control Command | 10-14 |

| 10,2.1.3 | The L/C Status Information                                      | 10-15 |

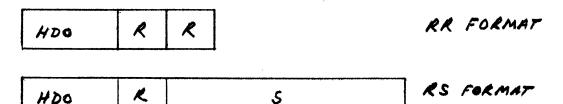

| 10.2.2   | Halt Device Operation (HDO) Instruction                         | 10-15 |

| 10.2.3   | Allowable Structor Formats for 1/0 Instruction                  | 10-17 |

| 10.3     | INPUT/OUTPUT INTERRUPTS                                         | 10-18 |

| 10.3.1   | The I/O Start Array                                             | 10-18 |

| 10.3.2   | The I/O Status Word                                             | 10-18 |

| 10.3.3   | Execution of I/O Interrupts                                     | 10-21 |

|          |                                                                 |       |

HONEYWELL PROPRIETARY - SENSITIVE

ix

## TABLE OF CONTENTS (Cont.)

1. m

. . .

## Paragraph

•

## Title

Page

.

## APPENDIX

| A-1 | DECIMAL | STR DIG | SIGN | CODES | A- 1 | 1 |

|-----|---------|---------|------|-------|------|---|

|-----|---------|---------|------|-------|------|---|

#### PROPRIETARY NOTICE

The information and design of the system described herein were originated by and are the property of Electronic Data Processing Division, Inc. The content of this document is <u>Honeywell Proprietary - Sensitive</u> and is for internal use only. Such information may not be reproduced, disclosed to others, or used by others for any purpose without written permission from an authorized Honeywell official.

#### SECTION II FORMAT REPRESENTATIONS AND DESCRIPTIONS

## 2.1 DATA REPRESENTATIONS AND DATA AND CONTROL DESCRIPTIONS

The following sections describe the data representation formats, as well as the formats for data and control structors. Structors are used to describe collections of data elements, control sequential and parallel instruction sequencing, and initiate input/output operations.

It should be noted that throughout the following sections any field designated RESERVED must contain binary zeros.

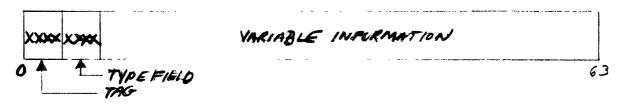

#### 2.2 TAGGED INFORMATION REPRESENTATIONS

Tagged information consists of self-descriptive data representations and structors. This information is selfdescriptive in the sense that its format includes a 4-bit field that specifies the interpretation appropriate to the remainder of the format. This 4-bit field is called a TAG field and is assigned the interpretations specified in Table 2-1.

All tagged information is 64-bits in length, with the leftmost 4 bits assigned to the TAG field. The format of the remaining 60 bits depends on the particular type of information being represented. These formats are specified in succeeding subsections.

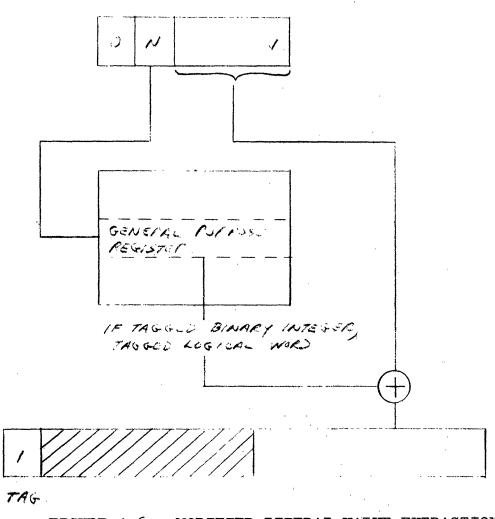

All information stored in general registers is tagged information. Tagged information may also be stored in main storage. In the latter case, each tagged information unit must originate at a storage address that is a multiple of 8 (doubleword boundary alignment). Arrays containing tagged items are called tagged doubleword arrays.

TABLE 2-1 TAG ASSIGNMENTS

| TAG | INTERPRETATION                                    |

|-----|---------------------------------------------------|

| 0   | Tagged Logical Word                               |

| 1   | Tagged Binary Integer                             |

| 2   | Tagged Hexadecimal Floating Point Number          |

| 3   | Unassigned*                                       |

| 4   | Explicit-Length, Modifier, Alterable Structor     |

| 5   | Explicit-Length, Modifier, Nonalterable Structor  |

| 6   | Explicit-Length, Specifier, Alterable Structor    |

| 7   | Explicit-Length, Specifier, Nonalterable Structor |

| 8   | Implicit-Length, Baselink, Structor               |

| 9   | Implicit-Length, Baselink, Structor               |

| А   | Implicit-Length, Data link, Alterable Structor    |

| В   | Implicit-Length, Data link, Nonalterable Structor |

| E   | Unassigned*                                       |

| F   | System Control Structor                           |

\*Unassigned TAG codes are reserved for future functional extensions.

#### 2.2.1 <u>Tagged Data Representations</u>

The tagged data representations consist of a TAG field and a fixed-length data field. The available tagged data representations are: tagged logical words, tagged binary integers, and tagged hexadecimal floating point numbers.

## 2.2.1.1 <u>Tagged Logical Word</u>

A tagged logical word is a 64-bit quantity, consisting of a TAG field (which is hexadecimal 0), a 28-bit reserved field, and a 32-bit value that is treated as a bit string of fixed-length (see Figure 2-1). This quantity must be aligned on a doubleword boundary in storage. It may also appear in a general purpose register.

|   |   | RESERVED | YALUE |   |

|---|---|----------|-------|---|

| 0 | 3 | 4 31     | 32 63 | ; |

#### FIGURE 2-1. TAGGED LOGICAL WORD

The value field of a tagged logical word may be interpreted as either a 32-bit logical quantity or as a 32-bit unsigned binary integer.

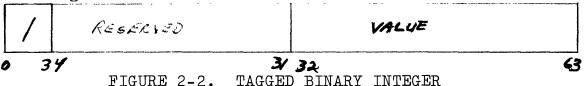

#### 2.2.1.2 Tagged Binary Integer

A tagged binary integer is a 64-bit quantity, consisting of a TAG field (which is hexadecimal 1), a 28-bit reserved field, and a 32-bit value that is treated as a binary twos complement integer of a fixed-length (see Figure 2-2). This quantity must be aligned on a doubleword boundary in storage. It may also appear in a general purpose register.

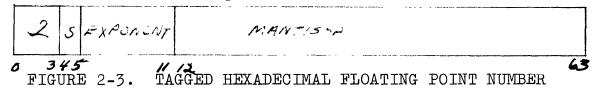

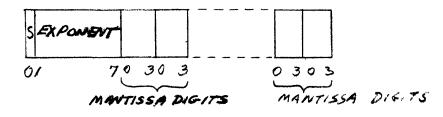

#### 2.2.1.3 Tagged Hexadecimal Floating Point Number

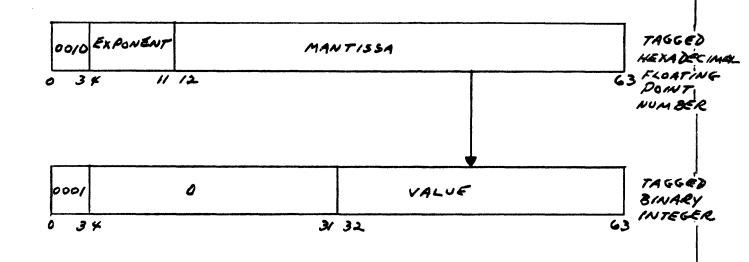

A tagged hexadecimal floating point number is a 64-bit quantity, consisting of a TAG field (which is 2), a sign bit, a seven-bit excess 64 exponent field, and a 13 digit hexadecimal mantissa (see Figure 2-3). A sign bit of 0 indicates that the mantissa is positive. This quantity must be aligned on a double word boundary in storage. It may also appear in a general purpose register.

#### HONEYWELL PROPRIETARY

## 2.2.2 Data Structors

Data Structors are entities used for structural description There are two basic forms of data structors, called implicit-length structors and explicit-length structors, that are used to describe arrays of fixed-length items and arrays of variable-length items, respectively. Data structors are tagged quantities and may be stored in general purpose registers or in storage. The number of storage accesses required to access an operand described by a data structor can be minimized by placing the structor in a general purpose register.

Explicit-length structors can assume one of two forms, called the modifier form and the specifier form. A modifier/specifier (M/S) indicator is included in the explicitlength structor TAG field to distinguish between these two forms. The M/S indicator is used to signal whether the structor specifies a particular data structure at a fixed main storage location or is used only to modify descriptions of areas of storage to conform to a desired data structure specification. Implicit-length structors can also assume one of two forms, called the baselink form and the data link form. The implicit-length structor TAG field distinguishes between these two forms and is used to specify whether the structor can be used as an indirection link for base reference creation or for effective operand formation, respectively.

Data structors specify several other important attributes of an information structure. In particular, the type of information described, the alterability of the information, and the number of items of information of the designated type are described by structors. Other attributes are given for certain types of information units. The attributes given in the data structor apply to all items in the array described by the structor. One type of array, called 2.2.2 tagged doubleword, allows any tagged quantity to be assigned

(Cont.)

to any item in the array, so that some of the attributes of this array item are associated with it, independent of the attributes of other array items.

The location field in data structors is 24 bits in length and identifies one of as many as 1,048,576 ( $2^{20}$ ) 8-bit bytes of storage. The addressing resolution required to locate a particular bit is achieved by use of an offset field contained in certain data structors. The location field, together with this offset field, always identifies the position of the leftmost (lowest numbered) bit of a particular array of items in storage.

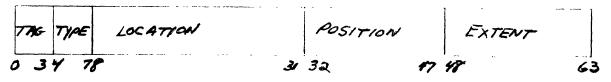

The general format for data structors is presented in Figure 2-4.

FIGURE 2-4. DATA STRUCTOR (GENERAL FORMAT)

The descriptions of the individual fields of data structors are specified as follows:

- a. TAG field -- this 4 bit field distinguishes between the implicit -- and explicit modifier and specifier or baselink and data link forms, and alterable and nonalterable cases of data structors. (See Table 2-1). These cases are specified as follows:

- i. Implicit-length/Explicit-length-Implicit-Length items always have a fixed bit length, which is determined by their TYPE field. Explicit-length items have a specified bit length, which is derived from the POSITION field of their describing data structor.

- 2.2.2 ii. Modifier/Specifier and Baselink/Data link -- For (Cont.) explicit-length modifier structors, the LOCATION field is interpreted as a relative byte displacement from an implied base location. For explicitlength specifier structors, the LOCATION field is interpreted as an absolute storage location at which the associated data structure originates. An implicit-length baselink or data link structor LOCATION field is always interpreted as the absolute storage location of a tagged doubleword or ministructor array origin. The modifier/specifier and baselink/datalink indicator is the third bit of the TAG field of a data structor.

- iii. Alterable/Nonalterable -- An alterable structor specifies that items in its associated array are alterable when the structor is used to access them, while a nonalterable structor prevents alteration of items in its associated array. Alterability indicator is the fourth bit of the TAG field of a data structor.

- b. TYPE Field -- This 4-bit field is used to identify the type of implicit -- or explicit -- length array items described by the structor. For implicit-length structors, the length of each item is specified by this field. The interpretation of the POSITION Field, which contains the item length, is specified by the TYPE Field for explicit-length structors. The available TYPE codes are presented in Table 2-2 and Table 2-3.

- c. LOCATION Field -- This 24-bit field specifies the byte location (0 - 1,048,575 with values greater than 1,048,575 illegal) in which the first array item has its origin. For explicit-length modifier structors, this field specifies the number of bytes of relative displacement from an implied base reference location as the location of the array described by the structor.

For explicit-length specifier structors and for implicit-length structors, this field specifies the absolute storage address of the byte in which the array associated with the structor originates. For bit and binary strings, the bit offset subfield of the POSITION field of the structor is also required to establish the array origin.

- d. POSITION Field -- The interpretation of this 16-bit field depends on the TAG and TYPE field codes. The specific interpretations are considered in subsection 2.2.2.1 below.

- e. EXTENT Field -- This 16-bit field specifies the number of items of the designated TYPE in the array described by the data structor. Extents 1 to 65,536 are associated with values of all zero bits to all one bits in this field.

Data structors must be aligned on doubleword boundaries. The entire array of items described by the data structor must be placed in contiguous storage locations. Every item in the array is a data representation with the same attributes, except for storage location.

The modifier form of explicit-length structor cannot be used to access an operand in storage, since it does not describe any particular collection of items in storage. The use of data structors to fetch or store operands is discussed in Subsections 3.2 and 3.3 Autofetch/Autostore.

## 2.2.2.1 POSITION Field of Data Structors

The interpretation of the POSITION field of data structors depends on the values of the TAG and TYPE fields of the structor. For explicit-length structors, the interpretations are specified in the subsections defining the explicitlength items. For implicit-length structors, the following

| TYPE<br>CODE | ITEM<br>DESCRIPTION               | UNIT SIZE<br>(BITS) |

|--------------|-----------------------------------|---------------------|

| 0            | Bit String                        | l                   |

| 1            | Binary String                     | l                   |

| 2            | Hexadecimal Floating Point String | 8                   |

| 3            | Unassigned*                       | -                   |

| 4            | Zoned Decimal String              | 8                   |

| 5            | Unsigned Zoned Decimal String     | 8                   |

| 6            | Packed Decimal String             | 8                   |

| 7            | Unsigned Packed Decimal String    | 8                   |

| 8            | Byte String                       | 8                   |

| 9            | Translated Byte String            | 8                   |

| A            | Unformatted Region                | 8                   |

| В            | Edit Control String               | 8                   |

| C-D          | Unassigned*                       | 8                   |

| E-F          | Software Assignable*              |                     |

TABLE 2-2TYPE CODES FOR EXPLICIT-LENGTH STRUCTORS

\*An attempt to use an explicit-length structor with this TYPE code will normally result in a trap.

| TYPE CODES FOR IMPLICIT-LENGTH STRUCTORS |                                |                     |  |  |

|------------------------------------------|--------------------------------|---------------------|--|--|

| TYPE                                     | ITEM<br>DESCRIPTION            | ITEM SIZE<br>(BITS) |  |  |

| 0                                        | Tagged Doubleword              | 64                  |  |  |

| 1                                        | Tagged Doubleword, LIFO Access | 64                  |  |  |

| 2                                        | Tagged Doubleword, FIFO Access | 64                  |  |  |

| 3                                        | Ministructor                   | 32                  |  |  |

| 4-D                                      | Unassigned*                    | n.a.                |  |  |

| E-F                                      | Software Assignable            | n.a.                |  |  |

TABLE 2-3 TYPE CODES FOR IMPLICIT-LENGTH STRUCTORS

\*An attempt to use an implicit-length structor with this TYPE code will normally result in a trap.

interpretations are specified:

- a. Tagged Doubleword -- the POSITION Field is RESERVED.

- b. Tagged Doubleword, LIFO Access -- the POSITION field is interpreted as an unsigned binary integer in the range 0 to 65,535. This integer, multiplied by 8 and added to the value of the LOCATION field of the structor, selects a particular tagged doubleword in the array of tagge doublewords described by the structor. The POSITION field value must be not greater than the EXTENT field value. When an item in a tagged doubleword, LIFO access array is retrieved or updated, the value of the POSITION field in the associated data structor may be decremented or incremented, respectively.

- Tagged Doubleword, FIFO Access -- The POSITION field с. is interpreted as a pair of 8-bit unsigned binary integers in the range 0 to 255. These integers multiplied by 8 and added to the value of the LOCATION field of the structor, select a pair of tagged doublewords in the array of tagged doublewords described by the structor. Each of these integers must be not greater than the EXTENT field value. When an item in a tagged doubleword, FIFO array is retrieved, the leftmost 8-bits of the POSITION field, called the FIFO tail, may be used to select an item and may be incremented. When an item in a tagged doubleword, FIFO array is updated, the rightmost 8-bits of the POSITION field, called the FIFO head, may be used to select an item and may be incremented.

- d. Ministructor -- the POSITION field is RESERVED.

#### 2.2.3 System Control Structors

System control structors are tagged information items used for system control operations. These structors are specified in Sections 2.5 (Control Information Representation) and Section 2.6 (I/O Information Representation).

## 2.3 <u>COMPACT INFORMATION REPRESENTATIONS</u>

The compact information representations are used to minimize the amount of storage required to store arrays of information containing items with certain homogeneous attributes. Each compact representation is equivalent to one of the tagged representations specified in Section 2.2.

## 2.3.1 <u>Compact Data Representations</u>

There are three compact data representations: bit strings, binary strings, and hexadecimal floating point strings. These data representations possess values over the same range as tagged logical words, tagged binary integers, and tagged hexadecimal floating point numbers, respectively.

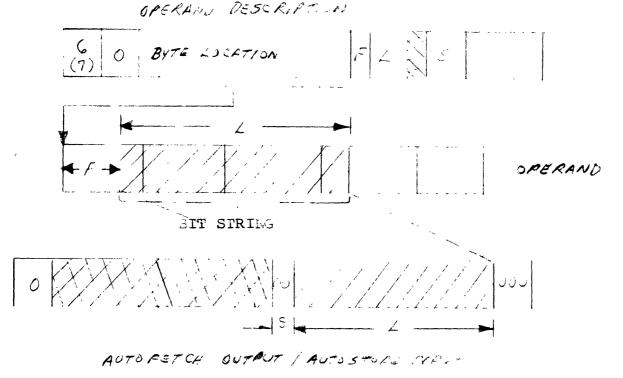

## 2.3.1.1 <u>Bit Strings</u>

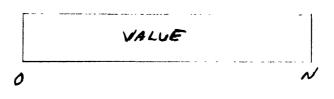

A bit string consists of a sequence of bits of specified length treated as a variable precision logical word or unsigned binary integer (see Figure 2-5). The maximun length for bit strings is 32 bits. The leftmost bit of a bit string may be any bit position in any byte of storage. Alignment and string length for bit strings affect their access time.

FIGURE 2-5. BIT STRING

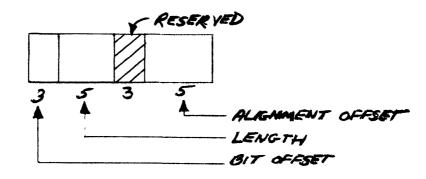

Bit strings are described by explicit-length structors The interpretation of the POSITION field of bit string structors is as follows. (See Figure 2-6).

FIGURE 2-6. POSITION FIELD FOR BIT AND BINARY STRINGS

The bit offset field specifies the bit position within the byte addressed by the LOCATION field of the structor that is associated with the leftmost bit of an array of bit strings. The bit offset has a range 0 to 7. The length field specifies the number of bits in each bit string item in the array. The length has a range 1 to 32, 1 to 31 associated with binary values 00001 to 11111, and 00000 associated with a length of 32 bits. The alignment offset field specifies the offset of the bit string in a tagged logical word and is used in Autofetch/Autostore conversion for bit strings. This field has a range of 0 to 31, associated with binary values 00000 to 11111.

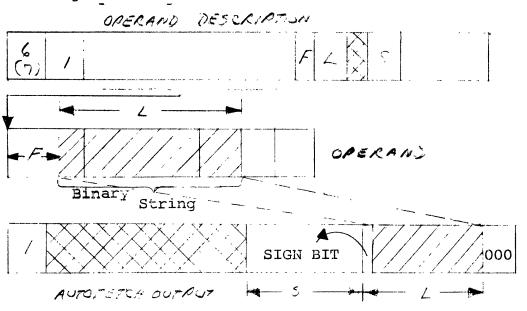

### 2.3.1.2 Binary Strings

A binary string consists of a sequence of bits of specified length treated a a variable precision twos complement binary integer (see Figure 2-7). The maximum length for binary strings is 32 bits. The leftmost bit of a binary string may be any bit position of any byte of storage. Alignment and string length for binary strings may affect their access time.

FIGURE 2-7. BINARY STRING

HONEYWELL PROPRIETARY - SENSITIVE

Binary strings are described by explicit-length structors. The interpretation of the POSITION field of binary string structors is identical to the interpretation for bit strings (see subsection 2.3.1.1) except the binary string alignment offset specifies the offset of the binary string within a tagged binary integer value.

## 2.3.1.3 <u>Hexadecimal Floating Point Strings</u>

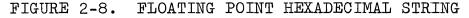

A hexadecimal floating point string consists of an 8-bit sign exponent byte followed by a sequence of from 0 to 7 contiguous bytes, which form a 0 to 14 hexadecimal digit mantissa. (See Figure 2-8.) The leftmost bit of the string is the sign of the manissa, encoded as 0 plus and 1 minus. The next seven bits contain the exponent. The exponent is encoded as an excess 64 number with a range of -64 through +63 and is interpreted as a power of sixteen. The remainder of the string consists of the hexadecimal digits used to encode the mantissa.

The minimum length of a hexadecimal floating point string (including the sign/exponent byte) is one byte, which corresponds to a zero digit mantissa. The maximum length is 8 bytes, which corresponds to a 14 digit mantissa.

A hexadecimal floating point string must be aligned on a byte boundary in storage. Boundary alignment and string length for hexadecimal floating point strings may affect their access time.

Hexadecimal floating point strings are described by explicit-length structors. The interpretation of the

HONEYWELL PROPRIETARY - SENSITIVE

POSITION field of hexadecimal floating point string structor is as follows. (See Figure 2-9.)

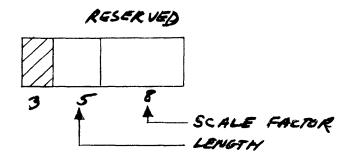

FIGURE 2-9. POSITION FIELD FOR HEXADECIMAL FLOATING POINT STRINGS

The length field specifies the number of bytes in each hexadecimal floating point string in the array described by the structor. The length has a range of 1 to 7 and 8, encoded as 001 to 111 and 000. The significance truncation field specifies the effective mantissa precision when the hexadecimal floating point string is manipulated in significance arithmetic mode. If this field is 1, significance truncation applies; otherwise, it does not.

#### 2.3.2 <u>Ministructors</u>

A reduction in the number of bits required to describe a particular information strucure is possible if the attributs of the structure are limited. The most important limitations are on the location and extent of arrays and on string length. Location information is reduced by requiring the data structure to be located a fixed relative displacement from the location of the descriptive quantity.

Arrays of less than a given extent and strings of less than a given length will require fewer bits in their associated descriptive quantities. The descriptive quantities assuming these abbreviated forms of description are called ministructors. Ministructors are normally stored in arrays and are converted into equivalent forms of data structors when used. Ministructors must be word boundary aligned and may reside only in main storage. The four distinct forms of ministructors are described below. In each case, the equivalent form of data structor is specified. This equivalent form is the form into which the ministructor is converted when, for example, it is placed in a general register.

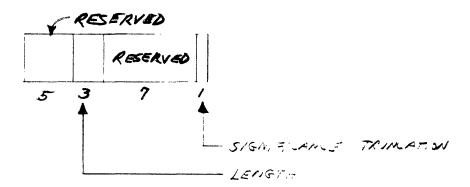

### 2.3.2.1 Singular Ministructor

The singular ministructor is a 32-bit quantity consisting of a two-bit classifier (which is 00), a one-bit modifier/ specifier or baselink/datalink indicator a one-bit alterability or reproducability indicator, a four-bit type code field, and a 24-bit location field. (See Figure 2-10.)

A singular ministructor is equivalent to a data structor with the following attributes:

- a. Modifier/specifier or baselink/datalink indicator and alterability indicator identical to the ministructor indicators.

- b. LOCATION field identical to the ministructor location field.

- c. EXTENT field set to zero (single item).

- d. the TAG, TYPE, and POSTION fields of the data structor are determined by the typecode field of the ministructor, according to Table 2-4.

This form of ministructor is convenient for printing of a single fixed-length item.

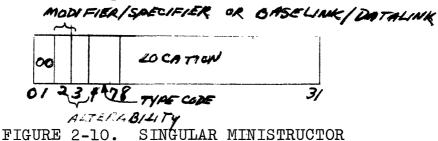

#### 2.3.2.2 <u>Dual Ministructor</u>

The dual ministructor is a 32-bit quantity consisting of a two-bit classifier (which is Ol), a one-bit modifier/ specifier or baselink/datalink indicator, a one-bit alterability indicator, a four-bit typecode field, and a 24bit location field. (See Figure 2-11.)

FIGURE 2-11. DUAL MINISTRUCTOR

A dual ministructor is equivalent to a data structor with the following attributes:

- a. Modifier/specifier or baselink/datalink indicator and alterability indicator identical to the ministructor indicators.

- b. LOCATION field identical to the ministructor location field.

- c. EXTENT field set to one (two items).

- d. the TAG, TYPE, and POSITION fields of the data structor are determined by the typecode field of the ministructors, according to Table 2-4.

This form of ministructor is useful in constructing binary tree structures, including chained lists and ring structures.

TABLE 2-4 MINISTRUCTOR EQUIVALENT STRUCTOR ATTRIBUTES

| TYPE<br>CODE | TAG*       | TYPE                | POSITION**     |

|--------------|------------|---------------------|----------------|

| 0            | Implicit   | Tagged doubleword   | naa.           |

| 1            | Implicit   | Ministructor        | n.a.           |

| 2-7          | Unassigned | n.a.                | n.a.           |

| 8            | Explicit   | Bit String (0) B    | =0, L=8, A=0   |

| 9            | Explicit   | Bit String (0) B    | =0, L=16, A=0  |

| A            | Explicit   | Bit String (0) B    | =0, L=32, A=0  |

| B            | Explicit   | Binary String (1) B | =0, L=8, A=24  |

| C            | Explicit   | Binary String (1) B | =0, L=16, A=16 |

| D            | Explicit   | Binary String (1) B | =0, L=32, A=0  |

| E            | Explicit   | Hex.f.p. String (2) | L=4, S=0       |

| F            | Explicit   | Hex.f.p. String (2) | L=8, S=0       |

\*The TAG field is also generated to include modifier/specifier or baselink/datalink and alterability on indicators.

\*\*The following abbreviations are used: B-bit offset, L-length, A-alignment offset, S-significance truncation.

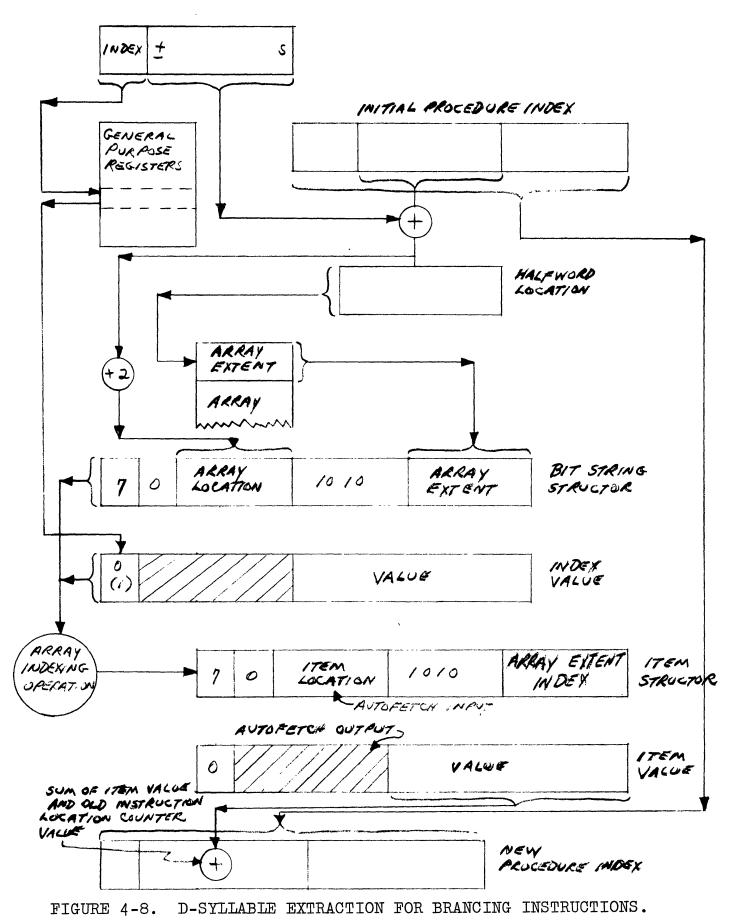

#### 2.3.2.3 Array Ministructor

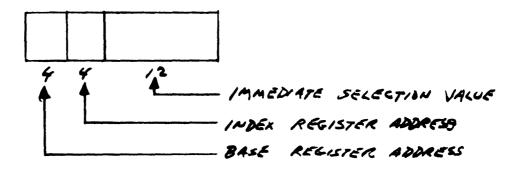

The array ministructor is a 32 bit quantity consisting of a two-bit classifier (which is 10), a one-bit modifier/ specifier or baselink/datalink indicator, a one-bit alterability indicator, a four-bit type field, a sixteen-bit relative displacement field, and a eight-bit extent field. (See Figure 2-12.)

MODIFIER/SPECIFIER OR BASELINK/DATALINK 10 3/ ALTERABILITY

FIGURE 2-12. ARRAY MINISTRUCTOR

2-16 HONEYWELL PROPRIETARY - SENSITIVE

An array ministructor is equivalent to a data structor with the following attributes:

- a. Modifier/specifier indicator or baselink/datalink and alterability indicator identical to the ministructor indicators.

- b. LOCATION field equals the value of the relative displacement field of the ministructor in bytes, if the ministructor is an explicit-length modifier or implicit-length baselink or the sum of the storage address of the ministructor plus the relative displacement field of the ministructor, when the ministructor is an explicit-length specifier or implicitlength datalink type.

- c. EXTENT field set to the value of the extent field of the array ministructor.

- d. The TAG, TYPE, and POSITION fields of the data structor are determined by the typecode field of the ministructor, according to Table 2-4.

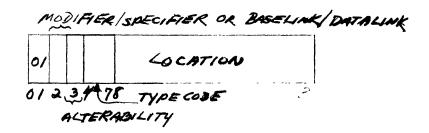

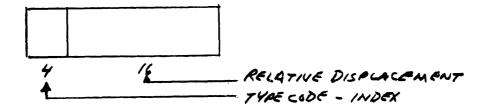

- 2.342.4 <u>String Ministructor</u>

The string ministructor is a 32-bit quantity consisting of a two bit classifier (which is 11), a one-bit modifier/ specifier indicator, a one-bit alterability indicator, a four-bit type code field, a sixteen bit relative displacement field, and an eight-bit position field. (See Figure 2-13).

MUDIFIER SPECIFIER OR BASELINK, DATALIAK 14 TYPE CODE 23 :

#### FIGURE 2-13. STRING MINISTRUCTOR

#### 2-17

HONEYWELL PROPRIETARY - SENSITIVE

2.3.2.4 A string ministructor is equivalent to an explicit-length (Cont.) structor with the following attributes:

- a. Modifier/specifier indicator and alterability indicator identical to the ministructor indicators.

- b. LOCATION field equals the value of the relative displacement field of the ministructor in bytes, if the ministructor is a modifier, or the sum of the storage address of the ministructor plus the relative displacement field of the ministructor, when the ministructor is a specifier.

- c. EXTENT field set to zero (single item).

- d. TYPE field set to the value of the typecode field of the ministructor.

- e. POSITION field determined by the position field of the string ministructor, as a function of the typecode field of the ministructor. The manner in which this is accomplished is discussed below.

The POSITION field of the equivalent structor is determined as a function of the typecode of the string ministructor. Table 2-5 presents the alternatives.

11-26-69

|          |       | $	extsf{TABLE}$ | 2-5 |        |               |

|----------|-------|-----------------|-----|--------|---------------|

| POSITION | FIELD | EQUIVALENTS     | FOR | STRING | MINISTRUCTORS |

| TYPECODE OF<br>MINISTRUCTOR | EQUIVALENT<br>TYPE                | POSITION<br>FIELD<br>EQUIVALENT* |

|-----------------------------|-----------------------------------|----------------------------------|

| 0                           | Bit String                        | A                                |

| 1                           | Binary String                     | А                                |

| 2                           | Hexadecimal Floating Point String | В                                |

| 3                           | Unassigned                        | n.a.                             |

| 4                           | Zoned Decimal String              | В                                |

| 5.                          | Unsigned Zoned Decimal String     | В                                |

| 6                           | Packed Decimal String             | В                                |

| 7                           | Unsigned Packed Decimal String    | В                                |

| 8                           | Byte String                       | C                                |

| 9                           | Translated Byte String            | C                                |

| A                           | Unformatted Region                | C                                |

| В                           | Edit Control String               | n.a.                             |

| C-F                         | Unassigned                        | n.a.                             |

\*The alternatives for position field equivalents are as follows:

- A- The POSITION field contains the position field of the ministructor as its leftmost eight bits. The rightmost eight bits of the POSITION field are set to zero. This allows bit and binary strings with offsets 0-7, lengths 1-32, and 0 alignment offset string ministructors.

- B- The POSITION field consists of 4 zero bits, followed by the leftmost 4 bits of the position field of the ministructor, followed by 4 zero bits, followed by the rightmost 4 bits of the ministructor position field. This allows zoned decimal strings with byte lengths 1-15 and 32 and zoned decimal strings with byte lengths 1-16, and both with scale factors 0-15, and hexadecimal floating point strings with byte lengths 1-8 with or without significance truncation to be described by string ministructors.

- C- The POSITION field consists of 8 zero bits, followed by the 8 bits of the position field of the ministructor. This allows byte strings, translated byte strings, and unformatted regions with lengths 0-255 to be described by string ministructors.

#### 2.4 BYTE SEQUENCE INFORMATION REPRESENTATIONS

The byte sequence information representations consist of a sequence of essentially identical units, each of which occupied a byte of storage. Information in the byte sequence is normally processed as an entity; that is, the entire sequence is considered to be a single operand value of variable length.

#### 2.4.1 String Data Representations

The string data representations are used to encode data that is of highly variable length such that it is impossible to place this information in general registers.

#### 2.4.1.1 <u>Byte String</u>

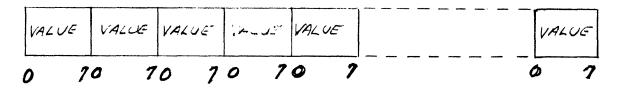

A byte string is a sequence of contiguous eight-bit bytes that are normally interpreted as logical values (see Figure 2-14). The maximum length for byte strings is 65,535 bytes. A byte string may originate at any byte boundary in storage. A byte string may have zero length.

FIGURE 2-14. BYTE STRING

Byte strings are described by explicit-length structors. The interpretation of the POSITION field of byte string structors is as follows. (See Figure 2-15).

FIGURE 2-15. POSITION FIELD FOR BYTE AND TRANSLATED BYTE STRINGS

1-16-70

The length field specifies the number of bytes in each byte string in the array of byte strings described by the data structor. This field has a range 0 to 65,535 and is interpreted as an unsigned binary integer.

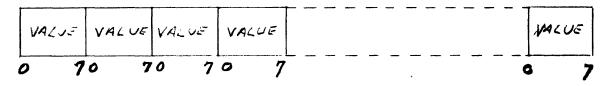

### 2.4.1.2 <u>Translated Byte String</u>

A translated byte string is a sequence of contiguous eight-bit bytes that are translated using as implicit translation table and are normally treated as logical values. (See Figure 2-16). The maximum length for translated byte strings is 65,535 bytes. A translated byte string may originate at any byte boundary in storage. The translation tables used to map from and to a translated byte string are called the load and store translation tables, respectively, and are located by means of the Task Code Map Description in the Task Status Block (see Section 2.5).

FIGURE 2-16. TRANSLATED BYTE STRING

Translated byte strings are described by explicit-length structors. The interpretation of the POSITION field of translated byte string structors is as follows. (See Figure 2-15). The length field specifies the number of bytes in each translated byte string in the array of translated byte strings described by the data structor. This field has a range 0 to 65,535 and is interpreted as an unsigned integer.

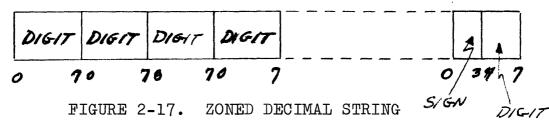

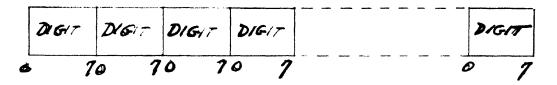

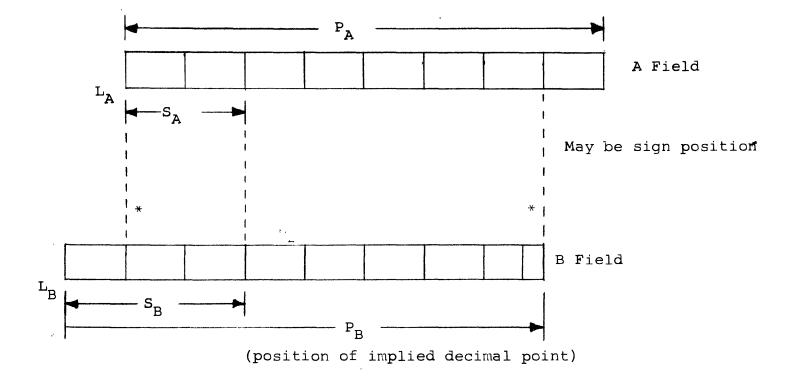

## 2.4.1.3 Zoned Decimal String

A zoned decimal string is a sequence of contiguous eightbit bytes, each containing an encoding of a decimal digit, the rightmost byte of which contains a signed digit (see Figure 2-17). The sign is stored as a zone field in the rightmost byte. The zone bits in the remaining digit positions are not interpreted by instructions manipulating zoned decimal strings, but are preserved by execution of these instructions. The numeric bits in each digit position are interpreted as follows: 0000 to 1001 correspond to decimal digits 0 to 9 and 1010 to 1111 are interpreted as illegal and generate a trap when encountered. The interpretation of the sign field is specified in Appendix A. Each zoned decimal string has an associated scale factor, which is used to specify the position of an implied decimal point for the string. The maximum length for zoned decimal strings is 32 digits, and the maximum scale factor is 128 digit positions to the left, and 127 digit positions to the right of the leftmost digit of the zoned decimal string. A scale factor of 0 places the implied decimal point to the left of the leftmost digit of the string. See Appendix A for sign encoding details. A zoned decimal string may originate at any byte boundary in storage.

Zoned decimal strings are described by explicit-length structors. The interpretation of the POSITION field of zoned decimal string structors is as follows. (See Figure 2-18).

HONEYWELL PROPRIETARY - SENSITIVE

FIGURE 2-18. POSITION FIELD FOR ZONED AND UNSIGNED ZONED DECIMAL STRING STRUCTORS.

The length field **s**pecifies the number of bytes in each zoned decimal string in the array of zoned decimal strings described by the structor. This field has a range 1 to 31 and 32, which is encoded as 00001 to 11111 and 00000. The scale factor field specifies the position of an implied decimal point for the zoned decimal string. This field has a range -128 to +127 and is encoded as a twos complement binary integer.

### 2.4.1.4 Unsigned Zoned Decimal String

An unsigned zoned decimal string consists of a sequence of contiguous eight-bit bytes, each containing an encoding of a decimal digit. (See Figure 2-19).

FIGURE 2-19. UNSIGNED ZONED DECIMAL STRING

The interpretation of unsigned zoned decimal strings is identical to the interpretation of zoned decimal strings, except that the zone of the rightmost byte of the string is not interpreted as a sign, but is preserved. A positive value is always implied for unsigned zoned decimal strings.

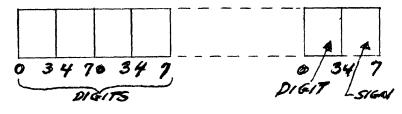

#### 2.4.1.5 Packed Decimal String

A packed decimal string is a sequence of contiguous eightbit bytes, each containing an encoding of a pair of decimal digits, except the rightmost byte, which contains an encoding of a decimal digit and of a sign. (See Figure 2-20). The sign code is the rightmost 4-bit field of the rightmost byte of the packed decimal string. The encoding of the sign code is specified in Appendix A. Each digit field in the string is interpreted as follows: 0000 to 1001 correspond to decimal digits 0 to 9, 1010 to llll are interpreted as illegal digits and generate traps when encountered. Each packed decimal string has an associated scale factor, which is used to specify the position of an implied decimal point for the string. The maximum precision for packed decimal strings is 31 decimal digits, and the maximum scale factor is 128 digit positions to the left or 127 digit positions to the leftmost digit of the packed decimal string. A packed decimal string may originate at any byte boundary in storage.

FIGURE 2-20. PACKED DECIMAL STRING.

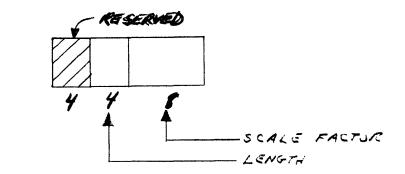

Packed decimal strings are described by explicit-length structors. The interpretation of the POSITION field of packed decimal strings is as follows. (See Figure 2-21).

FIGURE 2-21. POSITION FIELD FOR PACKED AND UNSIGNED PACKED DECIMAL STRING STRUCTORS

The length field specifies the number of bytes in each packed decimal string in the array of packed decimal strings described by the structor. This field has a range 1 to 15 and 16, which is encoded as 0001 to 1111 and 0000. The scale factor field specifies the digit position of an implied decimal point for the packed decimal string. This field has a range -128 to +127 and is encoded as a two's complementary binary integer.

# 2.4.1.6 <u>Unsigned Packed Decimal String</u>

An unsigned decimal string consists of a sequence of contiguous eight-bit bytes, each containing an encoding of a pair of decimal digits. (See Figure 2-22).

FIGURE 2-22. UNSIGNED PACKED DECIMAL STRING

The interpretation of unsigned packed decimal strings is identical to the interpretation of packed decimal strings, except that the rightmost 4 bit field of the rightmost byte in the string is interpreted as a decimal digit. A positive sign is always implied for unsigned packed decimal strings.

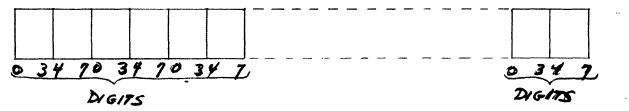

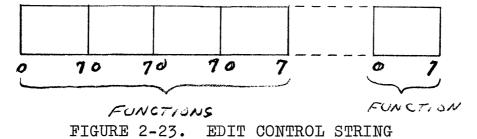

## 2.4.2 Edit Control String

An edit control string consists of a sequence of contiguous eight-bit bytes that are interpreted as either edit control function codes or as immediate operand bytes (see Figure 2-23). The maximum length of an edit control string is 65,536 bytes. An edit control string may originate at any byte boundary in storage.

The edit control string structor (explicit-length) has a format identical to that for zoned or packed decimal strings. The interpretation of the position and extent fields of this structor differ, however, from the interpretation appropriate to decimal string structors. In particular, the following interpretation applied to edit control string structors:

- a. The location field is used to identify the byte origin of the edit control string in storage.

- b. The length and scale factor fields may be used to imply the precision and scale appropriate to the destination string, if the source string is a decimal string.

- c. The extent field specifies the number of bytes in the edit control string and is used to terminate execution of the Edit instruction unless otherwise terminated.

An edit control string structor is valid as an operand only for the EDIT instruction. (See Section V).

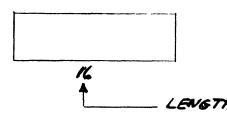

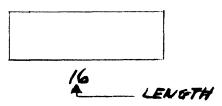

# 2.4.3 <u>Unformatted Region</u>

An unformatted region consists of a sequence of eightbit bytes for which no interpretation is implied. (See Figure 2-24). An unformatted region structor cannot be the effective operand of an instruction (see Section V), but can be used to represent an array of areas of storage allocated for a specific purpose. In this latter role, it is used in the Unformatted Region Qualification operation performed during instruction extraction. (See Subsection 3.5).

The maximum length for each unformatted region in an array of unformatted regions is 65,535 bytes. An unformatted region may originate at any byte boundary in storage, and may have zero length.

FIGURE 2-24. UNFORMATTED REGION

Unformatted regions are described by explicit-length structors. The interpretation of the POSITION field of unformatted region structors is as follows. (See Figure 2-25).

FIGURE 2-25. POSITION FIELD FOR UNFORMATTED REGION STRUCTORS

## HONEYWELL PROPRIETARY - SENSITIVE

The length field specifies the number of bytes in each unformatted region in the array of unformatted regions described by the structor. This field has a range 0 to 65,535 and is interpreted as an unsigned binary integer.

## 2.5 CONTROL INFORMATION REPRESENTATION

The operation of the task multiplexing and control facilities is dependent on the presence in main storage of information describing the current control structure of the system. This section is devoted to a description of this required information. The instructions which operate on the control information are described in subsection 5.6 and the operation of the task multiplexing and control facility is described in Section VI. The overall organization of the control information is shown in Figure 2-26.

# 2.5.1 <u>System Control Structors</u>

The format of the structors used for system control and I/O purposes is shown in Figure 2-27.

FIGURE 2-27. SYSTEM CONTROL STRUCTOR

The types applicable to system control are listed in Table 2-6.

1-16-70

TABLE 2-6 CONTROL STRUCTOR TYPES

| TY PE | PURPOSE                       |  |  |  |  |

|-------|-------------------------------|--|--|--|--|

| 0     | Procedure Index               |  |  |  |  |

| 1     | Relative Procedure Index      |  |  |  |  |

| 2     | TSB Identifier                |  |  |  |  |

| 3     | STOP Protected TSB Identifier |  |  |  |  |

| 4     | I/O Status Word               |  |  |  |  |

| 5     | External Status Word          |  |  |  |  |

| 6     | Type I Trap Effector          |  |  |  |  |

| 7     | Type II Trap Effector         |  |  |  |  |

| 8     | Reserved                      |  |  |  |  |

| 9     | Reserved                      |  |  |  |  |

| A     | Reserved                      |  |  |  |  |

| В     | Device Specifier              |  |  |  |  |

| C     | Alternate Array Specifier     |  |  |  |  |

| D     | Control Command Specifier     |  |  |  |  |

| E     | Reserved                      |  |  |  |  |

| F     | I/O Command Structor          |  |  |  |  |

The formats and purposes of these structors are discussed in the following subsections.

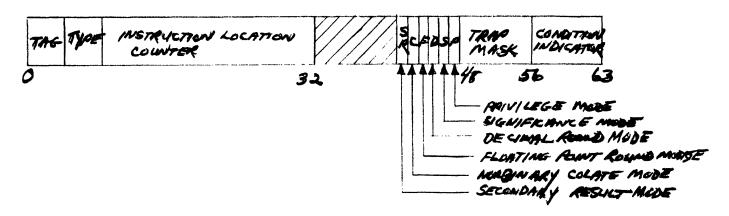

# 2.5.1.1 <u>Procedure Index</u>

A Procedure Index has the format shown in Figure 2-28. Procedure indices are used to describe the state of execution of a procedure. Each task has a Current Procedure Index as part of its TSB. The Current Procedure Index describes the state of the procedure which the task is executing. There may be many procedure indices associated with a single procedure.

FIGURE 2-28. PROCEDURE INDEX FORMAT

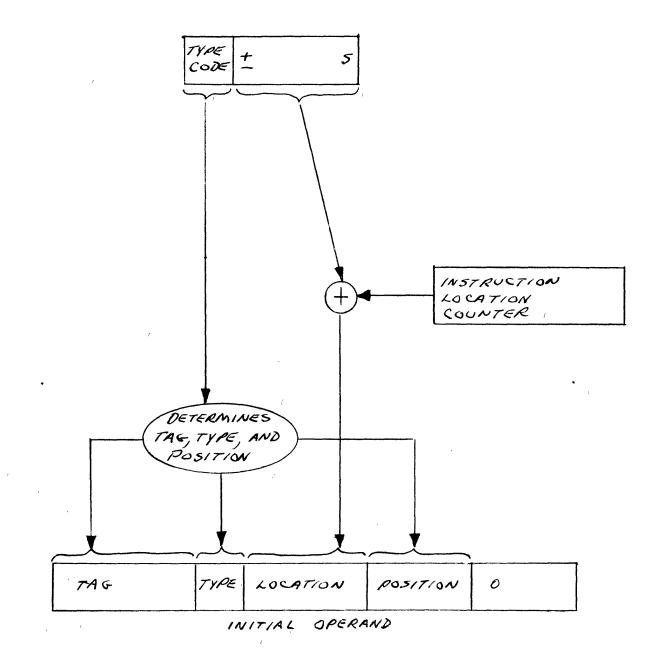

# 2.5.1.2 <u>Relative Procedure Index</u>

A Relative Procedure Index is identical to a Procedure Index except that the Instruction Location Counter field contains a displacement relative to the location of the Relative Procedure Index in main storage. A Relative Procedure Index is converted into a Procedure Index whenever it is loaded into a register. (See Subsection Autofetch Conversion).

## 2.5.1.3 <u>TSB Identifiers</u>

TSB identifiers are used as operands of the task control instructions which operate on the state of tasks. They are also used as elements of the I/O and External Start Arrays. (See subsections 7.6 and 7.7).

Two types of TSB identifiers are used. A TSB identifier is normally a legitimate operand for any task control instruction. A STOP Protected TSB identifier is a legitimate operand only for the START instruction. If an attempt is made to use a STOP Protected TSB identifier as the operand of a STOP, CONDITIONAL STOP, ISTOP, or SUSPEND instruction a illegal operand trap occurs.

FIGURE 2-29. TSB IDENTIFIER

# 2.5.1.4 Status Words

There are two types of status words: I/O and External. These tagged doublewords are used to transfer information from an I/O device or External source to a task. (See subsections 7.6 and 7.7).

**M**G TYPE STATUS INFORMAT ON

#### FIGURE 2-30. STATUS WORDS

## 2.5.1.5 Trap Effectors

Whenever an instruction references a trap effector either as an operand or during autofetch or autostore a trap occurs. The effects of these traps are described in subsection 8-1. The Trap Effector format is shown in Figure 2-31.

RESERVED FOR SOFFWARE JSE TAG TYPE

## FIGURE 2-31. TRAP EFFECTORS

## 2.5.2 System Base

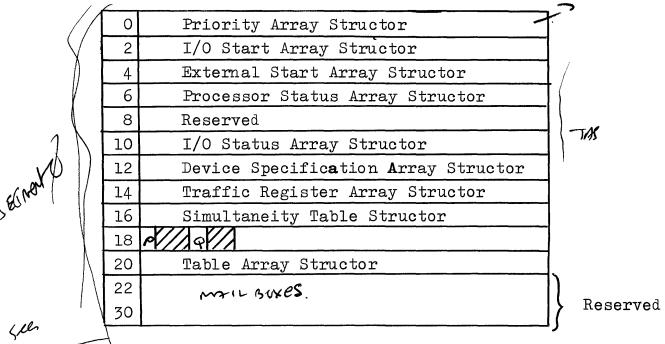

The System Base is an area in memory which contains information, or descriptions of information, concerning the state of the system as a whole. It acts as a fixed base through which the remainder of the system control

11-26-69

information may be accessed. It is always located in words 0-31 of main storage. The format of the System Base is shown in Figure 2-32.

FIGURE 2-32. SYSTEM BASE ORGANIZATION

The allocation of space in the System Base is as follows:

- Words O-1: The Priority Array Structor: This explicitlength bit-string structor describes the Priority Array. (See subsection 2.5.4).

- Words 2-3: The I/O Start Array Structor: This tagged double-word array structor describes the I/O Start Array.

- Words 4-5: The External Start Array Structor: This tagged doubleword array structor describes the External Start Array.

- Words 6-7: The Processor Status Array Structor: This explicit length byte string array structor describes the Processor Status Array.

Words 8-9: Reserved.

- Words 10-11: The I/O Status Array Structor: This

- explicit length byte string array structor describes the I/O Status Array.

- Words 12-17: Three array structors used to identify tables required by the I/O.

- Word 18: This word contains two lock bytes: P is the priority structure lock, and Q is the Queue lock.

- Words 20-21: The Table Array Structor: This byte string array structor describes an array of 252 byte strings, each of length 256, used for translation tables.

Words 22-25: These words are reserved.

## 2.5.3 <u>Task Status Block</u>

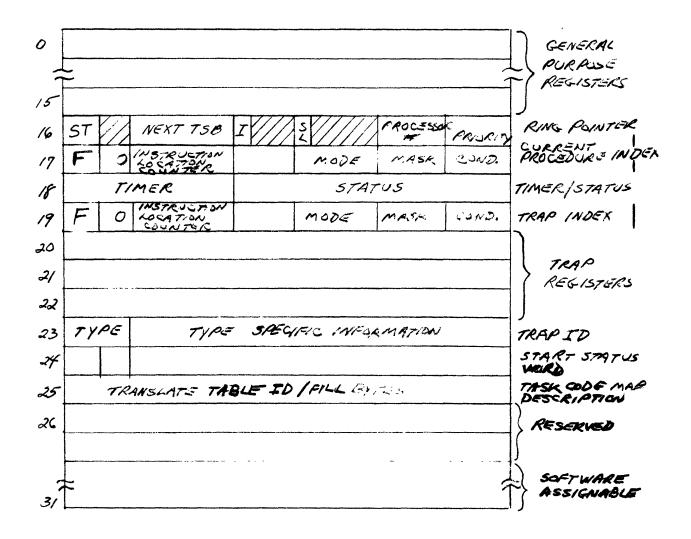

The existance and current status of a task is specified by a Task Status Block (TSB). TSB's are stored in main storage and must be located on a double word boundary. They are up to 32 double words long. The exact length is determined by the operating system. Certain portions of the TSB must be accessible to the hardware. For this reason the low order portion of the TSB has a fixed format as shown in Figure 2-33.

The allocation of the TSB is as follows:

(In the following descriptions all unused bits are required to be zero).

a. Doublewords 0-15:

Sixteen general purpose registers which may be used to hold tagged data or structors.

b. Doubleword 16:

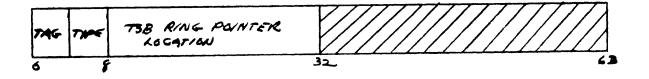

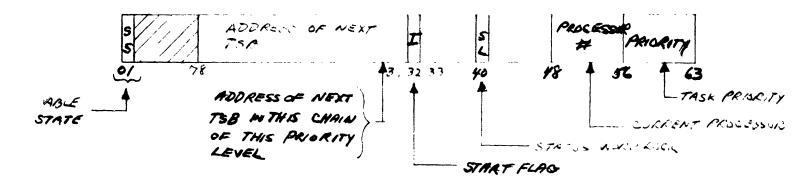

A Ring Pointer which is used to link all Tasks at a given priority level into a circular chain. (See Figures 2-33 and 2-34.)

Bits O and 1 specify the current state of the task. They are encoded as follows:

FIGURE 2-33. TSB FORMAT

- 00 Running: A running task is currently utilizing a processor.

- Ol Ready: A ready task is one which, while not currently using a processor, is prepared to do so.

- 10 Blocked: A blocked task is not prepared to run and is waiting for some event external to itself.

- 11 Available: An available task is one which is not prepared to run and which must be modified by the operating system before it may run.

Bits 8-31 contain the address of the next TSB in the chain. Bit 32 is a Start Flag which is set whenever an External of I/O Start is directed to the task. Bits 40-47 are a lock for the Start Status Word. Bits 48-55 specify the processor executing the task if it is in the running state. Bits 56-63 specify the priority of the task.

FIGURE 2-34. RING POINTER

c. Doubleword 17:

The current procedure index. This represents the state of the procedure which the task is currently executing.

d. Doubleword 18:

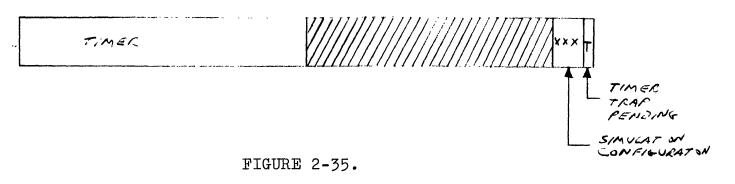

This word contains a 32 bit task timer and a 32 bit status field the task timer is discussed in subsection 9.3. The status field is allocated as shown in Figure 2-35.

## HONEYWELL PROPRIETARY - SENSITIVE

The emulation configuration field (bits 27-29) are used to indicate whether or not the task requires a non-native instruction set for its execution.

e. Doubleword 19:

The Trap Index is a procedure index with the format shown in Figure 2-28. Its contents exchanged with the contents of the current procedure index when a trap occurs.

f. Doublewords 20, 21, 22:

Three general purpose register images used for trap handling.

g. Doubleword 23:

A trap ID field where information about a trap may be stored.

h. Doubleword 24:

This doubleword contains either a status field used to store an External or I/O Status Word, or a FIFO structor used to point to an area where status words may be stored.

i. Doubleword 25:

This double word contains three one-byte indices used to select the Load Translate, Store Translate, and Non-Binary Collate Tables. The Tables are selected by using the index byte. to index the Table Array Structor in the system base. This doubleword also contains all numeric and alpha numeric fill bytes. 7 15 23 31 77 35 43 If any of these indices is set to all ones or exceed the extent of the Table Array Structor the corresponding table is not present.

FIGURE 3-36.

j. Doublewords 26-27:

These words are reserved.

k. Doublewords 28-31:

These words are assignable by the operating system.

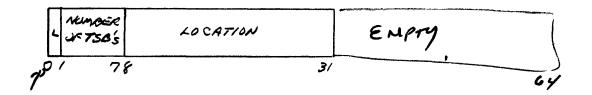

2.5.4 Task Priority Array

The Task Priority Array (TPA) is a doubleword aligned array of 32 bit binary strings identified by the Priority Array Structor in the System Base. There is one entry in the Task Priority Array for each priority level in the system. (The maximum number of levels is 255). Each of the entries in the array points to a ring structure of all the TSBs in the system at the corresponding priority level. The format of a TPA entry is shown in Figure 2-37. Bits 8-31 are the location field and specify the address of the ring pointer of a TSB in the ring structure.

FIGURE 2-37. TASK PRIORITY ARRAY ENTRY FORMAT

2-37 HONEYWELL PROPRIETARY - SENSITIVE 1-16-70

## HONEYWELL PROPRIETARY - SENSITIVE

Bit O is a Level Blocked Indicator which is set whenever the system discovers that none of the tasks in the corresponding level are in the ready state. The Level Blocked Indicator is reset whenever a task in the corresponding level makes a transition to the ready state.

Bits 1 through 7 specify the number of tasks in the ring structure at the corresponding level.

## 2.5.5 <u>I/O Start Array</u>

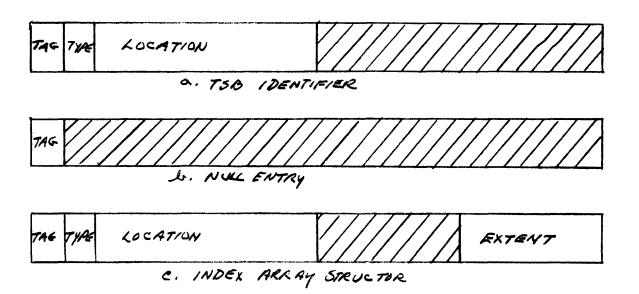

The I/O Start Array is an array of tagged doublewords identified by the I/O Start Array structor in the System Base. The number of entries in the I/O Start Array is a function of the I/O complement of the system and the software. Each entry may be one of the three types shown in Figure 2-38.

FIGURE 2-38. I/O AND EXTERNAL START ARRAY ENTRIES

The first allowable type of entry in the ISA is a TSB identifier ((b) in Figure 2-38). The location field in this entry addresses the ring pointer location in a TSB.

The second type of entry is a doubleword with a 0 tag field, ( (b) in Figure 2-38). This entry is used as a null element.

The final type of entry is an implicit length tagged doubleword structor ( (c) in Figure 2-38). This structor describes an Index Array which in turn may contain any one of these three types of entries. (See subsection I/O Starts).

# 2.5.6 <u>External Start Array</u>

The External Start Array is an array of tagged doublewords identified by the External Start Array Structor in the System Base. The number of entries in the array is a function of the size of the system and the operating system requirements. Each entry may be one of the three types described in subsection 2.5.5. The formats of these entries are identical with those described for the I/O Start Array in subsection 2.5.5.

# 2.5.7 <u>Processor Status Array</u>

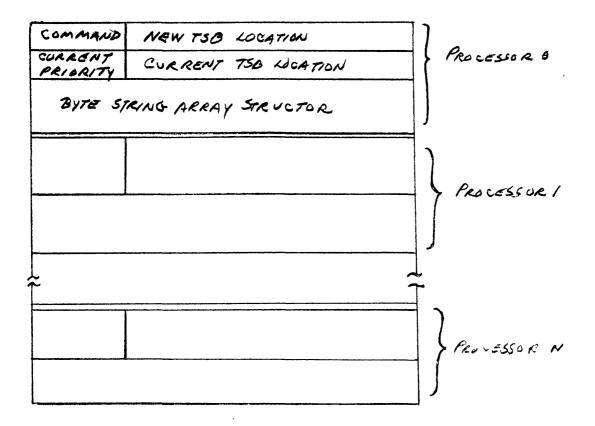

The Processor Status Array (PSA) is a doubleword aligned array of byte strings identified by the Processor Status Array Structor in the System Base. There is a 16 byte string in the array for each processor attached to the system. The organization of these strings is shown in Figure 2-39.

The first four bytes of a PSA entry has a one-byte command field and a three-byte location field. Both of these fields are used to convey information from the system to the associated processor.

FIGURE 2-39. PROCESSOR STATUS ARRAY

The second four bytes of a PSA entry is divided into two fields: the first byte specifies the priority of the task which is being executed by the processor. The other three bytes contain the address of the Ring Pointer of the task being executed by the processor. If the processor is in the wait state then the first byte is set to all ones and the other three bytes are unspecified.

The last eight bytes of a PSA entry is a byte string array structor used to point to an area of storage reserved for the use of the associated processor. The size of this area depends on the implementation of the processor.

> NOTE The first entry in the PSA (processor zero) is reserved for the DCS. Its priority field will always be set to zero.

# 2.5.8 <u>I/O Status Array</u>

The I/O Status Array is a doubleword aligned array of byte strings identified by the I/O Status Array Structor in the System Base. Each entry in the array consists of a 16 byte string. The first eight bytes are used as a communications buffer between the processors and the I/O. The other eight bytes form a string reserved for the use of the I/O.

The number of entries in the array depends on the implementation of the I/O subsystem.

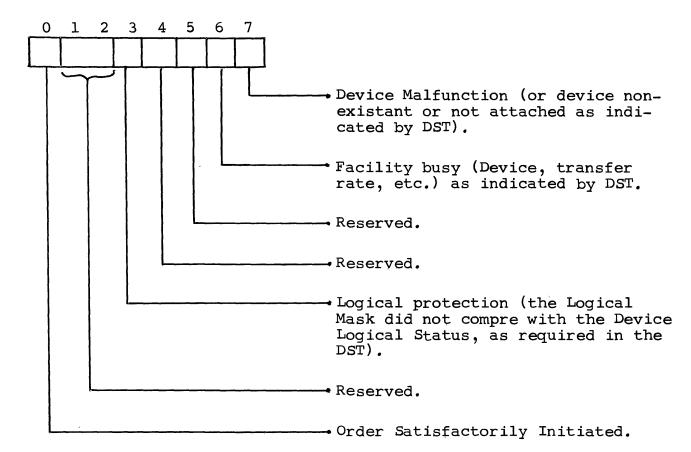

# 2.6 <u>I/O INFORMATION REPRESENTATION</u>

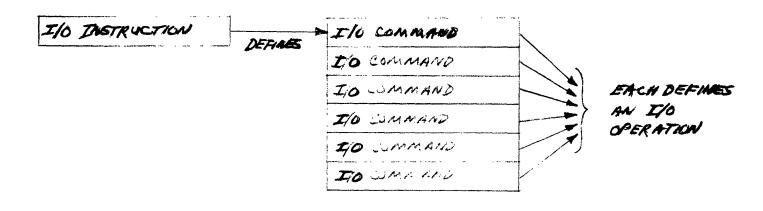

The execution of Input/Output instructions will require the use of information stored in main memory. Only the description and modification of this information will be specified in this section. A detailed explanation of how this information is to be used, the execution of I/O instructions and the I/O facilities, is presented in Section X.

# 2.6.1 <u>I/Q Structors</u>

Tag F structors are used for system control and I/O purposes. The general format is shown in Figure 2-27. The types applicable to Input/Output structors are listed in Table 2-7.

| TYPE                  | PURPOSE                                                                                                        |  |

|-----------------------|----------------------------------------------------------------------------------------------------------------|--|

| B<br>C<br>D<br>E<br>F | Device Specifier<br>Alternate Array Specifier<br>Control Command Specifier<br>Reserved<br>I/O Command Structor |  |

TABLE 2-7 I/O STRUCTOR TYPES

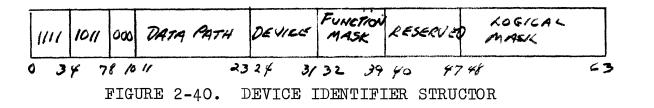

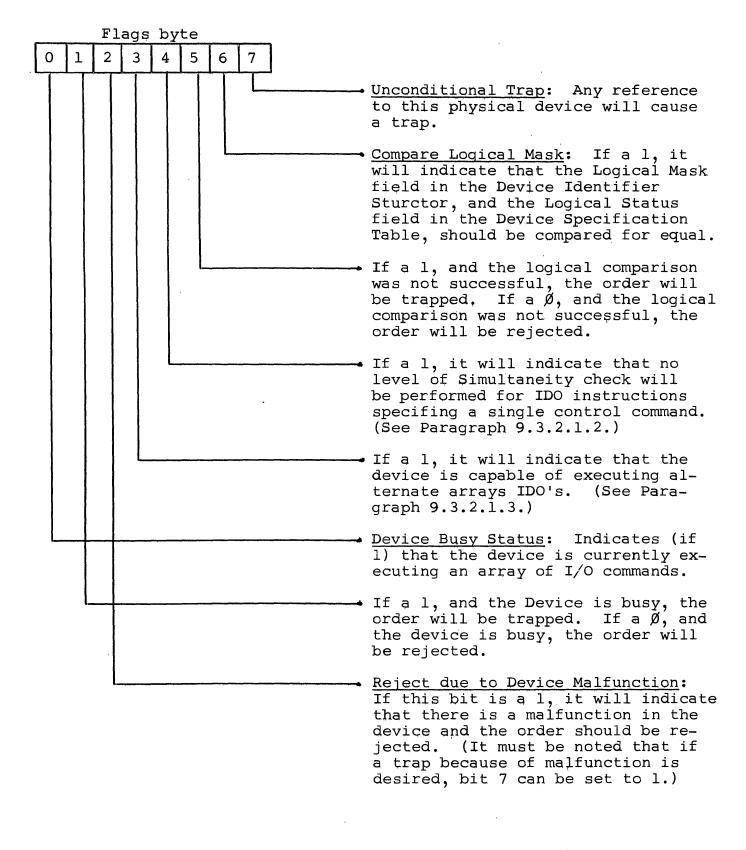

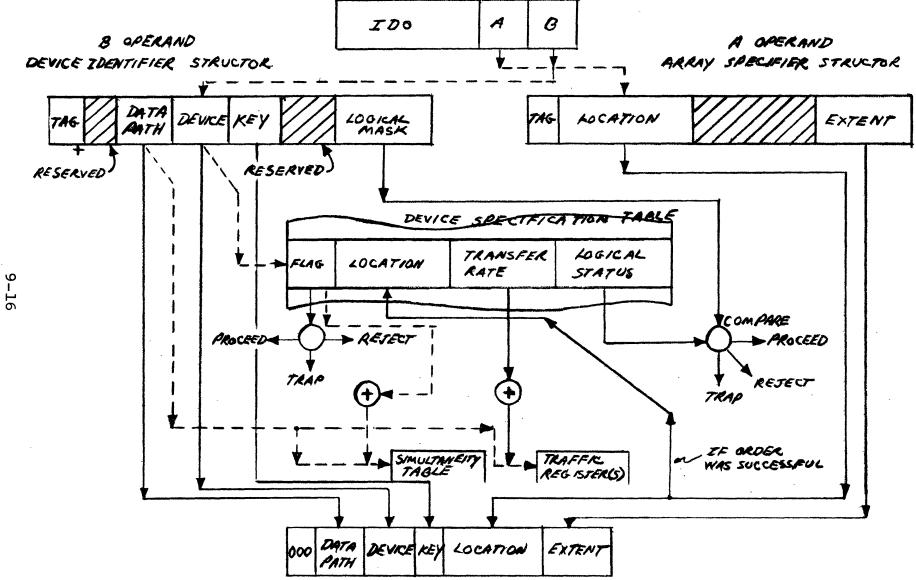

2.6.1.1 <u>Device Identifier Structor</u>

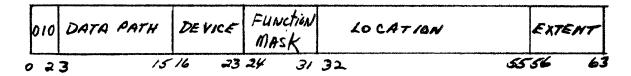

This structor is used to specify the logical device to be used in the peripheral operation. It is formatted as shown in Figure 2-40.

The eight-bit device and 13-bit data path fields define a device and routing information. The eight-bit Function Mask and 16-bit Logical Mask fields, which are used in protection are explained in Section IX.

2.6.1.2 Alternate Array Specifier Structor

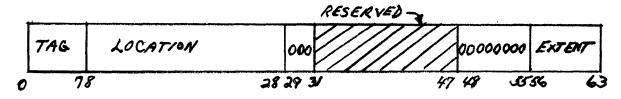

This structor will point to an array of I/O Command structors. It is to be used as the A operand in certain types of Initiate Device Operation Order. Its formats is shown in Figure 2.41,

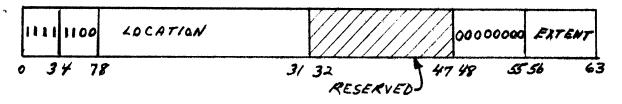

|   | [[]] | 1/20 | LOCATION | RESERVED | 00000000 | EXTENT |

|---|------|------|----------|----------|----------|--------|

| ć | 03   | 4 7  | 78 31    | 32 47    | 48 55    | 56 63  |

FIGURE 2-41. ALTERNATE ARRAY SPECIFIER

The 24-bit LOCATION field points to the first double word of an I/O Command Array, whose extent is specified in the EXTENT field.

This structor is used in the IDO order to initiate I/O operations on a busy device. Its application is further explained in Section X.

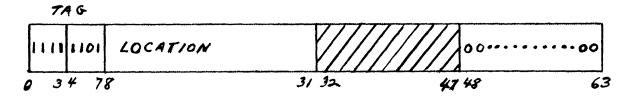

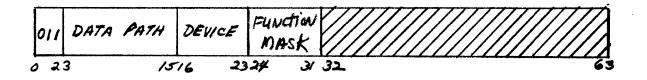

# 2.6.1.3 <u>I/O Control Command Specifier</u>

The I/O command defines a control operation. It is to be used as the A operand in the IDO instruction which specifies the execution of a single control command. Its format is shown in Figure 2-42.

| 111 | 1/0/ | LOCATION |    | RESERVED | 000000000000000000000000000000000000000 |   |

|-----|------|----------|----|----------|-----------------------------------------|---|

| 0 3 | ¥ 7  | F        | 31 | 32       | 5556 6                                  | 3 |

FIGURE 2-42. I/O CONTROL COMMAND SPECIFIER

It is similar to the implicit-length structor with the exception that the extent field is all zeros (it points to a single command).

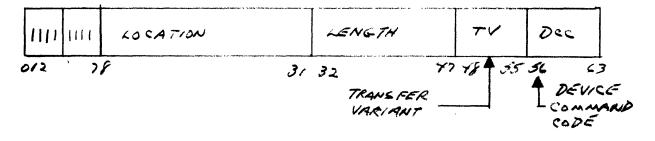

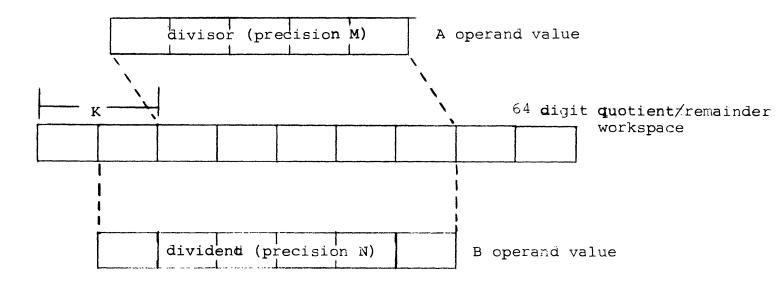

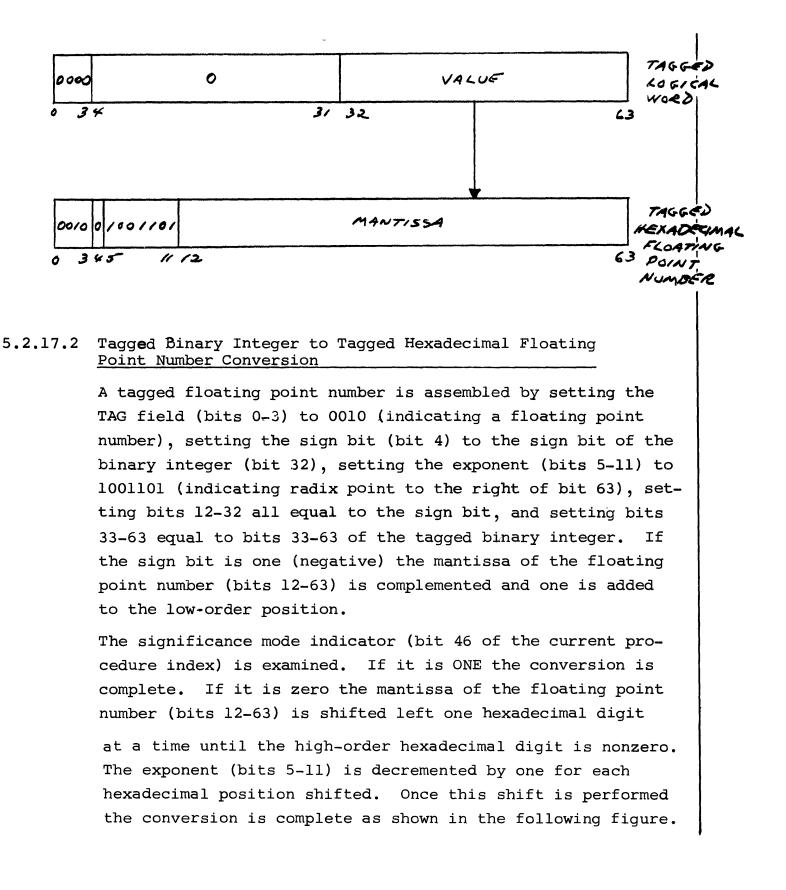

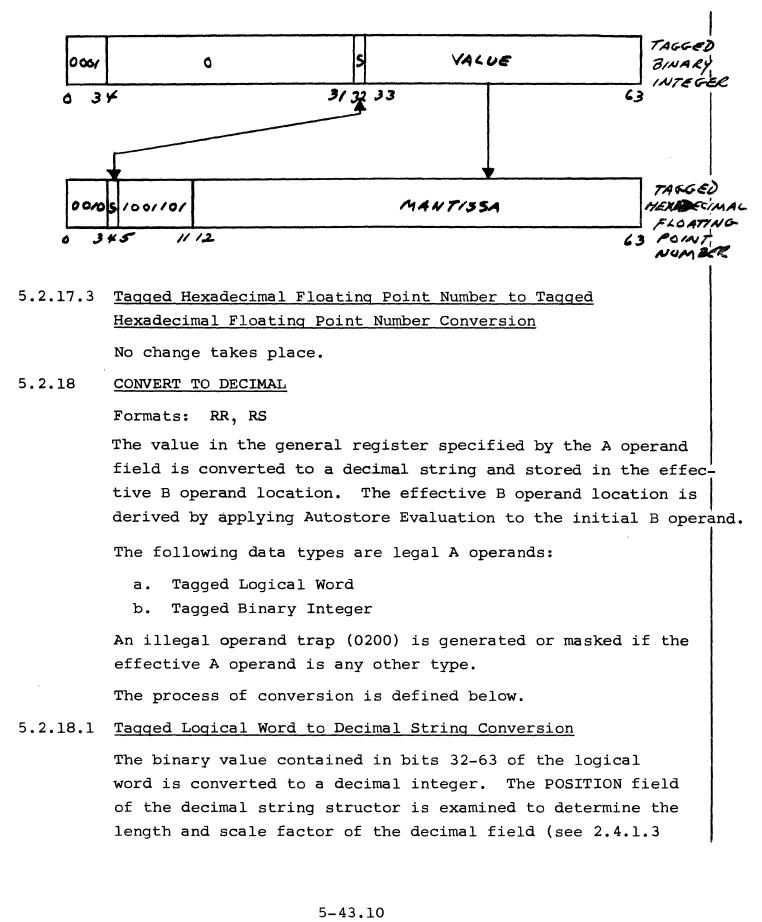

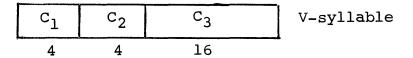

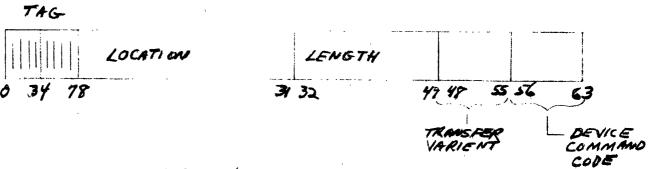

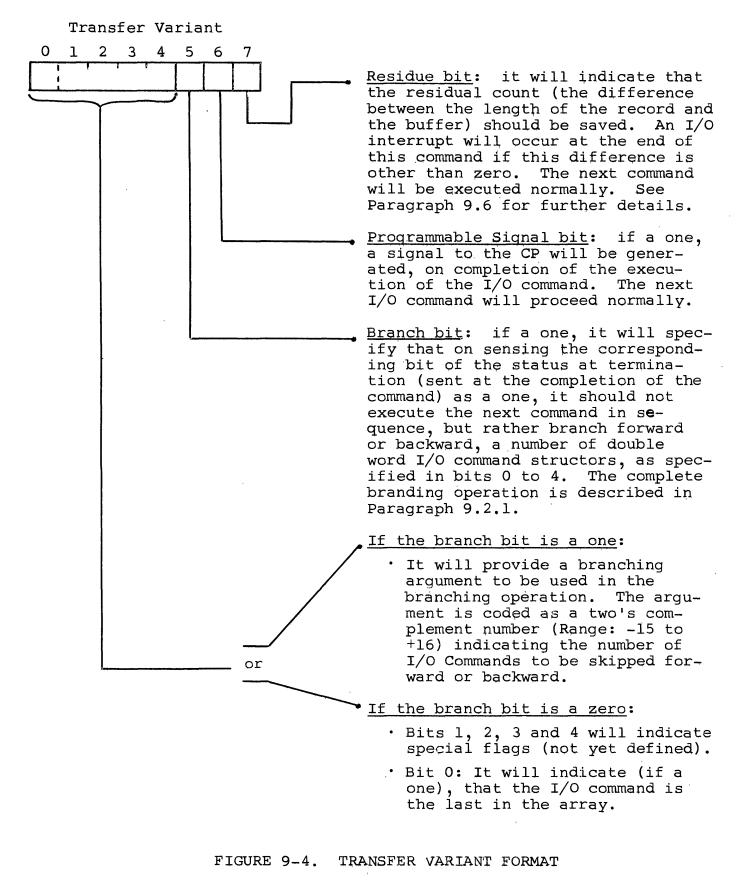

## 2.6.1.4 <u>I/O Command Structor</u>