TYPE 281-2BSC COMMUNICATION CONTROL AND TYPE 285-2BSC COMMUNICATION ADAPTER

# Honeywell

**SERIES 200**

# TYPE 281-2BSC COMMUNICATION CONTROL AND TYPE 285-2BSC COMMUNICATION ADAPTER

#### SUBJECT:

Hardware Description, Functional Characteristics, Operation, and Programming Information for the Type 281-2BSC Communication Control and Type 285-2BSC Communication Adapter.

#### **SPECIAL INSTRUCTIONS:**

This manual is one of a series of hardware publications for communication controls and adapters. It should be used in conjunction with the manual, *Type 286-6 and 286-7 Message-Mode Multi-Line Communication Controls*, Order No. G86, and the appropriate programmers' reference manual.

DATE:

March 31, 1971

FILE NUMBER: 113.0005.1100.0-F<sup>\*</sup>1

#### PREFACE

This manual provides the Honeywell Series 200 user with general information, functional characteristics, operating information, and programming information concerning the Type 281-2BSC Communication Control and the Type 285-2BSC Communication Adapter. Additional information concerning the central processors and other peripheral devices will be found in other Honeywell Series 200 publications.

©1971, Honeywell Information Systems Inc.

#### TABLE OF CONTENTS

| C   | 4:   | т |

|-----|------|---|

| Sec | tion | T |

Section II

|                                                   | Page                         |

|---------------------------------------------------|------------------------------|

| Introduction                                      | 1 - 1                        |

| General Description                               | 1-1                          |

| Line Transmission Characteristics                 | 1-1                          |

| Interface                                         | 1 - 1                        |

| Remote Terminals                                  | 1-3                          |

| Communication Codes                               | 1 - 3                        |

| Line Speeds                                       | 1-3                          |

| Test Units                                        | 1-4                          |

| Functional Characteristics                        | 2-1                          |

| Transmission Mode                                 | 2-1<br>2-1                   |

| Message Block Format                              | 2-1<br>2-1                   |

| Communication Control Characters                  | 2-1<br>2-1                   |

| Synchronization (SYN) Characters                  | 2-1<br>2-1                   |

|                                                   | 2 <b>-</b> 1<br>2 <b>-</b> 6 |

| Start-of-Heading (SOH) Character                  | 2-0<br>2-6                   |

| Start-of-Text (STX) Character                     | 2-0<br>2-6                   |

| End-of-Text (ETX) Character                       |                              |

| End-of-Transmission Block (ETB) Character         | 2-6                          |

| End-of-Transmission (EOT) Character               | 2-7                          |

| Enquiry (ENQ) Character                           | 2-7                          |

| Positive Acknowledgment Sequences (ACKØ and ACK1) | 2-7                          |

| Negative Acknowledgment (NAK) Character           | 2-7                          |

| Data Link Escape (DLE) Character                  | 2-7                          |

| End-of-Intermediate-Block (ITB) Character         | 2-8                          |

| Longitudinal Redundancy Check (LRC) and Cyclic    |                              |

| Redundancy Check (CRC) Characters                 | 2-8                          |

| Wait Before Transmitting (WACK) Character         | 2-8                          |

| Reverse Interrupt (RVI) Sequence                  | 2-8                          |

| Temporary Text Delay (TTD) Sequence               | 2-9                          |

| Pad Characters                                    | 2-9                          |

| Character Format                                  | 2-10                         |

| Line Format                                       | 2-10                         |

| Memory Allocation                                 | 2-10                         |

| Variable Character Recognition                    | 2-10                         |

| Error Control                                     | 2-10                         |

| VRC/LRC Combination                               | 2-12                         |

| Cyclic Redundancy Check (CRC-12/CRC-16)           | 2-13                         |

| VRC/CRC-16 Combination                            | 2-13                         |

| Format Errors                                     | 2-14                         |

| Overwrite                                         | 2-14                         |

| Timeouts                                          | 2-14                         |

| Transmit Timeout                                  | 2-14                         |

| Receive Timeout                                   | 2-14                         |

| Inactivity Timeout                                | 2-15                         |

| Underflow Timeout                                 | 2-15                         |

| Text Timeout                                      | 2-15                         |

| Text Delay Timeout                                | 2-15                         |

|                                                   |                              |

## TABLE OF CONTENTS (cont)

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Page                                                                                                                                                             |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section III | Operation<br>Point-to-Point Operation<br>Point-to-Point Operation with Contention<br>Switched Network Operation<br>Multipoint Operation<br>Limited Conversational Mode                                                                                                                                                                                                                                                                                                                                                                                           | 3-1<br>3-1<br>3-1<br>3-2<br>3-3<br>3-6                                                                                                                           |

| Section IV  | Programming InformationInterrupt ProcessingSystem RequirementsData TransferSix-Level CodesEight-Level CodesSeven-Level Codes (Plus Parity)ProgrammingInitializationSynchronizationData TransmissionControl SequencesTransmitting SequencesData ReceptionReceiving Control SequencesProcessing InterruptsReceptionReceptionReceptionTerminating CommunicationPeripheral Control and Branch (PCB) InstructionsFormatInstructions for Status and ControlPeripheral Data Transfer (PDT) InstructionsFormatTesting the 281-2BSCSimulated ReceptionSimulated Reception | $\begin{array}{c} 4-1\\ 4-1\\ 4-1\\ 4-1\\ 4-2\\ 4-2\\ 4-2\\ 4-2\\ 4-2\\ 4-2\\ 4-2\\ 4-3\\ 4-3\\ 4-4\\ 4-6\\ 4-7\\ 4-9\\ 4-9\\ 4-9\\ 4-9\\ 4-9\\ 4-9\\ 4-9\\ 4-9$ |

| Section V   | 285-2BSC Special Considerations<br>Control Signals<br>Received Illegal Sequence<br>Received Good Message<br>Received Message with Error<br>Received Abort<br>Sent Illegal Sequence<br>Sent Message<br>Delayed Answer                                                                                                                                                                                                                                                                                                                                             | 5 - 1<br>5 - 2                                                                                    |

iv

#F11

### TABLE OF CONTENTS (cont)

٠

| Section V (cont) | Underflow<br>Overwrite<br>Operation                                                            | 5 <b>-</b> 2      |

|------------------|------------------------------------------------------------------------------------------------|-------------------|

| Appendix A       | Miscellaneous Information<br>Message Formats<br>Headings<br>Text<br>Transparent Text Operation | A-1<br>A-1<br>A-1 |

|                  | Special Replies and Sequences                                                                  |                   |

#### LIST OF ILLUSTRATIONS

| Figure 1-1.  | - Je to                                                  | 1-2          |

|--------------|----------------------------------------------------------|--------------|

| Figure 2-1.  | Binary Synchronous Communication Formats                 | 2-2          |

| Figure 3-1.  | Point-to-Point Initialization Phase                      | 3-1          |

| Figure 3-2.  | Typical Polling Sequence                                 | 3-5          |

| Figure 3-3.  | Typical Selection Sequence                               | 3-5          |

| Figure 3-4.  |                                                          | 3-6          |

| Figure 4-1.  | PCB Instruction Format                                   | 4-11         |

| Figure 4-2.  | PDT Instruction Format                                   | 4-19         |

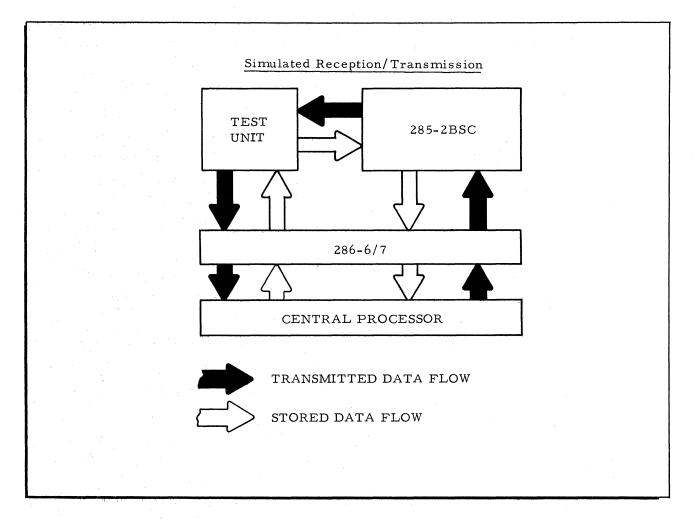

| Figure 4-3.  | Test Loop for Type 281-2BSC Communication Control        | 4-20         |

| Figure 4-4.  | Test Loop for Type 285-2BSC Communication Adapter        | 4-22         |

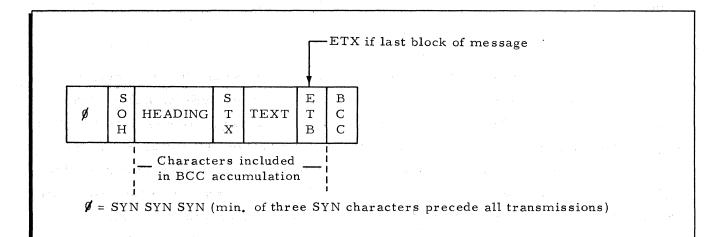

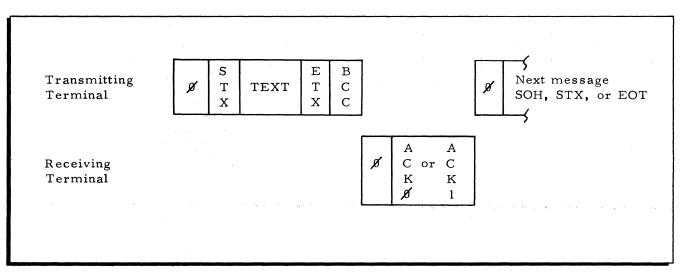

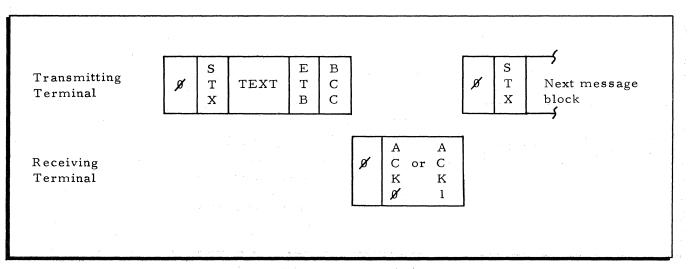

| Figure A-l.  | Block Check Character Accumulation — Entire Transmission | A-2          |

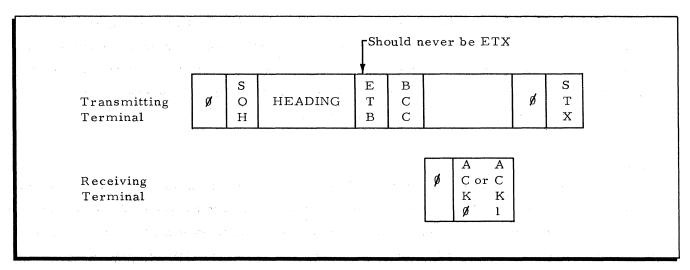

| Figure A-2.  | Block Check Character Accumulation — Heading Only        | A-2          |

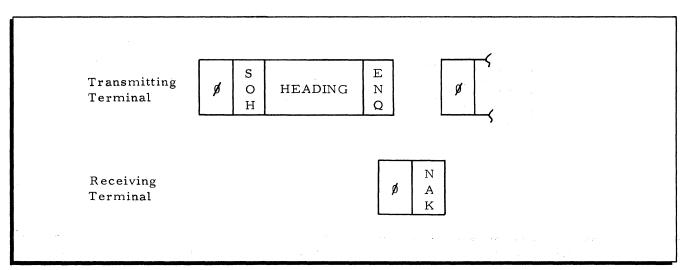

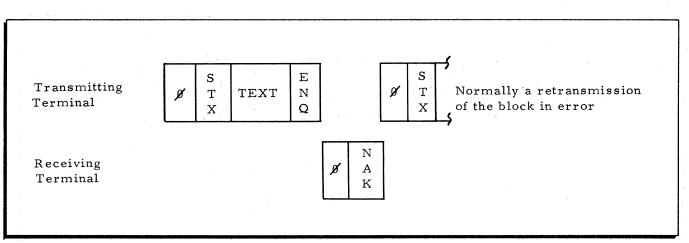

| Figure A-3.  | Use of ENQ to Terminate Heading                          | A-3          |

| Figure A-4.  | Format of Last Block                                     | A <b>-</b> 3 |

| Figure A-5.  |                                                          | A <b>-</b> 3 |

| Figure A-6.  | Format of Block Ended with Forced Error Condition        | A-4          |

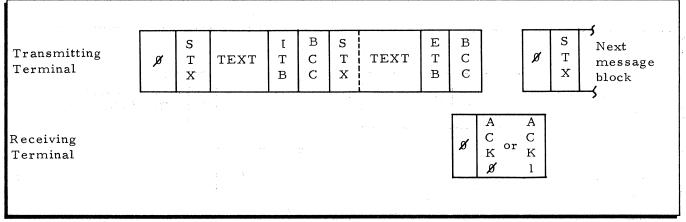

| Figure A-7.  | Format of Block with Intermediate Blocking               | A-4          |

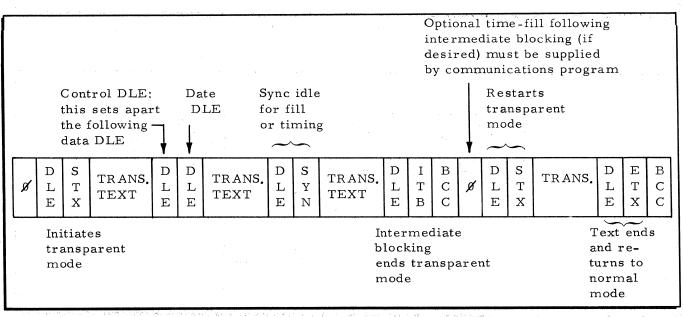

| Figure A-8.  | Transparent Data Block                                   | A-4          |

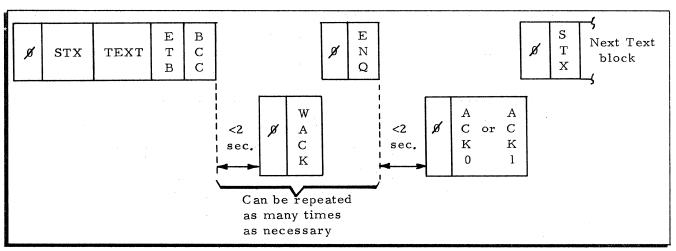

| Figure A-9.  | Example of Use of WACK Reply                             | A-5          |

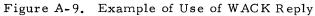

| Figure A-10. | Example of Use of RVI Reply                              | A-5          |

| Figure A-11. |                                                          | A-5          |

#### LIST OF TABLES

| Table 2-1. | BSC Line Control Characters 2-3              | 3  |

|------------|----------------------------------------------|----|

| Table 2-2. | Control Character Summary 2-4                | 4  |

| Table 2-3. | Error Checking Capabilities 2-1              | 12 |

| Table 4-1. | PCB Instructions for Transmit Status         | 12 |

| Table 4-2. | PCB Instructions for Receive Status 4-1      | 15 |

| Table 4-3. | Control PCB Instructions 4-1                 | 18 |

| Table A-1  | . EBCDIC Character Assignments A-(           | 6  |

| Table A-2  | . ASCII Character Assignments A-'            | 7  |

| Table A-3  | . Six-Bit Transcode Character Assignments A- | 8  |

| Table A-4  | . Control Character Conversion Chart A-      | 9  |

Page

•

#### SECTION I

#### INTRODUCTION

#### GENERAL DESCRIPTION

The Honeywell communication devices in this manual allow a Series 200 central processor<sup>1</sup> to communicate with remotely-located terminal equipment using binary synchronous communications (BSC). Data transfer can be initiated by the central processor or by the remote terminal.

The Type 281-2BSC Single-Channel Communication Control controls the flow of data between the central processor and the remote terminal over voice-grade telephone lines. The lines can be private (lines dedicated to a specific application) or switched (a telephone network where the connection between the local and remote terminals is established, as required, by dialing or some other means of switching). The Type 285-2BSC Communication Adapter allows a Type 286-6 or -7 Message-Mode Multi-line Communication Control to be used in lieu of the Type 281-2BSC in applications where a large number of communication channels are required.

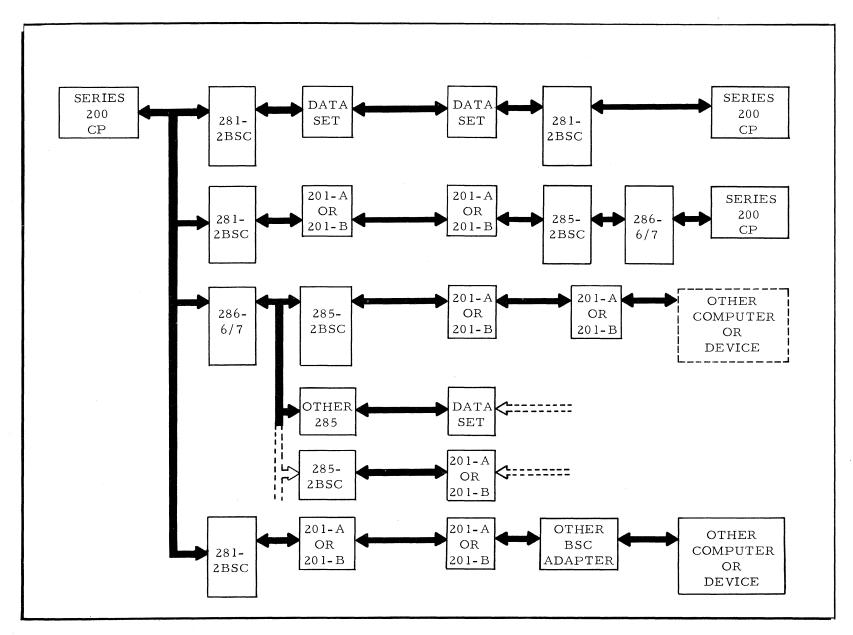

Figure 1-1 illustrates typical applications of the Type 281-2BSC and 285-2BSC. As shown, both units are connected to the line by means of internal sync data sets, and the same type of data set is required at both ends of the line. Data communication is in the message block mode.

#### LINE TRANSMISSION CHARACTERISTICS

Data transmission is two-way, nonsimultaneous (half-duplex). Clock pulses for bit stream synchronization are supplied by the data set. Character synchronization is achieved through recognition of two successive synchronization characters.

#### INTERFACE

The Type 281-2BSC Communication Control is connected to a standard Series 200 input/ output channel by means of standard peripheral interface logic. Each communication control occupies one standard Series 200 logic drawer.

The Type 285-2BSC Communication Adapter is connected to a Type 286-6 or -7 Message-Mode Multi-line Communication Control by way of standard cables and Series 200 interface packages. Two communication adapters occupy one standard Series 200 logic drawer.

<sup>&</sup>lt;sup>1</sup>A Series 200 Control Unit Adapter is required for attachment to a Type 121 Central Processor; these communication devices cannot be used with a Type 111, 121-0, 201, or 201-1 processor.

Figure 1-1. System Configuration

1-2

The communication controls and communication adapters interface with the data set in accordance with Electronic Industry Association RS-232C.

#### REMOTE TERMINALS

The Type 281-2BSC and 285-2BSC will operate with three types of remote terminals:

- 1. Series 200 central processor<sup>1</sup> equipped with a compatible BSC communication control and a compatible data set.

- 2. Keytape<sup>2</sup> 760/960 High-Speed Communicators.

- 3. Any computer or device that is equipped with a compatible data set and that satisfies the following requirements:

- a. The same code set must be used at both ends of the transmission line.

- b. BSC message format must be used at both ends of the transmission line.

- c. The same error checking procedures and conventions, as described later in this manual, must be used at both ends of the line.

- d. Operation must be in the continuous bit stream mode, with synchronization established for each text block.

#### COMMUNICATION CODES

Depending on the intended use established at the time of order, the EBCDIC (Extended Binary Coded Decimal Interchange Code) with 256 character assignments, the ASCII (American Standard Code for Information Interchange) with 128 character assignments, or the Six-Bit Transcode with 64 character assignments, can be selected as the communication code.

Also, on special order, the communication control or adapter can be made to operate with any 6- or 8-bit code. However, if a parity bit is required, bit 8 (the most significant bit) must be used for this purpose, and parity must be odd.

Regardless of the code specified, the communication control or adapter is capable of transmitting and receiving in a code transparency mode to allow the transmission of data that does not fall within the code set (pure binary, machine-language instruction, etc.).

#### LINE SPEEDS

Private line operation is normally at 2400 bits per second; switched line operation is normally at 2000 bits per second. When the 285-2BSC adapter is equipped with Feature 1072, 1073, 1074, 1075, or 1076, operating speed is increased to 3600, 4800, 5400, 7200, or 9600 bps, respectively. (The data sets and line must be capable of operation at the appropriate speed.)

<sup>&</sup>lt;sup>1</sup>Interrupt capabilities must be present.

<sup>&</sup>lt;sup>2</sup>Trademark.

#### TEST UNITS

All Type 281-2BSC Communication Controls and Type 285-2BSC Communication Adapters are supplied with a test unit, which is housed in the same logic drawer. The test unit can be used for loop-back testing, and is activated by the appropriate PCB and PDT instructions described later in this manual. The test unit simulates the data set timing signals to allow functional testing.

# SECTION II FUNCTIONAL CHARACTERISTICS

#### TRANSMISSION MODE

The Type 281-2BSC Communication Control and Type 285-2BSC Communication Adapter operate half-duplex in the message block mode. This means that after the initial block of test is transmitted, each ensuing block of text will be transmitted only after a response for the previous block has been received from the distant terminal. The text blocks may be of variable length; the maximum block size is determined only by available memory size and data storage capabilities at the terminals, except when transmitting in the transparent mode; then the block length cannot exceed 4096 line characters. (This restriction applies only to transmission.)

#### MESSAGE BLOCK FORMAT

The general message block format for BSC communication is as follows:

| Synchronization | Start of | Data | End of | BCC       |

|-----------------|----------|------|--------|-----------|

| Characters      | Text     |      | Text   | Character |

|                 |          |      |        |           |

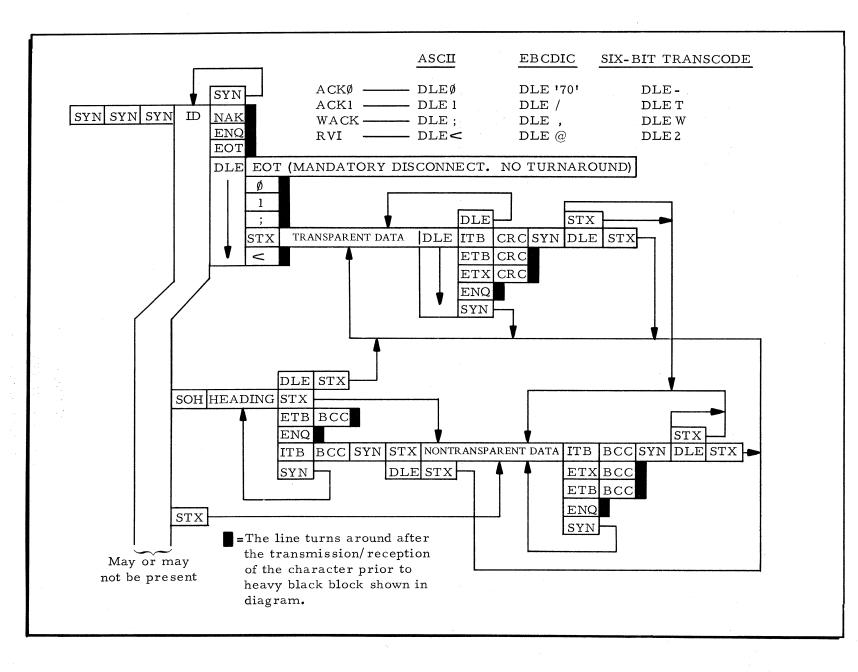

The variety of legal message block formats is shown in Figure 2-1. Table 2-1 shows the bit structure of the BSC line control characters shown in Figure 2-1, as well as the octal representation that is to be stored in memory.

#### COMMUNICATION CONTROL CHARACTERS

The 281-2BSC and 285-2BSC are capable of character recognition and decoding. The various control characters are summarized in Table 2-2 and described in the following paragraphs.

#### Synchronization (SYN) Characters

The synchronization (SYN) character is used to establish and maintain synchronism between the two ends of the communication line. Each block of characters must be preceded by at least three SYN characters. The 281-2BSC or 285-2BSC must recognize two successive SYN characters in order to synchronize with the remote terminal. Received SYN characters are not transferred to the central processor, nor are they included in LRC or CRC computation.

During communication the transmitting communication control automatically inserts two successive SYN characters into the data stream at one-second intervals to maintain character synchronization. Also, if the communication control is awaiting data from the central processor

SECTION II. FUNCTIONAL CHARACTERISTICS

#F11

2-2

|            | AS                              | CII                     | EBC                      | DIC                   | Six-Bit 7               | ranscode |

|------------|---------------------------------|-------------------------|--------------------------|-----------------------|-------------------------|----------|

| Character  | Binary                          | Octal #1                | Binary                   | Octal #1              | Binary                  | Octal #3 |

| SYN        | 00010110                        | 0026                    | 00110010                 | 0062                  | 111010                  | 72       |

| NAK        | 00010101                        | 0025                    | 00111101                 | 0075                  | 111101                  | 75       |

| ENQ        | 10000101                        | 0205                    | 00101101                 | 0055                  | 101101                  | 55       |

| EOT        | 00000100                        | 0004                    | 00110111                 | 0067                  | 011110                  | 36       |

| DLE        | 00010000                        | 0020                    | 00010000                 | 0020                  | 011111                  | 37       |

| Ø #2       | 10110000                        | 0260                    |                          |                       |                         |          |

| 1 #2       | 00110001                        | 0061                    |                          |                       |                         |          |

| ; #2       | 00111011                        | 0073                    |                          |                       |                         |          |

| '70' #2 #3 |                                 |                         | 01110000                 | 0160                  |                         |          |

| / #2       |                                 |                         | 01100001                 | 0141                  |                         |          |

| - #2       |                                 |                         |                          |                       | 100000                  | 40       |

| Т #2       |                                 |                         |                          |                       | 100011                  | 43       |

| W #2       |                                 |                         |                          |                       | 100110                  | 46       |

| < #2       | 10111100                        | 0274                    |                          |                       |                         |          |

| @ #2       |                                 |                         | 01111100                 | 0174                  |                         |          |

| 2 #2       |                                 |                         |                          |                       | 110010                  | 62       |

| STX        | 00000010                        | 0002                    | 00000010                 | 0002                  | 001010                  | 12       |

| ITB        | 00011111                        | 0037                    | 00011111                 | 0037                  | 011101                  | 35       |

| ETB        | 10010111                        | 0227                    | 00100110                 | 0046                  | 001111                  | 17       |

| ETX        | 10000011                        | 0203                    | 00000011                 | 0003                  | 101110                  | 56       |

| SOH        | 00000001                        | 0001                    | 00000001                 | 0001                  | 000000                  | 00       |

| , #2       |                                 |                         | 01101011                 | 0153                  |                         |          |

| NOTES: 1.  | stored in one<br>digit octal nu | memory loc              | ation. Each r            |                       |                         |          |

|            |                                 | st memory po            |                          | memory pos            | ition                   |          |

| 2.         | These charac                    | ters are use            | d only in the t          | wo character          | r sequences b           | pelow:   |

|            |                                 | ASCII                   | EBCDI                    | <u>C</u> <u>Six</u> . | -Bit Transco            | de       |

|            | ACKØ<br>ACK1<br>WACK            | DLE Ø<br>DLE 1<br>DLE ; | DLE '7<br>DLE /<br>DLE , |                       | DLE -<br>DLE T<br>DLE W |          |

Table 2-1. BSC Line Control Characters

3. '70' is a hexadecimal number representation of an unassigned EBCDIC code character.

DLE <

RVI

DLE @

DLE 2

| Table 2-2. | Control | Character | Summary |

|------------|---------|-----------|---------|

|------------|---------|-----------|---------|

| Character         | Name                             | No. Required | Action of Communication Control <sup>1</sup>                                                                                       |

|-------------------|----------------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------|

| SYN               | Synchronization<br>Character     | 3 (minimum)  | (R) Used to achieve and maintain synchronization. Not transferred to the central processor and not entered into BCC computation.   |

| SOH               | Start-of-Heading                 | 1            | (R) If synchronization is established, SOH is tranferred to the cen-<br>tral processor with all of the following characters.       |

|                   |                                  |              | (T and R) If first SOH or STX of a message, BCC accumulation is reset, and is restarted with the following character.              |

| STX               | Start-of-Text                    | 1            | (R) This and all following characters are transferred to the central processor, if synchronization is already established.         |

|                   |                                  | -            | (T and R) BCC accumulation is reset, and is restarted with the following character, if this is the first STX or SOH of the message |

| etx <sup>2</sup>  | End-of-Text                      | 1            | (T and R) Causes an interrupt.                                                                                                     |

|                   |                                  |              | (T) BCC accumulation is transferred immediately following ETX.                                                                     |

|                   |                                  |              | (R) BCC check is made with character(s) received immediately following ETX.                                                        |

| EOT <sup>2</sup>  | End-of-                          | 1            | (T and R) Causes an interrupt.                                                                                                     |

|                   | Transmission                     |              | (R) Transferred to the central processor.                                                                                          |

| enq <sup>2</sup>  | Enquiry                          | 1            | (T and R) Causes an interrupt.                                                                                                     |

|                   |                                  |              | (R) Transferred to the central processor.                                                                                          |

| nak <sup>2</sup>  | Negative                         | 1            | (T and R) Causes an interrupt.                                                                                                     |

|                   | Acknowledgment                   |              | (R) Transferred to the central processor.                                                                                          |

| ACKØ <sup>2</sup> | Positive                         | 1            | (T and R) Causes an interrupt.                                                                                                     |

| ACK1 <sup>2</sup> | Acknowledgment                   |              | (R) Transferred to the central processor.                                                                                          |

| ITB               | Intermediate<br>Block            | 1            | (R) Causes an interrupt in the transparent mode only. Transferret to the central processor.                                        |

| ETB <sup>2</sup>  | End-of-<br>Transmission<br>Block | 1            | Same as ETX. Both ETX and ETB are transferred to the central processor.                                                            |

| Table 2-2 | (cont). | Control | Character | Summary |

|-----------|---------|---------|-----------|---------|

|-----------|---------|---------|-----------|---------|

| Character         | Name                        | No. Required | Action of Communication Control <sup>1</sup>                                     |

|-------------------|-----------------------------|--------------|----------------------------------------------------------------------------------|

| DLE               | Data Link Escape            | l or 2       | Provides auxiliary control information, depending on the character that follows. |

| WACK <sup>2</sup> | Wait before<br>Transmission | 1            | (T and R) Causes an interrupt.<br>(R) Transferred to the central processor.      |

|                   |                             |              |                                                                                  |

~

$^{1}$ T = Transmission, R = Reception.

$^{2}$ Reception or transmission of these characters causes a line turnaround.

while transmitting, it sends SYN characters as a time-fill to prevent the receiving communication control from interpreting the lack of data as a transmission that has been interrupted prematurely.

#### Start-of-Heading (SOH) Character

The Start-of-Heading (SOH) character precedes a block of heading characters, and signals its beginning. The heading consists of a sequence of characters which constitutes the auxiliary information (such as routing and priority) necessary for the communication of the text portion of the message. If synchronization has been established, the SOH character and all subsequent heading, control, and data characters are transferred to memory (until an end character is recognized).

#### Start-of-Text (STX) Character

The Start-of-Text (STX) character precedes a block of text characters and signals the beginning of a data block. The data block constitutes that portion of the message that is treated as an entity, and transmitted through to its ultimate destination without change. If synchronization has been achieved, the STX character and all subsequent data characters are transferred to memory (until the recognition of an end character, which is also transferred to memory). Such a sequence is called "text."

The STX character can also be used to terminate a sequence of heading characters started by an SOH.

#### End-of-Text (ETX) Character

The End-of-Text (ETX) character terminates a data block. A block check character is transmitted immediately following the ETX character, and a status reply (ACK0, ACK1, NAK, or WACK) is expected from the receiving terminal. The ETX character is transferred to memory.

The ETX character is only used to end the <u>last</u> block of <u>text</u> in a message. All other blocks are ended by an ETB character (see the following paragraph).

#### End-of-Transmission Block (ETB) Character

The ETB character signals the end of a transmission block (heading or text) to which a status reply (ACK $\emptyset$ , ACK1, NAK, or WACK) is expected from the receiving terminal. The blocking structure is not necessarily related to the processing format. The block check character is sent immediately following the ETB character. The ETB is transferred to memory.

#### End-of-Transmission (EOT) Character

The EOT character signals the conclusion of a transmission, which may have contained one or more messages, consisting of one or more text blocks and any associated heading and responses. The EOT character is supplemented by a DLE-EOT sequence, known as the "mandatory disconnect," in switched-network operation.

#### Enquiry (ENQ) Character

The ENQ character is used in requesting a response, such as the identification or status (ACK $\emptyset$ , NAK, etc.), from the receiving remote terminal. The ENQ character can also be used to obtain a repeat transmission of a reply, if transmission was not received when expected or if it was garbled. When used in text, the ENQ character signifies the abnormal end of the text being transmitted. This is known as the abort sequence.

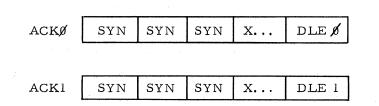

#### Positive Acknowledgment Sequences (ACKØ and ACK1)

Binary synchronous communication (BSC) employs two positive acknowledgment sequences referred to as ACK $\emptyset$  and ACK1. These are the 2-character sequences defined in note 2 of Table 2-1. The responses are used alternately in response to text transmission. ACK1 is the response to the first text transmission and to successive odd-numbered blocks during the transmission. ACK $\emptyset$  is the response to the second text block and to all even-numbered blocks.

These sequences indicate that the previous block was accepted and that the receiver is ready to accept the next block of transmission. Alternating positive acknowledgments (DLE sequences) must be transmitted.

#### Negative Acknowledgment (NAK) Character

The NAK character indicates that the previous block was unacceptable (an error was detected) and that the receiver is ready to accept a retransmission of that block. It is also the "not ready" reply to a terminal selection.

#### Data Link Escape (DLE) Character

The DLE character changes the meaning of a limited number of contiguous following characters. It is used exclusively to provide supplementary line control signals, which include Wait Before Transmitting (WACK), affirmative acknowledgments (ACKØ and ACK1), and start of transparent text (the sequences DLE STX and DLE ETX initiate and terminate transparent text). DLE EOT is used as a mandatory disconnect control sequence (in switched network operation). Other control sequences using DLE are available to provide active control characters within transparent text as required (see Section IV). DLE is normally sent as a single character; however, in transparent mode it is sent twice when a bit pattern in the data corresponds to the DLE character. In this case, the first DLE is "thrown away" by the control, and the second DLE is considered a data character. This doubling of DLE characters is done automatically by the transmitting control.

#### End-of-Intermediate-Block (ITB) Character

The ITB character signals (1) the end of an intermediate block of data, and (2) that the next character is the BCC character to be used to check for errors in that block. No response is transmitted to an ITB, but the character is transferred to memory and the BCC character is processed normally for an error check. The result is stored in the communication control or adapter and reported when the entire block of data is received. The central processor will therefore receive only one status report, which will be for the entire block of data just received.

The use of the ITB character allows the program to break up a long block of data into more easily handled intermediate blocks; however, an error in any intermediate block will necessitate the retransmission of the whole block. The US character (in ASCII and Six-Bit Transcode) and the IUS character (in EBCDIC) are used as the ITB character, since the ITB character is not directly provided in any of these codes.

#### Longitudinal Redundancy Check (LRC) and Cyclic Redundancy Check (CRC) Characters

The LRC or CRC character is transmitted or checked by the communication control immediately following an end character. Their composition and significance are discussed in the paragraph entitled "Error Control" (see page 2-10). They are not transferred to the central processor.

#### Wait Before Transmitting (WACK) Character

The WACK character allows the receiving terminal to indicate a temporary "not able to receive" condition to the transmitting terminal. It is sent as a positive acknowledgment to a text or heading block. The normal transmitting terminal response to WACK is ENQ; however, EOT and DLE EOT are also valid responses. When ENQ is received, the receiving terminal may continue to respond with WACK until it is ready to receive further data transmissions.

#### Reverse Interrupt (RVI) Sequence

The RVI control sequence is used in place of the ACKØ or ACK1 positive acknowledgment. RVI is transmitted by a receiving terminal to request termination of the current transmission because of a high priority message which it must transmit to the sending station, or, in a multipoint environment, because it now wishes to communicate with another station on the line. Successive RVI's cannot be transmitted except in response to ENQ.

2-8

The transmitting terminal treats RVI as a positive acknowledgment and responds by transmitting all data that prevents it from becoming a receiving station. To accomplish this, more than one block transmission may be required.

#### Temporary Text Delay (TTD) Sequence

The TTD control sequence (STX ENQ) is sent by a transmitting terminal when it wishes to retain the line but is not ready to transmit. STX ENQ should be sent when the TTD timeout occurs (approximately two seconds after the end of reception of the last reply). This 2-second timeout avoids the nominal 3-second receive timeout at the receiving terminal.

The receiving terminal must respond with a NAK to the TTD sequence, and wait for transmission to begin. If the transmitting terminal is still not ready to transmit, the TTD sequence can be repeated one or more times. It should be noted that any 281-2BSC communication control receiving a TTD sequence will signal the central processor that an abort has been received. Therefore, it is necessary that the program distinguish this sequence from an actual abort.

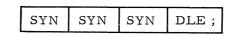

#### Pad Characters

To insure that the last character of a transmission is properly transmitted by the data set, all 281-2BSC controls and 285-2BSC adapters add a pad character after each transmission. Since ETB or ETX causes a line turnaround, the pad character follows the BCC. The trailing pad character ensures that the last significant character (for example ETB BCC, ETX BCC, NAK, EOT, ENQ, etc.) is sent before the data set transmitter turns off. The pad character is not transferred to the central processor.

It is suggested that the communications program add a pad character before the beginning synchronization sequence (the three SYN characters) of all transmissions to ensure that the data set is turned on and transmitting. This leading pad character can be another SYN character.

An example of block padding is shown below.

|     |     | 2   |     |     |      |     | -   | 3   |

|-----|-----|-----|-----|-----|------|-----|-----|-----|

| SYN | SYN | SYN | SYN | STX | TEXT | ETX | BCC | PAD |

In the example above, the SYN character designated "1" is the leading pad character added by the communications program. The three SYN characters designated "2" comprise the required synchronization pattern provided by the program. The character designated "3" is the trailing pad character added by the communication control.

#### CHARACTER FORMAT

#### Line Format

The 281-2BSC and 285-2BSC are capable of transmitting or receiving any 8-bit or 6-bit character, depending on the code chosen prior to the time of installation. In 8-bit operation, the character can be in any code with odd parity in the eighth bit, such as ASCII, or any code without parity, such as EBCDIC. In 6-bit operation, the character can be in any 6-bit code without parity.

#### Memory Allocation

If 8-bit operation is chosen, each character occupies two positions in main memory; if 6-bit operation is chosen, each character occupies one position. When an 8-bit character is stored, bits 1 through 6 occupy positions 1 through 6 of the second character position. Bits 7 and 8 occupy positions 1 and 2 of the first character position.

#### Variable Character Recognition

The 281-2BSC and 285-2BSC recognize and react to ten control characters and the twelve 2-character control sequences defined by BSC operating procedures. The control characters are selected prior to communication control installation. The 2-character sequences are comprised of control characters or, in some instances, of a control character and one of four data characters (which are also selected prior to installation).

It is important to note that character recognition cannot be changed by programming. The data characters selected only cause control action when they are immediately preceded by the control character DLE. The bit patterns and octal equivalents for the control characters, as defined for ASCII, EBCDIC, and Six-Bit Transcode, are presented in Table 2-1.

#### ERROR CONTROL

Error control is maintained by combining error detection with retransmission of messages until they are received error-free. The communication control performs the error detection function while the program must provide the necessary retransmission capabilities. Each block of data transmitted can be error-checked in any of several ways, depending on the codes and functions employed. Three major methods of error detection are employed in BSC: odd parity checking by the vertical redundancy check (VRC); message block checking by the longitudinal redundancy check (LRC); and the cyclic redundancy check (CRC). Checking is always done at the receiving terminal. In VRC checking, this occurs on a character-by-character basis as each character is received. The block check character (BCC), either LRC or CRC, is accumulated identically at both the transmitting and receiving terminals, for each block of data transmitted. The transmitting communication control transmits the BCC immediately following an ETB, ETX, or ITB character. The receiving control compares its accumulated BCC against the transmitted BCC for an equal condition, which indicates that the previous block was properly received. The results of the comparison are reported to the central processor via an interrupt, but the BCC is not transferred to the central processor. The basic ground rules for accumulating the BCC in any form are:

- 1. Reset accumulation to all zeros on the first STX or SOH character of the message after line turnaround.

- 2. Accumulate all characters that follow the first STX or SOH, except SYN characters.

- 3. In the transparent mode, following DLE STX, do not accumulate the first DLE of any 2-character control sequence.

- 4. Reset accumulation to all zeros following an ITB BCC, and restart accumulation with the first non-SYN character that follows.

The combinations of the three error checks that are used depend on the code employed and, in the case of ASCII and other similar codes (7 bits plus parity), whether transparent transmissions are to be allowed.

Table 2-3 lists the combinations available in the 281-2BSC and 285-2BSC. After each transmission, the receiving terminal replies with ACK $\emptyset$  or ACK1 (data accepted—continue sending) or NAK (data not accepted—retransmit previous block), depending on the results of the check. Retransmission of a block of data following an initial NAK is usually attempted at least three times. If the transmitting terminal does not receive a reply to a data block, or if the reply is garbled, the transmitting terminal can request retransmission of the reply by sending ENQ.

| na n                                                                                                                                                                                                                                                                                                        | Type of Checking                               |                                             |                                                 |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|---------------------------------------------|-------------------------------------------------|--|--|--|--|

| Transmission<br>Code                                                                                                                                                                                                                                                                                                                            | Transparency Not<br>Programmed                 | Transparency<br>Programmed and<br>Operating | Transparency<br>Programmed but<br>Not Operating |  |  |  |  |

| EBCDIC                                                                                                                                                                                                                                                                                                                                          | CRC-16                                         | CRC-16                                      | CRC-16                                          |  |  |  |  |

| ASCII                                                                                                                                                                                                                                                                                                                                           | VRC/LRC                                        | CRC-16                                      | VRC/CRC-16                                      |  |  |  |  |

| Six-Bit<br>Transcode                                                                                                                                                                                                                                                                                                                            | CRC-12                                         | CRC-12                                      | CRC-12                                          |  |  |  |  |

| NOTES: 1. No 281-2BSC communication controls and 285-2BSC communication<br>adapters that work with EBCDIC or Six-Bit Transcode need to be<br>programmed to allow transparent transmissions; ASCII controls<br>and adapters must be programmed to allow transparent trans-<br>missions, due to the different error-checking procedures employed. |                                                |                                             |                                                 |  |  |  |  |

| <ol> <li>The error checking methods are defined as follows:</li> <li>VRC Vertical redundancy check (odd parity on each character)</li> </ol>                                                                                                                                                                                                    |                                                |                                             |                                                 |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                 | LRC Longitudin                                 | al redundancy check                         |                                                 |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                 | CRC-16 Cyclic redundancy check (using 16 bits) |                                             |                                                 |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                 | CRC-12 Cyclic red                              | undancy check (using 12                     | bits)                                           |  |  |  |  |

Table 2-3. Error Checking Capabilities

#### VRC/LRC Combination

This combination of error checking methods is available only on those communication controls that operate with ASCII or similar codes (7 data bits plus one parity bit) and that are programmed not to handle transparent mode messages.

Vertical redundancy checking (VRC) is an odd-parity check performed on a per-character basis. The 281-2BSC accepts the seven data bits from memory and generates the eighth bit (parity bit) when transmitting. When receiving, the parity check is performed as each character is received; all eight bits are transferred to memory.

The longitudinal redundancy check (LRC) is a Block Check Character (BCC) that is accumulated from all the characters in the message block. The accumulation is performed both by the transmitting and receiving controls by modulo-2 half-adding each data bit position of each character of a message block to the corresponding data bit position of the LRC character. The transmitting control transmits the LRC character immediately following an ETB, ETX, or ITB character. The receiving control compares the transmitted BCC against its accumulated BCC for an equal condition, which indicates that the previous block was received without a block check error. The transmitting control generates an odd-parity bit for the 7-bit LRC character and the receiving control checks for odd parity in the LRC character. The LRC character is not transferred to memory, but the results of the comparison are reported to the central processor via an interrupt.

The LRC accumulation is reset to zero by the first SOH or STX character received in a transmission. All STX or SOH characters received thereafter, until the next line turnaround, are included in the accumulation. The accumulation is also reset to zero following an ITB BCC.

#### Cyclic Redundancy Check (CRC-12/CRC-16)

Cyclic redundancy checking (CRC) is a more powerful method of block checking than LRC. Two modes of CRC are employed with BSC. The first, CRC-12, is used for 6-bit transmission codes (such as Six-Bit Transcode); the second, CRC-16, is used for 8-bit transmission codes (EBCDIC and similar codes).

A cyclic redundancy check is a division performed by both the transmitting and receiving controls using the numeric binary value of the message as a dividend, which is divided by a constant. The quotient is discarded, and the remainder serves as the check character, which is then transmitted as the block check character immediately following an ITB, ETB, or ETX character. The receiving control compares the transmitted remainder to its own remainder, and finds no error if they are equal.

The 281-2BSC and the 285-2BSC use the polynomial  $x^{16} + x^{15} + x^2 + 1$  for the constant when performing a CRC-16 check. They use the polynomial  $x^{12} + x^{11} + x^3 + x^2 + x + 1$  when performing a CRC-12 check.

With these forms of block checking, the block check character actually consists of two characters (i.e., 16 bits for CTC-16 and 12 bits for CRC-12) when it is transmitted on the line.

#### VRC/CRC-16 Combination

This is a combination of VRC and CRC used by communication controls operating with ASCII and similar codes (7 data bits plus one parity bit) that are programmed to handle transparent mode transmissions. The VRC is inhibited during transparent operation and the communication control accepts all eight bits from memory when transmitting. The 16-bit CRC generator is used in both the normal and transparent modes.

#### Format Errors

A format error is defined as any sequence of communication control characters that is not defined by BSC procedures. Format errors are checked on a block-by-block basis, but are not checked through a line turnaround. (For example, the communication control does not report an erroneous replay as a format error if the format of the reply follows a correct BSC format.) See Figure 2-1 for legal formats.

Format errors cause an interrupt at the end of a received or transmitted message. If the communication control is transmitting, the "sent illegal message" flag is turned on. If the control is receiving, the "received illegal sequence" flag is turned on.

#### Overwrite

If a character contained in the Type 281-2BSC Communication Control's receive buffer is overwritten (by another character being received), an appropriate status signal is turned on and, at the end of reception of the data block, the central processor is notified via an interrupt. The Type 285-2BSC Communication Adapter is also subject to character overwrite; if this occurs, the overwrite status will be transferred to the Type 286-6 or -7 multi-channel communication control at the end of reception. The program must always transmit a reply of NAK to any data block received with an overwrite error.

#### TIMEOUTS

Timeouts are used during the reception and transmission of control (ID) heading and text data to ensure efficient utilization of transmission facilities. They prevent indefinite tie-ups caused by illegal sequences or missed turnaround signals (ETB, ETX, etc.). The timeouts provide a fixed time within which any particular operation must occur. Six timeout functions are provided: transmit, receive, inactivity, underflow, text, and text delay.

#### Transmit Timeout

This is a 1-second timeout that establishes the rate at which idle SYN characters are inserted automatically into transmitted headings and text data. In normal data transmission, two consecutive SYN characters are inserted for timing purposes only, and they have no effect on the message format. The programmer can insert extra idle characters into normal data, but cannot do so in transparent data.

#### Receive Timeout

This 3-second timeout limits the turnaround reply interval and is used as follows:

1. It limits the waiting time for a transmitting terminal to receive a reply after a line turnaround.

2. It permits the receiving terminal to check the line for idle characters. These idle characters indicate that the transmission is continuing and that character synchronization has been maintained. Thus, this timeout is restarted each time an idle character is detected. If a timeout occurs, the communication control initiates an interrupt by turning on the "loss of sync" status signal, and starts to scan for SYN characters. An "end-of-order" status signal is also sent to the central processor when this timeout occurs.

#### Inactivity Timeout

This is a nominal 30-second timeout that protects against prolonged periods of inactivity. The timeout is started when the "interlock" signal from the data set goes on. If, during the 30-second timeout period, no data is received or transmitted, the communication control will notify the central processor via an interrupt.

#### Underflow Timeout

This is a nominal 30-millisecond timeout that indicates a loss of data from either the central processor or the data set. If the communication control is transmitting and does not receive data from the central processor for a period equal to the length of this timeout, an interrupt occurs to notify the central processor that the communication control has transmitted an abort. If the communication control is receiving and the data set does not indicate that it is receiving a character during the timeout period, character synchronization is dropped, an interrupt occurs, and the 281-2BSC or 285-2BSC starts to scan for synchronization characters.

#### Text Timeout

This optional timeout is available for use as a "reasonableness" test for the length of heading or text data (i.e., the transmitted or received block of data). It is started when the communication control achieves character synchronization. It runs for a period determined by the user (prior to installation). Honeywell suggests that this period be approximately 15 seconds (equal to the time necessary to transmit 4500 8-bit characters using a Bell System 201B data set). If an end-of-block character (ETB, ETX, etc.) is not received during the timeout period, the communication control or adapter disconnects and initiates an interrupt.

#### Text Delay Timeout

This is a nominal 2-second timeout associated with the transmission of TTD and WACK sequences. It is used where the speed of input or output devices may cause transmission delays. This timeout starts at the end of a reception and runs until (1) a transmission is started, or (2) it runs out and causes an interrupt.

If the interrupt occurs at the transmitting terminal, it requests that the central processor start sending a message. If the interrupt occurs at the receiving terminal, it requests that the reply that was to be sent be delayed until the ENQ from the transmitting terminal is received.

# SECTION III OPERATION

#### POINT-TO-POINT OPERATION

A point-to-point data link consists of a communication facility between two terminals. All transmissions over the data link must be between the two terminals operating on that data link. The point-to-point link can be established over leased, nonswitched communication lines or a switched network. On a leased line (permanent-type connection), the transmissions are always between the same two terminals. On a switched network, the data link is disconnected after the two terminals complete their transmission; a new data link is established for subsequent transmissions by standard dialing procedures (either manual or automatic). The new data link can be established with any other terminal in the network.

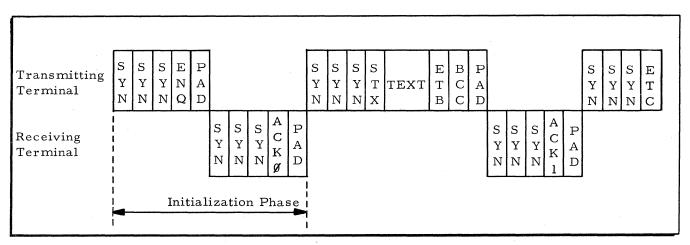

#### Point-to-Point Operation with Contention

When operating on a nonswitched, point-to-point network the connection is made by either privately owned lines or leased private lines. When transmission is started, an initialization sequence (SYN SYN SYN ENQ) must be instituted by the terminal attempting to acquire the line. A terminal receiving this sequence (and ready for message reception) replies with an affirmative acknowledgment sequence (SYN SYN SYN ACK0). If the station is not ready for reception, it replies with either of the following: (1) SYN SYN NAK (not ready to receive); or (2) SYN SYN WACK (temporarily unable to receive). The format for the complete initialization phase, including the start of the actual message transmission if shown in Figure 3-1.

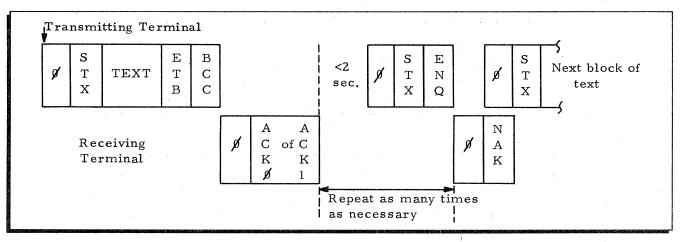

Figure 3-1. Point-to-Point Initialization Phase

To avoid the problems associated with simultaneous transmission requests, each terminal is assigned a primary or secondary priority. The higher priority (primary) terminal sends an ENQ to acquire the idle line; it continues to send ENQ until it receives an affirmative response or until the retry limits of the primary terminal are reached. If the primary terminal receives an ENQ and it has not initiated a request for the line, then it replies with ACKØ (ready to receive), WACK (temporarily unable to receive), or NAK (not ready to receive). Thus the secondary terminal can gain control of the line for transmission only when the line is left free by the primary terminal.

Message transmission is ended and the line is returned to an idle state by the transmission of EOT. The terminal sending EOT must not send an initialization sequence until three seconds have elapsed, thus allowing the other terminal to bid for the line.

#### Switched Network Operation

When operating in a switched network, the point-to-point connection is established by either manual or automatic means. Dialed connections are operated as a point-to-point line with contention. Both terminals begin in the circuit assurance mode. Once circuit assurance is established and identification (optional) is completed, the terminals use the normal BSC procedures required for operation (switched point-to-point). A disconnect signal is normally sent when both terminals have completed their message transmissions.

The circuit assurance mode is entered when the called terminal goes off-hook. At this time, the calling terminal is notified by a signal from its data set that a connection with another data set has been established. Once this indication is received, the calling station sends either of the following messages:

- 1. WRU-Who are you? The transmitted sequence is SYN SYN SYN ENQ.

- 2. IAM/WRU-I am X..., who are you? The transmitted sequence is SYN SYN SYN X... ENQ. "X" indicates the graphics for terminal identification and supplementary control purposes. This message identifies the calling terminal and requests the called terminal to identify itself.

Either message is then followed by an identification message from the called station: ID ACKØ. (The transmitted sequence is SYN SYN SYN X... ACKØ where ID is optional.)

NOTE: If the received ID is unsatisfactory, either terminal can initiate a disconnect sequence.

Additional signals available as a reply to the WRU and IAM/WRU messages are:

- 1. NAK This reply indicates that a "not ready" condition exists at the called station.

- 2. WACK (optional) This reply indicates that a "temporarily not ready to continue" condition exists at the called station.

BSC communication programs used with the 281-2BSC or 285-2BSC should provide the capability to transmit identification sequences in order to permit several types of BSC terminals to operate on the same switched line. An ID sequence can be from 2 to 15 characters long. The minimum 2-character sequence consists of the same character transmitted twice. All BSC communication programs at receiving terminals should be capable of recognizing control sequences regardless of the presence of leading graphics; the terminal's specifications determine whether the terminal will attach any functional significance to these characters or will have the ability to transmit them.

Both terminals exit from the circuit assurance mode when any of the following sequences are sent or received:

- 1. SYN SYN SYN EOT This sequence returns the data link to normal operation (the passive monitoring mode in which either terminal may bid for the line).

- 2. SYN SYN SYN SOH This sequence initiates a block of heading data.

- 3. SYN SYN SYN STX This sequence initiates a block of text data.

- 4. SYN SYN SYN DLE STX This sequence initiates a block of transparent text data.

All signals other than those described are considered to be errors. If a valid reply is not received by the calling station (following either a WRU or an IAM/WRU) within the receive timeout period, the request message can be retransmitted. However, the data link continues in circuit assurance mode until the circuit assurance sequence is satisfactorily completed.

The call between stations can be terminated by the inactivity timeout or by transmission of the disconnect sequence SYN SYN DLE EOT. This sequence may be initiated by either terminal when operating on a switched network basis. When operating with a control terminal, the control terminal normally initiates the disconnect sequence. As this sequence is transmitted and received, each terminal returns to an on-hook condition and the line is dropped.

For switched network operation, procedures should be provided to permit the connection to be broken and re-established (by hanging up and redialing the number) whenever transmission difficulties are experienced. This procedure provides the opportunity for establishing a totally different communication path, which may improve transmission capabilities, when the connection is re-established.

#### MULTIPOINT OPERATION

A multipoint data link consists of communication facilities between three or more terminals on privately owned or leased private lines. In the multipoint network, one terminal is designated as the control terminal, and the remaining terminals are designated as tributary terminals. All transmissions for this type of operation are regulated via the control terminal by means of polling or selection. By sequentially polling each tributary terminal, the control terminal directs the incoming message traffic. The outgoing traffic is regulated from the control terminal by selection of the desired tributary terminal, which receives the message. All transactions are between the control terminal and the selected tributary terminal.

The initialization phase for multipoint operation is accomplished by the control station transmitting the following sequence: SYN SYN EOT PAD SYN SYN SYN (polling or selection address) ENQ PAD. This sequence ensures that all monitoring tributary terminals are now in the control mode and are thus prepared to receive either a poll or a selection from the control terminal.

The polling or selection sequence transmitted while in the control mode designates the terminal that is to transmit or receive data. This sequence can also define the specific device required, if the terminal has several available. The recognition of the polling and selection sequences is performed by the program in the central processor. All action taken on the data contained in the selection or polling sequences must be initiated by the central processor. An example of the complete sequence transmitted from the control terminal is shown in Figure 3-2.

The polling and selection sequences, consisting of from one to seven characters, are followed by ENQ. For specific sequences, the appropriate terminal specifications should be considered.

The possible replies from a polled tributary terminal are:

- 1. Heading data SYN SYN SYN SOH...

- 2. Text data SYN SYN SYN STX ...

- 3. Transparent text data SYN SYN SYN DLE STX transparent text...

- 4. Negative reply when the terminal has nothing to send SYN SYN SYN EOT.

- 5. Temporary text delay when the terminal is unable to transmit its initial block within two seconds SYN SYN SYN STX ENQ.

The possible replies from a selected tributary terminal are:

- 1. Affirmative reply indicating that the tributary terminal is prepared to receive SYN SYN SYN ACKØ.

- 2. Negative reply indicating that the tributary terminal is not ready to receive SYN SYN SYN NAK.

- 3. Reply indicating that the tributary terminal is temporarily unable to receive SYN SYN SYN WACK.

#F11

The complete formatting of message traffic for a multipoint operation is shown in Figures 3-2 and 3-3 (polling and selection with respect to two different tributary terminals by the control terminal). The terminal identification for the two different operations is indicated by using upper case alphabetic characters for polling and lower case alphabetic characters for selection (for these examples). The component designations are 1 (for printer) and 6 (for reader) in these examples.

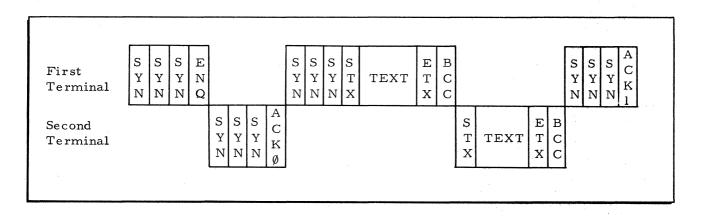

#### LIMITED CONVERSATIONAL MODE

This mode allows the transmission of heading or text data in reply to a complete message. A conversational reply can be sent in place of an affirmative reply to a block of text that ends with ETX or DLE ETX. Conversational replies are not permitted following a block of heading or blocks of text ending with ETB.

Either SOH or STX can start a conversational reply. The terminal receiving the conversational reply interprets the SOH or STX as the affirmative reply to the last data block it transmitted. Transparent text (beginning with DLE STX) is also a valid conversational reply. A terminal receiving a conversational reply is not permitted to respond by transmitting another conversational reply. An example of the limited conversational mode is given in Figure 3-4.

Figure 3-4. Limited Conversational Mode

The limited conversational mode of operation can be used on any network as long as all the terminals in the network realize that this mode of operation is to be used. This mode will most likely be used in networks where a remote terminal and a central processor must swap operating parameters before beginning the communication sequence. When and if this mode is to be used, it will be spelled out in the network specifications; it is mentioned here only to inform the reader that such a mode of operation exists.

#### SECTION IV

#### PROGRAMMING INFORMATION

#### INTERRUPT PROCESSING

The Type 281-2BSC Communication Control (and the Type 285-2BSC Communication Adapter when used with a Type 286-6 or -7 Communication Control) turns on an interrupt signal when it has a message status to report to the central processor. Upon interrupt, the central processor tests the state of the interrupt signal by an appropriate PCB (Peripheral Control and Branch) instruction. Since it is possible for more than one condition to cause an interrupt at any given time, it may be necessary to check all possible interrupt conditions by PCB instructions.

#### SYSTEM REQUIREMENTS

The central processor must be capable of being interrupted by the communication control. The control operates in the half-duplex mode; therefore, one read/write channel must be assigned to the communication control for the duration of the entire message.

#### Data Transfer

Each block of data to be transmitted must first be fully assembled in memory and transferred to the communication control character-by-character, as requested by the communication control, using a single PDT (Peripheral Data Transfer) instruction for the entire block. Similarly, in reception the entire block of data must be assembled in memory. When the communication control indicates error-free reception at the end of a block, the entire block should be transferred to the storage device using one PDT instruction.

For maximum line utilization, the memory area containing data to be transmitted should be double-buffered. That is, one buffer contains the last block of data transmitted (to be retransmitted if a NAK is received). The second buffer contains the next block of data to be transmitted if an ACK (positive acknowledgment) signal is received for the previous block. The second block can be prepared from storage while the first block is being transmitted. To prevent loss of information, buffering should also be adapted for reception. A block of data received accurately can be transferred to storage while the communication control is receiving the next block from the line.

#### SIX-LEVEL CODES

For a 6-level code, such as Six-Bit Transcode, each memory location in a block buffer will contain a 6-bit character which can be transferred to the communication control.

#### EIGHT-LEVEL CODES

For an 8-level code, such as EBCDIC, a character must be assembled in the communication control from two buffer locations. The two high-order bits of the coded character are contained in the two low-order positions of a buffer location, and are transferred to the communication control first. The six low-order bits of the character are contained in the next buffer location, and are transferred to the communication control next, as requested by the control. The same order is applicable for reception.

#### SEVEN-LEVEL CODES (PLUS PARITY)

For a 7-level code (plus parity), such as ASCII, the communication control behaves as it does for an 8-level code with the following differences:

- 1. In transmission the communication control generates parity; therefore, the buffer location that sends the high-order portion of the character to the communication control contains only one high-order bit (in its low-order position).

- 2. In reception the communication control checks for parity errors, but it transfers both the high-order and parity bits to the buffer as the high-order portion of the coded character.

The above differences apply equally to all characters, whether data or control characters, in a particular code.

#### PROGRAMMING

#### Initialization

To prepare the central processor and communication control for communication, the following initialization steps must be taken:

- 1. Issue an Initialize PCB instruction.

- 2. Issue a Turn On Allow PCB instruction.

- 3. Perform miscellaneous housekeeping, such as setting up any constants or fields necessary.

- 4. Keep a program running in the central processor so that it can be interrupted.

It is absolutely necessary that the communication controls that are to communicate with each other are code-compatible. If communication is attempted between two incompatible communication controls, error conditions will result.

#### Synchronization

Every transmitted message should begin with four SYN characters supplied by the program. This initial synchronizing sequence is the only one required from the program. All subsequent time-fill and transmit timeout synchronizing sequences are automatically generated by the communication control.

#### Data Transmission

Data is transmitted by issuing a Transmit PDT instruction to the communication control. The characters to be transmitted are extracted from memory using one memory cycle for a 6-bit code (Six-Bit Transcode) or two memory cycles for either an 8-bit code (EBCDIC) or a 7-bit code (ASCII). If two memory cycles are needed, the first cycle transfers the two highorder bits (or parity and high-order bit) of the character and the second cycle transfers the six low order bits.

NOTE: In normal mode transmissions of 7-bit codes, the parity bit received from memory is discarded and the parity bit calculated by the 281-2BSC is substituted. In the transparent mode, the parity bit position of 7-bit codes is used for data and the control accepts this bit position from memory. When receiving, the 281-2BSC always transfers all eight bits (eight data bits or seven data bits plus parity) to memory regardless of the mode of operation (except when operating with a 6-bit code). The 285-2BSC adapter operates in an identical manner except that it is the 286-6 or -7 communication control that generates the parity bit when necessary.

Regardless of the code set used, the necessary initial synchronization and framing characters (SOH, STX, ETB, ETX, etc.) must be supplied by the program

The transmit RWC (read/write channel) will be released in either of two conditions. The first is the transmission of a character that initiates a line turnaround. When this happens, an End-of-Order signal is transferred to the central processor and an interrupt follows with a status indicator that is dependent upon the status of the message transmitted. The second condition occurs when a record mark is encountered in memory. When this happens, an interrupt occurs with a status of "Frame Demand Out and No Order Stored." The communication control continues to transmit by inserting time-fill (SYN) characters into the void caused by the loss of the RWC until a new Transmit PDT instruction is issued. If a new PDT instruction is not issued within 30 milliseconds of the original interrupt, the "sent abort" status indicator is turned on and the communication control automatically aborts the message.

The transmission of transparent data proceeds in the same manner as the transmission of normal mode data. That is, the data is arranged in memory in 8-bit characters, such as EBCDIC and ASCII (the parity bit in ASCII-equipped communication controls is now used as a data bit), or 6-bit characters (Six-Bit Transcode) as it would be normally. The beginning characters (DLE STX) are inserted in front of the block of data and the ending sequence (DLE ITB, DLE ETB, or DLE ETX) is inserted at the end of the block of transparent data in the same manner as the SOH or STX characters and the ITB, ETB, or ETX characters would be for normal mode data.

In addition, a 12-bit binary number is inserted into the two line character positions immediately following the DLE STX sequence to define the number of line characters in the transparent text, exclusive of the beginning and ending sequence. This 12-bit binary number is used by the 281-2BSC or 285-2BSC to control some of its internal operations during transparent mode transmissions. It is the programmer's responsibility to see that this number is correct.

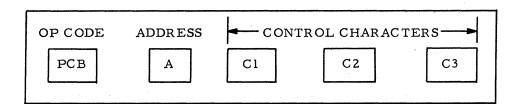

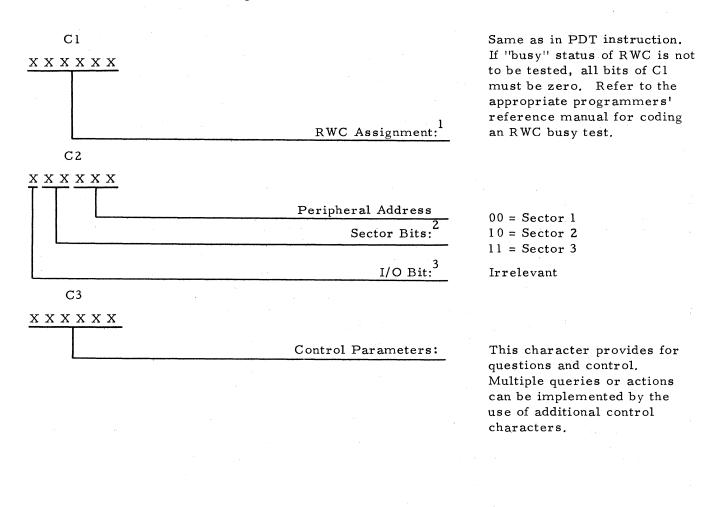

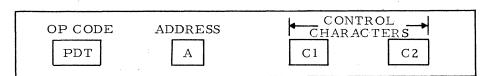

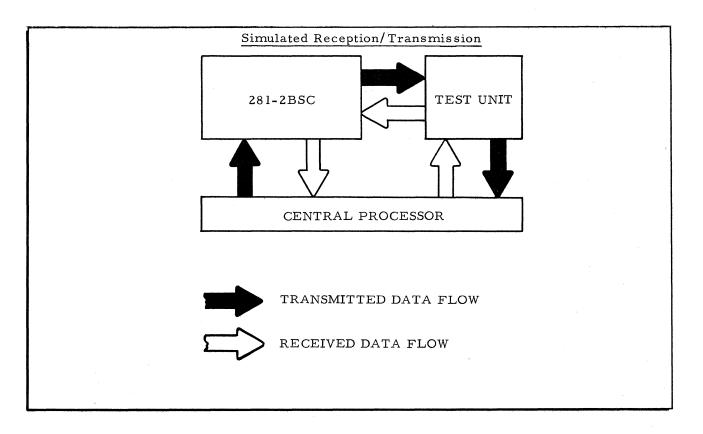

#### Control Sequences