# HONEYWELL EDP

# HARDWARE BULLETIN

# SERIES 200

# TYPE 286-4 AND TYPE 286-5 MESSAGE-MODE, MULTI-CHANNEL COMMUNICATION CONTROLS

#### SUBJECT:

SPECIAL INSTRUCTIONS: Equipment specifications for the Type 286-4 and Type 286-5 Message-Mode, Multi-Channel Communication Controls.

References used in this publication include the Honeywell Series 200 Programmers' Reference Manual (Models 200/1200/2200), Order No. 139, and the ASA document Control Procedure for Data Communications, X3. 3. 4/60, dated March, 1965.

DATE: June 30, 1966

FILE NO.: 112.0005.1124.0-270

8982 5666 Printed in U.S.A.

\*When ordering this publication please specify Title and Underscored portion of File Number.

## FOREWORD

The Type 286-4 or Type 286-5 Message-Mode, Multi-Channel Communication Control provides the interconnection of a Series 200 central processor with a maximum of 63 half-duplex communication lines via Type 285 Communication Adapters.

The communication control is compatible with all standard Series 200 central processors except the Models 201 and 201-1. The Model 121 central processor must be equipped with optional Feature 1015 or 1016 — see the <u>Honeywell Series 200 Programmers' Reference Manual</u> (Model 120), Order Number 141.

> Copyright 1966 Honeywell Inc. Electronic Data Processing Division Wellesley Hills, Massachusetts 02181

# TABLE OF CONTENTS

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                | Page                                                                                           |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| Section I   | Introduction<br>General Description<br>Interface with Series 200 Central Processors<br>Interface with Type 285 Communication Adapters<br>Secondary Bus.                                                                                                                                                                                                                                                                        | 1 -1<br>1 -2<br>1 -2                                                                           |

| Section II  | Type 286-4 and Type 286-5 System Considerations<br>American Standard Association (ASA) Compatibility<br>Read/Write Channel Assignments.<br>Stored Address Capabilities.<br>Data.<br>Throughput .<br>Rate of Data Transfer<br>Message Size<br>Synchronization for Synchronous Line<br>Start of Input Transfer for Asynchronous Lines                                                                                            | 2-1<br>2-1<br>2-1<br>2-1<br>2-1<br>2-1<br>2-1<br>2-1<br>2-2                                    |

| Section III | Functional Description .<br>Type 285 Communication Adapter.<br>Type 286-4, -5 Message-Mode, Multi-Channel Communi-<br>cation Control.<br>Data Transfer .<br>Memory Test Feature .<br>Memory Organization .<br>Scan Table .<br>Queues .<br>Line Control.<br>Present Command .<br>Present Address .<br>Present Recognition Characters .<br>Synchronization Character .<br>Synchronous Lines .<br>Next Command .<br>Line Status . | 3-1<br>3-1<br>3-2<br>3-2<br>3-2<br>3-2<br>3-3<br>3-3<br>3-4<br>3-4<br>3-4<br>3-4<br>3-5<br>3-5 |

| Section IV  | Programming Reference Data.<br>Operational States of the Type 286-4, -5<br>Initialized State<br>Load/Test State.<br>On-Line Operation<br>Inhibit Interrupt.<br>Off-Line State.<br>Interrupt Capability<br>Timing of Transmit Interrupts.<br>Timing of Receive Interrupts.<br>Interrupt Caused by Communication Control Parity Error.<br>Present Command Termination<br>Record Marks.                                           | 4-1<br>4-1<br>4-2<br>4-2<br>4-2<br>4-3<br>4-3<br>4-3<br>4-3<br>4-3<br>4-3                      |

# TABLE OF CONTENTS (cont)

# Section IV (cont)

Section V

|                                                 | Page |

|-------------------------------------------------|------|

| Location of Record Marks                        | 4-4  |

| Record Mark Effects                             | 4-4  |

| Parity                                          | 4-4  |

| Character Parity                                | 4-4  |

| Block Parity                                    | 4-5  |

| Transmit Mode                                   | 4-5  |

| Receive Mode                                    | 4-6  |

| Character Parity of the Block Parity Character  | 4-6  |

| Reset Block Parity Register                     | 4-7  |

| Control Unit Parity                             | 4-7  |

| Halt/Continue Control                           | 4-7  |

| Halt Condition                                  | 4-7  |

| Continue Condition                              | 4-7  |

| Peripheral Instructions                         | 4-8  |

| Peripheral Data Transfer (PDT) Instruction      | 4-8  |

| Peripheral Control and Branch (PCB) Instruction | 4-9  |

| Questions and Control of the Unit               | 4-10 |

| Questions and Control of a Line                 | 4-11 |

| Line Control Information PCB                    | 4-12 |

| Status Field                                    | 4-15 |

| Overwrite                                       | 4-16 |

| Scan Table                                      | 4-16 |

| Timer                                           | 4-18 |

| Character Location Feature                      | 4-19 |

| Programming Information                         | 5-1  |

| Control Unit Memory Sections                    | 5-1  |

| Memory Loading                                  | 5-1  |

| Scan Table Entries                              | 5-1  |

| Fixed Characteristics Entries                   | 5-3  |

| "Exit" PCB Instruction                          | 5-4  |

| Placing the Control Unit On-Line                | 5-4  |

| Intermediate Mode                               | 5-4  |

| Line Control Procedure                          | 5-5  |

| Start Transmission                              | 5-5  |

| Continual Transmission                          | 5-5  |

| Transmission Termination                        | 5-5  |

| Reception                                       | 5-6  |

| Continual Reception                             | 5-6  |

| End of Reception of a Message                   | 5-6  |

| Interpretation of the Status Field              | 5-6  |

| Character Location Feature                      | 5-7  |

|                                                 |      |

「「「「「「「」」」

# LIST OF ILLUSTRATIONS

|             |                                    | Page |

|-------------|------------------------------------|------|

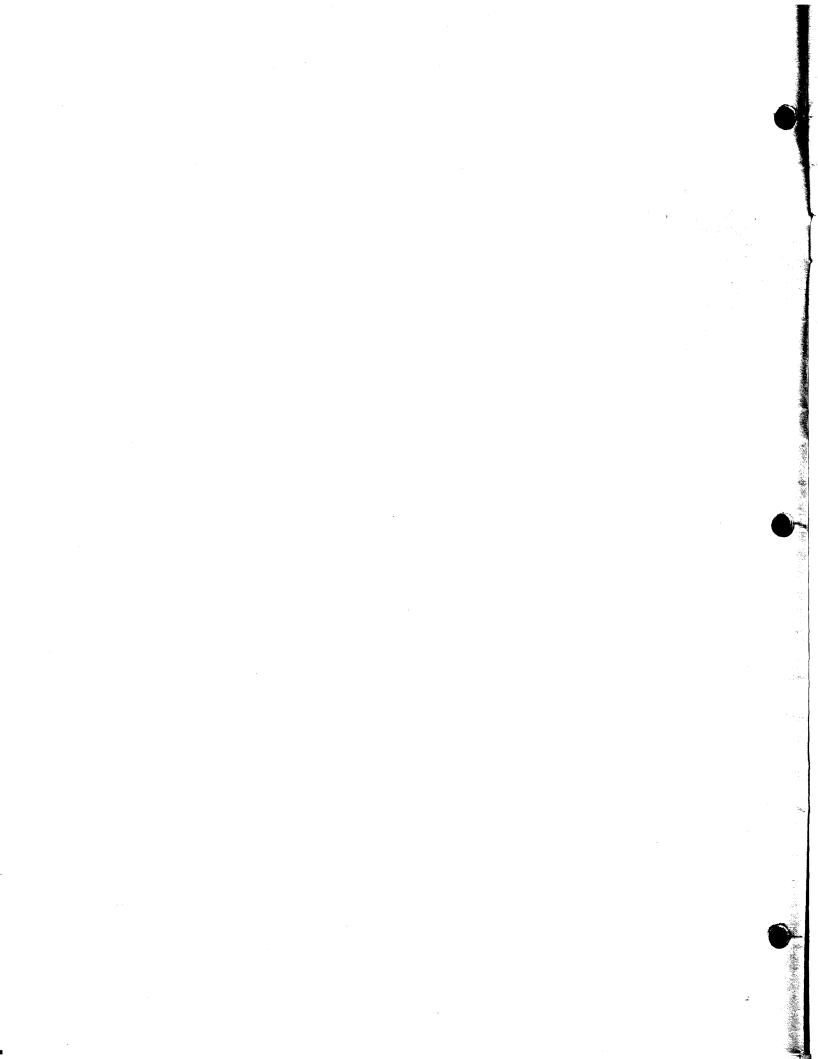

| Figure 1-1. | Types 286-4 and 286-5 Applications | 1-1  |

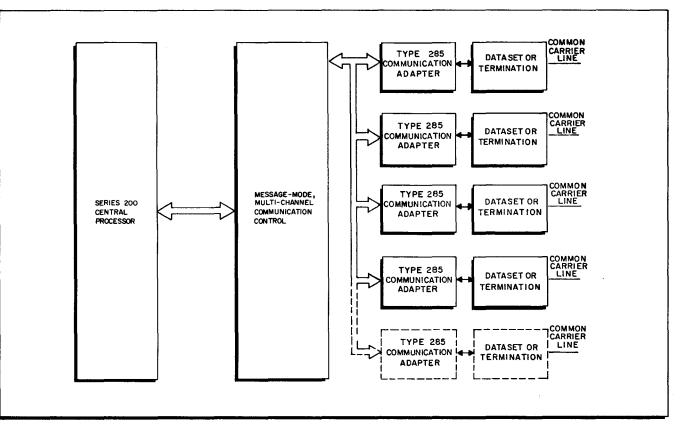

| Figure 4-1. | State Chart                        | 4-1  |

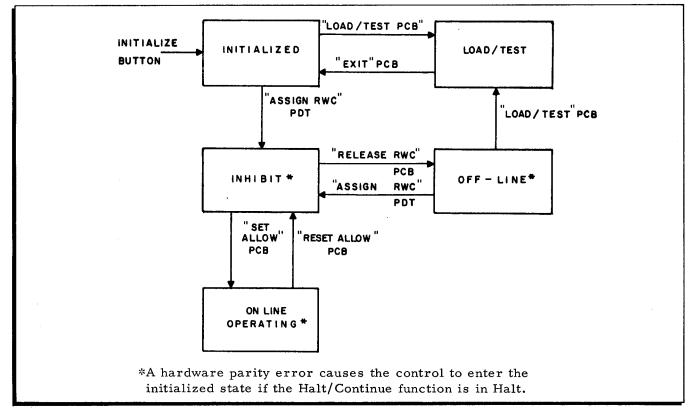

| Figure 4-2. | Format of PDT Instruction          | 4-8  |

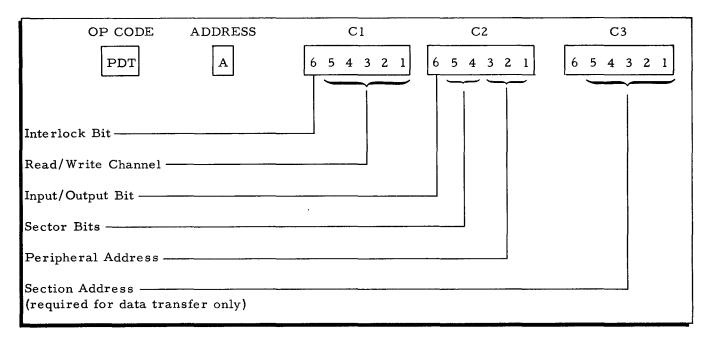

| Figure 4-3. | Format of PCB Instruction          | 4-9  |

| Figure 4-4. | Status Field                       | 4-15 |

## LIST OF TABLES

| Table 1-1. | Standard Secondary Bus Interconnections       | 1-2  |

|------------|-----------------------------------------------|------|

| Table 4-1. | Communication Control PCB C3 Character Coding | 4-10 |

| Table 4-2. | Questions and Control PCB C3 Character Coding | 4-12 |

| Table 4-3. | Line Control PCB C3 Character Coding          | 4-13 |

| Table 4-4. | Function of C8 and C9 Control Character Bits  | 4-14 |

| Table 4-5. | Line Scan Period                              | 4-16 |

| Table 4-6. | Example: Lines in a Communication Network     | 4-17 |

| Table 4-7. | Partially Completed Scan Table                | 4-17 |

| Table 4-8. | Completed Scan Table                          | 4-18 |

| Table 5-1. | Communication Control Memory Sections         | 5-1  |

v

# SECTION I INTRODUCTION

#### GENERAL DESCRIPTION

The Type 286-4 or 286-5 is organized as two processors, one servicing the bit terminus (interface with the communication adapter) and one servicing the character terminus (interface with the central processor). A one-microsecond — 2048 words by nine-bit — memory is timemultiplexed between each processor. Multiplexing is accomplished on an alternate cycle basis, providing an effective memory-cycle time of two microseconds for each processor. The data section of communication control memory has three memory areas for each of the 63 lines: buffer storage, adapter unit interface register, and block parity (BP) register. The control section of communication control memory is also subdivided into three parts: scan table, queues, and line control (see "Control Memory Organization," Section III). Interconnection of the communication control with the central processor and communication lines via Type 285 Communication Adapters is illustrated in Figure 1-1.

Figure 1-1. Types 286-4 and 286-5 Applications

## INTERFACE WITH SERIES 200 CENTRAL PROCESSORS

Standard peripheral interface logic connects the communication control to the standard Series 200 peripheral bus.

# INTERFACE WITH TYPE 285 COMMUNICATION ADAPTERS

The Type 286-4 and Type 286-5, equipped with a group of Series 200 interface packages, connects to a Type 285 Communication Adapter by means of miniature coaxial cables.

## SECONDARY BUS

The standard secondary bus is required to interconnect the Type 286-4 and -5 with any Type 285 Adapter. Table 1-1 lists the interconnecting lines. The secondary bus is connected in series between the logic drawers in which it is utilized. The aggregate maximum cable length is 50 feet. Circuit-driving ability restricts the number of attached logic drawers to eight.

| LINES                                                                      | DESCRIPTION                                                                    |

|----------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| <u>DATA</u><br>1 — Type 286 to Type 285<br>1 — Type 286 from Type 285      | Information out (serial by bit)<br>Information in (serial by bit)              |

| ADDRESS<br>6 — Type 286 to Type 285                                        | Select a particular Type 285                                                   |

| <u>REQUEST</u><br>1 — Type 286 from Type 285<br>1 — Type 286 from Type 285 | Type 285 requests a bit from Type 286<br>Type 285 requests Type 286 take a bit |

| <u>TIMING</u><br>1 — Type 286 to Type 285<br>1 — Type 286 to Type 285      | Bit ready on data-out line<br>Bit received on data-in line                     |

| <u>RESET</u><br>1 — Type 286 to Type 285                                   | Reset by INITIALIZE pushbutton on central processor control panel              |

| SPECIAL STROBE<br>1 - Type 286 to Type 285                                 | Control information to the Type 285                                            |

Table 1-1. Standard Secondary Bus Interconnections

#### SECTION II

#### TYPE 286-4 AND TYPE 286-5 SYSTEM CONSIDERATIONS

#### AMERICAN STANDARD ASSOCIATION (ASA) COMPATIBILITY

The message-mode, multi-channel communication control is capable of operation with the ASA-defined "basic mode" of control procedure (see <u>Control Procedures for Data Communica-</u> tions) using the standard character set of the ASCII code.

#### READ/WRITE CHANNEL ASSIGNMENTS

The message-mode, multi-channel controls will not operate with the high-speed transfer feature. The maximum transfer rate of a read/write channel assigned to the communication control is one access every six microseconds. If a read/write channel access occurs less frequently, the throughput (i.e., the over-all productivity of the control) may decrease.

#### STORED ADDRESS CAPABILITIES

In data transfer to main memory, the multiplexer feature of the peripheral bus enables the control to enter an 18-bit address in the assigned read/write channel. This addressing ability allows the control to place a data character anywhere within a 262K memory block. Any additional address bits — if required — are entered into the read/write channel by the program when the PDT instruction assigning the read/write channel is executed. This means that the main memory buffer area must be located in the same 262K block as the status field. The status field is specified by the address of the Peripheral Data Transfer (PDT) Instruction (see Section IV).

#### DATA

#### Throughput

The maximum character throughput of the control, independent of code level, is 7000 characters per second. System throughput is determined by message size and programming.

#### Rate of Data Transfer

The message-mode, multi-channel communication control handles any rate of data transfer provided its maximum character throughput is not exceeded. The data rate of a line is determined by the terminating line adapter.

#### Message Size

Characters must be handled in blocks if a high throughput is to be obtained. The number of characters required per block, or message, is a function of the number of active lines, character time, and program execution time. In order to utilize most effectively the capabilities of the communication control, the block size used must become progressively larger as the time between received or transmitted characters decreases. The formula below can be used to de-

termine the minimum block size for most efficient use of the Type 286-4 and Type 286-5. Block sizes for most efficient line usage will, in general, be far larger than the minimum figure derived from the formula.

Number of characters/block/line

number of active lines x program time/line character time

## SYNCHRONIZATION FOR SYNCHRONOUS LINE

The communication control compares the stored synchronization (SYNC) character with the incoming bit stream from a synchronous adapter. Upon recognition of two consecutive synchronization characters received over a line, the synchronization condition for that line is set. Synchronization is maintained from the time it is established until receipt of an EOT character. The only exception here occurs when the IBM STR unit is utilized (refer to the Honeywell Hardware Bulletins <u>Type 281-2A Communication Control and Type 285-2A Communication</u> <u>Adapter</u>, Order Number 416, and <u>Type 281-2D Communication Control and Type 285-2D</u> <u>Communication Adapter</u>, Order Number 079. In this case, the adapter recognizes the synchronization characters and it maintains synchronization throughout the operation.

The Type 286-4 or Type 286-5, having synchronized normally upon recognition of two consecutive synchronization characters, transfers all non-synchronization characters to the central processor. In addition to the synchronization characters, control and transmit leader characters — upon recognition — cause the communication control to synchronize. However, unlike the synchronization characters, the control and transmit leader characters are transferred to the central processor. Then, all non-synchronization characters are transferred to main memory under control of the present command.

The communication control remains in synchronization with the incoming bit stream until the control quits the receive mode. The "Resync" PCB instruction resets the synchronization condition for a specific line in the message-mode, multi-channel communication control.

#### START OF INPUT TRANSFER FOR ASYNCHRONOUS LINES

The Type 286-4 or Type 286-5 uses the stored synchronization character as a start-ofinput-transfer (SIT) character. When the SIT character is other than zero, the control will not transfer any characters received from an asynchronous line to the central processor until it receives a line character equal to the stored SIT character. The SIT character and all characters subsequently received are transferred to the central processor. This process continues until the control leaves the receive mode.

The "Resync" PCB instruction, addressed to any asynchronous line in the receive mode with a stored SIT character, halts character transfer to the central processor until a character equal to the SIT character is received. The stored SIT character is not interpreted when the line is in the transmit mode.

# SECTION III FUNCTIONAL DESCRIPTION

#### TYPE 285 COMMUNICATION ADAPTER

A Type 285 Communication Adapter provides the buffering, timing, control and interface required by a particular communication line/remote terminal configuration. At least one Type 285 Communication Adapter is required for each communication line serviced by the Type 286-4 or Type 286-5 Communication Control.

# TYPE 286-4, -5 MESSAGE-MODE, MULTI-CHANNEL COMMUNICATION CONTROL

The communication control regulates the data flow between the central processor and communication lines by means of commands stored in its memory. In transmission, the control of data flow consists of extracting a line character from main memory, transferring that character to buffer storage, and serializing it for transmission by a communication adapter. In reception, the communication control receives data from a Type 285 and assembles bits into characters then accesses main memory and transfers the characters from buffer storage to the central processor. The control, by means of the multiplexing peripheral bus, utilizes addresses stored in its own memory to access main memory.

The control is able to recognize characters for control purposes; such recognition may terminate the present command instruction and cause a stored second command to become the new present command instruction. The present command is also terminated when a record mark is sensed in main memory. An interrupt alerts the program to the change of commands. If the response bit is not set in the present command, the interrupt is prevented.

#### DATA TRANSFER

Data transfer occurs between the central processor and the communication control, also between the control and the adapters. Data transfer between the central processor and the communication control is accomplished in two phases: (1) the transfer of the main memory address, i.e., the location into which data is to be placed or from which it is to be removed; and (2) the transfer of the actual data. Data transfer between the control and the adapter is accomplished on a demand-per-bit basis to the adapter or from it, while the adapter is interrogated during scanning.

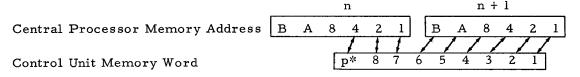

When the communication control senses a call for data transfer, the stored main memory address is transferred, in three buffer cycles, to the assigned read/write channel. The contents of the control buffer register is then transferred to main memory as one or two six-bit characters,

depending on the state of the character transfer bit. Thus, single-character transfers are located in consecutive main memory locations starting with location A, to location A+(n-1), where A is the initial address stored in the communication control by a "Control" PCB instruction and n is the number of characters transferred. Two character transfers are stored as consecutive pairs in main memory locations starting with location A, to location A+(2n-1), where A and n are as defined above. The main memory address to be stored in the control is incremented by one or two, depending on the state of the character transfer bit, before it is again stored in control memory.

#### MEMORY TEST FEATURE

The communication control is designed to allow the execution of a memory diagnostic program. The program is capable of writing into every memory location and interrogating it. An "Output" PDT instruction is required to enter the information into control memory and a subsequent "Input" PDT instruction transfers the contents of each word to main memory. The "Input" PDT instruction transfers the communication control parity bit together with the eight data bits. This enables a diagnostic program to have access to all bits in memory. No hardware parity check is associated with the input transfer. A record mark is required to terminate data transfer in either direction. Two central processor characters are required for each communication control word.

#### MEMORY ORGANIZATION

The control unit memory consists of two main sections, one for data and one for control. The data section of the control unit memory has three memory words for each of the possible 63 lines: buffer storage, adapter interface register, and block parity (BP) register. The control section of the control unit memory is subdivided into three parts: scan table, queues, and line control.

#### Scan Table

The scan table controls the servicing sequence of the Type 285 Adapters; it is "programloaded" prior to on-line operation. To guarantee no loss of data, the table should be weighted according to line speed. No priority is associated with the servicing of the adapters. Two hundred and fifty-six words are allocated to this table as described in Section IV (see "Scan Table").

#### Queues

Four queue tables are required for operation of the communication control. During realtime operation, the program does not have access to the queue tables. Each queue can store 63 service requests. There is no protection against queue overflow, nor is there any indication of its occurrence. Three queues are required to service the interface with the central processor.

Interrupt calls — handled on a "first-come, first-served" basis — are stored in one queue table. Two queues are required to stored requests for character processing. One of these is used for high-speed lines; it has priority over the other queue, used for lower-speed lines. The program, during initial loading, selects which queue a line is to utilize. Requests are handled on a "first-come, first-served" basis. The fourth queue is used for replies sent to the bit processor from the character processor. Again, requests are handled on a "first-come, first-served" basis.

#### Line Control

Line operation is controlled by information stored in control words in the control unit memory. The control words consist of program/variable and fixed characteristics. The program/variable characteristics are: present command, present address, and present recognition characters; these characteristics are defined in the following paragraphs. The fixed characteristics are defined under "Memory Loading" in Section V of this publication.

#### PRESENT COMMAND

The present command specifies the mode and operating characteristics of the associated line. There are four possible modes:

- 1. Transmit This mode transfers characters from the designated area in main memory and transfers one bit at a time to the adapter.

- 2. Transmit-Repeat During operation in the transmit-repeat mode, the first data character specified by the stored address is sent continually until transmission is halted by another command. No normal punctuation is required in main memory.

- 3. Receive In the present command receive mode of operation, the control receives bits from the line by means of the adapter. The control assembles these bits into characters and transfers them to the designated area in main memory.

- 4. Inhibit Line Operation In this mode, line operation is inhibited. After line operation is inhibited, no data transfers take place, no internal interrupt calls are generated and no bit activity from the adapter is serviced. The timer is independent of this command and must be disallowed to prevent timeout. Any interrupt calls stored in the interrupt queue are not inhibited, thus it is possible for an interruption to occur from a line which has been inhibited by interrupt calls previously stored in the queue.

The present command can specify seven operating characteristics of the associated line in addition to the four possible modes. These operating characteristics are:

1. Character Parity — The generation and checking of character parity can be specified on a command basis. Parity is specified as either odd or even. A line may also be specified to operate without parity being generated or checked.

- 2. Block Parity The generation and checking of block parity can also be specified. This modulo two sum (even parity) is calculated for all the characters in the message block (except synchronization characters) transferred to or from the central processor (see also "Block Parity," Section IV).

- 3. Parity Bit of the Block Parity Character This operating characteristic allows the parity bit to be handled either the same as the data character parity bit or as the modulo two sum of the parity bits.

- 4. Response This characteristic allows an interrupt to be initiated at the end of a termination sequence.

- 5. Allow Timer The allow timer characteristic permits the action of the timer on a designated line.

- 6. Command Termination This characteristic determines the number of characters transferred to/from main memory on account of termination caused by character recognition. The block parity and command termination characteristics are related (see "Block Parity, " Section IV).

- 7. Character Transfer The character transfer bit determines whether each line character is to be transferred as one central processor character or as two. This characteristic can be specified independent of line code.

#### PRESENT ADDRESS

The present address is stored as three six-bit characters in the communication control memory. When data is to be transferred to the central processor or from it, these characters are entered into the assigned read/write channel. The data itself is then transferred. The present address is incremented by one or two, depending upon the state of the character transfer bit.

#### PRESENT RECOGNITION CHARACTERS

The communication control checks all characters received and all characters to be transmitted. If they compare with either of the two stored recognition characters, except zero, the present command is terminated according to the state of the command termination bit. A zero character indicates no recognition is to take place for that recognition character.

#### SYNCHRONIZATION CHARACTER

The stored synchronization character is interpreted according to the type of adapter associated with the line. When the synchronization characters are entered into the control unit memory, the complete line character, including a parity bit, is entered; any unused bits must be zero.

#### Synchronous Lines

The synchronization character should be entered (on a per-line basis) during initialization of the system; it should not be changed during real-time operation of the system. In reception,

the synchronization character is used to obtain synchronization with the incoming bit stream and is deleted from the received data. In transmission, the synchronization character is transmitted if no new data characters are available. When the block parity feature is used, the synchronization character is not included in block parity computation in either the receive or transmit modes.

#### Asynchronous Lines

The start-of-input-transfer (SIT) synchronization character can be entered during initialization of the system or by a "Line Control Information" PCB instruction. The latter instruction is described in "Peripheral Control and Branch (PCB) Instruction, "Section IV. The SIT character is used to enable data transfers when the stored SIT character is other than zero. The SIT character is not deleted from the received data; it is included in block parity computation when the block parity feature is used. Characters which precede the SIT character and are not transferred to main memory are not included in block parity computation.

#### NEXT COMMAND

The next command, address, and recognition characters are stored in the Type 286-4 or Type 286-5 and become the present command instruction upon termination of the current present command. If no next command is stored, the line goes into an intermediate mode of operation (see "Intermediate Mode, " Section V).

#### LINE STATUS

Prior to the setting of the interrupt condition, line status information is transferred to the field specified by the A address of the "Read/Write Channel Assignment" PDT instruction, together with the line number. This information tells the program the cause of the interrupt. The character location feature of the control unit causes the address to be transferred. Punctuation is not required in the status field (see "Status Field," Section IV).

# SECTION IV PROGRAMMING REFERENCE DATA

#### OPERATIONAL STATES OF THE TYPE 286-4, -5

There are five operational states of the communication control. Figure 4-1 illustrates these five states together with the instructions required for entering and leaving each. The action and state of the control is unspecified if an instruction is executed in any state other than that shown in the figure.

Figure 4-1. State Chart

#### Initialized State

In its initialized state the control is completely reset, i.e., its lines are not serviced and data transfers and interrupts cannot occur. This state is entered by depressing the INITIALIZE button on the Series 200 control panel, or it may be entered from the Load/Test state of operation.

#### Load/Test State

The load/test state is entered by the control when it is in the initialize, or off-line, state and a "Load/Test" PCB instruction is executed. The load/test state enables the communication control to accept "Data Transfer" PDT instructions. Information is entered into the control unit memory by "Output" PDT instructions. Odd parity generation is performed on each word and the result is stored together with the data as the ninth bit. "Receive" PDT instructions transfer all nine bits to the central processor, but no parity checking occurs.

The load/test state is reset by the execution of an "Exit" PCB instruction or by depressing the INITIALIZE button the the Series 200 control panel. Interrupts cannot be generated in the communication control while it is in the load/test state.

#### **On-Line** Operation

In this operational state the control performs the functions stored in the present command registers of each line in the scan table. This state is entered by the execution of the "Set Allow" PCB instruction permitting interrupts.

#### Inhibit Interrupt

During operation in the inhibit interrupt state, the communication control can not interrupt the program, but it is continuing to scan the communication lines and to receive and transmit bits. Lines continue to operate until their present command and next command activities are completed.

Operation in this state may cause the interrupt queue to overflow. If this occurs only the last 63 interrupt calls are remembered; all earlier interrupt calls are lost. If the control is to enter the inhibit interrupt state from the on-line operational state, the allow function must be disabled. The Allow function is reset by executing a "Reset Allow" PCB instruction. Interrupts are inhibited but data transfers can continue to occur. The control unit leaves this operational state when the Allow function is again set, thus returning it to the on-line state or when the read/write channel is released, thus entering it into the off-line state.

#### Off-Line State

Here the central processor communication lines, interrupt function and read/write channels are not available to the communication control. The Type 285 Communication Adapters continue to be serviced according to the stored characteristics. Line operation for transmit is as though no next command were available. In the receive mode, overwrite errors may occur depending on how long the control remains in the off-line state of operation. The interrupt queue may possibly overflow as described in the inhibit state.

The control enters the off-line state from the inhibit state when a PCB instruction releases the assigned read/write channel. A new read/write channel assignment can again place the communication control in the inhibit state, or a PCB instruction can enter it into the load/test

state. Bit activity is stopped and the communication adapters are no longer serviced when the communication control enters the load/test state.

#### INTERRUPT CAPABILITY

A condition requesting program attention in the Type 286-4 or Type 286-5 sets the interrupt to the central processor. Prior to the actual interrupt — except in the case of a communication control parity error — the line status and the number of the line causing the interrupt are transferred to main memory. Once the program has utilized or moved the status information, a "Status Taken" PCB instruction must be executed to tell the control that another status transfer and subsequent interrupt can be sent to the central processor.

The causes for interrupts from the communication control are: a hardware-detected parity error occurring in the control unit memory; internally, a record mark sensed in memory, a recognition of characters entered into memory by a PCB instruction, or a forced sequence of commands; externally, a line timeout; or an address request.

#### Timing of Transmit Interrupts

An interrupt request is stored in the interrupt queue after a record mark is sensed in main memory or a character is recognized. When a record mark is sensed, the present command is terminated and the next command — stored in the control — becomes the present command before the interrupt call is stored. When a character is recognized, the termination procedure depends on the state of the command termination and block parity bits (see "Block Parity," later in this section).

#### Timing of Receive Interrupts

An interrupt request is stored in the interrupt queue after a record mark is sensed in main memory or a character is recognized. If a record mark is sensed, the present command is terminated and the next command becomes the present command. When a character is recognized, the termination procedure again depends upon the state of the command termination and block parity bits.

#### Interrupt Caused by Communication Control Parity Error

If an interrupt is caused by a hardware parity error, a PCB instruction tests for that error. A second PCB instruction is executed to reset the error function.

#### **Present** Command Termination

The following events cause the present command to be terminated and the next command — if one is stored — to become the new present command; a record mark is sensed in main memory;

a character is recognized and termination is completed; or a PCB instruction causes a forced sequence of commands.

## RECORD MARKS

## Location of Record Marks

In the transmit mode the record mark is located in the next memory location following the last character of the block, as shown below.

#### TRANSMIT

$A + n - 1 \quad A + n \quad A + n + 1$

| Last Character* | Record |

|-----------------|--------|

| of Block        | Mark   |

\*an 8-bit character is assumed.

In the receive mode, the record mark is located in the rightmost position of the last character in the receive area as shown below.

#### RECEIVE

A + n - 1 A + n

|              | Record<br>Mark |

|--------------|----------------|

| Last Charact | er of Block —  |

#### Record Mark Effects

If character recognition starts a termination sequence and a record mark is sensed in main memory, the record mark is ignored and the termination sequence is completed. In receive areas, allowances should be made for an extra character location (maximum of two locations) after the record mark. Here the status indicators would indicate termination due to character recognition and record mark sensing.

#### PARITY

#### Character Parity

Lines designated not to have character parity do not modify data received from the central processor or adapter in any manner. Lines designated to have character parity carry the parity bit in the most significant bit position of the line code. Parity for any line is designated on a block basis by the parity bits stored in the present command. When a character is recognized, its parity is checked; however, the block parity bit determines whether or not the parity of the next character is to be checked.

In the transmit mode of operation, the communication control generates the parity as designated by the parity bits, then inserts it in the parity bit position of the character before the character is included in the generated block parity register. The state of the parity bit position as it is received from main memory does not in any way affect parity generation.

In the receive mode of operation, the communication control checks the parity of each character. If the checked parity differs from that specified in the present command, the control stores this fact and sends it to main memory at the time of the next internal interrupt from the line. In the case of lines designated to check parity, the line parity bit is deleted before the character is transferred to main memory.

#### Block Parity

The block parity feature provides a half-add sum (even modulo two sum) on a bit position basis for each line character transmitted or received. If the unit has a stored synchronization character for the line, synchronization characters are not included in block parity computation. The start-of-input-transfer (SIT) characters are not considered to be synchronization characters; they are included in block parity computation. Characters not transferred to main memory preceding the SIT characters are not included in block parity computation.

The block parity feature is specified on a per-line basis by the block parity (BP) bit. To provide flexibility, the BP bit is used in conjunction with the character termination bit when the block parity feature is used. Both the character termination and block parity features are used in conjunction with character recognition.

#### TRANSMIT MODE

Four combinations of the character termination bit and the block parity bit are used in the transmit mode.

- 1. When a one-character termination sequence with no block parity bit is specified, the recognized character is sent to the Type 285 interface register to be transmitted. The present command is terminated.

- 2. When a two-character termination sequence with no block parity bit is specified, the recognized character is sent to the Type 285 interface register, then a second character is transferred from main memory. After this second character is sent to the adapter interface register to be transmitted, the present command is terminated.

- 3. When a block parity bit and a one-character termination sequence is specified, the termination sequence is started by recognition of a character. After that character is transferred to the adapter interface register, the contents of the block parity register are moved to buffer storage. From buffer storage they are moved to the adapter interface register when that register becomes available. The present command is terminated.

4. When a block parity bit and a two-character termination sequence is specified, the termination sequence is started by the recognition of a character. After that character is transferred to the Type 285 interface register, a second character (block parity correction) is transferred from main memory. This second character is included in the block parity register, then the contents of the block parity register are moved to buffer storage. From buffer storage they are moved to the adapter interface register when that register becomes available. The present command is terminated.

Character parity generation is not performed on the block parity correction character. Recognition is inhibited on the block parity correction character as well as on the block parity character.

#### RECEIVE MODE

Four combinations of the character termination bit and the block parity bit are also used in the receive mode.

- 1. When a one-character termination sequence with no block parity bit is specified, the recognized character is transferred to the central processor. The present command is terminated.

- 2. When a two-character termination sequence with no block parity bit is specified, the recognized character is transferred to the central processor and the termination sequence begins. The next character received is transferred to the central processor. The present command is terminated.

- 3. When a block parity bit and a one-character termination sequence are specified, the recognized character is transferred to the central processor and the termination sequence begins. The next character received is included in the block parity register. Neither this last line character nor the contents of the block parity register are sent to the central processor, but the block parity error indicator is set if the block parity register does not equal zero at this time. When the block parity register has been checked, the present command is terminated.

- 4. When a block parity bit and a two-character termination sequence are specified, the recognized character is transferred to the central processor and the termination sequence begins. The next character received is included in the block parity register, then the contents of the block parity register are moved to buffer storage. From buffer storage they are transferred to the central processor. The block parity error indicator is set if the contents of the block parity register did not equal zero at the time of the transfer. Finally, the present command is terminated.

### CHARACTER PARITY OF THE BLOCK PARITY CHARACTER

The parity bit of the block parity character can be handled in one of two ways:

1. The parity bit is the same as the character parity for the rest of the message. In the receive mode, the parity bit of the second character of a termination is deleted if a two-character termination sequence is called for.

2. The parity bit is the half-add sum of all the preceding parity bits of the message. In the receive mode, the parity bit of the second character of a termination is transferred to the central processor along with the character if a two-character termination sequence is called for.

The block parity character parity bit selects the method that is to be used. If the bit is set, step 1 is in effect; if the bit is reset, step 2 is in effect.

#### RESET BLOCK PARITY REGISTER

The block parity register is reset to zero by any command sequencing that results in a change in the mode of the unit. If a line goes into a No-Next-Command-Stored condition, and the line is returned by a new command back to the same mode it was in prior to the No-Next-Command-Stored condition, this is not considered a change in command as far as resetting the block parity register is concerned. The block parity register is also reset after a termination sequence caused by a character recognition.

#### Control Unit Parity

Each time a word is read from the control unit memory in the inhibit, off-line, or on-line operating state, its parity is checked. If there is an error, the parity error indicator is set and an interrupt is sent to the central processor. The "Parity Error" PCB instruction tests the error indicator. A "Reset Parity Error" PCB instruction is then executed to reset the error indicator and the interrupt caused by the error. The Halt/Continue function determines the action of the control unit when a control unit parity error occurs.

#### HALT/CONTINUE CONTROL

A Halt/Continue control is provided to enable the program to specify the action of the control unit when a control unit parity error occurs. Depressing the INITIALIZE pushbutton on the Series 200 control panel sets the communication control to the Halt condition. Two PCB instructions are provided to change the state of the communication control by program.

## Halt Condition

When the Halt/Continue control is set to the Halt condition and a parity error occurs, the interrupt function is set, the Read/Write Channel is released, the Allow condition of the control unit is reset and the unit goes into the initialize state. When the "Parity Error" PCB is executed to test for a parity error, the program will branch. The "Reset Parity Error" PCB must be executed to reset both the error function and the interrupt caused by the error.

#### Continue Condition

When the Halt/Continue control is set in the Continue condition and a parity error occurs, the interrupt function is set and the unit continues to operate. The interrupt function from the control unit could be set by both a memory parity error and an indication that the status field

has been loaded. The parity error must be tested first. The "Parity Error" PCB to test for a parity error will branch. The "Reset Parity Error" PCB resets the error function and interrupt condition caused by the error. If the interrupt is tested again after the "Reset Parity Error" PCB instruction, it will branch indicating that the status field has new data. The status information is used and a "Status Taken" PCB is executed to alert the unit to the fact that the status field is available.

#### PERIPHERAL INSTRUCTIONS

#### Peripheral Data Transfer (PDT) Instruction

A PDT instruction is interpreted according to the state of the control unit. When the unit is in the load/test state, the PDT instruction is a data transfer type. When the unit is in the initialized or off-line state, a PDT instruction assigns the RWC to the unit and loads the status field address into the starting location counter. The format for the PDT instruction used in conjunction with the communication control is shown in Figure 4-2.

#### Figure 4-2. Format of PDT Instruction

A address

- The A address interpretation is determined by the control unit:

Load/Test state: Specifies the leftmost character of the data field used by the PDT instruction.

Inhibit and On-Line operating state: Specifies the leftmost character of the status field used by the control unit to store the interrupt information.

| Interlock Bit            | - ONE = memory access not granted to alternate RWC.                                                                           |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------|

|                          | ZERO = memory access granted to alternate RWC.                                                                                |

| Read/Write Channel (RWC) | - Selects the RWC between main memory and the con-<br>trol unit (see the appropriate Programmers' Refer-<br>ence Manual).     |

| Input/Output Bit         | - Indicates direction of data transfer in load/test state:                                                                    |

|                          | ZERO = output, ONE = input. This bit is not inter-<br>preted for the PDT assigning an RWC to the unit.                        |

| Sector Bits (C2)         | — Bits 5 and 4 designate the sector: sector 1 = 00,<br>sector 2 = 10, sector 3 = 11.                                          |

| Peripheral Address       | - Logical address of the control unit on the peripheral bus.                                                                  |

| Section Address (C3)     | <ul> <li>This character is required when the control unit is<br/>in the load/test state, otherwise it is not used.</li> </ul> |

Control character C3 specifies the section where the transfer is to start and is loaded into the memory test address counter. The six least significant bits of the memory test address counter are reset at the beginning of each PDT instruction. The counter supplies the address to the memory address register. A record mark in the central processor main memory is required to terminate the transfer. The entire 2048 words of memory can be loaded or interrogated by a single PDT instruction. Address "wrap-around" can occur in the memory.

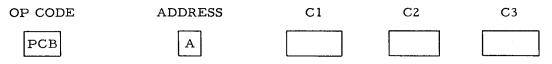

## Peripheral Control and Branch (PCB) Instruction

The PCB instruction is the only means the program has to communicate with the control unit except for the two types of PDT instructions outlined above. There are three types of PCB instructions for performing the following functions:

- 1. Questions and control of the communication control unit.

- 2. Questions and control of a particular line.

- 3. Transfer control information to a particular line.

The general format for PCB instructions is shown in Figure 4-3.

| OP CODE          | ADDRESS      | C1     | C2     | C3     | Cn     |   |

|------------------|--------------|--------|--------|--------|--------|---|

| PCB              | Α            | 654321 | 654321 | 654321 | 654321 |   |

| Interlock Bit —  |              |        |        |        |        | ľ |

| Read/Write Cha   | nnel         |        |        |        |        |   |

| Input/Output Bit |              |        |        |        |        |   |

| <br>Sector Bits  |              |        |        |        |        |   |

| Peripheral Addı  | ess          |        |        |        |        |   |

| Test or Control  | Parameters — |        |        |        |        |   |

Figure 4-3. Format of PCB Instruction

| A address                | - Dependent on the type of PCB, as follows:                                                                                                                                                            |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          | Branching PCB — The A address is the memory<br>location to which the program<br>will branch if the condition<br>tested for by the PCB is true<br>or the control unit cannot ac-<br>cept a control PCB. |

|                          | Nonbranching PCB — The address is not interpreted<br>but one must be specified.                                                                                                                        |

| Interlock Bit            | - Not interpreted.                                                                                                                                                                                     |

| Read/Write Channel (RWC) | <ul> <li>Selects the RWC being tested for availability and must<br/>be zero if the RWC is not to be tested (see the appro-<br/>priate Programmers' Reference Manual).</li> </ul>                       |

| Input/Output Bit         | - Not interpreted.                                                                                                                                                                                     |

| Sector Bits (C2)         | — Bits 5 and 4 designate the sector: sector 1 = 00,<br>sector 2 = 10, sector 3 = 11.                                                                                                                   |

| Peripheral Address       | <ul> <li>Logical address of the communication control unit on<br/>the peripheral bus.</li> </ul>                                                                                                       |

| Control Characters:      | C1 — Should be zero except when a test for RWC activity is desired.                                                                                                                                    |

|                          | C2 — The logical address address assigned to the control unit.                                                                                                                                         |

|                          | C3 — Distinguishes between the different types of<br>PCB's; control of the control unit or asking<br>questions of the unit.                                                                            |

# QUESTIONS AND CONTROL OF THE UNIT

The general format, using control character C3, is implemented with this type of PCB instruction. The format is as follows; chaining of C3 characters is permitted.

Communication control unit PCB C3 character coding for both questions and commands is shown in Table 4-1.

| TYPE OF<br>INSTRUCTION | BRANCHING | DESCRIPTION                                                                 | (OCTAL) |

|------------------------|-----------|-----------------------------------------------------------------------------|---------|

|                        |           | QUESTIONS                                                                   |         |

| Busy                   | Yes       | Is the communication control busy (RWC as-<br>signed)? If yes, branch to A. | 10      |

| Parity error           | Yes       | Is the control unit parity error indicator set?<br>If yes, branch to A.     | 40      |

# Table 4-1. Communication Control PCB C3 Character Coding

ş

# Table 4-1 (cont). Communication Control PCB C3 Character Coding

| TYPE OF<br>INSTRUCTION | BRANCHING | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | (OCTAL) |

|------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Interrupt              | Yes       | Did the communication control specified by the C2 variant cause the interrupt? If yes, branch to A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 75      |

|                        |           | COMMANDS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |

| Set Allow              | No        | Sets the Allow function in the control unit to per-<br>mit program interrupts from the unit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 71      |

| Reset Allow            | No        | Resets the Allow function and prevents future interrupts.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 70      |

| Load/Test<br>State     | No        | Places the control unit in the load/test state<br>and allows a PDT instruction to transfer data<br>to or from the unit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 25      |

| Exit                   | No        | Resets the load/test state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 24      |

| Status Taken           | No        | Notifies the control unit that the status field is<br>available for the next transfer and subsequent<br>interrupt. This PCB resets the present in-<br>terrupt if it was caused by an internal or ex-<br>ternal source or an address request.                                                                                                                                                                                                                                                                                                                                                                                                             | 74      |

| Release RWC            | No        | The assigned RWC is released by a "Release<br>RWC" PCB instruction addressed to the con-<br>trol unit. The release does not take place<br>during a data transfer; i.e., once the RWC<br>is loaded with an address the associated<br>data is transferred then, if required, the<br>RWC is released. If the status is being<br>transferred when a "Release RWC" PCB<br>instruction is executed, the transfer is com-<br>pleted and the interrupt function is set, then<br>the RWC is released. Once the RWC is re-<br>leased, status information cannot be sent to<br>the central processor, therefore interrupts<br>cannot be sent from the control unit. | 27      |

| Halt                   | No        | Places the Halt/Continue function in the Halt condition.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 20      |

| Continue               | No        | Places the Halt/Continue function in the Con-<br>tinue condition.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 21      |

| Reset Parity<br>Error  | No        | Resets the parity error function and the in-<br>terrupt caused by the error.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 26      |

# QUESTIONS AND CONTROL OF A LINE

The following is the only allowable format for this type of PCB; control characters cannot be chained.

Coding of control character C3 in Questions and Control PCB's is shown in Table 4-2. All line questions and line commands shown are branching PCB's. These PCB instructions may have to be reextracted; this is controlled by the communication control unit. It is suggested that these be self-branching PCB instructions (the A address specifies the address of the instruction).

| TYPE OF<br>INSTRUCTION              | DESCRIPTION                                                                                                                                                                                                                       | C3<br>(OCTAL) |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

|                                     | LINE QUESTIONS                                                                                                                                                                                                                    |               |

| Address Request                     | Request the address of the next transfer that is to take place<br>from the designated line. (NOTE: This feature is available<br>only when the Character Location option is present.)                                              | 36            |

|                                     | LINE COMMANDS                                                                                                                                                                                                                     |               |

| Forced Sequence<br>with Response    | Aborts the present command and causes the next command to<br>become the new present command. An interrupt is generated<br>due to command sequencing.                                                                              | 33            |

| Forced Sequence<br>without Response | Same action as the Forced Sequence with Response instruc-<br>tion but the interrupt is not generated due to command se-<br>quencing.                                                                                              | 32            |

| RESYNC                              | Resets the SYNC conditions of the designated line (see<br>Section II, "Syncronization for Synchronous Line," and<br>"Start of Input Transfer for Asynchronous Lines").                                                            | 37            |

| Special Strobe                      | Provides the program with direct control of an adapter unit<br>by activating the special strobe line to the adapter unit.<br>Refer to the appropriate Type 281/285 Hardware Bulletins<br>for the use of this special strobe line. | 34            |

#### Table 4-2. Questions and Control PCB C3 Character Coding

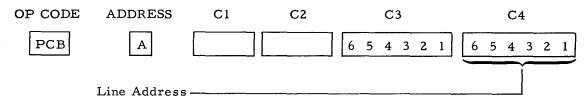

## LINE CONTROL INFORMATION PCB

This type of PCB must have control characters Cl through C7. Additional control characters through Cl3 can be used but are only required if contents of the next registers are to be changed. Control characters Cl4 and Cl5 should only be used for asynchronous lines. OP CODE ADDRESS Cl C2 C3 C4 C5 C6 C7 Cl3 Cl4 Cl5

|     |   | <br> | <br><u> </u> | <br> |       | <br> |  |

|-----|---|------|--------------|------|-------|------|--|

| PCB | А |      |              |      | • • • |      |  |

Coding of control character C3 in Line Control Information PCB's is shown in Table 4-3. All line commands are branching PCB's. These PCB instructions may have to be reextracted; this is controlled by the communication control. It is suggested that these be self-branching PCB instructions (the A address specifies the address of the instruction).

# Table 4-3. Line Control PCB C3 Character Coding

| TYPE OF<br>INSTRUCTION                                  | DESCRIPTION                                                                                                                                                                                                                                                                                         | C3<br>(OCTAL) |

|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

|                                                         | LINE COMMANDS                                                                                                                                                                                                                                                                                       |               |

| Next Command                                            | Alerts the communication control that the PCB contains the next command information.                                                                                                                                                                                                                | 30            |

| Next Command and<br>Forced Sequence<br>with Response    | Alerts the communication control that this PCB<br>contains the next command information and once it is<br>loaded the present command is aborted and the in-<br>formation just loaded becomes the new present com-<br>mand. As a result of the command changes, an in-<br>terrupt call is generated. | 33            |

| Next Command and<br>Forced Sequence<br>without Response | Same action as the next command and Forced Sequence<br>with Response instruction but the interrupt is not<br>generated.                                                                                                                                                                             | 32            |

The other control characters, C4 through C15, in the Line Control Information PCB's are used for the following purposes:

- 1. C4 is the line address control character.

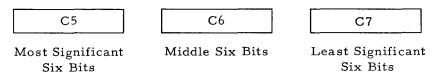

- 2. C5, C6, and C7 are the characters which contain the central processor memory address, six bits in each character, that is used by the control to load the RWC when a data transfer is to be made, as shown below.

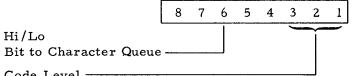

3. C8 and C9 control characters specify what action, if any, the line is to take. They are loaded into the next order sections of the memory. Bit arrangement is shown below; function and meaning of the individual bits in the C8 and C9 control characters are listed in Table 4-4.

|   |   | C | 3 |   |   |   |   | C | 9 |   |   |

|---|---|---|---|---|---|---|---|---|---|---|---|

| 6 | 5 | 4 | 3 | 2 | 1 | 6 | 5 | 4 | 3 | 2 | 1 |

- 4. Cl0 and Cl1 control characters contain the first recognition character in eight bits (two bits of Cl0 and six bits of Cl1).

- 5. Cl2 and Cl3 control characters contain the second recognition character in eight bits (two bits of Cl2 and six bits of Cl3). When the recognition characters are loaded by a "Line Control Information" PCB, the complete line character, including a parity bit, is loaded. Any usused bits must be zero. The following is the ASCII control character ETX (End-of-Text) with odd parity in the PCB format to be loaded as the first recognition character.

|                 |   |   | С | 10 |   |   | _ |   |   | С | 11 |   |   |

|-----------------|---|---|---|----|---|---|---|---|---|---|----|---|---|

| CP bit position | в | Α | 8 | 4  | 2 | 1 |   | в | А | 8 | 4  | 2 | 1 |

| ETX             | x | х | х | х  | 1 | 0 | ] | 0 | 0 | 0 | 0  | 1 | 1 |

X-these bits are transferred to the control unit.

6. Cl4 and Cl5 control characters contain the SIT character for asynchronous lines in eight bits (two bits of Cl4 and the six bits of Cl5). It should be noted that due to the delay in the control unit (interrupt queue), care must be taken when changing this character because the SIT character is loaded directly into the present command register and not into the next command register, as is the rest of the information contained in a "Line Control Information" PCB.

| Table 4-4. Function of C8 and C9 Control Character Bit | Table 4-4. | Function of | C8 and C9 | Control | Character | Bits |

|--------------------------------------------------------|------------|-------------|-----------|---------|-----------|------|

|--------------------------------------------------------|------------|-------------|-----------|---------|-----------|------|

| BIT  | MEANING OF C8 BIT                                                                                                                                                                                                                                                                                                                                         | BIT            | MEANING OF C9 BIT                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6, 5 | Bits 6 and 5 specify the mode of<br>operation of the line as follows:<br>Bits<br><u>6 5</u><br>0 0 - Inhibit<br>0 1 - Receive<br>1 0 - Transmit<br>1 1 - Transmit repeat<br>Bit 4 is the allow-timer bit:<br>0 - The timer is not allowed.                                                                                                                | 6<br>5, 4<br>3 | <ul> <li>Bit 6 is the response bit:</li> <li>0 - No interrupt is generated at the termination of the command.</li> <li>1 - An interrupt is allowed.</li> <li>Not used; must be zero.</li> <li>Bits 3 is the block parity bit:</li> <li>0 - The block parity feature is not used.</li> </ul>                                                                                                                                           |

| 3, 2 | <ul> <li>1 - The timer is not allowed.</li> <li>1 - The timer is allowed.</li> <li>Bits 3 and 2 specify the character parity feature as follows:</li> <li>Bits <ul> <li><u>3</u> <u>2</u></li> <li>0 0 No character parity gener-</li> <li>0 1 ation or checking is per formed.</li> <li>1 0 - Even character parity is specified.</li> </ul> </li> </ul> | 2              | <ol> <li>1 - The block parity feature is used.</li> <li>Bit 2 is the command termination bit:</li> <li>0 - The character that is recognized<br/>is the last transfer to or from the<br/>central processor before the com-<br/>mand is terminated.</li> <li>1 - One more data transfer is made<br/>to or from the central processor<br/>after the character that was recog-<br/>nized before the command is<br/>terminated.</li> </ol> |

| 1    | <ul> <li>1 1 - Odd character parity<br/>specified.</li> <li>Bit 1 is the character transfer bit:</li> <li>0 - Specifies one six-bit character<br/>transfer per line character.</li> <li>1 - Specifies two six-bit character<br/>transfers per line character.</li> </ul>                                                                                  | 1              | <ul> <li>Bit 1 is the parity bit:</li> <li>0 - The parity bit will be the half-add sum of the preceding parity bit.</li> <li>1 - The block parity character will have the same parity generated or checked as data characters.</li> </ul>                                                                                                                                                                                             |

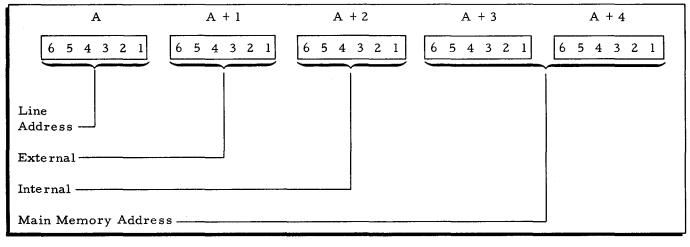

#### STATUS FIELD

The status field associated with interrupts is shown in Figure 4-4. The status field is not used when the interrupt is caused by a control unit parity error. Punctuation is not required in this field.

Figure 4-4. Status Field

Line Address

External

Internal

- The character specifies the line that caused the interrupt.

- If bit 6 is set (one) the interrupt is caused by external conditions. If bit 6 is not set, the cause of the interrupt is either internal or is a response to an address request. Bit 5, when set, indicates a timeout has occured on the line (no data has been moved by the bit end for at least eight seconds). Bits 1 through 4 are not used; they will be loaded as zeros.

- The setting of each bit indicates a status condition:

- Bit 1 When set, indicates termination has occurred due to character recognition.

- Bit 2 When set, indicates termination has occurred due to finding a record mark in the central processor main memory.

- Bit 3 When set, indicates the block parity summation, in the receive mode, was not equal to zero. (This bit can only be set when the block parity feature is specified for the line in the command just terminated.)

- Bit 4 When set, indicates a received character was detected with bad parity.

- Bit 5 When set, indicates that no next command was available at the time commands were sequenced.

Bit 6 — When set, indicates an overwrite error has occurred. The character processor was unable to transfer received data to the central processor. Main Memory Address

- The address sent to the central processor is modulo 4096. The A+3 character includes the middle six bits of the stored address in the communication control and the A+4 character includes the least significant six bits.

#### Overwrite

公式などの新たいがい

A STATE OF STATE OF STATE

When an overwrite error occurs, the character in buffer storage can not be transferred to the central processor before the next character is received from the line. The character in buffer storage is not altered in any way. All subsequent received characters, until buffer storage is available, are lost. Character recognition, parity checking, and block parity computation are not performed on the lost characters.

#### SCAN TABLE