## DATAmatic 1000

Electronic Data Processing System

Preliminary Manual of Information

## **DATA**matic Corporation

151 Needham Street

Newton Highlands 61, Massachusetts

# DATAmatic 1000

#### **Performance Specifications**

INPUT: Punched cards

INPUT RATE: 900 punched cards per minute

INTERNAL CODE: Binary coded decimal and alphanumeric

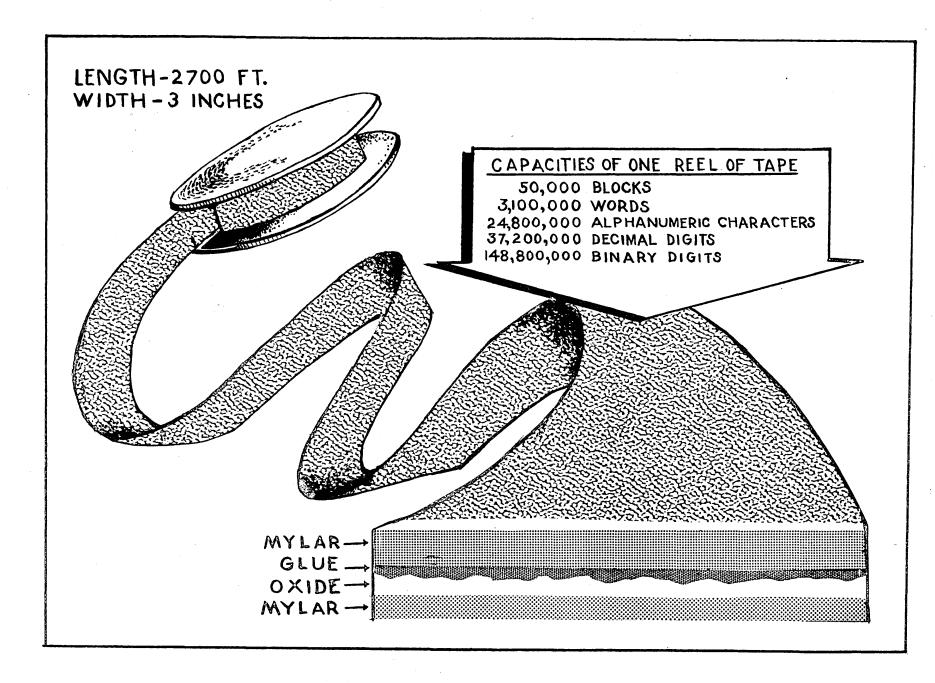

**STORAGE:** 2700-ft. reels of 3-inch wide magnetic tape

MAGNETIC TAPE CAPACITY: 37,200,000 decimal digits per reel, up to 100 reels can be directly connected.

MAGNETIC READ-WRITE RATE: 60,000 decimal digits per second

INDEPENDENT OPERATIONS: Input conversion, output conversion, and processing may take place concurrently

TRANSFER STORAGE: Two input, two output buffers

BUFFER CAPACITY: 744 decimal digits per buffer

INTERNAL MEMORY: Magnetic cores

MEMORY CAPACITY: 24,000 decimal digits

MEMORY ACCESS TIME: Parallel access to 12 decimal digits in 10 microseconds

MULTI-TAPE SEARCH: Scans up to 10 magnetic tapes simultaneously

SEARCH RATE: Up to 600,000 decimal digits per second

**COMPARISON RATE:** 5000 alphabetic or numeric comparisons per second

ADDITION RATE: 4000 sets 11-digit (plus sign) numbers per second

MULTIPLICATION RATE: 1000 sets 11-digit (plus sign) numbers per second

**OUTPUT FORMAT:** Exceptional flexibility via plugboards

**OUTPUT RATE** — PUNCHED CARDS: 100 per minute

OUTPUT RATE --- LOW SPEED PRINTER: 150 120-character lines per minute maximum

**OUTPUT RATE** — HIGH SPEED PRINTER: 900 120-character lines per minute maximum

**ORDER STRUCTURE:** Three address

151 NEEDHAM STREET . NEWTON HIGHLANDS 61, MASS.

Printed in U.S.A. DSA-5

### DATAmatic 1000

### TABLE OF CONTENTS

|                                               | Page No. |

|-----------------------------------------------|----------|

| INTRODUCTION                                  | 1        |

| INPUT-OUTPUT                                  | 2        |

| INFORMATION STORAGE                           | 2        |

| Machine Word                                  | 2        |

| Numeric Words                                 | 3        |

| Alphabetic Words                              | 3        |

| Order Words                                   | 3        |

| Magnetic Tape External Storage                | 4        |

| Magnetic Core Internal Storage                | 7        |

| Intermediate Storage Units                    | 9        |

| PROGRAMMING AND OPERATION                     | 10       |

| CHECKING                                      | 12       |

| DATAmatic CENTRAL PROCESSOR (TYPE 1000)       | 14       |

| DATAmatic 1000 ORDER DESCRIPTIONS             | 17       |

| Introduction                                  | 17       |

| Calculating Orders                            | 17       |

| Shift Orders                                  | 19       |

| Buffer Transfer Orders                        | 20       |

| Memory Transfer Orders                        | 24       |

| Tape Control Orders                           | 25       |

| Comparison Orders                             | 28       |

| Print Orders                                  | 30       |

| Control Orders                                | 30       |

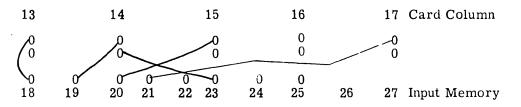

| THE DATAmatic INPUT CONVERTER TYPE 1200       | 32       |

| Reading Information from Card to Input Memory | 32       |

| Transferring Information from Input Memory to |          |

| Output Memory                                 | 34       |

| Automatic Checking                            | 36       |

| Application                                   | 36       |

| Details of Programming                        | 38       |

| 1. Wiring the Card Reader Plugboard           | 38       |

| 2. Wiring the Category Plugboard              | 41       |

| Central Processor Considerations              | 46       |

i

### TABLE OF CONTENTS (CONT.)

Page No.

| THE DATAmatic OUTPUT CONVERTER TYPE 1300 | 54 |

|------------------------------------------|----|

| Wiring for Conversion, Without Use of    |    |

| Special Control                          | 56 |

| Wiring for Special Functions             | 65 |

| Timing of Special Function Exit Hubs     | 67 |

| ADDRESSES OF SIGNIFICANCE                | 69 |

### LIST OF ILLUSTRATIONS

.

| Figure No.   | Title                                            | Page No. |

|--------------|--------------------------------------------------|----------|

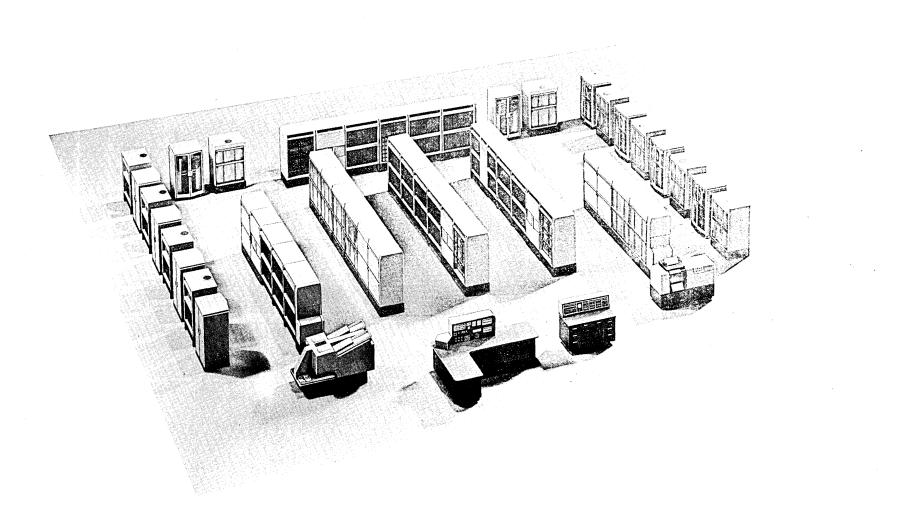

| Frontispiece | DATAmatic 1000 Electronic Data Processing System |          |

| 1            | DATAmatic 1000 Magnetic Tape                     | 5        |

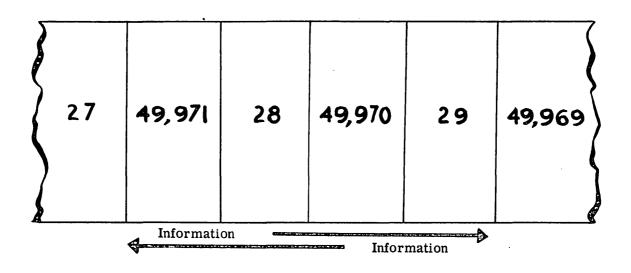

| 2            | Arrangement of Words on Magnetic Tape            | 6        |

| 3            | Interlacing of Blocks on DATAmatic 1000 Tape     | 7        |

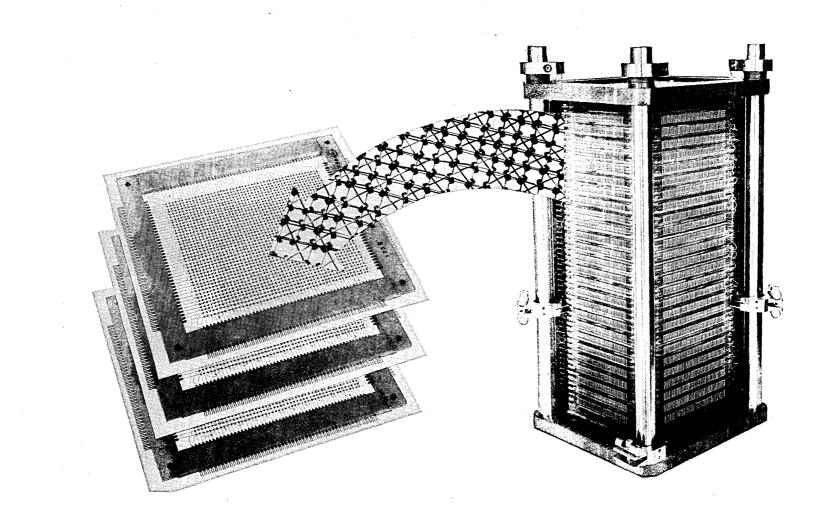

| 4            | DATAmatic 1000 Magnetic Core Memory              | 8        |

| 5            | Typical Magnetic Core                            | 9        |

| 6            | Input Buffer Storage                             | 11       |

| 7            | Output Buffer Storage                            | 11       |

| 8            | DATAmatic Order Word Structure                   | 17       |

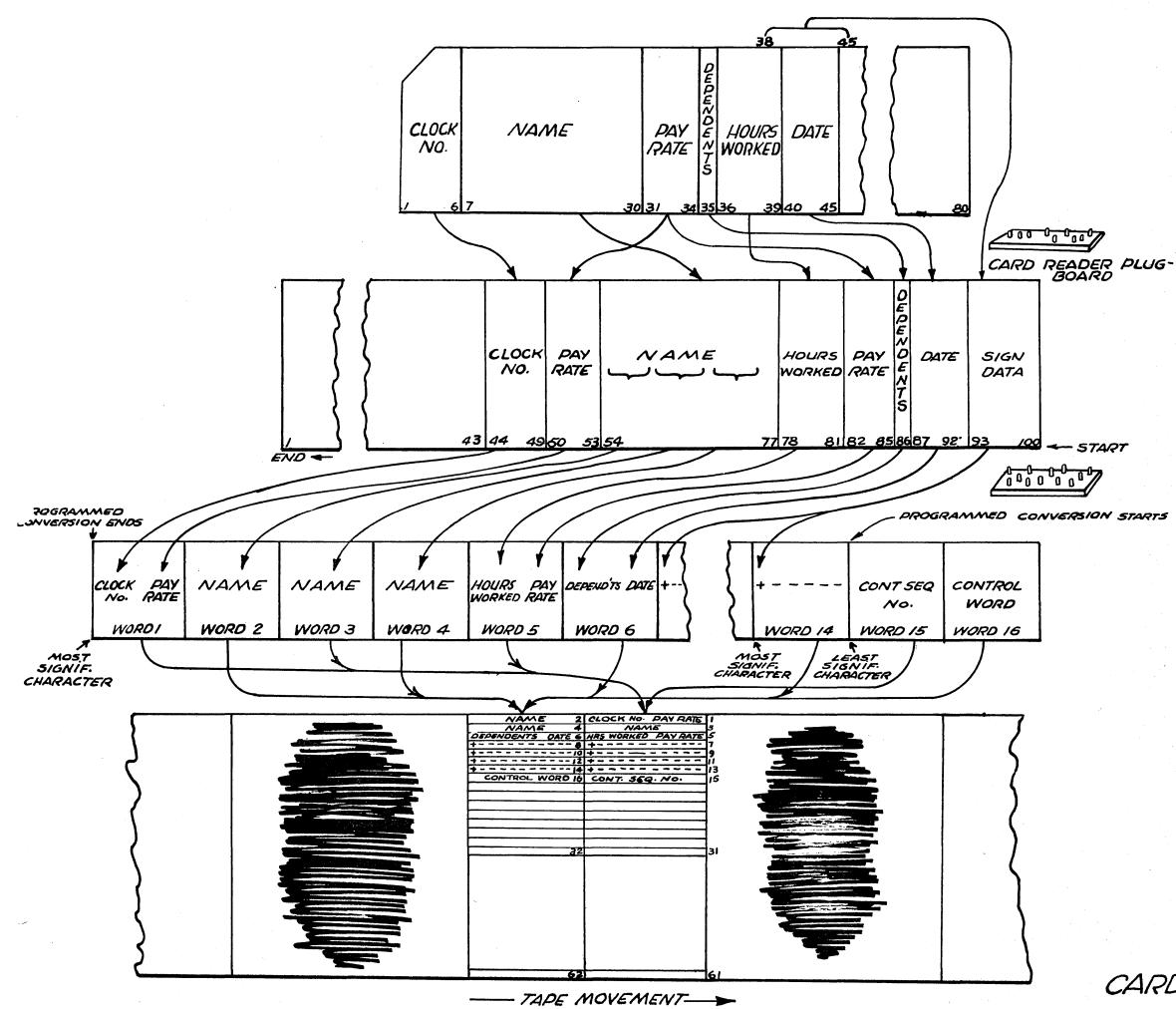

| 9            | Input Converter Type 1200                        | 33       |

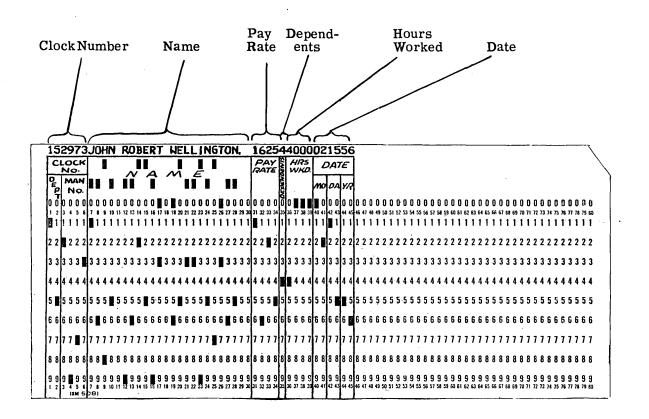

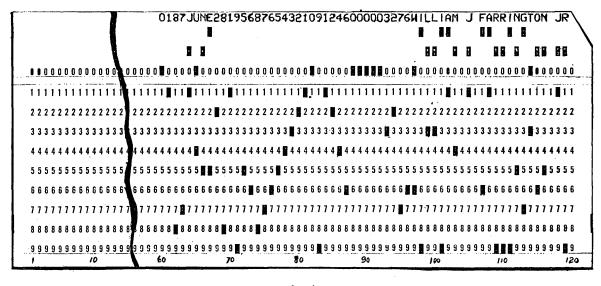

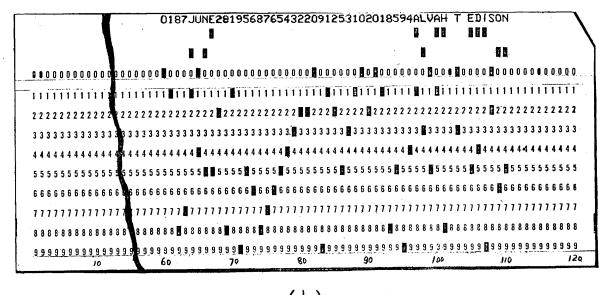

| 10           | Punched Card With Representative Data            | 37       |

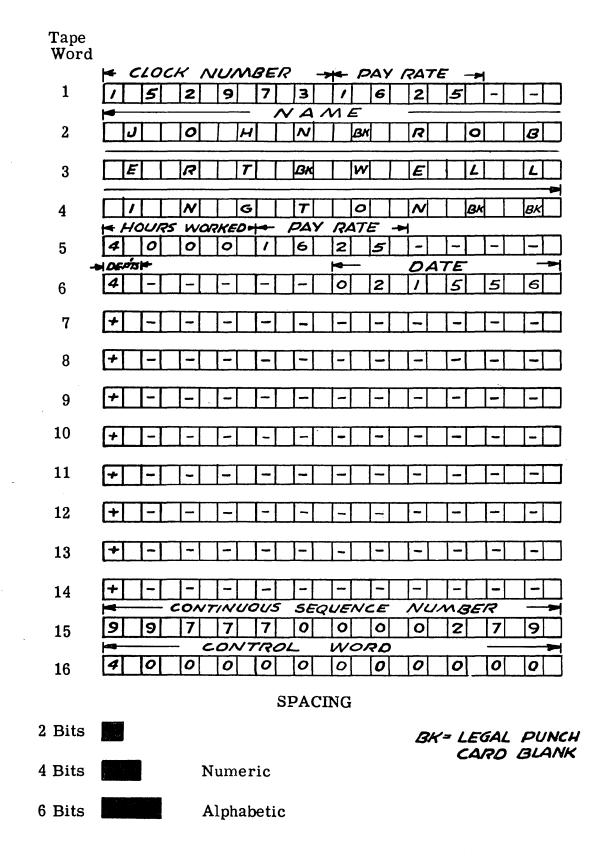

| 11           | Tape Format                                      | 39       |

| 12           | Card to Tape Conversion                          | 40       |

| 13           | Work Sheet                                       | 42       |

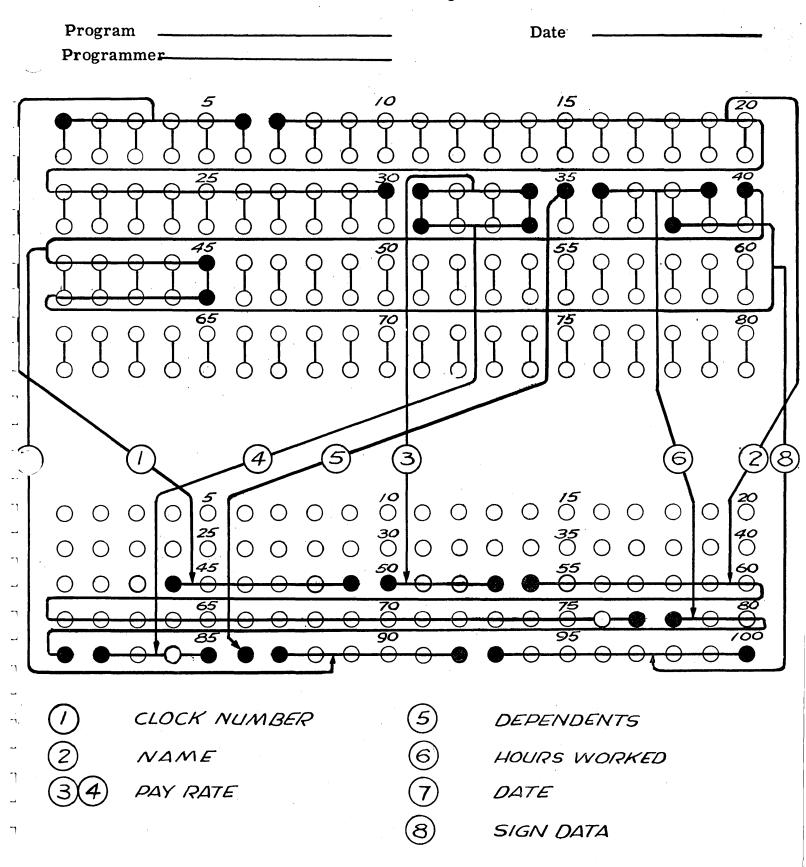

| 14           | Program Plugging Work Sheet                      | 43       |

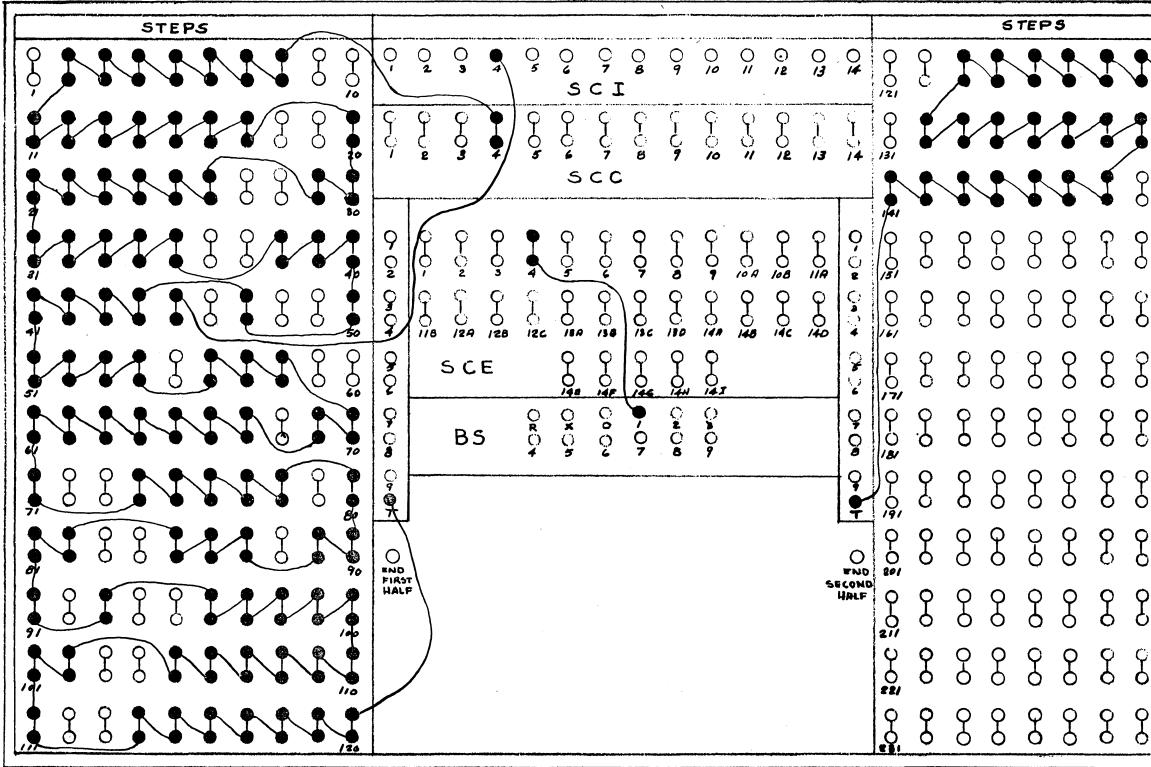

| 15           | Input Converter Category Plugboard               | 45       |

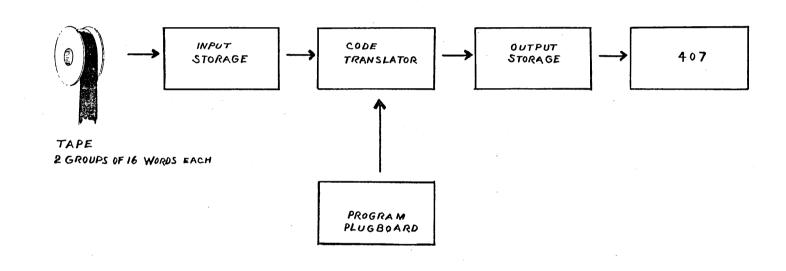

| 16           | DATAmatic Output Converter Type 1300             |          |

|              | (Block Diagram)                                  | 55       |

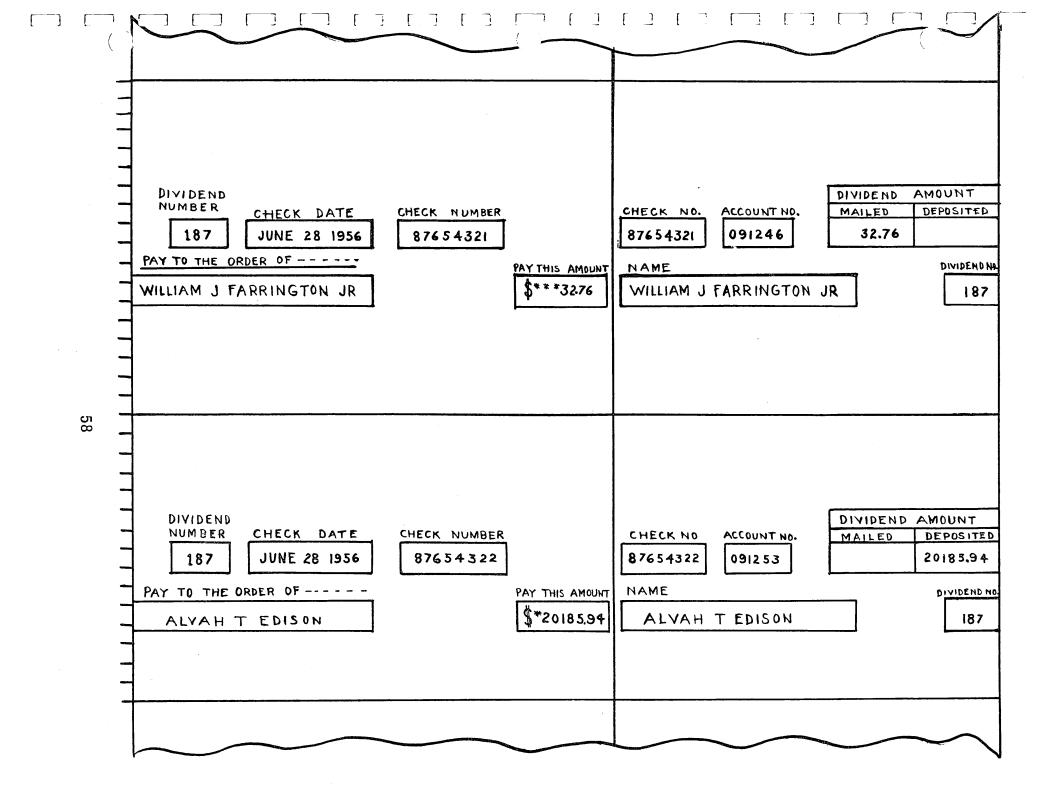

| 17           | Typical Dividend Checks                          | 58       |

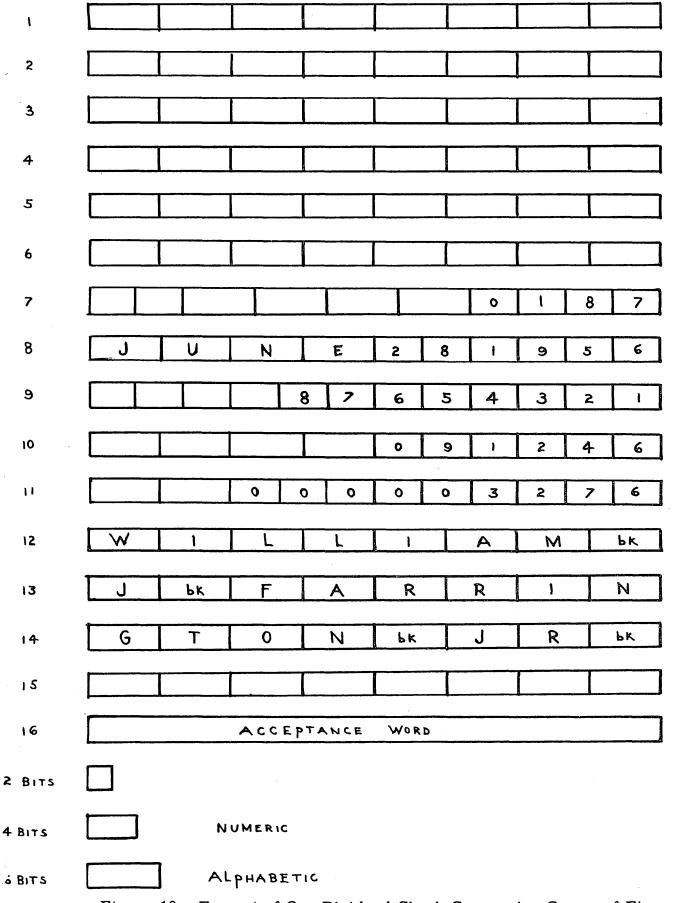

| 18           | Tape Format for Typical Dividend Checks          | 59       |

| 19           | Format of One Dividend Check Conversion          |          |

|              | Group of Figure 18                               | 60       |

| 20           | Allocation of Conversion Rules                   | 61       |

| 21 a         | Program Plugboard - Output Converter             | 62       |

| <b>21</b> b  | Program Plugboard - Output Converter             | 63       |

| 22           | Output Storage Array Showing Simulated           |          |

|              | 120 Column Card                                  | 64       |

| 23           | Program Plugboard - Output Converter             | 66       |

DATAmatic 1000 Electronic Data Processing System

# The DATAmatic 1000 Electronic Data Processing System

#### INTRODUCTION

The DATAmatic 1000 is an electronic data processing system designed and engineered as an efficient management tool. It incorporates entirely new concepts and procedures for handling business data, conceived to exploit the accuracy, speed and versatility available in the latest DATAmatic equipment.

The DATAmatic 1000 system consists of a group of electronic units which are used as building blocks to produce a data processing system of any desired capacity. A typical installation contains the following elements:

> Central Processor (Type 1000) Central Console (Type 1090) Magnetic File Unit (Type 1100) Input Converter (Type 1200) Output Converter (Type 1300) File Reference Unit (Type 1150) File Console (Type 1190)

Among the features of the DATAmatic 1000 are:

- 1. Separate input and output converters, each operating independently of the main machine.

- 2. 3 inch wide magnetic tape with magnetic material sandwiched between layers of tough plastic to make it practically unbreakable and impervious to handling.

- 3. Advanced frequency modulation principles used in recording information on the tape.

- 4. Magnetic core internal memory provides compact, low-power, high reliability storage.

- 5. Intermediate or buffer storage permits extremely fast File Maintenance by scanning up to 10 different Magnetic File Units simultaneously.

- 6. Comprehensive built-in checking systems guarantees unequaled performance in reliability and accuracy.

- 7. Extremely versatile system of orders permits ease of programming and greatly increases scope of applications.

- 8. Sorting can be accomplished with both input and output Magnetic File Units running at full speed reading and writing 60,000 decimal digits per second while the main machine is simultaneously sorting the items as they come and sending sorted items to the output, all of this completely self-checked.

- 9. Up to 100 Magnetic File Units can be connected into the system at any one time and can be split up in any way between the reading and recording operations.

#### INPUT-OUTPUT

In order to permit the main DATAmatic 1000 System to process data at its inherent electronic speeds, the conversion of original information onto magnetic tape for processing and also the printing or punching of output information from magnetic tape are carried on in input and output converters completely separate from the main machine.

The Input Converter incorporates as part of its own system a pluggable control panel that allows complete flexibility of format. Freedom of card format is obtained by column switching, duplication or deletion when reading the punched card. Numeric, alphabetic, multiple column punchings, symbolic punching can be handled with equal facility.

The Output Converter translates the information from the wide magnetic tape to either a 120 character line printer or an 80 column punched card. It also is a unit separate from the central processor and includes a pluggable control panel to edit information from the tape to a desired card or printed form format.

The Input Converter and the Output Converter both incorporate the comprehensive self-checking features available in the DATAmatic 1000. The most advanced and proven techniques using "magnetic core logic" have been applied in the design of these converters. These techniques employ magnetic cores to perform functions previously performed by electronic tubes, thereby increasing reliability by reducing the tube count and the cooling requirements.

#### INFORMATION STORAGE

#### Machine Word

For more efficient machine operation, numeric characters and alphabetic characters and mixtures of these are handled in groups inside the machine. Since each of these various groups of characters occupies the same amount of space in the machine it is convenient to refer to them by a term which is applicable to all of them. <u>Word</u> is the commonly used term. Thus, by a 2000 word memory is meant a memory with 2000 storage locations or "pigeon holes", each of which can store one word consisting of a

group of numeric, alphabetic or mixed characters. The difference between these words is automatically interpreted by the machine.

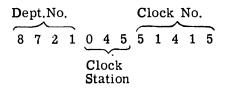

<u>Numeric words</u> are groups of 12 decimal digits. An example of a numeric word is the identification of an individual by clock number, department number and clock station, using fields in a word in a manner similar to a punched card field.

However, if numeric words are to be used in arithmetic operation they must have a plus or minus sign in the extreme left position. For example, if this week's gross pay is to be added to the gross pay to date, both numeric words would have a sign.

|                       | 12 Decimal Characters    |

|-----------------------|--------------------------|

| Gross Pay             | + 0 0 0 0 0 0 7 4. 8 3   |

| Gross Pay to Date     | + 0 0 0 0 3 4 7 1. 9 1   |

| New Gross Pay to Date | + 0 0 0 0 0 3 5 4 6. 7 4 |

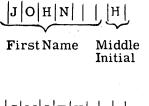

<u>Alphabetic words</u> are made up of 8 letters, in contrast to the 12 digits of a numeric word. This is necessary because it requires more space to identify any one of 26 letters than to identify one of 10 numbers. An example of the use of alphabetic words would be the name of an employee.

Example: John H Smith

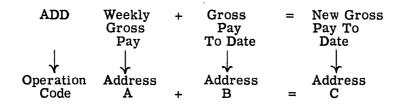

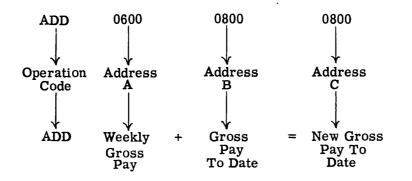

<u>Order words</u> are the instructions available to the programmer to guide the machine through a routine. The example shown under the numeric word description is the addition of weekly gross pay to gross pay to date to obtain a new gross pay to date. The 3 address order system used in the DATAmatic 1000 easily allows you to make this statement directly into a machine order.

Here the first 3 letters indicate the operation (ADD), the next 4 digits specify the address (Address A) or location in the 2000 word memory containing the Weekly Gross Pay, the next 4 digits (Address B) specify the address of the Gross Pay to Date and the last 4 digits (Address C) specify the location where the result of the addition (New Gross Pay to Date) shall be stored.

If the Weekly Gross Pay is located in memory address 600 and the Gross Pay to Date is located in memory address 800, the order appears in the following manner:

If the assignment of memory addresses had been 1643 and 1829 respectively the order would appear as:

ADD 1643 1829 1829

The coding of characters and operations within the machine need not concern the operator or programmer during normal operation.

#### Magnetic Tape External Storage

The 3 inch wide magnetic tape is one of the advancements available in the DATAmatic 1000 system. A single reel of tape can store up to 37, 200, 000 decimal digits (465, 000 fully punched 80 column cards) and moves at the rate of 100 inches per second. This tremendous capacity and speed permits 60, 000 decimal digits each second to be delivered to the central processing system for sorting, collating or other purposes. A single tape, when used as file storage, can store many years of historic files that require reference. Figure 1 shows how the magnetic oxide coating of the tape is sand-

# Figure 1. DATAmatic 1000 Magnetic Tape.

wiched between plastic layers that completely protect the recorded information and make the tape extremely durable.

The manner of recording information on the 3 inch wide magnetic tape has kept pace with the many other advancements available in the Magnetic File Unit and the tape itself. The DATAmatic 1000, to make more efficient use of the tape, records information along the tape in groups of 62 words each, called blocks. As shown in Figure 2, there are 31 levels across the tape and 2 words are recorded along the tape in each level when a block is recorded. In this fashion, 50,000 blocks of information are recorded on each tape.

| 7        | · · · · · · · · · · · · · · · · · · · | •            |               |         |     |

|----------|---------------------------------------|--------------|---------------|---------|-----|

| 2        | level 1                               |              | word 1        | word 2  | (   |

|          | level 2                               |              | word <b>3</b> | word 4  | /   |

|          | level 3                               |              | word 5        | word 6  |     |

|          | •                                     | ,            | word 7        | word 8  |     |

|          | •                                     | 3"           | •             |         | ł   |

|          | •                                     |              | ,             |         | N N |

|          | level 29                              |              | word 57       | word 58 | 1   |

| <b>_</b> | level 30                              |              | word 59       | word 60 |     |

| 5        | level 31                              | $\downarrow$ | word 61       | word 62 |     |

| <b></b>  |                                       |              |               |         |     |

Figure 2. Arrangement of Words on Magnetic Tape.

The Magnetic File Unit will traverse a single active block, including starting and stopping, in less than 18 milliseconds. When running continuously, 80 active blocks per second can be read either in the direction of recording or in the opposite direction.

Another advancement in the DATAmatic 1000 is the technique of recording the blocks themselves on tape. An interlace system is used to minimize the blank or dead spaces between the blocks. The dead spaces are normally necessary to permit the tape to accelerate and decelerate. This interlace is accomplished by recording on every other block while the tape is moving in one direction and upon reaching the physical end of the tape, returning and filling in the unrecorded blocks. Figure 3 shows this technique with arrows indicating the direction of tape motion.

Obviously, a further advantage of the interlace system is that, when a tape has been completely read or recorded, no rewinding is necessary because the tape is already back at its physical beginning.

To further improve the reliability of the magnetic tape storage, the principles of frequency modulation have been applied to the recording technique. Variations in signal amplitude now have no effect on the recorded information, thus increasing the quality of

Figure 3. Interlacing of Blocks on DATAmatic 1000 Tape.

the system in a manner similar to the well known improvement of frequency modulation over Standard Broadcast radio.

The recording techniques described are all completely automatic and therefore do not concern the programmer.

#### Magnetic Core Internal Storage

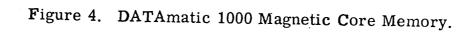

The ferrite magnetic cores used in the DATAmatic 1000 provide a high speed memory which is reliable, simple and compact. These cores, tiny doughnut-shaped rings, are strung together on fine wires as shown in Figure 4a.

A core can be magnetized in either of two opposite orientations. To distinguish them, one may speak of the "1" state and the "0" state. Thus, current passing through a core in one direction magnetizes the core in the "1" state as shown in Figure 5a, while current passing through the core in the opposite direction magnetizes the core in the "0" state. Using two wires for this purpose, as in Figure 5b, allows a group of cores to be arranged on common wires in a plane as in Figure 4a, since any desired core in the plane can be magnetized in the "1" or the "0" state by passing current through an appropriate pair of horizontal and vertical wires.

(b)

(a)

Figure 5. Typical Magnetic Core.

A single core plane contains 2,000 cores and thus can store, for example, the first pulse of each of the 2000 possible words to be stored in the memory. By stacking 52 of these planes together as in Figure 4b, 52 cores can be selected simultaneously (one in each plane) and thus a single machine word (numeric, alphabetic or order) is stored.

The total of 104,000 cores store the equivalent of 24,000 decimal digits or 16,000 alphabetic characters. Information is obtained from any one of the 2000 addresses, 12 decimal digits at a time, in approximately ten millionths of a second.

Certain addresses in the group 1983 to 1999 are of special interest. Those from 1983 to 1989 are usually reserved for control purposes and may be selected automatically as order sources under certain circumstances. Addresses from 1990 to 1999 are located in the Arithmetic and Control Units and contain special words used for control purposes. They can be read into and out of by orders.

#### **Intermediate Storage Units**

The need of management to handle large amounts of data is not filled by electronic processing speed alone. Many procedures are limited by the rate at which information stored on magnetic tape can be made available to the electronic high speed processing of the central machine.

The Input and Output Intermediate Storage Units of the DATAmatic 1000 are the devices that permit information to be transferred between the tape and the Central Processor at a constant rate. This rate of delivery of information may be maintained while the Magnetic File Unit is scanning the tape, at the rate of 80 blocks per second.

Complete flexibility is maintained when transferring between the Intermediate Storage Units and the magnetic core memory, both in the number of words being transferred and in the location in the memory where the information is stored.

The scope of application is greatly increased by the ability of the Input Intermediate Storage Unit to receive information simultaneously from 10 different Magnetic File Units. This feature makes it possible to search, simultaneously, on 10 Magnetic File Units.

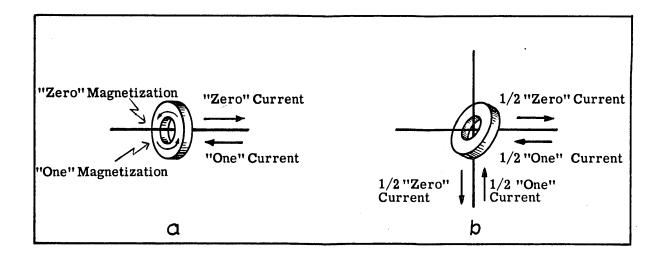

The Input Intermediate Storage Unit consists of two high speed storage sections each being capable of handling 62 words. Each section may be controlled independently or both may be coordinated to act as a single unit. Figure 6 shows in two diagrams the ability of this unit to accept one block of information from tape while transferring other information to the core memory for processing.

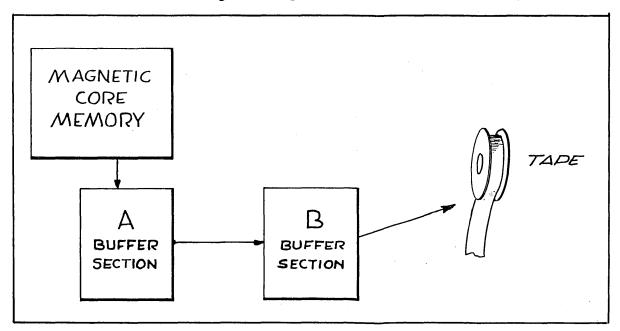

The Output Intermediate Storage Unit also consists of two high speed storage sections each capable of handling 62 words. Figure 7 shows how one block of information can be written onto magnetic tape while another block is being accumulated for later writing.

#### PROGRAMMING AND OPERATION

Many steps are followed prior to running a procedure on a machine. The procedure is first analyzed and broken down to the operations that can be performed by the DATAmatic 1000. Usually these procedures are set down in a detail flow chart. The instructions or orders that fulfill the purpose of the flow chart are then recorded on paper. For example, the procedure flow chart might indicate "Compute Gross Pay". Three instructions are necessary to accomplish this, assuming the source data (the time card) has been converted to magnetic tape. First read the information (employee identification, hours worked, rate of pay) from tape to the intermediate storage unit -- a read tape order. Second transfer information from the intermediate storage to the memory - - a transfer order. Third multiply hours worked times rate of pay - - - a multiply order. The setting down of the read order, the transfer order and the multiply order in sequence and in the form that can be interpreted by the machine is called programming. The complete sequence of instructions necessary to carry out a desired procedure are written down in this fashion and then recorded on the magnetic tape. Once this has been read into the high speed core memory the operator needs merely to manually insert a tape read order and a Transfer In order and depress the start button. The DATAmatic 1000 system will perform these instructions, and then proceed automatically to carry out each of the other instructions in sequence.

Each order, in turn, is selected from the high speed memory location whose address is contained in the Sequence Register. Unity is automatically added to the contents of the Sequence Register immediately following the selection.

Figure 7. Output Buffer Storage.

To provide flexibility of control, some orders have the ability to change the contents of the Sequence Register and thus change the sequence of operations. When this occurs, the Sequence Register is changed to the address indicated by the order being processed. After completion of such an order the next order is obtained from the new setting of the Sequence Register. The tape orders and control orders have this ability to change the Sequence Register.

Also available to the programmer is the ability to "subsequence" or step out of the normal sequence of orders to perform some extra order and then return to the normal sequence.

A further ability available in the DATAmatic 1000 is its ability to modify its own orders or to compose new orders, based on decisions which it makes in processing a set of information. This is possible since, as pointed out earlier, an instruction "word" looks just like a numeric or alphabetic word. Therefore the machine can choose to look on an instruction as a numeric word and modify it by an arithmetic operation.

An additional feature of the DATAmatic 1000 is that the programmer can easily tag any order as a sentinel order which will tell the computer that it has now reached a particular place in the program where special action should be taken. This powerful feature permits the utmost flexibility for the programmer.

Automatic programming is still another feature of the DATAmatic 1000. Delivered with each installation will be a library of routines which can be assembled by the programmer in many different variations by merely inserting a group of key instructions into the system. This automatic programming facility cuts to a minimum the time required to set up any desired program.

#### CHECKING

The DATAmatic 1000 is a completely internally checked machine. Four different types of <u>automatic checking</u> are performed to insure the accuracy that is required in processing business data. These built-in checking features when combined with the powerfully designed circuits (circuits which operate even though a tube is 50 percent weak) make the DATAmatic 1000 the most accurate machine available to management.

The four general types of automatic checking available are:

| <u>Transfer Checking</u> - to prove information is transferred between any two portions of the machine correctly.                          |

|--------------------------------------------------------------------------------------------------------------------------------------------|

| Arithmetic Checking - to prove the accuracy of all arithmetic operations.                                                                  |

| <u>Selection Checking</u> - to prove that proper interpretation is made of the orders and that the correct memory locations were selected. |

### <u>Tape Safe Checking</u> - to prove the proper tape unit has been selected and to guarantee against destruction of information on tape due to malfunction.

In addition, other specific automatic checks are provided to ensure the utmost in reliability. There is even an automatic double-check which checks the check circuits.

These types of checking are completely automatic and do not concern the programmer. In the event of an error the machine will stop and the type of failure will be indicated by lights on the console.

As part of a normal maintenance procedure a Marginal Checking system is used. This system detects weak components prior to their failure thus insuring operating time that permits a day's work to be done in a day's time.

#### DATAmatic CENTRAL PROCESSOR (TYPE 1000)

The DATAmatic Central Processor (Type 1000) consists of a High Speed Memory, an Input Buffer Storage Unit, an Output Buffer Storage Unit and a Manipulative Section consisting of an Arithmetic Unit and a Control Unit. As many as 100 Magnetic Tape Units may be controlled by the Central Processor.

The operation of the Central Processor is governed by orders which are stored in the High Speed Memory. As described earlier, each order constitutes one word and consists of an operation code and three addresses. Unless otherwise specified, orders are selected in sequence from the High Speed Memory. However, as previously mentioned under Programming, there are special provisions whereby this sequence may be departed from for one or more orders.

Transfer of information between the Central Processor and the Magnetic File Units takes place by way of the Input and Output Buffer Storage Units. The information channels on the tape are numbered from 1 to 31. The sequence in which the words are recorded on the tape via the Output Buffer Storage Unit is preserved, so that when information is recovered from tape, the 62 words of each block are delivered by the Input Storage Unit in the same sequence, regardless of the direction of tape motion. Channel 1 on the tape is called the key channel. It contains words 1 and 2 of each block which can be coded words identifying the contents of the block if the tape is a file tape. The other channels are called satellite channels.

Isolation between the reading and recording circuits is provided by relays, controlled by the orders. When a channel is in the Write state, it is connected to the recording circuits; when it is in the Read state it is isolated from them. The states of the key and satellite channels of each Magnetic File Unit are independent, and the Magnetic File Units are independent of each other. Any combination of states of the key and satellite channels of all the Magnetic File Units is legitimate, except that no Magnetic File Unit may have its key channel in the Write state and its satellite channels simultaneously in the Read state.

In searching, the key channel only of the selected Magnetic File Unit is read to a designated channel of the Input Storage Unit. Each Magnetic File Unit is addressed by a two-digit number, and the Magnetic File Units are grouped according to the units digit of this address; all Magnetic File Units of a group search to the same Input Storage Channel.

The Input Buffer Storage Unit consists of two halves, the A half section and the B half section as shown in Figure 6, each capable of storing 62 words. Information may be transferred from a selected Magnetic File Unit to a selected half of the Input Buffer Storage or from a selected half of the Input Storage to the High Speed Memory under the control of an appropriate order. Except in the case of searching, a full block of information comprising 62 words is transferred from the tape to the selected section of Input Storage. Except in the case of the Key Comparison orders, words are transferred sequentially from the selected section of Input Storage to the High Speed Memory, word 1 being transferred first. This is a destructive readout. As the words of the selected buffer half section are exhausted, fillers are automatically supplied. The two sections of the input Storage Unit are selected and operated independently.

During transfer of information between the High Speed Memory and Input or Output Buffer Storage, words are examined to see if they are sentinels. Sentinel sensing is the feature of the DATAmatic 1000 that provides an automatic monitoring of information under programmed control. This feature may be used with all orders that transfer information between the High Speed Memory in either Input or Output Buffer Storage Units. The sentinel is used by the Programmer to denote such conditions on tape as: beginning of information, end of information, classification of groups of information, the marking of an item as special or different, control input or output tape orders, and other such conditions.

A sentinel is any word having zeroes as the two highest order binary digits. The disposition of sentinels is specified in the descriptions of the orders.

Information is transferred to the Output Buffer Storage Unit for recording on magnetic tape. The Output Storage Unit consists of two sections each having a capacity of 62 words as shown in Figure 7. The A section of Output Storage accepts words transferred sequentially from the High Speed Memory. Under control of a Write order, the contents of the A section are transferred to the B section and subsequently recorded on the selected Magnetic File Unit, leaving the A section free to accept further information. If 62 or fewer words are transferred to Output Storage, the first two words will be recorded sequentially in the key channel, and fillers will be supplied where necessary to make up a full block. If more than 62 words are transferred to Output Storage before a Write order, sufficient words will be discarded, beginning with the first, to leave 62. The first two words not discarded will be recorded in the key channel. A full block of data (including fillers where needed) is always recorded.

Recording on magnetic tape, recovery of information from magnetic tape, and high speed manipulation, including transfer of information to and from the Buffer Storage Units, may all take place simultaneously, subject to the following restrictions (note that searching is considered separately from reading):

- 1. If any Magnetic File Unit is busy reading, no other Magnetic File Unit may be reading or searching.

- 2. If any Magnetic File Unit is searching, no other Magnetic File Unit in the same group (having the same units digit) may be searching.

- 3. Only one Magnetic File Unit may be writing at any one time.

- 4. If any Magnetic File Unit is reading or searching with its satellite channels in the Write state, the other Magnetic File Units are prevented from writing.

- 5. When any Magnetic File Unit is busy reading, searching or writing, a new order for the same Magnetic File Unit is delayed until the previous read, search or write is completed.

No precautions are necessary on the part of the user to prevent any of the above situations since automatic interlocking circuits prevent them from occurring.

|                                    | BIT POSITION              |

|------------------------------------|---------------------------|

|                                    | TRANSFER WEIGHT           |

|                                    |                           |

|                                    | ORDER WORD                |

| HOUSANDS DIGIT)                    |                           |

| HOUSANDS DIGIT)<br>HOUSANDS DIGIT) | ORDER WORD<br><u>No</u> 2 |

| DIGITS                             |                           |

| DIGITS                             | ORDER WORD                |

| DS DIGITS                          | <u>NO</u> 3               |

|                                    | ſ                         |

|                                    | ORDER WORD<br><u>NO</u> 4 |

|                                    |                           |

|                                    | NUMERIC WORD              |

|                                    | ſ                         |

|                                    | ALPHABETIC WORD           |

# LEGEND:

- Ds THE SIGN OF THE ORDER

- Da THE MEMORY DESIGNATOR (THOUSANDS DIGIT)

- DE THE MEMORY DESIGNATOR (THOUSANDS DIGIT) OF ADDRESS B

- DC THE MEMORY DESIGNATOR (THOUSANDS DIGIT) OF ADDRESS C

SUBSCRIPT U UNITS DIGITS t tens digits h hundreds digits

|    | 52               | 51        | 50             | 49                            | 48 | 47        | 46                     | 45                    | 44      | 43        | 42                     |

|----|------------------|-----------|----------------|-------------------------------|----|-----------|------------------------|-----------------------|---------|-----------|------------------------|

| Γ  | 8                | 4         | 2              | 1                             | 8  | 4         | 2                      | 1                     | 8       | 4         | 2                      |

|    |                  |           |                | ·                             | ·  |           |                        |                       |         |           |                        |

| RD |                  | me<br>des | emo<br>igno    | ory<br>ator                   | 0  | PE        | R۵                     | τı                    | ON      | I C       | 0                      |

|    | Ds               | Da        | D <sub>0</sub> | D <sub>c</sub>                |    |           | (                      |                       | )       |           |                        |

| RD | Ds               | D         | B              | D <sub>c</sub>                | 0  | PE        |                        | TI<br>D <sub>F</sub>  |         | C         | 0[                     |

| RD | Ds               | des       |                | ory<br>ator<br>D <sub>c</sub> | 0  | PE        | RA<br>(                | TI<br>Df              |         | C         | ;0[                    |

| RD | Ds               | des       | igno           | ory<br>ator<br>D <sub>c</sub> | 0  | PE        |                        | .ті<br>О <sub>ғ</sub> |         | С         | ;0[                    |

|    | S<br>I<br>G<br>N |           | 0              | 1                             |    | <br>D   ( | th<br>G I <sup>-</sup> | T                     | [       |           | ) <sup>th</sup><br>3∣⁻ |

| RD |                  |           |                | th<br>ACT<br>hifi             |    |           | С                      | ΗÆ                    | 7<br>AR | ∙th<br>AC |                        |

|    |                  |           |                | -                             |    |           |                        |                       |         |           |                        |

|      |        |          |                |                |              | <b>.</b> . |           |                |                        |                        |    |            |                       |                        |          |                    |            |     |             |                       |            |      |          |                         |                        |                |           |           |            |          |                        |      |     |          |                       |          |     |                  |           |        |                 |             |   |            |                                   |   |

|------|--------|----------|----------------|----------------|--------------|------------|-----------|----------------|------------------------|------------------------|----|------------|-----------------------|------------------------|----------|--------------------|------------|-----|-------------|-----------------------|------------|------|----------|-------------------------|------------------------|----------------|-----------|-----------|------------|----------|------------------------|------|-----|----------|-----------------------|----------|-----|------------------|-----------|--------|-----------------|-------------|---|------------|-----------------------------------|---|

|      | 52     | 51       | 50             | 49             | 48 4         | 474        | 464       | 54             | 44                     | 342                    | 41 | 403        | 393                   | 8 37                   | 7 30     | 6 35               | 5 34       | 133 | 32          | 31                    | 30         | 29 : | 28 2     | 72                      | 6 25                   | 524            | 23        | 22        | 21         | 20       | 19 1                   | 8 17 | 716 | 15       | 14                    | 13 1     | 211 |                  | 9         | 8      | 7               | 6           | 5 | 4 3        | 2                                 | 1 |

| ЭНТ  | 8      | <u> </u> | 2              |                |              | 4          |           | 1 6            |                        | 2                      |    | 8          |                       |                        | -        | 4                  | 1          | 1   | 8           |                       | 2          |      |          | 4 2                     |                        | 8              |           |           | 1          |          | 4                      |      | 8   |          | 2                     | 1 8      |     |                  |           | 8      | 4               | 2           | 1 | 8 4        | 2                                 | 1 |

| ORD  |        | de:      | iemo<br>signo  | ator           | OF           | PEF        |           |                | N                      | CO                     |    |            |                       | D D<br>reds            | <b>T</b> |                    |            |     | <br>        | 4<br><br>u n i        | ts         |      | hur      |                         | D [                    | -1             |           | ·         | r          | B        |                        |      |     |          | A D<br>Ired           | - r-     |     | S S<br>ens       |           | (<br>( |                 | its         | _ | WE I<br>CO | <u>UN</u>                         |   |

|      | DS     | Da       | D <sub>b</sub> | D <sub>c</sub> |              |            | <u> </u>  | P              |                        |                        |    |            |                       | its                    | İ        | te<br>dig          | gite       | 5   |             | dig                   | jits       |      |          | igi                     |                        | i<br>          | te<br>dig | gits      | 5 <b> </b> | d        | uni<br>ligi            | ts   |     | diç      | jits                  |          | di  | git              | S         |        |                 | its         |   | \          | $\mathcal{N}_{-}$                 |   |

| ORD  | Ds     | D        | B              | D              | OF           | ΡEF        | ат<br>С   | 10)<br>P       | N                      | 20[                    | DE | <u>hur</u> |                       | D D<br>reds<br>ts      |          |                    |            | • · |             | un                    | its<br>its |      |          | Bı                      |                        | B <sub>F</sub> | Bd        | Ba        |            | E        | <sup>3</sup> 2         |      |     | <br>und  | A D<br>red<br>gits    | -T<br>sl |     | SS<br>ens<br>git | - <b></b> |        | C<br>uni<br>dig |             |   | W E<br>CO  |                                   |   |

| ORD  | Ds     | de<br>   |                | ator           | OF           | PEF        | TAR<br>C  |                | N                      | 20[                    | DE |            | ndr                   | D D<br>eds             | 1        | - <u>-</u> -<br>†e | <br>ens    |     | Α<br>Τ<br>Γ | un.                   | its        |      | hun      | ndre                    |                        | 7-             | te        | ns        |            |          | nit                    |      | -   | m        | eanir                 | ngle     | SS  |                  |           |        | C <sub>2</sub>  |             |   |            | JN                                |   |

|      |        |          |                |                |              |            |           | <u>Р</u>       | <del></del>            |                        |    |            | igi                   | 15                     |          | di                 | gn         | 5   | 1           |                       | jits       |      | <u>u</u> | igit                    | 5                      |                | dig       | 115       | 1          | u        | igi                    | 15   |     |          |                       |          |     |                  |           | -      |                 |             |   |            | N                                 |   |

| ORD  |        |          | emo<br>signo   | ator           |              |            | <br>> ^ T |                |                        |                        |    |            | Α                     | DD                     | ) R      | ES                 | SS         |     | Δ           | \                     |            |      |          | Bh                      |                        | 0              | 1         | 0         |            | mea      | ning                   | less |     |          | A D                   | DF       | RE  | SS               | 6.<br>    | (      | C               |             | ļ | WEI        |                                   |   |

|      | Ds     | Da       | Db             |                |              | <u>с</u> г | ~         | ) <sub>P</sub> |                        |                        |    | nur        | ndr<br>igi            | eds<br>ts              |          |                    | ens<br>git |     |             | un<br>dig             |            |      |          | <sup>D</sup> n          |                        |                | B         | t         |            |          |                        |      | h   |          | red<br>jits           |          |     | ens<br>git       |           |        | uni<br>dig      |             |   |            |                                   |   |

| 2D   | S I GN |          | 0              |                | D            | II<br>IG   |           |                |                        | o <sup>th</sup><br>GIT |    |            | 9 <sup>† </sup><br>IG |                        |          | 8<br>DI            | 3th<br>G1  |     | [           | 7 <sup>1</sup><br>DIG |            |      | -        | , th<br>Gl <sup>-</sup> |                        |                | 5<br>DI(  | th<br>GIT |            |          | 4 <sup>th</sup><br>IGI |      | [   | 3<br>DIG |                       |          |     | nd<br>IGI        |           |        | ן<br>סוס        | st<br>GIT   |   |            | gh<br>UN <sup>-</sup><br><b>N</b> |   |

| WORD | 1      |          |                | CT             | TE F<br>cant |            | СН        |                | 7 <sup>††</sup><br>RA( | n<br>CTE               | ĒR | СН         |                       | S <sup>th</sup><br>RAC |          | ER                 | C          | CHA | -           | th<br>AC              | ΤE         | R    | СН       |                         | 4 <sup>th</sup><br>RA( |                | ER        | С         | НΔ         | 3<br>ARA |                        | ER   | c C | ΉΔ       | 2 <sup>r</sup><br>\RA |          | ER  |                  |           | ۹R.    |                 | TEF<br>ant) | ۶ |            | gh<br>unt<br><b>N</b>             |   |

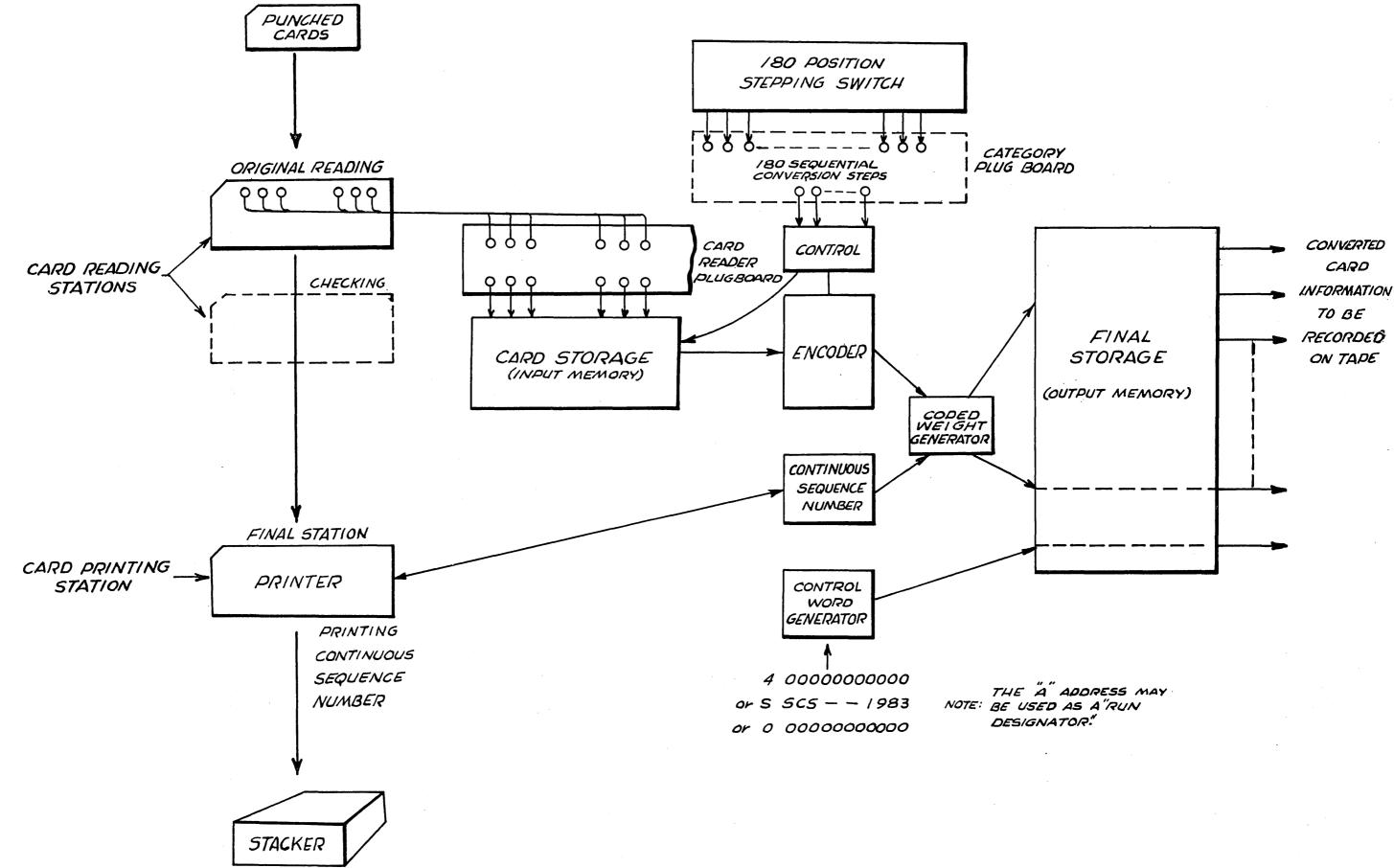

#### DATAmatic 1000 ORDER DESCRIPTIONS

#### Introduction

The DATAmatic 1000 employs a three-address order system in which each order contains a three-letter operation code and three four-decimal-digit addresses (A, B and C) arranged as shown in Figure 8.

| Operation Code Address A |                  |  |  |  |  |  | A           | ddres      | s B       |            | Address C   |            |           |            |  |  |

|--------------------------|------------------|--|--|--|--|--|-------------|------------|-----------|------------|-------------|------------|-----------|------------|--|--|

|                          | Second<br>letter |  |  |  |  |  | B<br>thous. | B<br>hund. | B<br>tens | B<br>units | C<br>thous. | C<br>hund. | C<br>tens | C<br>units |  |  |

Figure 8. DATAmatic Order Word Structure.

Normally an "address" refers to a storage location in the High Speed Memory and lies in the range 0000 - 1999. The usage of three addresses in an order is made clear by simple arithmetic examples, like "ADD the contents of Address A to the contents of Address B and deliver the result to Address C", which would be encoded ADD A B C.

However, there are orders which by their nature require less than three addresses, and, at the same time, require special numeric information. In such cases one of the address portions of the instruction word may carry numeric information which is not an address. This usage of an address portion is discussed fully in the order descriptions.

All programming can be done in this mnemonic notation. The Input Routine converts this order word to the internal machine form, so care should be taken to examine this internal form before serious detailed programming is undertaken.

Any order can be made a sentinel order provided its A address is not greater than 0999. To specify that the order is a sentinel order, place the letter "s" at the end of the order.

In the descriptions of the orders which follow, they are grouped for convenience into categories according to the type of function they perform.

#### Calculating Orders

The Calculating Orders group contains the usual arithmetic orders plus the SUB-STITUTE order. In all orders of this group the address positions are used to denote actual High Speed Memory Storage locations.

#### ADD ADD

Add the number at address A to the number at address B and deliver the sum to address C. In the event of an overflow, there is an automatic subsequence call to memory location 1988 where the first order of an appropriate routine is stored.

When using this order to modify another order the address of the order to be modified should go into the A position.

#### SUB SUBTRACT

Subtract the number at address B from the number at address A and deliver the difference to address C. In the event of an overflow, there is an automatic subsequence call to memory location 1988 where the first order of an appropriate routine is stored. When using this order to modify another order the address of the order to be modified should go into the address A position.

#### MUL MULTIPLY

Multiply the number at address A by the number at address B. Store the (rounded) high-order half of the 22-digit product in address C and the low-order half in the "Remainder" register (1995), each half accompanied by the sign of the product. Rounding is accomplished by adding 5 (with the same sign as the product) into the highorder digit of the Remainder register and permitting carry into the low-order digit of address.

#### DIV DIVIDE

Divide the number at address B by the number at address A. Deliver the quotient to address C and the remainder to the Remainder register (1995), unless the numerator equals or exceeds the denominator. If the numerator equals or exceeds the denominator in absolute value, make an automatic subsequence call to memory location 1986 where the first order of an appropriate routine is stored.

#### SST SUBSTITUTE

From the numbers stored at address A and address C form a new number and store it at address C. The new number is formed under the control of an Extractor word which is stored at address B. The Extractor may control the extraction of alphabetic or numeric characters or portions of characters. Thus, wherever the extractor digit is a 1, the new word gets its corresponding character from address A. Wherever the extractor digit is a 0; the corresponding character in address C is preserved.

# Notes

Calculating Orders

1. The Calculating orders are of word type 1 (see detailed word structure at end of orders.)

MULTIPLY - Both the Select Order Register (1994) and the Sentinel Register (1997) (see description of Addresses of Significance) are used by the Arithmetic Unit in performing multiplication. After the completion of a multiply order, unless the product is transmitted to one of them, these two registers contain respectively 7 times the word at address A and 4 times the word at address A - in each case without a sign.

- 3. MULTIPLY-DIVIDE If either operand contains a nondecimal 4-bit group or an incorrect sign, a weight count error occurs.

- 4. SUBSTITUTE The Extractor stored at address B may have any bit configuration. Each bit of address C is preserved if the corresponding bit of address B is a zero otherwise the bit of address C is replaced by the corresponding bit of address A.

#### Shift Orders

A group of orders are provided for shifting information within the machine. Shifting is defined as moving the characters of a machine word either right or left within the word itself.

In the Shift Orders, the A and C addresses are used for denoting High Speed Memory storage locations; the B address contains information controlling the amount of the shift. No attempt should be made to modify the amount of the shift internally without consulting a description of the internal machine structure of the order.

#### SLP SHIFT LEFT PRESERVING SIGN

Shift the word at address A to the left by the number of digit spaces indicated in address B, keeping the sign unchanged and unshifted. "B" must be in the range 0-12. Deliver the result to address C. The word remains unchanged at address A.

#### SLA SHIFT LEFT, ALPHABETIC

Shift the word at address A to the left by the number of alphabetic spaces indicated in address B, and deliver the result to address C. "B" lies in the range 1-8. This shift includes the sign position. The word remains unchanged at address A.

#### SLN SHIFT LEFT NUMBERIC, SIGN INCLUDED

Shift the word at address A to the left by the number of digit spaces indicated in address B, including the sign position. "B" must be in the range 0-12. Deliver the result to address C. The word remains unchanged at address A.

#### SRP SHIFT RIGHT PRESERVING SIGN

Shift the word at address A to the right by the number of digit spaces indicated in address B, keeping the sign unchanged and unshifted. "B" must be in the range 0-12. Deliver the results to address C. The word remains unchanged at address A.

#### SRA SHIFT RIGHT ALPHABETIC

Shift the word at address A to the right by the number of alphabetic spaces indicated in address B, and deliver the result to address C. "B" lies in the range 1-8. This shift includes the sign position. The word remains unchanged at address A.

#### SRN SHIFT RIGHT NUMERIC, SIGN INCLUDED

Shift the word at address A to the right, by the number of digit spaces indicated in address B, including the sign position. "B" must be in the range 0-12. Deliver the result to address C. The word remains unchanged at address A.

# Notes

#### Shift Orders

- 1. The Shift Orders are of word type 4 (see detailed DATAmatic Order Word Structure following description of orders). The amount of shift, is controlled by  $B_h$  and  $B_t$ . In every case the number of 4-bit shifts to be made is indicated by  $B_h$ , which is a hexadecimal digit in the range 0-12. For SLP and SRP orders  $B_t = 0$ . For the other shifts  $B_t$  can be zero or 5. If it is 5, an extra 2-bit shift occurs after the indicated number of 4-bit shifts has been completed. In the alphabetic shifts, the Input Routine converts "B" to the appropriate number of 4-bit shifts, and uses the 2-bit shift if necessary.

- 2. The B address may be modified by additions, except through the transition between  $B_h = 9$  and  $B_h = (10)$  (hexadecimal). The rule for modifying orders given with the ADD order description should be followed.

#### Buffer Transfer Orders

The orders of this group are used for transferring words between the Buffer Storage Units and the High Speed Memory. Information transmission between the High Speed Memory and magnetic tape passes through the Input and Output Buffers. Orders of the Tape Control group are concerned with the phase of the transmission between the magnetic tape and the Buffers. In addition to the Buffer Transfer orders described here the Key Comparison orders (described under Comparison Orders) transfer words into the High Speed Memory from the Input Buffer Storage.

The word structure of these words is:

| Ope             | ration C         | ode             |  | Addres     | ss A      |                   |             | Addre      | ss B      |            | Address C   |                                  |       |   |  |  |

|-----------------|------------------|-----------------|--|------------|-----------|-------------------|-------------|------------|-----------|------------|-------------|----------------------------------|-------|---|--|--|

| First<br>letter | Second<br>letter | Third<br>letter |  | A<br>hund. | A<br>tens | <b>A</b><br>units | B<br>thous. | B<br>hund. | B<br>tens | B<br>units | C<br>thous. | C C C C<br>ous. hund. tens units |       |   |  |  |

|                 |                  |                 |  |            |           |                   | В           | 1          | E         | 32         |             |                                  |       | 1 |  |  |

|                 | Storage          |                 |  |            |           |                   |             | Con        | trol      |            |             | Subse                            | quenc | e |  |  |

Address B is divided into two parts B1 and B2. B1 consists of the hundreds and and thousands digits of address B. B2 consists of the units and tens digits of address B. Both B1 and B2 are restricted to the range 1-32. No attempt should be made to modify address B internally without reference to the bit-structure of the order.

In each of the orders of the Buffer Transfer group, address A is the first location of a segment of the High Speed Memory to or from which B2 words are to be transferred. The range of addresses specified by A and B2 should not include Special Registers nor, in the same order, both 0999 and 1000. Address C provides for a Subsequence Call if desired and should not be 1990.

If a Weighted Count error is detected in any word transferred in, or in the Buffer word following the last one transferred in, the result is an automatic Subsequence Call to register 1985 where the first order of an appropriate routine is stored, or else results in a computer Stop, depending upon whether the Central Console "Rerun" switch is on or off.

For each type of order in this group which provides for transfer from the Input Buffer, the transfer can be made from either the A section or the B section. The choice of section is governed by the third letter of the code symbol. Thus, if the third letter of the code symbol is:

- A Transfer from the A section of the buffer

- B Transfer from the B section of the buffer

- S Transfer from the <u>same</u> section of the buffer to which the last previous connection was made (by Transfer In, Double Transfer and Select, Transfer and Select, or Read Orders)

- D Transfer from a different (the opposite) section of the buffer to which the last previous connection was made (by Transfer In, Double Transfer and Select, Transfer and Select, or Read Orders)

#### TRANSFER IN

The eight TRANSFER IN orders fall into two sets as follows:

- TIA Hold up if necessary, via the interlock, the transfer of words

- TIB from Input Buffer to the High Speed Memory until the Input

- **TIS** Buffer has received a block of words from a file unit as a result

- TID of the last Read order initiated prior to this order. This interlocking is necessary for the situation in which an order is given to transfer information out of one half of the Input Buffer after a Read order has been given to read information from tape into that same Buffer half.

- TBA Transfer words from Input Buffer to High Speed Memory during

- **TBB** the period between the time a Read order is given and the time

- **TBS** that the transfer of words from the file unit to the Input Buffer

- **TBD** is actually begun, by bypassing the interlock mentioned above.

Each of the orders causes the transfer of B2 words from the Input Buffer to consecutive High Speed Memory locations starting at address A. The B2 words transferred and also the next word in the Input Buffer are examined for sentinels. The first sentinel sensed is stored in the Sentinel Register (1997). If no sentinel is sensed a PASS order (see Control Orders) is stored in the Sentinel Register.

If B2 exceeds the number of words contained by the Input Buffer section then fillers will be added to make up B2 words. These fillers are sentinel Sequence Change orders (see Control Orders) whose A and B addresses are void and whose address C is 1985. If B2 equals the number of words contained in the Input Buffer section a filler of this type (being a sentinel) will go to the Sentinel Register (1997).

Make a Subsequence Call to address C. B1 is not used.

#### DOUBLE TRANSFER AND SELECT

There are eight Double Transfer and Select orders which fall into two sets of four each. The sets are identical except for the fact that interlocks are used or not used, as described below:

| DTA | At step (2) below delay, by means of an interlock, the transfer |

|-----|-----------------------------------------------------------------|

| DTB | of words from the Input Buffer to the High Speed Memory until   |

| DTS | the Input Buffer has received a full block of new words as a    |

| DTD | result of the last Read order initiated prior to this order.    |

|     |                                                                 |

| DBA | At step (2) below begin transferring words immediately from the |

| DBB | Input Buffer to the High Speed Memory, bypassing the interlock  |

| DBS | referred to above                                               |

| DBD |                                                                 |

|     |                                                                 |

There are four steps required for the performance of each order:

- Transfer B2 words to the Output Buffer Storage from the consecutive High Speed Memory locations starting at address A.

Output Buffer overflow is not examined for sentinels.

- (2) Transfer B2 words from the Input Buffer to the consecutive Memory locations starting at address A. Examine the B2 words transferred and the next Input Buffer word for sentinels. The first sentinel sensed is stored in the Sentinel Register. If no sentinel is sensed, a Pass order is stored in the Sentinel Register.

If B2 exceeds the number of words contained in the Input Buffer section then fillers will be added to make up B2 words. These fillers are sentinel Sequence Change orders (see Control Orders) whose address B is void and whose address C is 1985. If B2 <u>equals</u> the number of words contained in the Input Buffer section a filler of this type (being a sentinel) will go to the Sentinel Register (1997).

- (3) Extract one digit from the B1th word transferred from the Input Buffer, add it to the units digit of address C permitting carry into the tens digit, and make a Subsequence Call to the resultant address C. The particular digit which is extracted will be determined by the word in the Extractor Register which can be made to choose any one of the digits of the B1th word.

- (4) Store this order itself in the Select Order Register (1994) in its original form (i.e., not in the modified form it has after the completion of step (3)).

#### TRANSFER AND SELECT

The eight Transfer and Select orders are identical to the eight corresponding Double Transfer and Select orders except that step (1) is omitted. Consequently, all description of these orders apply to Transfer and Select, except for step (1). The symbols for these orders are:

| TSA | At step | (2) hold up, | via an interlock, | the transfer | of words |

|-----|---------|--------------|-------------------|--------------|----------|

|-----|---------|--------------|-------------------|--------------|----------|

- TSB from Input Buffer Storage to High Speed Memory until Input

- TSS Storage has received a full block of new words as a result

- TSD of the last Read order initiated prior to this order.

- BSA At step (2) begin transferring words immediately from the

- BSB Input Buffer Storage to the High Speed Memory, bypassing

- BSS the interlock mentioned above.

- BSD

#### TXO TRANSFER OUT

Transfer the number of words indicated by the units and tens digits of address B to the Output Buffer Storage from the consecutive memory locations starting with address A. If there is an overflow of words from the Output Buffer Storage, examine the overflow words for sentinels. The first sentinel word which overflows is transferred to the Sentinel Register (1997). If no sentinel overflows, a Pass order is stored in this Sentinel Register. Address C can be used for a subsequence call if desired.

The number of words transferred by this order can vary from 1 to 32.

# Notes

| Buffer Transfer Orders                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| <ol> <li>The Buffer Transfer orders are of word type 2 (see de-<br/>tailed DATAmatic Order Word Structure following de-<br/>scription of orders). The numbers B1 and B2 are 5-bit<br/>binary numbers (with the high order bit of B1 located in<br/>bit position 50) covering the range 1-32, with 32 being<br/>represented by all zeros.</li> <li>The three basic types of orders are specified by the fol-<br/>lowing 2-digit (hexadecimal) Operation Codes:</li> </ol>                                             |  |  |  |  |  |

| Order Type Operation Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| TRANSFER IN153DOUBLE TRANSFER AND SELECT1510TRANSFER AND SELECT1411The eight variations of each type are obtained by using<br>the three control bits in bit positions 22, 23, and 24.If $B_p = 0$ the Input Buffer interlock remains in effect and<br>this corresponds to the first set of 4 orders under each<br>heading. If $B_p = 1$ the interlock is inactivated giving the<br>second set of 4 orders.The Buffer to Memory connection is controlled by bits.<br>$B_a$ and $B_d$ as shown in the following table: |  |  |  |  |  |

| B <sub>d</sub> B <sub>a</sub> Letter Effect on the Buffer-<br>Designation Memory Connection                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| 0 0 S Leave unchanged                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| 0 1 A Connect to the A-section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| 1 0 B Connect to the B-section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| 1 1 D Change the connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

# Notes

#### Buffer Transfer Orders (Cont.)

2. DOUBLE TRANSFER AND SELECT (8 orders), TRANS-FER AND SELECT (8 orders). Step (3) of the description of these orders can be done with more generality if the bit structure of the order is taken into account. The following substeps describe this step in detail.

(3a) Form a word, K, which has binary ones in those bit positions wherein both the (B2-B1)th word transferred in and the word in the Extractor Register (1993) have binary ones, and zeros elsewhere. Either word may have any bit configuration whatever.

(3b) Superimpose all 12 of the 4-bit groups (hexadecimal digits) of the word K resulting from substep (3a) onto one digit position. This results in a hexadecimal digit which has a binary 1 in a given one of its four bit positions if and only if one or more of the 12 digits of K has a binary 1 in the corresponding position.

(3c) Add the hexadecimal digit constructed in substep (3b) to the units digit of address C of the order, permitting carry into the tens digit. This addition is accomplished as if the hexadecimal digit had been converted to a decimal in the range 0-16 except that a weight count error occurs if

- (c<sub>1</sub>) the sum of the hexadecimal digit and the units digit of address C exceeds 19 or

- (c<sub>2</sub>) the sum of the hexadecimal digit and address C causes a carry into the thousands column of address C.

Make a Subsequence Call to the resultant address C.

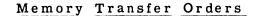

#### Memory Transfer Orders

There are three orders in the Memory Transfer group and they are used for making transfers of information from one part of High Speed Memory to another. One of them, the Transfer Internally (TXI) order, is the only order of the three which contains control information in the address C position.

#### TXI TRANSFER INTERNALLY

Transfer the number of words indicated by the units and tens digits of address C from consecutive memory locations starting with address A to consecutive memory locations starting with address B. The number of words transferred lies in the range 1-32. The range of addresses specified by "A" and "C" or by "B" and "C" should not include both 0999 and 1000 or any of the Special Registers.

If the programmer desires to modify the number of words expressed in address C, internal machine word structure should be understood.

#### TTX TWIN TRANSFER

Transfer the word in the Select Order Register (1994) to address A, and the word at address B to address C. This is a special order designed for use with the DOUBLE TRANSFER AND SELECT and the TRANSFER AND SELECT orders in sorting.

No Transfer is made to address A if this is the address of a Special Register (see Addresses of Significance). Neither address B nor address C should be 1990 (the Control Register).

#### TXS TRANSFER AND SUBSEQUENCE CALL

Transfer the word stored at address A to address B and make a subsequence call to address C. Neither address B nor address C should be 1990.

# Notes

- 1. TRANSFER INTERNALLY is an order of word type 3 (see detailed DATAmatic Order Word Structure following description of orders) and the number of words transferred is controlled by  $C_2$  which consists of 5 bits. When all bits are zero, 32 words are transferred.

- Address C cannot be modified by addition or subtraction through any part of its range which includes the pairs 9 and 10, 15 and 16, or 25 and 26.

#### Tape Control Orders

The Tape Control Orders are those which govern reading, writing, searching and rewinding of the Magnetic File Units. In each of the Tape Control Orders address B can be used for changing the Sequence Counter and address C for making a Subsequence Call. The units and tens digits of address A are used to designate the desired Magnetic File Unit.

If one of these orders (except the REWIND order) is given after the tape has reached its end (or its <u>beginning</u> in the case of the orders which move the tape backwards) the order is not executed. Instead, it is transferred to the Current Order Register (1999), and an automatic Subsequence Call is made to register 1989 where the first order of an appropriate routine is stored.

The operation of putting the key and satellite channels into the appropriate state for Reading, Searching, or Writing involves relay switching time; hence an order of this type can be performed more quickly if the channels have been left in the correct state by a previous order of the same type.

#### READING

Each READ order affects a Magnetic File Unit designated by the tens and units digits of address A. Each READ order (except for the READ FORWARD KEY and READ BACKWARD KEY) causes both the key and satellite channels of the specified Magnetic File Unit to be put into the Read state, if they are not already in that state. Then one block (62 words) from the designated tape is transferred to the indicated section of the Input Buffer. The reading may be accomplished in either the forward or reverse direction of tape movement. The resulting arrangement of information in the Input Buffer is independent of the direction of tape movement when a given block is read.

The third letter of the Operation Code governs the portion of Input Buffer into which the information from the tape is read.

#### READ FORWARD

| RFA | Read Forward to | the A section of | the Input Buffer. |

|-----|-----------------|------------------|-------------------|

|-----|-----------------|------------------|-------------------|

**RFB** Read Forward to the B section of the Input Buffer.

RFDRead Forward to that section of Input Buffer which was not<br/>read into by the last previous read order (i.e., change sections).Connect the section not being read into to the High Speed Memory.

#### **READ BACKWARD**

- **RBA** Read Backward to the A section of the Input Buffer.

- RBB Read Backward to the B section of the Input Buffer.

- RBD Read Backward to that section of Input Buffer which was not

read into by the last previous read order (i.e., change sections). Connect the section not being read into to the High Speed Memory.

There are two orders which permit the reading of the key channel into the B half of the Input Buffer, leaving the satellite channels in the Write state:

#### RFK READ FORWARD, KEY CHANNEL

Put the key channel of the Magnetic File Unit designated by the units and tens digits of address A into the Read state and the satellite channels in the Write state - if they are not already in these states, Read the key channel of one block to the B section of the Input Buffer, moving the tape forward.

RBK

#### READ BACKWARD, KEY CHANNEL

Same as RFK except that tape is moved backward.

#### WRITING

Writing consists of transferring one block of words from the Output Buffer to the Magnetic File unit designated by the units and tens digits of address A. If the Output Buffer is not full when the Write order is given, "fillers" are supplied in sufficient quantity to complete a block of 62 words. Each of these fillers is a sentinel Sequence Change order whose A and B addresses are void and whose C address is 1984.

If, on account of reaching the end of tape, a Write order can not be executed (see the earlier general discussion of Tape Control orders), the contents of the Output Buffer remain unchanged except that some fillers will have been added if needed.

Writing can be done only in the forward direction of tape movement.

WFA

#### WRITE FORWARD

Put both key and satellite channels of the designated Magnetic File Unit into the Write state, if they are not already in this state. Add fillers if necessary, and then Write one block.

#### WFP WRITE FORWARD, EXCEPT ON KEY CHANNEL

Put the satellite channels of the designated Magnetic File Unit into the Write state and the key channel into the Read state, if they are not already in the required states. Add fillers if necessary and then write one block.

#### SEARCHING

It is possible to search up to 10 tapes simultaneously, comparing the contents of the key channel of each tape with an interrogation key for branching control. One search order is used for each tape being searched (10 orders for 10 tapes) but the speed of processing is such that all the tapes being searched can be moving at the same time.

This is accomplished by designating a certain portion of the A-half of the Input Buffer to serve as ten independent "2-word Search Buffers" for each of the ten (or fewer) tapes. These ten 2-word Search Buffers are numbered zero through nine. The searching of any given tape is accomplished by reading its key channel into the 2-word Search Buffer having the same number as the units digit of that tape. This essentially means that the tapes can be considered grouped according to their units digit and only one tape from a group may be searched at a time. Thus, for example, tapes 20, 11, 42, 63, 84, 55, 36, 07, 98 and 79 can be searched at the same time. The example shows the restriction on the units digit but flexibility of the tens digit.