# FERRANTI PEGASUS COMPUTER

(F.P.C.I)

VOLUME 2

LOGICAL DESIGN

# FERRANTI PEGASUS COMPUTER

VOLUME 2

# LOGICAL DESIGN

# FERRANTI LTD.

Head Office: HOLLINWOOD, LANCASHIRE, ENGLAND

# COMPUTER DEPARTMENT

Offices and Works:

WEST GORTON WORKS THOMAS STREET WEST GORTON MANCHESTER, 12

Tel: EASt 1301

Copy No. 40

London Computer Centre:

21, PORTLAND PLACE, LONDON W.1

Tel: LANgham 9211

# SUMMARY

This volume, which forms part of the handbook on the Ferranti Pegasus Computer, deals with the logical design of the basic machine. This machine is supplied with a single high-speed tape punch and two photoelectric tape readers; provision has also been made for alternative input and output units to be added if desired. Modifications to the basic design made necessary by customers' special requirements will be dealt with in appendices or extra volumes issued separately. Two chapters, on binary arithmetic and logical operations, have been included for the benefit of readers who are not already conversant with the principles of digital computers.

This volume should be read in conjunction with Volume 2a, 'Logical Design (Diagrams)' and Volume 2b, 'Timing Charts'.

First issue MAY 1956

# CONTENTS

|         |      |             |         |        |        |        |     |     |    | Page |

|---------|------|-------------|---------|--------|--------|--------|-----|-----|----|------|

| CHAPTER | I    | BINARY ARI  | THMETIC | !      | ••     | ••     | • • |     | •• | 7    |

| CHAPTER | II   | LOGICAL OP  | ERATION | S      |        | ••     | ••  | ••  |    | 23   |

| CHAPTER | III  | BASIC LOGIC | CAL CIR | CUITS  | ••     |        | ••  | ••  | •• | 37   |

| CHAPTER | IV   | STORAGE AND | D THE O | RDER C | CODE   | ••     | • • | ••  |    | 47   |

| CHAPTER | v    | TIMING AND  | RHYTHM  | I      | ••     | ••     | ••  | ••  |    | 61   |

| CHAPTER | VI   | THE ORDER I | REGISTE | R AND  | DECODI | ING    | • • | • • |    | 71   |

| CHAPTER | VII  | THE MILL    |         | ••     | ••     | ••     | ••  | ••  | •• | 83   |

| CHAPTER | VIII | JUMPS       | • •     | ••     | ••     | ••     | ••  | ••  | •• | 91   |

| CHAPTER | IX   | STOPS AND S | STARTS  | ••     | •••    | ••     | ••  | ••  | •• | 99   |

| CHAPTER | X    | THE COMPUT  | ING STO | RE     | ••     | ••     | ••  | ••  | •• | 107  |

| CHAPTER | XI   | MAIN-STORE  | TRANSF  | ERS    | ••     | ••     | ••  | ••  |    | 115  |

| CHAPTER | XII  | INPUT AND   | OUTPUT  | ••     | ••     | ••     | ••  | ••  | •• | 127  |

| CHAPTER | XIII | MULTIPLICA  | TION    | ••     | ••     |        |     | ••  |    | 137  |

| CHAPTER | XIV  | DIVISION    |         | ••     | ••     | ••     |     | ••  | •• | 147  |

| CHAPTER | xv   | ADDRESSES ( | 6 AND 7 | AND J  | USTIFI | CATION | I   |     | •• | 159  |

| CHAPTER | XVI  | SHIFTS      | ••      | ••     |        | ••     |     | ••  |    | 165  |

| CHAPTER | XVII | MONITORING  | FACILI  | TIES   |        |        |     |     |    | 175  |

# ERRATA

- Page 57, para. 31

In the modifier column of the subroutine for 2 read 1

- Page 73, para. 9, line 5

For paragraph 27 read paragraphs 30 to 32

- Page 79, para. 31, line 2

For gate y read gate x

- Page 47, para. 3, line 7

Delete oblique after significant

- Page 100, para. 6, lines 1 and 3 For 12D2 read 12Q1

- Page 51.

For para. 17 read para. 15.

- Page 107, para. 1, line 3

For if read of

- Page 116, para. 4, line 8 For ROO read RO4

- Page 120, para. 23, line 8

After inhibited add by X77

line 9

Page 129, para. 11, line 2

For sprcoket read sprocket

After storage add or a supernumerary drum address have been specified in a 'read' order

- Page 130, para. 14, line 12

For taoe read tape

- Page 133, para. 23 line 3

Delete bracket after components

- Page 137, para. 3 line 1 For fig. 14.1 read fig. 13.1

- Page 175, para. 2, line 13

For 5 Kc/s read 500 c/s

- Page 176, para. 4, line 2

For continuously read continually

- Page 177, para. 10, line 4 and Page 178, para. 14, line 1

For red read black

- Page 181, para. 21

The function defining AE should be V3 & A & not J & not E

# CHAPTER I

# BINARY ARITHMETIC

|                        |      |       |     |     |       |     |     | Para. |

|------------------------|------|-------|-----|-----|-------|-----|-----|-------|

| SYSTEMS OF NUMERATION  | • '• | • •   | ••  |     | •••   |     |     | 1     |

| Place Value            | • •  | • •   | ••  | • • | ••    |     | ••  | 1     |

| Radices                | .• • | • •   | ••  | • • | • • • | ••  |     | 4     |

| The Binary Scale       | ••   | ••    | ••  | ••  | ••    | • • | • • | 6     |

| ARITHMETICAL PROCESSES |      |       | ••  |     |       | • • | • • | 10    |

| Addition               |      |       |     |     | ••    | ••  | • • | 10    |

| Subtraction            |      | •, •  | • • | • • | ••    | ••  |     | 12    |

| Negative Numbers       |      |       | ••  |     | • •   | ••  | • • | 14    |

| Overflow               |      | ••    |     |     |       |     | ••  | 16    |

| Multiplication         | ••   | ••    | ••  |     |       |     | • • | 18    |

| Rounding               | • •  | • •   | • • | ••  |       | ••  | ••  | 21    |

| Division               | • •  | • •   | • • | • • | • •   | ••  | • • | 23    |

| Double-length Working  | • •  | • • - | ••  | ••  | ••    | • • | • • | 30    |

| Floating Point         |      | • •   |     |     |       |     |     | 33    |

# CHAPTER I

# BINARY ARITHMETIC

Chapters I and II of this handbook are provided as an introduction to the rest of the work. They may be omitted by readers already conversant with the principles of electronic binary computers.

#### SYSTEMS OF NUMERATION

# Place Value

1. The numeration system used almost universally today is, to give it its full title, a place-value decimal system. It is a place-value system because the value to be ascribed to a figure depends on its position in a series: the two expressions 17 and 71 signify different numbers, although the same two figures are used. It is a decimal, or scale-of-ten, system because the value represented by each place is some power of ten. By convention, the less significant figures, i.e. those with the lower place values, are written on the right, and the more significant figures are written on the left. Thus the number 1728 in the decimal scale must be interpreted as

$$1 \times 10^3 + 7 \times 10^2 + 2 \times 10 + 8 \times 1$$

- 2. Many numeration systems have been devised without recourse to place-value notation. The ancient Greeks used the letters of their alphabet as numerals; the first nine characters represented the units, the next nine the tens, and the last nine the hundreds. Thus 800 was represented by  $\omega$ , 40 by  $\mu$  and 2 by  $\beta$ , so that  $\omega\mu\beta$  would represent the number 842. It will be noticed that the order of the symbols  $\omega$ ,  $\mu$  and  $\beta$  does not matter, whereas changing the order of the figures 8, 4 and 2 in the place-value system changes the number represented. The decimal place-value system originated among the Arabs; because of this, the figures 0 to 9 are sometimes referred to as Arabic numerals, although quite different symbols are used in Arabia today.

- 3. Intermediate between the Greek and Arabic systems come the Roman and Chinese systems. In Roman numerals, the order of the symbols is sometimes important, e.g. in the distinction between IV (four) and VI (six). As in the Greek system, however, different symbols are used for five, fifty and five hundred (V, L and D). In the Chinese system, the numbers one to nine have separate characters; for numbers greater than nine these characters are given values by special 'value' characters placed below them (Chinese writing is read downwards). The expanded form of the number 1728 given at the end of paragraph 1 is similar to the Chinese method of writing a number if the symbols  $10^3$ ,  $10^2$  etc. are thought of as 'value' characters. The chief advantage of

the place-value system of numbering is that there is no limit to the size of number that can be represented, whereas, without place values, the numbers that can be represented are limited by the number of characters available. Furthermore, the place-value system makes calculation much easier.

#### Radices

4. The number ten is called the 'radix' of the decimal system. Its choice was quite arbitrary; it seems to have been selected for no better reason than that the majority of human beings, with eight fingers and two thumbs, had 'at hand' a rudimentary decimal digital computer that sufficed for everyday calculations. Nevertheless, other civilisations have used other numeral radices. The Babylonians, for instance, used the scale of sixty, and vestiges of their system remain today in the relationships between seconds, minutes and hours and between the smaller divisions of angle. The method of selling and buying by the dozen or the gross, and the relationship between feet and inches, or shillings and pence, reflect the influence of a number scale with radix twelve, although the numbers 12 and 144 are now always written in the decimal notation. In the scale of twelve, the number 1728 (decimal scale), being the cube of twelve, would appear as 1000. The number 1234 regarded as being in the scale of twelve is equivalent to

$$1 \times 1728 + 2 \times 144 + 3 \times 12 + 4 \times 1$$

= 1728 + 288 + 36 + 4

= 2056 in the decimal scale.

5. The scale of twelve has much to recommend it as a basis of calculation. Twelve has more divisors than ten, and consequently would give rise to more short cuts to make computation easier. Sixty has more divisors still; but, to make calculations rapidly in the scale of sixty, one would have to know no fewer than fifty-eight multiplication tables, each containing sixty identities. Another disadvantage of the scale of sixty is that, even with a place-value notation, sixty symbols would be required. The number of symbols required (including the zero symbol) in any place-value numeration system is equal to the radix of the system; thus in the so-called 'Arabic' decimal system there are ten symbols including 0.

# The Binary Scale

6. In digital computers numbers are represented digit by digit by different states of the computing elements. Thus in a mechanical decimal digital computer, the ten digits possible in each place could be represented by the stable positions of a tentoothed ratchet. It is, of course, possible to construct an electronic computer to operate in the scale of ten. For instance, the ten digits could be represented by ten different voltage levels at each point in the machine. The difficulty would be in designing circuits that could, notwithstanding circuit tolerances and valve drift, distinguish with absolute certainty between the various levels. The fewer the voltage levels, therefore, the simpler the circuits that would be needed, and the lower the probability of error. In the limit, if the number of voltage levels be reduced to two, an 'all-or-nothing' relationship is established between two states at any point

in the machine, so that ambiguity cannot arise unless there is actually a component failure.

7. With a radix of two, i.e. in the binary scale, only two symbols are required in a place-value representation of a number; the symbols usually used are '0' and '1', and they are represented in the computer by two distinct voltage levels. In the conventional notation, the places represent ascending powers of two, according to their distance from the right-hand end. Thus the binary number

# 10110011

# represents

$$1 \times 2^{7} + 0 \times 2^{6} + 1 \times 2^{5} + 1 \times 2^{4} + 0 \times 2^{3} + 0 \times 2^{2} + 1 \times 2 + 1 \times 1$$

= 128 + 32 + 16 + 2 + 1

= 179 in the decimal scale.

Decimal numbers can be converted to binary numbers by successive divisions by two, the remainders being the required binary digits. Thus, as a check on the transformation carried out above.

|       | remainders |

|-------|------------|

| 2)179 |            |

| 2) 89 | 1          |

| 2) 44 | 1          |

| 2) 22 | 0          |

| 2) 11 | 0          |

| 2) 5  | 1          |

| 2) 2  | 1          |

| 2) 1  | 0          |

| 0     | 1          |

$\therefore$  179 (decimal) = 1 0 1 1 0 0 1 1 (binary).

Note that the remainders must be written in order from the bottom upwards to give the conventional binary representation.

8. The use of the binary scale in digital computers has the further advantage that arithmetical operations in this scale can be expressed easily in terms of still more fundamental 'logical' operations. A logical operation can be defined as a choice of one from two or more mutually exclusive contingencies. The series of pulses (binary 'ones') or gaps (binary 'noughts') representing numbers in the machine are fed to crystal-diode gates and to other simple electronic circuits, which produce outputs according to the result of some logical operation on the inputs. The subject of logical operations is dealt with in more detail in Chapter II.

9. Numbers in a computer can be regarded as integers; but it will be more convenient here to regard all binary numbers entering into computation as fractions. The script notation for fractions in the binary scale is analogous to the notation for decimal fractions: a point is placed at the more significant end of the number, and the place values to be ascribed to the digits are successive powers of 1/2. For instance, the number 51/64 is equivalent to

$$1 \times 1/2 + 1 \times 1/4 + 0 \times 1/8 + 0 \times 1/16 + 1 \times 1/32 + 1 \times 1/64$$

and would be written as a binary fraction thus

0.110011

# ARITHMETICAL PROCESSES

# Addition

10. As an introduction to binary addition, consider the summation of the two decimal numbers 65966 and 82935

| 1      | 0 | 1 | 1 | 1 |       | carry digits |

|--------|---|---|---|---|-------|--------------|

|        | 6 | 5 | 9 | 6 | 6     | number (a)   |

|        | 8 | 2 | 9 | 3 | 5     | number (b)   |

| _<br>1 | 4 | 8 | 9 | 0 | <br>1 | sum (s)      |

The two numbers are added digit by digit from the right-hand (less significant) end. Since the sum of the unit digits, 6 + 5, is greater than the radix, 10, the number 1 must be 'carried' into the next column and added in with the two digits already there. In this case, the carry digit makes the sum in the 'tens' column greater than the radix, and another 1 must be carried. It will be noticed that the carry digit cannot be greater than 1 if only two numbers are added. When three numbers are added, the carry digit can be as great as 2, and only when eleven or more numbers are added can the number carried exceed the radix, 10.

11. Binary addition is similar to decimal addition; the process can be illustrated with another example.

| 1     | 1001        | carry digits          |

|-------|-------------|-----------------------|

|       | 0 1 1 1 0 1 | number (a) number (b) |

| 0 . 1 | 1 0 1 1 0   | sum (s)               |

As before, the digits are added column by column from the right. In the first (right-hand) column, the sum of the two digits is equal to the radix, so a 0 is entered in

the sum for that column and a 1 is carried into the next column. In the fifth column from the right, the digits in the two numbers, together with the carry digit, make up one more than the radix, so a 1 is entered and a 1 is carried. It is easily seen that, if three or more binary numbers were added together, the 'carry' would often run into more than one digit. To cater for multi-digit carries would involve quite a lot of extra equipment; it is usual, therefore, in binary computers to add numbers in pairs only. If more than two numbers are to be summed, two are added together, the third is added to the sum of those, the fourth to the resultant sum and so on; this may be done either by using a series of adder circuits or by working repetitively through the same adder.

# Subtraction

12. Binary subtraction can be compared similarly with decimal subtraction. Consider, for example, the following decimal subtraction.

|        | -1     | -1 | -1     | (10)          |        | 'borrow' line         |

|--------|--------|----|--------|---------------|--------|-----------------------|

| 3<br>2 | 7<br>3 | -  | 7<br>7 | <b>4</b><br>8 | 5<br>1 | number (a) number (b) |

| 1      | 3      | 3  | 9      | 6             | 4      | difference (d)        |

In the first column, one from five leaves four. In the second column, eight from four would give a negative entry, so a number equal to the radix, must be 'borrowed' from the column immediately to the left. The 'borrow' digit is entered as -1; consequently, the operation in the third column from the right (7 - 1 - 7) requires a further 'borrow' operation. In this example, borrowing must be carried on up to the fifth column from the right, where, for the first time, the digit in (a) exceeds the digit in (b).

13. It should be realised that a computer can only operate digit by digit, i.e. it cannot make an inspection several digits ahead to find a possible source for the borrowed digit. 'Borrowing' therefore entails the use of a 'carry' digit that must enter into the computation at every stage until it is cancelled by a particular combination of digits in numbers (a) and (b). For example, consider the following subtraction.

|   |   |   | 1 | 1 | 1 | 1 | (2)    | carry digit | ;          |  |  |

|---|---|---|---|---|---|---|--------|-------------|------------|--|--|

| - | - | _ |   | - |   |   | 0<br>1 |             | (a)<br>(b) |  |  |

| 0 |   | 1 | 0 | 1 | 1 | 0 | 1      | difference  | (d)        |  |  |

A carry digit is generated in the first column because the digit in number (a) has a smaller value than the digit in number (b). It is carried on through various combinations of digits in the two numbers until it is cancelled, after four more columns, as soon as the digit in number (a) is greater than the digit in number (b). The entry in this column is a 0.

# **Negative Numbers**

14. Consider now what will happen when number (b) is greater than number (a), i.e. when the difference is a negative number:

| • | • | • | 1 | • | 1 | (2)    |   |   |   | carr         | carry digit |  |  |  |  |

|---|---|---|---|---|---|--------|---|---|---|--------------|-------------|--|--|--|--|

|   |   |   |   |   |   | 0<br>1 |   |   |   | numb<br>numb |             |  |  |  |  |

| _ | _ | _ | 1 |   | 1 | 1      | 1 | 0 | 1 | diff         | erence (d)  |  |  |  |  |

Here there is nothing to cancel the carry digit, which must be imagined to be repeated an infinite number of times to the left of the point. However, sustained repetition of the carry digit adds nothing to the information contained in the number. If it is stipulated that all numbers are to be regarded as fractions, a single digit to the left of the point will be enough to ensure that the number is interpreted as negative. This digit is generally referred to as the 'sign' digit. The subtraction operation shown above is equivalent to

$$7/32 - 10/32 = -3/32$$

The difference, as written, is 1 29/32, which is the complement with respect to 2 of the true negative difference, i.e.

$$1 29/32 - 2 = -3/32$$

15. A system in which negative numbers are recorded as their complements with respect to some number outside the operating range of the computer greatly simplifies the processes of addition and subtraction. The alternative system of using a sign digit as a direct indication of sign, for example by expressing the number -n as 1 + n, would often involve numerical complementation (i.e. the conversion of n to 1-n) during a computation and would in consequence increase either the computing time or the amount of equipment required. It has been assumed in the above explanation that the numbers in the machine are to be regarded as wholly fractional, implying that negative numbers are to be expressed as their complements with respect to 2. The convention for integers is similar; for example, a 38-digit negative binary integer would be recorded as its complement with respect to  $2^{40}$ . Two important consequences of this method of recording negative numbers are, first, that the binary number

must be interpreted as -1, there being no permissible way of representing +1; and, second, that zero is to be treated as a positive number since the sign digit is necessarily zero.

# **Overflow**

16. With the sign convention described in the previous paragraph, all fractional numbers must lie in the range

$$-1 \le n \le 1$$

.

It will often happen, however, that the addition or subtraction of two numbers will cause 'overflow', i.e. produce a number outside the permitted range and in the range

$$-2 \leqslant n \leqslant -1$$

or

$$1 \leqslant n < 2$$

.

To ensure that overflow is detected as such, and is not mistaken for a change of sign, 'carry' must not be suppressed until the third digit place to the left of the point. With this proviso, the addition of 35/64 and 52/64 would give

we,

The fact that the two digits preceding the point are different is to be understood as showing that the result of the operation is the positive number 1 23/64 and not the negative number -41/64. The negative number -41/64 would appear instead with two identical digits preceding the point as for instance, in the result of the following subtraction:

17. Not only must the result of an addition or subtraction appear with two digits preceding the point; the operands entering into these operations must also have two significant digits preceding the point. Thus negative numbers that are to be added or subtracted must first be expressed as their complements with respect to 4, which simply means that their sign digits must be repeated. As an example of negative overflow consider the addition of the two negative numbers-35/64, represented as (4 - 35/64), and -52/64, represented as (4 - 52/64)

In the sum, the two digits preceding the point are different, indicating overflow. The more significant digit of the two is 1, showing that the sum must be interpreted as a negative number, i.e. not as 2 41/64, its apparent value, but as 2 41/64 - 4, or -1 23/64.

# Multiplication

18. Multiplication by powers of two in the binary scale, like multiplication by powers of ten in the decimal scale, is accomplished by shifting the whole digit series the corresponding number of places to the left. Similarly division by powers of two

can be accomplished by shifting to the right. It will be seen that the method of expressing negative numbers as their complements with respect to 2 allows them to be shifted to the right in the normal way, provided that the sign digit is repeated before each shift. Thus the negative number

1.01

or -3/4

becomes

1.11101

or -3/32 after three right shifts.

Overflow in left shifts, like overflow after addition or subtraction, can be detected by comparing the digits preceding the point. Thus the number -17/64

1.100001

becomes

110.0001

or -1/16 after two left shifts, the non-equivalence of the digits preceding the point showing that there has been overflow. Normally the digits to the left of the point are deleted after they have been compared for overflow.

19. Multiplication by numbers other than powers of 2 can be accomplished by successive shifts and additions. Thus multiplication by ten, which is  $2^3 + 2$ , would require the multiplicand shifted three places to be added to the multiplicand shifted only one place. Thus 5/64 could be multiplied by ten as follows

|   | ,    |   |    | 5/64 |   | 0 | 0 | • | 0 | 0 | 0 | 1 | 0 | 1 |   |       |   |

|---|------|---|----|------|---|---|---|---|---|---|---|---|---|---|---|-------|---|

|   | 5/64 | × | 8  |      |   | 0 | 0 |   | 1 | 0 | 1 | 0 | 0 | 0 |   |       |   |

| + | 5/64 | × | 2  |      | + | 0 | 0 | • | 0 | 0 | 1 | 0 | 1 | 0 |   |       |   |

|   |      |   |    |      |   | _ |   |   |   |   |   |   | _ |   |   |       |   |

| = | 5/64 | X | 10 |      |   | 0 | 0 |   | 1 | 1 | 0 | 0 | 1 | 0 | = | 50/61 | ļ |

It will be appreciated that the same result could be obtained by shifting the multiplicand twice, adding to the original multiplicand, and shifting once more, thus

| 5/64        | 0 | , ( | ) | • | U | 0 | 0 | 1 | 0 | 1 |      |   |    |

|-------------|---|-----|---|---|---|---|---|---|---|---|------|---|----|

| shift twice | 0 | C   | ) | • | 0 | 1 | 0 | 1 | 0 | 0 | 5/64 | × | 4  |

| add         | 0 | C   | ) |   | 0 | 1 | 1 | 0 | 0 | 1 | 5/64 | x | 5  |

| shift again | 0 | 0   | ) |   | 1 | 1 | 0 | 0 | 1 | 0 | 5/64 | x | 10 |

A logical circuit could be designed to perform the necessary shifts and additions.

20. The process described in the previous paragraph for multiplication by ten is analogous to the 'long multiplication' taught in schools; but it is much simpler, since digits of the multiplier can only have the values 0 or 1, so that there is no necessity for the use of tables. Ten, in the binary scale, is

The process of multiplication by ten can therefore be written in full thus:

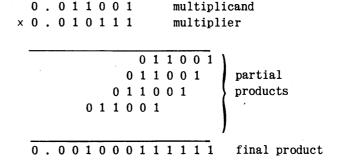

As a further example consider the formation of the product of the two fractions 25/64 and 23/64. The null partial products are omitted for brevity in this example.

giving the required product 575/4096

#### Rounding

and

21. The last example shows that the product of two six-digit binary fractions is a binary fraction twelve digits in length. This result is general; the product of two full-length numbers is a double-length number, which will normally have to be treated in two parts. (The implications of double-length working are discussed in paragraph 30). Alternatively the product can be 'rounded' to a single length. The rounding process used in Pegasus is similar to the 'rounding up' process used in decimal arithmetic, in which the digits to be deleted are made to 'carry' 1 up into the rounded result if the most significant of them is a 5 or greater. Similarly, in rounding a binary number, a 1 is 'carried' up into the rounded result if the most significant of the digits to be deleted is a 1. Thus, in rounding from six figures to three,

| 0. | 0 1 1 0 1 1 | becomes | 0.011 |

|----|-------------|---------|-------|

| 0. | 0 1 1 1 0 0 | becomes | 0.100 |

22. In fact, the rounding process can be replaced by the addition of 1 at the most significant end of the portion of the number to be deleted; this will automatically produce the 'carry' digit required for rounding. Thus

Rounding may occasionally cause overflow; but overflow can never result from rounding after multiplication. If the two operands in multiplication are fractions, the product cannot be numerically greater than the smaller of them; hence rounding cannot produce a number greater than would be produced by adding 1 one place beyond the end of the smaller.

#### Division

- 23. The normal method of decimal 'long' division involves at each stage some form of inspection to determine whether the divisor will 'go into' the dividend. The only way in which a computer can make an inspection of this kind is to carry out a subtraction (or addition if divisor and dividend have opposite signs) and to test the residue for sign. To avoid the necessity for reconstituting the dividend after such an operation, a process is used in which the machine makes an addition or subtraction at each stage. Briefly, the process is one in which the numerical value of the residue is made as small as possible by repetitive additions or subtractions of the divisor, each operation being carried out with a significance one place lower than that of its predecessor. The sign of the residue is tested after each addition or subtraction to determine the type of operation for the next step. At the end of the process, the record of the amount of addition or subtraction is the required quotient.

- 24. Consider, for example, the division of 15/64 by 5/8

The two operands in this example have the same sign: hence, for the numerical value of the dividend to be decreased, the first operation must be subtraction. The residue

resulting from the first operation is negative, i.e. of opposite sign to the divisor, so that the second operation (carried out one place to the right) must be addition, This again gives a negative residue, prescribing addition as the third operation. The fourth operation is subtraction as the third residue is positive. Altogether the divisor has been subtracted from the dividend in the first and fourth places, and has been added in the second and third places. The net amount that has been subtracted is therefore

$$(1 + 0.001) - (0.1 + 0.01)$$

times the divisor. Hence the quotient is

25. In general, of course, division operations will not 'come out' exactly. The end procedure will then depend on whether we wish the final residue to have a particular sign (unrounded division) or to be as small as possible, regardless of sign (rounded division). Consider, for example, the division of 13/64 (0.001101) by 5/8 (0.101). The rounded quotient is obviously 3/8 (0.011) with a residue of -2/64 (1.11110). The unrounded quotient, if the residue is to be positive, is 1/4 (0.010), with a residue of 3/64 (0.00011). The first three steps of the division process are as follows:

It will be seen that the residue and quotient happen to be correct at this stage for unrounded division. It would be uneconomical on equipment, however, to make the machine sense this condition and stop; it must be allowed to finish the last division operation.

26. The quotient and residue now happen to be correct for rounded division. However, rounding in general requires one further digit to be examined that will not appear in the rounded quotient, and thus requires the process to be taken one step further. A 'nought' is therefore 'brought down' to form the last digit of the residue, and the next operation - in this case, addition - is carried out

27. Now, owing to the method of forming it, the last digit of the quotient must always be a 'one'. It would change to a 'nought' or would remain the same according as the next operation on the quotient were to be subtraction or addition. In this case, as the residue is positive, the next operation on the residue would be subtraction, and on the quotient addition; so the fourth quotient digit is not going to change. If the quotient is to be rounded to three digits, therefore, its third digit must be made 1, and its fourth digit 0. The simplest way of doing this is to add 1 in the fourth place of the quotient; of course a corresponding operation must be carried out on the residue.

Note that operations in the last stage take place with the same significance as operations in the penultimate stage. The general rule for *rounded* division is therefore that the process must be taken two stages 'too far', the last two operations being carried out with the same significance.

28. It is convenient to make the process of unrounded division as nearly as possible the same as the process of rounded division. The division is therefore taken only one stage 'too far', and the surplus quotient digit is then removed by a straightforward subtraction, which implies, of course, an addition to the residue.

final residue unrounded quotient

As in rounded division, the last two operations are carried out with the same significance; but in unrounded division, the last operation on the residue is always addition, and on the quotient always subtraction.

29. In the division examples given, the operands have been regarded as fractions (although they might equally well have been regarded as integers, e.g. as 5 and 15 in the example of paragraph 24). If the dividend is numerically greater than the divisor, the quotient will overflow, i.e. will be greater than unity if the numbers are treated as fractions. The computation should, of course, be organised so that this condition either does not occur or is corrected if it occurs. Notice that, since it is possible for a quotient to be taken out of range by rounding, the overflow condition cannot be tested conclusively until the end of the division process.

# Double-length Working

- 30. To avoid the accumulation of 'rounding' errors, it is sometimes necessary to work with double-length numbers. The sign of a double-length number is indicated by the sign digit of the more significant half; the less significant half is then always positive, and can be regarded as a small correction term that is to be added to the rest of the number. As the two halves of a double-length number must enter into arithmetical operations separately, some facility must be provided whereby a 'carry' operation can take place between them if the less significant half overflows or changes its sign.

- 31. The 'carry' operation between the two halves of a double-length number is termed 'justification'. In the case of simple positive overflow, the justification process must add 1 in the last place of the more significant half. A change of sign might produce a number such as

11.101

which is to be interpreted as

$$3 5/8 - 4 = 5/8 - 1$$

To keep the less significant half of the number positive (equal to + 5/8), a 'one' must be subtracted from the last place of the more significant half.

32. The term 'justification' is used in the printing trade to denote the process of adjusting to a uniform length, the lines on a printed page. It is used in a similar sense here. The process outlined in the previous paragraph can be used to form a double-length number from a single-length number that has overflowed, i.e. has exceeded the standard length. For this purpose, the out-of-range number is regarded as the less significant half of a double-length number, the more significant half being wholly zero. There are two possibilities, according as the out-of-range number to be justified is positive or negative. Thus if the number is positive,

0 . 0 0 ..... 0 0 justified with 0 1 . 1 0 ..... 0 1

becomes 0 . 0 0 . . . . 0 1, 1 0 . . . . 0 1

whereas, if it is negative,

0 . 0 0 .... 0 0 justified with 1 0 . 1 0 .... 0 1

becomes 1 . 1 1 . . . . 1 0, 1 0 . . . . 0 1

1 . 1 1 ..... 1 0, 1 0 ..... 0

It will be noticed that positive overflow involves the addition of 1 in the last place of the more significant half, whereas negative overflow involves the subtraction of 1 in the penultimate place. If the numbers are regarded as wholly fractional, justification becomes equivalent to a right shift of as many places as there are digits in a single-length number.

# Floating Point

33. In floating-point arithmetic, a number is treated in two parts, the argument and the exponent. The argument is simply a fraction, positive or negative; the exponent (in binary arithmetic) is a power of two by which the argument is assumed to be multiplied. Thus the argument 0.011 together with the exponent 7, would express the binary number:

$$0.011 \times 2^7 = 110000$$

or 48 in decimal notation. Multiplication in floating-point arithmetic requires the arguments to be multiplied together and the exponents to be added; thus

0 . 0 1 1

$$\times$$

2<sup>7</sup>  $\times$  0 . 1 0 1  $\times$  2<sup>6</sup>

= 0 . 0 1 1  $\times$  0 . 1 0 1  $\times$  2<sup>13</sup>

= 0 . 0 0 1 1 1 1  $\times$  2<sup>13</sup>

34. Floating-point addition involves a few more operations, as the two numbers must first be adjusted to have the same exponent. The usual practice is to shift the argument of the number with the smaller exponent, and to adjust this exponent correspondingly, until the two exponents are equal. The arguments can then be added directly. This process involves only right shifts, (i.e. towards the less significant end) and consequently cannot lead to overflow. Thus

$$(0.011 \times 2^{7}) + (0.101 \times 2^{5})$$

=  $(0.011 \times 2^{7}) + (0.00101 \times 2^{7})$

=  $(0.011 + 0.00101) \times 2^{7}$

=  $0.10001 \times 2^{7}$

35. It is usual to express the arguments of floating-point numbers in a standard form. Ideally this form should ensure that overflow cannot ensue from a single addition or subtraction, which means that the argument should be in the range

$$-1/2 \le n \le -1/4$$

$1/4 \le n \le 1/2$

or

i.e. the first two digits after the point should be different. The process of putting the argument into this form is called 'normalisation'; the argument is shifted to the left the desired number of places, and the number of the shifts is subtracted from the exponent. Thus

In the case of one right shift - the maximum necessary if there has been no overflow - the exponent is increased by one.

# CHAPTER II

# LOGICAL OPERATIONS

|                      |         |          |    |     |     |     |     |     | Para. |

|----------------------|---------|----------|----|-----|-----|-----|-----|-----|-------|

| PRINCIPLES OF LOGIC  | ••      | ••       | •• | ••  | ••  |     | ••  | ••  | 1     |

| AND Operation        | ••      | ••       | •• | ••  | ••  | ••  |     | ••  | 1     |

| OR Operation         | ••      | ••       | •• | ••  | ••  | ••  | ••  | ••  | 3     |

| NOT Operation        | ••      | ••       | •• | ••  | ••  | ••  | ••  | ••  | 4     |

| Truth Tables         | ••      | ••       | •• | ••  |     |     | ••  | • • | 7     |

| Boolean Algebra      | ••      | ••       | •• | ••  | ••  | • • | • • | ••  | 9     |

| APPLICATIONS IN ARIT | THMETIC | <b>;</b> | •• | • • | • • | • • | ••  | ••  | 12    |

| Addition             | ••      |          | •• | ••  | • • | ••  |     | • • | 12    |

| Subtraction          | ••      | ••       | •• | ••  | ••  | ••  | ••  | • • | 16    |

| Multiplication a     | and Div | rision   | •• | ••  | ••  | ••  | ••  | ••  | 19    |

| OTHER LOGICAL OPERAT | rions   |          |    |     |     |     |     |     | 20    |

# CHAPTER II

# LOGICAL OPERATIONS

Chapters I and II of this handbook are provided as an introduction to the rest of the work. They may be omitted by readers already conversant with the principles of electronic binary computers.

#### PRINCIPLES OF LOGIC

# AND Operation

- 1. Suppose that it is required to select a team of computer-maintenance engineers, and that the only requirement for selection is the possession of the following two qualifications:

- (a) the ability to use a soldering iron

- (b) the ability to understand logic.

then, out of the set of all applicants for the post of computer-maintenance engineer, those would be selected who possessed qualification (a) and qualification (b). A selection such as this, in which a smaller class is chosen out of a larger set according to some rule, is called a 'logical operation'. This particular logical operation is called the 'AND operation'.

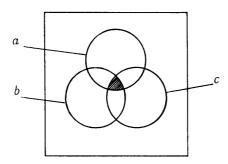

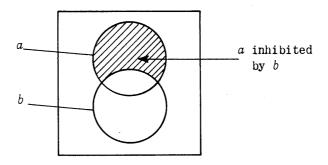

2. The AND operation can be illustrated diagrammatically as follows. Suppose that all applicants for posts as computer-maintenance engineers are put together in one room like this.

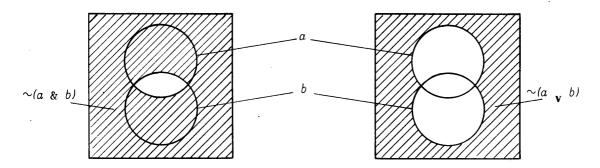

Suppose now that they can be arranged in the room in such a way that one circle can be drawn around all those who possess qualification (a), and another circle can be drawn

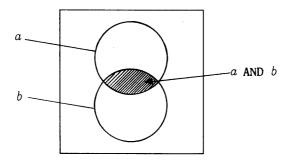

around all who possess qualification (b), thus

The region of 'overlap' of the two circles, the shaded area, then includes all those who possess qualification (a) and qualification (b). We shall use the algebraic expression

a & . b

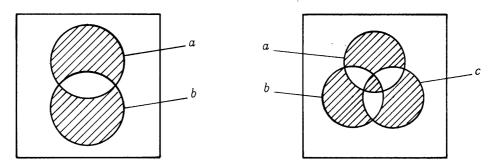

to designate a class selected in this way. If we wish, we can apply the AND operation to more than two classes like this.

The area shaded would then correspond to the algebraic expression

a & b & c

# **OR** Operation

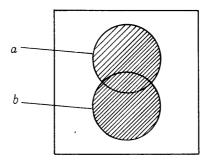

3. Suppose, now that more computer-maintenance engineers are required than the AND operation can select. To obtain the requisite numbers, the requirements might be relaxed so that the successful candidate need have only one of the two qualifications on the assumption that the other can be learnt in time; of course, those who possess both qualifications will be selected as well. The class of successful candidates can

then be represented by a figure-of-eight area like this.

The logical operation employed here is called the 'OR operation', and is expressed in symbolic form by

$$a \mathbf{v} b$$

(Read 'a or b'. The symbol  $_{\bf V}$  is the first letter of Latin 'vel', meaning 'or'.) The OR operation, like the AND operation, can be applied to three or more operands.

The OR operation is sometimes referred to as 'mixing'; the reason for this term will be evident when the electrical design of the packages is considered.

# NOT Operation

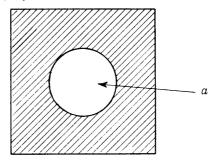

4. It will be noticed that the AND and OR operations require at least two operands. To these must be added a third operation, which can be applied to one operand alone. This is the 'NOT operation', also called 'inversion'. Applied to the class of all those who can use a soldering iron, the NOT operation would produce all those who cannot use a soldering iron. In the following diagram, if the unshaded area represents (a), the shaded area will represent NOT (a).

Algebraically, the NOT operation is shown by putting a bar over the operand, thus  $\bar{a}$ , or by putting a tilde before it, thus  $\sim a$ .

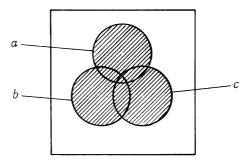

5. The NOT operation can, of course, be applied to the result of a previous logical operation. For instance, these two figures

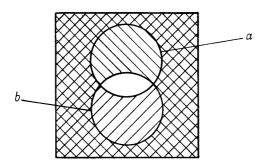

show shaded areas representing  $\sim (a \& b)$  and  $\sim (a V b)$ . Similarly, the AND and OR operations can be applied to the results of inversion. In the next diagram, areas representing  $\sim a$  and  $\sim b$  are shaded in different directions; the cross-hatched area is therefore

6. It will be noticed that the cross-hatched area in the last figure is exactly the same as the shaded area representing  $\sim (a_{V}b)$  in the figure preceding it. This illustrates an important logical theorem, which may be stated algebraically, thus

$$\sim a \& \sim b = \sim (a \lor b)$$

It can be shown similarly that

$$\sim a v \sim b = \sim (a \& b)$$

In other words, the AND operation before inversion is equivalent to the OR operation after inversion and vice versa.

# Truth Tables

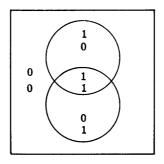

7. A method has been given above whereby the consequences of logical operations may be investigated with the aid of diagrams. Another graphical aid to understanding logical processes is the 'truth table'. With the two hypothetical qualifications for computer maintenance engineers given at the beginning of this chapter, there are the following four possibilities: possession of both qualifications, possession of qualification (a) only, possession of qualification (b) only, possession of neither. These four possibilities are represented by the four columns in the table below, in which a 1 represents the presence, and a 0 the absence, of the qualification

These four columns represent the four areas into which a square is divided by two overlapping circles as shown below.

8. The truth table can now be expanded to include logical combinations of a and b as follows:

The combination (a & b), i.e. a and b both present, occurs only in the first column, where a 1 must be written in the row representing (a & b). The combination  $(a \ v)$ , a or b or both, occurs in the first three columns, but not in the fourth. The inverses,  $\sim a$  and  $\sim b$ , are obtained simply by substituting a 0 for a 1 and a 1 for a 0 in a and b. It will be noticed that the (a & b) row gives the product that would be obtained by multiplying together, column by column, the digits in the first two rows. Thus

$$1 \times 1 = 1$$

and in all other cases the product is zero. The (a & b) row also gives the 'carry' digit that would be produced in a binary sum, column by column, of the digits in the first two rows. The other results of binary arithmetical operations can be produced, as will be shown, by more complex combinations of logical operations.

# Boolean Algebra

9. The algebra of logic is called Boolean algebra after George Boole, its inventor, a Lincoln mathematics teacher. Consider the following identity in ordinary algebra.

$$a \times (b + c) = (a \times b) + (a \times c)$$

The identity will still hold if the arithmetical operators are replaced by logical operators

$$a & (b \ v \ c) = (a & b) \ v \ (a & c)$$

This can easily be checked diagrammatically, or by using a truth table. Eight columns are now necessary to exhaust the eight possible combinations of a, b and c. Thus

The fifth and eighth rows of the truth table are identical, proving the truth of the proposition.

10. An important feature of Boolean algebra is that the operators & and  $_{\bf V}$  have identical properties, whereas the arithmetical operators + and  $_{\bf V}$  have not. In mathematical terms, & and  $_{\bf V}$  are distributive over each other, whereas + is not distributive over  $_{\bf V}$ . If, in the first identity in paragraph 9, the + and  $_{\bf V}$  signs are interchanged, the identity no longer holds for all values of  $_{\bf C}$ ,  $_{\bf C}$  and  $_{\bf C}$ . If the signs are interchanged in the second identity, however, a new identity is produced

$$a_{v}(b \& c) = (a_{v}b) \& (a_{v}c)$$

which can be checked as before.

11. Two further symbols are used in Boolean algebra. The symbol I is the totality element and would correspond to a row of ones in a truth table. In diagrammatic form, it is the square that contains all the circles representing operands. The symbol 0 is the null element; in the truth table it is a row of noughts: diagrammatically it is a circle of zero area. With these conventions the following identities emerge:

$$a \quad \mathbf{v} \sim a = \mathbf{I}$$

$a \quad & \sim a = 0$

$$a \quad \mathbf{v} \quad \mathbf{I} = \mathbf{I}$$

$a \quad & \mathbf{I} = a$

to which may be added the trivial identities

$$a_{\mathbf{v}}a = a & a = a$$

# APPLICATIONS IN ARITHMETIC

# Addition

12. It was shown in paragraph 8 that certain results of binary arithmetic appear in a simple truth table. The truth table for binary addition of two single-digit numbers is

It is important to realise that the four columns are treated individually here, the table is *not* meant to represent the addition of two four-digit binary numbers. As was stated in paragraph 8, the carry digit is given by

$$c = a & b$$

The occurrence of the sum digit can be expressed in words by 'a or b, but not both'. In algebraic symbols, therefore

'a or b' becomes

$$a \ _{\mathbf{V}} b$$

'not both' becomes  $\sim (a \ \& b)$

Hence the sum digit is given by

$$s = (a b) & \sim (a b)$$

This formula can be checked by building it up step by step in a truth table in the manner shown in paragraph 9.

13. The occurrence of the sum digit in the table might have been expressed alternatively by the phrase, 'a, but not a and b; or b, but not a and b'. In algebraic form therefore

$$s = [a \& \sim (a \& b)] \cup [b \& \sim (a \& b)]$$

There are obviously other ways of writing the formula for the sum digit; the two given here have been chosen because of their immediate practical application.

14. The truth table given in paragraph 12 does not represent the full process of binary addition, as no account has yet been taken of the carry digit. If c' is the carry digit from a previous operation and c the carry digit to the next operation, the full truth table for addition is

It will be noticed that a carry digit is generated when a 1 is present in at least two of a, b and c'. The full formula for the carry digit is therefore

$$c = (a \& b) v (b \& c') v (a \& c'),$$

the OR operations ensuring that the special case is included when a 1 is present in a, b and c together. This formula can be condensed somewhat by combining any two of the bracketed terms; thus

$$c = [a & (b v c')] v (b & c');$$

15. A sum digit is generated in the presence of a 1 in one or all of a, b and c'; but there is no sum digit when a 1 is present in only two rows. Several formulae for s are possible in terms of a, b and c'. One of these is given below on account of its practical application; the proof is left as an exercise for the reader

$$s = \sim [\sim (b \& c') \& (b \lor c') \& a] \& [a \lor \{ \sim (b \& c') \& (b \lor c') \}]$$

#### Subtraction

16. The process of binary subtraction can be analysed in the same way as addition. The four possible cases where two single-digit numbers are involved are

These may be written in the form of a truth table:

It will be noticed that the 'difference' row is exactly the same as the 'sum' row given in the addition table (refer to paragraph 12). This is convenient, because it means that the same circuit arrangement, with minor modifications, can be used for addition or subtraction. The carry digit occurs when b is greater than a. It corresponds to the case when  $\sim a$  and b are present together, i.e. it can be expressed by the formula.

$$c = a \& b$$

17. The full truth table for subtraction, in which the carry digit, c', from the previous column is taken into account, is given below. The first four columns can be compiled from the example given in paragraph 13 of Chapter I; the last four columns are, of course, the same as the four in the truth table given in the preceding paragraph, with 'noughts' in the c' row.

As before, row d is the same as row s in the addition table.

18. The carry digit in subtraction is what would be generated if  $\sim a$  were substituted for a in the addition table. Consequently, the formula for the subtractive carry digit can be derived from that for the additive carry digit (paragraph 14) by a simple substitution, viz:

$$c_{(a-b)} = [\sim a \& (b_{\mathbf{v}} c')]_{\mathbf{v}} (b \& c')$$

# Multiplication and Division

19. Multiplication consists simply of a series of additions and shifts, the partial products being given by the operation (a & b). Division, as was shown in Chapter I, can be carried out by a series of additions and subtractions, the next operation and the sign of the quotient digit being determined by the sign digit resulting from the previous operation. (See Chapter I, paragraph 23 et seq.)

# OTHER LOGICAL OPERATIONS

20. As well as the AND and OR operations and the inversion operation discussed at the beginning of this chapter, it is sometimes useful to work in terms of another operation, the NOT-EQUIVALENT operation, which is written

$$a \neq b$$

(read 'a not equivalent to b'). It amounts to a selection of those instances where a and b are not the same, e.g. those candidates for the post of computer maintenance engineer who have either of the two qualifications but not both. The NOT-EQUIVALENT operation on two and three operands is shown in terms of shaded areas in the diagrams. It is also referred to as the 'EXCLUSIVE-OR' operation.

21. In truth table form, the various possibilities for the NOT EQUIVALENT operation are shown below for two and three operands.

If reference is made to previous truth tables, it will be seen that the NOT-EQUIVALENT operation gives the sum digit in binary addition and the difference digit in binary subtraction. This fact cannot readily be used in computer work, as there is no simple electronic circuit that will perform the operation. Moreover, the NOT-EQUIVALENT operation does not obey the rules of simple algebra, in that it is non-distributive, and should consequently be avoided as far as possible. The expressions given in paragraphs 12 and 13 for the sum digit can, of course, be used to give the NOT-EQUIVALENT operation in terms of the AND, OR and NOT operations.

$$a \neq b = (a \vee b) \& \sim (a \& b)$$

$a \neq b = [a \& \sim (a \& b)] \vee [b \& \sim (a \& b)]$

22. An important theorem on the NOT-EQUIVALENT operation can be enunciated algebraically as follows:

$$a \neq (a \neq b) = b$$

and conversely

$$b \not\equiv (a \not\equiv b) = a$$

This principle can be used to exchange the locations of two numbers in a computer without the need for a third location as a temporary store. Thus the process to be used is:

- (i) replace a with  $(a \neq b)$ (ii) replace b with  $b \neq (a \neq b) = a$

- (iii) replace  $(a \neq b)$  in the original location of a with  $a \neq (a \neq b) = b$

A trivial identity with a useful application is

$$a \not\equiv I = \sim a$$

Thus a NOT-EQUIVALENT operation taken digit-by-digit between a binary number

$$a = 0.11011$$

say

and a 'full house' of 'ones', representing I, thus

$$I = 1.11111$$

would give the result.

Now the negative of a, with the convention referred to in Chapter I of representing a negative number as its complement with respect to 2, is

$$-a = 1.00101$$

which is the same as the result of the NOT-EQUIVALENT operation, but with the least significant digit changed.

With a suitable correcting operation, therefore, the NOT-EQUIVALENT operation can be used for forming arithmetical complements.

23. Another important logical operation is that of 'inhibition', the suppression of one operand when the other is present; diagrammatically

This operation is obviously equivalent to

$$a \& \sim b$$

In general, any logical operation can be expressed in terms of others. It is interesting to note that there is one logical operation, NEITHER-NOR, from which all the others can be synthesised. For instance

$$a \quad NN \quad a = -a$$

also

$$a \quad NN \quad b = -(a \quad V \quad b)$$

hence

$$a \quad V \quad b = -(a \quad NN \quad b)$$

$$= (a \quad NN \quad b) \quad NN \quad (a \quad NN \quad b)$$

# CHAPTER III

# BASIC LOGICAL CIRCUITS

|                       |     |     |     |     |     |    |     |     | Para. |

|-----------------------|-----|-----|-----|-----|-----|----|-----|-----|-------|

| LOGICAL ELEMENTS      | • • | ••  | ••  | ••  | • • | •• | ••  | • • | 4     |

| ARITHMETICAL CIRCUITS |     | ••  | ••  |     | ••  |    | ••  |     | 8     |

| Adders                | • • | • • | • • | • • | • • | •• | • • | • • | 8     |

| Subtractors           | ••  | • • | ••  | ••  | ••  | •• | ••  | ••  | 14    |

| CIRCUIT SYMBOLS       | • • | ••  | ••  | ••  | ••  | •• | ••  | ••  | 17    |

| Annligations          |     |     |     |     |     |    |     |     | 99    |

# BASIC LOGICAL CIRCUITS

- In Pegasus, a binary number is represented by a time series of voltage pulses, the presence of a pulse at a particular instant representing a 'one' in the corresponding binary place, and its absence representing a 'nought'. The pulses, which have a peak level between +2 V and +13 V and a base level of -10 V, are fed into logical elements; these are electronic circuits that perform operations analogous to the logical operations discussed in Chapter II. The logical elements can be grouped so as to perform the relatively more complex operations of binary arithmetic. It should be realised at the outset that, since arithmetical operations are most conveniently begun at the less significant ends of numbers, the pulse trains representing those numbers should be fed through the system with their least significant digits first. The digit pulses, as seen on an oscilloscope with a normal left-to-right timebase, would appear, therefore, in the reverse order to that of the corresponding digits in the conventional representation of a binary number. For this reason, the oscilloscopes in the built-in monitor in Pegasus have been designed with right-to-left timebases. The timing charts. Volume 2b, have been drawn with the time arrow running from right to left for the same reason.

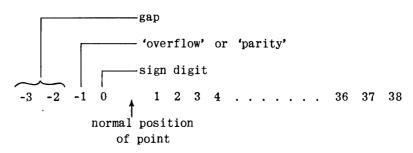

- 2. The longest binary number that can enter into arithmetical operations as a single unit is called a 'word'. In Pegasus, the word consists of 38 significant binary digits with a 'sign' digit placed at the more significant end (and therefore appearing last in time). This means that decimal numbers up to approximately a quarter of a billion (British) can be dealt with, or an equivalent accuracy can be obtained in fractions, without the need for double-length working. The full word length corresponds to 42 binary digits. Two of these are zero, and act as a buffer between one word and the next. The digit occurring next in time after the sign digit may be 1 or 0; it is used for overflow testing (see Chapter I, paragraph 16) or for checking against storage errors by the 'parity count' method (see Chapter X).

- 3. For convenience, the digit places are numbered according to the power of 1/2 given in their place value when the binary point is assumed to be in the normal position, i.e. after the sign digit. Thus the sign digit is numbered 0, the 'overflow' or 'parity' digit -1, and the two gap digits -2 and -3, like this:-

Digit timing in Pegasus is referred to p-pulses that run from 0 to 41. A word is said to be in 'standard timing' when digit-pulse 38 occurs simultaneously with timing pulse p0; the sign digit then occurs with p38 and the two gap digits with p40 and p41. In general, if a word is delayed on standard timing by t digit-times, digit-pulse t0 will occur with timing-pulse t1 where

b = 38 + t - d

#### LOGICAL ELEMENTS

- 4. The logical OR operation on pulses is performed by a network of crystal diodes and resistors called an OR gate; this is arranged so that an output is obtained if a pulse is present on at least one of the input terminals. (This type of circuit is sometimes referred to as a 'threshold-1' element). The AND operation is performed by an AND gate, another network of crystal diodes and resistors, which gives an output only if a pulse is present on all the input terminals. There are three types of AND gate in Pegasus, having two, three or four input terminals. (These can be referred to as 'threshold-2', 'threshold-3' and 'threshold-4' elements if all the input terminals are used). It is worth noting here that a three-input AND gate of the type used in Pegasus can be used as a two-input gate, or a four-input gate as a three-input gate, by leaving one input 'floating'. The NOT operation (inversion) is performed by a thermionic-valve circuit, which inverts the digit-pulse waveform.

- 5. In addition to the AND and OR gates and inverters, the system requires some method of shifting a binary number one digit place to the left, i.e. of delaying the pulse train by one digit-time. Digit delays are required in forming the partial products in multiplication; also, the carry digit in addition and subtraction must be delayed to bring it into the next 'column'. The action of a digit delay is essentially that of deleting a pulse and reshaping it one digit time later; digit delays are often used, therefore, to 'clean up' pulses that have become attenuated or mis-shapen or have been slightly delayed by stray circuit time constants. It is also necessary to delay pulse trains by one word-time; a word can be stored (i.e. 'remembered') for an indefinite time by making it circulate repetitively through such a one-word delay. The type of one-word delay used in Pegasus is a magnetostrictive nickel line; pulses are propagated down a line of appropriate length as compression waves, and are amplified and reshaped after detection at the remote end. Further details of the logical elements will be found in a companion volume to this handbook.

- 6. Fig. 3.1 shows the symbols used for AND gates, OR gates, inverters and delays; later it will be necessary to introduce symbols to represent the combinations of these elements that make up the logical packages. Note that the presence of 'arrowheads' distinguishes an OR gate from an ordinary soldered connection in which a lead divides into two branches.

- 7. Fig. 3.1 also shows how an inverter, two AND gates and a nickel line can be used as a one-word store. The input word is allowed through AND gate x by a train of gating pulses, which are positive for one word-time only. It passes down the line, emerging one word-time later, and recirculates through AND gate y as long as the output of the

inverter is positive, i.e. as long as there are no pulses applied at the input of the inverter. The content of the store can be erased simply by feeding one word-length of pulses into the inverter so as to close AND gate y. Another type of 'memory' circuit is the 'staticiser', which will 'remember' a single digit only. The circuit is similar (see fig. 3.1) except that a digit delay is used instead of a nickel line. The digit to be 'remembered' is selected by a setting pulse, which is applied to AND gate x at the appropriate instant. If the digit is a 1, so that it is represented by a positive pulse, a pulse will circulate via AND gate y until it is erased by a resetting pulse fed at any instant into the inverter.

#### ARITHMETICAL CIRCUITS

# Adders

8. In paragraph 10 of Chapter II, it was shown that the carry digit in addition is obtainable by a simple AND operation, i.e.

$$c = a & b$$

Hence the first logical circuit in fig. 3.2 would be enough to generate the carry digit, the delay being needed to bring the digit into the next 'column' for the next step in the addition. The binary digits inserted in the diagram are not intended to be binary numbers, but are truth-table representations of conditions at various points in the circuit. Thus

9. The sum digit in addition can be expressed by the formula

$$s = (a v b) & \sim (a b)$$

This sequence of operations can be expressed in words as follows:-

- (i) OR operation on a and b.

- (ii) AND operation on a and b.

- (iii) Invert result of step (ii).

- (iv) AND operation on results of steps (i) and (iii).

The second logical circuit shown in Fig. 3.2 will perform this series of operations; as before, digits are inserted in the diagram to represent the truth-table condition at each point, thus:

- 10. The circuits just described will generate the carry and sum digits when two binary numbers are added; but they cannot perform the full process of addition, as no account has yet been taken of the carry digit, c', from the previous column. The combination of these two circuits is called a 'half adder'. It can be used in cases where a digit cannot be present both in the 'carry' and in input b. The third circuit in fig. 3. Shows a half adder. During the first digit-time, a digit at b is added to the digit at a; during the second and successive digit times, any carry digit produced in the previous place is added to the digit at a.

- 11. In paragraph 13 of Chapter II, an alternative formula for the sum digit was given. This was

$$s = [a \& \sim (a \& b)] \cup [b \& \sim (a \& b)]$$

which implies the following sequence of operations:

- (i) AND operation on a and b.

- (ii) Invert result of step (i).

- (iii) AND operation on a and result of step (ii).

- (iv) AND operation on b and result of step (ii).

- (v) OR operation on results of steps (iii) and (iv).

An alternative circuit for generating the sum digit, and a half adder built on this principle are shown on the right-hand side in fig. 3.2; as before, truth-table digits are inserted in the figure at the appropriate points. Two of the AND gates in each of the half adders are doing the same job, producing (a & b), and could, of course, be replaced with a single gate. However, small economies like this have been sacrificed in Pegasus in favour of greater economies resulting from the use of standard packages.

- 12. A half adder can only deal with two full-length inputs, one of which must be, after the first digit-time, the sequence of carry digits, whereas the full process of addition requires three inputs two numbers and a carry sequence. It is possible, however, to make a full adder by combining two half adders as shown in fig. 3.3; the arrangement is shown schematically on the left. In the first half adder, number b is added to the carry sequence; in the second half, the sum of these two is added to number a to give the final output. The carry digit can arise in either half of the addition, but not in both, as can be easily verified from the truth table: the two 'carry' outputs can therefore be combined in an OR gate to give the final carry sequence.

- 13. The central diagram of fig. 3.3 shows the complete circuit of a full adder evolved from two half adders. One half adder is of the first type discussed: the other half adder is of the second type. The truth-table for full addition is given below, and the lines of this table are inserted in the appropriate places in the figure.

This is the most convenient general arrangement for the Pegasus packages; but there are certain economies that can be made without upsetting its operation. First, two 'carry' delays are unnecessary: the OR operation can take place as well before the delay as after it. Second, the AND gate numbered 6 is unnecessary. It can easily be verified - by a truth-table or otherwise - that two two-input AND gates in cascade can be replaced by one three-input AND gate. AND gate 6 may therefore be omitted; its two inputs would then be applied direct to AND gates 7, 8 and 11, which would become three-input gates. Third, no connection need be made between inverter 5 and AND gate 7. It will be recalled that the purpose of gate 3 and inverter 5 is to suppress the sum digit in the first half adder when b and c' are present together; it is cherefore unnecessary to connect these to gate 7, which is concerned only with the carry digit. The carry digit resulting from the simultaneous presence of b and c' is produced in any case by gate 1. The final circuit of the full adder is therefore as shown in the third diagram of fig. 3.3.

#### Subtractors

14. In Chapter II (paragraph 16 et seq.) it was shown that the difference digit in subtraction is identical with the sum digit in addition, and that the two operations differ only in the carry sequence generated. It was shown, too, that the subtractive carry can be produced in the same way as the additive carry if  $\sim a$  be substituted for a in its generation so that the carry digit becomes

$$\sim a \& b$$

instead of  $a \& b$

The short truth tables are given below for reference.

It would, of course, be possible to modify the half adder to form a half subtractor by supplying an extra inverter to form  $\sim a$  from a; but this is not really necessary. The inverter already in the half adder produces  $\sim (a \& b)$ ; an AND operation between its output and b would therefore give  $\sim (a \& b) \& b$ , which, by Boolean algebra, can be shown to be equivalent to

$$(a v \sim b) & b = v \sim b$$

=  $v \sim b$  (since  $v \sim b \sim b = 0$ )

Thus a half subtractor can be formed from a half adder simply by connecting the output of the inverter, instead of a, to the AND gate producing the carry digit. A half subtractor derived from the second form of half adder is shown in fig. 3.4, with 'truth-table' lines inserted as appropriate.

15. The half subtractor, like the half adder, cannot deal with two input sequences as well as a carry sequence. A full subtractor can, however, be built up from a half

adder and a half subtractor. In this context, it should be remembered that the subtractive carry digit is to be regarded as negative, i.e. it must be added to b if the difference (a-b) is required and to a if the difference (b-a) is required. This point is illustrated in the schematic diagram at the top of fig. 3.4. The full-subtractor circuit of fig. 3.4 is derived from this in the same way as the full-adder circuit was derived, one delay, one AND gate and one unnecessary connection being eliminated. The full truth table is given below for reference.

16. The adder and subtractor circuits can be combined to form the adder-subtractor circuit shown in fig. 3.4. When the circuit is used as an adder, AND gate 16 is opened by the triggering waveform so that a is used in generating the carry sequence. If it is required to use the circuit as a subtractor, gate 17 is opened instead of gate 16, so that the output of inverter 10 is used in place of a for generating the carry sequence.

#### CIRCUIT SYMBOLS

- 17. Certain combinations of logical elements occur very frequently in logical circuits. For example, the arrangement of a digit delay preceded by an OR gate fed from two AND gates occurs in the adder-subtractor and in the staticiser. For this reason, the standard packages used in Pegasus have been designed in terms of common combinations of logical elements. Inevitably there are components that remain unused in the logical design; but the number of package types is reduced, with consequent manufacturing economies. As well as the logical elements already discussed, the use of cathode followers is demanded by considerations of output loading. Furthermore, output amplifiers are required so that the results of computer operations can be transmitted to some form of output mechanism.

- Nine types of logical package are used in Pegasus. The symbols for the com-18. binations of logical elements on these are given in fig. 3.5. It will be noticed that there are generally several logical combinations to a package. The basic elements that incorporate thermionic valves, viz. digit delays, nickel lines, inverters and cathode followers, are generally preceded by crystal gates. Digit delays may be preceded by one three-input AND gate (single delay, package type 2) or by two three-input AND gates feeding an OR gate (twin delay, package type 1). Nickel lines (package type 6), of which there is only one to a package are fed in the same way as twin delays; the output stage is actually a digit-delay circuit. The nickel-line package also contains a special inverter for use as the 'erase' element of a one-word store. Two lengths of nickel line. 35-digits and 42-digits, are used in Pegasus. Most of the logical combinations have alternative outputs, a direct output and a 'mix' output through an OR crystal (which is drawn obliquely on the symbol). OR gates are usually made up from these 'mix' outputs; otherwise the combination of OR gate and cathode-follower (package type 8) is used.

- 19. The number generator, package type 7, is used for producing a train of digit pulses from tape-reader outputs or handkey settings. It consists of three two-input AND gates whose outputs feed a cathode-follower through an OR gate. This cathode-follower has a 'mix' output only, as several such elements must generally be used together in practice. Output-one elements, package type 9, are used for feeding neon indicator lamps or external-conditioning relays. In the latter application two elements are used in parallel, and are preceded by two AND gates feeding an OR gate, suitable gating networks being provided on the packages. Output-two elements, package type 10, can supply more power than output-one elements, and are used for driving the output equipment.

- 20. All packages except those of type 6 (nickel line) carry two or more identical elements. These are numbered in logical diagrams, as shown in the last column of fig. 3.5, to correspond to the related pin numbers on the package connected, the element with the lowest pin numbers being referred to as element 1 on the package. Where an element has two or more entry gates, these are distinguished from one another with the letters x, y and z, the letter x referring to the gate with the lowest pin numbers. The actual construction and layout of the packages is the subject of a separate handbook, to which the reader is referred for details of pin numbers and component values.

- 21. The packages may carry up to seven test points, which are accessible from the front of the cabinet. A test point is provided at the output of each element, those elements with alternative direct and 'mix' outputs generally being provided with a test point for each. All 'mix' test points are marked 'M', with reference number of the corresponding element on the package. Direct-output test points are marked with a letter, representing the type of logical circuit, and the reference number. Cathode-follower test points are marked with a number only. The test points corresponding to elements 4 and 5 on the cathode-follower package (type 8) may be connected either to the direct or to the 'mix' output as convenient.

- 22. The Pegasus computing cabinet comprises three bays, each of which is large enough to accommodate ten rows of twenty packages each. There are only four rows in the first bay; these are numbered from the top downwards 10 to 13. The rows in the second and third bays are numbered 20 to 29 and 30 to 39 respectively. The packages within a row are designated by letters, which are in alphabetical order from left to right when the row of packages is viewed from the front of the cabinet. The letters used are:

# CDEFGHJKLMPQRSTUVWXY

Letters B, I, O and N are omitted, and letters A and Z are used for the interconnectors between bays. In logical diagrams, each symbol is marked with the row number and the letter of the package carrying the corresponding components, and the reference number of the element on the package. Thus a logical symbol marked 26G1 would correspond to the first element on the fifth package in the seventh row down of bay 2.

#### Applications

- 23. To illustrate the use of the combined symbols the staticiser and one-word store of fig. 3.2 and the adder-subtractor of fig. 3.4 are redrawn in fig. 3.6. As inverters do not exist in Pegasus as separate entities, a combination of inverter and AND gate must be used for erasing the content of the store or for clearing (resetting) the staticiser. Note how the 'mix' outputs of the cathode-followers after the 'add' and 'subtract' AND gates in the adder-subtractor are used together to make an OR gate. Note too that the output is taken through a delay; delays are often used in Pegasus, as here, simply to restore the amplitude and timing of a waveform after a series of logical operations. When a negative number is produced by subtraction, an infinite series of carry digits is generated. As only one of these, the sign digit, is necessary for general purposes, or two of them for overflow detection, a 'carry suppression' waveform is employed to close the two AND gates preceding the 'carry' delay at the appropriate instant.

- 24. Fig. 3.6 also shows a parity-counting circuit. If the number of 'ones' in a binary number is odd, the parity is said to be odd: if the number is even, the parity is even. Parity counts applied at strategic points in a computer provide a simple method of checking for circuit faults automatically; if any one digit changes its value, the fact will be detected immediately. The circuit shown consists of a staticiser, S, an inverter (preceded by an AND gate) and a cathode-follower. The staticiser is 'set' just before the digit waveform appears at the inputs of the cathode-follower and inverter, so that a pulse circulates through the 'y' gate until the first 'one' in the digit waveform appears; this acts as an 'erase' signal and resets the staticiser, The output of the staticiser is now zero, so the AND gate before the inverter is closed. The next 'one' in the digit waveform will pass through the cathode-follower and activate the staticiser again, until it is reset again by the next 'one'. Owing to the staticiser delay, the final parity will not be indicated until after the last digit has passed. The parity count will then be positive for a waveform with even parity, and zero for a waveform with odd parity. Note the use here again of 'mix' outputs to form an OR gate.

# CHAPTER IV

# STORAGE AND THE ORDER CODE

|                    |     |      |     |     |     |     |     |     | Para. |

|--------------------|-----|------|-----|-----|-----|-----|-----|-----|-------|

| STORAGE FACILITIES | ••  | ••   | ••  | ••  | ••  | ••  | ••  | ••  | 1     |

| Main Store         | • • | ••   | ••  |     | ••  | ••  | ••  | ••  | 1     |

| Computing Store    | ••  | ••   | ••  | ••  | ••  | ••  | ••  | • • | 2     |

| Symbols            | ••  | ••   | • • | ••  | • • | • • | • • | ••  | 5     |

| THE ORDER CODE     |     | . •• | ••  | • • | • • | • • | ••  | ••  | 7     |

| Function Code      | ••  | ••   | ••  | ••  | ••  | ••  | • • |     | 10    |

| Modification       | • • | ••   | • • | ••  | • • | ••  | • • | ••  | 26    |

| EV AMDI E          |     |      |     |     |     |     |     |     | 20    |

# CHAPTER IV

# STORAGE AND THE ORDER CODE

Readers who are not conversant with the techniques and terminology of computer engineering are advised to study the Introduction to Volume I before reading any further in this volume.

#### STORAGE FACILITIES

#### Main Store

1. The main store in Pegasus is a drum coated with ferromagnetic material and rotating at 3720 r.p.m. It carries 40 information tracks (strictly speaking, track pairs; alternate digits are written on alternate tracks as will be explained in Chapter XI) of which 32 are available for normal storage; the other 8 tracks are reserved for the permanent record (initial orders and test routines) and are capable of being 'read from' but not 'written on'. Each track carries 128 words, which are arranged, from the standpoint of the programme, in 16 'blocks' of eight words each. The magnetic drum will thus accommodate up to 512 8-word blocks, or 4096 words, in normal-storage locations, and 128 8-word blocks, or 1024 words, as a permanent record.

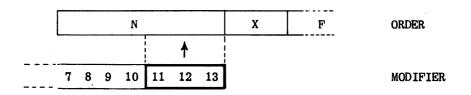

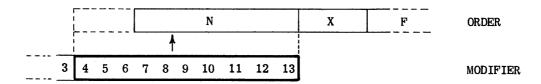

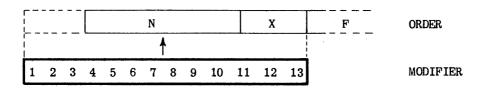

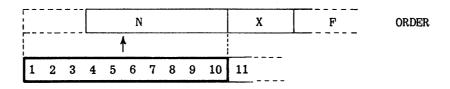

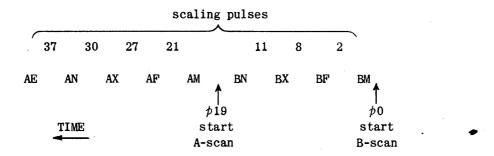

## Computing Store