# Development and Analysis of a Workstation Computer

# A dissertation submitted to the SWISS FEDERAL INSTITUTE OF TECHNOLOGY ZURICH

for the degree of Doctor of Technical Sciences

presented by Johann Jakob Eberle, Dipl. El.-Ing. ETH born August 18, 1959 citizen of Häggenschwil (St.Gallen)

accepted on the recommendation of Prof. Dr. N. Wirth, examiner Prof. Dr. W. Fichtner, co-examiner

# Acknowledgements

I am deeply indebted to Professor N. Wirth for giving me the opportunity to develop the hardware of the workstation Ceres and for supervising this thesis. His profound competence and insight are invaluable.

I thank Professor W. Fichtner for his willingness to be my co-examiner and for advising me on this thesis.

I am grateful to my colleagues for many valuable discussions and for their help. In particular, thanks go to the colleagues and friends who participated in the Ceres project: Frank Peschel and Matthias Wille, who shared the project from the beginning and worked on the system software for Ceres; Immo Noack, who helped in the construction of the Ceres hardware, and thanks to his engagement the Institut für Informatik is now equipped with 50 Ceres workstations. Their efforts were indispensable. I also thank Hans Hablützel for proof-reading the thesis paper.

On behalf of the project team I acknowledge the support by National Semiconductor Corporation and the helpful cooperation of its representative in Switzerland, H. Eisenring.

# Contents

| Ack | nowl   | edgements                                   | 3  |

|-----|--------|---------------------------------------------|----|

| Cor | ntents |                                             | 4  |

| Abs | stract |                                             | 6  |

| Kur | zfassı | ung                                         | 7  |

| 1   | Intro  | oduction                                    | 9  |

| 2   | Haro   | dware Description of the Workstation Ceres  | 11 |

|     | 2.1    | Introduction                                | 11 |

|     | 2.2    | Hardware Structure                          | 11 |

|     | 2.3    | Hardware Implementation                     | 13 |

|     |        | 2.3.1 Processor Board                       | 13 |

|     |        | 2.3.2 Memory Board                          | 23 |

|     |        | 2.3.3 Display Controller Board              | 25 |

|     |        | 2.3.4 Disk Controller Board                 | 29 |

|     |        | 2.3.5 Motherboard                           | 30 |

|     | 2.4    | Hardware Extensions                         | 30 |

| 3   | Rast   | ter Graphics Interface Design               | 32 |

|     | 3.1    | Introduction                                | 32 |

|     | 3.2    | Raster Graphics Principles                  | 32 |

|     |        | 3.2.1 Image Storage                         | 33 |

|     |        | 3.2.2 Image Creation                        | 37 |

|     | 3.3    | Raster Graphics Interface for Ceres         | 39 |

|     |        | 3.3.1 Frame Buffer                          | 39 |

|     |        | 3.3.2 Display Refresh Controller            | 40 |

|     |        | 3.3.3 Why no Hardware Support for RasterOp? | 41 |

| 4   | Mic    | rocomputer Bus Design                       | 44 |

|     | 4.1    | Introduction                                | 44 |

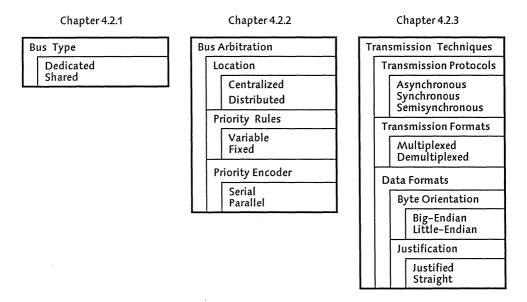

|     | 4.2    | Classification Criteria                     | 44 |

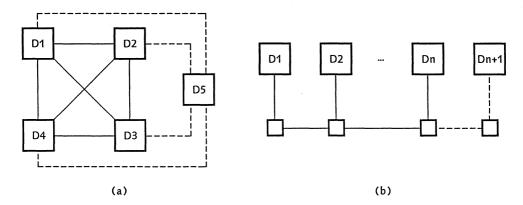

|     |        | 4.2.1 Bus Topology                          | 45 |

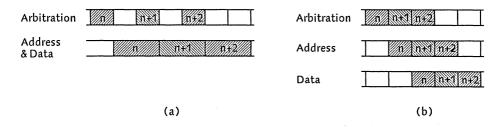

|     |        | 4.2.2 Bus Arbitration                       | 48 |

|     |        | 4.2.3 Transmission Techniques               | 51 |

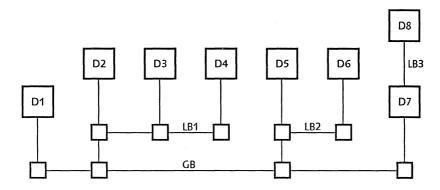

|     | 4.3    | Design of the Ceres Bus System              | 54 |

|     |        | 4.3.1 Slave Processor Bus                   | 55 |

|     |        | 4.3.2 Memory Bus                            | 56 |

|     |        | 4.3.3 Why not a Standard Bus?               | 63 |

| 5   | Ana    | lysis of Processor-Memory Communication     | 67 |

|     | 5.1    | Introduction                                | 67 |

|     | 5.2    | Experimental Methods                        | 69 |

|    | 5.3                 | Experimental Evaluations                  | 70  |  |

|----|---------------------|-------------------------------------------|-----|--|

|    | 5.4                 | Cost Analysis of the Memory Bus           | 79  |  |

|    | 5.5                 | Conclusions                               | 81  |  |

| 6  | Exp                 | eriences with Complex Integrated Circuits | .82 |  |

| 7  | Results             |                                           |     |  |

|    | 7.1                 | Summary of the Thesis                     | 84  |  |

|    | 7.2                 | Practical Results                         | 85  |  |

| Ар | pendi               | ces                                       |     |  |

| Α  | Circ                | 86                                        |     |  |

|    | A.1                 | Processor Board                           | 86  |  |

|    | A.2                 | Memory Board                              | 93  |  |

|    | A.3                 | Display Controller Board                  | 95  |  |

| В  | PAL Logic Equations |                                           | 100 |  |

| C  | Test Programs       |                                           |     |  |

| Re | ferenc              | res                                       | 107 |  |

| Cu | rricul              | ım Vitae                                  | 113 |  |

#### **Abstract**

The workstation Ceres is a stand-alone computer for a single user. The design is an example of a simple system architecture reflected by a careful implementation with minimal costs. Ceres is based on the 32-bit microprocessor NS32032, which is oriented to the use of high-level and modular languages. A key feature is the high-resolution bitmapped graphics display which is attractive for applications such as program development or document processing. The arbitrated memory bus and the modular system organization are open to future hardware extensions.

This thesis documents the hardware development of the workstation Ceres. The design objectives of the raster graphics interface and of the bus structure are discussed in detail. Finally, processor-memory communication of two prototype versions is analysed, which differ only in the width of their data paths to memory.

The raster graphics interface of Ceres contains an integral frame buffer memory, which is directly addressable by the CPU. The frame buffer is based on video RAM technology which ideally meets the high video bandwidth requirements of the 1024 x 800 non-interlaced display. An inexpensive and flexible solution is retained by dispensing with dedicated hardware support for image manipulation.

The backbone of the Ceres computer is the memory bus, which is shared by multiple master devices. The bus is controlled by a centralized arbiter. Short response times are ensured in that the shared memory is re-allocated for every memory cycle according to fixed priorities. A default assignment strategy prevents the processor from being significantly slowed by arbitration delays.

The analysis of processor-memory communication is motivated by the observed small benefit in performance gained by replacing the NS32016 CPU with the NS32032 CPU and thus doubling the memory bus bandwidth. Measurings show that the bus capacity of the NS32032-based Ceres is only used to a small degree. Therefore, the additional costs can hardly be justified. This contrasts with the frequently heard claims of the superiority of 32-bit computers.

# Kurzfassung

Ceres ist ein Arbeitsplatzrechner für einen einzelnen Benützer. Der Entwurf ist ein Beispiel einer einfachen Systemarchitektur, welche sich in einer sorgfältigen Implementierung mit minimalem Aufwand widerspiegelt. Ceres basiert auf dem 32-bit Mikroprozessor NS32032, der auf die Verwendung von höheren, modularen Programmiersprachen ausgerichtet ist. Eine Besonderheit ist der hochauflösende Rastergrafik-Bildschirm, welcher Anwendungen wie die Programmentwicklung oder das Bearbeiten von anspruchsvollen Dokumenten attraktiv gestaltet. Der arbitrierte Speicherbus und der modulare Systemaufbau erlauben künftige Erweiterungen der Hardware.

Die Dissertation dokumentiert die Hardware-Entwicklung des Arbeitsplatzrechners Ceres. Ausführlich werden die Entwurfskriterien der Rastergrafik-Schnittstelle und der Busstruktur besprochen. Schliesslich wird die Prozessor-Speicher-Kommunikation zweier Prototypen-Versionen untersucht, die sich lediglich in der Breite ihrer Datenpfade zum Speicher unterscheiden.

Die Rastergrafik-Schnittstelle von Ceres enthält einen separaten Bildschirmspeicher, welcher von der CPU direkt zugegriffen werden kann. Der Bildschirmspeicher ist mit Video-RAMs aufgebaut, die sich auf ideale Weise für die benötigte hohe Video-Bandbreite des ohne Zeilensprungverfahren arbeitenden Bildschirms eignen. Eine kostengünstige und flexible Lösung ist gewährleistet, indem auf spezielle Hardwareunterstützung der Bildmanipulationen verzichtet wurde.

Das Rückgrat des Ceres-Rechners ist der arbitrierte Speicherbus, der von mehreren sendenden, als auch empfangenden Teilnehmern gemeinsam benutzt wird. Der Bus wird von einem zentralen Arbiter verwaltet. Indem jeder Zugriff auf den gemeinsamen Speicher gemäss festen Prioritäten einzeln vergeben wird, werden kurze Antwortzeiten ermöglicht. Liegen keine anderweitigen Busanforderungen vor, so kann die CPU dank einer bevorzugten Behandlung ohne Verzögerung auf den Speicher zugreifen.

Die Analyse der Prozessor-Speicher-Kommunikation wurde durch den geringen Leistungsgewinn veranlasst, welcher beobachtet wurde, nachdem die NS32016 CPU durch die NS32032 CPU ersetzt wurde und damit die Speicherbus-Bandbreite verdoppelt wurde. Messungen zeigen, dass die Buskapazität der NS32032-basierten Ceres nur wenig ausgelastet ist. Die zusätzlichen Kosten sind deshalb kaum zu rechtfertigen. Diese Feststellung steht im Widerspruch zur oft gehörten Ansicht der Überlegenheit einer 32-bit Rechnerarchitektur.

# 1 Introduction

This thesis documents and analyses the design and implementation of the 32-bit workstation Ceres. The design sets an example of a simple system architecture reflected by a careful implementation. The development was made in an environment free from commercial restrictions such as compatibility with existing products or industrial standards. This was both the chance and the obligation to develop general and powerful concepts.

The machines currently being designed are based on principles that have been known for years. Technology is the motive force for new designs, more than new principles. Old principles are reapplied by using new technologies, they are analysed and, if necessary, improved. Learning about computer hardware engineering means designing and implementing. In this sense, the thesis shall be a contribution to systematic computer hardware engineering.

Personal computing has its roots at the Xerox Palo Alto Research Center, where in 1973 the Alto computer was developed [Thacker 79]. Rather than providing a centralized computing facility, computing power was distributed to its users. Further innovative provisions were the bitmapped raster display and the mouse pointing device.

Under the influence of the Alto computing environment, the Lilith computer was developed in the years 1977 until 1979 [Ohran 84]. With it, personal computing made its entry into the Institut für Informatik of the Swiss Federal Institute of Technology (ETH). The architecture of Lilith is optimized for the development and execution of Modula-2 programs. The processor is realized as a microprogrammed stack machine based on bit-slice technology. While the Lilith processor architecture still compares favourably with today's microprocessors, its implementation is getting on in years.

The rapidly evolving VLSI technology has provided the motivation to design a new workstation. The project was stipulated by Professor N. Wirth in his efforts to systematically develop useful tools for research and education. Notable, already mentioned results of these efforts are the workstation Lilith [Wirth 81a] and the programming language Modula-2 [Wirth 82]. The new workstation has been named CERES, an acronym for Computing Engine for Research, Engineering, and Science. In the old Italian and later Greek mythology, Ceres is the name of the goddess of fertility.

The project started in early 1984 when the basic concepts of the hardware architecture were proposed by Professor N. Wirth. A first prototype was finished a year later in the spring of 1985. The prototype was based on the 16-bit processor NS32016 from National Semiconductor. At that time, future developments of integrated circuits were seen to be concentrated on 32-bit processors. Therefore, a second prototype based on the 32-bit processor NS32032 was developed, which is software compatible with its family member NS32016. In fall 1985, the redesign was complete. By the end of 1986, a series of 30 computers was built. Another series of 20 computers is currently being finished.

The venture to develop a personal computer was shared with Frank Peschel and Matthias Wille, who have ported the Lilith operating system Medos-2 [Knudsen 83, Peschel 87]. A one-pass Modula-2 compiler was developed by Professor N. Wirth [Wirth 86b]. The two prototypes were implemented and debugged by the author alone. Roger Burlet developed

the computer cabinet. Immo Noack designed the layouts for the printed circuit boards and was in charge of manufacturing the two series.

The following goals were set for the development of the workstation Ceres:

- The computer, particularly the processor has to efficiently support the execution of high-level language programs. The architecture should incorporate one of the recent microprocessors that claim to be oriented to the use of high-level languages.

- A high-resolution, flicker-free display and a mouse pointing device have to be included in order to provide flexibility and comfort for the human interaction with the computer.

- The design of the computer has to be simple and systematic. The realization has to be modular and extensible.

- Development and manufacturing costs have to be minimized. Only available standard components must be used.

The thesis consists of seven chapters. Chapter 2 contains a detailed hardware description of the workstation Ceres. Chapter 3 adds some design considerations made during the development of the raster graphics interface for Ceres. Chapter 4 provides a classification of microcomputer buses, and based on it discusses the bus structure of Ceres. Chapter 5 examines processor-memory communication of Ceres in order to find an explanation for the observed low performance benefit gained by the doubled memory bus bandwidth of the second prototype. Chapter 6 describes the experiences with complex integrated circuits made during the period of development. Finally, Chapter 7 summarizes the results presented in this thesis.

# 2 Hardware Description of the Workstation Ceres

#### 2.1 Introduction

The hardware of Ceres sets an example of a simple system architecture reflected by a clean implementation. The concise description is presented within this chapter and is appreciated in particular by the hardware designer who wants to add his own extensions and by the software designer who wants to write system programs. Hardware and software have to be designed together in order to attain efficiency and reliability. The basis is a brief and comprehensible documentation of the design.

The entire machine is implemented with 250 integrated devices ranging from SSI up to VLSI. Nearly half of these components are storage devices. Random logic is provided by standard TTL devices, mostly ALS and AS; where a desired function could not appropriately be realized with available fixed TTL functions, programmable logic was used. The circuits are mounted on four printed circuit boards that are connected by a backplane board. All printed circuit boards are fabricated with four metal layers allowing separate power and ground planes in order to minimize electrical problems.

The following sections contain a textual description of the Ceres hardware. The corresponding schematic circuit drawings are contained in Appendix A. The functional specifications of the programmable logic devices are listed in Appendix B.

#### 2.2 Hardware Structure

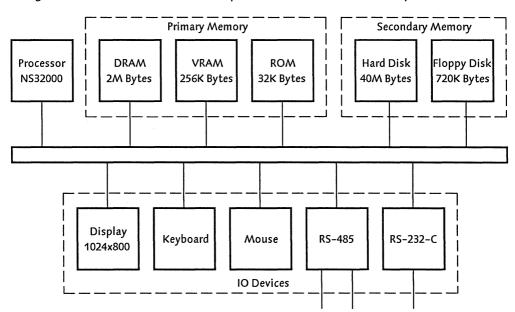

The Ceres hardware consists of a 32-bit processor based on the National Semiconductor Series 32000 chip set, primary memory, secondary memory, and miscellaneous input and output devices. These include a high-resolution display, a serial keyboard, a mouse pointing device, an RS-232-C serial line interface, and an RS-485 serial line interface. Figure 2.1 shows a block diagram of the hardware structure. This section gives a brief description of the main hardware characteristics.

#### Processor

The switchboard of the Ceres computer is a National Semiconductor NS32032 32-bit microprocessor. Two slave processors add capabilities for virtual memory management and floating-point arithmetic. The processor operates at a clock rate of 10 MHz, resulting in a memory cycle time of 400 ns. It has an addressing range of 16M bytes. Its repertoire includes 83 basic instructions with 9 addressing modes [NS 86a].

# Primary Memory

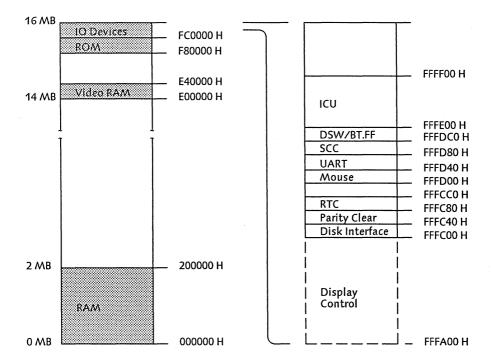

The primary storage of Ceres consists of 2M bytes of dynamic RAM, 256K bytes of video RAM, and 32K bytes of ROM. The former is implemented with 256K-bit dynamic RAM chips. Parity checking makes it possible to detect single bit errors within a data byte. A special type of dynamic RAM, a 64K-bit video RAM, is used to store the display bitmap. 64K-bit chips form the ROM memory for bootstrap and diagnostic software.

#### Secondary Memory

The secondary storage of Ceres consists of a Winchester hard disk drive and a floppy disk drive. The 5 1/4" hard disk has a formatted capacity of 40M bytes, an access time of 40 ms, and a data transfer rate of 5 Mbits per second. For backup, a 3 1/2" floppy disk is available with a formatted capacity of 720K bytes, an access time of 94 ms, and a data transfer rate of 250 Kbits per second.

# Input/Output Devices

The display is a high-resolution 17" raster scan monitor. It can display 819'200 dots which are stored in a matrix called bitmap that is 1024 dots wide and 800 dots high. The picture is refreshed at a rate of 62.15 frames per second (non-interlaced) which results in a nearly flicker-free image. The bitmap information is stored in a separate, dedicated memory implemented with video RAMs.

In addition to a standard serial ASCII keyboard, an opto-mechanical, three-button mouse is provided with a resolution of 380 counts per inch.

The standard RS-232-C serial interface works with asynchronous data transfer rates from 50 to 38'400 bits per second. A higher transmission speed can be obtained with two RS-485 serial ports for data transfer rates up to 230.4 Kbits per second. In a multipoint configuration, this interface allows the implementation of a low-cost computer network.

**Figure 2.1** Hardware structure of the Ceres computer.

## 2.3 Hardware Implementation

The Ceres computer is packed in a 465 mm x 190 mm x 365 mm cabinet small enough for desktop application. Display monitor, keyboard, and mouse are separate and individually connected to the computer cabinet. The cabinet houses the power supply, the hard disk drive, the flexible disk drive, and the card cage, which can hold up to six circuit boards. The board dimensions are the extended double-Eurocard format, which is 220.0 mm x 233.4 mm. Packaging and the parallel interconnection structure of the backplane make it possible to access every signal with a scope probe for debugging and maintenance without providing additional facilities such as a bus extension card.

The power supply is rated for a wattage of 130 W. Excluding the display monitor, the basic configuration of Ceres consumes 78 W during power-up and 57 W during normal operation (typical values). The capacity of the power supply, therefore, will still be sufficient if hardware extensions are added. It must be noted that the hard disk drive and the disk controller consume about as much as half of the figure given for normal operation.

The hardware of Ceres is physically divided into several boards which are connected by the memory bus:

- the *processor board* contains the processor chip set, the memory bus access and timing controller, the boot ROM, and various IO devices

- the *memory board* holds the dynamic RAM memory

- the display controller board comprises the video RAM memory for the displayed bitmap and the logic to serialize the bitmap data into the video refresh data

- the disk controller board combines a controller for both the hard disk and the floppy disk drives

- all boards communicate via the *motherboard* which contains the memory bus

Based on the circuit diagrams in Appendix A, the hardware of Ceres is explained in the following sections. The specifications of the integrated circuits used are contained in the referred data sheets.

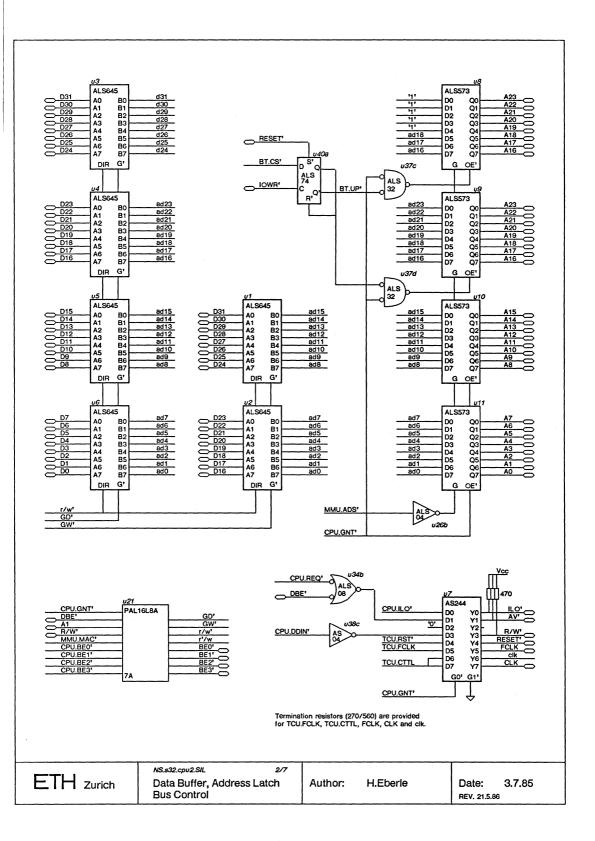

#### 2.3.1 Processor Board

#### Processor

The NS32032 central processing unit (CPU) has a uniform linear 16M-byte addressing range and a full 32-bit architecture and implementation [NS 86a]. Internal working registers, internal and external data paths, and ALU are all 32-bit wide. There are eight general purpose registers which provide local, high-speed storage for the processor, such as holding temporary variables and addresses. Eight dedicated registers are used to store address and status information. The register set, the supported data types, and the instruction set are fashioned after high-level language instructions [NS 84a]. Code generation is made easier by a high degree of symmetry. (Note: A processor's architecture is said to be symmetrical if every supported data type is provided with a complete set of operators and if each operator can use any addressing mode to access operands.) An analysis of the NS32000 architecture in respect of the code generation by a compiler is contained in [Wirth 86a].

A slave processor is an auxiliary processing unit which operates in coordination with the CPU. The NS32082 memory management unit (MMU) performs address translation, virtual memory management, and memory protection [NS 86a]. The NS32081 floating-point unit (FPU) operates on two floating-point data types: single precision (32 bits) and double precision (64 bits). Arithmetic operations include Add, Subtract, Multiply, Divide, and Compare. Several Move and Convert instructions are also available.

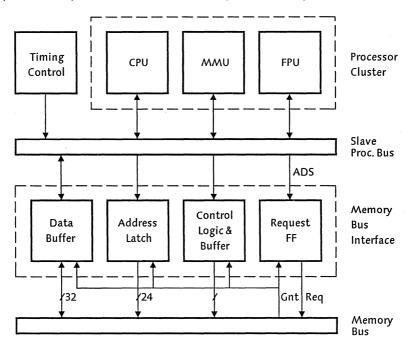

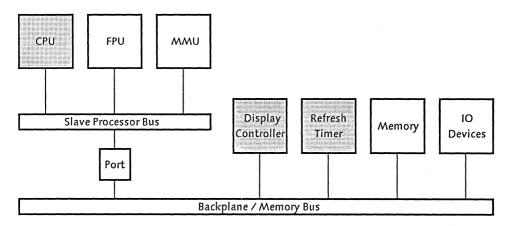

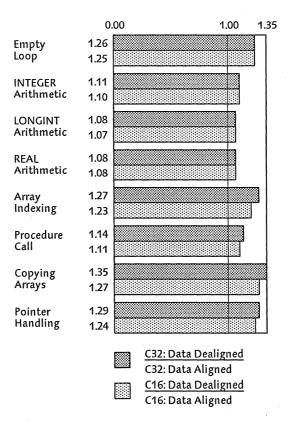

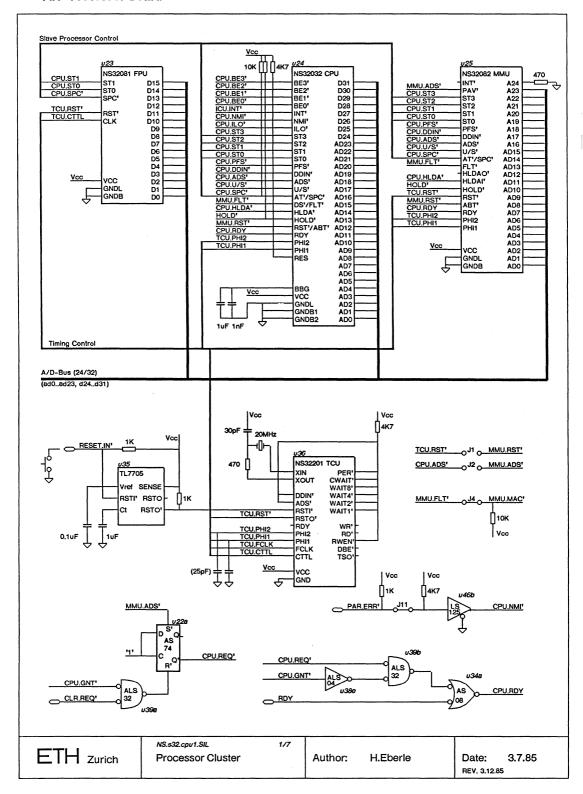

The structure of the processor and its memory bus interface are illustrated in the block diagram of Figure 2.2. The following blocks may be distinguished:

- the processor cluster consists of the NS32032 CPU, the NS32082 MMU, and the NS32081

FPU

- the *timing control unit* generates the clock and reset signals for the slave processor and the memory bus

- the *memory bus interface* connects the address, data, and control signals of the local, multiplexed slave processor bus to the demultiplexed memory bus

**Figure 2.2** The processor and its memory bus interface.

The processor cluster, i.e. the CPU (u24) and its slave processors (u23, u25) are connected to a local, multiplexed address and data bus (ad0-ad23, d24-d31) that combines 32 bits of data with 24 bits of address. The local bus is required either for memory access (or access to IO devices which are memory mapped) or slave processor communication. In the former case, the memory bus is transparent to the slave processor bus. In the latter case, only the two least significant bytes of the data bus are used. Note that the CPU is solely responsible for memory access, i.e. operands of a slave processor instruction are always fetched from memory by the CPU.

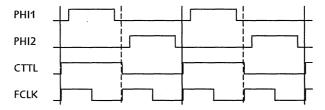

The NS32201 timing control unit (TCU, u36) provides a two phase, non-overlapping 10 MHz clock (TCU.PHI1, TCU.PHI2), which is used by the processor chips [NS 86a]. In addition, a 10 MHz and a 20 MHz TTL compatible clock (TCU.CTTL, TCU.FCLK) are generated. The timing waveform of these clock signals is shown in Figure 2.3. The TCU also provides circuitry that meets the reset requirements of the processor chips. If the reset input line RSTI' is pulled low, the TCU asserts TCU.RST' which resets the processor chips. The RSTI' input signal is provided by the TL7705 (u35) which contains a power voltage sensor and a debounce circuit. It is activated at power-up or when the externally mounted reset button has been pressed. The reset and clock signals on the memory bus (RESET' and CLK, FCLK) are buffered versions of the corresponding TCU signals (u7).

Figure 2.3 TCU clock signals.

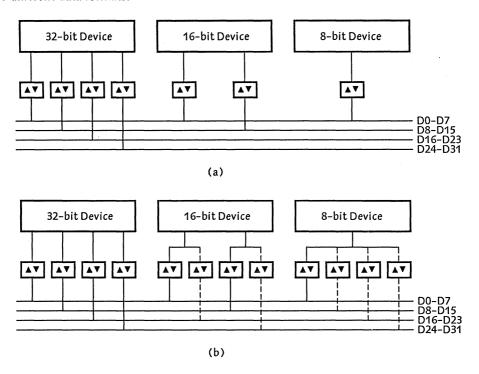

The *memory bus interface* consists of a 32-bit wide data buffer, a 24-bit wide address latch, a buffer for several control lines, and a circuitry that requests a bus cycle when the processor wants to access the memory. The data buffer is made up of four 74ALS645 octal bus transceivers (u3-u6) [TI 83c]. Two additional 74ALS645s (u1, u2) are needed for the MMU with its 16-bit wide data bus to access the higher data word of the main memory. When the MMU accesses an odd memory word (A1=1), the higher data word of the memory bus (D16-D31) has to be mapped onto the lower word of the processor bus (ad0-ad15). The signals GW' and GD', required for the buffer enable inputs, are generated by part of a PAL16L8A PAL device (u21) [MMI 78]. The MMU has to access the memory in order to update its internal address translation cache from page table entries in memory or to update certain status bits within them.

The address latch uses three 74ALS573 octal D-type transparent latches (u9-u11). Using the address strobe signal MMU.ADS', the information of the multiplexed address/data bus is retained by the latches at the beginning of a bus cycle. At power-up or after a system reset, a flip-flop (u40a) with the output signal name BT.UP' is set. If BT.UP' is asserted and the CPU is accessing memory, the address information of the signal lines ad19-ad23 will not be gated to the memory address bus lines A19-A23; instead, another ALS573 (u8) sets these lines to high as long as BT.UP' enables this latch. This maps address locations 000000-07FFFF (hex) to F80000-FFFFFF (hex) where the boot ROM and IO devices are located. Note that the processor starts program execution with a PC value zero after reset. The boot flip-flop is reset irreversibly under software control.

The following control signals are provided: ILO', AV', R/W', and BEO'-BE3'. ILO' is a buffered version of the corresponding CPU signal CPU.ILO' (u7), which indicates that an interlocked instruction is being executed. It is made available to external bus arbitration circuitry in order to implement the semaphore primitive operations for resource sharing. This signal is, however, not used in the present circuits. AV' marks a valid address on lines A0-A23 and is

activated when a processor request has been granted (u34b, u7). R/W' indicates the direction of the data transfer as seen from the processor (u38c, u7). BE0'-BE3' facilitate individual byte accessing on the 32-bit data bus. Any data item, regardless of size, may be placed starting at any memory address; therefore, the 24-bit address A0-A23 is a byte address. While the data bus always transfers double-word data, the memory uses BE0'-BE3' to select the appropriate bytes. A PAL16L8A device (u21) contains the necessary logic to generate the byte enable signals. During a memory write cycle, these signals are defined by either the CPU (CPU.BE0'-CPU.BE3') or the MMU (A1). A CPU memory access can contain one, two, three, or four bytes, while the MMU always accesses words. An MMU memory cycle can be identified if MMU.MAC' is low. During a memory read cycle, BE0'-BE3' are all active. This precaution must be taken to prevent floating data buffer inputs caused by non-selected memory devices.

The cycle request circuitry consists of a 74AS74 flip-flop (u22a). It is set by the address strobe signal MMU.ADS', which signals that the processor is starting a bus cycle. A CPU memory cycle request (signalled by a low CPU.REQ' signal) is acknowledged by the bus arbiter with an active CPU.GNT' signal. CPU.GNT' is used as an output enable of the buffers and latches of the memory bus interface. The RDY signal is used to extend the current processor bus cycle. This is necessary if the CPU bus cycle request cannot be acknowledged immediately (u39b) or in case of a slow access (u34a).

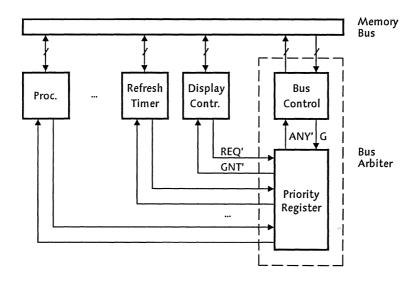

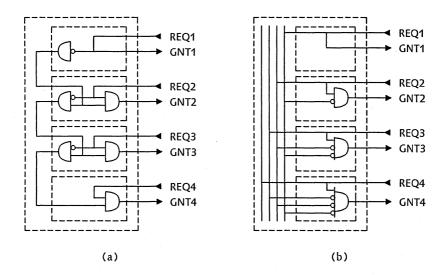

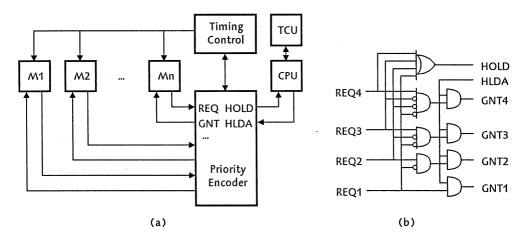

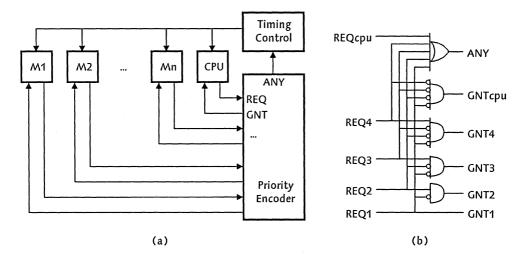

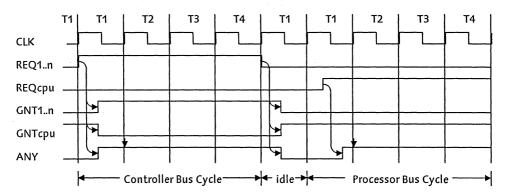

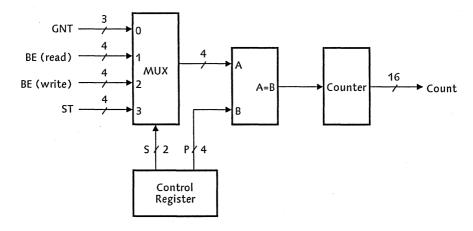

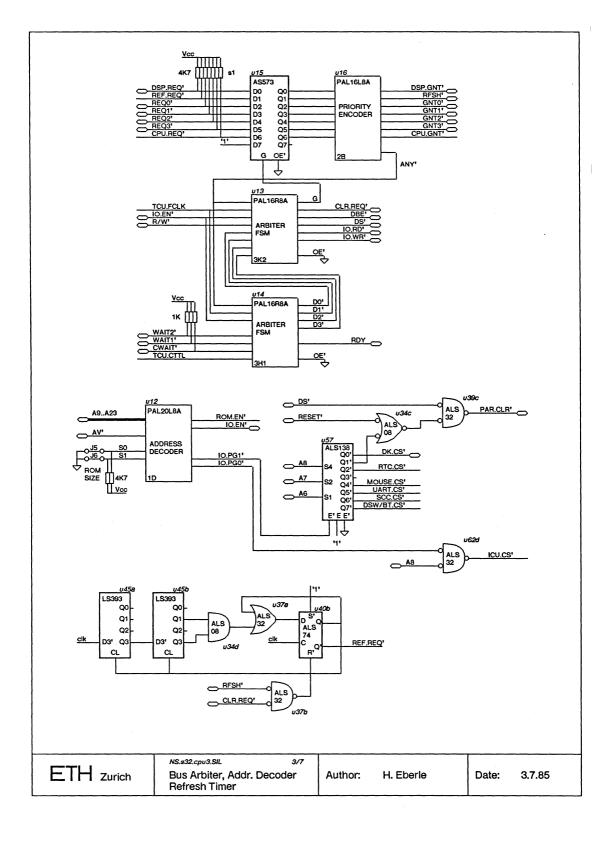

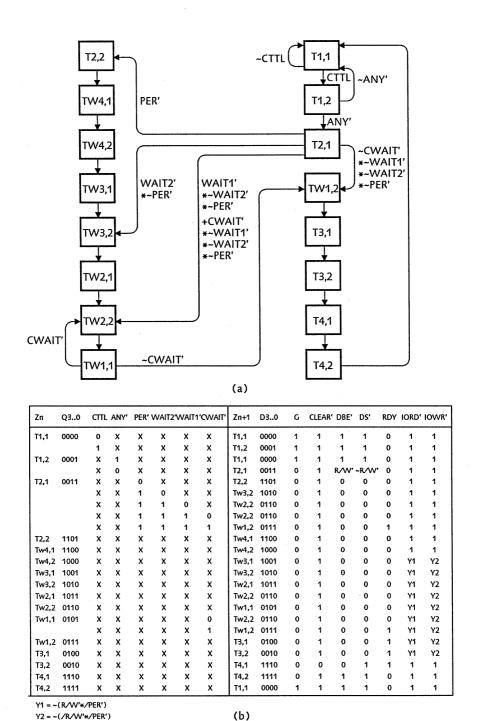

# Memory Bus Arbiter

Processor, display controller, and DRAM refresh timer share access to the main memory and the memory bus. The device that controls the bus is known as the bus master. The transfer of bus control from one device to another is defined by a set of bus request and bus grant signals. The circuit is outlined in Figure 2.4. The arbiter consists of a *priority register* and a *bus control* unit that controls the timing of a memory cycle. The priority register is made up of a PAL16L8A (u16) and a 74AS573 octal D-type transparent latch (u15). The bus control signals are generated by a finite state machine (FSM) built from two PAL16R8As (u13, u14). A detailed description of the bus control FSM including a state diagram is contained in Appendix B. Note that the state machine is clocked by the fast clock (f = 20 MHz) in order to achieve higher granularity.

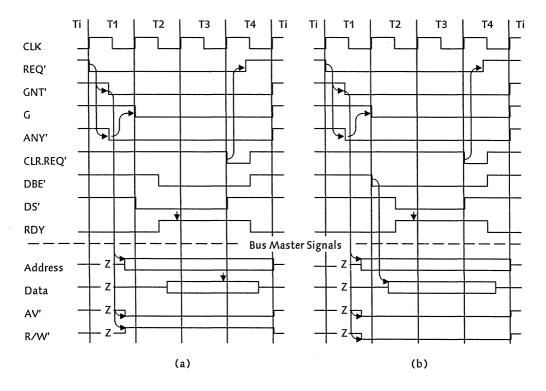

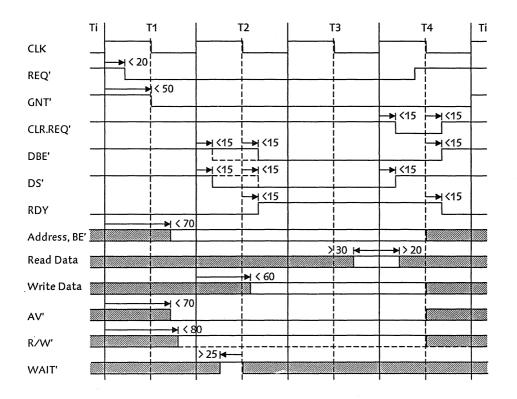

The sequence of events during a read and a write memory cycle is shown in Figure 2.5. A full speed memory cycle is performed in four cycles of the processor clock CLK, labeled T1 through T4. Clock cycles not associated with a memory cycle are designated Ti (for "idle"). In order to acquire control of the bus, the device asserts its bus request signal that is fed into the priority register. The highest-order signal applied at a request input is transferred to the appropriate grant output. If any request has been submitted to the priority register, ANY' becomes low, thereby informing the bus control FSM that a memory cycle has to be started. The FSM responds with a low G signal causing the state of the request lines to be latched by the priority register. At the end of a memory cycle, the signal CLR.REQ' clears the processed request. The following bus master devices are provided (listed in descending priority):

DSP.REQ' DSP.GNT' Display refresh controller REF.REQ' REF.GNT' DRAM refresh timer REQ0' GNTO' not used

Figure 2.4 Memory bus arbiter.

| REQ1'    | GNT1'    | not used  |

|----------|----------|-----------|

| REQ2'    | GNT2'    | not used  |

| REQ3'    | GNT3'    | not used  |

| CPU.REO' | CPU.GNT' | Processor |

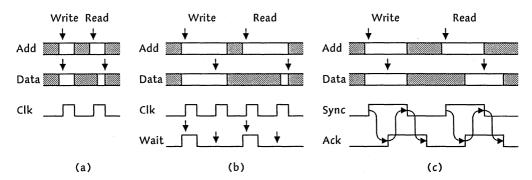

The bus control FSM provides further control signals that are specifically introduced to suit the NS32000 processor chips, but are general enough to serve other master devices as well. The data buffer enable signal DBE' is used to control the data bus buffers. The leading edge of DBE' is delayed a half clock period during read cycles to avoid bus conflicts between data buffers and either the CPU or the MMU. As the multiplexed slave processor bus holds the address until shortly after the end of T1, conflicts occur if data buffers are opened too early. DBE' goes inactive in the middle of T4, having provided the necessary data hold times. If the processor is performing a read cycle, the data bus is sampled at the end of T3. The data strobe DS' signals the beginning of a data transfer. This signal is used by the control circuitry for the dynamic RAMs. The leading edge of DS' is delayed a half clock period during write cycles to guarantee the appropriate data setup time for the DRAMs. DS' returns to the high level at the beginning of T4. During a write cycle, the processor presents data from the beginning of T2 to the end of T4.

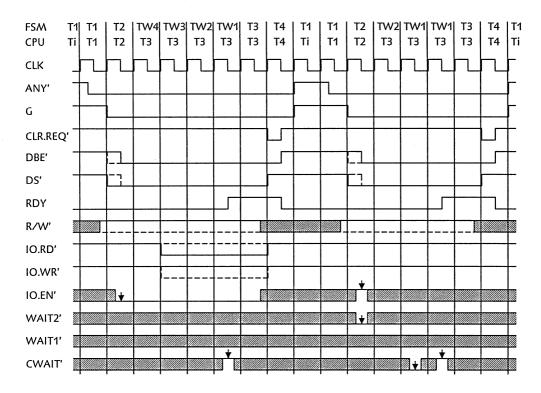

To allow sufficient strobe widths and access times for any speed of memory or peripheral device, the bus control FSM provides cycle extension. As explained in Section 4.3.2 the arbitrated memory bus does not allow the use of the cycle extension capabilities of the TCU. The FSM uses the following wait input signals (listed in descending priority):

- a low IO.EN' during T2 causes the FSM to perform a so-called peripheral cycle, which is characterized by four added wait states (TW4, TW3, TW2, TW1). In addition, a read or write strobe signal (IO.RD', IO.WR') is generated which meets the setup and hold timing requirements of slower peripherals. IO.RD' and IO.WR' are decoded from R/W'

- if WAIT2' is sampled low during T2, two wait states (TW2, TW1) are inserted

Figure 2.5 Read (a) and write cycle timing (b).

- if WAIT1' is sampled low during T2, one wait state (TW1) is inserted

- CWAIT' initiates a continuous wait. As long as sampled low during T2 and TW1, one wait state (TW1) is inserted

Examples of cycle extension are shown in Figure 2.6. The processor is informed of an extended bus cycle by means of the RDY signal. At the end of T2, the RDY signal is sampled by the CPU or MMU. If RDY is high, the next T-states will be T3 and then T4 ending the bus cycle. If RDY is low, then another T3 state will be inserted after the next T-state, and the RDY line will again be sampled during the next T-state.

Although the processor has the lowest-order priority and thereby looses competition with any other bus masters, it is treated in a privileged way. Whenever no other master requests the bus, the processor is given control over the memory bus by default; as a result, there is no arbitration delay in case of a memory access by the processor.

The introduction of the address valid signal AV' is necessary for the following reasons. Since the processor also controls the memory bus during idle times, AV' is used to indicate a valid memory address during a memory bus cycle. Furthermore, bus masters such as the refresh timer for the DRAMs request so-called "dummy" bus cycles in order to prevent other devices from simultaneously accessing the memory bus. AV' is then set to inactive, hindering any bus slave in decoding the address.

The mentioned DRAM refresh timer is placed on the processor board. It is assumed that a central timer is responsible for refreshing all dynamic memory devices. The refresh timer

Figure 2.6 Cycle extension.

consists of a 74LS393 dual 4-bit counter (u45) which divides the system clock CLK by 160. The refresh request line REF.REQ' is, therefore, asserted every 16  $\mu$ s. A memory refresh cycle is indicated by a low RFSH' signal.

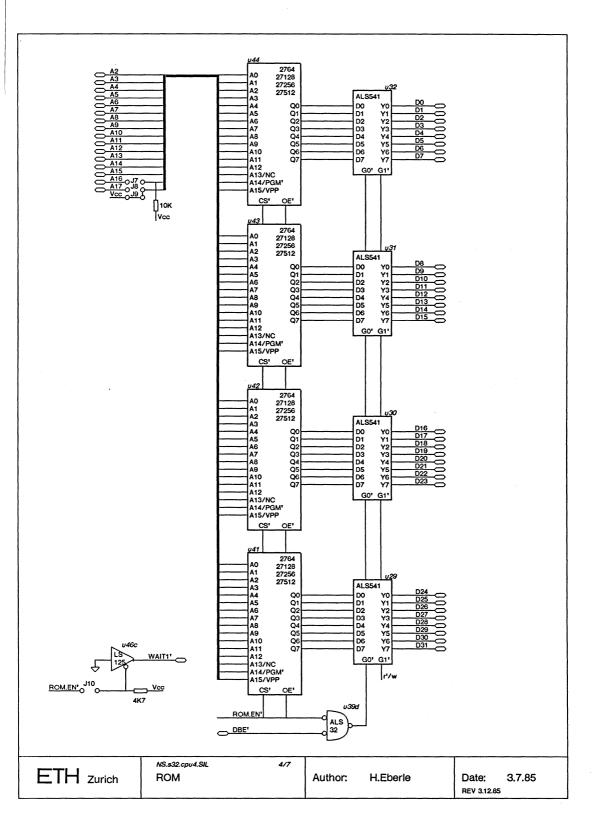

# Boot ROM and Standard Input/Output Devices

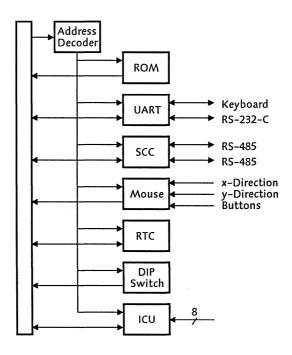

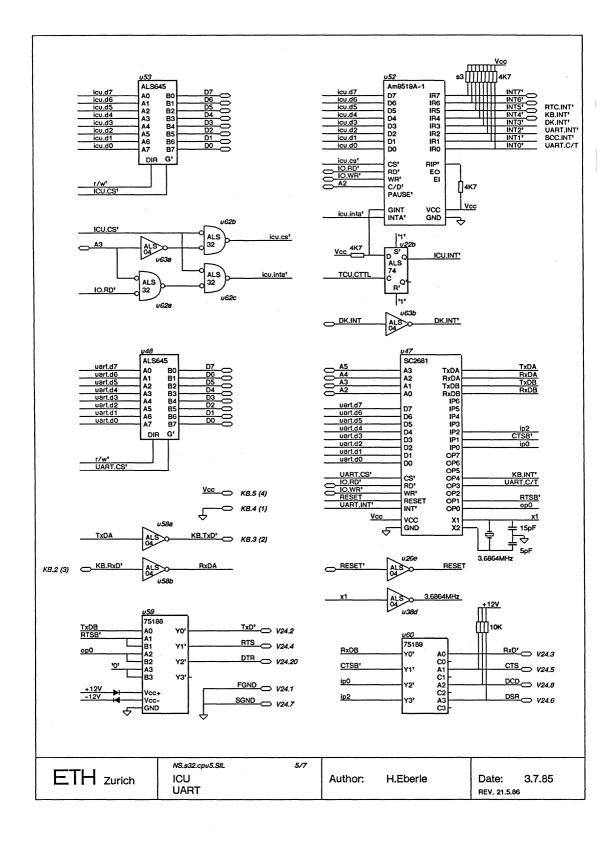

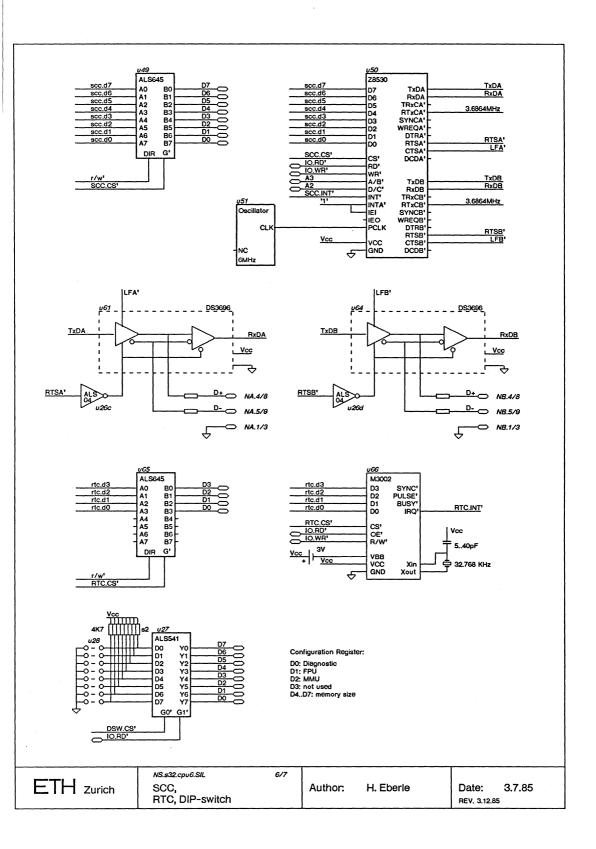

The boot ROM and several standard IO devices are also on the processor board. Part of the address space is assigned to IO ports. This strategy is called memory-mapped IO with devices residing in the reserved IO address space loosely called IO devices. An address decoder provides the appropriate select signals. As can be seen in Figure 2.7, the IO devices include:

- a dual universal asynchronous receiver/transmitter (UART) that interfaces the serial keyboard and offers an additional RS-232-C serial port

- a dual-channel serial communications controller (SCC) providing two RS-485 serial interfaces

- a mouse interface

- a battery-backed real time clock (RTC)

- a DIP-switch holding system parameters

- an interrupt control unit (ICU) supporting up to eight interrupt sources

The width of the 32-bit data bus is not fully used by the peripheral devices. Their data paths are 4-, 8-, or 16-bit wide. The data bus interfaces are aligned with the 32-bit data bus using

Figure 2.7 Boot ROM and standard IO devices.

the lower-order data bits. An 8-bit peripheral unit, for example, is connected with data bits D0-D7. All IO devices are accessed with addresses modulo 4 equal 0, i.e. device register addresses are double-word addresses and address bits A0 and A1 are ignored.

A PAL20L8A (u12) and a 74ALS138 3- to 8-line decoder (u57) implement the address decoder. The PAL device provides the ROM and IO device enable signals ROM.EN' and IO.EN'. The reserved memory locations for ROM and IO devices are shown in Figure 2.8. To simplify future IO expansions, IO.EN' is also available on the memory bus. This signal further causes the arbiter to perform an extended, peripheral cycle. For the two uppermost 512-byte-sized IO pages, additional select signals are generated (IO.PGO', IO.PG1'). The ICU resides in the uppermost IO page (IO.PGO'). This is required by the fact that the CPU reads the interrupt vector from the fixed address FFFE00 (hex) [NS 86a]. The ICU chip select signal (ICU.CS') must not be activated when the CPU reads a dummy byte from address FFFF00 (hex) during a nonmaskable interrupt sequence; therefore, ICU.CS' is disabled if A8 is high (u62d). The next lower IO page (IO.PG1') is reserved for the other standard IO devices. A 74ALS138 (u57) provides eight select signals each having an address range of 64 bytes.

The boot ROM is made up of four EPROM devices (u41-u44). The corresponding sockets can be configured for different ROM types (2764, 27128, 27256, 27512) with a range in total memory capacity from 32K bytes to 256K bytes. 150 ns parts are required in order to avoid wait states. The ROM data outputs are connected to the memory data bus with four 74ALS541 octal unidirectional buffers (u29-u32). The ROM address inputs are connected to the address lines A2-A17 (double-word address).

Figure 2.8 Memory map.

SC2681 (u47) provides two independent, full-duplex, UART asynchronous receiver/transmitter channels with software selectable baud rates up to 38'400 bits per second [Philips 83]. One channel is used for the keyboard. The receive and transmit data signals of the keyboard interface (KB.TxD', KB.RxD') are TTL compatible; the other channel implements an RS-232-C interface. A standard RS-232-C line driver (75188, u59) and a line receiver (75189, u60) [TI 77] are used to provide the data transmission and the most common modem control signals: TxData, RxData, Request to Send, Data Terminal Ready, Clear to Send, Data Carrier Detected, and Data Set Ready. Also provided on the UART chip is a programmable 16-bit counter/timer. Individual interrupt signals are output by the UART for the keyboard interface (KB.INT'), the RS-232-C interface (UART.INT'), and the counter/timer (UART.C/T). The crystal oscillator of the UART requires an external 3.6864 MHz crystal. A buffered version of this clock signal is also used by the SCC.

The Z8530 SCC (u50) is a dual-channel, multiprotocol data communication peripheral [Zilog 82a, Zilog 82b, Zilog 85]. The SCC can handle asynchronous and synchronous formats including SDLC. In the latter case, data rates up to 230.4 Kbits per second are possible. Each of both channels constitutes an RS-485 serial line interface using DS3696 high-speed differential tristate line transceivers (u61, u64) [NS 83]. The SCC's "request to send" output (RTSA', RTSB') defines the data transmission direction. The "clear to send" input (CTSA', CTSB') is used to detect a line fault condition (LFA', LFB'), which is reported by the transceiver in case of bus contention or fault situations that cause excessive power dissipation within the device. The SCC requires an external 6 MHz clock oscillator (u51). The 3.6864 MHz clocking signals for the receiver/transmitter channels are derived from the UART's oscillator circuit.

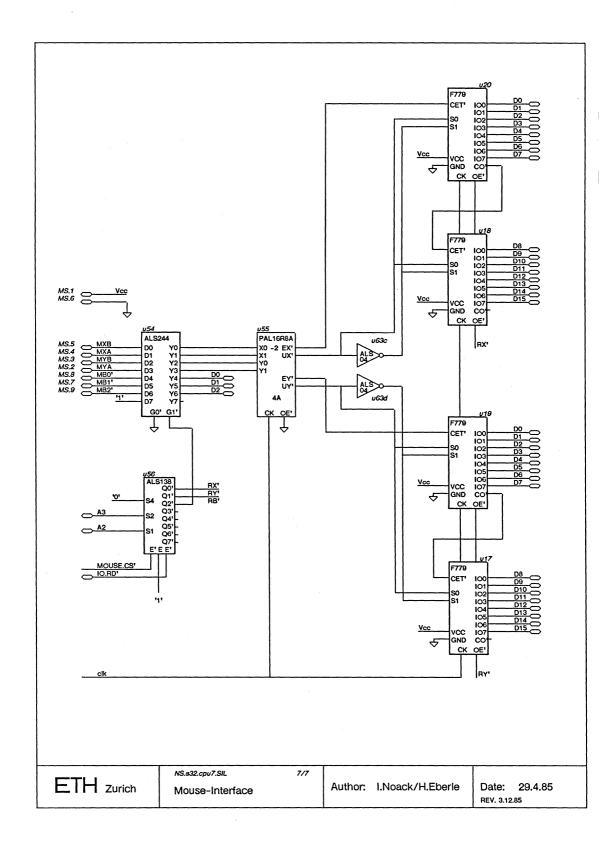

The mouse interface keeps track of the relative mouse position and holds the state of the three mouse buttons. A direction discriminator controls the up/down counter for the x- and y-directions. The three switches can be directly read on a parallel port and polled by software. The mouse interface is composed of the following components. A 74ALS138 3- to 8-line decoder (u56) provides select signals for the x-register (RX'), y-register (RY'), and button state register (RB'). All registers are read-only. The state of the mouse buttons (MB0', MB1', MB2') is isolated from the data bus (D0-D2) by a 74ALS244 octal buffer (u54), which is enabled by RB'. For each direction the mouse generates two phase-shifted signals (MXA, MXB and MYA, MYB). This information is evaluated by the direction discriminator which is realized with a PAL16R8A (u55). This device generates the necessary control signals for the x- and y-counters. Each counter is made up of two cascaded 74F779 8-bit counter chips (u17-u20) [Philips 84]. A built-in tristate IO port reduces the part count of the data bus interface.

The M3002 RTC chip (u66) contains a time of day clock and a calendar [MEM 84]. The register address and data are multiplexed over four data lines; therefore, no separate address lines are needed. External components include a 32.768 KHz crystal for the on-chip oscillator and a battery back-up to keep time and date when no external power is supplied. Because of the low power consumption of this device, the lithium cell provided has a lifetime of more than 10 years.

The *DIP-switch* (u27, u28) holds 8 bits of information (read-only). The off-position corresponds to a logic 1. The switches can be used to set the processor configuration, the size of installed memory, or a machine number in a network.

The Am9519A-1 *ICU* (u52) accepts up to eight maskable interrupt request inputs, resolves priorities, and supplies programmable response bytes for each interrupt [AMD 80, AMD 84]. The latter feature allows the CPU to acknowledge interrupt requests in the so-called vectored mode, interpreting the ICU's response byte as a vector value. Depending on the applied address, an additional circuit (u62) distinguishes between a "normal" access to the ICU's register (icu.cs') and an interrupt acknowledge cycle (icu.inta'). The group interrupt output ICU.INT' is synchronized with the rising edge of TCU.CTTL (u22b) in order to minimize the possibility of metastable states as recommended in [NS]. The ICU inputs the following interrupt signals (listed in descending priority):

```

INTO'

counter/timer (UART.C/T)

INT1'

two RS-485 channels (SCC.INT')

INT2'

RS-232-C interface (UART.INT')

INT3'

disk controller (DK.INT')

keyboard (KB.INT')

INT4'

real time clock (RTC.INT')

INT5'

not used

INT6'

INT7'

not used

```

Interrupt lines INT4'-INT7' are available on the backplane bus. In particular, INT6' and INT7' are provided for future IO device expansion.

The address decoder further generates the signals BT.CS' and PAR.CLR'. Any write access to an IO address assigned to BT.CS' clears the boot flip-flop (u40a). The parity error flag is reset during a hardware reset (u34c) or by accessing an address assigned to PAR.CLR' (u39c).

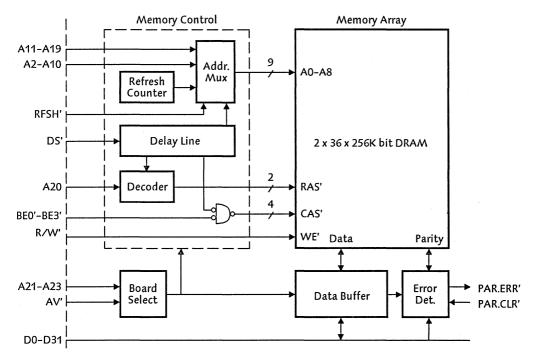

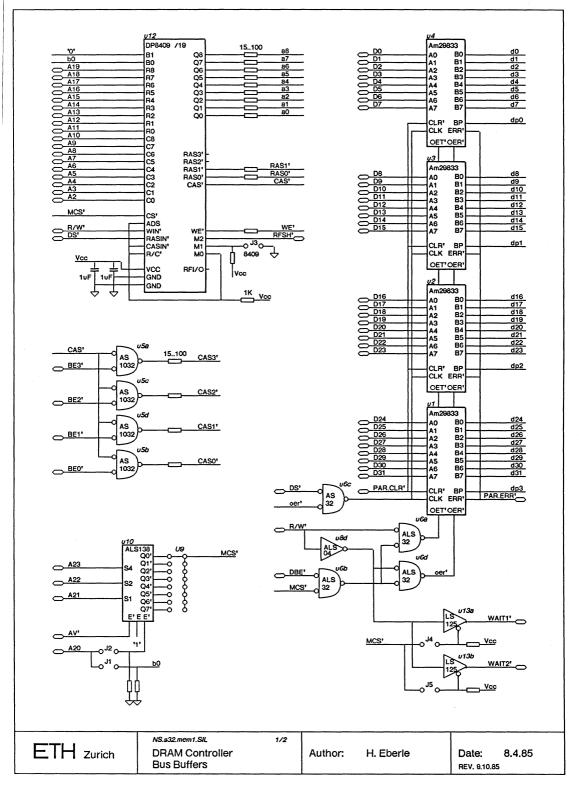

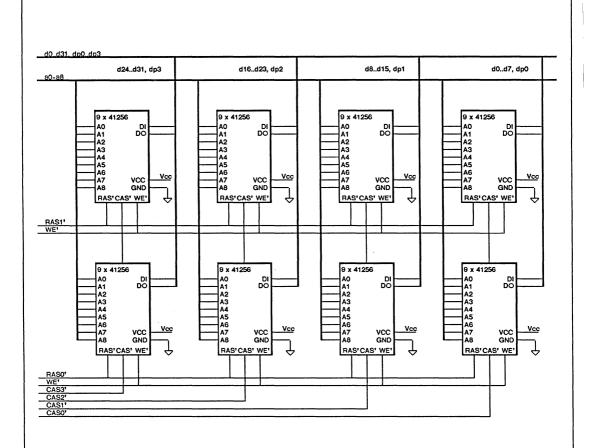

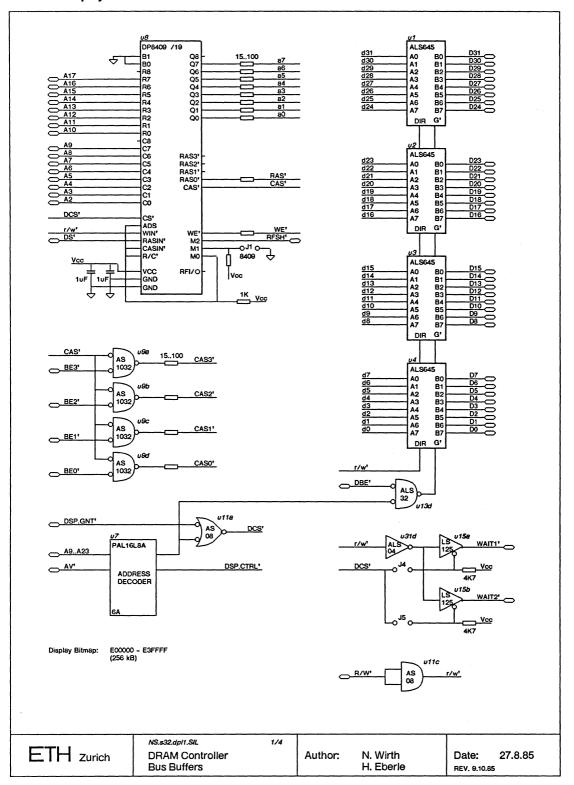

## 2.3.2 Memory Board

The Ceres memory board contains 2M bytes of dynamic memory and is occupied by 72 DRAM devices organized with a 36-bit wide data bus which allows for 32 bits of data plus byte parity. The memory is designed to accept 256K-bit 120 ns dynamic RAM chips, which operate with the processor at 10 MHz without wait states. Memory can be expanded by additional memory boards.

The organization of the memory is shown in the block diagram of Figure 2.9. In addition to the *memory array*, the following components are needed:

- the board selection logic allows the board to be activated for different address ranges

- the memory control logic takes care of the proper sequence of a memory cycle. Derived from the original address, the row and the column address together with the appropriate row and column address strobe signals are generated successively.

Further, the memory control logic is periodically forced to refresh the dynamic memory

- chips. The contents of a refresh counter are then sent as the address to the memory array the error detection unit generates parity bits (write-cycle) and checks the read

- information (read-cycle)

- the bidirectional data line buffers connect the data paths of the memory array and the memory bus

Figure 2.9 The 2M byte dynamic memory.

The *memory array* is divided into two banks each consisting of 36 DRAM devices. Address lines A2-A20 provide a double-word address. Individual byte accessing is controlled by the byte enable signals BEO'-BE3'.

The board selection logic uses a 74ALS138 3- to 8-line decoder (u10). If the signal AV indicates a valid address, the three most significant address bits A21-A23 are decoded and assign an address range of 2M bytes to each decoder output. One of these is chosen as the board select signal MCS' by closing the appropriate jumper (u9).

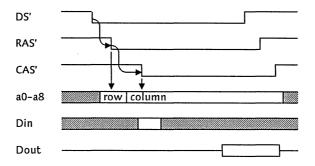

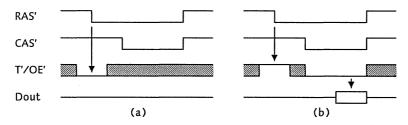

Most functions of the memory control logic are provided by the DP8419 DRAM controller (u12) [NS 86a]. The higher-order address bits A11-A19 serve as the row address and the lower-order address bits A2-A10 as the column address. These addresses are output sequentially on the address lines a0-a8 that drive the memory devices. The address strobe signals RAS' and CAS' are generated by an internal delay line induced by the signal DS'. The corresponding timing diagram is shown in Figure 2.10. Individual control lines for each memory bank (RASO', RAS1') and for each byte (CASO'-CAS3') are generated by using the signals A20 and BEO'-BE3', respectively. A20 is used as an input to the internal bank decoder of the DRAM controller. BEO'-BE3' ORed with CAS' yield CASO'-CAS3'. The write enable signal WE' is a buffered version of the bus signal R/W'. The DRAM controller uses high output current drivers for all address and control lines. External damping resistors reduce both overshoot and undershoot on these signal lines caused by the high-capacity load of the memory devices. The DRAM controller performs a "normal" memory cycle, if the CS' input driven by the MCS' line is activated and the mode input M0-M2 is set to the so-called auto access mode. This implies that the signal RFSH' must be inactive. If RFSH' is active, a refresh memory cycle takes place. The state of the address lines A2-A23 including MCS' is not relevant in this mode.

Figure 2.10 DRAM timing.

Error detection and data line buffers are made up of four Am29833 9-bit parity bus transceivers (u1-u4) [AMD 85]. The bidirectional tristate buffers need separate output enable signals for each direction. They are obtained through combination of the signals R/W', DBE', and MCS' (u6). The error detection circuit contains a parity generator and checker. The result of the parity checker is latched in an internal flip-flop which is triggered by the trailing edge of the signal DS' at the end of a read cycle (u6c). In case of a parity error, the open-collector output signal PAR.ERR' becomes active. The flip-flop can be reset by the signal PAR.CLR'. PAR.ERR' is connected with the nonmaskable interrupt signal of the CPU.

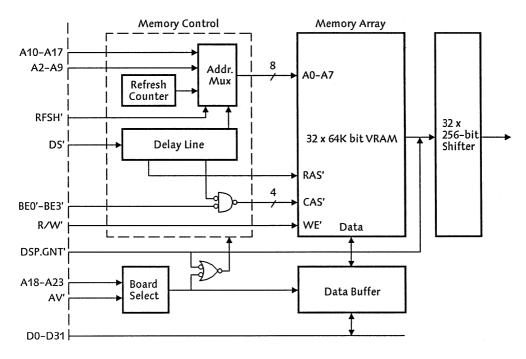

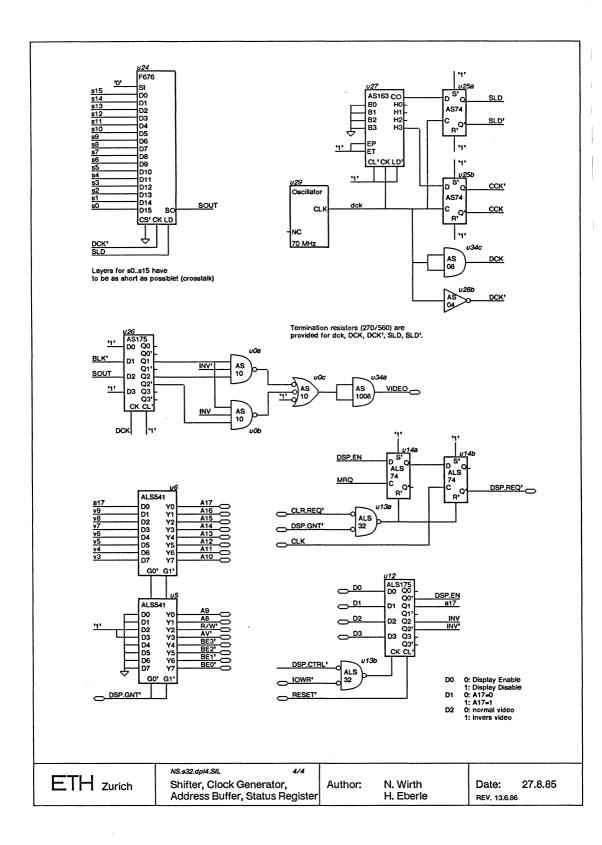

# 2.3.3 Display Controller Board

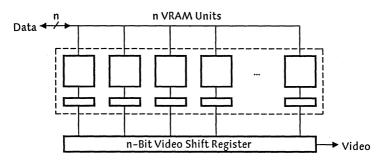

The design of the display refresh controller has mainly been influenced by the use of so-called video RAM devices (VRAM) that have been developed specifically for video applications. The multiport VRAM combines a standard 64K-bit DRAM with an on-chip 256-bit shift register and the necessary controls to transfer data between the memory array and the shift register. The two ports (that is the memory array and the shift register) can be accessed simultaneously except during a data transfer between the memory array and the register.

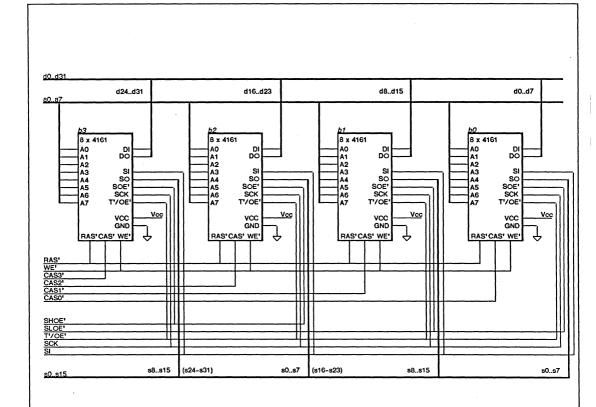

The display controller board houses 256K bytes of display memory and the display refresh controller. The display memory is made up of 32 VRAM chips organized with a 32-bit wide data bus as seen from the processor and a 8192-bit wide video data bus as seen from the display refresh controller. 64K-bit 150 ns VRAM chips [TI 83b] are used which are accessed with one additional wait state. The display memory accommodates two bitmaps that can be displayed alternatively.

# Display Memory

The organization of the display memory is shown in Figure 2.11 and is very similar to the one of the memory board with the exception of the error detection circuit which has been omitted. The following explanation of the implementation, therefore, concentrates on the differences.

Figure 2.11 The display memory.

The memory array contains one bank only. The board selection logic is done through a PAL16L8A device (u7). Using address bits A18-A23 the decoder assigns the address range at E00000-E3FFFF (hex) to the display memory. When the display refresh controller accesses the display memory (DSP.GNT'=0) the address decoder is omitted (u11a). As no data are transferred on the memory bus in this case, the data line buffers are not enabled. The memory control logic is again realized with a DP8419 DRAM controller (u8). Because of the smaller address range, fewer address lines are needed (A2-A17). The data line buffers are made up of four 74ALS645 8-bit bus transceivers (u1-u4).

# Display Refresh Controller

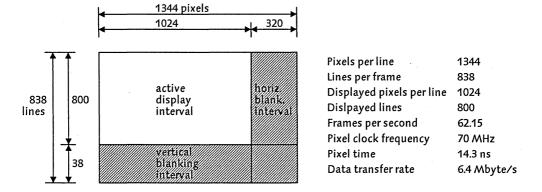

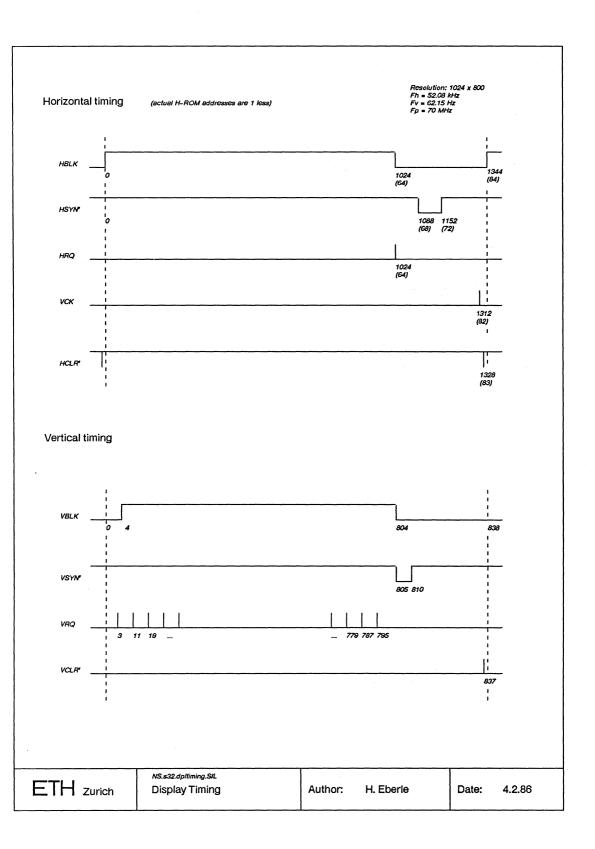

In order to better understand the display refresh controller, the display parameters of the high-resolution CRT-monitor are explained first. As can be seen in Figure 2.12, the total frame time consists of the active display interval, the horizontal blanking interval (horizontal retrace), and the vertical blanking interval (vertical retrace). The pixel clock frequency is the product of pixels per line, lines per frame, and frames per second:

$$f(pixel) = 1344 \cdot 838 \cdot 62.15 \text{ s}^{-1} = 70 \text{ MHz}$$

Figure 2.12 The display parameters of the high-resolution CRT-monitor.

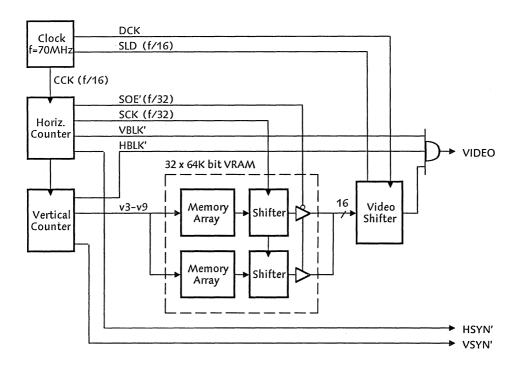

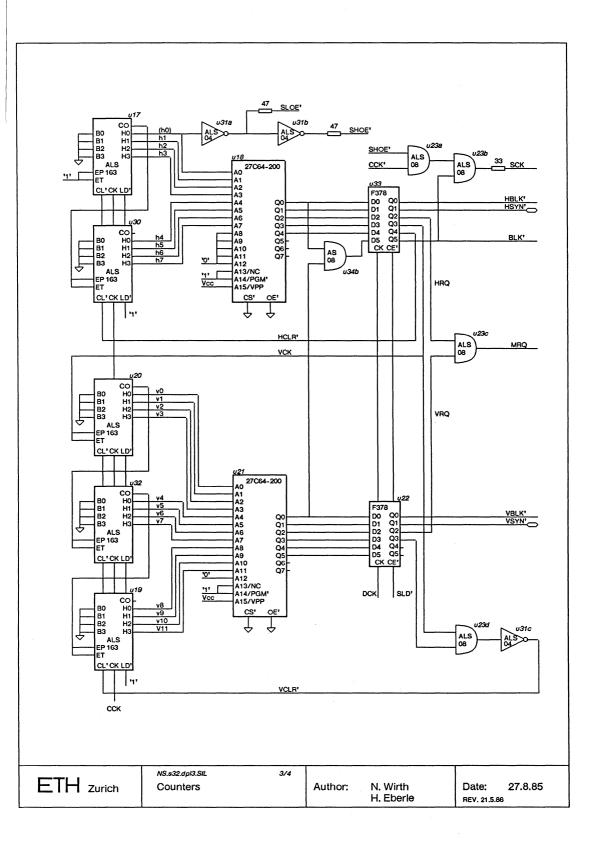

The structure of the *display refresh controller* is shown in a further block diagram (Figure 2.13). The following blocks can be distinguished:

- the *clock generator* circuitry provides the clock signals for the video shifter and the horizontal and vertical counters

- the horizontal and vertical counters keep track of the position of the displayed picture element (or pixel). Derived from the state of the counters, control signals such as the ones for the synchronization of the display monitor are generated; furthermore, the counters determine the memory array address of those display lines which have to be refreshed next

- the *display memory*, which is arranged as a three-dimensional array of 32 memory devices each being organized as 256 words of 256 bits

- the *video shift register* transforms the data which are transmitted by the VRAMs as 32-bit entities into the bit-serial video data signal

Figure 2.13 The display refresh controller.

Not shown in the block diagram is the *display control register* and the *memory cycle request* circuitry needed to gain access to the "video port".

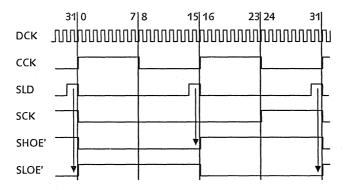

The clock generator circuitry uses a hybrid 70 MHz oscillator chip (u29). Its output provides the pixel or dot clock DCK. A 74AS163 4-bit counter (u27) acts as a divider of the dot clock frequency. It produces the clock signal CCK for the horizontal counter and the load signal SLD for the video shift register. The timing relationship of these signals is shown in Figure 2.14.

Figure 2.14 Clocking signals of the display refresh controller.

The horizontal and vertical counters are made up of two, respectively three 74ALS163 4-bit counters (u17, u19, u20, u30, u32), a 27C64 EPROM each (u18, u21), and a 74F378 6-bit

latch each (u22, u33). Horizontally, the counter represents the pixel position divided by 16, while the vertical counter state corresponds to the line position. The two EPROMs generate the waveforms of the horizontal and vertical control signals based on the counters state (Appendix A.3). The following signals are provided:

- HBLK' and VBLK' deactivate the video outputs during the horizontal and vertical blanking intervals

- HSYN' and VSYN' are responsible for the line and frame synchronization of the video beam

- HRQ and VRQ cause the VRAM shift register to be reloaded with a new bitmap block every 8 display lines, thus allowing the counter output signals v3-v9 to be used as the bitmap block address

- VCK is the clock signal of the vertical counter

- HCLR' and VCLR' initialize the horizontal and vertical counters to the zero state at the end of a line or a frame, respectively

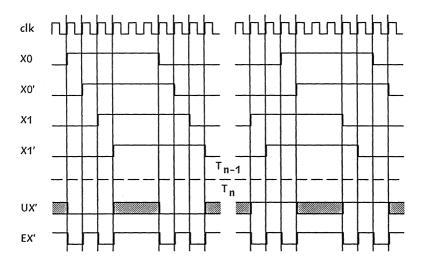

The horizontal counter also controls the clock signal SCK and the output enable signals SLOE' and SHOE' of the VRAM shift registers. The timing relationship can be seen in Figure 2.14. The 16-bit video shift register is loaded, alternating with the lower and the higher 16 bits of the VRAM shift register data outputs.

The video shift register is realized with a 74F676 16-bit shift register (u24) [Philips 84]. Its output, the serialized video data SOUT, and the blanking signal BLK', first have to be synchronized with the dot clock DCK by a 74AS175 quad D-flip-flop (u26), before SOUT can be masked by BLK' (u0). The display control register provides the signal INV which, when set to 1, inverts the video data signal (u0).

In order to access the display memory, the display refresh controller periodically requests a memory cycle from the bus arbiter. The *memory cycle request* flip-flop (u14) asserts the DSP.REQ' line when the horizontal and vertical counters activate MRQ (MRQ = VRQ AND HRQ, u23c) and the display control register bit DSP.EN is set to 1. Another flip-flop is needed to synchronize the request signal with the system clock CLK. A granted memory cycle is indicated by an active DSP.GNT' signal. At the end of a memory cycle, the signal CLR.REQ' clears the request.

DSP.GNT' serves as the output enable of two 74ALS541 octal buffers (u5, u6) that gate the address and control signals to the memory bus. The address is made up of the vertical counter outputs v3-v9 and the display control register output a17. Signals v3-v9 define the display line that has to be scanned next; a17 determines in which half of the display memory the displayed bitmap is located. This address information is directed to the address lines A10-A17 which define the memory row of each VRAM that is to be loaded into the internal shift register. If the two address bits A8 and A9 equal 00 during this register transfer cycle, a total of 256 bits can be subsequently read out (it is possible to transfer 64, 128, 192, or 256 bits of a memory row into the shift register). All other address bits are neglected (A0-A7, A18-A23). As address decoding now has to be inhibited (AV'=1), the display memory also has to be selected (DCS') when DSP.GNT' is active (u11a).

The signal T'/OE', which is input to the VRAMs, has two functions that are shown in Figure 2.15. First, it selects either shift register transfer or random-access operation when RAS' falls; therefore, during a memory access of the display refresh controller, T'/OE' equals DSP.GNT', which is already low as RAS' falls. Second, if a random-access operation is performed, it functions as an output enable after CAS' falls. For this reason, it can then be identical to CAS' (u11b).

Figure 2.15 VRAM shift register transfer (a) and random access operation (b).

The display control register is implemented with a 74ALS175 quad D-flip-flop (u12). The flip-flops are reset by a RESET' pulse. The address decoding is performed by half a PAL16L8A (u7). The register is located at FFFA00 (hex). The meaning of the three write-only bits is as follows:

- Bit 0 0 Display Enable (initialized value)

- 1 Display Disable

- Bit 1 0 A17=0 (initialized value)

- 1 A17=1

- Bit 2 0 Normal Video (initialized value)

- 1 Inverse Video

DSP.EN set to 0 (bit 0 of the control register) prevents any display requests. Nevertheless, the display is refreshed with the contents of the VRAM shifters which will no longer be loaded. The shifter input signal SI now defines the video data signal. In order to guarantee a blank screen, SI is connected to INV (bit 2 of the control register). In the inverse mode SI is set to 1 in order to get an inverted video data signal of 0.

The design of a display refresh controller with a pixel frequency of 70 MHz requires special care. At a clock period of 14.3 ns, gate delays of 5 ns are of considerable significance. The following provisions have been made:

- all registers generating critical signals are clocked by the same clock signal (u22, u33, u24, u26)

- synchronizers adjust different signal delays (u25, u26)

- all paths in a combinatorial circuit are of the same length (u0)

# 2.3.4 Disk Controller Board

The Western Digital WD1002-05 disk controller board [WD 83] contains a Winchester interface (Seagate ST506 compatible) and a floppy interface (Shugart SA450 compatible). The controller holds all of the logic required for a variable sector length (up to 1K bytes),

ECC correction, data separation, and host interface circuitry. The latter consists mainly of an 8-bit bidirectional parallel bus and appropriate control signals. Programmed IO is used to transfer sector data to and from an on-board sector buffer. Except for the board select signal DK.CS' and the interrupt request signal DK.INT, all signals of the host interface are "standard" memory bus signals. Additional circuitry for the signals DK.CS' (u57) and DK.INT (u63b) resides on the processor board.

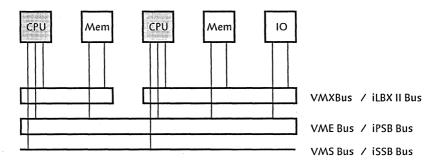

#### 2.3.5 Motherboard

Physical extensibility is obtained by placing the circuitry on several boards that are connected by a backplane (motherboard). The Ceres motherboard offers slots for six boards connected with a common, parallel backplane bus. Three slots are occupied by the already explained standard boards. Packaging flexibility is provided by requiring that the physical card position on the motherboard has no effect on the functioning of the system. This is accomplished by avoiding the use of daisy chain signals, which would require that there be no empty slots between boards and by having all signals independent of the backplane position. To avoid floating values, pullup resistors are provided for the address and data signals. The backplane bus contains the following lines:

Address A0-A23 Data D0-D31

Control

Data Transfer AV', BEO'-BE3', DS', DBE', R/W'

Bus Arbitration REQ0'-REQ3', GNT0'-GNT3', DSP.REQ', DSP.GNT', CLR.REQ'

Cycle Extension CWAIT', WAIT1', WAIT2'

IO Devices IO.EN', IO.RD', IO.WR', DK.CS', DK.INT

Interrupts INT4'-INT7'

Clock CLK, FCLK

Miscellaneous RESET', RESET.IN', RDY, ILO', PAR.ERR', PAR.CLR', RFSH'

#### 2.4 Hardware Extensions

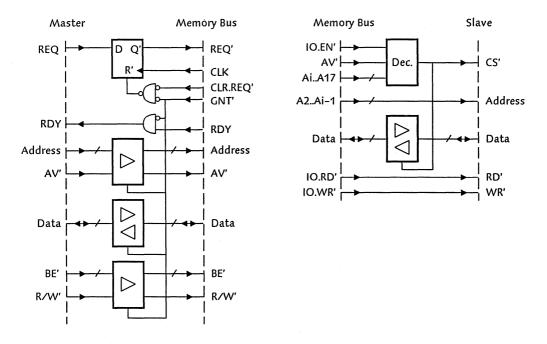

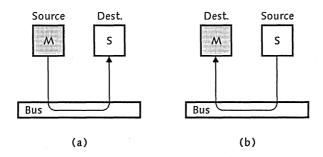

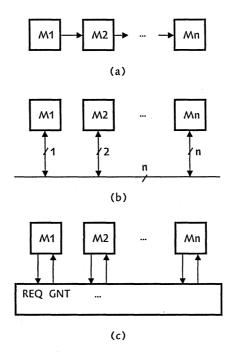

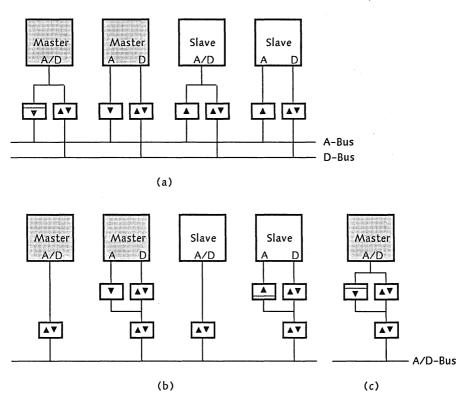

The modular, extensible multiboard arrangement invites not only the addition of more memory but, in particular, hardware which extends the versatility of the Ceres computer. The memory bus provides all necessary signals to either add new bus master or bus slave devices. In Figure 2.16, bus interfaces for both types are proposed. Note that the slave must be "synchronous" in the sense that it is always available and does not provide a completion signal.

The timing specification of a basic memory cycle is presented in Figure 2.17. Based on a processor clock period of 100 ns, the unit of value is the nanosecond. For a peripheral cycle, four wait states are inserted between T2 and T3.

Figure 2.16 Interfaces for a bus master and a bus slave.

Figure 2.17 Timing specifications of a basic memory cycle.

# 3 Raster Graphics Interface Design

#### 3.1 Introduction

In early computers, limited storage capacity led to a display output of little flexibility. A dense encoding of display information allowed a restricted set of symbols mostly consisting of alphanumeric characters. Progress in technology has removed these restrictions: cheap and large semiconductor memories can be used to store high-resolution display images in an unencoded form, thus providing maximum flexibility. As a consequence, large amounts of memory data have to be accessed in order to create the image and to refresh the display monitor. While the concern of earlier designs was to reduce the required storage capacity, recent designs are concerned with how to provide enough processing performance to manipulate and refresh video data.

As technological constraints of storage and processing performance become less severe and various VLSI-solutions for graphics applications are offered, the designer of a raster graphics system has to give thought to what the software designer really needs and to concentrate on clean and clear concepts. Hardware and software have to be designed as an entity in order to complement each other.

The graphics system of Ceres is a typical example of a simple and straightforward design. In contrast to many other workstations, the graphics functions of Ceres are completely software-based, i.e. no hardware assistance for image manipulations is provided. A detailed description of the display controller board is contained in Section 2.3.3. This chapter adds some design considerations that are in particular applicable to raster graphics with mostly stationary objects as found in document processing, for instance. The design of the raster graphics interface for Ceres is aimed at using only available integrated circuits and at economizing on the hardware expense.

The first part of this chapter outlines raster graphics principles and shows some possible realizations. The explanations are made with respect to the design of the raster graphics interface for Ceres which is discussed in the second part.

# 3.2 Raster Graphics Principles

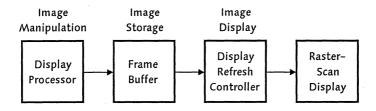

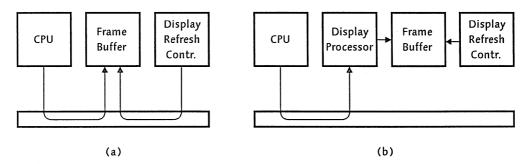

A typical raster graphics system has the organization of the block diagram in Figure 3.1. The image is stored in a memory, called the *frame buffer*, as a matrix of intensity values, known as the *pixmap*, where each unit of storage corresponds to a picture element, or a *pixel*. In the simplest case of a monochrome image each pixel can be represented by a single bit: the pixmap is then called *bitmap*. Multiple bits per pixel are required to display greyscale or colour images. The subsequent discussion concentrates on monochrome raster graphics only. The frame buffer is accessed by the *display processor* in order to manipulate the image data, and by the *display refresh controller* in order to route the image data to the *raster-scan display*. Raster scanning implies that the image is scanned onto the display screen surface in a raster sequence as a fixed succession of scan lines, made up of pixels.

Figure 3.1 Structure of a raster graphics system.

Significant architectural characteristics of a display system are:

- the *update performance*, i.e. the time required to generate a new image in response to a user request, and

- the *refresh performance* that determines the resolution and stability of the displayed image.

Both the update and refresh process compete for the frame buffer as a shared resource. Because the implementation of the frame buffer normally does not allow for simultaneous access, the display processor and the display refresh controller compete for a finite number of available memory cycles. Since the display refresh controller has to supply the video data to the raster display according to strict timing requirements, it always goes ahead of the display processor, which has to put up with the remaining memory cycles. Note that the bandwidth requirements of the display refresh controller can be precisely quantified, while the bandwidth requirements of the display processor vary significantly with each application.

As cheaper and larger semiconductor memories have become available, higher resolution bitmaps can be stored. However, the display processor and the display refresh controller have to access the frame buffer more frequently, making the contention problem even worse. The main concerns of designing a raster graphics system are to increase the bandwidth of the port to the shared frame buffer, to speed up the operations for manipulating bitmap data, and to reduce memory access conflicts caused by the display refresh controller.

#### 3.2.1 Image Storage

The development of image storage technology can best be illustrated by studying representative workstations such as the Alto, Lilith, and Ceres.

The Xerox Alto was one of the first personal computers that incorporated a raster graphics display [Thacker 79]. The  $608 \times 808$  bitmap is displayed with a refresh rate of 30 frames/s. The bandwidth required by the serial video data comes to 20 MHz. The frame buffer is single-ported and can reside anywhere in memory. The unique aspect is that the display refresh action is programmed in microcode and executed by the CPU. During the active line interval the CPU fetches double-words in  $1.05~\mu s$ , and the 32 bits are displayed in  $1.6~\mu s$ . A full screen bitmap occupies about half of the main memory of 128K bytes and displaying it consumes about 48.36% of all available memory cycles. In the lack of a large memory the displayed bitmap is pieced together by a list of smaller bitmaps, so that white spaces do not consume any memory space.

Raster graphics technology was further refined for the design of the Lilith computer [Ohran 84, Wirth 81b]. The bitmap has an increased resolution of 704 x 928 pixels, displayed with a refresh rate of 30 frames/s resulting in a video data bandwidth of 27 MHz. In contrast to the Alto, the display refresh of Lilith is performed by a separate hardware unit. A quad-word is fetched in 0.375  $\mu$ s, and the 64 bits are displayed in 2.0  $\mu$ s. The displayed bitmap occupies a fourth of the main memory of 256K bytes and refreshing the display consumes 11.48% of all memory cycles.

The raster graphics interface for the Ceres computer has been developed even further. The 1024 x 800 bitmap is now refreshed at a rate of 62.15 frames/s. The video data bandwidth reaches 70 MHz. The display refresh controller accesses 8192 bits in 0.400  $\mu$ s, and these are displayed in 154  $\mu$ s. If the display refresh controller could only access 32 bits in 0.400  $\mu$ s, then all memory cycles would be absorbed because the 32 bits would be displayed in 0.457  $\mu$ s only. The displayed bitmap occupies about a twentieth of the main memory of 2M bytes and refreshing the display consumes as little as 0.25% of all memory cycles.

|        |      | Resolution [pixels] | Bitmap<br>Size<br>[K bytes] | Refresh<br>Rate<br>[frames/s] | Video<br>Bandwidth<br>[MHz] | Memory<br>Cycles<br>[%] |

|--------|------|---------------------|-----------------------------|-------------------------------|-----------------------------|-------------------------|

| Alto   | 1973 | 608 x 808           | 60                          | 30                            | 20                          | 48.36                   |

| Lilith | 1978 | 704 x 928           | 80                          | 30                            | 27                          | 11.48                   |

| Ceres  | 1986 | 1024 x 800          | 100                         | 62.15                         | 70                          | 0.25                    |

Figure 3.2 Examples of raster graphics interfaces.

The technological trends can easily be seen in Figure 3.2. The resolution of raster displays is steadily increasing; likewise the stability of the displayed image is improved by higher refresh rates. Although the frame buffer has to supply a significantly larger amount of video data, the table shows that techniques have been found to reduce drastically the memory cycles required for refreshing the display.

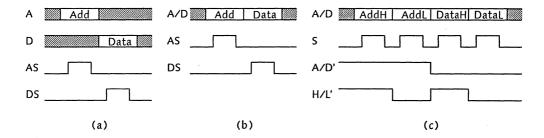

Different techniques have been developed for the implementation of frame buffers. Some typical architectural concepts shall be discussed in this section. A tutorial in memory design for raster graphics displays is contained in [Whitton 84]. Reference to [Baecker 79] can be made for a history of early frame buffer devices.

With available dynamic RAMs (DRAM), it is not possible to realize a true multi-port frame buffer that can be accessed simultaneously by the display processor and the display refresh controller; they both have to use the same port at different times. To suit the update and refresh process, techniques have to be found that equip the frame buffer with a considerably higher access bandwidth than required for accessing normal main memory.

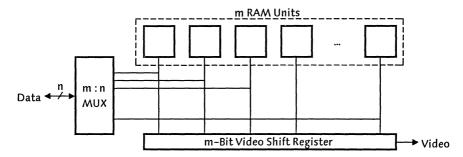

A common method is to widen the data bus for accesses of the display refresh controller. Figure 3.3 illustrates a *wide-word* memory architecture: while the display processor has an n-bit wide access path to the frame buffer, the display refresh controller can access m bits in one memory cycle, whereby m is an integral multiple of n; typical values are n = 16 and m = 64. The implementation can be facilitated by using wide-word memory devices. Typical organizations of such DRAM units are 16K x 4 bits or 64K x 4 bits allowing a reduction in

part count, savings in power, and improved reliability. The disadvantage of this design is the expense due to the m-bit wide multiplexer and shift register. Furthermore, electrical problems are likely to arise due to the expensive interconnection structure: an m-bit wide bus connects the memory devices, multiplexer, and shift register. This layout was used for several computers, such as the Xerox Dorado [Lampson 80] and the Lilith [Ohran 84].

Figure 3.3 A wide-word memory organization of a frame buffer.

However, the application of this method is limited. Figure 3.4 lists memory cycle requirements of the display refresh controller during the active display interval as a function of the number of pixels that are fetched per memory access. Assumed display parameters are a resolution of 1024  $\times$  800 pixels and a refresh rate of 30 Hz (interlaced) and 60 Hz (non-interlaced), respectively. The memory cycle time is assumed to be 400 ns. Especially the figures shown for the non-interlaced mode demand alternative methods.

|                          | 1                                    | 00, 30 Hz<br>xel Time           | 1024 x 800, 60 Hz<br>12.5 ns Pixel Time |                                  |  |

|--------------------------|--------------------------------------|---------------------------------|-----------------------------------------|----------------------------------|--|

| Pixels per<br>DRC Access | Time between<br>DRC Accesses<br>[ns] | Memory<br>Cycles for DRC<br>[%] | Time between<br>DRC Accesses<br>[ns]    | Memory<br>Cycles for DRC<br>[%]  |  |

| 16<br>32<br>64           | 400<br>800<br>1600                   | 100<br>50<br>25                 | 200<br>400<br>800                       | cannot be supported<br>100<br>50 |  |

Figure 3.4 Memory cycle requirements of the display refresh controller (DRC) for different frame buffer access widths.

Another method to meet the high bandwidth requirements is to use a special, fast access mode as provided by most DRAMs. The modes are called page mode, nibble mode, and ripple mode. They allow multiple bits of data to be sequentially read or written within an extended cycle and are applicable, if data are accessed that are located at successive addresses. A detailed analysis of using *burst modes* for the realization of a frame buffer is contained in [Whitton 84]. However, the achieved reduction of memory cycles required for refreshing the display is comparable with a wide-word memory architecture.

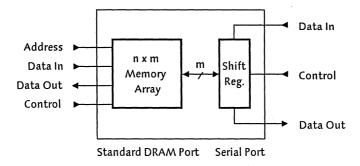

Recognizing the need for significantly higher data transfer rates chip designers developed a DRAM unit with an internal shift register [Pinkham 83]. A block diagram of this memory device is shown in Figure 3.5.

Figure 3.5 The organization of a VRAM.

The device, also known as *video RAM* (VRAM), contains a standard dynamic memory internally organized as a matrix of n x m memory cells and an m-bit wide shift register. Both ports, the standard DRAM port and the serial port can be accessed simultaneously. The contents of a complete memory row (m bits) can be transferred between the memory array and the shift register in one memory cycle. During that time it is not possible to access any port of the VRAM. As Figure 3.6 shows, a typical frame buffer contains n N x 1 bit VRAMs, whereby n is determined by the width of the bus connecting the display processor and the frame buffer. The serial output ports of the n memory devices feed in parallel to an external n-bit video shift register. With a maximum clock rate f at which the shift register of the VRAM can be operated, video data rates of up to  $n \cdot f$  can be achieved with n VRAMs. Current VRAM implementations specify a clock rate f of 25 MHz.

Figure 3.6 Frame buffer organization based on VRAMs.

VRAM technology appears to be ideal for frame buffer design. The video bandwidth is no longer limited by accessing the frame buffer. Furthermore, no significant delay of display processor operations is caused by interfering frame buffer accesses of the display refresh controller.

# 3.2.2 Image Creation

The most important bitmap operator is *BitBlt*, which stands for <u>bit block transfer</u> as designed by Ingalls in 1975 [Ingalls 81]. A detailed discussion is contained in [Newman 79] where it is called *RasterOp*, short for <u>raster operator</u>. RasterOp works on rectangular regions within a bitmap. The operator takes two rectangles, called the source s and the destination d and modifies d using values of s:

$$d \leftarrow F(d,s)$$

Of the sixteen possible Boolean functions, four appear to be useful for monochrome image manipulations: F(d,s) typically is s (replace), d OR s (paint), d XOR s (invert), or d AND NOT s (erase). The importance of RasterOp and its generality in application have been discussed extensively in [Newman 79, Ingalls 81, Gutknecht 83]. Graphics primitives are either implemented in software and executed by the CPU, or assisted by special hardware.

A software-based implementation is simple, flexible, and inexpensive. However, executing RasterOp on a general purpose microprocessor is expected to be slow. An improvement can be obtained by providing RasterOp as a single machine instruction, as it is possible with a microprogrammable processor. This is advantageous because the instruction sequence, which is repetitively executed by a processor with a fixed instruction set, can be encoded in a single instruction thus reducing the time needed to fetch and decode the instructions and because lower level optimizations are possible. A nice example of a purely software-based implementation for an MC68000 CPU is the AT&T graphics terminal Blit [Pike 85]. Microcoded RasterOp can be found in the Xerox Alto and the Lilith computers.

Various hardware assistance for raster graphics has been proposed, ranging from devices that cooperate with a general purpose microprocessor in manipulating single words, up to display processors that execute high-level graphics functions. Depending on the kind of hardware assistance, there are differences for the CPU in accessing the frame buffer, as shown in Figure 3.7. In an *integral* frame buffer design, the frame buffer is an integral part of the CPU's memory address space. In a *peripheral* frame buffer design, the frame buffer is not directly accessible from the CPU, but is controlled instead by a display or graphics processor.

Figure 3.7 An integral frame buffer (a) and a peripheral frame buffer (b).

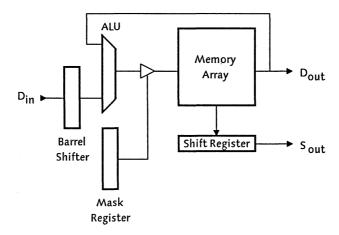

A modest solution is to add hardware assistance for shifting, masking, and Boolean operations as it is shown in Figure 3.8. The processor's duty is then reduced to simply move data from one memory area to another. By executing a read-modify-write memory cycle a

destination word obtains a new value given by the logic operation between the destination word ( $D_{out}$ ) and the source word ( $D_{in}$ ). A barrel shifter is provided in order to align the source words with the destination words. A mask register is useful if the destination words have to be modified only partially.

Figure 3.8 Frame buffer with hardware assistance for RasterOp.

While these provisions could be easily implemented with standard components, an even less expensive solution is provided by a special VRAM. The HM53462 from Hitachi already contains an ALU and a mask register [Hitachi 1986]. The device offers the ability to internally interpret a write cycle as a read-modify-write cycle modifying the data according to a specified ALU-operation. Similar concepts have been followed up in the design of VLSI-circuits such as the MergeOp Unit described in [Kronfeld 85] or the RALU (RasterOp ALU) from VTI [VTI]. In addition to an ALU and a mask register, these devices also contain a barrel shifter. Unfortunately, both devices are only 16-bit wide and are not cascadable.

The CPU can be completely freed from image manipulations by providing a separate display processor, which is equipped with a dedicated instruction set that allows to efficiently execute high-level graphics functions. Furthermore, the normally required peripheral frame buffer design allows the display processor and the CPU to work in parallel. Display processors are welcome VLSI-applications and are or will become available from most larger semiconductor manufacturers. A collection of descriptions of current display processors can be found in [CG&A 86]. All these devices show similar architectures that not only contain the display processor itself, but also a DRAM controller/driver, and a display refresh controller.

A disadvantage associated with display processors is their lacking flexibility due to a predefined set of instructions. It will be difficult, or even impossible, to extend the display processor's firmware. This limits the exploration of novel raster operations, e.g. drawing of spline curves or filling of bitmap areas.

A severe problem of most hardware assisted raster graphics systems is that <u>RasterOp cannot</u> be uniformly applied to both the bitmap memory and the general memory. Bitmaps have to reside in a dictated memory area that in the case of a peripheral frame buffer is not even transparent for the CPU. However, modern raster graphics software requires non-visible

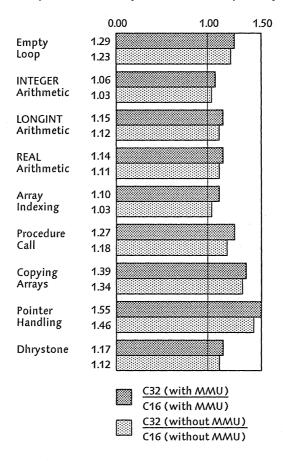

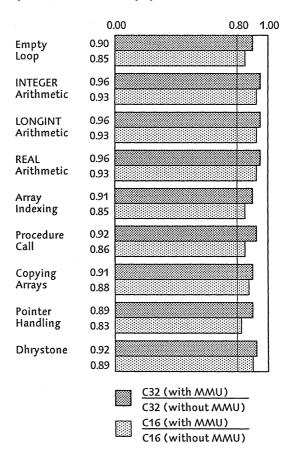

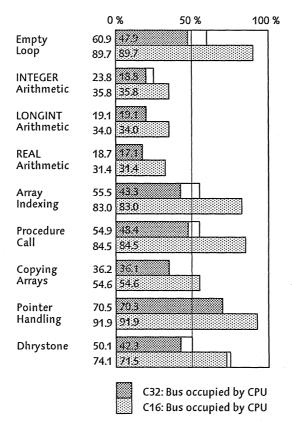

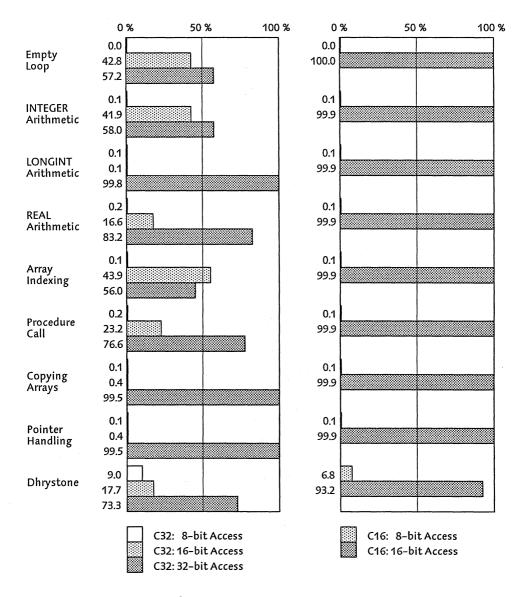

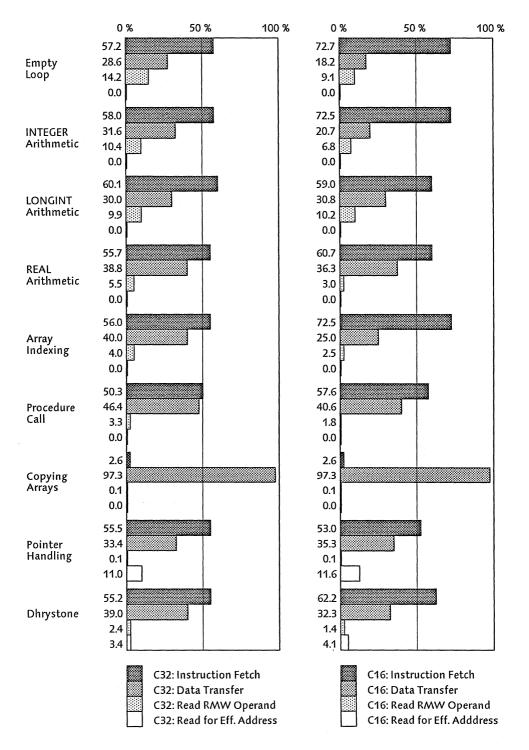

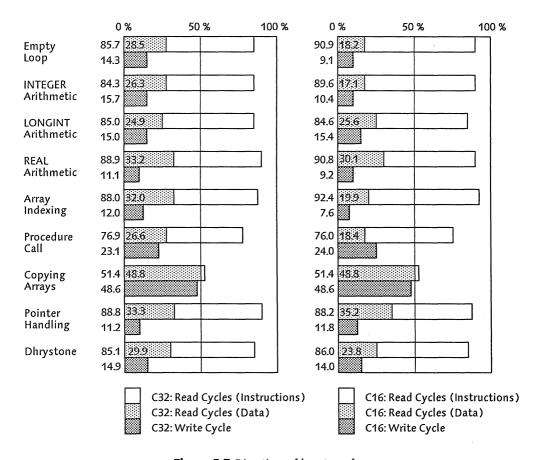

bitmaps of which there can be a large number and which have to be processed as efficiently as the displayed bitmap [Pike 83]. Note that every non-uniformity of the address space complicates the software.