# DSD 5215 Multibus Disk Controller User Guide

Copyright<sup>©</sup> 1983 All rights reserved. No part of this book may be reproduced in any form or by any means without prior written permission of Data Systems Design, Inc.

7

# PREFACE

This manual describes the features, specifications, and programming of the DSD 5215 Multibus Disk Controller. Instructions for equipment installation, operation, and elementary troubleshooting are included.

The material in this manual is subject to change without notice. The manufacturer assumes no responsibility for any errors which may appear.

Please note that Intel, iSBC, iSBX, Multibus and the combination of iSBC, iSBX, or RMX and a numerical suffix are registered trademarks of Intel Corporation. CP/M is a trademark of Digital Research, Inc. UNIX is a trademark of Bell Laboratories. HyperDiagnostics, Rapid Module Exchange, StacPac, and HyperService are trademarks of Data Systems Design.

# CONTENTS

## 1. General Information

| 1.1 |                            | 1-1 |

|-----|----------------------------|-----|

| 1.2 | Features                   | 1-1 |

| 1.3 | Self-Test and Diagnostics  | 1-1 |

| 1.4 | Off-Line Backup Čapability | 1-1 |

| 1.5 | Summary                    | 1-1 |

## 2. Specifications

| 2-2      |

|----------|

|          |

| 2-2      |

| ons      |

| 2-4      |

| 2-5      |

| 2-6      |

| <b>(</b> |

# 3. Installation

| 3.1 |                              | 3-1 |

|-----|------------------------------|-----|

| 3.2 | Unpacking and Inspection     | 3-1 |

| 3.3 | Installation                 | 3-1 |

| 3.4 | Jumper Options               | 3-1 |

|     | 3.4.1 Jumper Configurations  | 3-1 |

|     | 3.4.2 Jumper Group W6        |     |

|     | Configuration                | 3-3 |

|     | 3.4.3 Bus Arbitration Modes  | 3-4 |

|     | 3.4.4 Drive Jumpering        | 3-4 |

| 3.5 | Initial Checkout and         |     |

|     | Acceptance Tests             | 3-4 |

|     | 3.5.1 Test and Verification. | 3-4 |

## 4. Programming

| 4.1<br>4.2<br>4.3 | Introduction                     | 4-1<br>4-1<br>4-1 |

|-------------------|----------------------------------|-------------------|

|                   | Floppy Disk Organization         |                   |

| 4.4               | Streaming Tape Organization      | 4-1               |

| 4.5               | Issuing Commands and             |                   |

|                   | Receiving Status                 | 4-2               |

| 4.6               | Host/Controller Communications   | 4-3               |

|                   | 4.6.1 Input/Output Commands      | 4-3               |

|                   | 4.6.2 Interrupts                 | 4-4               |

|                   | 4.6.3 Memory-Based Control Paths | 4-4               |

|                   | 4.6.4 Address Representation     | 4-4               |

|     | 4.6.5 Wake-Up Block                 | 4-4  |

|-----|-------------------------------------|------|

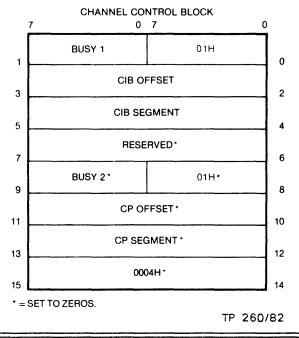

|     | 4.6.6 Channel Control Block         | 4-6  |

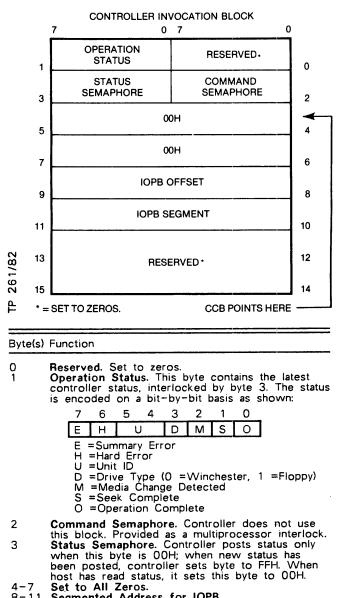

|     | 4.6.7 Controller Invocation Block . | 4-6  |

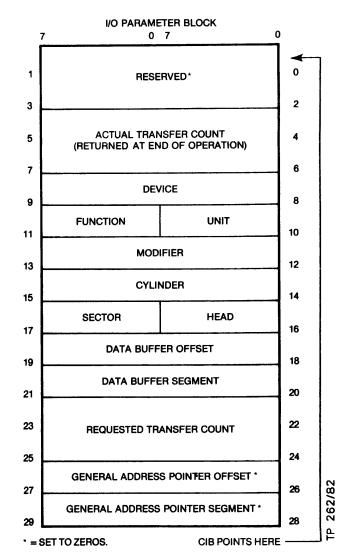

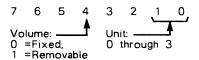

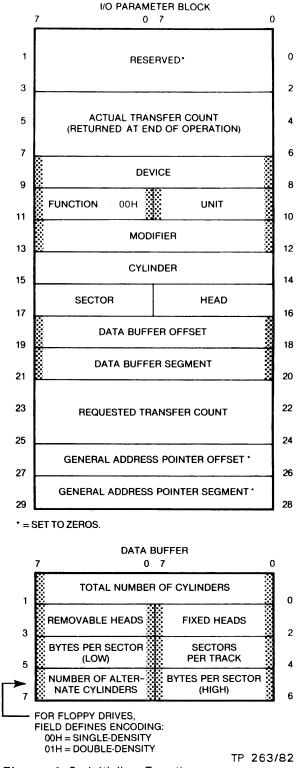

|     | 4.6.8 I/O Parameter Block           | 4-7  |

| 4.7 | Controller Commands                 | 4-8  |

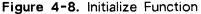

|     | 4.7.1 Initialize (00H)              | 4-9  |

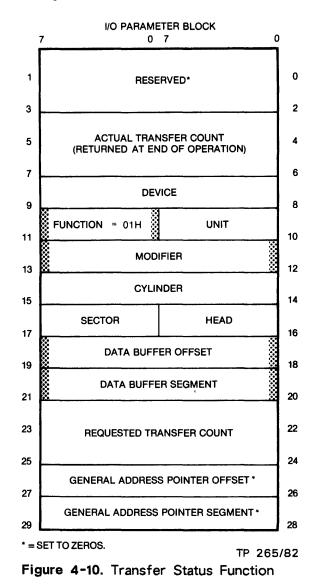

|     | 4.7.2 Transfer Status (01H)         | 4-11 |

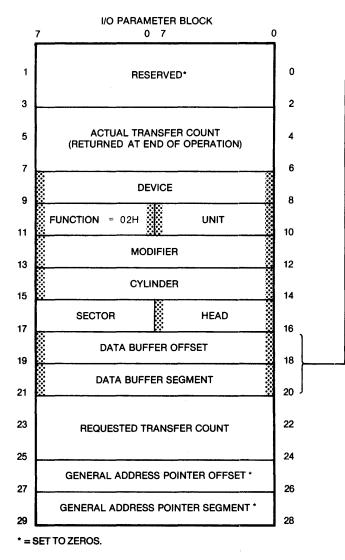

|     | 4.7.3 Format (02H)                  | 4-12 |

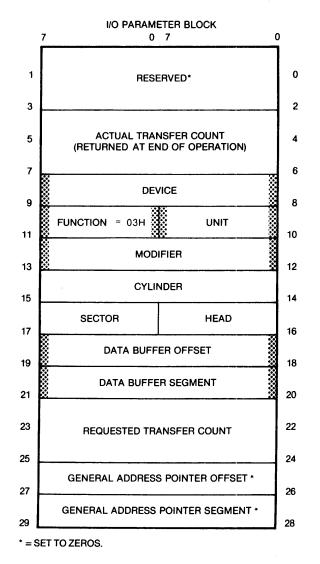

|     | 4.7.4 Read Sector ID (03H)          | 4-14 |

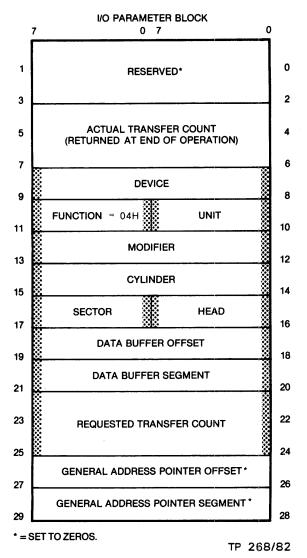

|     | 4.7.5 Read Data (04H)               | 4-15 |

|     | 4.7.6 Read Buffer and               |      |

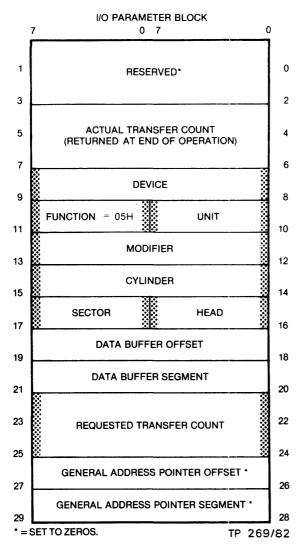

|     | Verify (05H)                        | 4-15 |

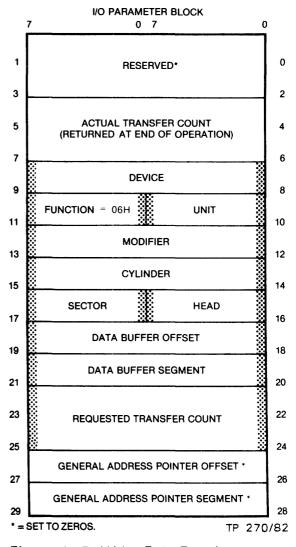

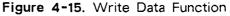

|     | 4.7.7 Write Data (06H)              | 4-16 |

|     | 4.7.8 Write Buffer Data (07H) .     | 4-17 |

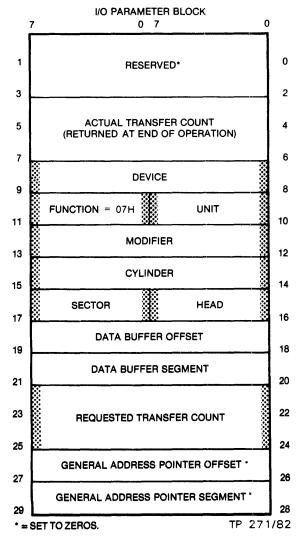

|     | 4.7.9 Initiate Track Seek (08H) .   | 4-18 |

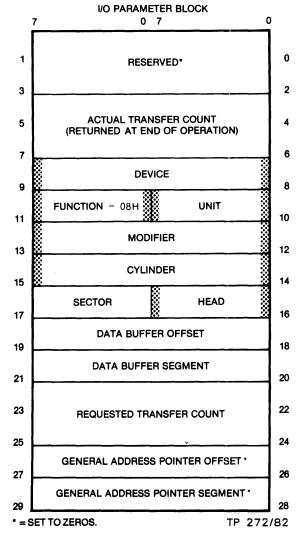

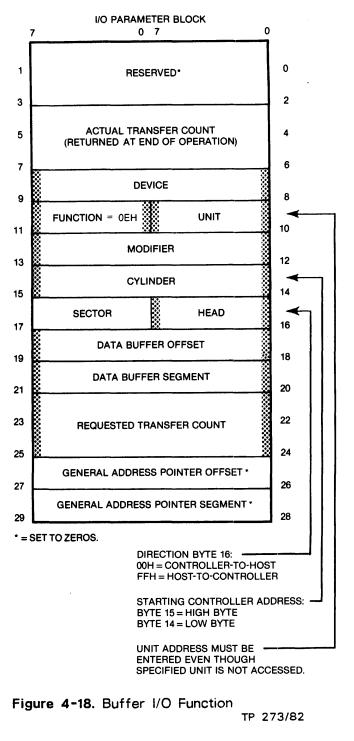

|     | 4.7.10 Buffer I/O (0EH)             | 4-18 |

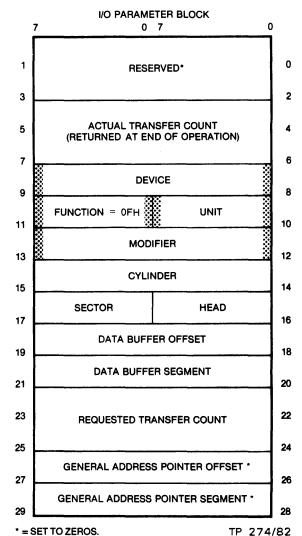

|     | 4.7.11 Diagnostics (OFH)            | 4-19 |

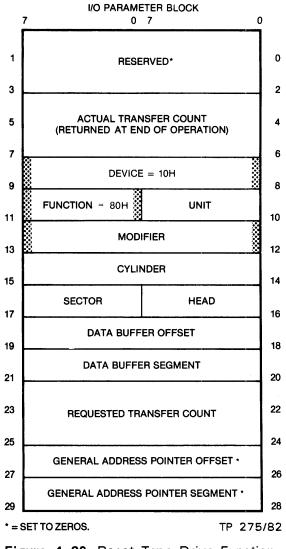

|     | 4.7.12 Reset Tape Drive (80H)       | 4-21 |

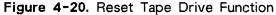

|     | 4.7.13 Disk Image Backup (81H)      | 4-21 |

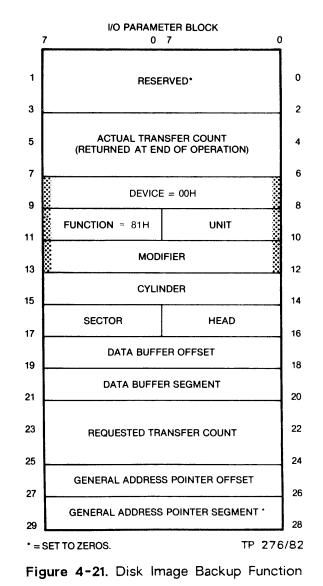

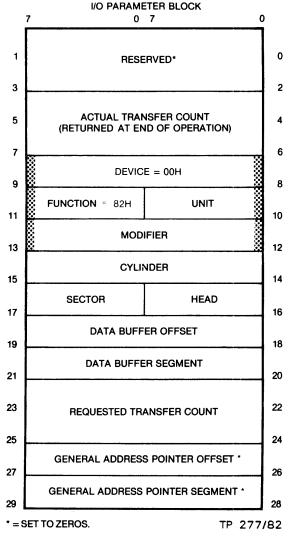

|     | 4.7.14 Disk Image Restore (82H).    | 4-22 |

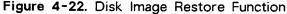

|     | 4.7.15 Read Tape Status (83H)       | 4-22 |

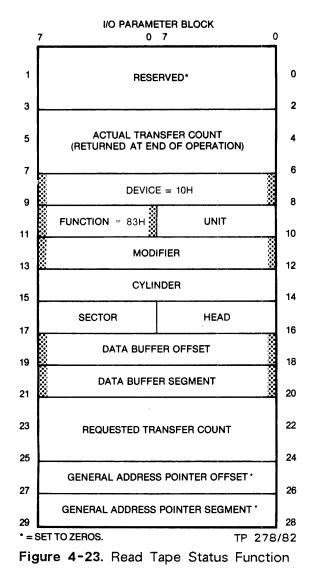

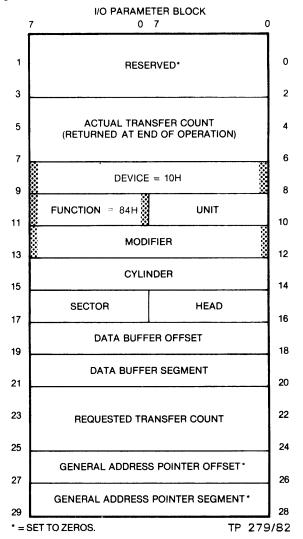

|     | 4.7.16 Tape Retension Cycle (84H)   | 4-23 |

| 4.8 | Error Processing                    | 4-24 |

|     | 4.8.1 Bad Track Handling            | 4-24 |

|     |                                     |      |

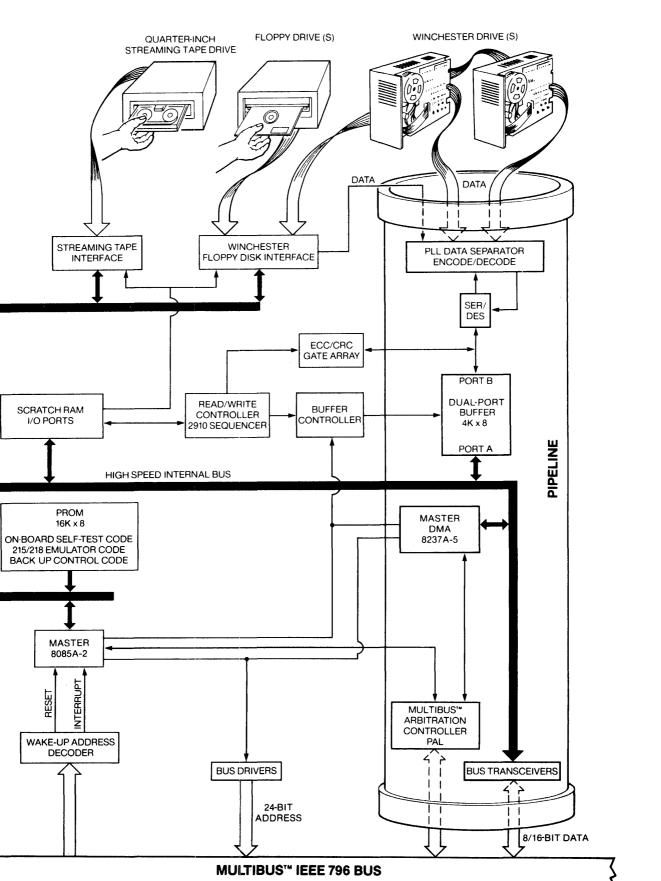

# 5. Controller Architecture

| 5.1 | Introduction               | 5-1 |

|-----|----------------------------|-----|

| 5.2 | DSD Controller Description | 5-1 |

## 6. User Level Maintenance

| 6.1 | Introduction                                         | 6-1 |

|-----|------------------------------------------------------|-----|

| 6.2 | Troubleshooting and Fault Analysis                   | 6-1 |

| 6.3 | Off-Line HyperDiagnostics 6.3.1 HyperDiagnostics and | 6-1 |

|     |                                                      | 6-3 |

| 6.4 | Maintenance Assistance                               | 6-4 |

|     |                                                      |     |

## Appendix A: DSD 5215 Multibus Disk Controller Drive Configuration

Appendix B: Cross Reference Index

# List of Figures:

| 1-1<br>2-1<br>2-2 | DSD 5215 Multibus Controller .<br>Cable and Connector Configuration<br>Master Command Access Timing |            | 2-1<br>2-2 |

|-------------------|-----------------------------------------------------------------------------------------------------|------------|------------|

| 3-1<br>4-1        | Jumper Locations                                                                                    | 3-3<br>4-1 | 2-3        |

| 4-2               | Winchester Sector Data Format                                                                       | -4-2       | 2-4        |

| 4-3               | Chain of Communication Blocks .                                                                     | 4-5        | 2-5        |

| 4-4               | Wake-Up Block                                                                                       | 4-6        |            |

| 4-5               | Channel Control Block                                                                               | 4-6        | 2-6        |

| 4-6               | Controller Invocation Block                                                                         | 4-7        |            |

| 4-7               | Input Output Parameter Block                                                                        | 4-7        | 2-7        |

| 4-8               | Initialize Function                                                                                 | 4-9        |            |

| 4-9               | Initialization Examples                                                                             | 4-10       | 2-8        |

| 4-10              | Transfer Status Function                                                                            | 4-11       |            |

| 4-11              | Format Function                                                                                     | 4-13       | 2-9        |

| 4-12              | Read Sector ID Function                                                                             | 4-14       | 2-10       |

| 4-13              | Read Data Function                                                                                  | 4-15       | 2-11       |

| 4-14              | Read Buffer and Verify Function                                                                     | 4-16       | 3-1        |

| 4-15              | Write Data Function.                                                                                | 4-16       | 3-2        |

| 4-16              | Write Buffer Data Function                                                                          | 4-17       |            |

| 4-17              | Initiate Track Seek Function                                                                        | 4-17       | 3-3        |

| 4-18              | Buffer I/O Function                                                                                 | 4-18       | <b>.</b> . |

| 4-19              | Diagnostic Function                                                                                 | 4-19       | 3-4        |

| 4-20              | Reset Tape Drive Function                                                                           | 4-20       | ~ -        |

| 4-21              | Disk Image Backup Function                                                                          | 4-20       | 3-5        |

| 4-22              | Disk Image Restore Function.                                                                        | 4-21       | 4-1        |

| 4-23              | Read Tape Status Function                                                                           | 4-22       | 4-2        |

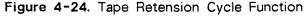

| 4-24              | Tape Retension Cycle Function                                                                       | 4-22       | 4-3        |

| 5-1               | DSD 5215 Multibus Controller                                                                        | E 0        | 4-4        |

| 6-1               | Block Diagram.                                                                                      | 5-3        | 4-5        |

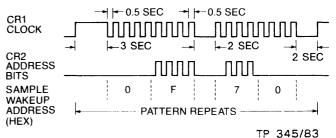

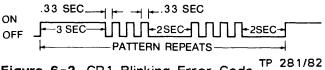

| 0-1               | Timing for CR1, CR2 Blinking                                                                        | 6-2        | 4-6<br>6-1 |

| 6-2               | Wakeup Address Test                                                                                 | 6-2<br>6-3 | 0-1        |

| 0-2               | CR1 Blinking Error Code                                                                             | 0-3        |            |

# List of Tables:

| 2-1<br>2-2 | Specifications                     | 2-1      |

|------------|------------------------------------|----------|

| 2-2        | Multibus P1 Connector              |          |

|            | Pin Assignment                     | 2-2      |

| 2-3        | Multibus P2 Connector              |          |

|            | Pin Assignment                     | 2-2      |

| 2-4        | Controller/Multibus Signals        | 2-3      |

| 2-5        | Tape Drive                         |          |

|            | Control Connector J1               | 2-4      |

| 2-6        | Winchester Drive                   | 2 7      |

| 20         | Control Connector J2A              | 2 4      |

| ~ 7        |                                    | 2-4      |

| 2-7        | Floppy Drive                       | <u> </u> |

|            | Control Connector J2B              | 2-5      |

| 2-8        | Winchester Data                    |          |

|            | Connectors J3 and J4               | 2-5      |

| 2-9        | Disk Formats                       | 2-5      |

| 2-10       | Winchester Drive Characteristics . | 2-6      |

| 2-11       | Floppy Drive Characteristics       | 2-6      |

| 3-1        | Jumper Configurations              | 3-2      |

| 3-2        | W7 and W9 WUA Jumper               | 0 2      |

| 52         |                                    | 3-3      |

| 2 2        | Configurations                     | 3-3      |

| 3-3        | W6 Jumper Configurations,          | ~ ~      |

| • •        | Winchester                         | 3-3      |

| 3-4        | W6 Jumper Configurations,          |          |

|            | Floppy                             | 3-3      |

| 3-5        | Indicator Sequence                 | 3-4      |

| 4-1        | Addressing                         | 4-4      |

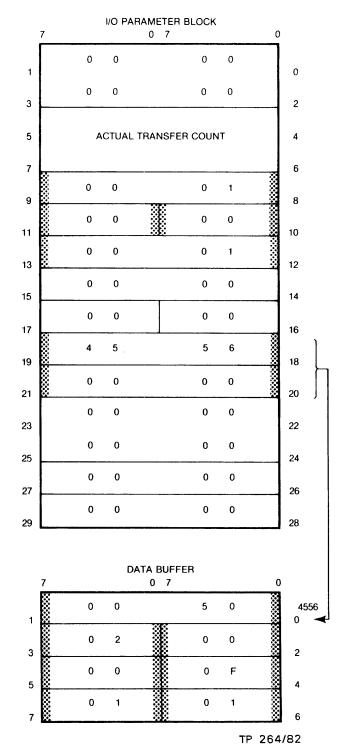

| 4-2        | Byte Values Example (IOPB)         | 4-11     |

| 4-3        | Error Status Buffer                | 4-12     |

| 4-4        | Error Status Bit Definition        | 4-12     |

| 4-5        | Extended Error Status Codes        | 4-12     |

| 4-6        | On-Line Diagnostics                | 4-19     |

| 6-1        | Off-Line HyperDiagnostics and      | 5        |

| 0-1        | lumper M/G Configuration           | 6-2      |

|            | Jumper W6 Configuration            | 6-2      |

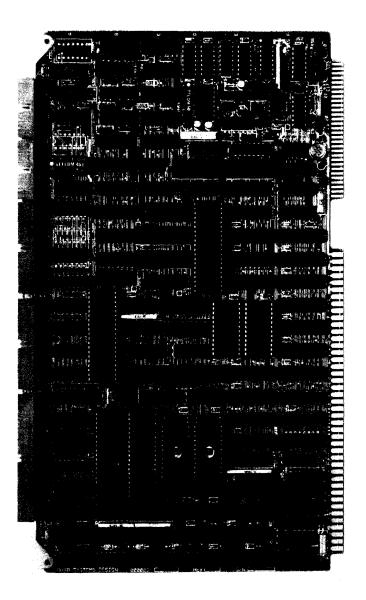

Figure 1-1. DSD 5215 Multibus Controller

# **1 GENERAL INFORMATION**

## 1.1 Introduction

The DSD 5215 Multibus Disk Controller is a compact single-board controller for 5-1/4 inch Winchester, floppy, and any QIC-02 compatible streaming tape drive. The DSD 5215 emulates the Intel iSBC 215 and iSBX 218 controller combination. Operation is compatible with software and operating systems supporting that product.

This manual provides user information for the DSD 5215 controller. Coverage includes features, specifications, installation, operation, programming, block diagram and architecture, and user level maintenance.

#### 1.2 Features

Features of the DSD 5215 Controller are:

- Standard interfaces for Winchester, floppy, and streaming tape drives.

- All drives are connected pin-for-pin by flat ribbon cables for easier installation.

- All interfaces plus data separation are on a single Multibus card for best system cost.

- Buffering provided for non-interleaved operation and off-line mirror image disk-totape backup operations.

- Built in high reliability and data integrity.

- Meets the requirements of the IEEE-P796 specifications for the Multibus standard, including 24-bit addressing.

- Emulates Intel's iSBC 215 and iSBX 218 controller combination.

- Compatible with operating systems supported by Intel, such as RMX-86.

## **1.3 Self-Test and Diagnostics**

Two LEDs, labelled CR1 (ERR) and CR2 (RDY) are mounted on the controller card. These LEDs respond according to the option setting and error condition. LED CR2 (RDY) indicates whether the controller is ready to accept a new command (ON) or is busy (OFF). LED CR1 (ERR) is active when an error is detected. Use of these indicators during initial checkout and acceptance testing is detailed in Chapter 3.

Resident PROM diagnostics (jumper selectable by user) may be used for fault isolation to determine if a problem involves the controller hardware, disk drives, or bus. Refer to Chapter 6 for detailed fault isolation procedures.

## 1.4 Off-Line Backup Capability

Off-line backup for the Winchester drive can be provided by the quarter-inch streaming tape drive. Tape backup control is provided by an I/O port supporting the QIC-02 interface. This provides the user with high capacity backup at a low cost. Commands are provided for full image backup and restore at five megabytes per minute. The cartridge can store up to 45 megabytes of data.

## 1.5 Summary

Disk memory systems combining Winchester, floppy, and tape drives are opening new application possibilities for small computer systems. Their functional design and performance rival that of large disk systems costing several times as much. When considering a Winchester based disk memory system, the user should look beyond the usual considerations of capacity and backup and examine the function and capability of the entire system. Data Systems Design has been an industry leader in the design and manufacture of disk storage systems since 1975. The DSD Multibus Controller is a powerful and effective design offering a combination of price, features, and performance unavailable from any other source. These features are summarized below:

#### Compatible:

- Multibus compatible board format

- Emulates the iSBC 215 and iSBX 218 combination

- Standard formats for disks (singleand double-density)

- Standard drive interfaces

- IEEE-P796 standard bus, including 24-bit addressing

#### Flexible:

- Supports floppy, tape, and Winchester

- Variety of standard drive selections

- Up to two disk drives of each type

- 8- or 16-bit I/O address for 8or 16-bit systems

- Several bus arbitration choices

- Variable disk interleave

- Four sector sizes

#### **Powerful:**

- Non-interleaved disk transfer (floppy and Winchester)

- Byte or word transfers

- Burst mode transfer of any length (multiple sector transfers, up to entire disk)

- Overlapped seeks

- Five megabytes per minute disk backup without computer intervention

- Efficient bus arbitration

- Wide bandwidth design

- Memory based commands

#### **Cost Effective:**

- Three controllers in one

- No extra boards to buy

- Integrated data separator

#### Easy to Integrate:

- Single-board, occupies one slot

- One-to-one cable connection

- Easy jumper configuration

- Standard software interface

- Complete table top systems available

- Clear, complete, professional documentation

#### **Reliable:**

- Effective media flaw management

- Thorough test and burn-in

- Power up self-test

- Wide margin phase-locked-loop

- Full sector buffering eliminates data overrun and potential for lost data

- ECC for Winchester disk, 22-bit detect, 11-bit correct. Automatic error recovery and retry. Transparent data error correction

- Full disk backup

- Bus time-out eliminates hang-up states

- Conservative, no compromise design

#### Serviceable:

- Flashing error codes for easy problem identification

- On-board diagnostics for fault isolation

- HyperService with Rapid Module Exchange

- Customer Service hotline

# **2 SPECIFICATIONS**

#### 2.1 Introduction

This section contains specifications, environmental and power requirements, and dimensions for the DSD 5215 Controller/Interface.

Specifications listed in Table 2–1 include drive characteristics for Winchester, floppy, and tape drives. Requirements include those for interface cabling and connectors, and pin assignments for the controller connectors.

Table 2-1. Specifications

#### General:

| Multibus Interface    | IEEE P796, Master D16M24,                      |  |  |  |

|-----------------------|------------------------------------------------|--|--|--|

|                       | Slave D8116VOEL                                |  |  |  |

| I/O Address           | User selectable, 8 or 16 bit                   |  |  |  |

| Data Transfers        | 8 or 16 bits wide                              |  |  |  |

| Drive Capacity        | Any capacity drive with<br>supported interface |  |  |  |

| Memory Addressing     | 20 or 24 bit addressing                        |  |  |  |

| Bus Arbitration Modes |                                                |  |  |  |

|                       | Single transfer                                |  |  |  |

|                       | Yield to any request                           |  |  |  |

|                       | Yield to higher priority                       |  |  |  |

|                       | Override                                       |  |  |  |

| Interrupts            | One interrupt, jumpered by                     |  |  |  |

| interrupts            | user to any one of Multibus                    |  |  |  |

|                       | lines INTO/ to INT7/                           |  |  |  |

|                       |                                                |  |  |  |

| Standard Interfaces   | :                                              |  |  |  |

| Winchester            | ST506                                          |  |  |  |

| Floppy                | SA460                                          |  |  |  |

| Tape                  | QIC-02                                         |  |  |  |

| + •                   |                                                |  |  |  |

| DMA Bus Usage: (S     | ingle transfer mode)                           |  |  |  |

| Reading from bus      | 0.9 usec plus memory<br>read access time/word  |  |  |  |

| Writing to bus        | 0.5 usec plus memory                           |  |  |  |

#### **Recording Formats:**

write access time/word

#### Formatting:

| Winchester:<br>Sector Size (Bytes)<br>Sectors/Track | 128,<br>54, | 256,<br>31, | 512,<br>17, | 1024<br>9 |

|-----------------------------------------------------|-------------|-------------|-------------|-----------|

| Floppy:<br>Sector Size (Bytes)<br>Sectors/Track     | 128,        | 256,        | 512,        | 1024,     |

| Single-density:<br>Double-density:                  | 15,         | 8,<br>15,   | 4,<br>8,    | 2<br>4    |

#### Data Rates:

| Winchester | 5 Mbits/sec   |

|------------|---------------|

| Floppy     | 250 Kbits/sec |

| Таре       | 87 Kbytes/sec |

#### Transfer Rates:

| Winchester (Non-interle<br>Within a sector<br>Within a cylinder<br>Across entire disk<br>(8 tracks/cylinder) | 1024<br>625<br>529 | format)<br>byte sectors<br>Kbytes/sec<br>Kbytes/sec<br>Kbytes/sec |

|--------------------------------------------------------------------------------------------------------------|--------------------|-------------------------------------------------------------------|

| Floppy                                                                                                       | 256<br>31.:        | byte sectors<br>25 Kbytes/sec                                     |

#### Error Detection/Correction:

| Floppy and Tape | CRC checksum                                          |

|-----------------|-------------------------------------------------------|

| Winchester      | 32-bit ECC polynomial<br>22-bit burst error detection |

|                 | 11-bit burst error correction                         |

| Activity Lights | Two LED indicators (also used                         |

|                 | by HyperDiagnostics)                                  |

#### **Environmental Specifications:**

| Operating | Temperature | 41°F to 131°F (5°C to 55°C) |

|-----------|-------------|-----------------------------|

| Humidity  |             | Up to 90% non-condensing    |

| Cooling   |             | DSD 5215 dissipates 24W     |

|           |             | of heat (80 BTU/hr).        |

|           |             | Adequate air circulation    |

|           |             | must be maintained to       |

|           |             | prevent a temperature rise  |

|           |             | above 131°F (55°C).         |

#### **Power** Requirements:

+5 Vdc, ±5% @ 5.1 Amp typical +12 Vdc, ±5% @ 0.1 Amp typical

#### **Physical Specifications:**

| Mounting            | Occupies one card slot in the Multibus backplane.                                      |

|---------------------|----------------------------------------------------------------------------------------|

| Dimen <b>s</b> ions | Width: 12.0 in. (30.5 cm.)<br>Height: 7.1 in. (18 cm.)<br>Thickness: 0.6 in. (1.5 cm.) |

# 2.2 Cables and Connectors

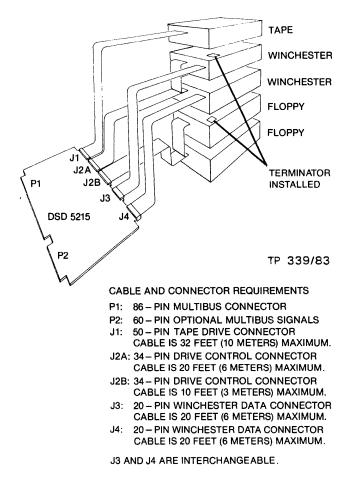

Figure 2-1 shows all connector and cabling requirements. The connectors (wired pin-to-pin) used with J1 through J4 are female connectors with 1/10-inch pin spacing.

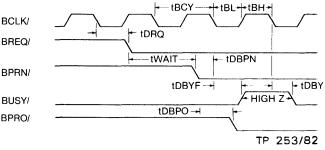

#### 2.2.1 Multibus P1 and P2 Configurations

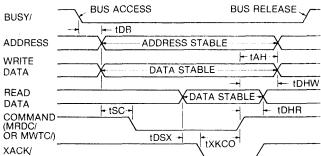

The controller communicates with the CPU via the Multibus interface. Table 2-2 and 2-3 list the Multibus connector pin assignments. Table 2-4 describes the controller/Multibus interface signals. Figure 2-2 is a diagram of the controller/Multibus interface timing signals with timing requirements. The controller is connected to the Multibus interface through connector P1, an 86-pin, double-sided, printed circuit edge connector. Connector P2 provides for optional Multibus signals, as listed in Figure 2-1.

Figure 2-1. Cable and Connector Configuration

Table 2-2. Multibus P1 Connector Pin Assignment

| able 2-2. Nultibus Pl                                                                                                                                                                                                                        | Connector Pin Assignment                                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| Component Side<br>Pin Signal Name                                                                                                                                                                                                            | Circuit Side<br>Pin Signal Name                                                              |

| Power         Supplies:           1         GND           3         +5Vdc           5         +5Vdc           7         +12Vdc           9         -5Vdc (Not Use           11         GND                                                   | 2 GND<br>4 +5Vdc<br>6 +5Vdc<br>8 +12Vdc<br>d) 10 -5Vdc (Not Used)<br>12 GND                  |

| Bus         Controls:           13         BCLK/           15         BPRN/           17         BUSY/           19         MRDC/           21         IORC/           23         XACK/                                                      | 14 INIT/<br>16 BPRO/<br>18 BREQ/<br>20 MWTC/<br>22 IOWC/<br>24 INH1/                         |

| Bus Controls and Add<br>25 Reserved<br>27 BHEN/<br>29 CBRQ/<br>31 CCLK/                                                                                                                                                                      | Iress Bus:<br>26 INH2/ (Not Used)<br>28 ADR10/<br>30 ADR11/<br>32 ADR12/<br>34 ADR13/        |

| Interrupts:<br>33 INTA/<br>35 INT6/<br>37 INT4/<br>39 INT2/<br>41 INT0/                                                                                                                                                                      | 36 INT7/<br>38 INT5/<br>40 INT3/<br>42 INT1/                                                 |

| Address         Bus:           43         ADRE/           45         ADRC/           47         ADRA/           49         ADR8/           51         ADR6/           53         ADR4/           55         ADR2/           57         ADR0/ | 44 ADRF/<br>46 ADRD/<br>48 ADRB/<br>50 ADR9/<br>52 ADR7/<br>54 ADR5/<br>56 ADR3/<br>58 ADR1/ |

| Data         Bus:           59         DATE/           61         DATC/           63         DATA/           65         DAT8/           67         DAT6/           69         DAT4/           71         DAT2/           73         DAT0/    | 60 DATF/<br>62 DATD/<br>64 DATB/<br>66 DAT9/<br>68 DAT7/<br>70 DAT5/<br>72 DAT3/<br>74 DAT1/ |

| Power Suppies:<br>75 GND<br>77 Reserved<br>79 -12Vdc (Not U<br>81 +5Vdc<br>83 +5Vdc<br>85 GND                                                                                                                                                | 76 GND<br>78 Reserved<br>sed) 80 - 12Vdc (Not Used)<br>82 +5Vdc<br>84 +5Vdc<br>86 GND        |

"/" following the signal name indicates an active low.

Table 2-3. Multibus P2 Connector Pin Assignment

| Pin | Signal Name | Pin | Signal Name |

|-----|-------------|-----|-------------|

| 55  | ADR16/(Hex) | 56  | ADR17/(Hex) |

| 57  | ADR14/(Hex) | 58  | ADR15/(Hex) |

Table 2-4. Controller/Multibus Signals

| Signal                                | Functional Description                                                                                                                                                                                                                                                                                               |

|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADR0/-<br>ADRF/,<br>ADR10/-<br>ADR13/ | Address: These 20 lines transmit the address<br>of the memory location or I/O port to be<br>accessed. For memory access, ADR0/(when<br>active) enables the even byte bank DAT0/-<br>DAT7/ on the Multibus connector; i.e., ADR0/<br>is active for all even addresses. ADR13/ is<br>the most significant address bit. |

| BCLK/                                 | Bus Clock: Used to synchronize the bus con-<br>tention logic on all bus masters.                                                                                                                                                                                                                                     |

| BHEN/                                 | Byte High Enable: When active low, enables the odd byte bank (DAT8/- DATF/) onto the Multibus connector.                                                                                                                                                                                                             |

| 3PRN/                                 | Bus Priority In: When low, indicates to a particular bus master that no higher priority bus master is requesting use of the bus.<br>BPRN/ is synchronized with BCLK/.                                                                                                                                                |

| BPRO/                                 | Bus Priority Out: In serial (daisy chain) priority resolution schemes, BPRO/ must be connected to the BPRN/ input of the bus master with the next lower bus priority.                                                                                                                                                |

| BREQ/                                 | Bus Request: In parallel priority resolution<br>schemes, BREQ/ indicates that a particular bus<br>master requires control of the bus for one or<br>more data transfers. BREQ/ is synchronized<br>with BCLK/.                                                                                                         |

| BUSY/                                 | Bus Busy: Indicates that the bus is in use and<br>prevents all other bus masters from gaining<br>control of the bus. BUSY/ is synchronized<br>with BCLK/.                                                                                                                                                            |

| CBRQ/                                 | <b>Common Bus Request:</b> Indicates that a bus master wishes control of the bus but does not presently have control. As soon as control of the bus is obtained, the requesting bus controller raises the CBRQ/ signal.                                                                                              |

| DAT0/-<br>DATF/                       | Data: These 16 bidirectional data lines transmit<br>and receive data to and from the addressed<br>memory location or I/O port. DATF/ is the<br>most significant bit. For data byte operations,<br>DATO/- DAT7/ is the even byte and DAT8/-<br>DATF/ is the odd byte.                                                 |

| INIT/                                 | Initialize: Reset the entire system to a known internal state.                                                                                                                                                                                                                                                       |

| NT0/-<br>NT7/                         | Interrupt Request: These eight lines transmit<br>interrupt requests to the appropriate interrupt<br>handler. INTO/ has the highest priority.                                                                                                                                                                         |

| owc/                                  | I/O Write Command: Indicates that the<br>address of an I/O port is on the Multibus<br>connector address lines and that the contents<br>on the Multibus connector data lines are to be<br>accepted by the addressed port.                                                                                             |

| MRDC/                                 | Memory Read Command: Indicates that the<br>address of a memory location is on the Mul-<br>tibus connector address lines and that the<br>contents of the location are to be read<br>(placed) on the Multibus connector data lines.                                                                                    |

| MWTC/                                 | <b>Memory Write Command:</b> Indicates that the<br>address of a memory location is on the Mul-<br>tibus connector address lines and that the<br>contents on the Multibus connector data lines<br>are to be written into that location.                                                                               |

| XACK/                                 | Transfer Acknowledge: Indicates that the ad-<br>dress memory location has completed the<br>specified read or write operation. That is, data<br>has been placed onto or accepted from the<br>Multibus connector data lines.                                                                                           |

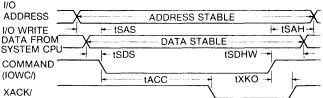

#### MASTER COMMAND ACCESS TIMING

SLAVE COMMAND TIMING

BUS EXCHANGE TIMING

| Parameter                                                               | Nanose<br>Min              |                             | Description                                                                                                                                                                                                   |

|-------------------------------------------------------------------------|----------------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| tDB<br>tSC<br>tXKCO<br>tAH<br>tDHW<br>tDHR<br>tDSX                      | 60<br>50<br>50<br>0        | 61<br>500                   | Busy-to-address/data delay<br>Address/ data set-up to CMD<br>XACK/ to CMD turn off<br>Address hold time<br>Data hold time<br>Read data hold time<br>Data set-up time before XACK/                             |

| tSAS<br>tSDS<br>tSAH<br>tSDHW<br>tACC<br>tXKO                           | 23<br>32<br>36<br>50<br>10 | 77<br>63                    | Address set-up time to I/O CMD<br>Data set-up time to I/O CMD<br>Address hold time from I/O CMD<br>Data hold time from I/O CMD<br>I/O access time<br>XACK/ hold time from I/O CMD                             |

| tBCY<br>tBL<br>tBH<br>tDRQ<br>tDBY<br>tDBYF<br>tDBPN<br>tDBPO<br>tVVAIT | 100<br>35<br>35<br>0       | 655<br>652<br>465<br>7<br>8 | Bus clock cycle time<br>Bus clock low<br>Bus clock high<br>Bus request delay<br>Bus busy turn of delay<br>Priority input set-up time<br>BPRO/ serial delay from BPRN/<br>Requesting master bus access<br>time |

Figure 2-2. Master Command Access Timing

## 2.2.2 Connector Configuration, J1 Through J4

Tables 2–5 through 2–8 show the pin assignments for controller drive connectors J1, J2A, J2B, J3, and J4. These connectors are mounted on the component side of the board with an embossed arrow to indicate pin 1. The odd numbered pins of these connectors are the upper row of pins.

| Table 2-5. Tape Drive Control Connector |

|-----------------------------------------|

|-----------------------------------------|

| Pin Signal                                                                | Description                                                                                                                                                                                                                                     |

|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2,4,6,8,10                                                                | Reserved.                                                                                                                                                                                                                                       |

| 12 HB7/                                                                   | Host Bus Bit 7. MSB of eight-bit bidirec-<br>tional data bus.                                                                                                                                                                                   |

| 14 HB6/<br>16 HB5/<br>18 HB4/<br>20 HB3/<br>22 HB2/<br>24 HB1/<br>26 HB0/ | Bit 6<br>Bit 5<br>Bit 4<br>Bit 3<br>Bit 2<br>Bit 1<br>Bit 0. LSB of eight-bit bidirectional data<br>bus.                                                                                                                                        |

| 28 ONL/                                                                   | On-Line. Control signal to terminate a read/write operation. On-line going false terminates the command and returns tape to beginning of tape (BOT).                                                                                            |

| 30 REQ/                                                                   | Request. User by host to inform controller that a command is on data bus. Also to handshake status information from control-ler to host.                                                                                                        |

| 32 RES/                                                                   | Reset. Used after power up to initialize drive and controller and to recalibrate drive head position.                                                                                                                                           |

| 34 XFER/                                                                  | Transfer. Host handshake signal to transfer<br>data to and from drive. During read opera-<br>tion, XFER going true means host has re-<br>ceived data. During write, XFER going true<br>means host has put data on bus.                          |

| 36 ACK/                                                                   | Acknowledge. Controller handshake signal<br>to transfer data to and from drive. During<br>read, ACK going true means data is avail-<br>able on bus for host. During write, ACK<br>going true means data has been received<br>by the controller. |

| 38 RDY/                                                                   | <ul> <li>Ready. Used by controller for following functions:</li> <li>1. Ready in true state indicates controller can accept new command.</li> <li>2. During command transfer, RDY going true means command has been read.</li> </ul>            |

|                                                                           | <ol> <li>Used to signal asynchronous transfer<br/>of status information from controller<br/>to host.</li> </ol>                                                                                                                                 |

|                                                                           | 4. Used to indicate that a block of data is ready to be transferred.                                                                                                                                                                            |

| 40 EXC/                                                                   | Exception. Used by controller to inform<br>host of a condition which has terminated<br>an operation. When EXC goes true, host<br>must respond with a Read Status<br>Command.                                                                    |

| 42 DIR/                                                                   | Direction. Used by controller to indicate the direction of data flow on data lines. When true, flow of data is from controller to host.                                                                                                         |

| 44,46,48,50                                                               | Reserved                                                                                                                                                                                                                                        |

All odd numbered pins, 1-49, are at signal ground.

Table 2-6. Winchester Drive Control Connector J2A

| lab      | le 2-0. V                | Vinchester Drive Control Connector J2A                                                                                                                                                                 |

|----------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin      | Signal                   | Description                                                                                                                                                                                            |

| 2        | RWC/                     | Reduce Write Current. When true, the lower value of write current is selected.                                                                                                                         |

|          | OR<br>HS2 <sup>3</sup> / | Head Select Line (2 <sup>3</sup> bit) For class 5, or higher, drives not requiring reduced write current.                                                                                              |

| 4        | HS2 <sup>2</sup> /       | Head Select Line (2 <sup>2</sup> bit)                                                                                                                                                                  |

| 14       | HS2 <sup>0</sup> /       | Head Select Line (2 <sup>0</sup> bit)                                                                                                                                                                  |

| 18       | HS2 <sup>1</sup> /       | Head Select Line (2 <sup>1</sup> bit)                                                                                                                                                                  |

| 6        | WG/                      | Write Gate. When true, enables write data<br>to be written to disk. When false, enables<br>transfer of data from drive and enables<br>step pulses to reposition head arm.                              |

| 8        | SKCOMP                   | /Seek Complete. True when heads settled on final track at completion of a seek.                                                                                                                        |

| 10       | TRK000/                  | Track 000. True only when heads are at track zero.                                                                                                                                                     |

| 12       | WTFLT/                   | Write Fault: Indicates drive condition ex-<br>ists that could cause improper writing on<br>disk. Occurs when write current in the<br>head without write gate active or multiple<br>heads are selected. |

| 16       |                          | Reserved.                                                                                                                                                                                              |

| 20       | INDEX/                   | Index. Drive provides this signal once each revolution to indicate beginning of track.                                                                                                                 |

| 22       | RDY/                     | <b>Ready.</b> When true, together with seek complete, indicates drive is ready to read, write, or seek, and that the signals are valid.                                                                |

| 24       | STEP/                    | Step. Causes heads to move in the direc-<br>tion defined by direction in line.                                                                                                                         |

| 26<br>28 | DS1/<br>DS2/             | Drive Select 1-2. When true, connects<br>the selected drive to the control lines.<br>Only one drive select line may be active at<br>a time.                                                            |

| 30,      | 32                       | Reserved.                                                                                                                                                                                              |

| 34       |                          | <b>Direction In.</b> Defines the direction of mo-<br>tion of the heads when step line is pulsed.<br>Direction in true and step line is pulsed,<br>the heads will move toward center of<br>disk.        |

All odd numbered pins, 1-33, are at signal ground.

Table 2-7. Floppy Drive Control Connector J2B

Description

Die

Signal

| Pin      | Signal            | Description                                                                                                                        |

|----------|-------------------|------------------------------------------------------------------------------------------------------------------------------------|

| 2,4      | 4,14,34           | Reserved                                                                                                                           |

| 6        | RDY/              | <b>Ready.</b> When true, indicates drive is ready for read/write operations.                                                       |

| 8        | INDEX/            | Index. Signal provided by drive each time<br>an index hole is sensed by photo detec-<br>tor.                                       |

| 10<br>12 | DS1/<br>DS2/      | Drive Select $1-2$ . When true, connects the selected drive to control lines. Only one drive select line may be active at a time.  |

| 16       | MTR<br>ON/        | Motor On. When true, will turn on drive motor allowing read/write operations.                                                      |

| 18       | DIRC<br>IN/       | Direction In. Defines direction of motion of heads when step line is pulsed.                                                       |

| 20       | STEP/             | Step. Causes heads to move in direction defined by direction in line.                                                              |

| 22       | WR<br>DATA/       | Write Data. This line provides the data to be written on disk.                                                                     |

| 24       | WG/               | Write Gate. When true, allows write data to be written on disk.                                                                    |

| 26       | <b>TRK</b><br>00/ | Track 00. When true, indicates heads are at track zero.                                                                            |

| 28       | WR<br>PROT/       | Write Protect. Signal provided by drive to indicate write protected disk installed.                                                |

| 30       | RD<br>DATA/       | <b>Read Data.</b> This line provides raw data (clock and data together) as detected by the drive electronics.                      |

| 32       | S SEL/            | Side Select. This signal defines which side<br>of a two-sided disk is to be written to<br>or read from. True means side 0 of head. |

All odd numbered pins, 1-33, are at signal ground.

| <b>Table 2–9.</b> Disk Format | ts |

|-------------------------------|----|

|-------------------------------|----|

Table 2-8. Winchester Data Connectors J3 and J4

| Pin | Signal       | Description                                                        |

|-----|--------------|--------------------------------------------------------------------|

| 1   | DS/          | Drive Select. When true, drive is connected to I/O lines.          |

| 13  | +WR<br>DATA/ | +Write Data. Defines bits written to disk.                         |

| 14  | -WR<br>DATA/ | -Write Data. Defines bits written to disk.                         |

| 17  | +RD<br>DATA/ | +Read Data. Data recovered by reading disk.                        |

| 18  | -RD<br>DATA/ | <ul> <li>Read Data. Data recovered by reading<br/>disk.</li> </ul> |

J3 and J4 have identical pinouts and are interchangeable. Pins 2,4,6,8,11, 12,15,16,19, and 20 are at signal ground. Pins 3,5,7,9, and 10 are spares.

#### 2.3 Disk Drive Formats

The Winchester and floppy disk drives operate with all standard iSBC 215 sector sizes. These include the 128, 256, 512, and 1024 bytes per sector formats. The floppy disks handle standard formats, single-density (128 to 1024 bytes per sector) and double-density (256 to 1024 bytes per sector), including double-sided. See Table 2–9. This flexibility enables the user to copy programs from one format to another using the Winchester as intermediate storage.

|                                                        | Physical            | Index —                          | <b></b>              |                | 1           |                      |                      |                       |                          |                  |                  |                           |                       |                          |

|--------------------------------------------------------|---------------------|----------------------------------|----------------------|----------------|-------------|----------------------|----------------------|-----------------------|--------------------------|------------------|------------------|---------------------------|-----------------------|--------------------------|

|                                                        |                     |                                  | G1                   | P1             | IAM         | G2                   | P2                   | ID                    | G3                       | Р3               | DAM<br>DDAM      | DATA                      | G4                    | G5                       |

| Single-Density                                         | Sectors/<br>Track   | Bytes/<br>Sector                 | FF                   | 00             | FC/DC       | FF                   | 00                   |                       | FF                       | 00               | FB/C7<br>F8/C7   |                           | FF                    | FF                       |

| IAM=FC/D7<br>IDAM=FE/C7<br>DAM=FB/C7<br>DDAM=F8/C7     | 15<br>8<br>4<br>2   | 128<br><b>256</b><br>512<br>1024 | 40<br>40<br>40<br>40 | 6<br>6<br>6    | 1<br>1<br>1 | 26<br>26<br>26<br>26 | 6<br>6<br>6          | 7<br>7<br>7<br>7<br>7 | 1 1<br>1 1<br>1 1<br>1 1 | 6<br>6<br>6<br>6 | 1<br>1<br>1      | 130<br>258<br>514<br>1026 | 27<br>42<br>58<br>170 | 232<br>404<br>640<br>598 |

|                                                        |                     |                                  |                      |                |             |                      |                      |                       |                          | Rep              | eat              |                           |                       | Total 31                 |

| Double-Density                                         |                     |                                  | 4E                   | 00             |             | 4E                   | 00                   |                       | 4E                       | 00               |                  |                           | 4E                    | 4E                       |

| IAM=3(C2/14),FC<br>IDAM=3(A1/0A),FE<br>DAM=3(A1/0A),FE | 4                   | 256<br>512<br>1024               | 80<br>80<br>80       | 12<br>12<br>12 | 4<br>4<br>4 | 50<br>50<br>50       | 12<br>12<br>12       | 10<br>10<br>10        | 22<br>22<br>22           | 12<br>12<br>12   | 4<br>4<br>4      | 258<br>514<br>1026        | 54<br>80<br>116       | 524<br>872<br>1296       |

| DDAM=3(A1/0A),F<br>*IBM Personal                       | Computer            | Format                           |                      |                |             |                      |                      |                       |                          | Rep              | eat              |                           |                       | Total 62                 |

| Winchester                                             |                     |                                  |                      |                |             | 4E                   | 00                   |                       | 4E                       | 00               |                  |                           | 4E                    | 4E                       |

| IDAM=A1/0A,FE<br>DAM=A1/0A,FB<br>DDAM=A1/0A,F8         | 54<br>31<br>17<br>9 | 128<br>256<br>512<br>1024        |                      |                |             | 4<br>4<br>4          | 12<br>12<br>12<br>12 | 10<br>10<br>10<br>10  | 3333                     | 6<br>6<br>6<br>6 | 2<br>2<br>2<br>2 | 132<br>260<br>516<br>1028 | 21<br>30<br>44<br>61  | 368<br>399<br>331<br>314 |

|                                                        |                     |                                  |                      |                |             |                      |                      |                       |                          | Repe             | eat              |                           |                       | Total 10                 |

Write to read recovery time left in addition to a six percent drive speed tolerance gap: 128: 20  $\mu$ s; 256: 22  $\mu$ s; 512: 20  $\mu$ s; 1024: 0  $\mu$ s.

# 2.4 Drive Characteristics

One method of classifying Winchester and floppy drives is according to control timing sequence, precompensation requirements, and for Winchester drives only, requirements for reduced write current.

Tables 2-10 and 2-11 show characteristics of Winchester and floppy drives respectively with some drives grouped according to the indicated characteristics. Not all drives are listed, only a representative selection to show examples of drives matched to chosen characteristics. Contact the factory for correct jumper configuration for higher performance Winchester drives not listed.

These tables will be referred to again in Chapter 3, to show required board jumper settings for drive groups listed.

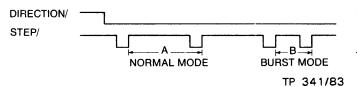

WINCHESTER CONTROL TIMING/PRECOMP/READ WRITE CURRENT

Table 2-10. Winchester Drive Characteristics

| Drive<br>Class | STEP/<br>Normal<br>A | STEP/<br>Burst<br>B | Precomp<br>12 ns<br>Cylinders | Reduced<br>Write<br>Current<br>Cylinders |

|----------------|----------------------|---------------------|-------------------------------|------------------------------------------|

| 0              | 3 ms                 | 25 μs               | ≥128                          | ≥128                                     |

| 1              | 3 ms                 | 25 μs               | ≥77                           | ≥77                                      |

| 2              | 2 ms                 | 25 μs               | ≥0                            | ≥132                                     |

| 3              | 3 ms                 | 25 μs               | ≥0                            | ≥96                                      |

| 4              | 3 ms                 | 3 ms                | ≥128                          | ≥128                                     |

| 5              | 3 ms                 | 10.8 µs             | none                          | none                                     |

| 6              | 3 ms                 | 10.8 µs             | ≥320                          | none                                     |

| 7              | 3 ms                 | 10.8 µs             | ≥256                          | none                                     |

| Drive<br>Class | Typical Drive Types                 |

|----------------|-------------------------------------|

| 0              | ST412; SA602, 604, 606;             |

|                | Tandon 602, 603, CDC 9415-21-5      |

|                | CMI CM5206, 5412                    |

| 1              | RMS 503, 506, 512                   |

| 2              | PYXIS 7, 13, 20, 27 (Rodine)        |

| 3              | PYXIS 4, 8, 12, 16 (Ampex)          |

| 4              | ST506                               |

| 5              | Et 5510, 5520, 5530, 5540; XT-1065, |

|                | 1105, 1140; V130, V150, V170        |

| 6              | 3020, 3033, 3046 (Atasi)            |

| 7              | Q-500 (Quantum)                     |

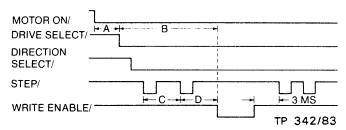

FLOPPY CONTROL TIMING/PRECOMP

| Table | 2-11.  | Floppy  | Drive | Characteristics  |

|-------|--------|---------|-------|------------------|

|       | £ 1,1. | i ioppy |       | 0112120101131103 |

| Drive<br>Class   | Motor<br>On                             | Head<br>Load            | Step<br>Settle        | Seek<br>Settle          | Precomp<br>160 ns |

|------------------|-----------------------------------------|-------------------------|-----------------------|-------------------------|-------------------|

|                  | А                                       | В                       | С                     | D                       |                   |

| 0<br>1<br>2<br>3 | 250 ms<br>500 ms<br>1500 ms<br>Reserved | 50 ms<br>50 ms<br>75 ms | 3 ms<br>6 ms<br>30 ms | 15 ms<br>15 ms<br>50 ms | None<br>*<br>*    |

| Drive<br>Class | Typical Drive Types                    |

|----------------|----------------------------------------|

| 0              | Mitsubishi M4853; Tandon TM100-3, -4   |

| 1              | CDC 9409-T; Tandon TM100-1,-2;         |

|                | Shugart SA410, SA460; MPI 51, 52       |

| 2              | Pertec FD200, 250; Shugart SA400, 450; |

|                | BASF 6106, 6108;                       |

|                | Micropolis 1015 I, II, III, IV, V, VI; |

|                | Qumetrak 592; TEAC 50A, 50C, 50F       |

| 3              | Reserved                               |

\*If cylinder  $\geq 1/2$  (total) +4

# **3 INSTALLATION**

## 3.1 Introduction

This chapter contains information on unpacking, inspection, configuration, and initial checkout of the DSD Multibus Disk Controller.

## 3.2 Unpacking and Inspection

When the DSD Controller arrives, inspect the shipping container immediately for evidence of mishandling during transit. If the container is damaged, request that the carrier's agent be present when the package is opened. Compare the packing list attached to the shipping container against your purchase order to verify the shipment is correct.

Unpack the shipping container and inspect each item for external damage such as broken controls and connectors, or scratches and loose components. If damage is evident, notify DSD Customer Service immediately.

Retain the shipping container and packing materials for examination in the settlement of claims, or for future use.

## 3.3 Installation

The controller board may be installed in any Multibus-compatible backplane that meets the power and cooling requirements specified in Chapter 2. Note that power **MUST** be **OFF** when installing or removing controller board.

Up to two floppies and two Winchesters may be connected to the controller (see Figure 2-1).

Note

*Terminators must be installed in last floppy drive and last Winchester drive.*

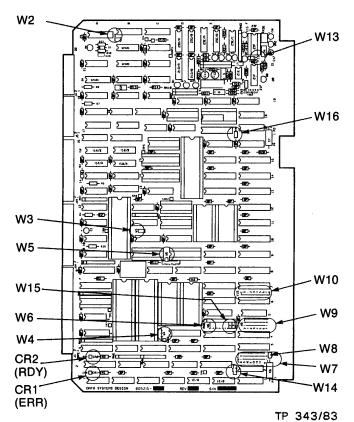

# 3.4 Jumper Options

Jumper options allow the user to tailor the installation to the requirements of his particular system. Figure 3-1 shows jumper locations and pin configuration of each jumper on the controller board.

Normally, jumper options are exercised by placing a Berg mini-jumper on the indicated pins. The exception to this is jumper W10. It is wire-wrapped at the factory because the physical layout of the pins precludes the use of the mini-jumpers.

## 3.4.1 Jumper Configurations

Tables 3-1 and 3-2 summarize the DSD Controller jumper configuration installed at the factory. Table 3-1 covers all board jumpers except W6, W7, and W9. These jumpers are of slightly different configuration and are described in Tables 3-2, 3-3, and 3-4. Jumpers W2, W4, and W13 are for factory use only, and should not be changed in the field. User should note that there are no jumpers labelled W1, W11, or W12 on the board.

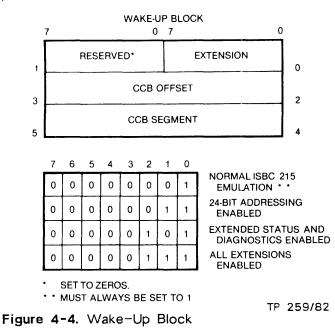

Jumper groups W7 and W9 (Table 3-2) select the 8-or 16-bit I/O port address. This address is logically related to the memory address of the wake up block. Refer to paragraphs 4.5.4 and 4.5.5 for details on address selection. W-9 contains the low order bits (0 to 7) and W7 the high order bits (8 to 15) of the WUA jumper setting. These bits are set at the factory to 0F70 hex.

Jumper W6 provides options for selection of types of drives supported by the controller (See Table 3-3 and 3-4). It is also used to select off-line diagnostic testing. Refer to Chapter 6 for using W6 Jumper group with off-line HyperDiagnostics.

| Table 3-1. Jumper | Configurations |

|-------------------|----------------|

|-------------------|----------------|

| Jumper | Function                                      | Factory S<br>Pins IN                                   | etting<br>OUT                         | Options                                                                                                                                                                                       | Remarks                                                                                               |

|--------|-----------------------------------------------|--------------------------------------------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| W2     | Factory Use Only                              | 1-2 X                                                  |                                       | None.                                                                                                                                                                                         | Leave as set.                                                                                         |

| W3     | Byte- or Word-Size<br>Data Transfers          | 1-2                                                    | х                                     | Byte-size data bus selected.<br>IN selects 16-bit data bus.                                                                                                                                   | User option.                                                                                          |

| W4     | Factory Use Only                              | 1-2 X<br>3-4 X                                         |                                       | None.                                                                                                                                                                                         | Leave as set.                                                                                         |

| W5     | Bus Arbitration<br>Mode Select                | 1-2 X<br>2-3<br>2-4<br>5-6                             | x<br>x<br>x                           | Yield to higher priority mode.<br>IN= yield to any request mode.<br>IN= single-transfer mode.<br>1-2 and 5-6 IN = override mode.                                                              | User option.<br>Except for override mode,<br>only one jumper at a time is IN.<br>See Paragraph 3.4.3. |

| W8     | Serial or Parallel Bus<br>Priority Continuity | 1-2 X                                                  |                                       | Serial bus priority scheme selected.<br>OUT= parallel bus priority scheme.                                                                                                                    | User option.                                                                                          |

| W10    | Interrupt Priority<br>Level Select            | C-0<br>C-1<br>C-2<br>C-3<br>C-4<br>C-5 X<br>C-6<br>C-7 | × × × × × × × × × × × × × × × × × × × | Priority level 0 (Highest)<br>Priority level 1<br>Priority level 2<br>Priority level 3<br>Priority level 4<br>Priority level 5 (Factory Set)<br>Priority level 6<br>Priority level 7 (Lowest) | User option.<br>Factory set at level 5.<br>Factory wire-wrapped.<br>User may change as required.      |

| W13    | Factory Use Only                              | 1-2 X                                                  |                                       | None.                                                                                                                                                                                         | Leave as set.                                                                                         |

| W14    | 8- or 16-Bit I/O<br>Address Select            | 1-2<br>2-3 X                                           | x                                     | 8-bit I/O addressing selected.<br>Reverse selects 16-bit.                                                                                                                                     | User option. Jumpers 1-2 IN,<br>2-3 OUT selects 16-bit addr.                                          |

| W15    | Factory Set                                   | A X<br>B                                               | ×                                     | None.                                                                                                                                                                                         | Leave as set.                                                                                         |

| W16    | Factory Set                                   | x                                                      | x                                     | 5215-01/03 Version (ECC)<br>5215-02 Version only (CRC)                                                                                                                                        | Leave as set.                                                                                         |

For jumper groups W6, W7, and W9 see page 3-3. Jumpers W1, W11, W12 are not physically present on the 5215 board.

Table 3-2. W7 and W9 WUA Jumper Configurations

| Jumper                                                                         | Factory<br>Pins      | Settin<br>1      | 9<br>0                | Hex<br>Setting |

|--------------------------------------------------------------------------------|----------------------|------------------|-----------------------|----------------|

| W9 sets least significant<br>eight bits to be converted<br>to wake-up address. | 0<br>1<br>2<br>3     |                  | X<br>X<br>X<br>X<br>X | LSB<br>0       |

|                                                                                | 4<br>5<br>7          | X<br>X<br>X      | x                     | 7              |

| W7 sets most significant<br>eight bits to be converted<br>to wake-up address.  | 8<br>9<br>10<br>11   | ×<br>×<br>×<br>× |                       | F              |

|                                                                                | 12<br>13<br>14<br>15 |                  | ×<br>×<br>×           | MSB<br>0       |

Address Example: The 16-bit WUA jumper setting (W7 and W9) = 0F70H multiplied by 16 gives the 20-bit Multibus address of WUB = 0F700H. The 8-bit I/O port address = 70H. Optionally, the 16-bit I/O port address = 0F70H.

Figure 3-1. Jumper Locations

#### 3.4.2 Jumper Group W6 Configuration

In Chapter 2, Table 2–10, Winchester drives were classified according to timing control characteristics. Here, these same classifications will be related to jumper group W6 for drive type selection.

The DSD 5215 Controller will handle up to two Winchester drives that are compatible with an ST506 interface. See Table 2–10. If your drive is listed, set jumper W6 as follows in Table 3–3. If your drive is not listed, attempt to match it with classes shown in the table, or call Customer Service for assistance.

| Table | 3-3. | W6 | Jumper | Configurations, | Winchester |

|-------|------|----|--------|-----------------|------------|

|-------|------|----|--------|-----------------|------------|

| Winchester  | Ju   | nper Group W6 | W6   |

|-------------|------|---------------|------|

| Drive Class | W6-4 | W6-3          | W6-2 |

| 0           | IN   | IN            | IN   |

| 1           | IN   | IN            | OUT  |

| 2           | IN   | OUT           | IN   |

| 3           | IN   | OUT           | OUT  |

| 4           | OUT  | IN            | IN   |

| 5           | OUT  | IN            | OUT  |

| 6           | OUT  | OUT           | IN   |

| 7 Reserved  | OUT  | OUT           | OUT  |

W6-5, normally installed, selects HyperDiagnostics when removed.

Table 2–11, Chapter 2, classifies 5-1/4 inch floppy drives according to control timing characteristics. These classifications are related to jumper group W6 for proper drive type selection in Table 3–4.

The DSD 5215 Controller can handle up to two floppy disk drives compatible with an SA460 interface. See Table 2–11. If your drive is listed, set jumper group W6 as follows. If your drive type is not listed, attempt to match it with classes shown in the table, or call Customer Service for assistance.

| Table | 3-4. | W6 | Jumper | Configurations, | Floppy |

|-------|------|----|--------|-----------------|--------|

|-------|------|----|--------|-----------------|--------|

| Floppy      | Jumper | Group W6 |

|-------------|--------|----------|

| Drive Class | W6-1   | W6-0     |

| 0           | IN     | IN       |

| 1           | IN     | OUT      |

| 2           | OUT    | IN       |

| 3 Reserved  | OUT    | OUT      |

# **3.4.3 Bus Arbitration Modes**

The following bus arbitration mode options are placed in order of increasing throughput and decreasing bus availability. The bus, acquired on the basis of availability, is always released at the end of burst transfer. Maximum burst length is one full sector per bus grant.

- Single-Transfer: Control of the Multibus is acquired before each data transfer and released immediately after. This minimizes controller time on the bus, but compromises maximum throughput capability.

- Yield to Any Request: The bus is released for any request, regardless of priority, through use of the CBRQ signal, or when the transfer of a block of data is completed. This allows maximum throughput capability only when other bus masters do not want to use the bus.

- Yield to Higher Priority: The bus is released only for higher priority requests, or when the transfer of a block of data is completed. This allows maximum throughput capability only when higher priority bus masters do not want to use the bus.

- Override: Higher priority bus master requests are overridden. The bus is released only at the end of data transfer. This guarantees maximum throughput performance.

# 3.4.4 Drive Jumpering

Information concerning jumper operations on the disk or tape drive controller cards is contained in Appendix A. All drives must be jumpered to ensure proper operation, and terminators **MUST** be installed in the last Winchester and last floppy disk drive connected to the DSD Controller. Drive mapping tables are provided for the following type drives:

- Winchester: ST412

- Floppy: SA460

# 3.5 Initial Checkout and Acceptance Tests

Two LEDs, at board positions A1 and A3 (upper left corner), respond according to board option settings and error condition. LED CR2 (RDY) indicates whether the board is ready to accept a new command (ON), or is busy (OFF). LED CR1 (ERR) is active when an error is detected. These indicators, after a reset condition, indicate if the board is performing properly. Normal indicator sequence is shown in Table 3-5.

| Sequence                                          | Power | CR 1<br>(ERR)                | CR2<br>(RDY)            | Remarks                                  |

|---------------------------------------------------|-------|------------------------------|-------------------------|------------------------------------------|

| During a Reset,<br>Multibus INIT/<br>or Power Up: | ON    | ON<br>X                      | ON<br>X                 | Good<br>Bad<br>Board                     |

| After Reset:<br>(During<br>Self-Test)             | ON    | OFF<br>ON                    | ON<br>ON                | Good<br>Self-Test<br>Failure             |

| While Running:                                    | ON    | OFF<br>OFF<br>ON<br>Blinking | ON<br>OFF<br>OFF<br>OFF | Ready<br>Busy<br>Not Valid<br>Error Code |

When self-test is complete, CR2 (RDY) will be ON. If CR1 (ERR) is OFF, self-test was successful and the board is ready to receive a new command. If CR1 (ERR) is blinking on and off, a recognized error is indicated. Refer to Chapter 6 for fault analysis procedures.

# 3.5.1 Test and Verification

Up to this point, no other Multibus cards have been required, only power. The user may further verify system operation using off-line diagnostics to check that all peripherals are operational. These tests are selected using jumper W6, refer to Section 6 for information on tests and jumper reconfiguration.

# 4 PROGRAMMING

#### 4.1 Introduction

This chapter describes the programming conventions that must be followed to initiate and monitor the transfer of data between the host memory and a disk drive. Included are discussions of disk organization and track formats, host/controller communications, command descriptions, and error processing.

# 4.2 Winchester Disk Organization

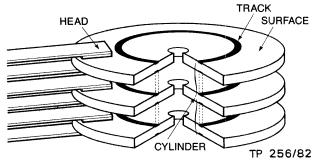

In the following discussion, a head is assumed to be associated with a single disk surface. Each surface can have up to 4096 tracks (circular data paths numbered 0 through 4095). The set of tracks on multiple recording surfaces at a given head position is referred to as a cylinder (See Figure 4–1). A drive that has 4096 tracks per surface also has 4096 cylinders.

Figure 4-1. Winchester Disk Organization

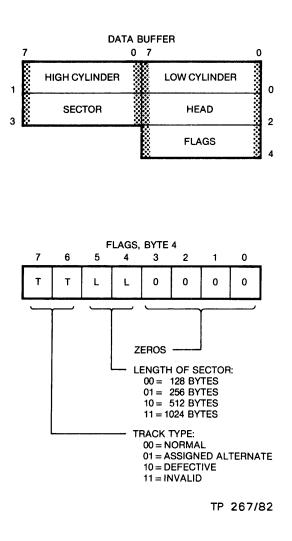

Each track is divided into equal sized sectors. Each sector includes a sector identification block with error checking information and a data block with error checking information. The controller allows the user to select the size of the data block. The size of the data block determines the maximum number of sectors permitted per track (Refer to Chapter 2).

The controller generates the format of the sector identification block and the error checking fields of each sector of the disk, one track at a time.

## 4.3 Floppy Disk Organization

The floppy disk drives use standard IBM single- or double-sided media. The formats supported are single-density (128 to 1024 byte sectors), and double-density (256 to 1024 byte sectors).

# 4.4 Streaming Tape Organization

Data are recorded on this drive in 512 byte blocks. The track selection is transparent to the host, and is accomplished by the internal controller unit.

#### 4.5 Issuing Commands and Receiving Status

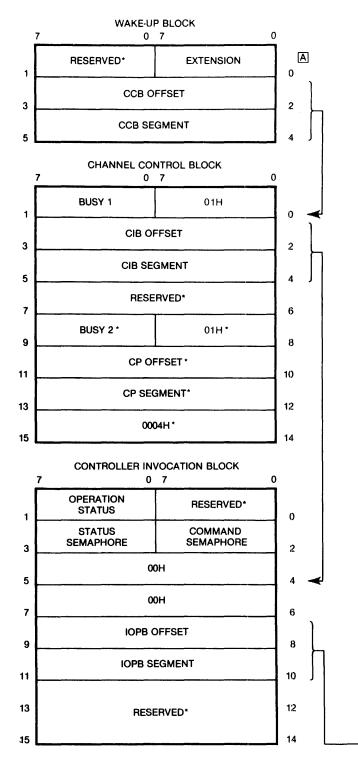

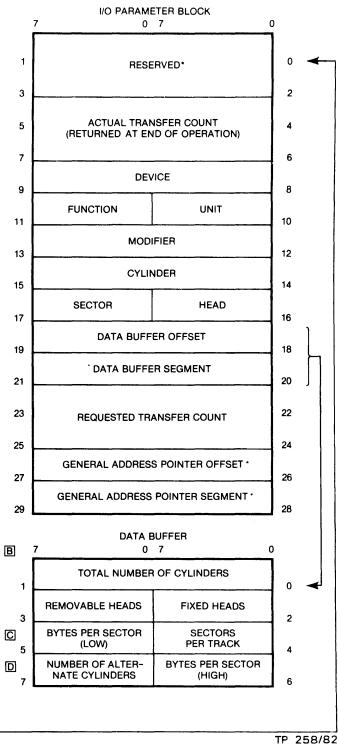

The main channel of communication is the memory-based tables. The protocol for issuing commands and receiving status is simple, straight-forward, and essentially constant for all commands. Put controller into reset condition, set up the WUB, CCB, and CIB as required, issue clear and start commands, and wait for not busy. For any subsequent command: set up the CCB, CIB, and IOPB for command, issue start command and wait for interrupt or poll status semaphore. These steps are detailed as follows:

- A Put Controller Into Reset Condition: Issuing a programmed I/O reset command clears pending interrrupts and applies a hardware reset to the controller hardware. All drives are deselected. Disk writes in process are terminated. Floppy heads are unloaded.

- B Set WUB, CCB, and CIB as Required: The wake-up block is set up, pointing to the CCB. The channel control block is set up, pointing to the CIB and finally, the controller invocation block is set up. The status sema-phore byte in the CIB is cleared by the host to 00H. The busy flag in the CCB is set by the host to FFH.