# VAX/VMS Internals and Data Structures

LAWRENCE J. KENAH & SIMON F. BATE

### **VAX/VMS Internals and Data Structures**

# VAX/VMS Internals and Data Structures

LAWRENCE J. KENAH SIMON F. BATE

Copyright 1984 by Digital Equipment Corporation.

All rights reserved. Reproduction of this book, in whole or in part, is prohibited. For information, write Digital Press, Educational Services, Digital Equipment Corporation, Bedford, Massachusetts.

The painting reproduced on the front cover is "From Red to Violet" [1970, oil on canvas] by Hannes Beckmann, courtesy of the DeCordova Museum Collection: Gift of Mr. Michael F. Lynch.

DEC, DECnet, UNIBUS, VAX, and VMS are trademarks of Digital Equipment Corporation.

Designed by David Ford.

Automatically typeset utilizing a VAX-11/780 by York Graphic Services, Incorporated.

Printed in U.S.A. by Halliday Lithograph.

Order number EY-00014-DP.

#### Library of Congress Cataloging in Publication Data

Kenah, Lawrence J., 1946– VAX/VMS internals and data structures.

Includes index.

1. VAX/VMS (Computer operating system) 2. VAX-11 (Computer)—Programming. 3. Data structures (Computer science) I. Bate, Simon. II. Title. III. Title: V.A.X./V.M.S. internals and data structures. QA76.6.K454 1984 001.64'2 83-26187 ISBN 0-932376-52-5

#### **Preface**

This book explains how the VAX/VMS executive works. It describes the data structures maintained and manipulated by the VMS operating system, discusses the mechanisms that transfer control between user processes and the VMS operating system (and among the components of the operating system itself), and describes some of the features of the VAX hardware as they are used by the VMS operating system. It also describes the VMS executive, including all the major components of the executive, as well as system initialization and the operation of all system services. It does not include a general discussion of the I/O subsystem, because that subject is already described in the *VAX/VMS Guide to Writing a Device Driver* (Digital Equipment Corporation, 1982). However, the details of some VAX/VMS device drivers, as well as the operations of I/O-related system services are included in this book.

This book is intended for system programmers and other users of the VAX/VMS operating system who wish to understand the internal workings of the executive. The detailed description of data structures should help system managers make better informed decisions when they configure systems for space-or time-critical applications. It will also help application designers to appreciate the effects (in speed or in memory consumption) of different design and implementation decisions. This book assumes that the reader is familiar with the VAX architecture and the VMS operating system, particularly with its use of system services and its techniques of memory management.

In explaining the operation of a subsystem of the executive, this book emphasizes the data structures manipulated by that component, rather than detailed flow diagrams of major routines.

This book differs from the reference manuals that make up the VAX/VMS documentation set in that it describes internal operations and data structures. While it is unlikely that any component described in this book will be drastically changed with any major release of the VAX/VMS operating system, there is no guarantee that a particular data structure or subroutine described here will remain the same from release to release. With each new version of the operating system, privileged application programs that rely on details contained in this book must be tested before they are used for production work with a standard load of users.

This book is divided into nine parts, each of which describes a different aspect of the operating system.

Part 1 presents an overview of the VAX/VMS operating system and reviews those concepts that are crucial to understanding the workings of that system.

- Part 2 describes the mechanisms used to pass control between user programs and the operating system and within the VMS system itself.

- Part 3 describes scheduling and timer support, concluding with a discussion of the internals of the VAX/VMS lock manager.

- Part 4 discusses memory management.

- Part 5 describes the I/O subsystem.

- Part 6 describes the creation and deletion of a process and the activation and termination of an image in the context of a process.

- Part 7 deals with system initialization and also includes a discussion on the VAX-11/782.

- Part 8 discusses miscellaneous topics that are not conveniently classified in any conventional catalog of operating systems:

- —The implementation of logical names

- —The functions of miscellaneous system services

- —The use of listing and map files

- —The conventions used in naming symbols

- Part 9 provides information on VMS data structures.

Most of the operations of the VMS executive can be easily understood once the contents of the various data structures are known. Although selected structures are described throughout the book, Appendix B describes (or provides pointers to) all the structures used by the operating system. The structures related to device drivers and the file system are not described. The data structures related to device drivers are described in the VAX/VMS Guide to Writing a Device Driver. Data structures specific to the file system have yet to be documented.

Several documents in the VAX/VMS document set supply important background information for the topics discussed in this book. The following provide an especially valuable foundation: VAX/VMS System Services Reference Manual, the VAX-11 software installation guides, and the chapter in the VAX-11 Run-Time Library Reference Manual that describes condition handling.

The concepts underlying the operating system are discussed in the VAX/VMS Summary Description and Glossary, and the VAX Software Handbook. The following documents are also helpful references: the VAX/VMS Guide to Writing a Device Driver, the VAX-11 Architecture Reference Manual, and the VAX Hardware Handbook.

An excellent description of the VAX architecture, as well as a discussion of some of the design decisions made for its first implementation, the VAX-11/780, can be found in *Computer Programming and Architecture: The VAX-11* by Henry M. Levy and Richard H. Eckhouse, Jr. (Digital Press, 1980). This

book also contains a bibliography of some of the literature dealing with operating system design.

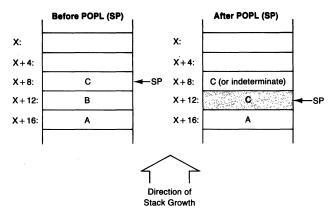

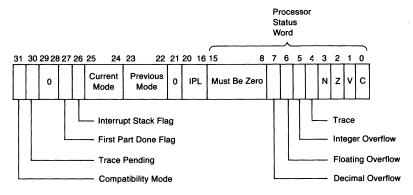

The reader should be aware of several conventions used throughout this book. In all diagrams of memory, the lowest virtual address appears at the top of the page and addresses increase toward the bottom of the page. This convention means that the direction of stack growth is toward the top of the page. In diagrams that display more detail, such as bytes within longwords, addresses also increase from right to left. That is, the lowest addressed byte (or bit) in a longword is on the righthand side of a figure and the most significant byte (or bit) is on the lefthand side.

The words "system" or "VMS system" are used to describe the entire software package that is a part of a VAX-11 system, including privileged processes, utilities, and other support software as well as the executive itself.

The word "executive" refers to those parts of the VMS operating system that reside in system virtual address space. The executive includes the contents of the file SYS.EXE, device drivers, and other code and data structures loaded at initialization time, including RMS and the system message file.

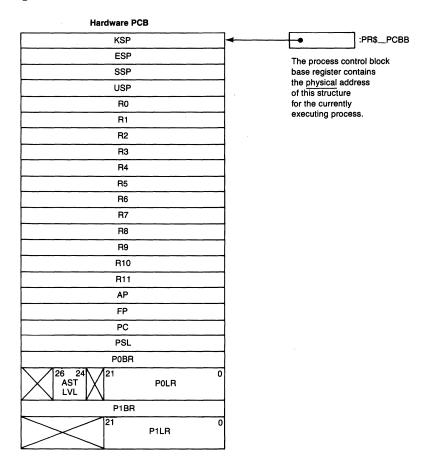

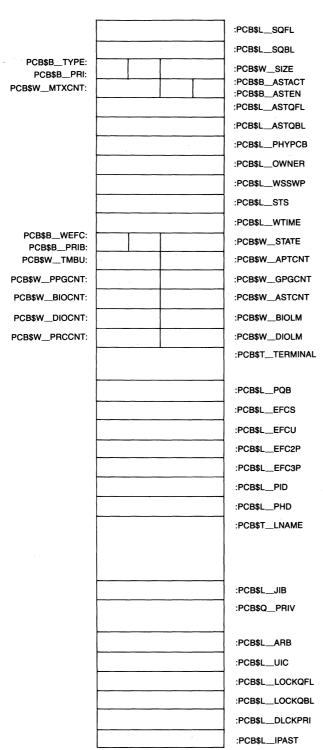

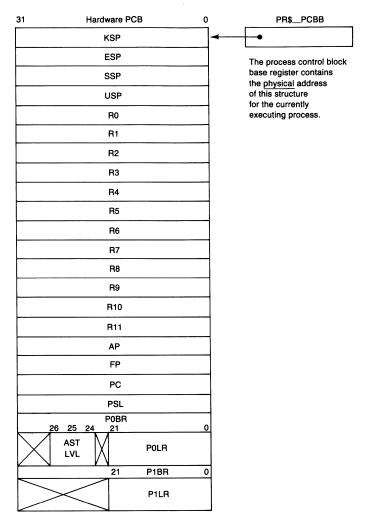

When either "process control block" or "PCB" is used without a modifier, it refers to the software structure used by the scheduler. The data structure that contains copies of the general registers (that the hardware locates through the PR\$\_PCBB register) is always called the "hardware PCB."

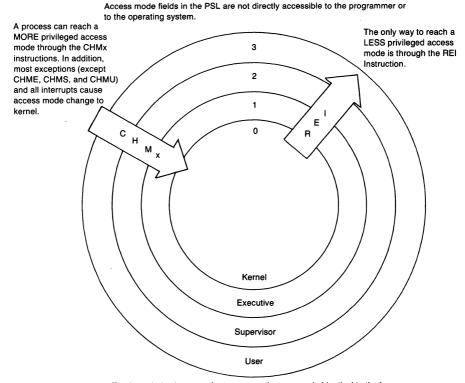

When referring to access modes, the term "inner access modes" means those access modes with more privilege. The term "outer access modes" means those access modes with less privilege. Thus, the innermost access mode is kernel and the outermost access mode is user.

The term "SYSBOOT parameter" is used to describe any of the adjustable parameters that are used by the secondary bootstrap program SYSBOOT to configure the system. The adjustable parameters include both the dynamic parameters that can be changed on the running system and the static parameters that require a reboot in order for their values to change. These parameters are referred to by their parameter names rather than by the global locations where their values are stored. Appendix A relates the SYSBOOT parameter names to their corresponding global locations.

The terms "byte index," "word index," "longword index," and so on, refer to a method of access that uses the VAX-11 context indexing addressing capability. That is, the index value will be multiplied by one, two, four, or eight (depending on whether a byte, word, longword, or quadword is being referenced) as part of operand evaluation in order to calculate the effective address of the operand.

In general, the component called INIT refers to a module of that name in the executive and not the volume initialization utility. When that utility program is being referenced, it will be clearly specified. Three conventions are observed for lists.

- In lists such as this one, where there is no order or hierarchy, list elements

are indicated by leading bullets (•). Sublists without hierarchy are indicated by dashes (—).

- Lists that indicate an ordered set of operations are numbered. Sublists that indicate an ordered set of operations are lettered.

- Numbered lists with the numbers enclosed in circles indicate a correspondence between individual list elements and numbered items in a figure.

#### **ACKNOWLEDGMENTS**

Our first thanks must go to Joe Carchidi, for suggesting that this book be written, and to Dick Hustvedt, for his help and enlightening conversations.

We would like to thank John Lucas for putting together the initial versions of Chapters 7, 10, 11, and 30 and Vik Muiznieks for writing the initial versions of Chapters 5, 18, and 19.

Appreciation goes to all those who reviewed the drafts for both editions of the book (VAX/VMS Version 2.2 and 3.3). We would particularly like to thank Kathy Morse for reviewing the first edition in its entirety and Wayne Cardoza for reviewing the entire second edition. Our special thanks go to Ruth Goldenberg for reviewing both editions in their entirety, and for her many corrections, comments, and suggestions.

We owe a lot of thanks to our editing staff, especially to Jonathan Ostrowsky for his labors in preparing the first edition, and Betty Steinfeld for her help and suggestions. Many thanks go to Jonathan Parsons for reviewing and editing the second edition, and for all his help, patience, and suggestions.

We would like to thank the Graphic Services department at Spitbrook, particularily Pat Walker for her help in paging and production of the first edition, and Paul King for his help in transforming innumerable slides and rough sketches into figures. Thanks go to Kathy Greenleaf and Jackie Markow for converting the files to our generic markup language.

Thanks go to Larry Bohn, Sue Gault, Bill Heffner, Kathleen Jensen, and Judy Jurgens for their support and interest in this project.

Finally, we would like to thank all those who originally designed and implemented the VAX/VMS operating system, and all those who have contributed to later releases.

Lawrence J. Kenah Simon F. Bate August 1983

| PART I/Introduction |                                                               | 2.1.2 | Other IPL Levels Used for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------|---------------------------------------------------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| _                   |                                                               |       | Synchronization 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1                   | System Overview 3                                             | 2.1.3 | IPL\$_QUEUEAST 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1.1                 | Process, Job, and Image 3                                     | 2.1.4 | IPL 2 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1.1.1               | Process 3                                                     | 2.2   | Serialized Access 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1.1.2               | Image 5                                                       | 2.2.1 | Fork Processing 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1.1.3               | Job 6                                                         | 2.2.2 | I/O Postprocessing 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

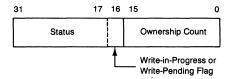

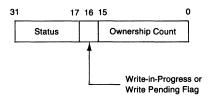

| 1.2                 | Functionality Provided By VAX/VMS 6                           | 2.3   | Mutual Exclusion Semaphores (Mutexes) 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1.2.1               | Operating System Kernel 6                                     | 2.3.1 | Locking a Mutex for Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1.2.3               | User Interface 9                                              |       | Access 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1.2.4               | Interface among Kernel Subsystems 11                          | 2.3.2 | Locking a Mutex for Write<br>Access 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1.3                 | Hardware Implementation                                       | 2.3.3 | Mutex Wait State 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                     | of the Operating System                                       | 2.3.4 | Unlocking a Mutex 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                     | Kernel 13                                                     | 2.3.5 | Resource Wait State 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1.3.1               | VAX Architecture Features Exploited by VMS 13                 | 2.4   | VAX/VMS Lock Management<br>System Services 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1.3.2               | VAX-11 Instruction Set 14                                     |       | and the second of the second o |

| 1.3.3               | Implementation of VMS Kernel Routines 15                      | 2     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1.3.4               | Memory Management and Access Modes 19                         | 3     | Dynamic Memory Allocation 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

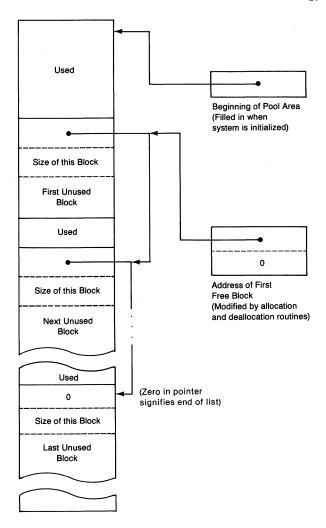

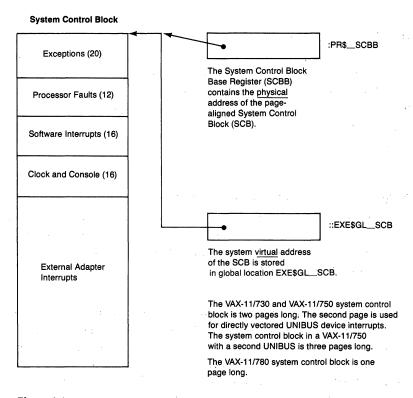

| 1.3.5               | Exceptions, Interrupts, and REI 20                            | 3.1   | Allocation Strategy and<br>Implementation 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 1.3.6               | Process Structure 21                                          | 3.1.1 | Allocation of Dynamic  Memory 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

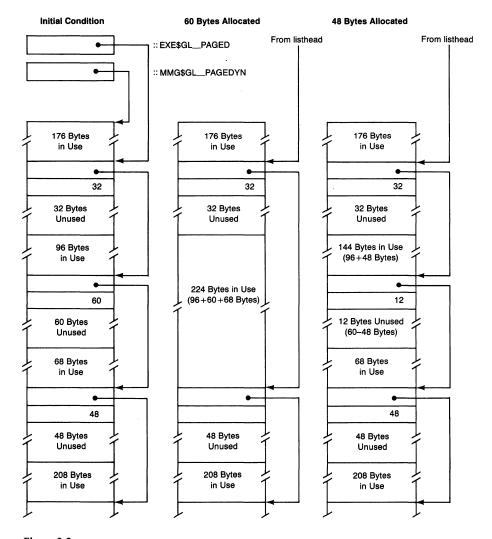

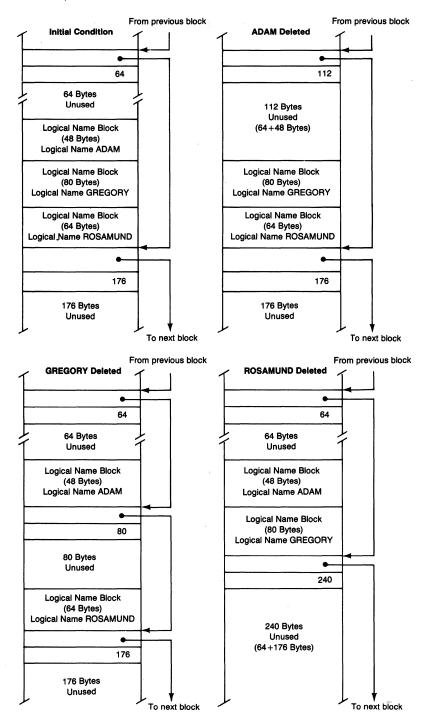

| 1.4                 | Other System Concepts 22                                      | 3.1.2 | Example of Allocation of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1.4.1               | Resource Control 22                                           | 0.1.2 | Dynamic Memory 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1.4.2<br>1.5        | Other System Primitives 23 Layout of Virtual Address Space 24 | 3.1.3 | Deallocation of Dynamic<br>Memory 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

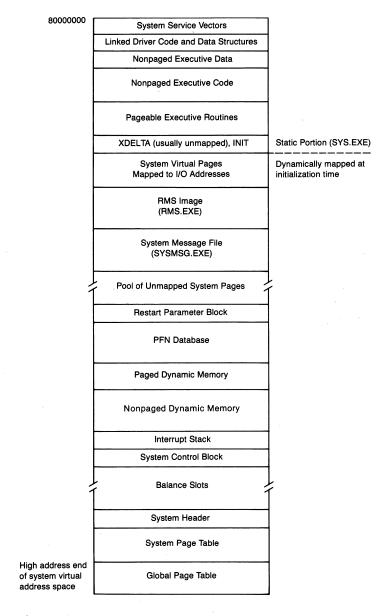

| 1.5.1               | System Virtual Address Space 24                               | 3.1.4 | Example of Deallocation of<br>Dynamic Memory 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

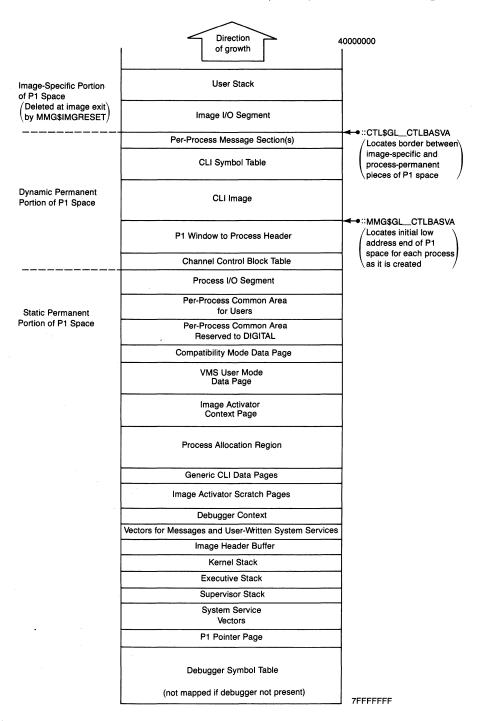

| 1.5.2               | The Control Region (P1                                        | 3.1.5 | Synchronization 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1.0.2               | Space) 26                                                     | 3.1.6 | Granularity of Allocation 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

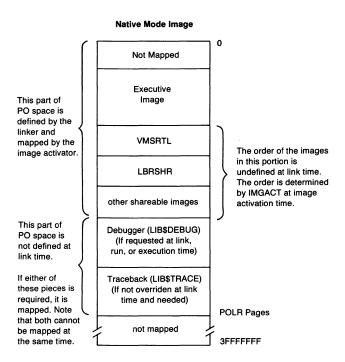

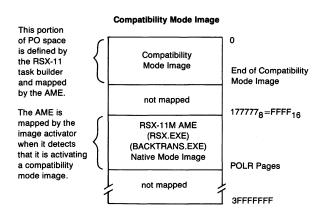

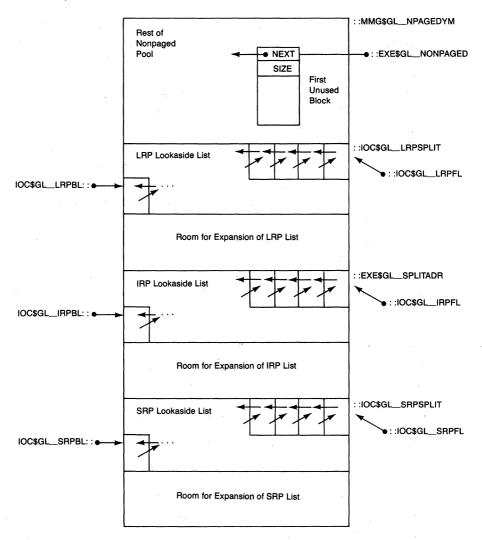

| 1.5.3               | The Program Region (P0<br>Space) 26                           | 3.2   | Preallocated Request Packets 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                     |                                                               | 3.2.1 | Allocation from One of the Lookaside Lists 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

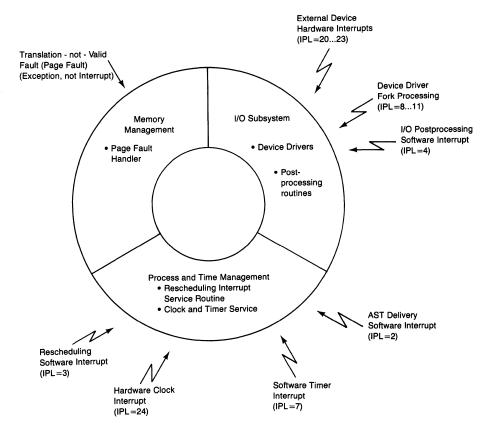

| 2                   | Synchronization<br>Techniques 30                              | 3.2.2 | Deallocation to the Lookaside<br>List 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.1                 | Elevated IPL 30                                               | 3.3   | Use of Dynamic Memory 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2 1 1               | Use of IPL\$ SYNCH 31                                         | 3.3.1 | Process Allocation Region 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3.3.2                                                                              | Paged Dynamic Memory 53                                                                                                                                                                                                                                                                                                                                 | 5                                                         | Hardware Interrupts 98                                                                                                                                                                                                                                                                |