DMC11 IPL synchronous line unit maintenance manual

DMC11 IPL synchronous line unit maintenance manual

digital equipment corporation • maynard, massachusetts

)

Copyright © 1977, 1978 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

This document was set on DIGITAL's DECset-8000 computerized typesetting system.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

| DIGITAL | DECsystem-10 | MASSBUS |

|---------|--------------|---------|

| DEC     | DECSYSTEM-20 | OMNIBUS |

| PDP     | DIBOL        | OS/8    |

| DECUS   | EDUSYSTEM    | RSTS    |

| UNIBUS  | VAX          | RSX     |

|         | VMS          | IAS     |

## CONTENTS

### CHAPTER 1 INTRODUCTION

| 1.1       | SCOPE1-1                                   |

|-----------|--------------------------------------------|

| 1.2       | DMC11 LINE UNIT GENERAL DESCRIPTION1-1     |

| 1.3       | DMC11 LINE UNIT SPECIFICATIONS1-2          |

| 1.4       | GENERAL DESCRIPTION                        |

| 1.4.1     | Introduction1-3                            |

| 1.4.2     | Operating Modes1-4                         |

| 1.4.3     | Microprocessor – Line Unit Data Path1-4    |

| 1.4.4     | Transmitter1-5                             |

| 1.4.5     | Receiver1-5                                |

| 1.4.6     | Signal Conversion and Maintenance Logic1-6 |

| 1.5       | BASICS OF CYCLIC REDUNDANCY CHECKING1-6    |

| 1.5.1     | Mathematical Background1-6                 |

| 1.5.2     | Hardware Implementation of CRC1-8          |

| 1.5.3     | CRC Operation in DDCMP Mode1-8             |

| 1.5.4     | CRC Operation in Bit Stuff Mode1-8         |

| CHAPTER 2 | INSTALLATION                               |

| 2.1       | SCOPE                                      |

| 2.2       | UNPACKING AND INSPECTION                   |

| 2.3       | PREINSTALLATION SETUP PROCEDURES           |

| 2.4       | INSTALLATION AND CHECKOUT                  |

| 2.5       | JUMPER AND SWITCH CHECKLIST2-8             |

| 2.6       | LOCAL LINK CABLE                           |

| 2.6.1     | Selection                                  |

| 2.6.2     | Installation2-11                           |

| 2.6.2.1   | Connectors                                 |

| 2.6.2.2   | Grounding2-14                              |

| 2.6.3     | Maintenance2-15                            |

| 2.7       | FULL-DUPLEX/HALF-DUPLEX OPERATION2-15      |

| CHAPTER 3 | PROGRAMMING                                |

|           |                                            |

| 3.1       | INTRODUCTION                               |

| 3.2 | REGISTERS AND DEVICE ADDRESS SELECTION |  |

|-----|----------------------------------------|--|

| 3.3 | REGISTER BIT ASSIGNMENTS               |  |

# **CONTENTS** (Cont)

### Page

| 3.3.1 | Data Silo Registers                       | 3-3 |

|-------|-------------------------------------------|-----|

| 3.3.2 | Out Control Register                      | 3-3 |

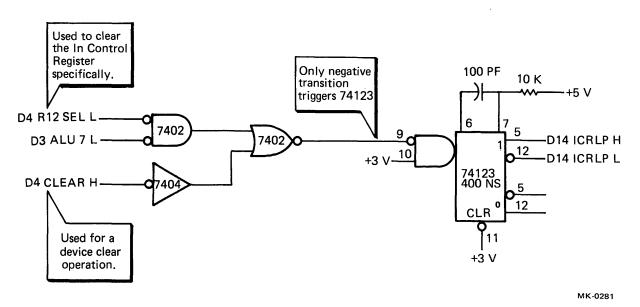

| 3.3.3 | In Control Register                       |     |

| 3.3.4 | Modem Control Register                    |     |

| 3.3.5 | Sync Register                             |     |

| 3.3.6 | Switch Selectable Registers (R15 and R16) |     |

| 3.3.7 | Maintenance Register                      |     |

| 3.4   | PROGRAMMING PROCEDURES                    |     |

### CHAPTER 4 DETAILED DESCRIPTION

|         | 4-1                                         |

|---------|---------------------------------------------|

|         | FRODUCTION4-1                               |

|         | NCTIONAL DESCRIPTION4-3                     |

| 4.2.1   | Logic Description4-3                        |

| 4.2.1.1 | Registers4-3                                |

| 4.2.1.2 | Out Control Logic                           |

| 4.2.1.3 | In Control Logic4-4                         |

| 4.2.1.4 | Transmitter Control Logic4-4                |

| 4.2.1.5 | Receiver Control Logic4-5                   |

| 4.2.1.6 | CRC Logic                                   |

| 4.2.1.7 | Data Set Interface Logic4-7                 |

| 4.2.2   | Major Operating Features                    |

| 4.2.2.1 | Introduction4-7                             |

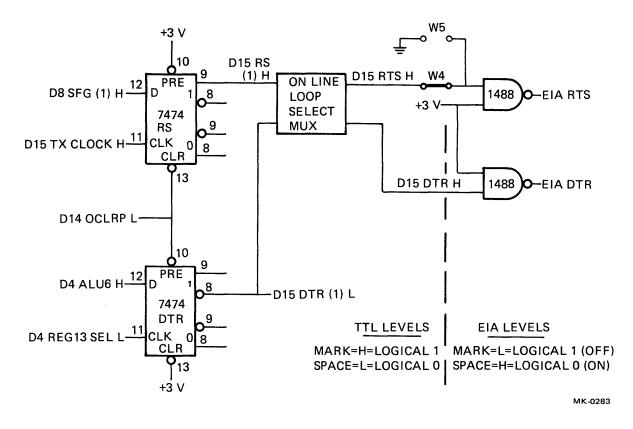

| 4.2.2.2 | Modem Control4-7                            |

| 4.2.2.3 | Transmitter Section                         |

| 4.2.2.4 | Receiver Section4-10                        |

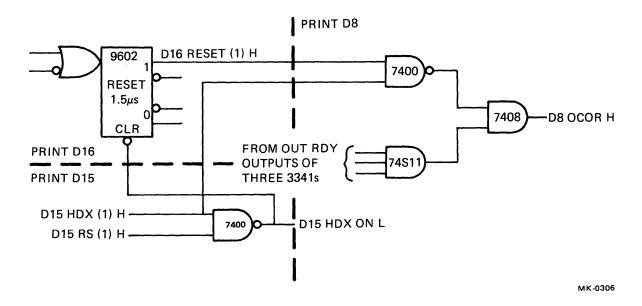

| 4.3 DE  | TAILED DESCRIPTION4-12                      |

| 4.3.1   | Introduction4-12                            |

| 4.3.2   | Registers4-12                               |

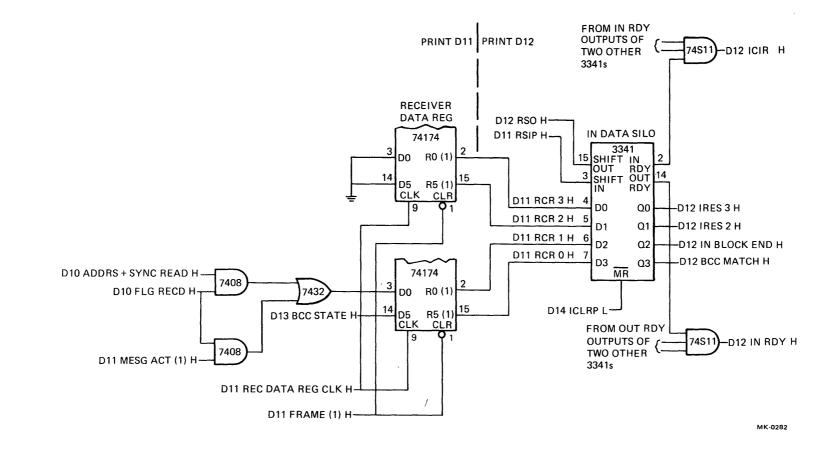

| 4.3.2.1 | In Data Silo Register4-12                   |

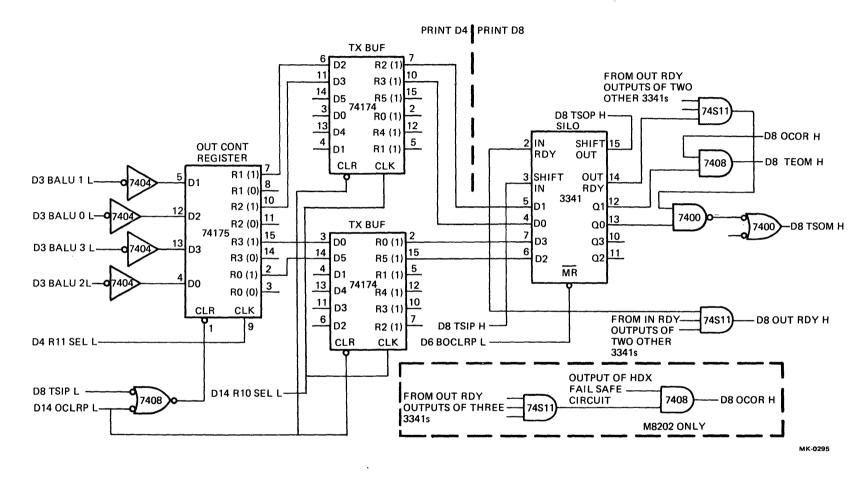

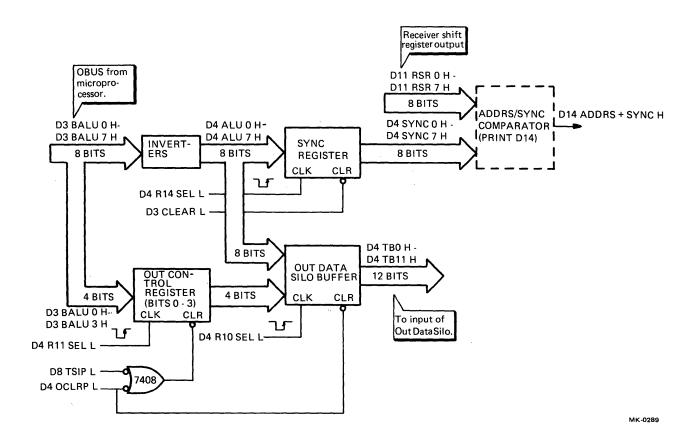

| 4.3.2.2 | Out Data Silo Register4-14                  |

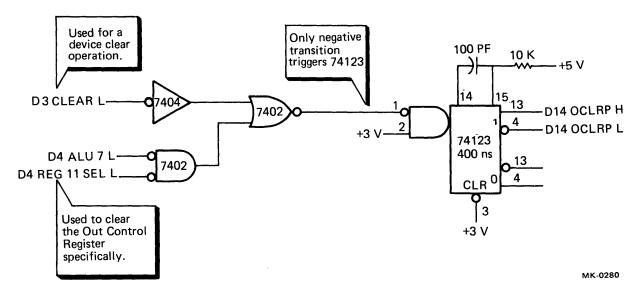

| 4.3.2.3 | Output Control Register4-17                 |

| 4.3.2.4 | Input Control Register4-19                  |

| 4.3.2.5 | Modem Control Register4-21                  |

| 4.3.2.6 | Sync Register                               |

| 4.3.2.7 | Reserved Switch Registers (R15 and R16)4-23 |

| 4.3.2.8 | Maintenance Register                        |

| 4.3.3   | Out Control Logic                           |

| 4.3.4   | In Bus Control Logic4-26                    |

| 4.3.5   | Transmitter Control Logic4-29               |

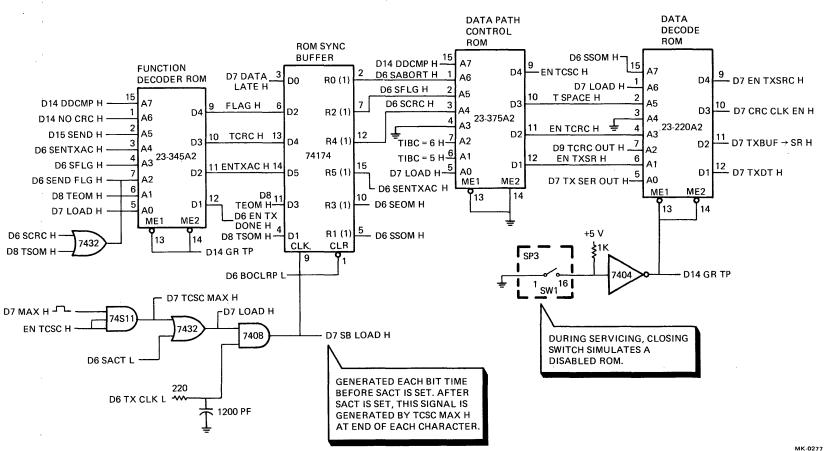

| 4.3.5.1 | ROMs and ROM Sync Buffer                    |

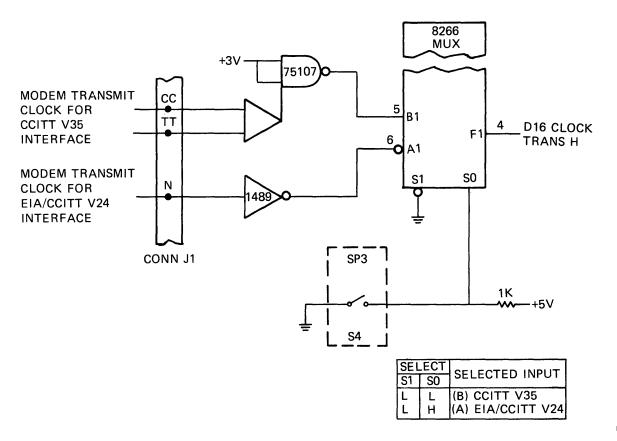

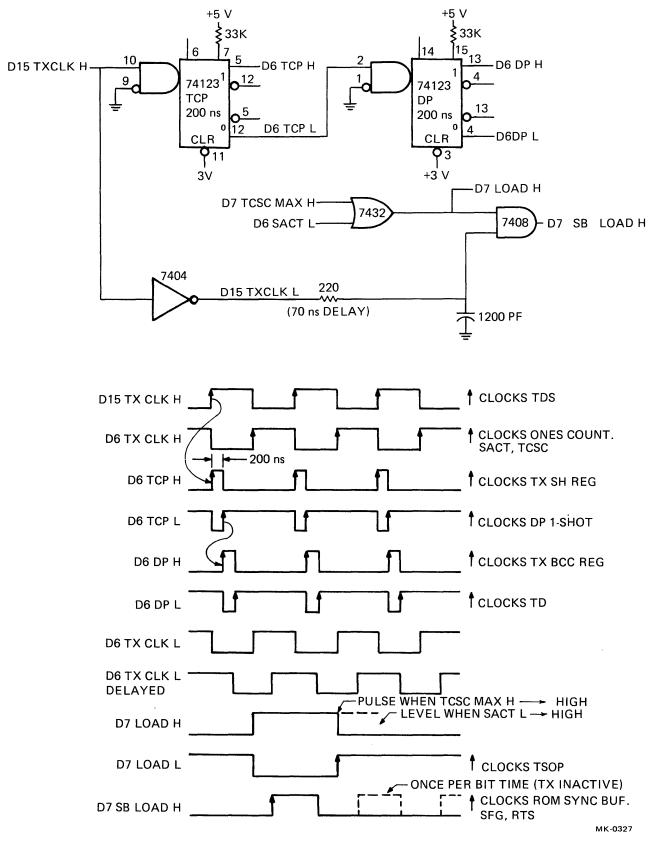

| 4.3.5.2 | TX Clock Logic                              |

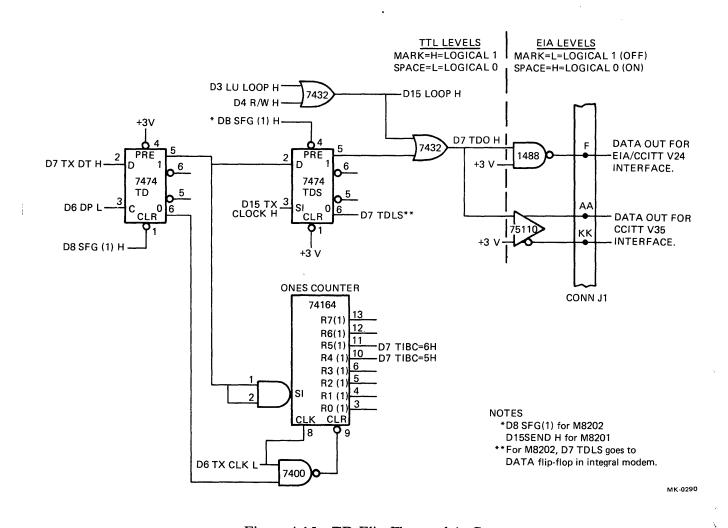

| 4.3.5.3 | TD Flip-Flop and 1s Counter4-37             |

### **CONTENTS** (Cont)

#### Page

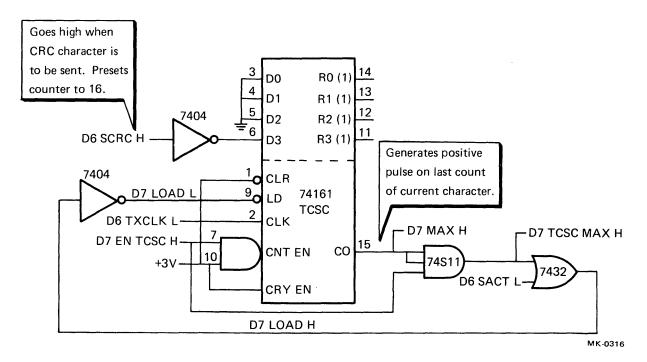

| 4.3.5.4   | Transmitter Character Serialization Counter (TCSC)            | 4-39 |

|-----------|---------------------------------------------------------------|------|

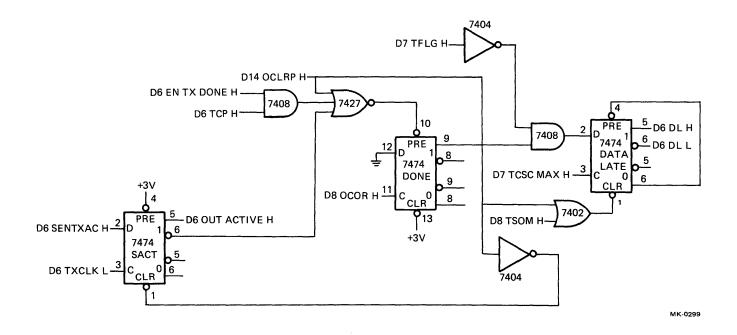

| 4.3.5.5   | SACT, DONE, and DATA LATE Flip-Flops                          |      |

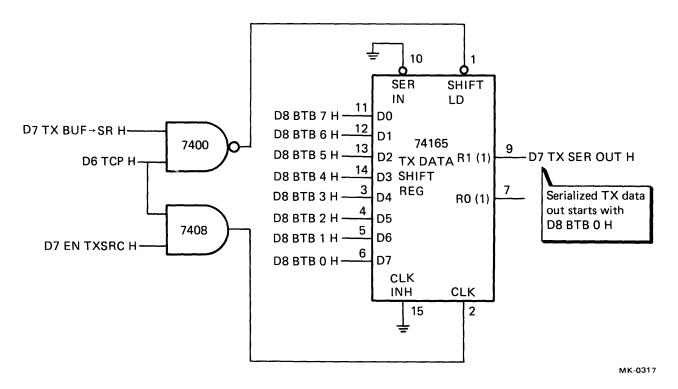

| 4.3.5.6   | Transmitter Shift Register (Print D7)                         |      |

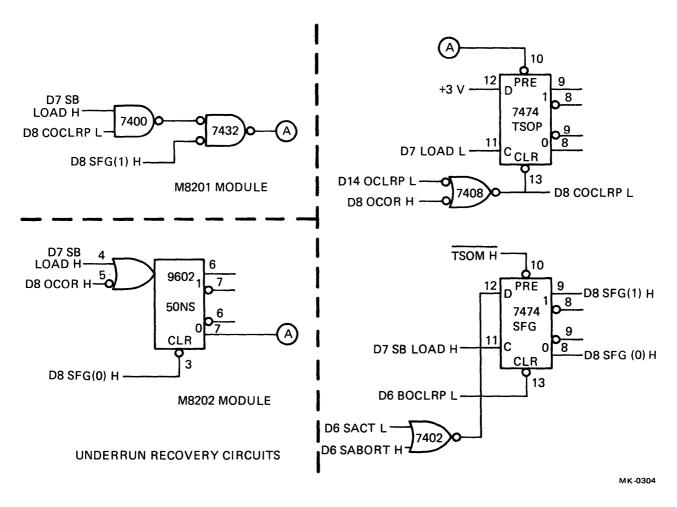

| 4.3.5.7   | SFG Flip-Flop and Underrun Recovery Circuit (Auto Silo Flush) |      |

| 4.3.5.8   | Half-Duplex Fail Safe Circuit (M8202 Only)                    |      |

| 4.3.6     | Receiver Logic                                                |      |

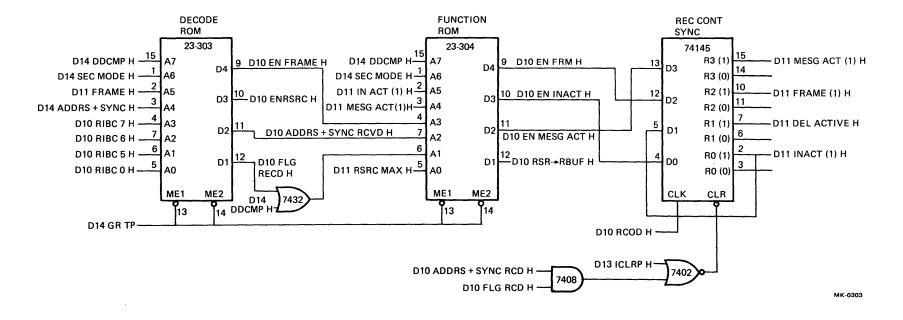

| 4.3.6.1   | ROMs and RCS Flip-Flop                                        |      |

| 4.3.6.2   | Clock Logic                                                   |      |

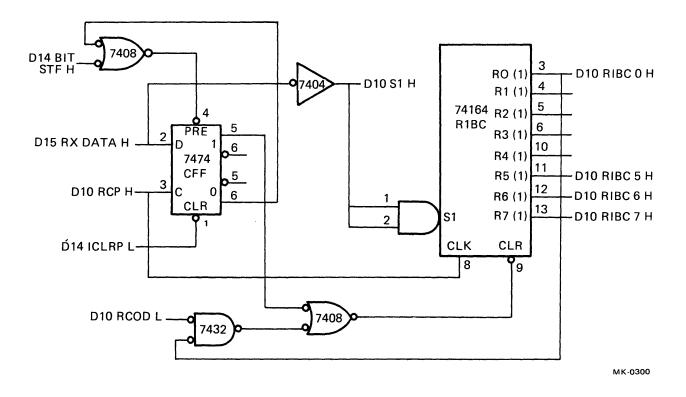

| 4.3.6.3   | CFF Flip-Flop and R1BC Counter (Print D10)                    | 4-52 |

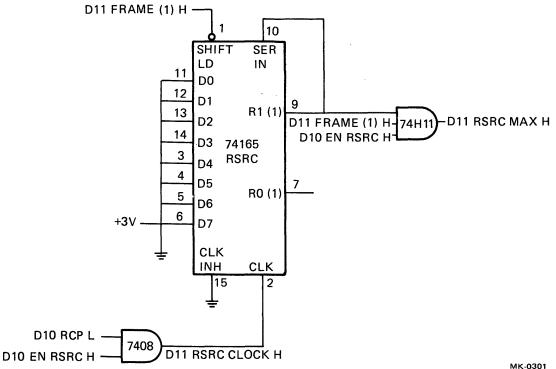

| 4.3.6.4   | Shift Register Counter                                        |      |

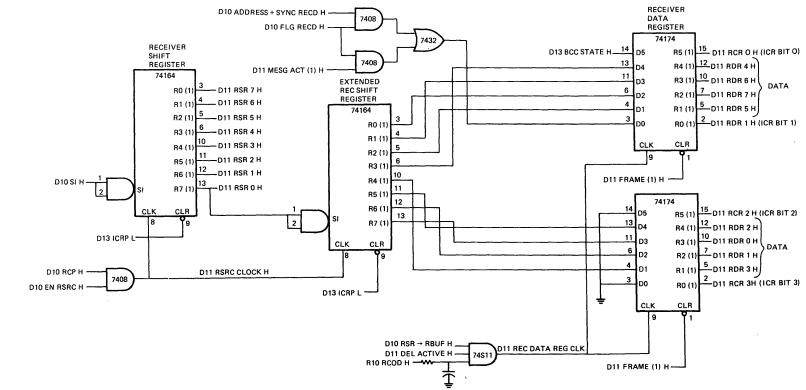

| 4.3.6.5   | Shift Register and Data Buffer                                |      |

| 4.3.6.6   | In Data Silo                                                  |      |

| 4.3.7     | CRC Logic                                                     |      |

| 4.3.7.1   | General                                                       |      |

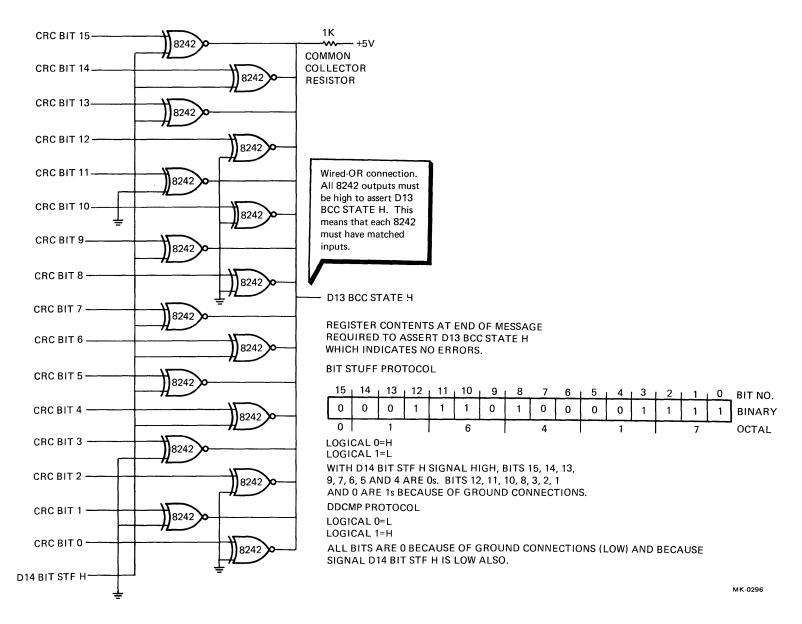

| 4.3.7.2   | Error Detection Logic                                         |      |

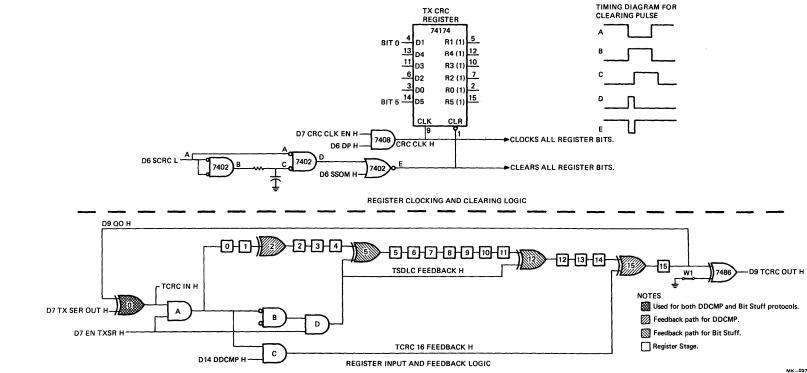

| 4.3.7.3   | Transmitter CRC Register                                      |      |

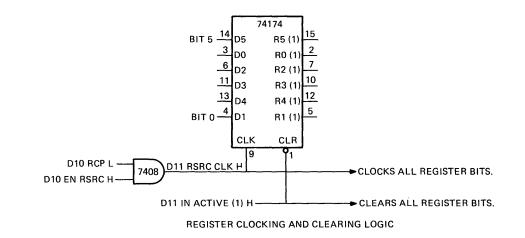

| 4.3.7.4   | Receiver CRC Register                                         |      |

| 4.3.7.5   | Typical CRC Accumulation                                      |      |

| 4.3.8     | Data Set Interface Logic (M8201 Only)                         |      |

| 4.3.8.1   | General                                                       |      |

| 4.3.8.2   | Conversion of Signals from the Modem                          |      |

| 4.3.8.3   | Conversion of Signals to the Modem                            |      |

| 4.3.9     | Maintenance Logic                                             |      |

| 4.3.9.1   | General                                                       |      |

| 4.3.9.2   | RC Clock                                                      |      |

| 4.3.9.3   | Maintenance Multiplexers                                      | 4-68 |

| 4.3.10    | Initialization Logic                                          |      |

| 4.3.11    | Integral Modem (M8202 Only)                                   |      |

| 4.3.11.1  | General Information                                           | 4-72 |

| 4.3.11.2  | Functional Description                                        | 4-72 |

| 4.3.11.3  | Detailed Description                                          |      |

| CHAPTER 5 | MAINTENANCE                                                   |      |

| 5.1       | SCOPE                                                         | 5-1  |

| 5.2       | MAINTENANCE PHILOSOPHY                                        |      |

| 5.3       | PREVENTIVE MAINTENANCE                                        |      |

5.4

5.5

5.5.1

5.5.1.1 5.5.1.2

5.5.1.3

5.5.2

# **CONTENTS** (Cont)

### Page

| 5.5.2.1 | M8201 Isolation     | 5-3 |

|---------|---------------------|-----|

| 5.5.2.2 | M8202 Isolation     | 5-7 |

| 5.5.2.3 | Modem Compatibility | 5-8 |

| 5.5.3   | Sample Waveforms    |     |

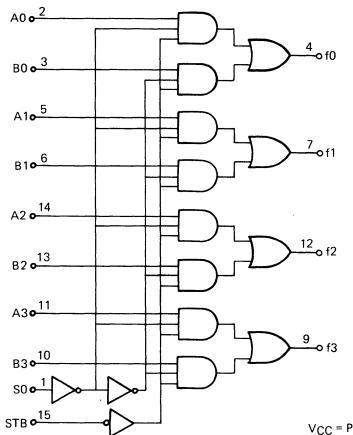

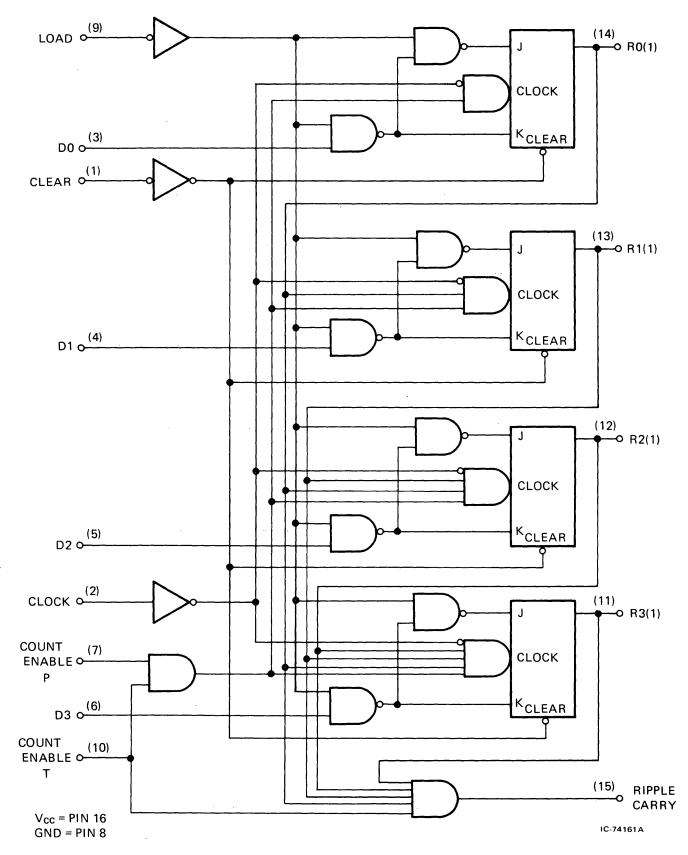

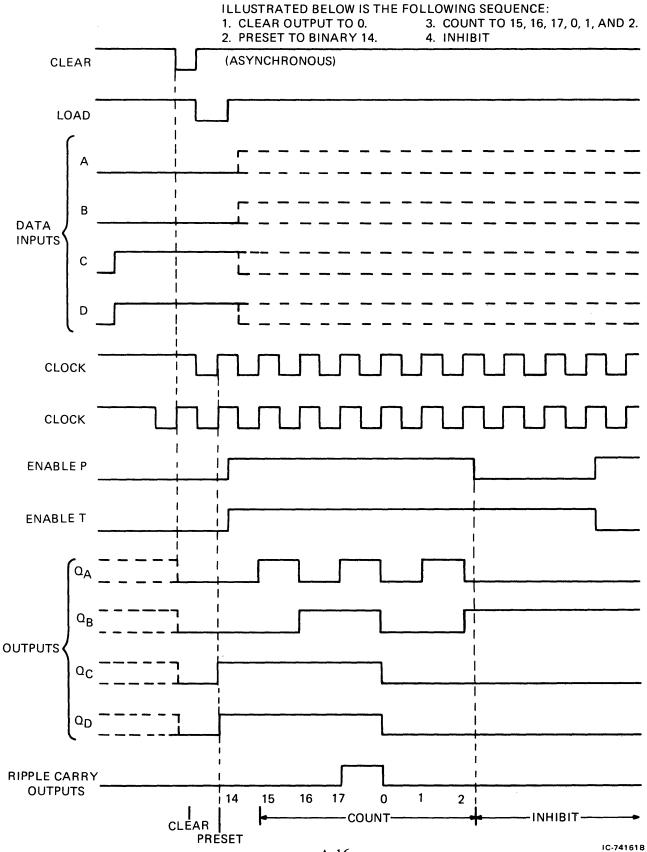

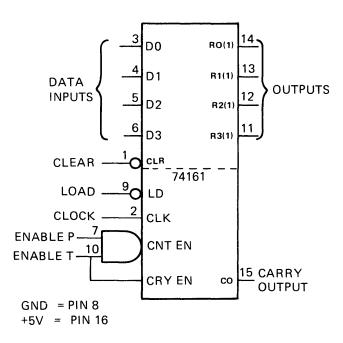

### APPENDIX A INTEGRATED CIRCUIT DESCRIPTIONS

# **FIGURES**

### Figure No.

### Title

### Page

| 2-1  | Jumpers and Switches – M8201 Module2-2                |

|------|-------------------------------------------------------|

| 2-2  | Jumpers and Switches – M8202 Module2-3                |

| 2-3  | Local Link Cable Connectors                           |

| 2-4  | Signal Reflections from a Line Fault2-16              |

| 2-5  | Full-Duplex/Half-Duplex Connections                   |

| 3-1  | Line Unit Register Configurations and Bit Assignments |

| 3-2  | Out Control Register Format                           |

| 3-3  | In Control Register Format                            |

| 3-4  | Modem Control register Format                         |

| 3-5  | Maintenance Register Format                           |

| 4-1  | Line Unit Simplified Block Diagram4-2                 |

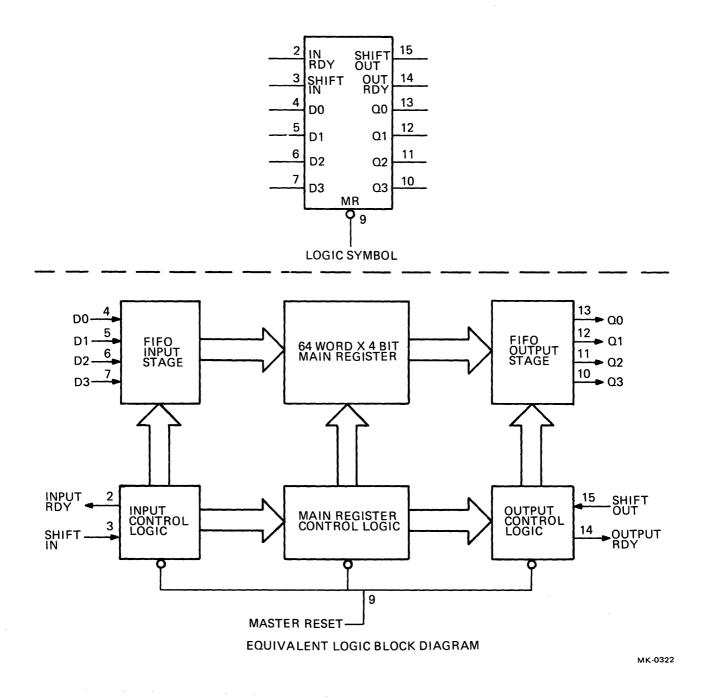

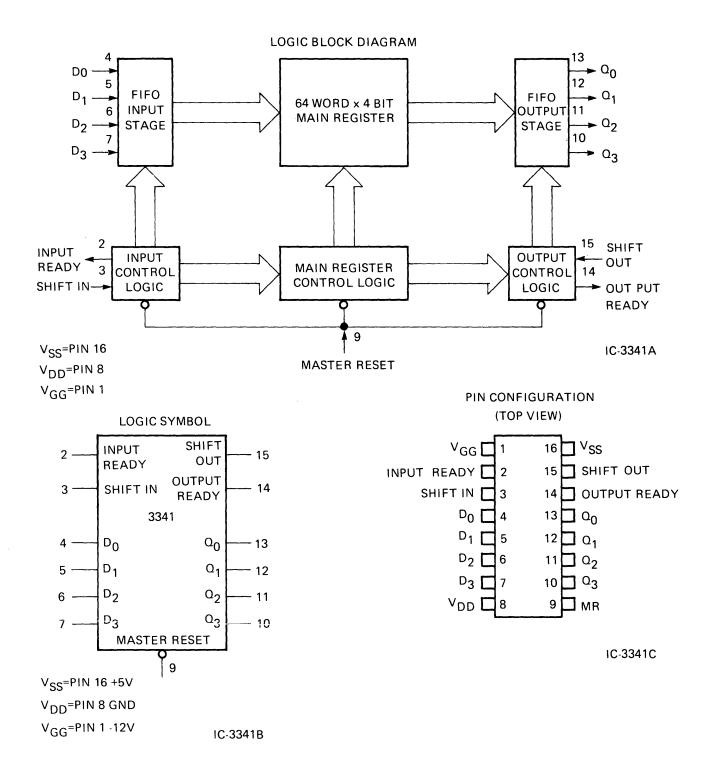

| 4-2  | Logical Representation of 3341 FIFO4-13               |

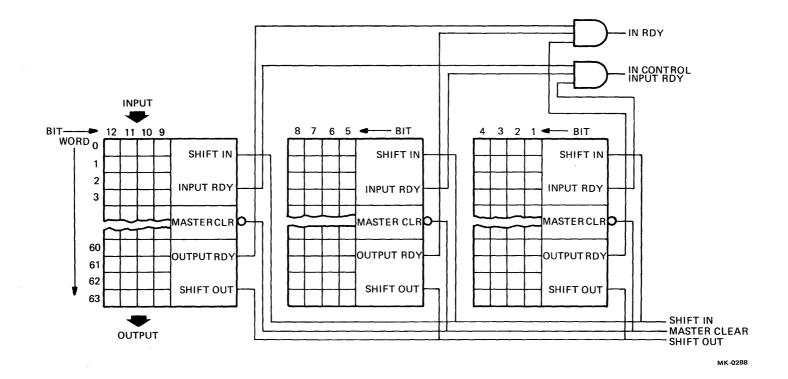

| 4-3  | Architecture of In Data Silo4-15                      |

| 4-4  | Logic for Output Control Register Bits 0-44-18        |

| 4-5  | Logic for Output Control Register Bit 74-19           |

| 4-6  | Logic for Input Control Register Bits 0–34-20         |

| 4-7  | Logic for Input Control Bit 74-21                     |

| 4-8  | RTS and DTR Flip-Flops and Associated Drivers         |

| 4-9  | Block Diagram of OBUS and Associated Logic            |

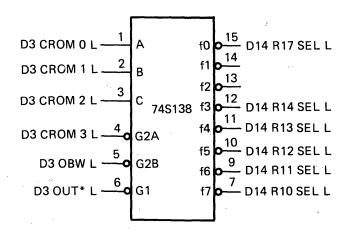

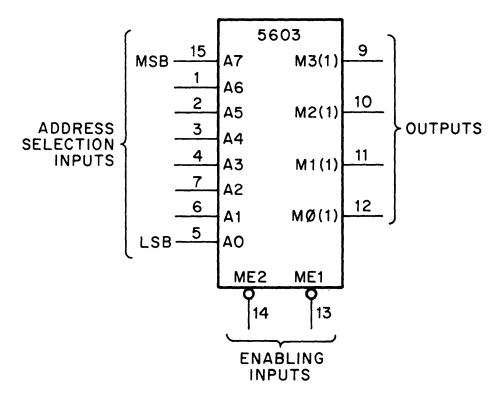

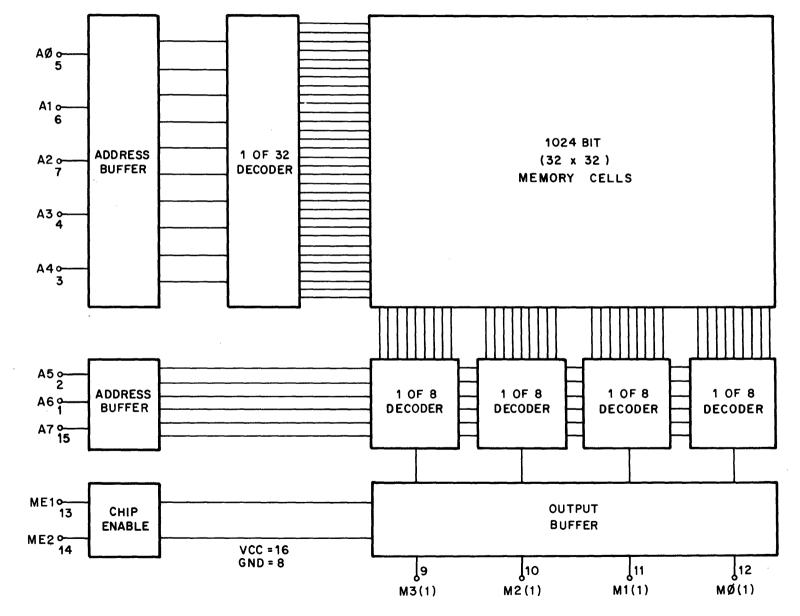

| 4-10 | Register Decoder                                      |

| 4-11 | IBUS Control Logic (1-Bit Slice)                      |

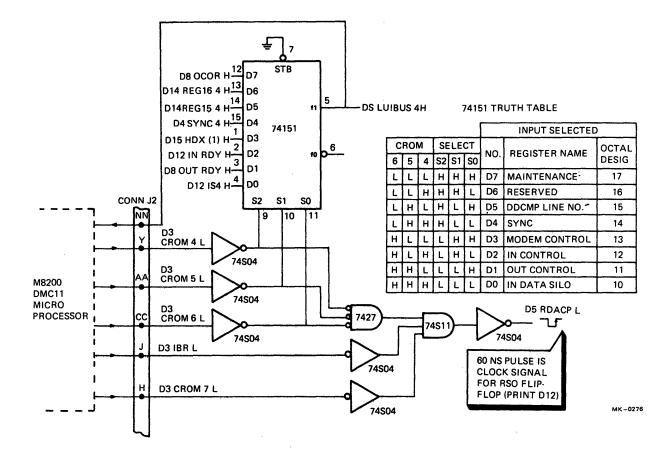

| 4-12 | Transmitter ROMs and Associated Logic                 |

| 4-13 | EIA Transmitter Clock Conversion Logic                |

| 4-14 | Transmitter Clock Logic and Timing Diagram            |

| 4-15 | TD Flip-Flop and 1s Counter                           |

| 4-16 | TCSC Counter                                          |

| 4-17 | SACT, DONE, and DATA LATE Flip-Flops4-41              |

| 4-18 | Transmitter Shift Register                            |

| 4-19 | SFG Flip-Flop and Underrun Recovery Circuit           |

| 4-20 | Half-Duplex Fail Safe Circuit                         |

| 4-21 | Receiver ROMs and Associated Logic                    |

# FIGURES (Cont)

| Figure No. | Title                                                           | Page |

|------------|-----------------------------------------------------------------|------|

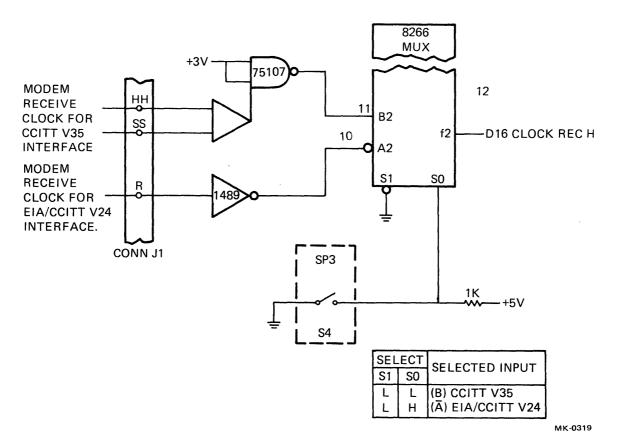

| 4-22       | EIA Receiver Clock Conversion Logic                             | 4-50 |

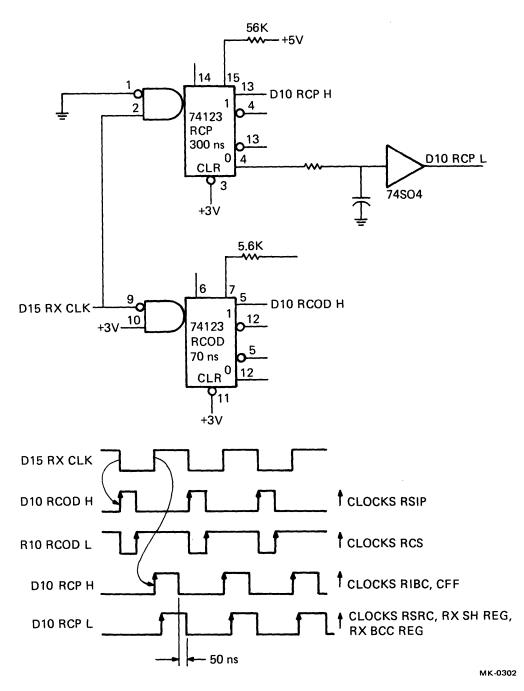

| 4-23       | Receiver Clock Logic and Timing Diagram                         | 4-51 |

| 4-24       | CFF Flip-Flop and R1BC Counter                                  | 4-52 |

| 4-25       | Receiver Shift Register Counter                                 |      |

| 4-26       | Receiver Shift Register and Data Buffer                         | 4-56 |

| 4-27       | CRC Error Detection Logic                                       | 4-58 |

| 4-28       | Transmitter CRC Register                                        |      |

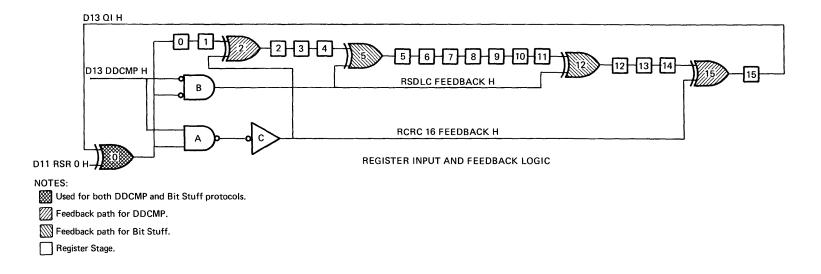

| 4-29       | Receiver CRC Register                                           | 4-63 |

| 4-30       | Typical Transmit and Receive CRC Accumulation                   | 4-64 |

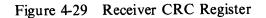

| 4-31       | Conversion Logic for DSR and CS Signals                         |      |

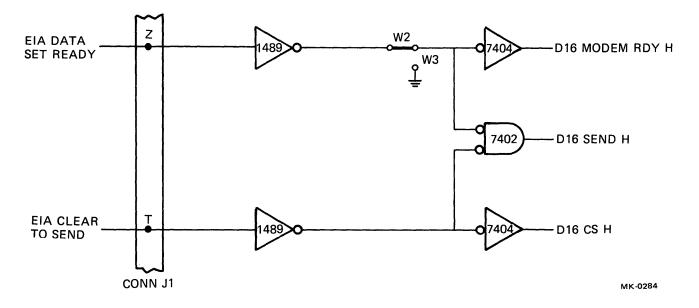

| 4-32       | Maintenance Logic                                               |      |

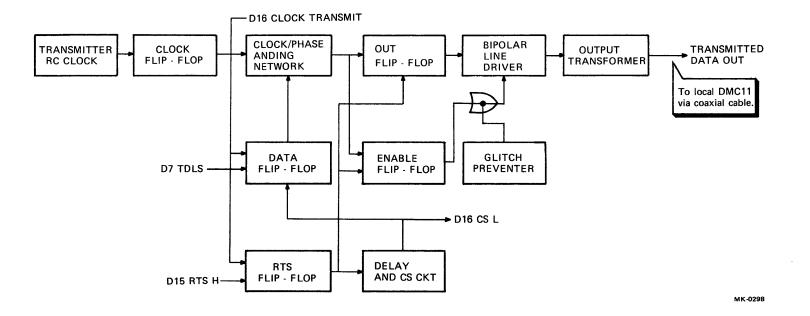

| 4-33       | Simplified Block Diagram of Modem Transmitter                   | 4-73 |

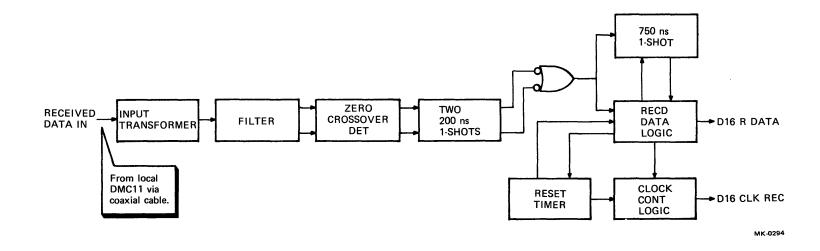

| 4-34       | Simplified Block Diagram of Modem Receiver                      | 4-75 |

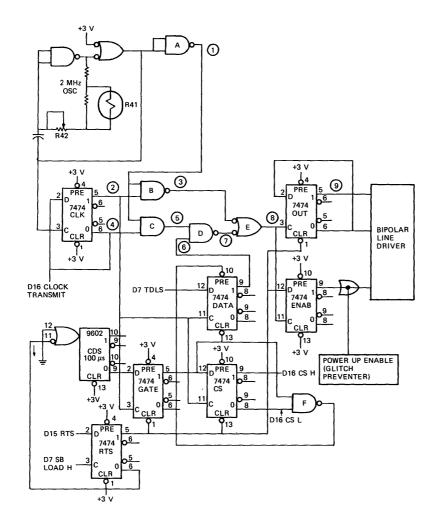

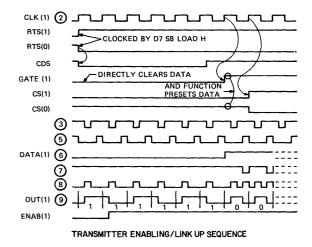

| 4-35       | Schematic and Timing Diagrams for Modem Transmitter Logic       | 4-77 |

| 4-36       | Schematic and Timing Diagram for Modem Receiver Logic           |      |

| 4-37       | RESET Retriggerable One-Shot                                    |      |

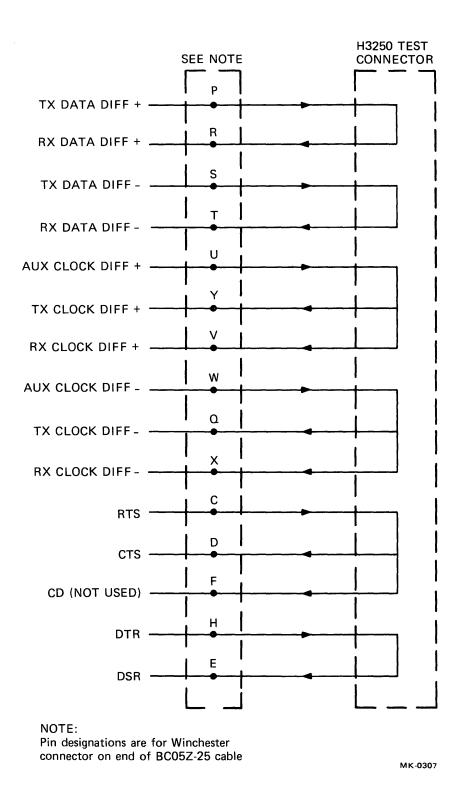

| 5-1        | Schematic of H325 Test Connector for DMC11-DA Option (EIA/CCITT |      |

|            | V24 Interface)                                                  | 5-4  |

| 5-2        | Schematic of H3250 Test Connector for DMC11-FA Option (CCITT    |      |

|            | V.35 Interface)                                                 | 5-5  |

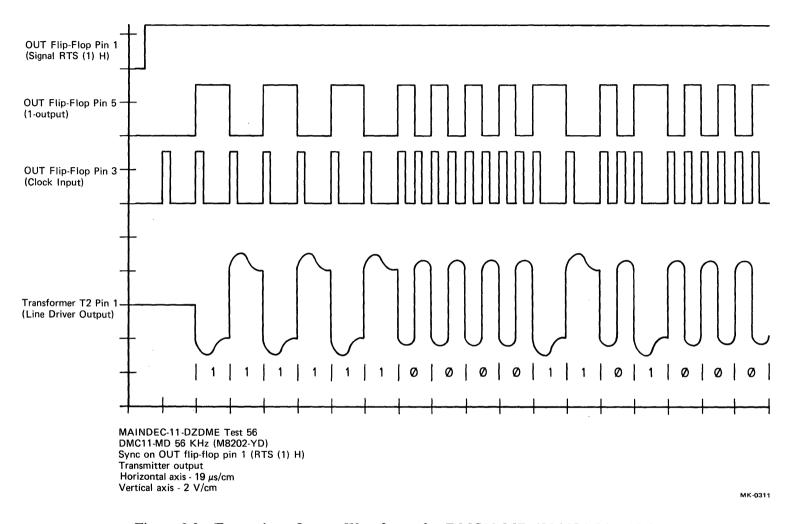

| 5-3        | Transmitter Output Waveforms for DMC11-MD (56 kHz) Line Unit    |      |

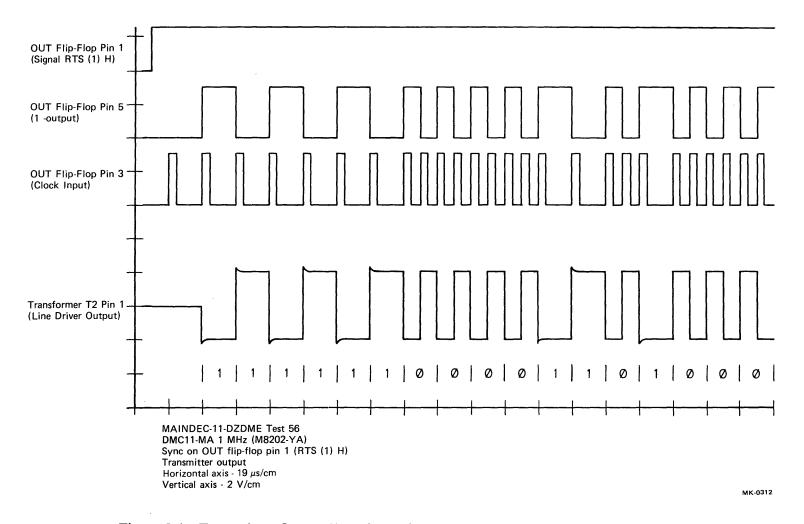

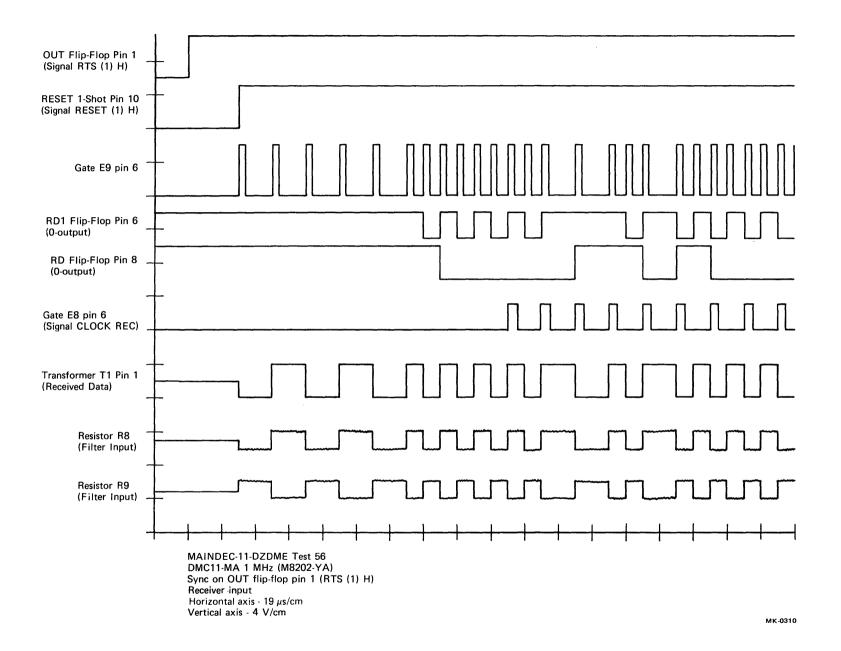

| 5-4        | Transmitter Output Waveforms for DMC11-MA (1 MHz) Line Unit     | 5-10 |

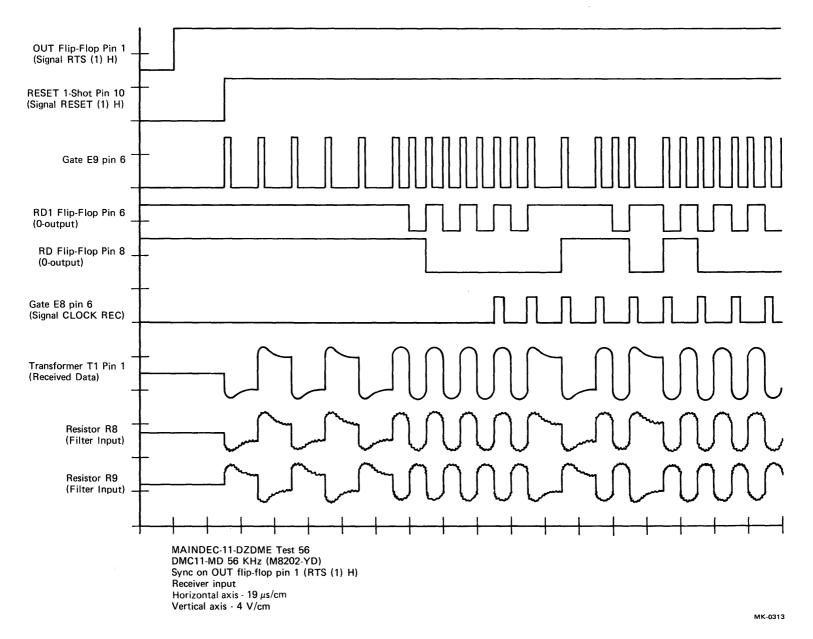

| 5-5        | Receiver Input Waveforms for DMC11-MD (56 kHz) Line Unit        | 5-11 |

| 5-6        | Receiver Input Waveforms for DMC11-MA (1 MHz) Line Unit         |      |

### **TABLES**

### Table No.

### Title

### Page

| 2-1 | M8201 Jumper Configurations                     | 2-4  |

|-----|-------------------------------------------------|------|

| 2-2 | M8202 Jumper Configurations                     |      |

| 2-3 | Configuration of Switch Pack No. 1              |      |

| 2-4 | Jumper and Switch Checklist                     |      |

| 3-1 | Line Unit Registers                             | 3-1  |

| 4-1 | Transmitter Function Decode ROM Input Signals   |      |

| 4-2 | Transmitter Data Path Control ROM Input Signals |      |

| 4-3 | Transmitter Data Decode ROM Input Signals       | 4-33 |

| 4-4 | Receiver Decode ROM Input Signals               | 4-49 |

| 4-5 | Receiver Function ROM Input Signals             | 4-49 |

| 4-6 | Signals from the Modem                          |      |

| 4-7 | Signals to the Modem                            | 4-67 |

| 5-1 | Test Equipment Required                         | 5-2  |

| A-1 | Integrated Circuits                             |      |

. (

### CHAPTER 1 INTRODUCTION

#### 1.1 SCOPE

This manual provides the information necessary to install, operate and maintain the DMC11 Line Unit. It is organized into five chapters and one appendix as follows.

- Chapter 1 Introduction

- Chapter 2 Installation

- Chapter 3 Register Descriptions and Programming Information

- Chapter 4 Detailed Description

- Chapter 5 Maintenance

- Appendix A Integrated Circuit Descriptions

This chapter provides a general description of the two basic variations of the DMC11 Line Unit. They are the remote unit (M8201) and the local unit (M8202). Some background material on Cyclic Redundancy Checking (CRC) methods is presented also.

#### **1.2 DMC11 LINE UNIT GENERAL DESCRIPTION**

The DMC11 Network Link consists of a synchronous line unit that is controlled by a microprocessor. The DMC11 is used to interconnect PDP-11 computers in local and remote network applications.

This manual covers four models of the line unit. They all contain circuitry to accommodate DDCMP and Bit Stuffing protocols. However, they are controlled by the DMC11 Microprocessor which handles only DDCMP. The remote line units require the DMC11-AR Microprocessor and the local line units require the DMC11-AL Microprocessor.

#### DMC11-DA and DMC11-FA Line Units (Remote)

The module designation for both these line units is M8201. It contains modem control and level conversion logic that is compatible with both EIA/CCITT V.24 and CCITT V.35 interfaces. The DMC11-DA is shipped with a cable that accommodates only the EIA/CCITT V.24 interface. This line unit has a maximum speed of 19.2K bits/second. The DMC11-FA is shipped with a cable that accommodates and has a maximum speed of 250K bits/second.

#### DMC11-MA and DMC11-MD Line Units (Local)

Both of these line units have built-in modems. The module designation for the DMC11-MA option is M8202-YA. It operates at a speed of 1M bits/second over triaxial cable up to a maximum distance of 2 km (6362 ft). The module designation for the DMC11-MD option is M8202-YD. It operates at a speed of 56K bits/second over triaxial cable up to a maximum distance of 6 km (19,685 ft). The triaxial cable is not included with either option.

### 1.3 DMC11 LINE UNIT SPECIFICATIONS

# DMC11-MA and DMC11-MD Line Units (Local)

| Operating Mode                            | Half-duplex (single cable), Full-duplex (two cables)                                                                                                                                             |  |

|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Data Format                               | Synchronous serial by bit, LSB first                                                                                                                                                             |  |

| Character Size                            | 8 bits                                                                                                                                                                                           |  |

| Block Check                               | 16-bit polynomials: CRC-16 and modified CRC-CCITT                                                                                                                                                |  |

| Data Rate                                 | 1,000,000 bits/second (DMC11-MA), 56,000<br>bits/second (DMC11-MD)                                                                                                                               |  |

| Maximum Distance<br>DMC11-MA              | Belden 8232 or equivalent: 1 km (3281 ft)<br>Belden 8233: 2 km (6562 ft)                                                                                                                         |  |

| DMC11-MD                                  | Belden 8232: 3 km (9843 ft)<br>Belden 8233: 6 km (19,685 ft)                                                                                                                                     |  |

| Modulation                                | Diphase (double frequency) NRZ                                                                                                                                                                   |  |

| Transmitter Timing                        | RC Osc., trimmable ±5%                                                                                                                                                                           |  |

| Receiver Timing                           | From received signal                                                                                                                                                                             |  |

| Line Interface                            | Transformer coupled                                                                                                                                                                              |  |

| Common Mode Rejection                     | 500 to 1                                                                                                                                                                                         |  |

| Transmitter Signal                        | 4 volts P-P (min.)                                                                                                                                                                               |  |

| Receiver Signal                           | 150 mV P-P (min.)                                                                                                                                                                                |  |

| Connector Type                            | AMP 20606X series                                                                                                                                                                                |  |

| Mounting Space                            | One hex SPC slot (DD11B, C or D), cut out per-<br>mits use in end slots of backplane as well, provided<br>the Unibus in/out slots contain low height (6.35<br>cm, 2.5 in) modules like the M930. |  |

| Power Consumption                         | 3.0 A at +5 V<br>0.046 A at -15 V<br>0.018 A at +15 V                                                                                                                                            |  |

| DMC11 DA and DMC11 EA Line Units (Remote) |                                                                                                                                                                                                  |  |

### DMC11-DA and DMC11-FA Line Units (Remote)

| Operating Mode         | Full- or half-duplex     |

|------------------------|--------------------------|

| Communications Channel | Private wire or switched |

| Data Format       | Synchronous, serial by bit, LSB first                                                                                                                                                                      |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Character Size    | 8 bits                                                                                                                                                                                                     |

| Block Check       | 16-bit polynomials: CRC-16 and modified CRC-CCITT                                                                                                                                                          |

| Data Rate         | Up to 19,200 bits/second (DMC11-DA)                                                                                                                                                                        |

|                   | Up to 250,000 bits/second (DMC11-FA) using V.35 level conversion, limited by (DMC11-AR) microcode. Up to 1 M bits/second; limited by hardware.                                                             |

| Interface         | RS232C or CCITT V.24 compatible (DMC11-<br>DA),<br>CCITT V.35 compatible (DMC11-FA)                                                                                                                        |

| Modems            | Bell 208, 209 or equivalent (DMC11-DA)<br>GTE/Lenkurt L500A-5,<br>WECo. (Bell) 500A L1/5,<br>or equivalent (DMC11-FA)                                                                                      |

| Signals Supported | BA transmit data<br>DB serial clock transmit (SCT)<br>BB receive data<br>DD serial clock receive (SCR)<br>CC data set ready<br>CD data terminal ready<br>CA request to send<br>CB clear to send<br>CE ring |

| Cable             | 7.62 m (25 ft) with EIA connector supplied                                                                                                                                                                 |

| Mounting Space    | One hex SPC slot (DD11B, C, or D), cutout permits use in end slots of backplane as well, provided the Unibus in/out height ( $\leq 6.35$ cm, 2.5 in) modules like the M930.                                |

| Power Consumption | 3.2 A at +5 V<br>0.31 A at -15 V<br>0.03 A at +15 V                                                                                                                                                        |

### **1.4 GENERAL DESCRIPTION**

**1.4.1 Introduction** This section provides a general description of the M8201 and M8202 Line Units. A more detailed description at the function level is contained in Chapter 4, Detailed Description.

The DMC11 Line Units (M8201 and M8202) perform the standard functions associated with a synchronous communications device. They are:

Parallel-to-serial data conversion. Serial-to-parallel data conversion. SYNC character detection. Leading SYNC character stripping.

In addition, the line units can perform the following functions.

Modem control and monitoring Cyclic redundancy character testing. Zero bit stuffing Zero bit stripping Automatic flag transmission. Automatic flag recognition. Automatic abort sequence transmission. Automatic abort sequence recognition. Automatic pad character transmission.

#### **1.4.2 Operating Modes**

The line units may operate in either of two microprogrammable modes. The modes are:

1. DDCMP mode – This is an 8-bit byte mode of operation. It is designed for the highly efficient byte oriented Digital Data Communications Message Protocol (DDCMP) using the CRC-16 polynomial.

#### NOTE

Less efficient character oriented protocols that use many control characters can use this mode of operation but the CRC logic must be disabled. The microprogram within the DMC11 Microprocessor would have to compute the CRC.

2. Bit Stuff mode – This is a bit oriented mode of operation. It is designed for the bit oriented message protocols using the flag and abort sequences and the modified CRC-CCITT polynomial.

The line unit provides a data path between the microprocessor and a data set (or local link) and vice versa.

#### 1.4.3 Microprocessor – Line Unit Data Path

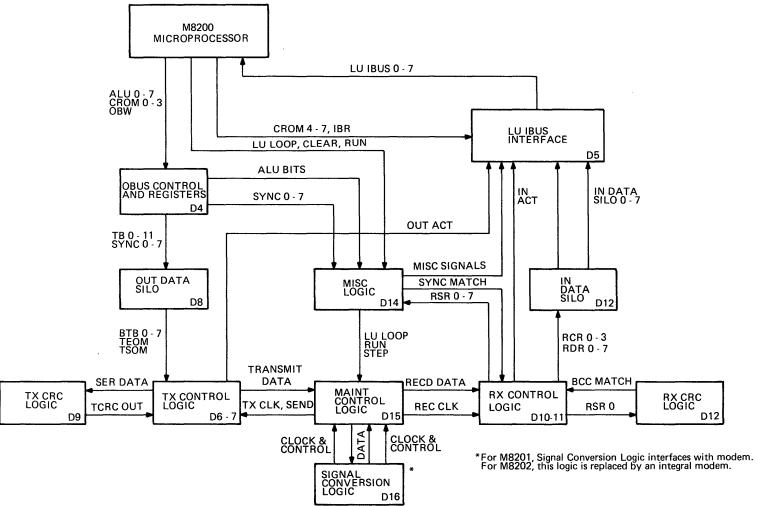

The following discussion is keyed to the block diagram shown in Figure 4-1.

The microprocessor and line unit communicate through two unidirectional data paths. Signals BALU 0-7 compose the data path from the microprocessor to the line unit. The line unit appears to the microprocessor as eight registers. The data is passed to the correct register by control signals CROM 0-3. Signal OBW is the strobe.

The line unit communicates with the microprocessor through the Line Unit In Bus (LU IBUS). The microprocessor controls all reading of the line unit registers.

Various maintenance signals are passed to the Maintenance and Miscellaneous logic. These signals control the functioning of the receiver and transmitter in the maintenance mode.

#### 1.4.4 Transmitter

The transmitter portion of the line unit consists of three functional groups of logic. They are:

- 1. Out Data Silo

- 2. Transmitter Control

- 3. Transmitter CRC Logic

This logic performs specific parts of the transmission function. The functions are explained below.

The Out Data Silo is seen as a write only register to the microprocessor. The Transmitter Control logic sees it as a buffer. The silo is a 64-word-deep data path between the microprocessor and the Transmitter Control logic.

The hardware implementation of this silo is through the use of FIFO (First In/First Out) devices. The silo effect is necessary because of the speed difference between the serialization process and the data available from the microprocessor. Because of the speed with which the microprocessor could load characters (conceivably, one character every 300 nanoseconds) and the speed at which the characters can be serialized (using dial up facilities, approximately one character every 160 microseconds), there must be a multicharacter buffer. Additionally, in order to relieve the microprogram of the need to have timers to know when to load another message or when to end a message, transmitter control bits Start of Message (SOM) and End of Message (EOM) are siloed also.

A typical sequence of operation is:

- 1. Microprogram loads Start of Message into the Out Control register.

- 2. Microprogram loads data into the Out Data Silo.

- 3. The Transmitter detects SOM at the silo output.

- 4. Request to Send is asserted by the transmitter, automatically.

- 5. Clear To Send and Data Set Ready come true.

- 6. The transmitter is enabled. Serialization begins.

As long as the SOM bit is true, the data being serialized is not included in the CRC computation.

When the Tx Control detects a character available from the silo without the SOM bit set, it includes that character, and all the characters following it, in the CRC computation.

When End of Message is detected, the Tx Control transmits the CRC Check Character (called the BCC). If more data follows the EOM, a new CRC computation is begun.

#### 1.4.5 Receiver

The receiver portion of the line unit consists of three functional groups of logic. They are:

- 1. In Data Silo

- 2. Receiver Control

- 3. Receiver CRC Logic

This logic performs specific parts of the receive function. The functions are explained below.

The In Data Silo is seen by the microprocessor as a read only register. The Rx Control sees it as an output buffer. The silo is a 64-word-deep data path between the Rx Control and the microprocessor.

The hardware implementation of the silo is similar to that used in the transmitter. Input to the In Data Silo is controlled by the Rx Control while output is controlled by the microprogram. The silo is present for the same reasons mentioned in the discussion of the transmitter.

A typical sequence of operations is:

- 1. The receiver becomes active after detecting the first data character preceded by two or more synchronizing sequences (one flag sequence in the case of Bit Stuff mode).

- 2. The data character is included in the CRC computation automatically.

- 3. The data character is loaded into the silo by the Receive Control.

- 4. The microprogram detects, by bit testing, both In Active and In Ready (bits 6 and 4, respectively, of the In Control register).

- 5. The microprogram reads the In Data Silo.

- 6. The silo presents In Ready with each subsequent character.

- 7. The microprogram, having determined when the message ends, checks the BCC Match bit (bit 0 of the In Control register). If the bit is set, the message had no detected errors.

- 8. In Bit Stuff mode, the Block End bit (Bit 1 of R12) is set with the BCC Match bit, if no errors were detected.

#### 1.4.6 Signal Conversion and Maintenance Logic

The signal conversion and maintenance logic provide automatic modem control, clock sources for the transmitter and receiver, and the receiver data source.

#### **1.5 BASICS OF CYCLIC REDUNDANCY CHECKING**

#### 1.5.1 Mathematical Background

A cyclic code message consists of a specific number of data bits and a Block Check Character (BCC) that is computed by the CRC logic. Let n equal the total number of bits in the message and k equal the number of data bits; then n-k equals the number of bits in the BCC.

The code message is derived from two polynomials which are algebraic representations of two binary words, the generator polynomial P(X) and the message polynomial G(X). The generator polynomial is the type of code used (CRC-12, CRC-16, CRC-CCITT, etc.); the message polynomial is the string of serial data bits. The polynomials are usually represented algebraically by a string of terms in powers of X such as  $X^{n}...+X^{3} + X^{2} + X + X^{0}$  (or 1). In binary form, a 1 is placed in each position that contains a term; absence of a term is indicated by a 0. The convention followed in this manual is to place the least significant bit (X<sup>0</sup>) at the right. For example, if a polynomial is given as  $X^{4} + X + 1$  its binary representation is 10011 (3rd and 2nd degree terms are not present).

Ν

Given a message polynomial G(X) and a generator polynomial P(X), the objective is to construct a code message polynomial F(X) that is evenly divisible by P(X). It is accomplished as follows.

- 1. Multiply the message G(X) by  $X^{n-k}$  where n-k is the number of bits in the BCC.

- 2. The resulting product  $X^{n-k}[G(X)]$  is divided by the generator polynomial P(X).

- 3. The quotient is disregarded and the remainder C(X) is added to the product to yield the code message polynomial F(X), which is represented as  $X^{n-k}[G(X)] + C(X)$ .

The division is performed in binary without carries or borrows. In this case, the remainder is always one bit less than the divisor. The remainder is the BCC and the divisor is the generator polynomial; therefore, the bit length of the BCC is always one less than the number of bits in the generator polynomial.

A simple example is explained below.

1. Given:

Message polynomial  $G(X) = 110011 (X^5 + X^4 + X + X^0)$ Generator polynomial  $P(X) = 11001 (X^4 + X^3 + 1)$ G(X) contains 6 data bits P(X) contains 5 bits and will yield a BCC with 4 bits; therefore, n-k = 4

2. Multiplying the message G(X) by  $X^{n-k}$  gives:

$X^{n-k}[G(X)] = X^{4}(X^{5} + X^{4} + X + X^{0}) = X^{9} + X^{8} + X^{5} + X^{4}$

The binary equivalent of this product contains 10 bits and is 1100110000.

3. This product is divided by P(X)

P (X)→11001 10000

$$\checkmark$$

X<sup>n-k</sup> [G (X)]

11001

10000

11001

1001  $\checkmark$  Remainder=C (X)=BCC

4. The remainder C(X) is added to  $X^{n-k}[G(X)]$  to give F(X) = 1100111001.

The code message polynomial is transmitted. The receiving station divides it by the same generator polynomial. If there is no error, the division will produce no remainder and it is assumed that the message is correct. A remainder indicates an error. The division is shown below.

$$P(X) \rightarrow 11001 \qquad \frac{100001}{1100111001} \leftarrow F(X) \\ \frac{11001}{11001} \\ \frac{11001}{00000} \leftarrow \text{no remainder}$$

#### **1.5.2** Hardware Implementation of CRC

The BCC is computed and accumulated in a shift register during transmission. Another shift register is used during reception to examine the received data and BCC. In each register, the number of stages is equal to the degree of the generating polynomial. In the line unit, the registers have 16 stages because 16 degree generating polynomials are used. The Bit Stuff mode uses code CRC-CCITT whose generator polynomial is  $X^{16} + X^{12} + X^5 + 1$ . DDCMP uses code CRC-16 whose generator polynomial is  $X^{16} + X^{12} + X^5 + 1$ .

Both the transmitter and receiver CRC registers have control logic that allows the registers to be configured for the selected CRC code.

When a message and accompanying BCC character have been received, the CRC logic only indicates whether the message is in error or not. It does not correct errors nor does it even enumerate or locate errors. Under protocol discipline, the sending station is requested to retransmit the message.

#### 1.5.3 CRC Operation in DDCMP Mode

Under DDCMP protocol control, CRC operation is exactly like that described in Paragraph 1.3.4.1, Mathematical Background.

The transmitter and receiver CRC registers are initialized to all 0s. At the sending station, the transmitter CRC register accepts the information being transmitted and accumulates the BCC. When the last bit of information has been transmitted, the contents of the transmitter CRC register are transmitted.

At the receiving station, the information plus the 16-bit BCC is examined by the receiver CRC register. At the end of the message (information plus BCC), the contents of the receiver CRC register should read 0 if the message is errorless. The CRC error detection logic asserts a flag if the register reads 0. If an error is present, the register reads non-0 and the flag is not asserted. The line unit does not count characters, so it is the program's responsibility to look for the CRC error flag at the proper time.

#### **1.5.4** CRC Operation in Bit Stuff Mode

Under Bit Stuff protocol control, CRC operation is slightly different than that described in Paragraph 1.3.4.1, Mathematical Background. The differences are:

1. The factor  $X^k (X^{15} + X^{14}...+ X + 1)$  is added to  $X^{n-k}[G(X)]$  which corresponds to initializing the transmitter CRC register to all 1s. This function is equivalent to inverting the first 16 bits of G(X). This allows detection of the addition or deletion of 0s at the leading end of the message due to erroneous flag characters.

$\mathbf{i}$

- 2. The accumulated BCC, which is called Frame Check Sequence (FSC) in the Bit Stuff mode, is complemented before being transmitted. This results in a unique non-0 remainder  $(016417_8)$  at the receiver. This allows detection of the erroneous addition or deletion of 0s at the trailing edge of the message due to errors.

- 3. At the receiving station, the receiver CRC register is initialized to all 1s. The information plus the FCS constitutes the message and it is added to  $X^k (X^{15} + X^{14}... + X + 1)$  and divided by P(X) to give 016417<sub>8</sub>, if the transmission is errorless. If an error is present, the flag is asserted.

### CHAPTER 2 INSTALLATION

#### 2.1 SCOPE

This chapter provides information for installation and checkout of the M8201 and M8202 line units.

#### 2.2 UNPACKING AND INSPECTION

The line unit comes in four versions which are described below.

DMC11-DA (For EIA/CCITT V.24 Interface)

M8201 - Line Unit Module BC08R-1 or BC08S-1 - Interconnect Cable BC05C-25 - Modem Cable H325 - Test Connector

DMC11-FA (For CCITT V.35 Interface)

M8201 - Line Unit Module BC08R-1 or BC08S-1 Interconnect Cable BC05Z-25 - DSU Cable H3250 - Test Connector

DMC11-MA (Local 1M bits/second)

M8202-YA - Line Unit Module BC08R-1 or BC08S-1 Interconnect Cable 12-12528 - Coaxial Test Connector

DMC11-MD (Local 56K bits/second) M8202-YD - Line Unit Module BC08R-1 or BC08S-1 - Interconnect Cable 12-12528 - Coaxial Test Connector

#### NOTE

An additional cable may be included with either of the local line units (DMC11-MA and -MD). It is a 30.48 m (100 ft) long coaxial cable that is designated BC03N-A0. This is not part of the DMC11. It is a DEC catalog item that can be ordered by the customer.

Inspect these parts for visible damage. Report any damage or shortage immediately to the shipper and the DEC representative.

#### 2.3 PREINSTALLATION SETUP PROCEDURES

#### NOTE

The line unit cannot function without the DMC11-AR or -AL Microprocessor (M8200). It is assumed that the microprocessor has been installed and checked out in accordance with Chapter 2, Installation of the Microprocessor manual (EK-DMCMP-MM-001).

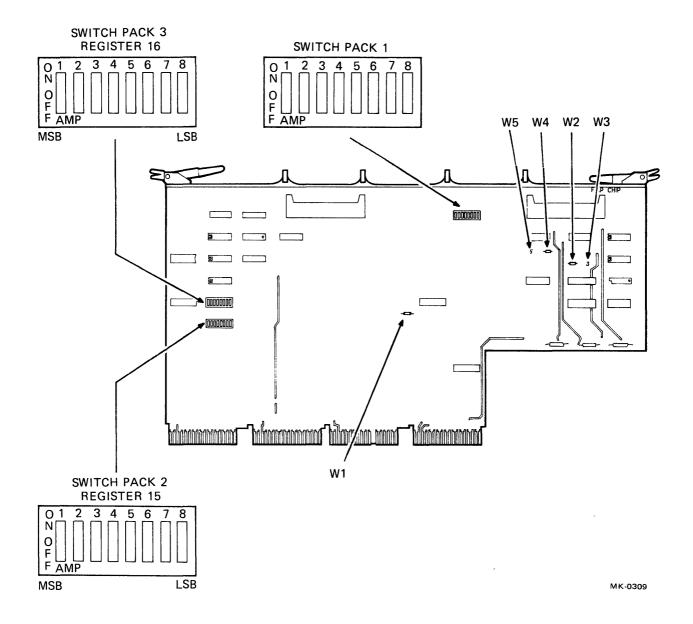

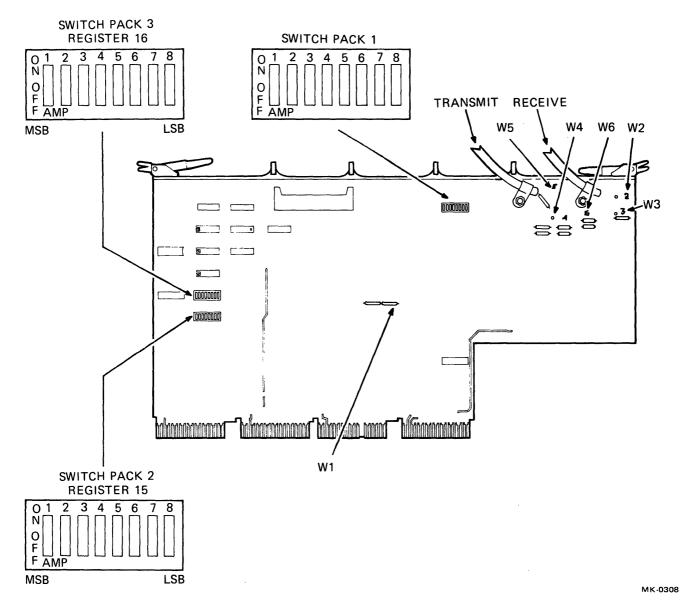

Before installing the line unit, check the jumpers and switches to be sure that they are in the normal configuration. Locations of the switches and jumpers are shown in Figure 2-1 for the M8201 Module and Figure 2-2 for the M8202 Module.

Figure 2-1 Jumpers and Switches – M8201 Module

Figure 2-2 Jumpers and Switches – M8202 Module

#### 1. Jumpers

The M8201 Line Unit contains five jumpers (W1-W5). The M8202 Line Unit contains six jumpers (W1-W6). The normal jumper configurations are described in Table 2-1 for the M8201 and Table 2-2 for the M8202.

| Jumper<br>Number | Normal<br>Configuration | Function                                                                                                                                                                 |  |

|------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| W1               | Installed               | With this jumper installed, the transmitter CRC charac-<br>ter is not inverted by the CRC register output gate.                                                          |  |

|                  |                         | This jumper must be installed to ensure proper oper-<br>ation of codes CRC-16 and CRC-CCITT under the dis-<br>cipline of DDCMP and Bit Stuff protocols.                  |  |

|                  |                         | If the user removes this jumper for some special reason,<br>the Transmitter CRC character is inverted by the CRC<br>register output gate. The diagnostic will fail also. |  |

| W2               | Installed               | Jumpers W2 and W3 are used together.                                                                                                                                     |  |

| W3               | Removed                 | With W2 installed and W3 removed, the modem Data<br>Set Ready line controls the state of signal D16 MODEM<br>RDY H.                                                      |  |

|                  |                         | With W3 installed and W2 removed, signal D16<br>MODEM RDY H is always asserted. This feature ac-<br>commodates modems that do not assert Data Set<br>Ready.              |  |

| W4               | Installed               | Jumpers W4 and W5 are used together.                                                                                                                                     |  |

| W5               | Removed                 | With W4 installed and W5 removed, signal D15 RTS H controls the state of the modem Request to Send line.                                                                 |  |

|                  |                         | With W5 installed and W4 removed, the Request to<br>Send line is on continuously. This feature accom-<br>modates modems that require this condition.                     |  |

Table 2-1

M8201 Jumper Configurations

#### NOTE If W2-5 jumpers are not installed in the normal configuration, diagnostics will report modem control errors.

| Jumper<br>Number | Normal<br>Configuration | Function                                                                                                                                                                 |  |

|------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| <b>W</b> 1       | Installed               | With this jumper installed, the transmitter CRC charac-<br>ter is not inverted by the CRC register output gate.                                                          |  |

|                  |                         | This jumper must be in to ensure proper operation of codes CRC-16 and CRC-CCITT under the discipline of DDCMP and Bit Stuff protocols.                                   |  |

|                  |                         | If the user removes this jumper for some special reason,<br>the Transmitter CRC character is inverted by the CRC<br>register output gate. The diagnostic will fail also. |  |

| W2,W3            | Removed                 | When installed, the modem receiver protection trans-<br>former is disabled. Installation is not recommended.                                                             |  |

| W4, W5           | Removed                 | When installed, the modem transformer protection transformer is disabled. Installation is not recommended.                                                               |  |

| W6               | Removed                 | Installed for single cable half-duplex operation only.                                                                                                                   |  |

| Table 2-2 M8202 Jumper Configu | urations |

|--------------------------------|----------|

|--------------------------------|----------|

Switch Packs No. 2 and No. 3

Switch packs no. 2 and no. 3 are both 8 switch DIPs. Switch pack no. 2 is Register 15 and is installed in location E87 on the M8201 Line Unit and in location E90 on the M8202 Line Unit. Switch pack no. 3 is Register 16 and is installed in location E88 on the M8201 Line Unit and in location E91 on the M8202 Line Unit.

When the line unit module is shipped, all switches in both pack numbers 2 and 3 are OFF. This is the default status  $(377_8)$ .

For both switch pack no. 1 and switch pack no. 2:

Switch OFF = 1. Switch no. 1 = MSB, Switch no. 8 = LSB.

Correct settings of these switches may be verified by examination of STAT 2 of the diagnostic printout if run with autosize. Check diagnostic listings for which diagnostics support autosize and a detailed description of the status words. These switches are a function of the remote load detect feature of the DMC11. After installation, the switches can be positioned to accommodate the user's requirements.

#### NOTE When used with the DMC11-AR or DMC11-AL Microprocessor, switch pack number 2 is the password and switch pack number 3 is the boot address offset.

For details concerning the use of these switches, refer to Chapter 3 in the microprocessor manual.

3. Switch Pack No. 1

Switch pack no. 1 is an 8 switch DIP that is installed in location E26 on the M8201 Line Unit and in location E29 on the M8202 Line Unit.

For the M8201, all switches except no. 5 are used. For the M8202, all switches except no. 4, 5, and 8 are used. The ON and OFF positions and the switch numbers are marked on the package. The switches are the rocker type and are pushed to the desired position.

Table 2-3 describes the normal configuration for switch pack no. 1.

| Switch<br>Number | Normal<br>Position | Function                                                                                                                                                                  |

|------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                | OFF                | With S1 OFF, signal D14 GRTP is low which enables the following ROMs.                                                                                                     |

|                  |                    | Transmitter Function Decode ROM<br>Transmitter Data Decode ROM<br>Receiver Decode ROM<br>Receiver Function ROM                                                            |

|                  |                    | During servicing with the automatic module tester, if S1 is ON, signal D14 GRTP is high, which disables these ROMs; manufacturing test only.                              |

| 2                | OFF                | With S2 OFF, signal D14 NO CRC is low, which allows the CRC function to be enabled.                                                                                       |

|                  |                    | With S2 ON, the CRC function is inhibited.                                                                                                                                |

| 3                | OFF                | With S3 OFF, signal D14 SEC MODE is low which in-<br>hibits operation of the line unit in the secondary mode.<br>This mode is applicable only in the Bit Stuff protocols. |

| 4                | OFF                | With S4 OFF, Received Data, Modem Receive Clock, and Modem Transmit Clock are presented to the line unit through the EIA/CCITT V.24 interface.                            |

Table 2-3Configuration of Switch Pack No. 1

| Switch<br>Number | Normal<br>Position | Function                                                                                                                                                                    |

|------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  |                    | With S4 ON, these signals are received through the CCITT V.35 interface.                                                                                                    |

|                  |                    | This switch is used only on the M8201 Line Unit.                                                                                                                            |

| 5                | OFF                | Not Used                                                                                                                                                                    |

| 6                | OFF                | Reserved                                                                                                                                                                    |

| 7                | Module Dependent   | Signal D14 SW is associated with this switch. It is read<br>only bit 1 of the Modem Control Register. It is read by<br>the diagnostics and indicates the type of line unit. |

|                  |                    | With an M8201 Line Unit, S7 should be ON (D14 SW is low).                                                                                                                   |

|                  |                    | With an M8202 Line Unit, S7 should be OFF (D14 SW is high).                                                                                                                 |

| 8                | ON                 | With S8 ON, the internal RC clock is sent to the modem cable connector (J1) on the M8201 Line Unit.                                                                         |

|                  |                    | During servicing with the H325 or H3250 test connector installed on the modem cable, the RC clock is sent back to the line unit as the transmit and receive clocks.         |

|                  |                    | During normal operation, the switch should remain ON.                                                                                                                       |

|                  |                    | This switch is used only on the M8201 Line Unit.                                                                                                                            |

#### Table 2-3 Configuration of Switch Pack No. 1 (Cont)

#### 2.4 INSTALLATION AND CHECKOUT

The M8201 and M8202 Line Units are hex modules that do not interface with the Unibus. The corner of the module in the vicinity of the A and B connectors has been removed. This allows the M8201 or M8202 to be installed in the end slots of the DD11-B, C, or D System Interfacing Units. The module plugs into connectors C, D, E, and F and fits over the Unibus cable connectors and short length (approximately 6.35 cm, 2.5 in) Unibus terminator that are installed in connectors A and B.

Proceed with the installation and checkout as follows.

- 1. Install the M8201 or M8202 Line Unit and check  $\pm 15$  V and  $\pm 5$  V supplies.

- 2. Interconnect the line unit and the microprocessor using cable BC08R-1 or BC08S-1 which is a 0.305 m (one foot) long 40 connector flat mylar cable with H856 female connectors on each end. The mating connector on the microprocessor and line unit is an H854 male connector. On the microprocessor this connector is designated J1. On the M8201 Line Unit it is designated J2 and on the M8202 Line Unit it is J1.

3. On the M8201 Line Unit, install the modem (DSU) cable to connector J1. For the DMC11-DA Line Unit, use the BC05C-25 cable. For the DMC11-FA Line Unit, use the BC05Z-25 cable. On the other end of this cable, install the test connector. Use the H325 connector for the BC05C-25 cable and the H3250 connector for the BC05Z-25 cable, with SP1, switch 4 on.

On the M8202 Line Unit, install the 12-12528 coaxial test connector which ties the two coaxial pig-tails together. These two 0.915 m (3 foot) cables are soldered to the M8202.

- 4. Run MAINDEC-11-DZDME and DZDMF to verify correct line unit operation.

- 5. The M8201 (DMC11-DA or FA) line unit and the M8200-YA (DMC11-AR) microprocessor, or the M8202-YA through YD (DMC11-MA through MD) line unit and the M8200-YB (DMC11-AL) microprocessor run the MAINDEC-11-DZDMG to verify the correct microcode, and MAINDEC-11-DZDMH to verify the operation of the line unit and the microprocessor working together.

- 6. Remove the test connector from the modem (DSU) cable.

M8201 – For the DMC11-DA, connect the BC05C-25 Cinch connector to the customer supplied modem. For the DMC11-FA, connect the BC05Z-25 Winchester connector to the customer supplied DSU.

M8202 - Connect the coaxial pig-tails to the customer supplied coaxial cables or the BC03N-A0 cable.

#### CAUTION The maximum allowable length for the BC05C or BC05Z cable is 15.24 m (50 ft).

#### 2.5 JUMPER AND SWITCH CHECKLIST

Table 2-4 represents a concise checklist of the M8201 and M8202 Line Unit switch settings and jumper configuration as shipped.

| Jumper Configuration  |                   |                     |                      |

|-----------------------|-------------------|---------------------|----------------------|

| Jumper<br>Designation | DMC11-DA<br>M8201 | DMC11-FA<br>M8201   | DMC11-MA/MD<br>M8202 |

| <b>W</b> 1            | IN                | IN                  | IN                   |

| W2                    | IN                | IN                  | OUT                  |

| W3                    | OUT               | OUT                 | OUT                  |

| W4                    | IN                | IN                  | OUT                  |

| W5                    | OUT               | OUT                 | OUT                  |

| W6                    | NA                | NA                  | IN FOR HD            |

|                       | Settings for      | Switch Pack No. 1   |                      |

| S1                    | OFF               | OFF                 | OFF                  |

| S2                    | OFF               | OFF                 | OFF                  |

| <b>S</b> 3            | OFF               | OFF                 | OFF                  |

| S4                    | OFF               | ON                  | OFF                  |

| S5                    | OFF               | OFF                 | OFF                  |

| S6                    | OFF               | OFF                 | OFF                  |

| <b>S</b> 7            | ON                | ON                  | OFF                  |

| <b>S</b> 8            | ON                | ON                  | OFF                  |

|                       | Settings for Swi  | tch Pack Nos. 2 and | 3                    |

| <br>S1-S8             | OFF               | OFF                 | OFF                  |

Table 2-4

Jumper and Switch Checklist

#### **NOTES:**

1. Switch Pack Locations

SP1-E26 on M8201 and E19 on M8202 SP2-E87 on M8201 and E90 on M8202 SP3-E88 on M8201 and E91 on M8202

2. All switches OFF in SP2 and SP3 represents the default status. Reference the DMC11 Microprocessor Manual for details on the use of these switches.

#### 2.6 LOCAL LINK CABLE

This section discusses the selection, installation, and maintenance of the local link cable. This cable serves two purposes. It must deliver the generated signal to the receiver with sufficient amplitude to exceed the receiver threshold and it must shield the signal from external electrical noise.

#### 2.6.1 Selection

DIGITAL does not sell cables over 100 ft for use with the DMC11-MA and DMC11-MD integral modem line units. DIGITAL recommends Belden 8232 for runs up to 1 km with the DMC11-MA, and 3 km with the DMC11-MD. Belden 8233 is recommended for longer runs; up to 2 km with the DMC11-MA, and 6 km with the DMC11-MD. Both cables are double shielded (triaxial). The electrical characteristics listed below are maximum/nominal values.

| <b>NOTE</b><br>The cable should be provided and installed by the customer. |                                                           |  |  |

|----------------------------------------------------------------------------|-----------------------------------------------------------|--|--|

| Inductance                                                                 | 0.318 microhenry/meter<br>(0.097 microhenry/ft)           |  |  |

| Capacitance                                                                | 56.7 pF/meter (17.3 pF/ft)                                |  |  |

| Vel. of Prop.                                                              | 78%                                                       |  |  |

| Impedance                                                                  | 75 ohms                                                   |  |  |

| Voltage Rating                                                             | 175 Vrms                                                  |  |  |

| Sweep Test                                                                 | 22 dB min.                                                |  |  |

| Center Conductor DC Resistance<br>Belden 8232                              | 112 ohms/km<br>(35 ohms/1000 ft)                          |  |  |

| Belden 8233                                                                | 8.5 ohms/km<br>(2.6 ohms/1000 ft)                         |  |  |

| Shield DC Resistance<br>Belden 8232                                        | 8.53 ohms/km<br>(2.6 ohms/1000 ft)                        |  |  |

| Belden 8233                                                                | 4.6 ohms/km<br>(1.4 ohms/1000 ft)                         |  |  |

| Physical Requirements                                                      | Triaxial, cellular polyethylene insulation, braid shield, |  |  |

and minimum of 20 AWG center conductor

(

The cable used must be 75 ohms impedance type. The maximum total dc resistance for the cable shield and center conductor must be less than 200 ohms for the DMC11-MA, and 400 ohms for the DMC11-MD. The maximum total capacitance from the shield to the center conductor must be less than 0.14  $\mu$ F for the DMC11-MA and 0.4  $\mu$ F for th DMC11-MD. The double shield provides excellent noise rejection when properly grounded. The cellular polyethylene dielectric provides low signal loss and low distortion. The polyethylene jacket has excellent weather and abrasion resistance.

#### NOTE

Typical cables using 20 AWG copper weld center conductors vary from 35 to 70 ohms dc resistance. Use of dc resistance over 35 ohms per 1000 ft severely derates the maximum length of the cable. The longer cable must use solid copper, 14 AWG.

When selecting cable, several factors must be considered in determining cable attenuation. The value given by the cable vendor is for room temperature and is nominal, being subject to deviation up to 20 percent. The attenuation increases with temperature at approximately 0.20 percent per degree Celsius (0.11 percent per degree Fahrenheit). At 50° C (122° F) an additional loss of 5 percent over the room temperature specification can be expected. Finally, use at elevated temperatures causes aging at a faster than normal rate and, after 5 years, could produce yet another permanent 10 percent increase in attenuation. Thus the initial nominal 8.53 dB/km (2.6 dB/1000 ft) loss could become, after 5 years use at high temperature, 17.06 dB/km (5.2 dB/1000 ft) worst case.

#### 2.6.2 Installation

The characteristics of the local link cable should be measured prior to installation. In particular, there are two parameters that the user should measure and note for future reference. These are the propagation time delay, which can be measured with a pulse generator and an oscilloscope, and the dc resistance of the cable with the far end of the center conductor shorted to the inner shield. For the Belden 8232, these parameters can be expected to be nominally 4.26 ns/m (1.30 ns/ft) and 105 ohms/km (320hms/1000 ft). For Belden 8233, these parameters can be expected to be nominally 4.26 ns/m (1.30 ns/ft) and 12 ohms/km (4 ohms/1000 ft). Once the cable is installed, and both ends are therefore not available at the same place, the latter parameter can still be measured easily, and the former can be measured by use of the TDR method described in Paragraph 2.6.3.

While installing the cable, make a complete map of its layout, showing the position of the cable with respect to buildings, equipment and so forth, and also the locations of all access points, including not only splices and in-line connectors, but pull boxes also. Carefully measure and record cable lengths between landmarks. Such a map will greatly facilitate maintenance.

The user must take the following factors into account when installing the local link cable.

TEMPERATURE – The polyethylene used as the dielectric material in most coaxial and triaxial cables begins to soften above 80° C. As the conductor moves off center, variations in cable characteristics occur. If installed under tension with sharp bends, the conductor may short to the shield. Additionally, the open circuit resistance should be measured after installation to ensure against shorts incurred during installation. This resistance should be  $\geq 20$  Kilohms. The closed circuit resistance should be 118.4 ohms/km (36.1 ohms/1000ft).

MOISTURE – Moisture or moisture-related impurities may enter the cable through cuts or scratches in the outer jacket or through improperly installed connectors. Minute amounts of water vapor will condense into water, which can migrate along the braid. Water condensed from a polluted atmosphere can contaminate the entire length of cable, shorten its lifetime, and seriously degrade performance. PULLING TENSION – For most environmental conditions, it is generally preferred that the cable be installed in conduit, through which the cable must be pulled. During installation, the total pulling tension on the 20 AWG center conductor must not exceed 8.8N (2 pounds).

For ease in maintenance, it is best to divide the cable into sections. For long cable runs in conduit, it is convenient to have a pull box every 30.48 m (100 ft) or equivalent. A 90 degree conduit bend is equal to 9.15 m (30 ft) of straight level conduit. It is recommended that an antifriction agent be used during pulling, provided the agent is compatible with the cable jacket material.

SPLICES AND CONNECTORS – The cable layout should provide access points for test purposes and for replacing defective sections. (See Paragraph 2.6.2.1.) Strain relief must be provided at all splices and in-line connectors.

**RECOMMENDED WIRING PRACTICES** – Chapter 8, Article 800 of the National Electric Code defines wiring rules for communications circuits. These rules must be observed for safe operation of the DMC11. In particular, note these provisions of the code:

"Communication conductors shall not be placed in a raceway, compartment, outlet box, junction box or similar fitting with conductors for light and power. . ."

"Communication conductors may be run in the same shaft with conductors for light and power provided the conductors of the two systems are separated by at least two inches."

"Suitable protective devices must be employed for wiring between buildings."

SURGE WITHSTAND CAPABILITY – The receiver has no provision for protection against normal mode voltage surges exceeding 30 V. If surge withstand is required, the user must install a separate circuit to condition signals to the receiver.

NOISE – The M8202 is designed to operate with a common mode rejection ratio  $\geq$  500:1. Cable selection, installation grounding and noise suppression are means of reducing line error rates.

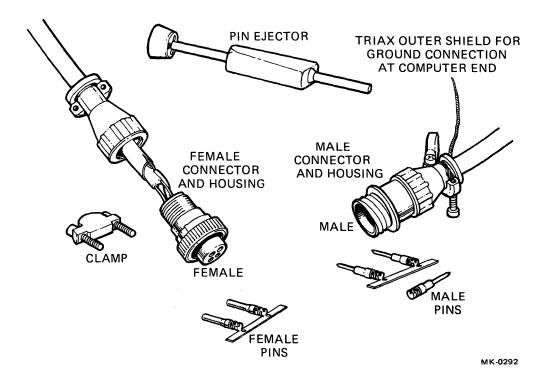

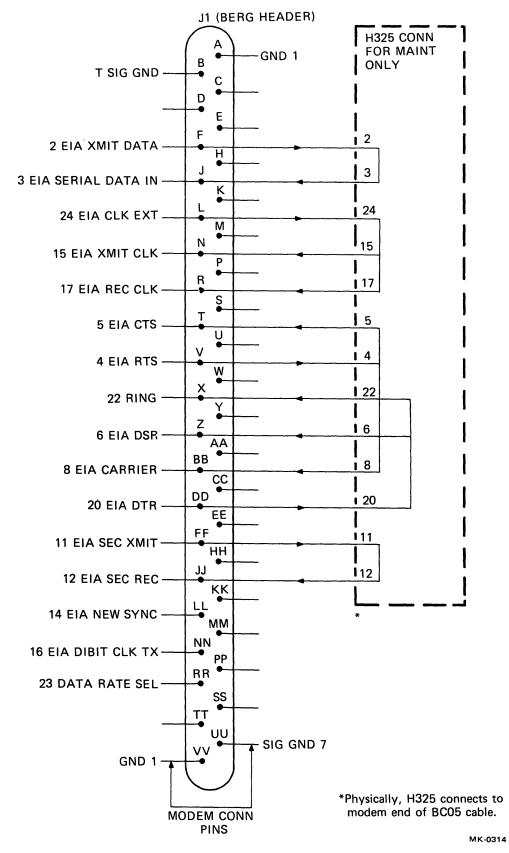

**2.6.2.1** Connectors – The following components are recommended for use in joining cable sections and also for connecting the cable to the M8202 pigtails. All of these components, which are shown in Figure 2-3, are manufactured by AMP Inc., Harrisburg, Pennsylvania.

| Component      | Digital Part Number | AMP Part No. |

|----------------|---------------------|--------------|

| Cable clamp    | 12-11430            | 206062-1     |

| Male housing   | 12-12527            | 206153-1     |

| Male pin       | 12-12001            | 66589-2      |

| Female housing | 12-12526            | 206060-1     |

| Female pin     | 12-12000            | 66590-2      |

| 14 ga male pin | 12-12001-1          | 66587-2      |

The connectors are installed by crimping the pins to the cable; the recommended crimper is the AMP Type V1, 90277-1. It is very unlikely that one can install a set of connectors without requiring the use of an ejector, to remove pins that have been inserted incorrectly; the proper ejector for the above pins is the AMP 305183.

Figure 2-3 Local Link Cable Connectors

The pin holes in the housing and receptacle are numbered. When working with a connector, always orient it so that hole 1 is at the top, then hole 4 is at the bottom, and the holes on either side are 2 and 3.

- 1. The cable clamp assembly is supplied as a shell, two screws, and three clamps, of which the one for the largest cable size should be used. Slide the shell onto the cable.

- 2. Dress the center conductor back enough so it will fit into a pin with the pin crimped to its insulation as well as to the conductor. Dress both shields back about another half inch, and taper the final half inch of the inner insulation so that its tip fits into the pin, and about a quarter inch fits into the connector, along with the center conductor. Crimp the pin to both the conductor and its insulation, and insert the pin in hole 1.

- 3. Separate the inner shield into two parts, attach pins to them, and insert the pins into holes 2 and 3.

- 4. Pull the outer shield together, insulate it from the inner shield, crimp a pin to it, and insert the pin in hole 4 for splicing connections. The end connectors should have the outer shield brought out of the shell and tied to the grounded wire.

- 5. Screw the shell into the housing, and screw the clamp to the shell.

- 6. After male and female connectors have been plugged together, screw the other ring of the female housing over the male housing.

Both M8202 pigtails have female connectors, therefore, the local link cable must have a male connector. The connectors at the ends of the cables are installed in the same manner described above except that at the ends the outer shield must be grounded as described in Paragraph 2.6.2.2. The male connector shown in Figure 2-3 is made up for a spliced connection. The wire sticking out the back end of the connector is the outer shield, which must be grounded.

**2.6.2.2** Grounding – This paragraph describes the proper grounding techniques that must be used to prevent the possibility of personal injury.

There is a possibility of a difference in ground potential between two computers that are separated by some distance, especially if they are powered from different sockets.

If in doubt about the recommendations in this paragraph, consult a competent professional for advice.

The following warnings should be adhered to.

#### WARNING

# 1. Never connect the outer shield of the local link cable to a computer cabinet or accessory.

#### 2. Always ground both ends of the local link cable.

The outer braided shield of the cable must be grounded near, but not to, the computer system chassis. The grounding conductor should be connected to a water pipe electrode, or if none is available, to the power service conduit, service equipment closure, or grounding electrode conductor where the ground ing conductor of the power service is connected to a water pipe electrode at the building.

When neither of the above means of grounding is available, it is permissible to connect the grounding conductor to the service conduit, service equipment enclosure, grounding electrode conductor, or grounding electrode of the power service of a multigrounded neutral power system.

If it is impossible to ground the cable shield by one of the above methods, connect the grounding conductor to one of the following:

- 1. A concrete-encased electrode of not less than 6.09 m (20 ft) of bare copper conductor, no smaller than 4 AWG, encased in at least 5.08 cm (2 in) of concrete, and located within and near the bottom of a concrete foundation footing that is in direct contact with the earth.

- 2. An effectively grounded metal structure.

- 3. A continuous and extensive underground gas-piping system, where acceptable to both the servicing gas supplier and to the authority having jurisdiction.

- 4. A ground rod or pipe driven into permanently damp earth.

#### NOTE

The minimum ground wire size is 4 AWG.

#### WARNING

Under no circumstances shall the grounding conductor be connected to a steam or hot water pipe, a lightning rod conductor, or pipe or rod electrodes grounding other than multiground neutral power circuits.

#### 2.6.3 Maintenance

For maintenance purposes, the user should keep a record of the initial cable characteristics, particularly the propagation time delay and short circuit line resistance as indicated at the beginning of Paragraph 2.6.2. Once the system is operational, record the received signal amplitude at the M8202. Then repeat this measurement at every scheduled PM date (at least four times per year). If a deviation of 20 percent is observed in the signal amplitude, disconnect both ends of the cable from the M8202 and measure both the open circuit and short circuit resistance of the line. If the measured open circuit resistance is less than 20 megohms, inspect the cable for contamination of the dielectric, and for adverse effects of sharp bends or stress points, elevated temperatures, or aging. If the line resistance with a shorted end increases above the value measured at installation, inspect the cable for loose connectors, contaminated connectors, and excessive tension.

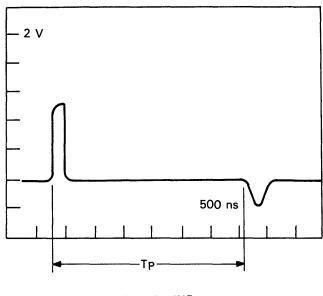

LOCATING A DEFECTIVE SECTION – An ohmmeter can be used to diagnose an open line or a low impedance shorted line, by checking one section at a time until the faulty section is located. If the cable is not partitioned into small enough sections, the distance to the fault can be measured by making use of time domain reflectometry (TDR).

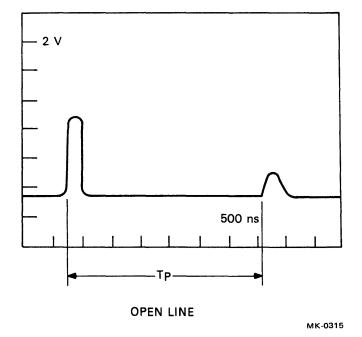

Although TDR cable testers are available from Tektronix and others, a pulse generator and oscilloscope can be used for approximate measurements. Disconnect both ends of the cable, and drive one end with a 5 V peak, 100 ns wide pulse with a repetition rate below 10 kHz. Measure the time interval between the leading edge of the driven pulse and the leading edge of the first reflection. The reflected pulse will be in the 10 mV to 1 V range. It will be normal for a line open, but inverted for a line short. Figure 2-4 shows typical oscilloscope traces for both cases. The time interval represents the propagation time delay for a round trip from the signal generator to the fault and back again. The distance D to the fault in feet (meters) is

$D = T_p/2p$

where  $T_p$  is the measured time delay in nanoseconds, and p is the propagation time in nanoseconds per foot (meter) recorded before the cable was installed.

#### 2.7 FULL-DUPLEX/HALF-DUPLEX OPERATION

The DMC11 is capable of either full-duplex or half-duplex operation. The microprogram controls the transmitter/receiver interaction in half-duplex mode in order to minimize the line control contention problems.

While there are few considerations required when selecting half-duplex operation of the DMC11-DA or DMC11-FA Line Units, careful thought should be given to the selection of full- or half-duplex operation of the DMC11-MA-DMC11-MD Line Units.

Full- or half-duplex operation of the DMC11-DA/FA requires selecting the proper data set and informing the microprogram that half-duplex mode has been selected.

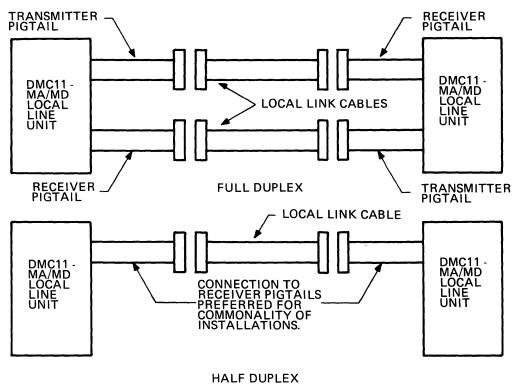

Operation of the DMC11-MA/MD Line Units require hardware considerations. Full-duplex operation requires two separate local link cables. Half-duplex operation requires only one. The two cable requirement for full-duplex operation cannot be eliminated through the use of a dual Coax/Triax cable.

SHORTED LINE

Figure 2-4 Signal Reflections from a Line Fault

ί

While full-duplex operation requires two cables, it also provides full throughput potential. Half-duplex operation implies half the throughput potential but requires only one cable. The following factors should be considered when selecting full-duplex or half-duplex operation.

- 1. Traffic Flow Is most of the data going one way or is data flow nearly equal in both directions?

- 2. Data Rate

- a. Is it necessary to use maximum data rate now and in the foreseeable future?

- b. Will the maximum data rate cause unibus latency problems?

- 3. Cable Expense Is the two cable full-duplex operation worth the expense?

The local link line units (DMC11-MA/MD) require installation of the W6 jumper for half-duplex operation. This allows either line unit pigtail to be used as the output connection to the local link cable.

The connection to the local link cable is made so that the local transmitter pigtail is connected to the distant receiver pigtail through the local link cable (Figure 2-5).

In the case of half-duplex operation, the connection to the local link cable is made with either of the pigtails (Figure 2-5).

MK-0291

Figure 2-5 Full-Duplex/Half-Duplex Connections

- . .....

### CHAPTER 3 PROGRAMMING

#### **3.1 INTRODUCTION**

This chapter contains general programming information. It is divided into two sections: one lists the register bit functions and the other discusses programming procedures.

#### 3.2 REGISTERS AND DEVICE ADDRESS SELECTION

The nine registers used in the line unit are shown in Table 3-1. They are all 8-bit registers.

The DMC11 (microprocessor plus line unit) is assigned a device address in the floating address space which includes addresses 760010 through 764000. The device address selection logic is located physically on the microprocessor module. The line unit registers are selected by four address signals from the microprocessor.

| Name                   | Address | Comments                                |

|------------------------|---------|-----------------------------------------|

| In Data Silo           | 10      | Read-only                               |

| Out Data Silo          | 10      | Write-only                              |

| Out Control Register   | 11      | Read/write                              |

| In Control Register    | 12      | Read/write                              |

| Modem Control Register | 13      | Read/write                              |

| Sync Register          | 14      | Read/write                              |

| Register 15            | 15      | Bits are switch selectable<br>Read-only |

| Register 16            | 16      | Bits are switch selectable<br>Read-only |

| Maintenance Register   | 17      | Read/write                              |

Table 3-1Line Unit Registers

#### 3.3 REGISTER BIT ASSIGNMENTS

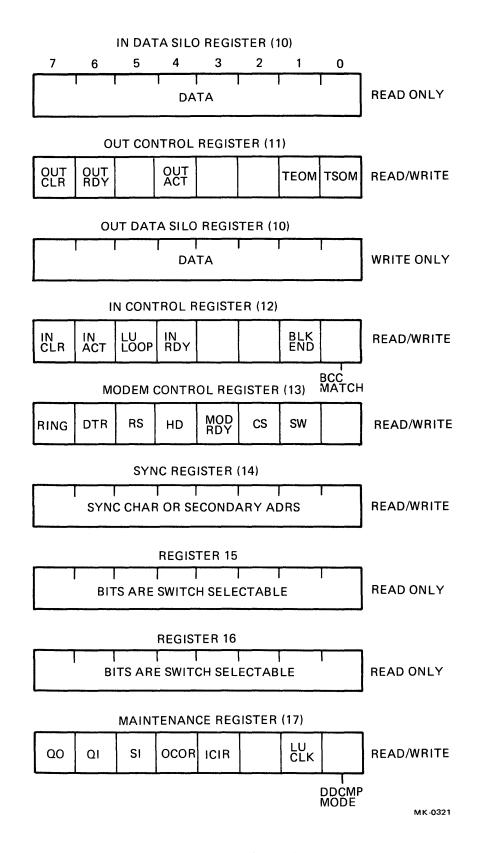

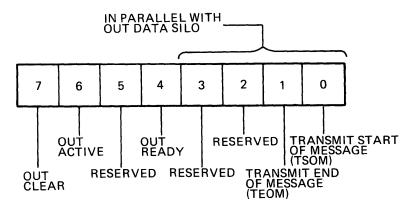

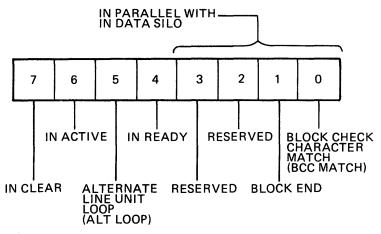

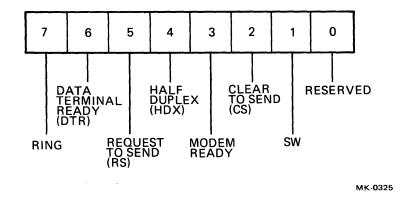

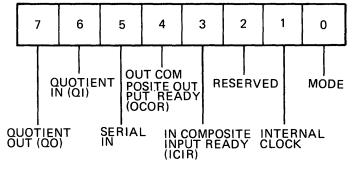

Bit assignments for all the registers are shown in Figure 3-1. If applicable, the register is described by showing a bit assignment illustration and an accompanying table that discusses each bit in detail.

Figure 3-1 Line Unit Register Configurations and Bit Assignments

The cable that connects the line unit and the microprocessor contains two buses. The IN BUS (IBUS) carries information from line unit to the microprocessor. The OUT BUS (OBUS) carries information from the microprocessor to the line unit.

### 3.3.1 Data Silo Registers

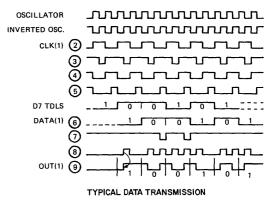

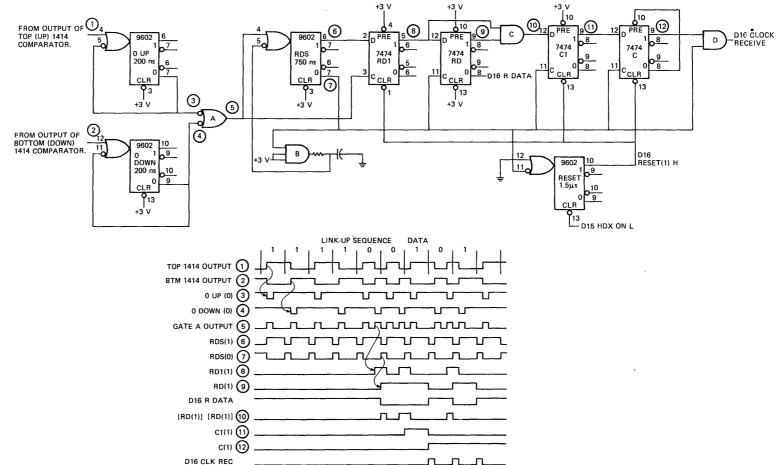

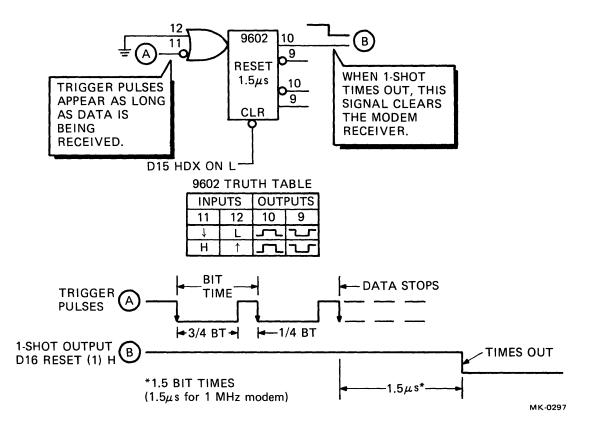

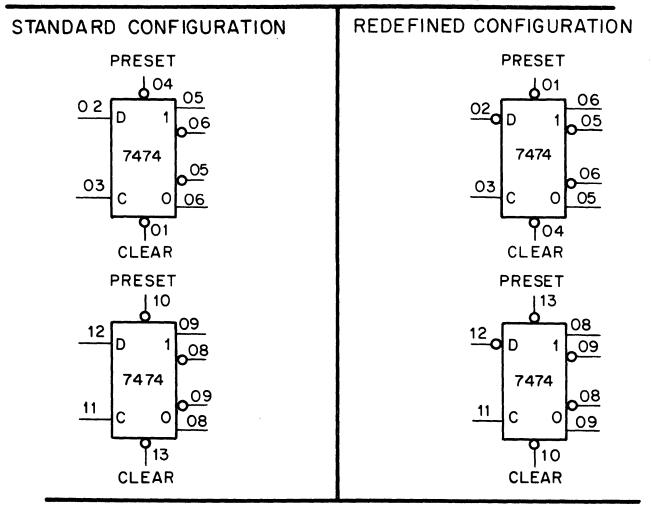

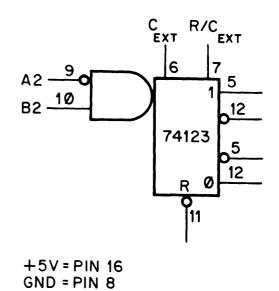

The line unit contains two data silo registers. The In Data Silo is the read-only data path for characters going from the receiver to the microprocessor. The Out Data Silo is the write-only data path for characters going from the microprocessor to the transmitter. The two buses (In Bus and Out Bus) that interconnect the line unit and microprocessor allow these registers to share the same address (10 octal). When register 10 is selected on the In Bus, the data in the In Data Silo is read by the microprocessor. This is an 8-bit data character from the receiver. When register 10 is selected on the Out Bus, the microprocessor writes data into the Out Data Silo. This is an 8-bit data character to be transmitted.