1986

1986

# Semiconductor Databook

Semiconductors in your future...

1986

## Semiconductor Databook

Semiconductors in your future...

Digital Equipment Corporation makes no representation that the interconnection of its products in the manner described herein will not infringe on existing or future patent rights, nor do the descriptions contained herein imply the granting of license to make, use, or sell equipment constructed in accordance with this description.

Digital believes the information in this publication is accurate as of its publication date; such information is subject to change without notice. Digital is not responsible for any inadvertent errors.

The following are trademarks of Digital Equipment Corporation: CTS-300, DATATRIEVE, DEC, DEC, DEC, DECnet, DECservice, DIBOL-83, the Digital logo, DSM-11, FMS, FORTRAN IV, Internet, LA, Letterprinter 100, Letterwriter 100, MicroPDP-11/23, MicroPDP-11/73, MicroPower/Pascal, Micro/RSTS, Micro/RSX, MicroVAX, MicroVMS, Packetnet, PDP, Professional, Q-bus, Rainbow, ReGIS, RSTS, RSX, RT, ULTRIX, UNIBUS, VAX, VAXELN, VMS, VT.

This handbook was produced by Digital Equipment Corporation, Corporate Communications Group, 200 Baker Avenue, West Concord, Massachusetts 01742.

Copyright © 1986 Digital Equipment Corporation. All Rights Reserved.

#### **Disclaimer and Proprietary Notice**

This databook contains proprietary product information that should not be distributed outside of Digital Equipment Corporation without proper authorization. The product information is believed to be reasonably accurate at the time of publication. However, it was compiled from engineering and purchase specifications, data sheets, and other technical sources that are subject to change or are under ECO control. If discrepancies in the documentation are found or revisions and corrections are required, please report them to

Digital Equipment Corporation Semiconductor Marketing Group HL02-1/N11 Hudson, Massachusetts 01749-2809

#### - New Products in Development

The following products are currently in development at the Semiconductor Engineering Group, Hudson, Massachusetts. All information related to these products should be considered preliminary and subject to change.

For more information, contact Hudson hotline at DTN 225-5061 (617-568-5061) or HUDSON::HOTLINE.

The information in this section is proprietary and should be handled in accordance with DEC STD 128, Confidential Engineering Information and Documentation: Policy and Requirements.

| Part     | Device                                                                                                                                          | Documentation                                                                                            |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| 78690-GB | Dragon (ADDER II)—Custom video processor<br>interface for the subsystem plus single pixel clipping<br>attribute.                                | Product bulletin<br>Product brief (preliminary)<br>Data sheet (preliminary)<br>Engineering specification |

| 78680-GA | SCVIPER—Standard cell CMOS version of the 78660 video processor (VIPER).                                                                        | Product bulletin<br>Product brief (preliminary)<br>Data sheet (preliminary)<br>Engineering specification |

| 78620-GA | Video D/A Converter (VDAC)—Custom color map<br>and digital-to-analog converter device.                                                          | Engineering specification                                                                                |

| 78630-GA | VAXStar Monochrome Timing Chip (VMTC)—<br>Semicustom video device for monochrome timing.                                                        | Engineering specification                                                                                |

| 78640-GA | Dragon Timing Chip (DTC)—Semicustom video device for color timing                                                                               | Engineering specification                                                                                |

| 78650-GA | FIFO Compression Chip (FCC)—Semicustom FIFO and data compression device.                                                                        | Engineering specification                                                                                |

| DC501    | Terminal Wire Concentrator (TWC)—Custom VLSI device that provides the main function of the Janus terminal interconnect products.                | Engineering specification                                                                                |

| DC508    | Analog-to-Digital/Digital-to-Analog (ADDA) converter.                                                                                           |                                                                                                          |

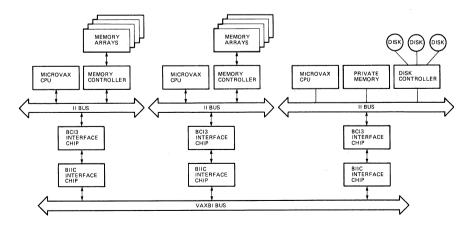

| DC514    | Second-generation CMOS VAXBI Interface Chip<br>(CBIC)—Combines the functionality of the VAXBI<br>78732 BIIC and VAXBI 78743 BCAI on one device. | Engineering specification                                                                                |

| DC518    | CI-2 Link Protocol Chip—Implements the UltraNet full-duplex link protocol.                                                                      | Engineering specification                                                                                |

| DC519    | CI-2 Switch Chip—Provides "crossbar" intercon-<br>nect for five standard UltraNet Interfaces.                                                   | Engineering specification                                                                                |

| Part  | Device                                                                                                                                                                                                                                                                                                                         | Documentation             |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| 78034 | CVAX Central Processor Unit (CVAX CPU)—High<br>performance 32-bit virtual memory microprocessor:<br>CMOS implementation of the MicroVAX architec-<br>ture; provides 2.7 to 3.3 times the performance of<br>the MicroVAX 78032 CPU.                                                                                             | Engineering specification |

| 78134 | CVAX Floating-point Accelerator (CFPA)—<br>Designed for use with the CVAX CPU; high-per-<br>formance floating-point coprocessor that processes<br>F_, D_, and G_ format floating-point instructions.                                                                                                                           | Engineering specification |

| 78135 | CVAX Clock Chip (CCLOCK)—Supports CVAX-<br>based systems by providing all the precision MOS<br>clock signals necessary to operate the CVAX CPU,<br>CFPA, and CVAX Memory Controller (CMCTL).                                                                                                                                   | Engineering specification |

| 78588 | CVAX Memory Controller (CMCTL)—Engineering<br>specification features two memory error checking<br>modes (ECC or parity); performs single- and multi-<br>ple-transfer memory read and write operations initi-<br>ated by either the CVAX 78034 or external DMA<br>devices.                                                      | Engineering specification |

|       | RTVAX Central Processor Unit—The Realtime<br>MicroVAX CPU is a unique version of the MicroVAX<br>78032 CPU. Because it will run VAXELN and VAX<br>applications and not VMS, it is ideal for applications<br>such as realtime controllers and dedicated I/O<br>processors.                                                      |                           |

| 78332 | System Support Chip (SSC)—Incorporates the core<br>functions required to support the VAX environment<br>on a single chip to enable significant cost savings on<br>module space. Also interfaces with the MicroVAX<br>78032 CPU.                                                                                                | Engineering specification |

| 78534 | CVAX DMA Controller (CDMA)—High-perform-<br>ance, dual-ported, virtual memory DMA controller<br>that features full VAX-11 compatible paged memory<br>management capabilities; provides a simple inter-<br>face to the CVAX CPU bus for intelligent I/O subsys-<br>tems and can function with 8, 16, and 32-bit I/O<br>devices. | Engineering specification |

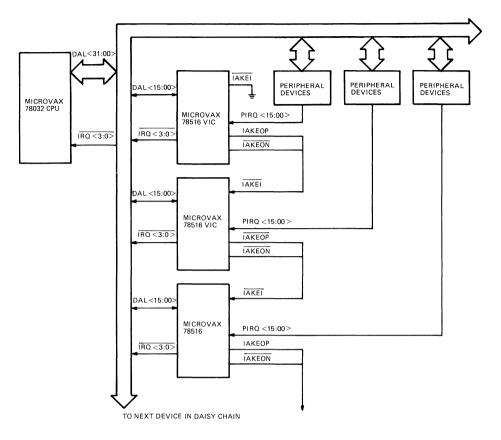

| 78516 | Vectored Interrupt Controller (VIC)—Featured in<br>Section 1 of this databook can also be used with the<br>CVAX 78034 CPU.                                                                                                                                                                                                     |                           |

## Functional Product Classification

| Name                                                                                                                               | Number                                                                                                                                                                           | Description                                                                                                                                                                                                                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Microprocessor s                                                                                                                   |                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                         |

| 78032<br>78132<br>78532<br>78516<br>78584<br>ADVICE                                                                                | 21-20887-01<br>21-22797-01<br>21-24329-01<br>21-24334-01<br>21-23864-01                                                                                                          | MicroVAX 32-bit CPU<br>MicroVAX Floating-point Unit<br>MicroVAX Direct Memory Access<br>MicroVAX Vectored Interrupt Controller<br>MicroVAX Dynamic RAM Controller<br>MicroVAX Incircuit Emulation Unit                                                                                  |

| DC327<br>DC328<br>DC329<br>DC330                                                                                                   | 21-20852-AA<br>21-20851-AA<br>21-20850-AA<br>21-20849-AA                                                                                                                         | V-11 ROM/RAM<br>V-11 Instruction/Execution Logic<br>V-11 Memory Management Logic<br>V-11 Floating-point Accelerator Logic                                                                                                                                                               |

| DCJ11<br>FPJ11                                                                                                                     | 21-21858-00                                                                                                                                                                      | DCJ11 16-bit Microprocessor<br>FPJ11 Floating-point Accelerator                                                                                                                                                                                                                         |

| DCT11                                                                                                                              | 21-17311-01                                                                                                                                                                      | DCT11 16-bit Microprocessor                                                                                                                                                                                                                                                             |

| Video Controllers                                                                                                                  |                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                         |

| 78610<br>78660<br>78690                                                                                                            | 21-24941-01<br>21-21552-01<br>21-21553-01                                                                                                                                        | Programmable Sprite Cursor<br>Video Processor (VIPER)<br>Video Control (ADDER)                                                                                                                                                                                                          |

| Communications                                                                                                                     |                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                         |

| 78808<br>DC319                                                                                                                     | 21-23458-01<br>21-17312-00                                                                                                                                                       | Octal ART<br>DLART                                                                                                                                                                                                                                                                      |

| Bus Support                                                                                                                        |                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                         |

| 78071<br>78072<br>78732<br>78733<br>78743<br>DC003<br>DC004<br>DC005<br>DC006<br>DC010<br>DC013<br>DC021<br><i>General Purpose</i> | 19-22110-01<br>19-22111-01<br>21-21689-00<br>21-23839-01<br>21-23838-01<br>19-12730-00<br>19-12729-00<br>19-13040-00<br>19-14035-00<br>19-14038-00<br>19-14438-00<br>19-19015-00 | VAXBI Clock Driver<br>VAXBI Clock Receiver<br>VAXBI BIIC<br>VAXBI BCI3<br>VAXBI BCAI<br>Dual-interrupt Circuit<br>Register Selector (Protocol Chip)<br>4-Bit Transceiver<br>Word Count/Bus Address Logic<br>Direct Memory Access Logic<br>UNIBUS Request Logic<br>Octal Bus Transceiver |

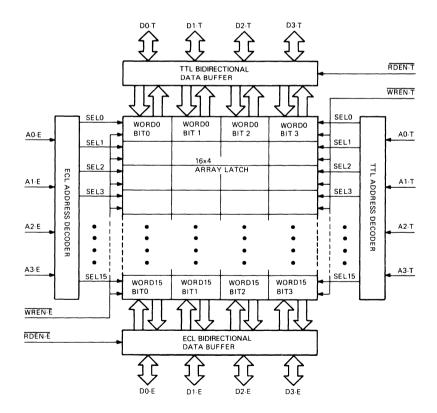

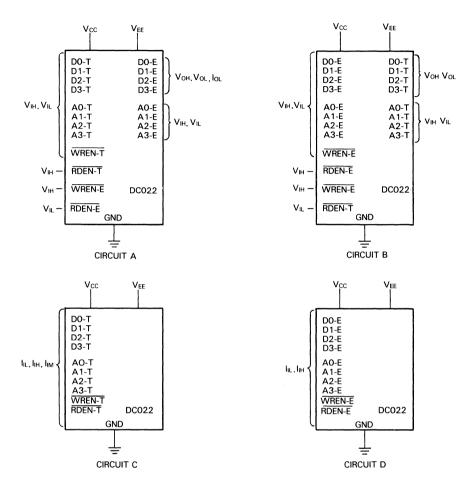

| DC022                                                                                                                              | 19-17871-00                                                                                                                                                                      | 16-word by 4-bit Register File                                                                                                                                                                                                                                                          |

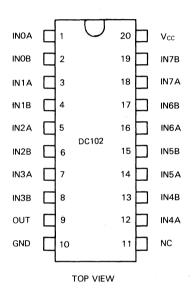

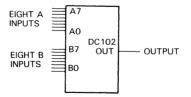

| DC102<br>DC301                                                                                                                     | 19-13888-00<br>21-12623-00                                                                                                                                                       | Equals Checker<br>Dual Baud Rate Generator                                                                                                                                                                                                                                              |

| Mass Storage Supp                                                                                                                  | ort                                                                                                                                                                              |                                                                                                                                                                                                                                                                                         |

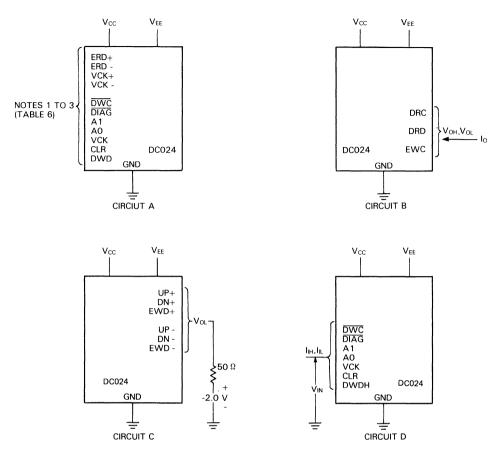

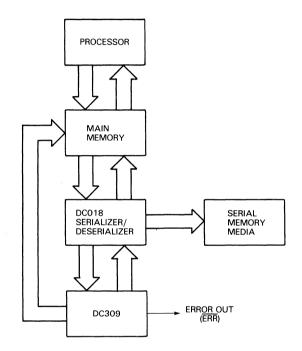

| DC018<br>DC024<br>DC309                                                                                                            | 19-19015-00<br>19-20116-01<br>21-15102-00                                                                                                                                        | Serializer/Deserializer Logic<br>Encoder/Decoder Logic<br>Reed Solomon Generator                                                                                                                                                                                                        |

## Part Identification Codes

The following identification codes are used with the devices in this databook.

#### 780 Series

78xyz

| $\uparrow$ 0 = Processors | 5 = Controllers            |

|---------------------------|----------------------------|

| 1 = Coprocessor           | 6 = Graphic devices        |

| 2 = Memories              | 7 = Bus interfaces         |

| 3 = I/O Devices           | 8 = Communications devices |

| 4 = Reserved              | 9 = Reserved               |

| DC Series                 |                            |

## DCxyz

| 1 | 0 = Custom bipolar devices | 5 = MOS devices |

|---|----------------------------|-----------------|

|   | 1 = Custom bipolar devices | 5 = MOS devices |

## Cross-referencing of Semiconductor Products

| Part  | Part     | Purchase      | Description                           |

|-------|----------|---------------|---------------------------------------|

| Name  | Number   | Number        |                                       |

| DC003 | DC003    | 19-12730-00   | Dual-interrupt Circuit                |

| DC004 | DC004    | 19-12729-00   | Register Selector (Protocol) Logic    |

| DC005 | DC005    | 19-13040-00   | 4-bit Transceiver                     |

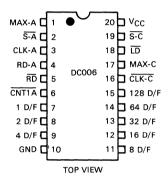

| DC006 | DC006    | 19-14035-00   | Word Count/Bus Address Logic          |

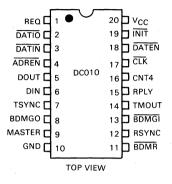

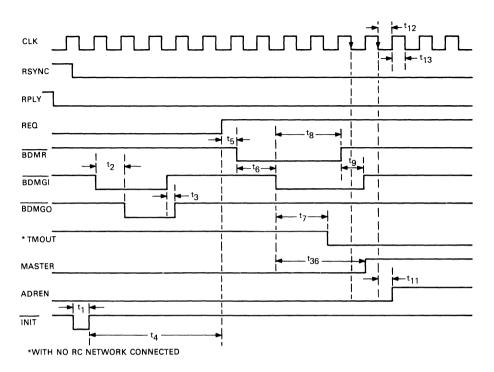

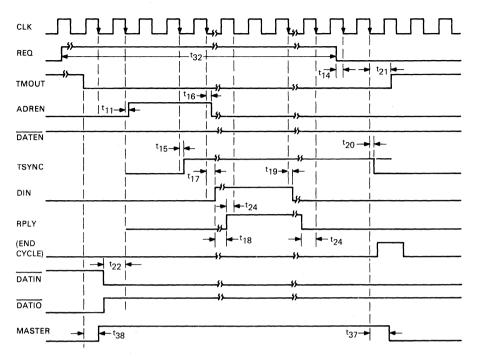

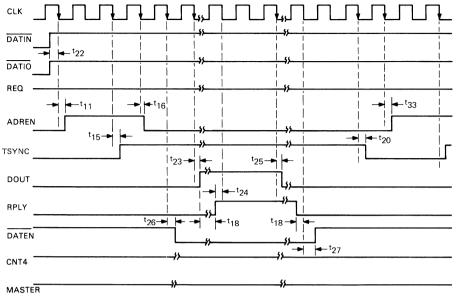

| DC010 | DC010    | 19-14038-00   | Direct Memory Access                  |

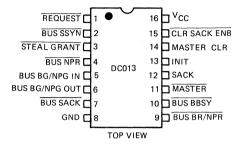

| DC013 | DC013    | 19-14438-00   | UNIBUS Request Logic                  |

| DC018 |          | 19-17043-00/1 | Serializer/Deserializer               |

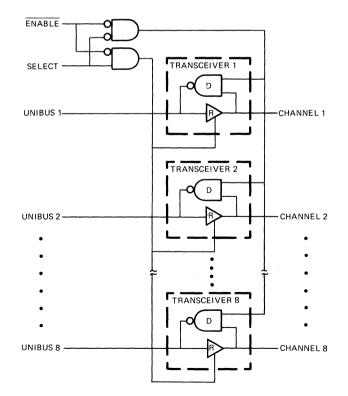

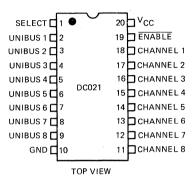

| DC021 | DC021    | 19-19015-00   | Octal Bus Transceiver                 |

| DC022 | _        | 19-17871-00   | 16-Word by 4-bit Register File        |

| DC024 |          | 19-20116-01   | Encoder/Decoder Logic                 |

| DC028 | 78701    | 19-22110-01   | VAXBI Clock Driver                    |

| DC029 | 78072    | 19-22111-01   | VAXBI Clock Receiver                  |

| DC102 |          | 19-13888-00   | Equals Checker                        |

| DC301 |          | 21-12623-00   | Dual Baud Rate Generator              |

| DC309 |          | 21-15102-00   | Reed Solomon Generator                |

| DC310 | DCT11    | 21-17311-01   | DCT11 16-bit Microprocessor           |

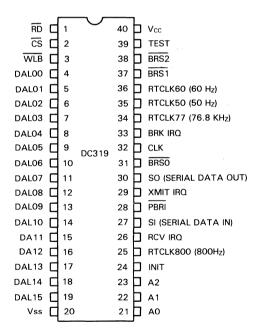

| DC319 | DC319    | 21-17312-00   | DLART                                 |

| DC321 | FPJ11    | 21-21858-00   | FPJ11 Floating-point Accelerator      |

| DC322 | 78660-GA | 21-21552-01   | Video Processor (VIPER)               |

| DC323 | 78690-GA | 21-21553-01   | Video Control (ADDER)                 |

| DC324 | 78732-PA | 21-21689-00   | VAXBI BIIC                            |

| DC327 |          | 21-20852-AA   | V-11 ROM/RAM                          |

| DC328 |          | 21-20851-AA   | V-11 Instruction/Execution Logic      |

| DC329 | <u> </u> | 21-20850-AA   | V-11 Memory Management Logic          |

| DC330 |          | 21-20849-AA   | V-11 Floating-point Accelerator Logic |

| DC333 | 78032-GA | 21-20887-01   | MicroVAX 32-bit CPU                   |

| DC335 | DCJ11    | 21-17679-00   | DCJ11 16-bit Microprocessor           |

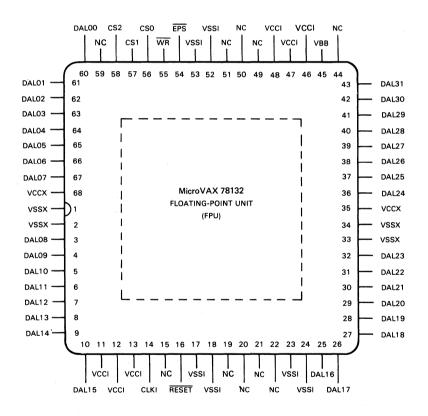

| DC337 | 78132-GA | 21-22797-01   | MicroVAX Floating-point Unit          |

| DC343 | 78743-PA | 21-23838-01   | VAXBI BCAI                            |

| Part<br>Name | Part<br>Number | Purchase<br>Number | Description                                  |

|--------------|----------------|--------------------|----------------------------------------------|

| DC344        | 78733-PA       | 21-23839-01        | VAXBI BCI3                                   |

| DC349        | 78808-GA       | 21-23458-01        | Octal ART                                    |

| DC357        | 78584-GA       | 21-23864-01        | Dynamic RAM Controller (DYRC)                |

| DC358        | 78532-GA       | 21-24329-01        | MicroVAX Direct Memory Access (DMA)          |

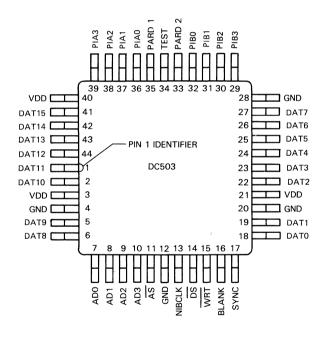

| DC503        | 78610-GA       | 21-24941-01        | Programmable Sprite Cursor                   |

| DG506        | 78516-GA       | 21-24334-01        | MicroVAX Vectored Interrupt Controller (VIC) |

| ADVICE       | ADVICE         | _                  | MicroVAX Incircuit Evaluation/Emulation Unit |

#### Foreword

Who would have thought 10 years ago that by 1986 Digital would have its own semiconductor facility, and further, that the products we would produce would challenge the state-of-the-art. As a result of the vision of our management in the early 1970s, we embarked on a strategy that eventually led us to such a facility with processes and products that truly are a step ahead.

Our MicroVAX 78032 CPU chip and its associated peripherals represent the leading edge in processor technology. No other company has been able to match the performance or price of this product, although many have tried.

Our next generation of products, based on further improvements in process and manufacturing technology and more sophisticated CAD, will continue this trend. The chipsets we are building to satisfy the Team Computing requirements are equally impressive.

As the competition from IC vendors in this country and Japan intensifies in our system markets, you can depend on a helping hand from the people at the semiconductor facility in Hudson, Massachusetts. We will be there offering you the leading edge in system-engineered products using the most advanced semiconductor technology available, at reasonable prices. This is our main strategy. We are here to give the systems designers at Digital direct access to the technology they need to keep our systems products the best in the world.

As we move into the next year and our product line expands, you can feel confident in our ability to compete successfully in the marketplace. More important, you can feel confident about your ability to contribute to the solution of many of the problems that face our world by offering the computing tools necessary to understand, manage, and respond to the difficult challenges that we face.

We certainly hope you will find as much excitement in using these products as we have had in bringing them to you.

Sincerely,

tim

Leonard J.Umina Manager, Semiconductor Marketing Group

,

## Contents

#### Section 1 • Microprocessors and Support Devices

| MicroVAX 78032 32-bit Central Processing Unit         | 1-1   |

|-------------------------------------------------------|-------|

| MicroVAX 78132 Floating-point Unit                    | 1-59  |

| MicroVAX 78516 Vectored Interrupt Controller          | 1-79  |

| MicroVAX 78532 Direct Memory Access                   | 1-103 |

| MicroVAX 78584 Dynamic RAM Controller                 | 1-169 |

| MicroVAX Incircuit Emulator Unit                      | 1-193 |

| Introduction to the V-11 Chipset                      | 1-201 |

| DC327 V-11 Processor ROM/RAM Logic                    | 1-203 |

| DC328 V-11 Processor Instruction/Execution Logic      | 1-211 |

| DC329 V-11 Processor Memory Management Logic          | 1-219 |

| DC330 V-11 Processor Floating-point Accelerator Logic | 1-235 |

| DCJ11 16-bit Microprocessor                           | 1-243 |

| FPJ11 Floating-point Accelerator.                     | 1-317 |

| DCT11 16-bit Microprocessor                           | 1-343 |

#### Section 2 - Video Processors and Controllers

| 78660/78680 Video Processor (VIPER). | 2-1  |

|--------------------------------------|------|

| 78690 Video Control (ADDER)          | 2-31 |

| DC503 Programmable Sprite Cursor     | 2-75 |

#### Section 3 - Communications Devices

| 78808 Eight-channel Asynchronous Receiver/Transmitter   | 3-1  |

|---------------------------------------------------------|------|

| DC319 DL11 Compatible Asynchronous Receiver/Transmitter | 3-27 |

#### Section 4 • Bus Support Devices

| VAXBI 78732 General Purpose Bus Interconnect Interface | 4-1   |

|--------------------------------------------------------|-------|

| VAXBI 78743 BCI Adapter Interface                      | 4-133 |

| VAXBI 78733 BCI Bus to MicroVAX II Bus Interface       | 4-157 |

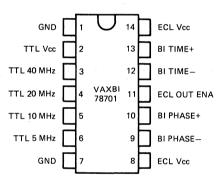

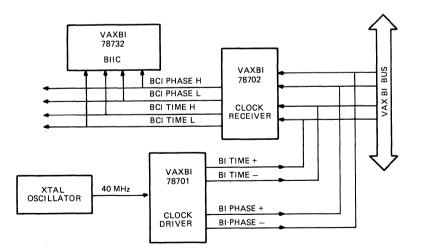

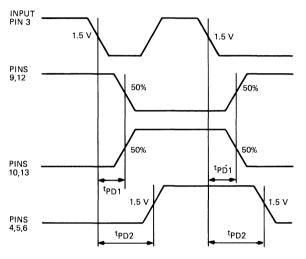

| VAXBI 78701 Clock Driver                               | 4-189 |

| VAXBI 78701 Clock Receiver                             | 4-201 |

| DC003 Dual-interrupt Logic                             | 4-211 |

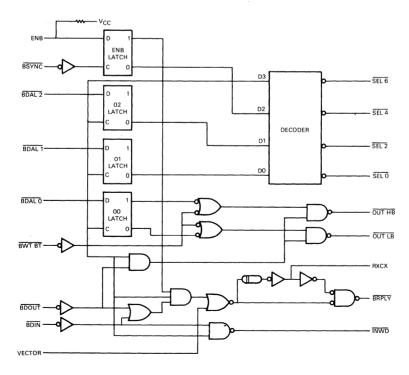

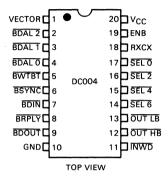

| DC004 Register Select (Protocol) Logic.                | 4-221 |

| DC005 4-Bit Transceiver                                | 4-231 |

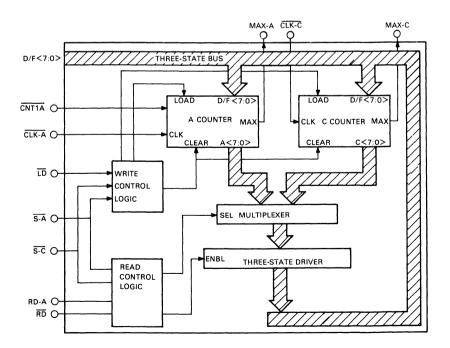

| DC006 Word Count/Bus Address Logic                     | 4-241 |

| DC010 Direct Memory Access Logic                       | 4-253 |

| DC013 UNIBUS Request and Control Logic                 | 4-267 |

| DC021 Octal Bus Transceiver                            | 4-275 |

|                                                        |       |

#### Section 5 • Mass-storage Devices

| DC018 Serializer/Deserializer Logic  | 5-1  |

|--------------------------------------|------|

| DC024 Encoder/Decoder Logic          |      |

| DC309 Reed Solomon Generator for ECC | 5-49 |

#### Section 6 • General Purpose Devices

| DC022 16-Word by 4-bit Register File | 6-1  |

|--------------------------------------|------|

| DC102 Eight-channel Equals Checker   | 6-23 |

| DC301 Dual Baud Rate Generator       | 6-31 |

## Appendixes

| Appendix A • MicroVAX 78032 CPU and MicroVAX 78132 FPU Instruction Set | A-1 |

|------------------------------------------------------------------------|-----|

| Appendix B • DCT11 and DCJ11 Microprocessors Instruction Set           | B-1 |

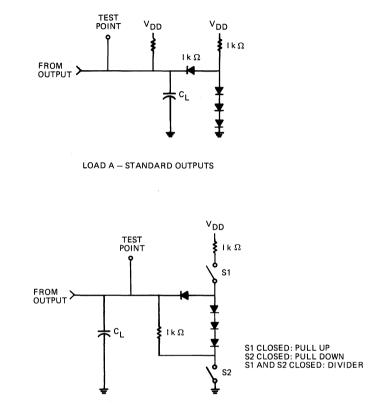

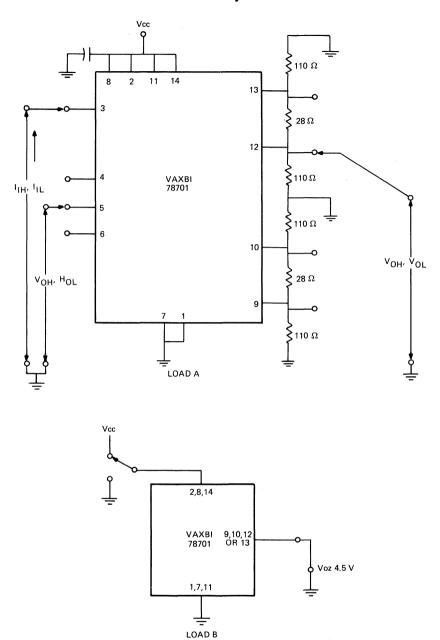

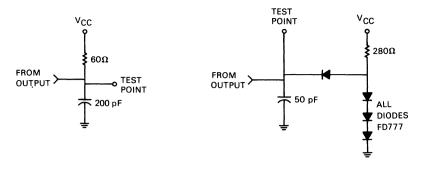

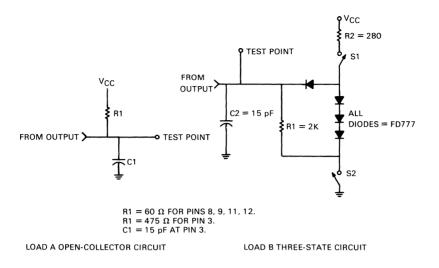

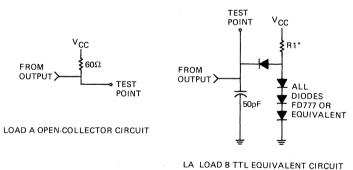

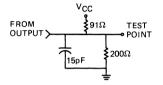

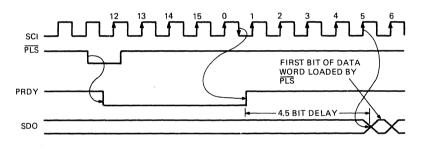

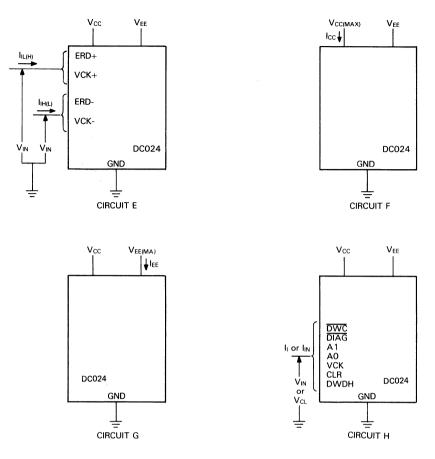

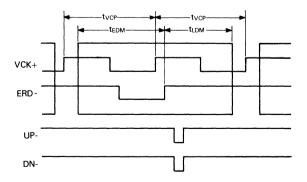

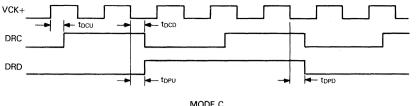

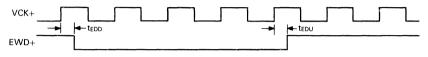

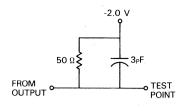

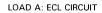

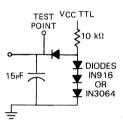

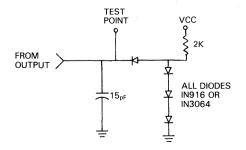

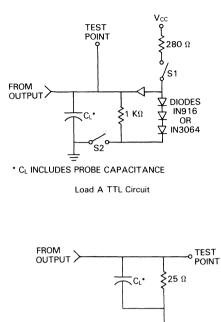

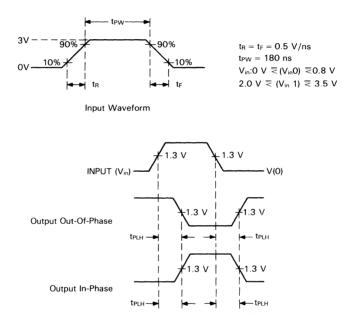

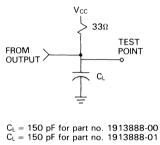

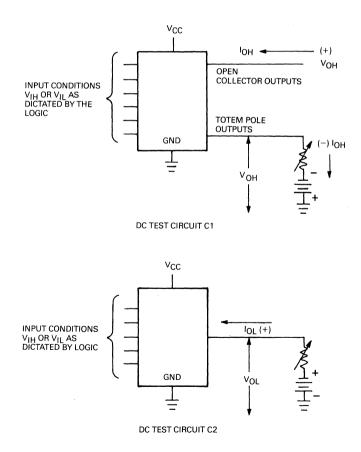

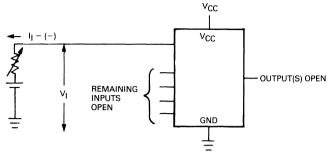

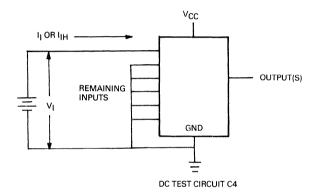

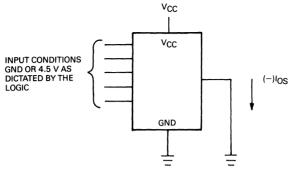

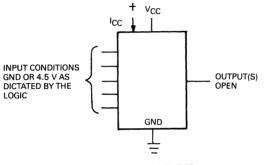

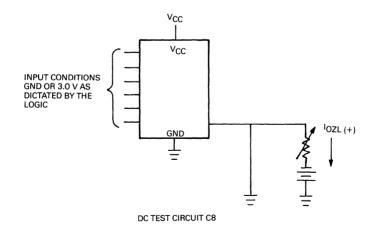

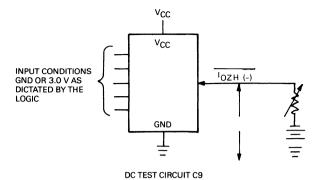

| Appendix C • dc Specification Test Circuits                            | C-1 |

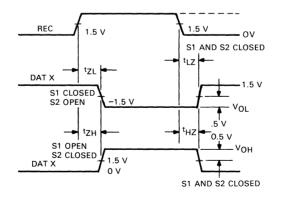

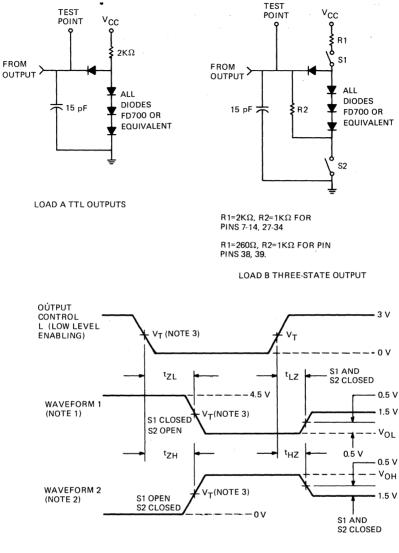

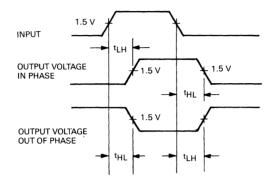

| Appendix D • Input/Output Voltage Waveform Parameters                  | D-1 |

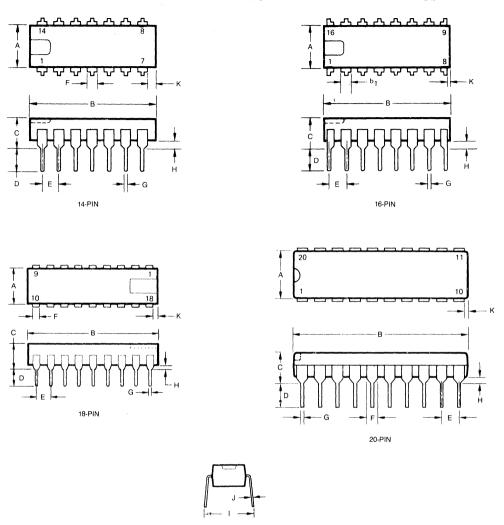

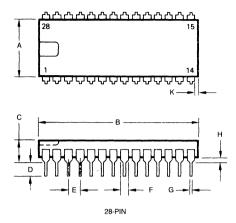

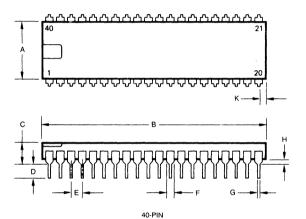

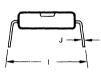

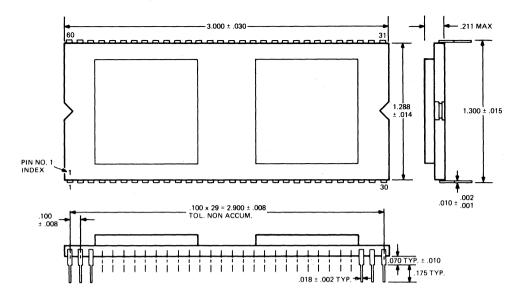

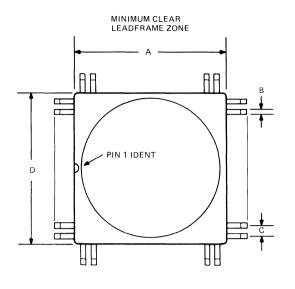

| Appendix E • Mechanical Specifications.                                | E-1 |

#### - Section 1—Microprocessor and Support Devices

The microprocessors and support devices provide a low-cost means to implement the power and versatility of the PDP-11 and VAX computers into system designs.

#### MicroVAX 32-bit Microprocessor

*MicroVAX 78032 Central Processing Unit*—The MicroVAX CPU is a 32-bit high-performance microprocessor that contains the architecture and functions of a VAX minicomputer. The MicroVAX 78032 implements a subset of the VAX instruction set and full VAX-11 memory management. It is fabricated in ZMOS (double metal NMOS) and is contained in a single 68-pin package.

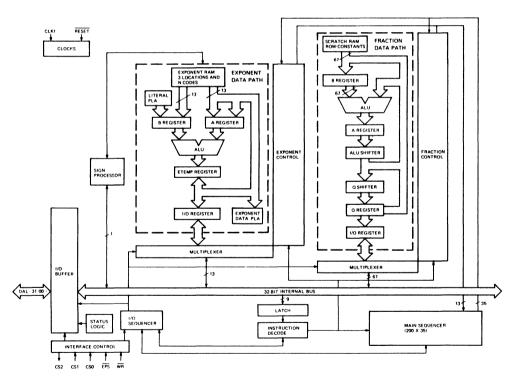

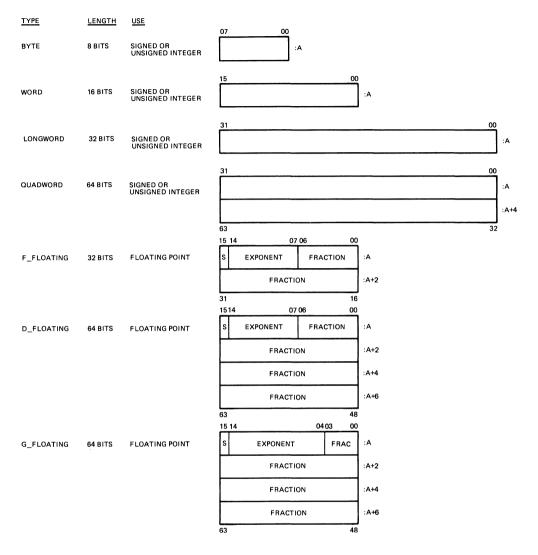

*MicroVAX 78132 Floating-point Unit*—The MicroVAX FPU is a high-performance cooperative processor used to accelerate the floating-point instructions of the MicroVAX 78032 CPU. It supports floating-point add, subtract, multiply, divide, and convert and other VAX-11 floating-point operations. The FPU is fabricated in ZMOS and is contained in a 68-pin package.

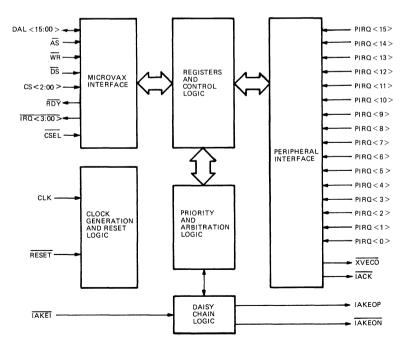

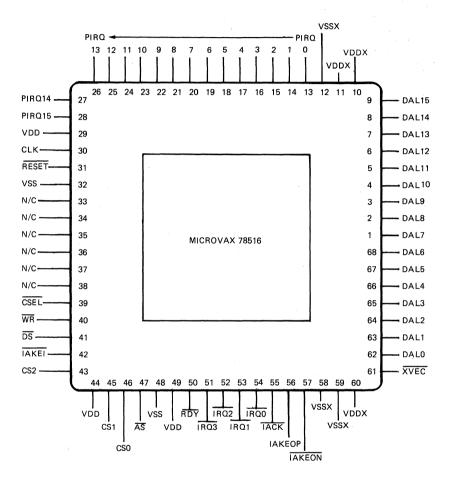

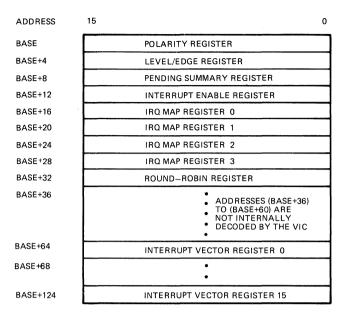

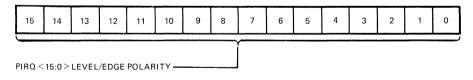

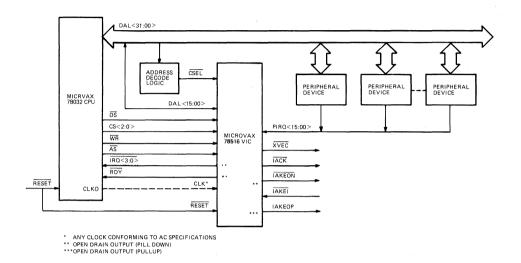

*MicroVAX* 78516 Vectored Interrupt Controller—The VIC is a programmable interrupt controller that is fully compatible with the MicroVAX 78032 CPU. The 78516 VIC services up to 16 interrupt sources, resolves interrupt priorities, drives the IRQ lines of the CPU, and provides a programmable 16-bit interrupt to the CPU. It is fabricated in high-speed CMOS and is contained in a 68-pin package.

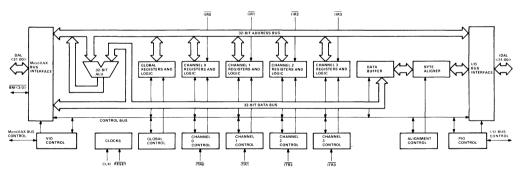

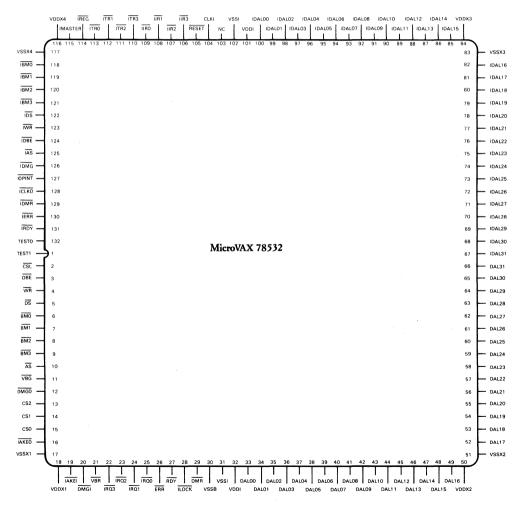

*MicroVAX 78532 Direct Memory Access Controller*—The 78532 DMA is a high-performance dualported four channel virtual memory DMA controller that enables high-speed data transfers between I/O subsytems and peripheral devices and the MicroVAX 78032 CPU bus. It contains dual ports and four channels that are independently programmable. The 132-pin device is fabricated in CMOS.

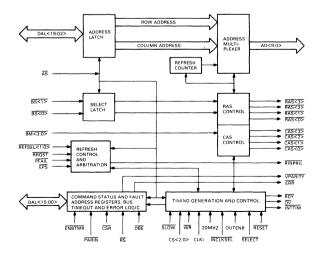

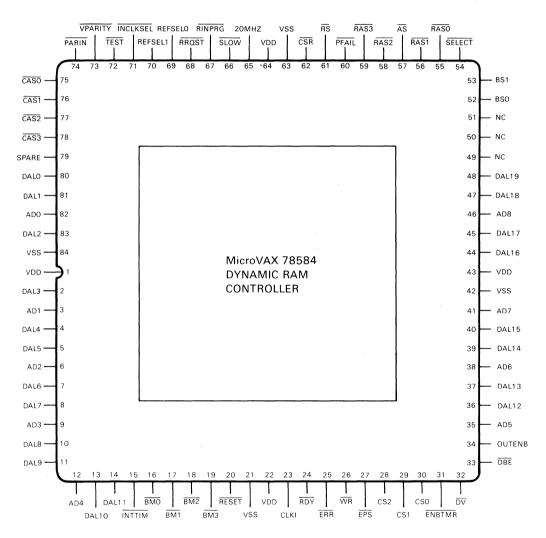

*MicroVAX 78584 Dynamic RAM Controller*—The MicroVAX DYRC provides an interface between the MicroVAX CPU and up to 4 Mbytes of dynamic random access memory (DRAM). The 78584 DYRC operates at two speeds to support 256K by 1-bit DRAMs that operate at different speeds. It is contained in an 84-pin package and is fabricated in CMOS.

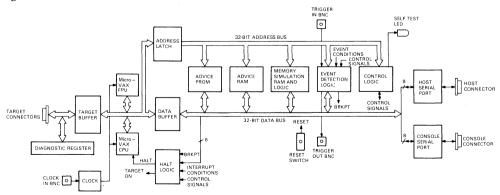

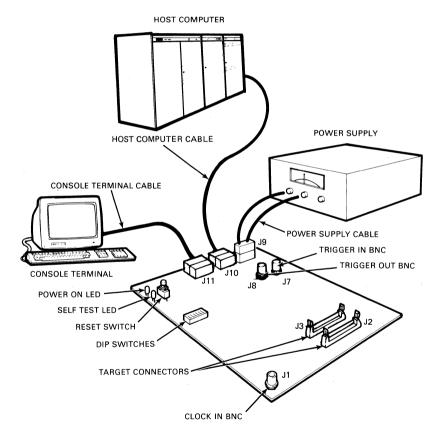

Advanced Development VAX Incircuit Emulator—The ADVICE is contained on a single module and provides a full-speed incircuit emulator of the MicroVAX 78032 CPU and MicroVAX 78132 FPU. It is used for the development of hardware and software products using the MicroVAX CPU and FPU.

#### V-11 32-bit VAX Processor

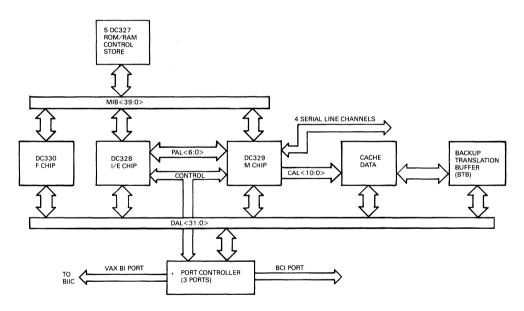

The V-11 processor chip set consists of four custom VLSI chips that were developed for use with the Scorpio CPU module which is a single module VAX system.

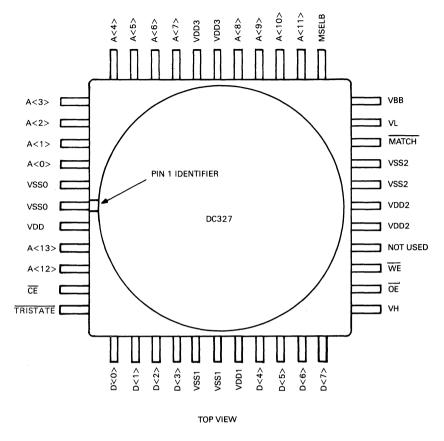

*DC327 ROM/RAM Logic*—The ROM/RAM chip is a 44-pin CERQUAD device that provides the microcode control store function for the V-11 processor.

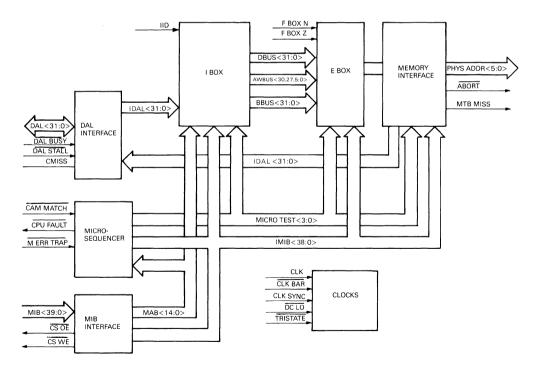

*DC328 Instruction/Execution Logic*—The I/E chip is a 132-pin PGA device that functions as the main data path and contains the microsequencer, minitranslation buffer, and instruction buffer.

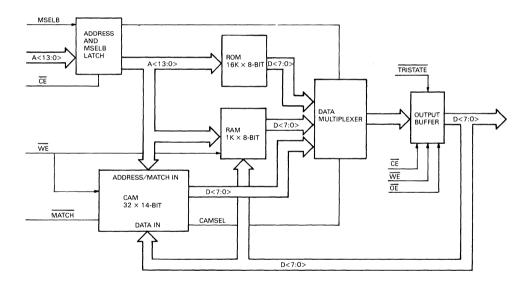

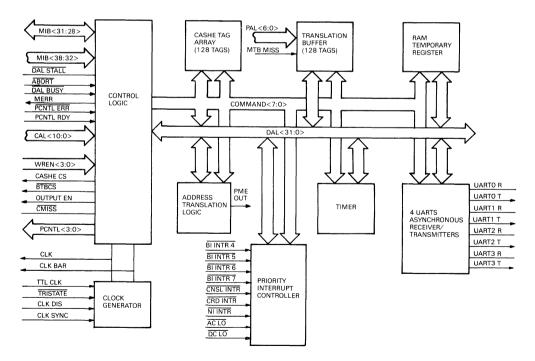

*DC329 Memory Management Logic*—The M chip is a 132-pin PGA device that provides most of the memory management logic and includes a tag store for cache memory, four UARTS, and a 512-entry backup translation buffer.

*DC330 Floating-point Accelerator Logic*—The F chip is a 132-pin PGA device used to decrease the execution time of F, D, and G floating-point instructions and some integer multiply and divide instructions.

#### PDP-11 16-bit Processors

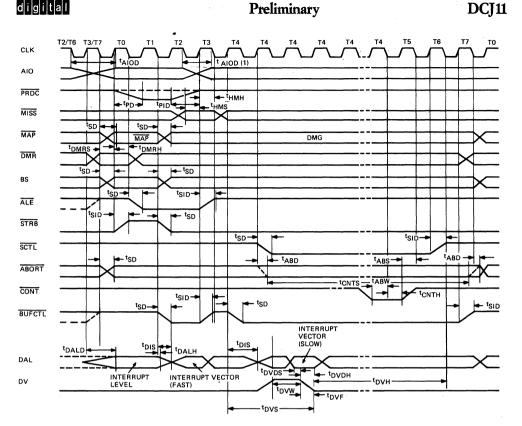

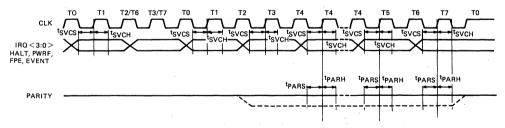

*DCJ11 Microprocessor*—The DCJ11 microprocessor is a 60-pin CMOS DIP device that implements the full PDP-11 instruction set and has a performance comparable to the PDP-11/44 miniprocessor.

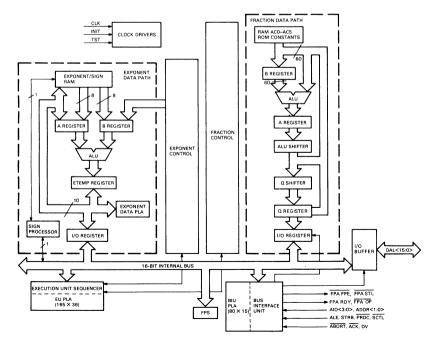

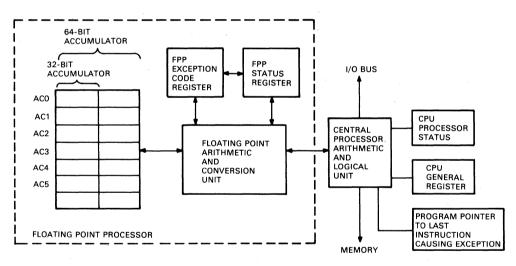

*FPJ11 Floating-point Accelerator*—The FPJ11 FPA is a 40-pin DIP that implements in hardware all the floating-point instructions of the DCJ11 thereby significantly improving the performance of floating-point instructions.

DCT11 Microprocessor—The DCT11 microprocessor is a 40-pin DIP device that contains the essential elements of the PDP-11 architecture.

#### Features

| <ul> <li>High performance</li> <li>32-bit internal and external data path</li> <li>Pipelined architecture</li> <li>Instruction prefetch</li> </ul> | <ul> <li>Subset of the VAX instruction set</li> <li>245 instructions</li> <li>21 address modes</li> <li>9 data types</li> </ul> |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| • 4 gigabyte virtual address space                                                                                                                 | Sixteen 32-bit general purpose registers                                                                                        |  |  |  |  |

| <ul> <li>1 gigabyte physical address space</li> <li>– 512 Mbyte physical memory space</li> <li>– 512 Mbyte I/O space</li> </ul>                    | <ul> <li>22 interrupt levels</li> <li>15 software</li> <li>7 hardware</li> </ul>                                                |  |  |  |  |

| VAX memory management                                                                                                                              | Vectored software and hardware interrupts                                                                                       |  |  |  |  |

| - Full memory protection                                                                                                                           | <ul> <li>Industry compatible external interface</li> </ul>                                                                      |  |  |  |  |

| <ul> <li>Four privilege modes</li> <li>Process and system space mapped</li> </ul>                                                                  | Single 5 Vdc power supply                                                                                                       |  |  |  |  |

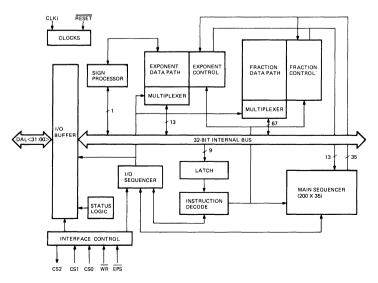

#### Description

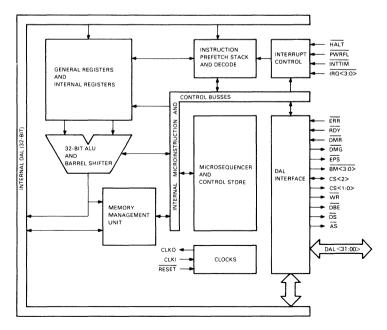

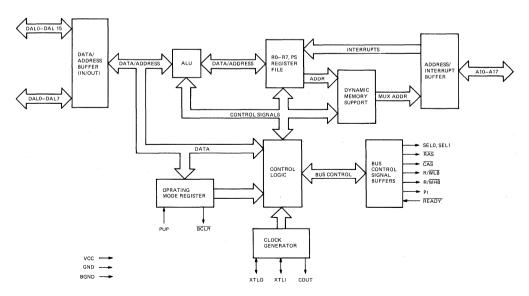

The MicroVAX 73082 is a high-performance single-chip microprocessor that provides the architecture and functions of the VAX minicomputer in a single 68-pin package. Fabricated in ZMOS (double-metal MOS), the MicroVAX 78032 implements a full 32-bit architecture that can directly access 4 Gbytes of virtual memory and 1 Gbyte of physical memory. Figure 1 is a block diagram of the MicroVAX 78032 microprocessor.

Figure 1 • MicroVAX 78032 Microprocessor Block Diagram

#### Preliminary

The MicroVAX 78032 uses a single 5 Vdc power supply, requires no special support logic, and is easily interfaced with industry standard peripheral chips. It is ideal for use as a single-board computer, personal computer and workstation, and as a low-end system.

#### · Pin and Signal Descriptions

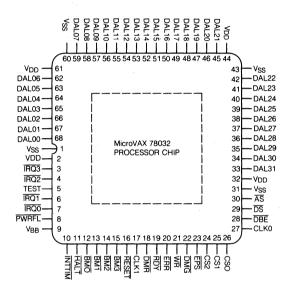

This section provides a brief description of the input and output signals and power and ground connections of the MicroVAX 78032 68-pin package. The pin assignments are identified in Figure 2 and the signals are summarized in Table 1.

Figure 2 • MicroVAX 78032 Pin Assignments

| Table 1 • MicroVAX 78032 Pin and Signal Summary |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Signal                                          | Input/Output*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Definition/Function                                                                                                                                                                                                                                                   |  |  |  |  |  |

| DAL<31:00>                                      | input/output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Data/Address lines—Time multiplexed, bidirec-<br>tional data and address bus.                                                                                                                                                                                         |  |  |  |  |  |

| ĀS                                              | output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Address strobe—System address strobe.                                                                                                                                                                                                                                 |  |  |  |  |  |

| DS                                              | output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Data strobe—System data strobe.                                                                                                                                                                                                                                       |  |  |  |  |  |

| BM<3:0>                                         | input/output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Byte masks—Identifies the bytes of the DAL bus that contain valid data.                                                                                                                                                                                               |  |  |  |  |  |

| WR                                              | output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Write—Provides read/write control for the bus.                                                                                                                                                                                                                        |  |  |  |  |  |

| DBE                                             | output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Data buffer enable—Provides control of the DAL bus transceivers.                                                                                                                                                                                                      |  |  |  |  |  |