PDP-15 Systems

Volume 1

# Maintenance Manual

# PDP-15 SYSTEMS MAINTENANCE MANUAL VOLUME 1

First Edition, October 1970 2nd Printing (Rev), December 1970 3rd Printing (Rev), October 1973 4th Printing (Rev), February 1975

#### Copyright © 1970, 1973, 1975 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DEC FLIP CHIP PDP FOCAL

DIGITAL

**COMPUTER LAB**

UNIBUS

# CONTENTS

|           |                                                    | Page |

|-----------|----------------------------------------------------|------|

| CHAPTER 1 | GENERAL DESCRIPTION                                |      |

| 1.1       | Introduction                                       | 1-1  |

| 1.2       | System Description                                 | 1-1  |

| 1.3       | Central Processor                                  | 1-4  |

| 1.3.1     | KP15 Central Processor                             | 1-4  |

| 1.3.2     | Teletype Control                                   | 1-4  |

| 1.3.3     | KC15 Console                                       | 1-4  |

| 1.3.4     | KE15 Extended Arithmetic Element (optional)        | 1-4  |

| 1.3.5     | KF15 Power Fail (optional)                         | 1-7  |

| 1.4       | I/O Processor                                      | 1-7  |

| 1.4.1     | KD15 I/O Processor                                 | 1-7  |

| 1.4.2     | KW15 Real-Time Clock (optional)                    | 1-7  |

| 1.5       | Memory                                             | 1-7  |

| 1.5.1     | MM15 Memory                                        | 1-7  |

| 1.5.2     | MK15 4K Memory Expander (optional)                 | 1-7  |

| 1.5.3     | ME15 Memory                                        | 1-7  |

| 1.5.4     | MP15 Memory Parity (optional)                      | 1-8  |

| 1.6       | BA15 Peripheral Option Expander                    | 1-8  |

| 1.6.1     | PC15 High-Speed Paper-Tape Reader/Punch (optional) | 1-8  |

| 1.6.2     | LT15A Single Teletype Control (optional)           | 1-8  |

| 1.6.3     | VP15 Display Control (optional)                    | 1-8  |

| 1.7       | BB15 Internal Option Expander                      | 1-8  |

| 1.7.1     | KA15 Automatic Priority Interrupt (API – optional) | 1-9  |

| 1.7.2     | KM15 Memory Protect (optional)                     | 1-9  |

| 1.7.3     | KT15 Memory Protect and Relocate (optional)        | 1-9  |

| 1.8       | System Interconnections                            | 1-9  |

| 1.8.1     | CPU and IPU-to-Memory Bus                          | 1-9  |

| 1.8.2     | IPU-to-I/O Devices (I/O Bus)                       | 1-9  |

| 1.8.3     | Console-to-CPU (I Bus)                             | 1-10 |

| 1.8.4     | BB Option Panel to Central Processor               | 1-10 |

| 1.9       | System Specifications                              | 1-10 |

|           |                               | Page |

|-----------|-------------------------------|------|

| CHAPTER 2 | MM15 MEMORY                   |      |

| 2.1       | Introduction                  | 2-1  |

| 2.2       | Core Addressing Matrix        | 2-1  |

| 2.2.1     | Stack Dimensions              | 2-1  |

| 2.2.2     | X-Y Matrix Construction       | 2-2  |

| 2.2.3     | Inhibit/Sensing Construction  | 2-2  |

| 2.3       | Control Logic Architecture    | 2-5  |

| 2.4       | Control Logic Flow            | 2-6  |

| 2.4.1     | Read/Restore Cycle            | 2-8  |

| 2.4.2     | Clear/Write Cycle             | 2-8  |

| 2.4.3     | Read/Pause/Write Cycle        | 2-9  |

| 2.5       | Memory Port Switch            | 2-12 |

| CHAPTER 3 | CENTRAL PROCESSOR             |      |

| 3.1       | Registers                     | 3-1  |

| 3.1.1     | Accumulator (AC)              | 3-1  |

| 3.1.2     | Link (L)                      | 3-1  |

| 3.1.3     | Program Counter (PC)          | 3-1  |

| 3.1.4     | Memory Input Register (MI)    | 3-1  |

| 3.1.5     | Memory Output Register (MO)   | 3-2  |

| 3.1.6     | Operand Address Register (OA) | 3-2  |

| 3.1.7     | Instruction Register (IR)     | 3-2  |

| 3.1.8     | Index Register (XR)           | 3-2  |

| 3.1.9     | Limit Register                | 3-2  |

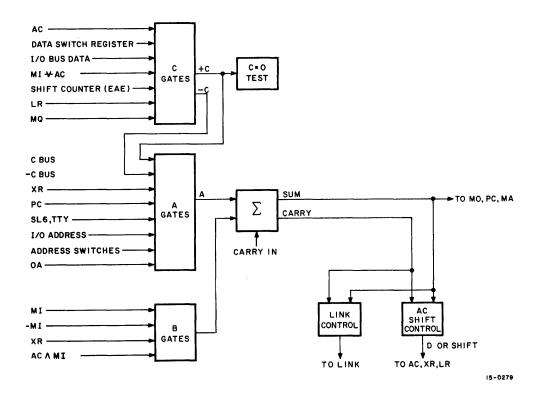

| 3.2       | Bus Structure                 | 3-2  |

| 3.2.1     | C Bus                         | 3-3  |

| 3.2.2     | A Bus                         | 3-4  |

| 3.2.3     | B Bus                         | 3-4  |

| 3.2.4     | Sum Bus                       | 3-4  |

| 3.2.5     | Shift Bus (D Bus)             | 3-5  |

| 3.3       | Data Manipulation Hardware    | 3-5  |

| 3.4       | Control State Generation      | 3-6  |

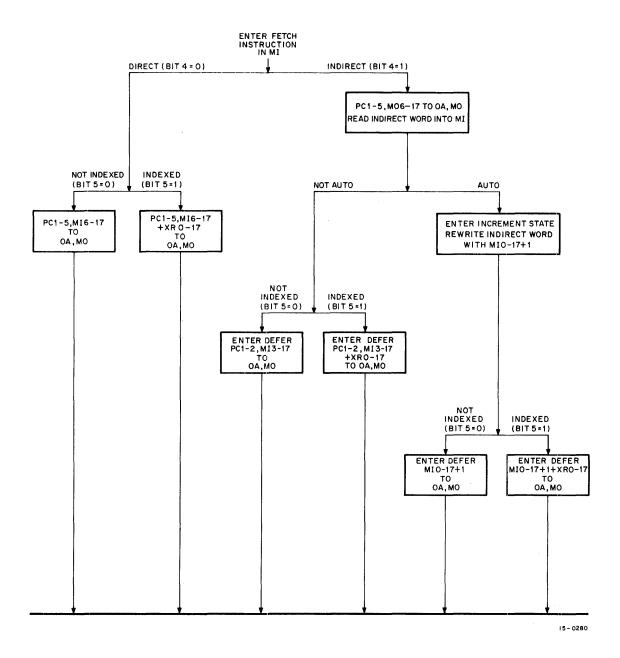

| 3.5       | Addressing                    | 3-7  |

| 3.5.1     | Page Mode                     | 3-7  |

|           |                                             | Page                  |

|-----------|---------------------------------------------|-----------------------|

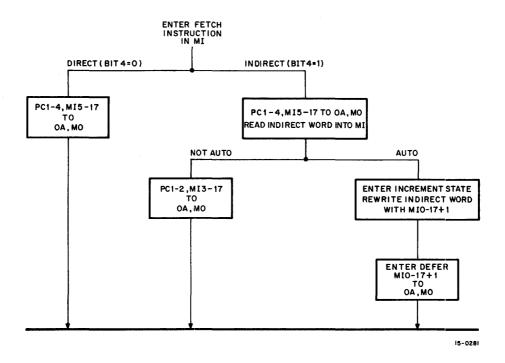

| 3.5.2     | Bank Mode                                   | 3-9                   |

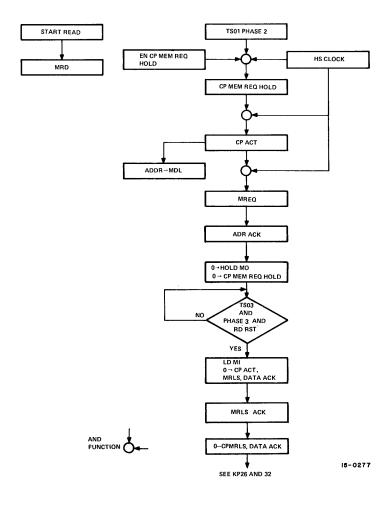

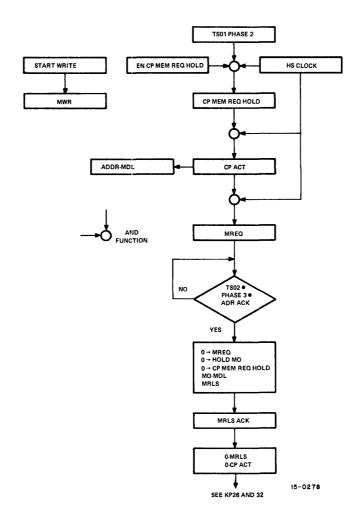

| 3.6       | Memory Read and Write                       | 3-10                  |

| 3.7       | Instruction Fetch                           | 3-10                  |

| 3.8       | Instruction Operation Details               | 3-11                  |

| 3.8.1     | Read Group (LAC, ADD, TAD, AND, XOR)        | 3-11                  |

| 3.8.2     | DAC and DZM                                 | 3-11                  |

| 3.8.3     | JMP                                         | 3-11                  |

| 3.8.4     | JMS and CAL                                 | 3-11                  |

| 3.8.5     | ISZ                                         | 3-15                  |

| 3.8.6     | SAD                                         | 3-16                  |

| 3.8.7     | XCT                                         | 3-16                  |

| 3.8.8     | OPR                                         | 3-16                  |

| 3.8.9     | LAW                                         | 3 <b>-</b> 1 <i>7</i> |

| 3.8.10    | IOT                                         | 3 <b>-1</b> 7         |

| 3.8.11    | Index Group (XG)                            | 3 <b>-1</b> 7         |

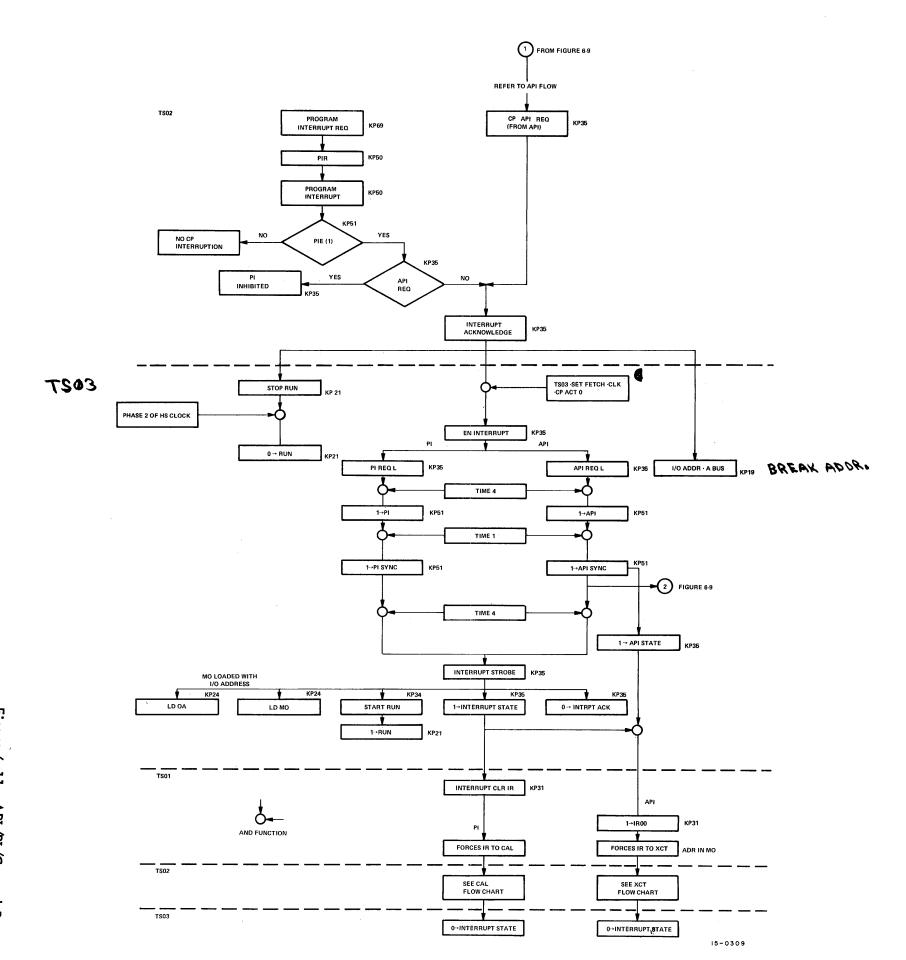

| 3.8.12    | Interrupts (API and PI)                     | 3-18                  |

| 3.9       | Defer and Auto-Increment                    | 3-18                  |

| 3.10      | Console Operation                           | 3-20                  |

| 3.10.1    | Console Cable Multiplexer                   | 3-20                  |

| 3.10.2    | Key Functions                               | 3-21                  |

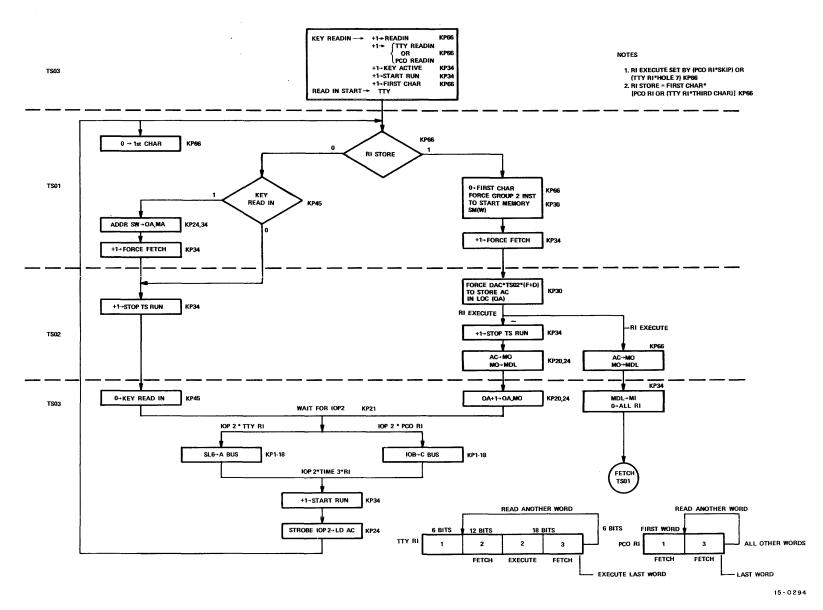

| 3.11      | Read In                                     | 3-21                  |

| CHAPTER 4 | I/O PROCESSOR                               |                       |

| 4.1       | KD15 Input/Output Processor                 | 4-1                   |

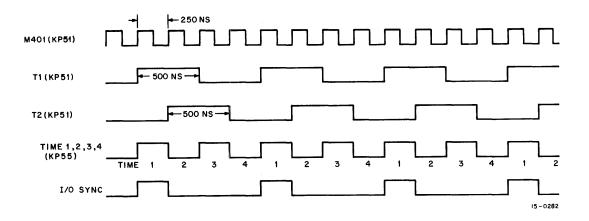

| 4.2       | Timing Generator                            | 4-3                   |

| 4.3       | Request Synchronization                     | 4-4                   |

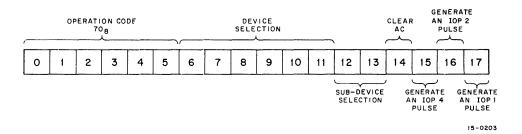

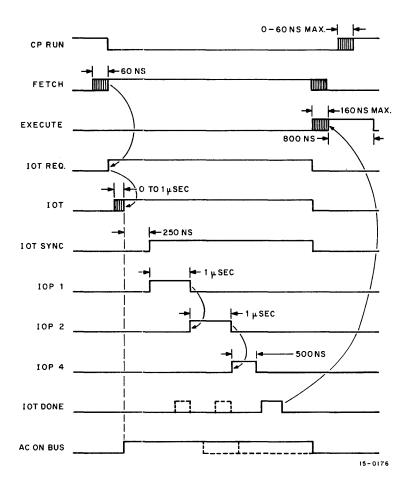

| 4.4       | IOT                                         | 4-4                   |

| 4.5       | I/O Bus                                     | 4-5                   |

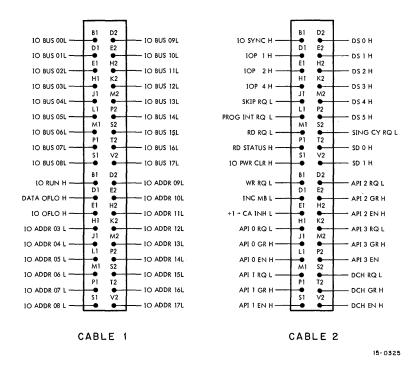

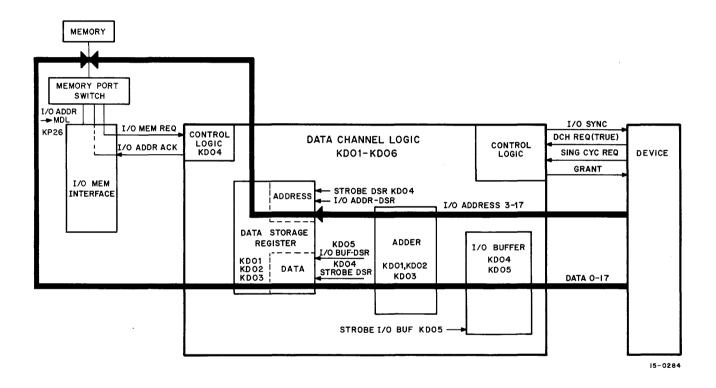

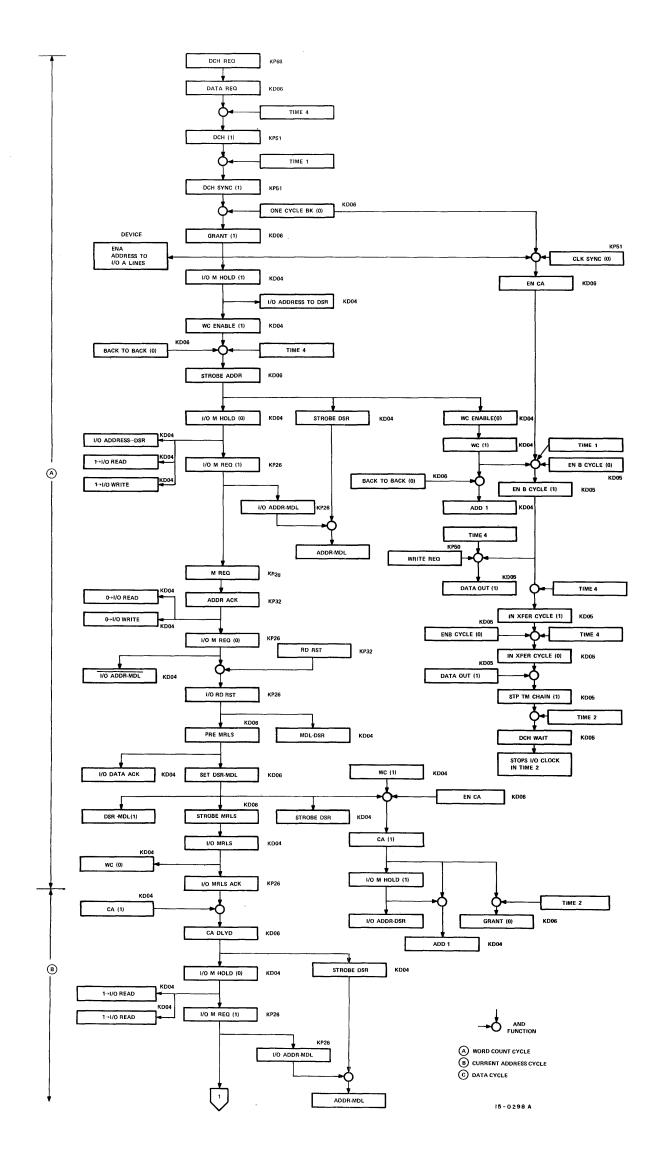

| 4.6       | Data Channel Facility (DCH)                 | 4-5                   |

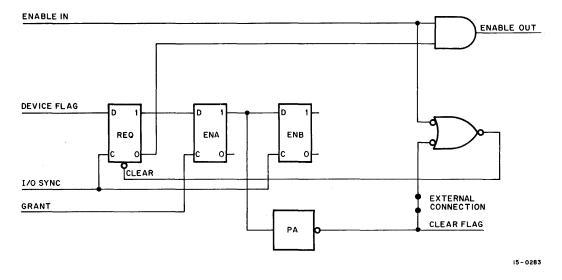

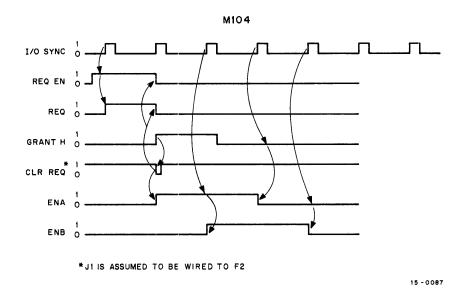

| 4.7       | I/O Bus Device Priority and Synchronization | 4-16                  |

| 4.8       | Single Cycle Input Transfers                | 4-18                  |

| 4.9       | Single Cycle Output Transfers               | 4-23                  |

| 4.10      | Multicycle Input Transfers                  | 4-23                  |

| 4.11      | Multicycle Output Transfers                 | 4-33                  |

|           |                                         | Page |

|-----------|-----------------------------------------|------|

| 4.12      | Add to Memory                           | 4-33 |

| 4.13      | Increment Memory                        | 4-33 |

| 4.14      | Inhibit Increment the Current Address   | 4-33 |

| 4.15      | Data Channel Latency                    | 4-41 |

| 4.16      | Program Interrupt                       | 4-41 |

| CHAPTER 5 | POWER DISTRIBUTION                      |      |

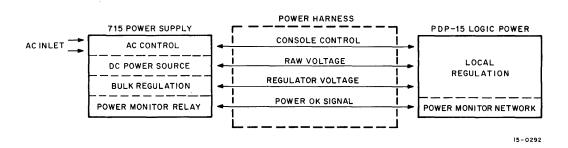

| 5.1       | PDP-15 Power                            | 5-1  |

| 5.1.1     | 715 Power Supply                        | 5-1  |

| 5.1.2     | AC Control                              | 5-2  |

| 5.1.3     | DC Power Source                         | 5-2  |

| 5.1.4     | Bulk Regulation                         | 5-3  |

| 5.1.5     | Power Harness                           | 54   |

| 5.1.6     | Local Regulation                        | 5-4  |

| 5.1.7     | Power Monitor Network                   | 54   |

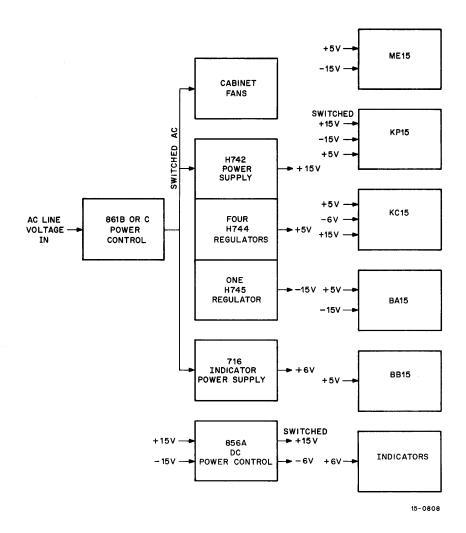

| 5.2       | PDP-15/C Power                          | 5-5  |

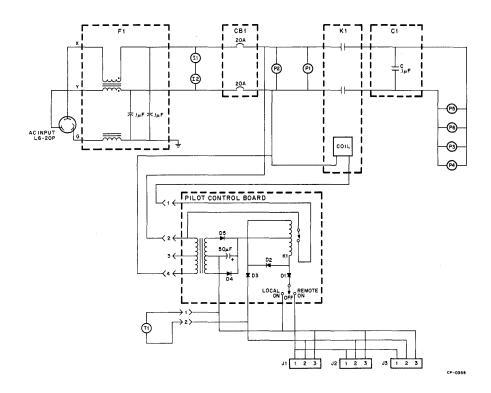

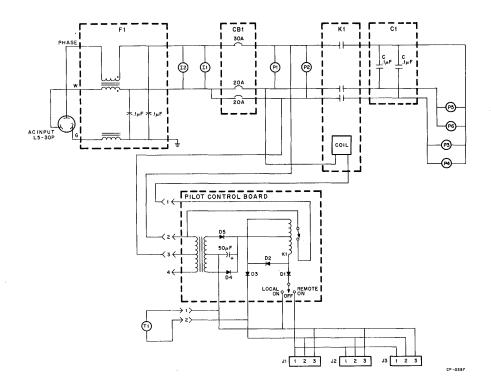

| 5.2.1     | 861 Power Controls                      | 58   |

| 5.2.2     | PDP-15/C Power Supply Adjustments       | 511  |

| CHAPTER 6 | OPTIONS                                 |      |

| 6.1       | KE15 Extended Arithmetic Element (EAE)  | 6-1  |

| 6.1.1     | General Operation                       | 6-1  |

| 6.1.2     | Normalize Instructions                  | 6-3  |

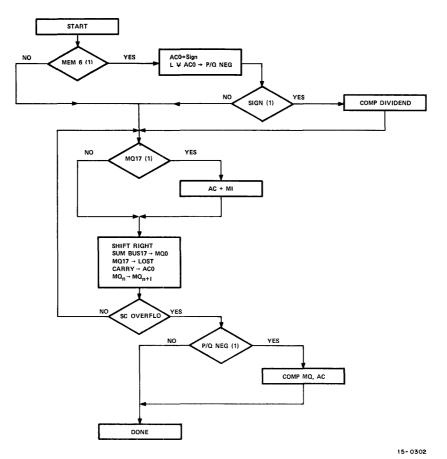

| 6.1.3     | MUL(S) Instruction                      | 66   |

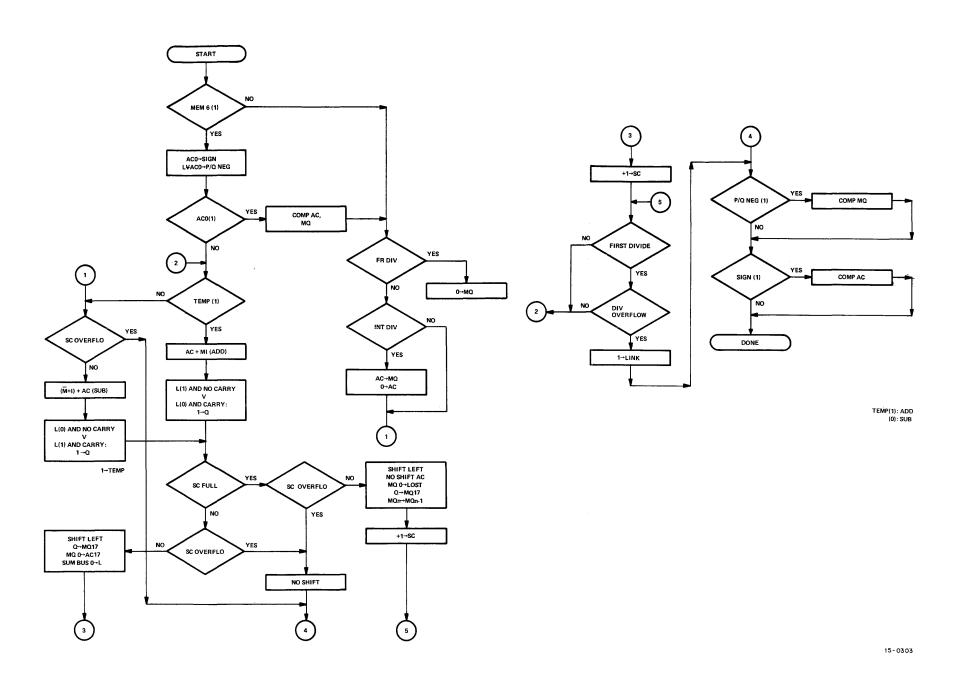

| 6.1.4     | DIV(S) Instruction                      | 6-15 |

| 6.1.5     | IDIV(S) Instruction (See Table 6-19)    | 6-20 |

| 6.1.6     | FRDIV(S) Instruction (See Table 6–20)   | 6-21 |

| 6.1.7     | Indicators                              | 622  |

| 6.1.8     | EAE Execution Times                     | 622  |

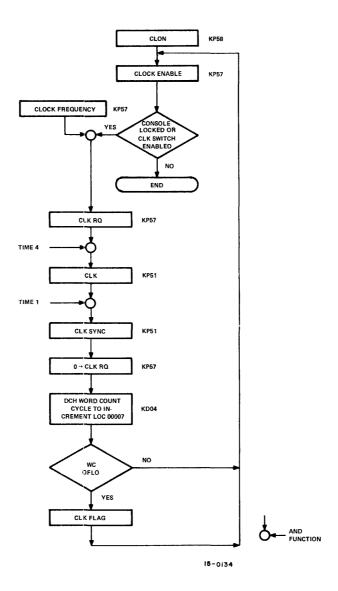

| 6.2       | KW15 Real-Time Clock                    | 6-22 |

| 6.3       | KF15 Power Fail Option                  | 6-23 |

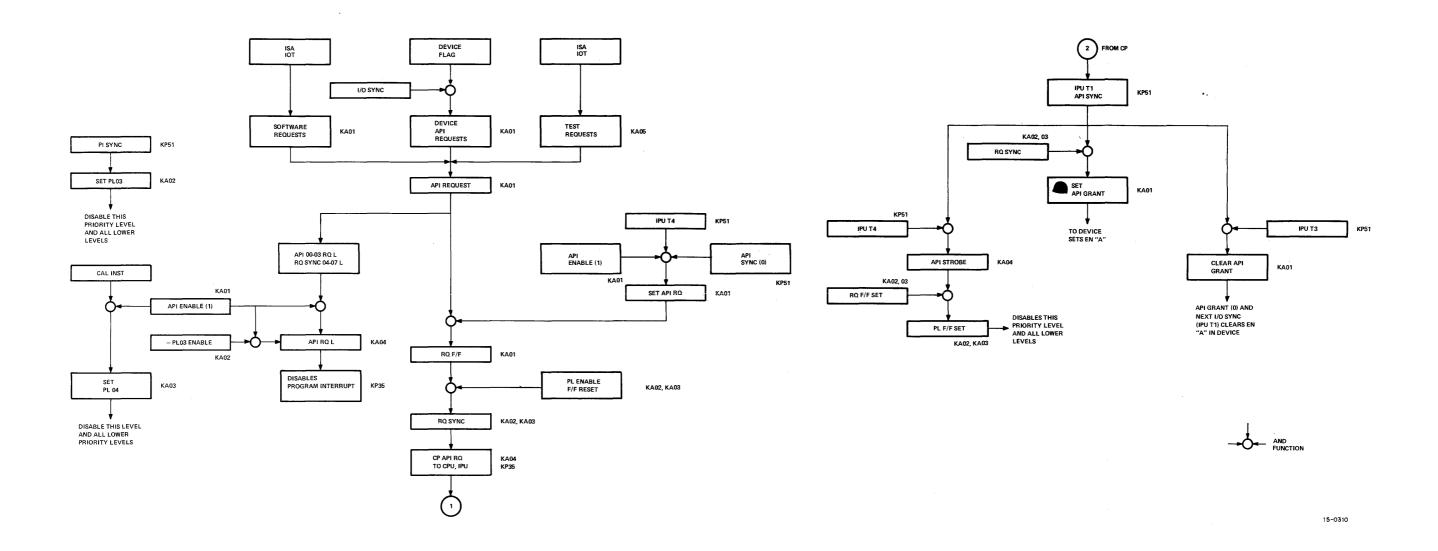

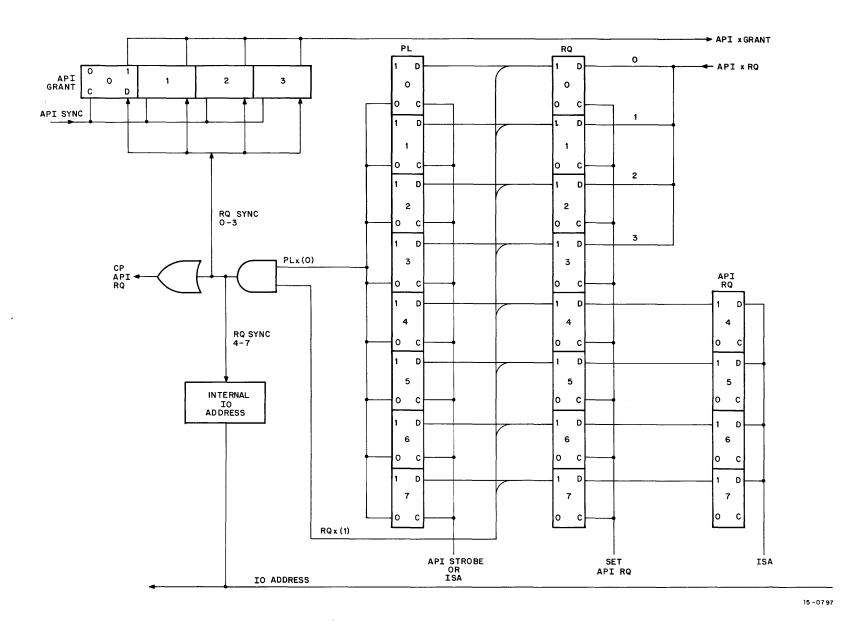

| 6.4       | KA15 Automatic Priority Interrupt (API) | 6-26 |

| 6.4.1     | General Description                     | 6-26 |

| 6.4.2     | Operational Description                 | 629  |

|           |                                           | Page        |

|-----------|-------------------------------------------|-------------|

| 6.5       | MP15 Memory Parity                        | 6-37        |

| 6.6       | KM15 Memory Protect                       | 6-38        |

| 6.7       | KT15 Memory Protect and Relocate          | 6-42        |

| 6.8       | PC15 High-Speed Paper-Tape Reader/Punch   | 6-45        |

| 6.8.1     | High-Speed Reader                         | 6-45        |

| 6.8.1.1   | Alpha Mode                                | 6-47        |

| 6.8.1.2   | Binary Mode                               | 6-48        |

| 6.8.1.3   | Read-In                                   | 6-48        |

| 6.8.2     | High-Speed Punch                          | 6-48        |

| 6.9       | LT15A Teletype Interface                  | 6-48        |

| 6.10      | VP15 Display Control                      | 6-55        |

| 6.10.1    | Display Control                           | 6-56        |

| 6.10.2    | Digital-to-Analog Converters (D/A)        | 6-56        |

| 6.10.3    | VP15A Storage Tube Display IOTs           | 6-57        |

| 6.10.3.1  | Non-Store Mode                            | 6-57        |

| 6.10.3.2  | Store Mode                                | 6-57        |

| 6.10.3.3  | Store and Non-Store Mode                  | 6-57        |

| 6.10.4    | VP15C Display and VP15B Oscilloscope IOTs | 6-57        |

| 6.10.5    | Principles of Operation                   | 6-58        |

| CHAPTER 7 | MAINTENANCE                               |             |

| 7.1       | Introduction                              | 7-1         |

| 7.2       | System Maintenance                        | 7-1         |

| 7.2.1     | Maintenance Equipment                     | <i>7</i> -1 |

| 7.2.2     | Maintenance Test Programs                 | 7-2         |

| 7.3       | Preventive Maintenance                    | 7-4         |

| 7.3.1     | Introduction                              | 7-4         |

| 7.3.2     | Scheduled Maintenance                     | <b>7–</b> 5 |

| 7.4       | Corrective Maintenance                    | 7-6         |

| 7.4.1     | Introduction                              | 7-6         |

| 7.4.2     | Preliminary Investigation                 | 7-7         |

| 7.4.3     | System Troubleshooting                    | 7-7         |

| 7.4.4     | Console Checks                            | 7-8         |

| 7.4.5     | Processor Troubleshooting                 | 7-9         |

| 7.4.6     | Logic Troubleshooting                     | 7-10        |

|            |                                                    | Page                 |

|------------|----------------------------------------------------|----------------------|

| 7.4.6.1    | Troubleshooting Intermittent System Problems       | <i>7</i> -11         |

| 7.4.7      | Module (Circuit) Troubleshooting                   | 7-12                 |

| 7.4.8      | Repairs and Replacements                           | 7-14                 |

| 7.4.9      | Validation Tests                                   | 7-14                 |

| 7.4.10     | Recording (Log Book)                               | 7 <b>-</b> 15        |

| 7.5        | Adjustment Procedure                               | 7-15                 |

| .5.1       | DC Voltage Adjustments                             | 7-15                 |

| 7.5.2      | Memory Timing Adjustments                          | 7-1 <i>7</i>         |

| 7.5.2.1    | Memory Strobe with Current Probe                   | 7-17                 |

| 7.5.2.2    | Memory Strobe with No Current Probe                | <b>7-</b> 18         |

| 7.5.3      | CP Timing Adjustment                               | <i>7</i> <b>-</b> 18 |

| 7.5.3.1    | CP Clock                                           | <i>7</i> -18         |

| 7.5.4      | I/O Timing                                         | 7-20                 |

| 7.5.4.1    | I/O Clock                                          | 7-20                 |

| 7.5.4.2    | Console Clock                                      | 7-20                 |

| 7.5.4.3    | Teletype Clock                                     | 7-22                 |

| 7.5.5      | Timing Adjustment Summary                          | 7-22                 |

|            | ILLUSTRATIONS                                      |                      |

| Figure No. | Title                                              | Page                 |

| 1-1        | PDP-15 Configuration                               | 1-1                  |

| 1-2        | PDP-15 System Block Diagram                        | 1-2                  |

| 1-3        | PDP-15/10 System Configuration Diagram             | 1-3                  |

| 1-4        | PDP-15/20 System Configuration Diagram             | 1-3                  |

| 1-5        | PDP-15/30 System Configurati on Diagram            | 1-5                  |

| 1-6        | PDP-15/40 System Configuration Diagram             | 1-5                  |

| 1-7        | PDP-15/C System Configuration Diagram              | 1-6                  |

| 2-1        | Current Path Diagram                               | 2-3                  |

| 2-2        | Sense Amplifier/Inhibit Driver, Simplified Diagram | 2-3                  |

| 2-3        | Typical Inhibit Current Waveforms                  | 2-4                  |

| 2-4        | Basic Device-Memory Control Signal Flow            | 2-7                  |

| 2-5        | Memory Cycle Detailed Flow Chart                   | 2-13                 |

| 2-6        | Central Processor Read Cycle                       | 2-15                 |

| 2-7        | Control Process or Write Cycle                     | 2-16                 |

# ILLUSTRATIONS (Cont)

| Figure No.    | No. Title                                               |               | Title P |  |

|---------------|---------------------------------------------------------|---------------|---------|--|

| 3-1           | CPU Bus Structure                                       | 3-3           |         |  |

| 3-2           | Page (PDP-15) Mode Address Formation                    | 3-8           |         |  |

| 3-3           | Bank (PDP-9) Mode Address Formation                     | 3-9           |         |  |

| 3-4           | Read-In Flow Diagram                                    | 3-22          |         |  |

| 4-1           | Basic I/O Timing                                        | 4-3           |         |  |

| 4-2           | IOT Instruction Format                                  | 4-4           |         |  |

| 4-3           | IOT Instruction Timing                                  | 4-6           |         |  |

| 4-4           | IOT Flow Diagram                                        | 4-7           |         |  |

| 4-5           | I/O Bus Cables                                          | 4-9           |         |  |

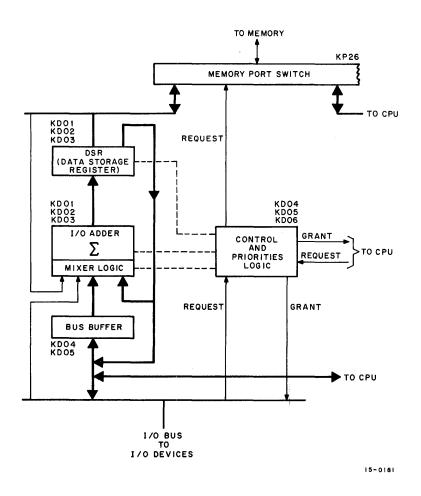

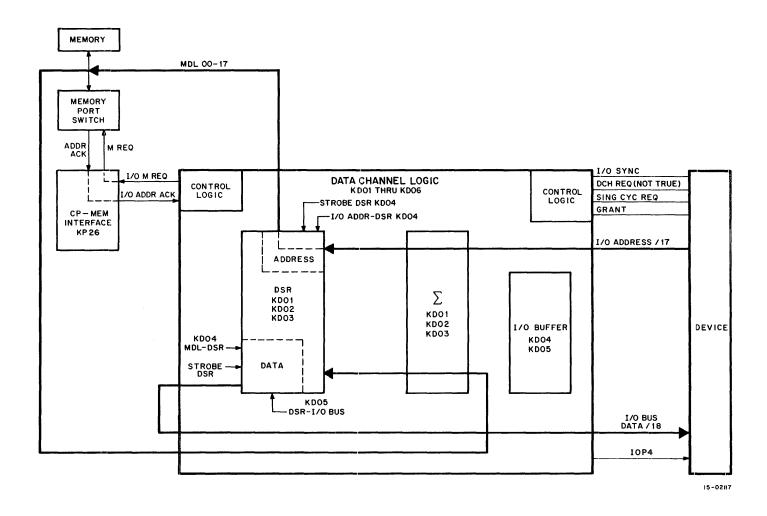

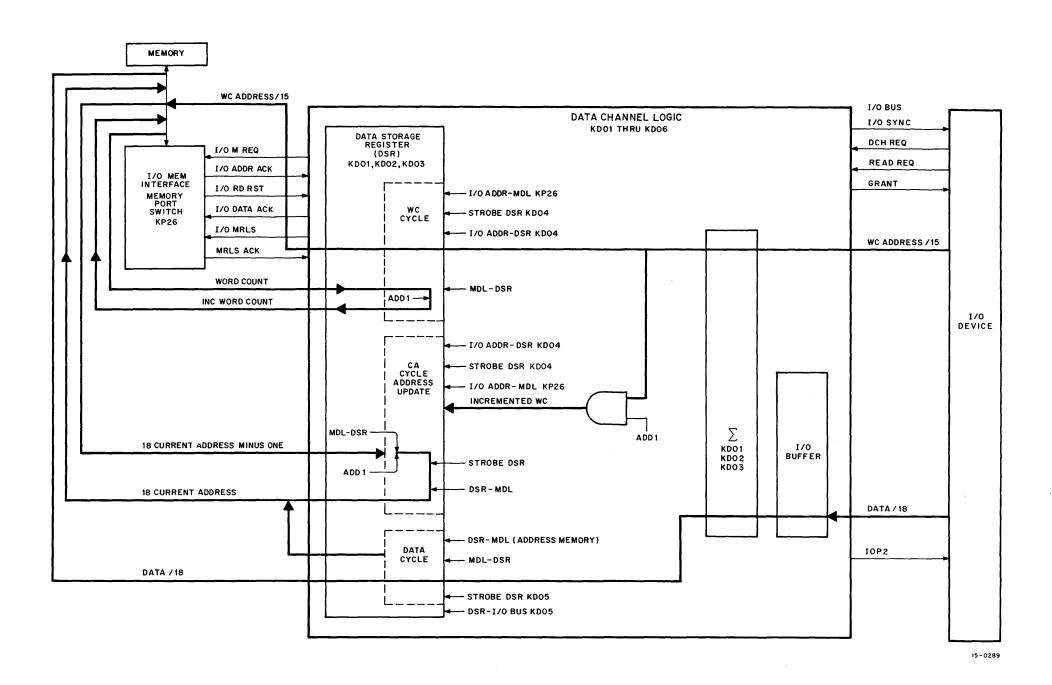

| 4-6           | Data Channel Block Diagram                              | 4 <b>-</b> 17 |         |  |

| 4-7           | Simplified M104 Module Diagram                          | 4-1 <i>7</i>  |         |  |

| 4-8           | M104 Timing Diagram                                     | 4-18          |         |  |

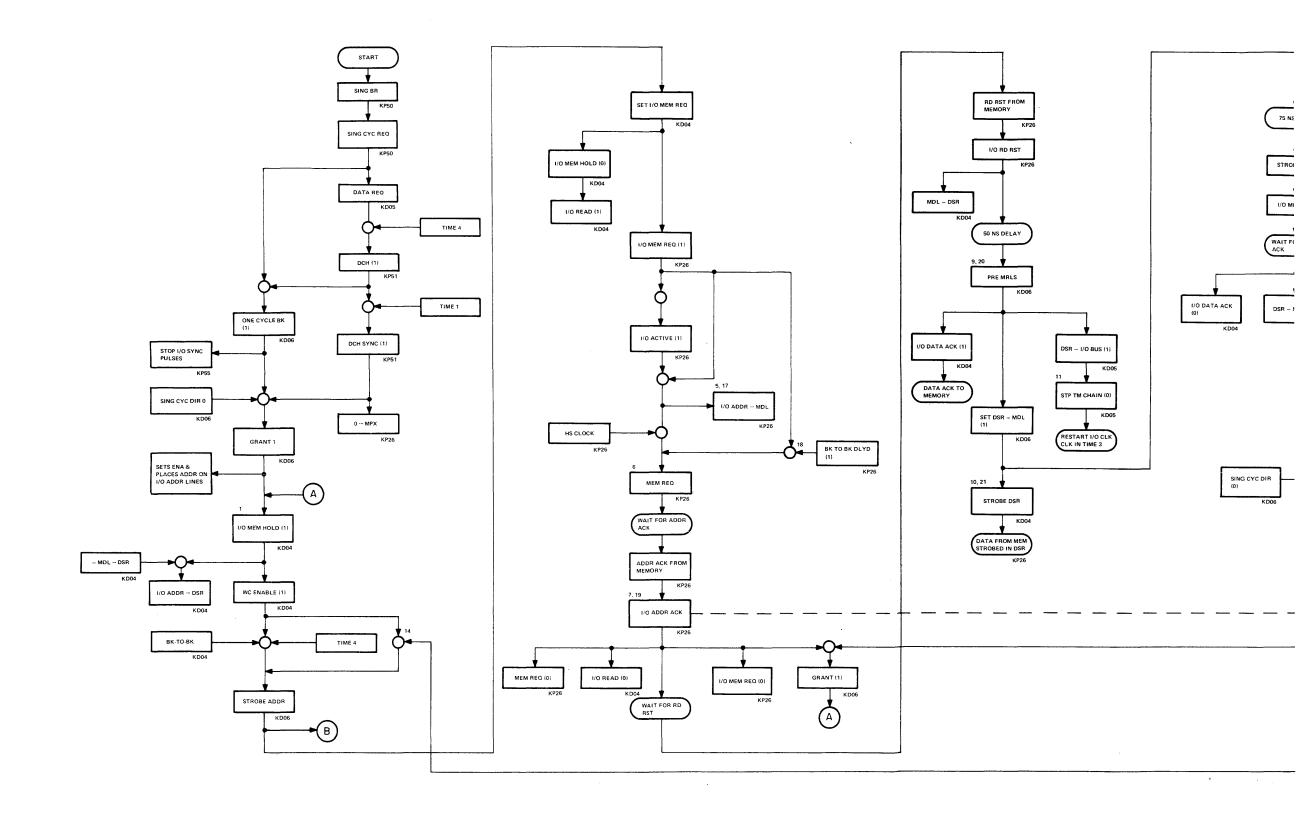

| 4-9           | Single Cycle Data In Transfer, Block Diagram            | 4-19          |         |  |

| 4-10          | Single Cycle Data In Transfer, Detailed Flow Chart      | 4-21          |         |  |

| 4-11          | Single Cycle Data Out Transfer, Block Diagram           | 4-24          |         |  |

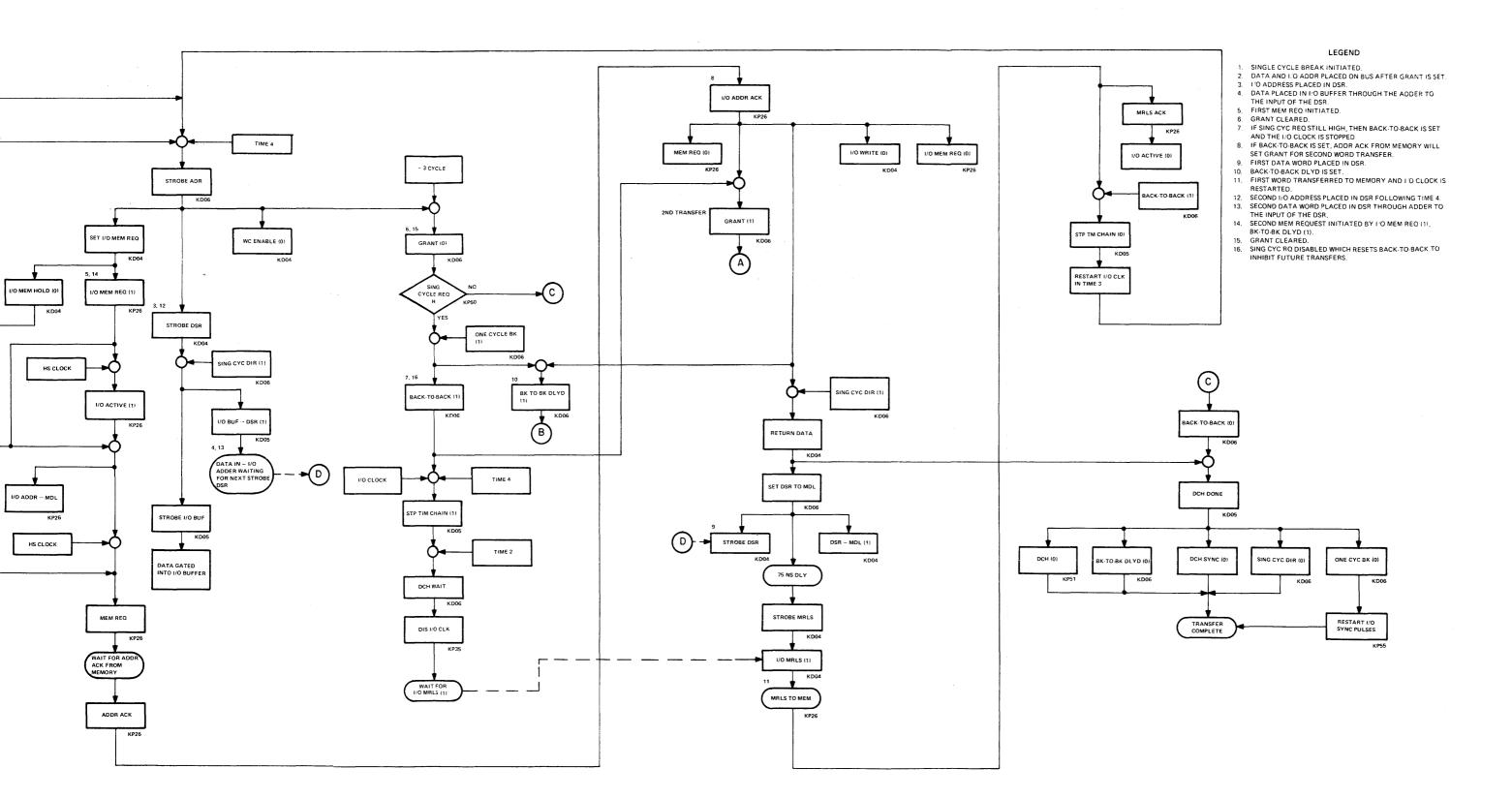

| 4-12          | Single Cycle Data Out Transfers, Detailed Flow Chart    | 4-25          |         |  |

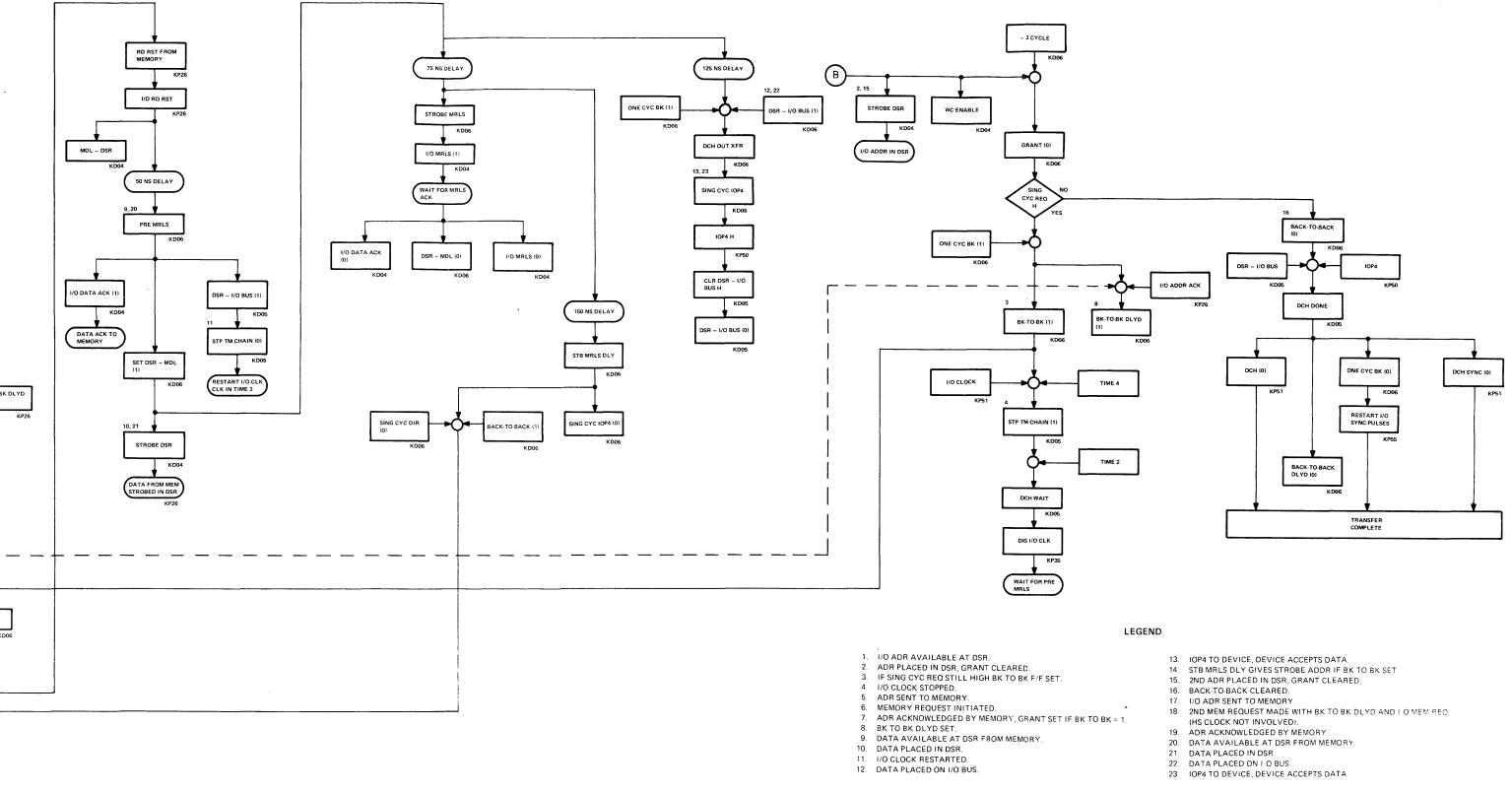

| 4-13          | Multicycle Data In Transfer Block Diagram               | 4-27          |         |  |

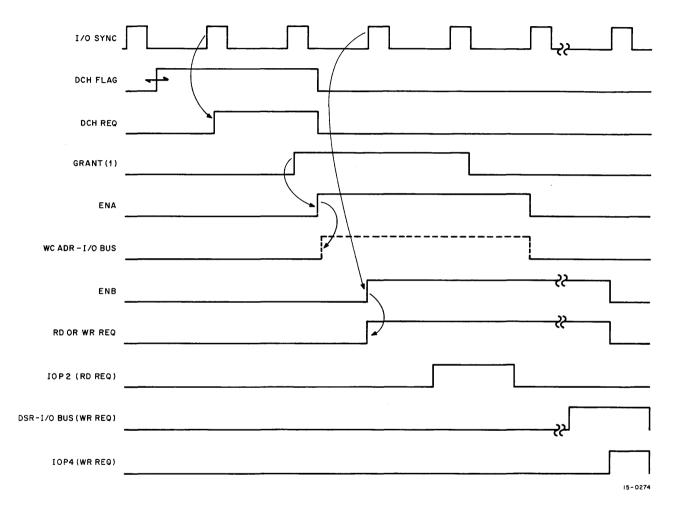

| 4-14          | Multicycle Timing Diagram                               | 4-29          |         |  |

| 4-15          | Multicycle Data In Transfer, Block Diagram              | 4-31          |         |  |

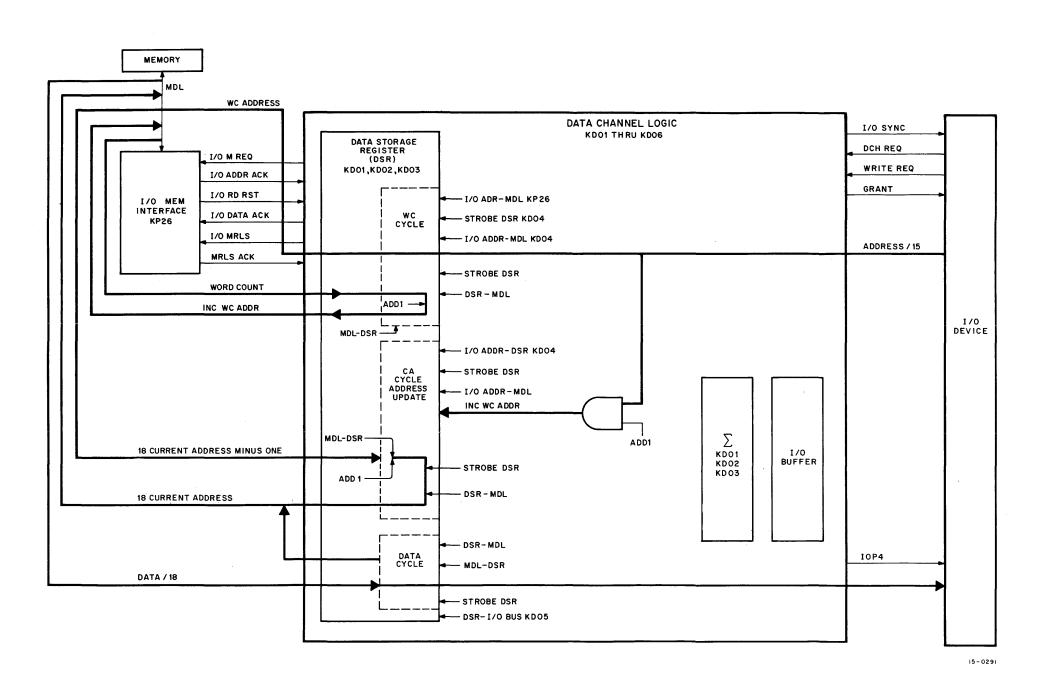

| 4-16          | Multicycle Data Out Transfers, Block Diagram            | 4-35          |         |  |

| 4 <b>-</b> 17 | Multicycle Data Out Transfer, Detailed Flow Chart,      |               |         |  |

|               | Sheet 1 of 2                                            | 4-37          |         |  |

| 5-1           | Power Distribution Block Diagram                        | 5-1           |         |  |

| 5-2           | PDP-15/C Power Distribution Block Diagram               | 5 <b>-7</b>   |         |  |

| 5-3           | 861B Power Controller Schematic                         | 5 <b>-</b> 9  |         |  |

| 5-4           | 861C Power Controller Schematic                         | 5 <b>-</b> 9  |         |  |

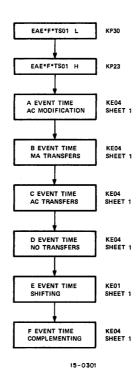

| 6-1           | EAE General Flow Diagram                                | 6-4           |         |  |

| 6-2           | EAE Multiply                                            | 6-7           |         |  |

| 6-3           | EAE Divide                                              | 6-17          |         |  |

| 6-4           | Real-Time Clock, General Flow Diagram                   | 6-24          |         |  |

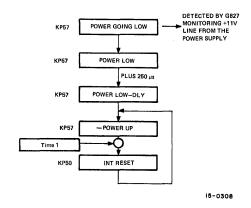

| 6-5           | Power Fail Sequence With Power Fail Option Disabled,    |               |         |  |

|               | Flow Diagram                                            | 6-25          |         |  |

| 6-6           | Power Restore Sequence With Power Fail Option Disabled, |               |         |  |

|               | Flow Diagram                                            | 6 <b>-</b> 25 |         |  |

# ILLUSTRATIONS (Cont)

| Figure No.           | Title                                                  | Page                 |

|----------------------|--------------------------------------------------------|----------------------|

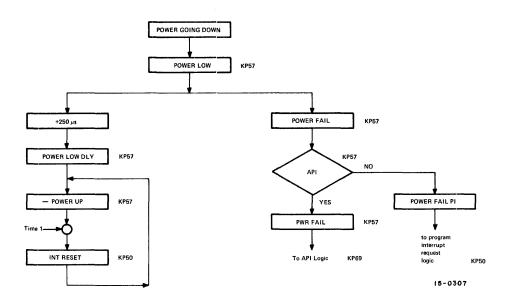

| 6-7                  | Power Fail Sequence With Power Fail Option Enabled,    |                      |

|                      | Flow Diagram                                           | 6-26                 |

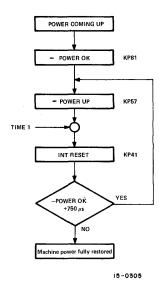

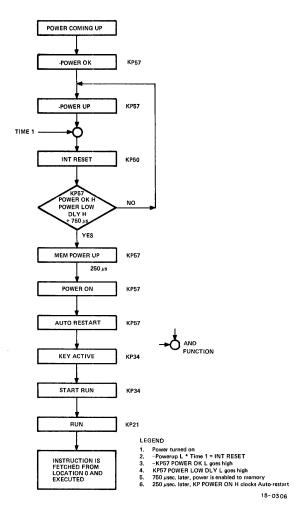

| 6-8                  | Power Restore Sequence With Power Fail Option Enabled, |                      |

|                      | Flow Diagram                                           | 6-27                 |

| 6-9                  | API Flow Diagram                                       | 6-31                 |

| 6-10                 | API Block Diagram                                      | 6-33                 |

| 6-11                 | API/PI/Central Processor Flow Diagram                  | 6-35                 |

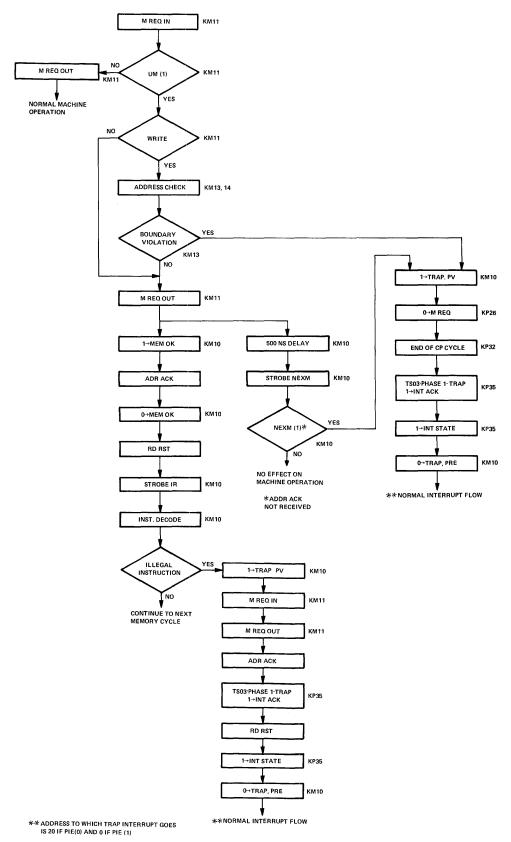

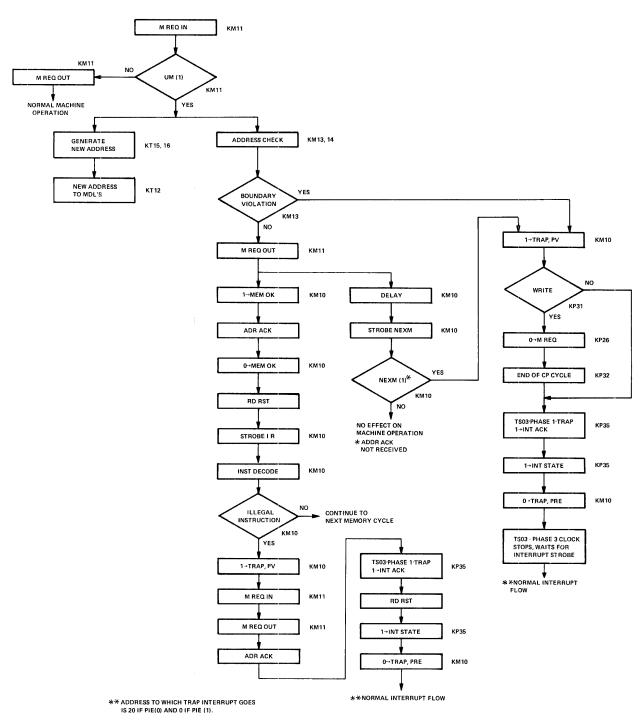

| 6-12                 | KM15 Memory Protect Flow Diagram                       | 6-41                 |

| 6-13                 | KT15 Memory Protect/Relocate Flow Diagram              | 6-44                 |

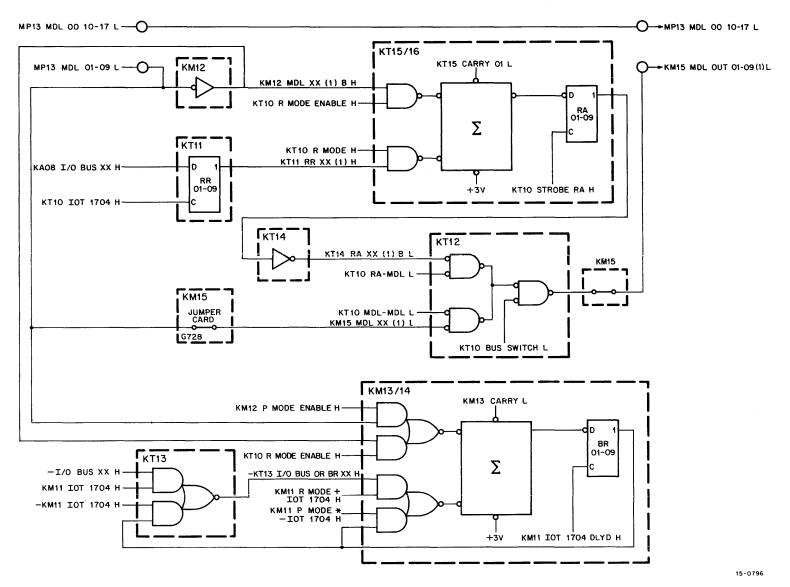

| 6-14                 | Memory Protect and Relocate Interconnection Diagram    | 6-46                 |

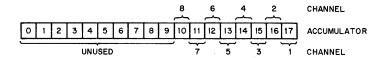

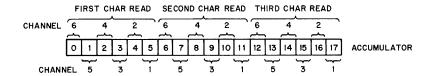

| 6-15                 | Tape Format and Accumulator Bits (Alphanumeric Mode)   | 6-47                 |

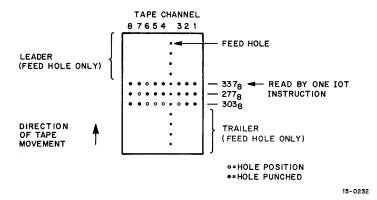

| 6-16                 | HRI Tape Format and Accumulator Bits (Binary Mode)     | 6-49                 |

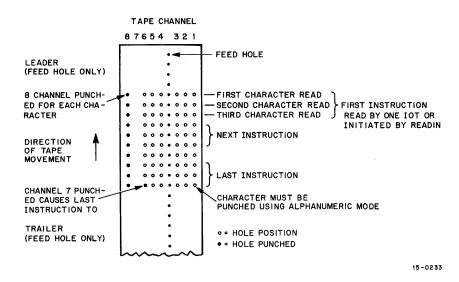

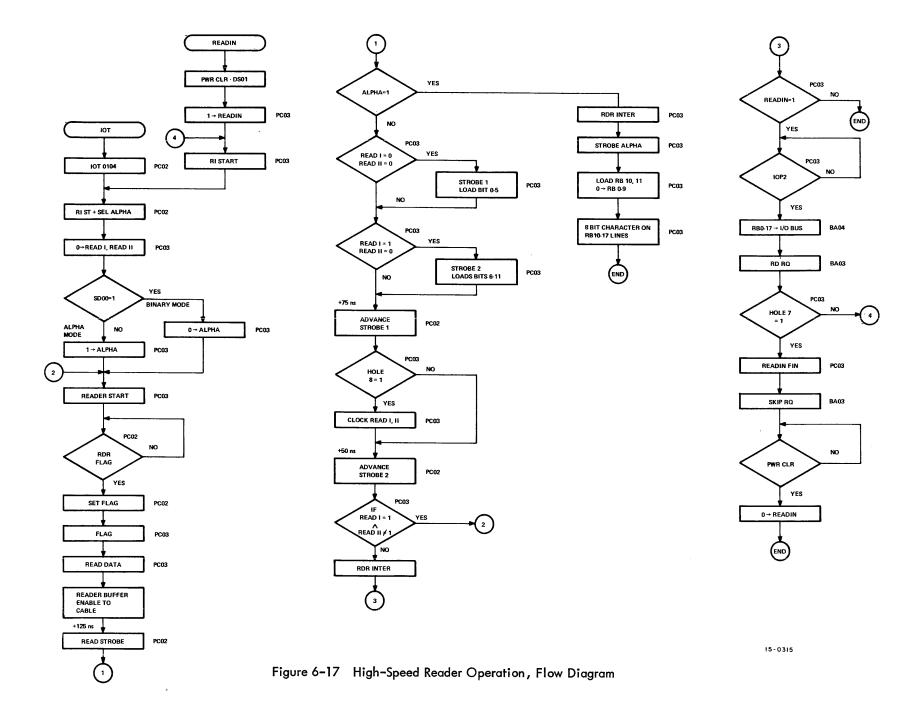

| 6-17                 | High-Speed ? ader Operation, Flow Diagram              | 6-50                 |

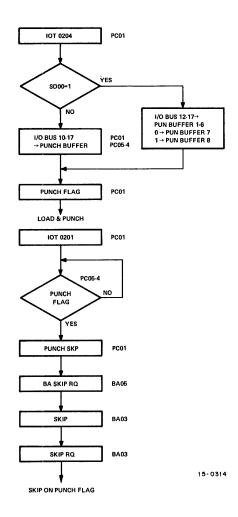

| 6-18                 | High-Speed Punch Operation, Flow Diagram               | 6-51                 |

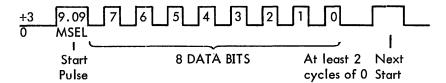

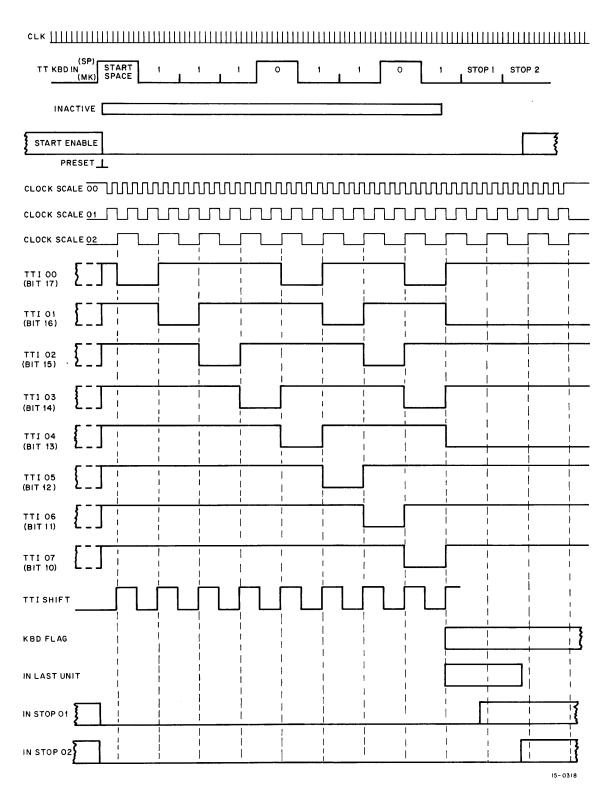

| 6-19                 | Teletype Receiver (Keyboard) Timing                    | 6-53                 |

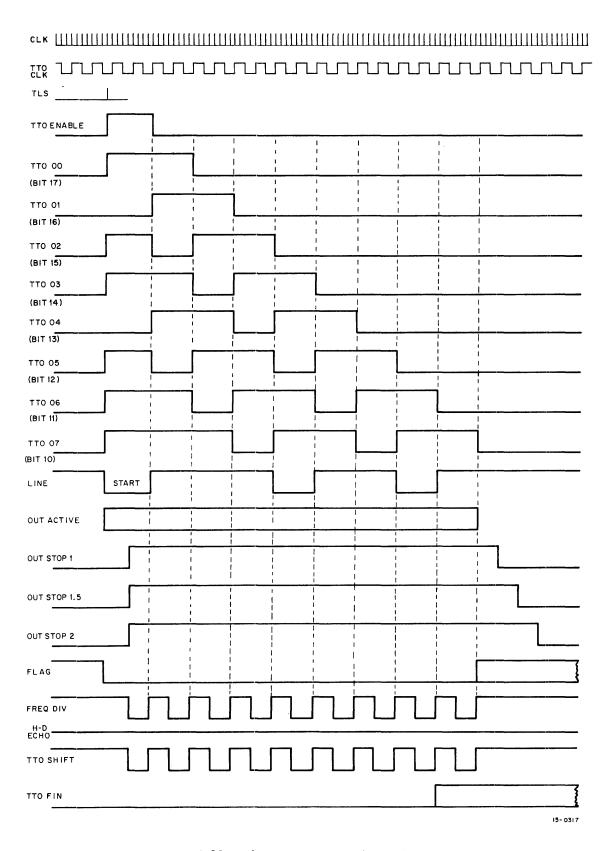

| 6-20                 | Teletype Transmitter (Printer) Timing                  | 6-54                 |

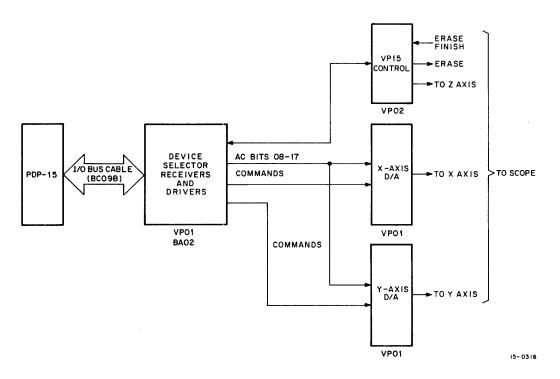

| 6-21                 | VP15 Controller, Simplified Block Diagram              | 6-58                 |

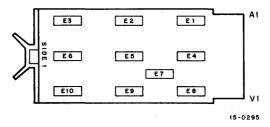

| 7-1                  | Integrated Circuit Location                            | 7-13                 |

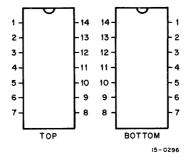

| 7-2                  | Integrated Circuit Pin Location                        | <i>7</i> -13         |

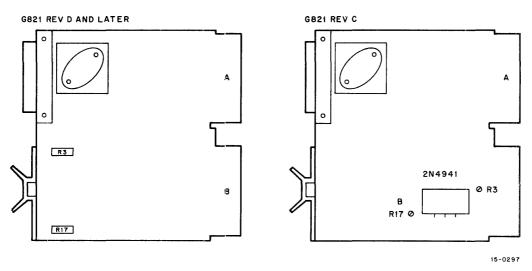

| 7-3                  | G821 Module Adjustment                                 | 7 <b>-</b> 16        |

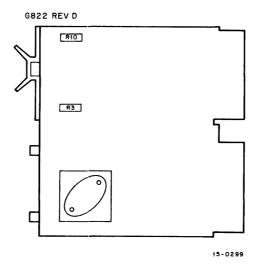

| 7-4                  | G822 Module Adjustment Locations                       | 7 <b>-</b> 16        |

| <b>7-</b> 5          | G823 Module Adjustment Locations                       | <i>7</i> –1 <i>7</i> |

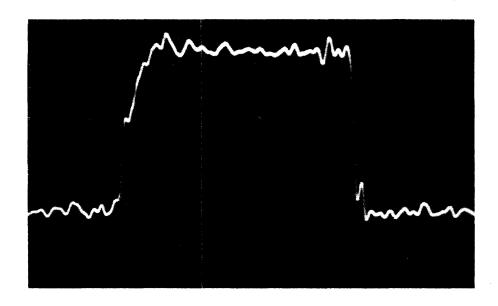

| 7-6                  | MEM Current                                            | <i>7</i> –1 <i>7</i> |

| 7-7                  | MEM Strobe Delay                                       | <i>7</i> –18         |

| 7-8                  | MEM Strobe/Sense Amp Output                            | <i>7</i> –19         |

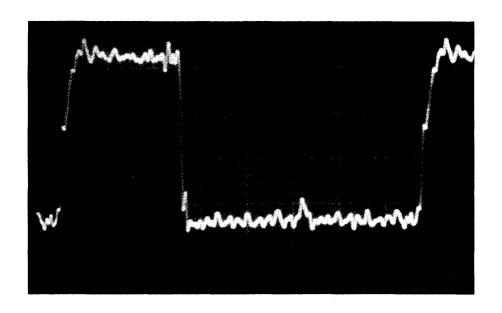

| 7-9                  | CP Clock                                               | 7 <b>-1</b> 9        |

| <i>7</i> <b>-</b> 10 | TS01 Duration                                          | 7-20                 |

| 7-11                 | Machine Cycle Time                                     | <i>7</i> -21         |

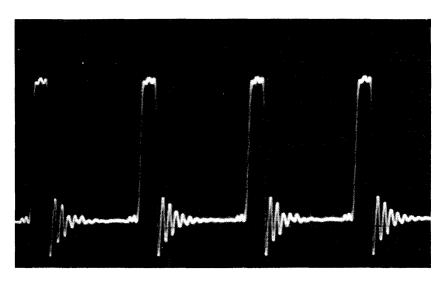

| <b>7-12</b>          | I/O Clock                                              | 7-21                 |

| <i>7</i> –13         | Console Clock                                          | 7-22                 |

| 7-14                 | Teletype Clock                                         | 7-23                 |

# TABLES

| Table No. | Title                                           | Page |

|-----------|-------------------------------------------------|------|

| 1-1       | PDP-15 Central Processor Cycle Times, Basic and |      |

|           | Expanded Configurations*                        | 1-10 |

| 2-1       | Memory Bus Signals and Data Lines               | 2-5  |

| 2-2       | Control Flops and Register Responsibilities     | 2-10 |

| 3-1       | Control States for LAC Instruction              | 3-7  |

| 3-2       | CPU/Memory Interaction                          | 3-12 |

| 3-3       | Instruction Operation                           | 3-13 |

| 3-4       | ISZ Instruction Operation                       | 3-15 |

| 3-5       | XCT Instruction Operation                       | 3-16 |

| 3-6       | Deferred Addressing Operation                   | 3-19 |

| 3-7       | Auto-Increment Operation                        | 3-20 |

| 4-1       | Summary of PDP-15 Input/Output Facilities       | 4-2  |

| 4-2       | I/O Bus Signal Functions                        | 4-10 |

| 5-1       | 715 Power Supply Distribution                   | 5-5  |

| 5-2       | PDP-15/C Power Supply Source Distribution       | 5-8  |

| 5-3       | PDP-15/C Voltage Regulator Adjustments          | 5-11 |

| 6-1       | EAE Instructions                                | 6-2  |

| 6-2       | EAE Microinstructions                           | 6-3  |

| 6-3       | EAE NOP 640000                                  | 6-9  |

| 6-4       | OSC 640001                                      | 6-9  |

| 6-5       | OMQ 640002                                      | 6-9  |

| 6-6       | CMQ 640004                                      | 6-10 |

| 6-7       | LACS 641001                                     | 6-10 |

| 6-8       | LACQ 641002                                     | 6-10 |

| 6-9       | ABS 644000                                      | 6-11 |

| 6-10      | CLQ 650000                                      | 6-11 |

| 6-11      | LMQ 652000                                      | 6-11 |

| 6-12      | GSM 664000                                      | 6-12 |

| 6-13      | LRS 6405XX and LRSS 6605XX                      | 6-12 |

| 6-14      | LLS 6406XX and LLSS 6606XX                      | 6-13 |

| 6-15      | ALS 6407XX and ALSS 6607XX                      | 6-13 |

| 6-16      | NORM 640444 and NORMS 660444                    | 6-13 |

| 6-17      | MULS 6531XX and MULS 6571XX                     | 6-14 |

| 6-18      | DIV 6403XX and DIVS 6443XX                      | 6-19 |

# TABLES (Cont)

| Table No.   | Table No. Title                           |             |

|-------------|-------------------------------------------|-------------|

| 6-19        | IDIV 6533XX and IDIVS 6573XX              | 6-21        |

| 6-20        | FRDIV 6503XX and FRDIVS 6543XX            | 6-21        |

| 6-21        | EAE Indicators                            | 6-22        |

| 6-22        | Standard API Channel/Priority Assignments | 6-28        |

| 6-23        | MP15 IOT Instructions                     | 6-38        |

| 6-24        | High-Speed Reader IOTs                    | 6-47        |

| 6-25        | High-Speed Paper Tape Punch               | 6-48        |

| 6-26        | Primary Teletype IOTs                     | 6-52        |

| 6-27        | The LT15A Instruction Set                 | 6-55        |

| 6-28        | Settling and Intensification Times        | 6-59        |

| 7-1         | Maintenance Equipment                     | 7-2         |

| 7-2         | MAINDEC Diagnostic Programs               | <b>7-</b> 3 |

| <i>7</i> –3 | PDP-15 Timing Adjustment Summary          | 7-23        |

# CHAPTER 1 GENERAL DESCRIPTION

#### 1.1 INTRODUCTION

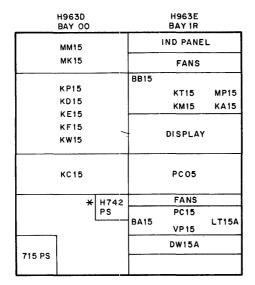

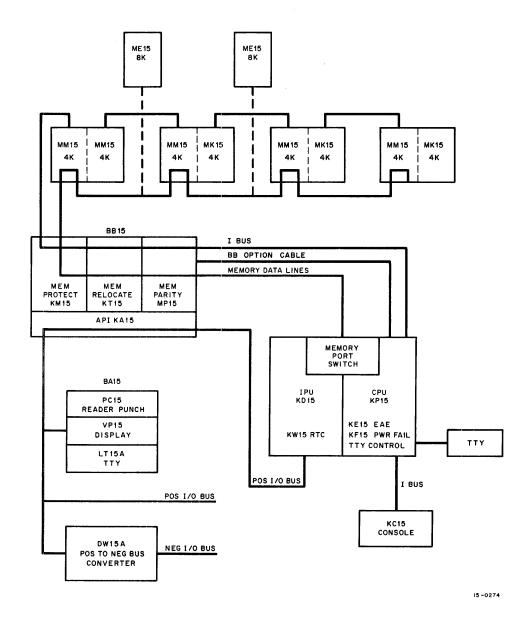

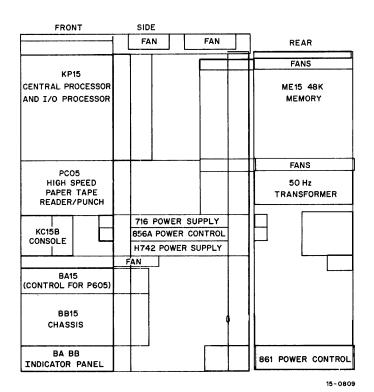

This chapter identifies and describes the modular parts of the PDP-15 system hardware, and shows how they are incorporated into the system. Figure 1-1 shows the physical location of these parts in the PDP-15 system configuration. Figure 1-2 is a block diagram of the inter-connection of the elements of the system which are covered by this manual. Other options are covered by separate manuals.

<sup>\*</sup> H742 Power Supply is employed if ME15 Memory is installed.

| KP15<br>KD15<br>KE15<br>KF15<br>KW15 |                                                      |

|--------------------------------------|------------------------------------------------------|

| KD15<br>KE15<br>KF15<br>KW15         |                                                      |

| KE15<br>KF15<br>KW15                 |                                                      |

| KF15<br>KW15                         |                                                      |

| KF15<br>KW15                         | :<br>:                                               |

|                                      |                                                      |

| PCO5                                 | · · · · · · · · · · · · · · · · · · ·                |

| PC05                                 |                                                      |

| PC05                                 |                                                      |

|                                      |                                                      |

|                                      |                                                      |

|                                      |                                                      |

| KC15                                 |                                                      |

|                                      |                                                      |

| FANS                                 |                                                      |

| PC15                                 | LT15A                                                |

|                                      |                                                      |

| BB15                                 |                                                      |

|                                      |                                                      |

| KA15                                 |                                                      |

|                                      | 544151                                               |

| ATOR                                 | PANEL                                                |

|                                      | FANS<br>PC15<br>VP15<br>BB15<br>KT15<br>KM15<br>KA15 |

PDP-15/C

15 - 0272

Figure 1-1 PDP-15 Configuration

#### 1.2 SYSTEM DESCRIPTION

The PDP-15 System consists of a KP15 Central Processor, KD15 I/O Processor, KC15 Console, ME15 and/or MM15 Memory, associated cabinets, hardware, power supplies, and any of a large number of options.

Figure 1-2 PDP-15 System Block Diagram

Hardware configurations for which special software systems have been developed are designated as follows:

- a. PDP-15/10 Compact System consists of a 4K core memory, Central Processor, I/O Processor, and ASR33 Teletype <sup>®</sup>. This is the basic PDP-15 System (see Figure 1-3).

- b. PDP-15/20 Advanced Monitor System consists of the basic PDP-15 with 8K of core memory, DECtape control and 2 DECtape transports, high-speed paper-tape reader/punch, extended arithmetic element, and KSR 35 Teletype (see Figure 1-4).

$<sup>^{\</sup>circledR}$  Teletype is a registered trademark of Teletype Corporation .

Figure 1-3 PDP-15/10 System Configuration Diagram

|          | H963D<br>(BAY 00)                                                                                | H963E<br>(BAY IR)                                | H963F<br>(BAY 2R)                 |

|----------|--------------------------------------------------------------------------------------------------|--------------------------------------------------|-----------------------------------|

|          | FAN                                                                                              | FAN                                              | FAN                               |

|          | MM15A, MK15A                                                                                     | INDICATOR                                        | INDICATOR                         |

|          | 8K MEMORY                                                                                        | ·                                                |                                   |

|          | KPI5 CENTRAL<br>PROCESSOR AND<br>I/O PROCESSOR<br>AND KE I5<br>EXTENDED<br>ARITHMETIC<br>ELEMENT | - BLANK                                          | BLANK                             |

|          | KC15<br>CONSOLE<br>TABLE                                                                         | PC15<br>HIGH SPEED<br>PAPER TAPE<br>READER/PUNCH | TU56 DUAL<br>DECTAPE<br>TRANSPORT |

| 35 KSR   | * H742                                                                                           | D                                                |                                   |

| TELETYPE | SUPP                                                                                             | LY FANS                                          | TC15                              |

|          |                                                                                                  | BA15 (CONTROL FOR<br>PC15)                       | DECTAPE<br>CONTROL                |

|          | 715<br>POWER                                                                                     | BLANK                                            |                                   |

|          | SUPPLY                                                                                           | AC UTILITY<br>OUTLETS                            | BLANK                             |

$<sup>\</sup>star$  H742 Power Supply is employed if ME15 Memory is installed.

15-0326

Figure 1-4 PDP-15/20 System Configuration Diagram

- c. PDP-15/30 Background-Foreground System consists of a PDP-15/20 with a 16K core memory, four DECtapes, a real-time clock, automatic priority interrupt, a second online Teletype and memory protect (see Figure 1-5).

- d. PDP-15/35 Disk Oriented Real-Time Executive System (RSX) consists of a PDP-15/20 with a 16K core memory, two DECtape transports, automatic priority interrupt option, real-time clock, a DECdisk file with 262K words of storage and memory protect.

- e. PDP-15/40 Disk Criented Background-Foreground System consists of a PDP-15/30 with a 24K core memory, two DECtapes, DECdisk Control, two random access DECdisk files with a capacity of 524K words of storage and memory protect (see Figure 1-6).

- f. Unichannel 15 System. Refer to Unichannel 15 System Maintenance Manual (DEC-15-HUCMA-B-D) for a complete description of the system.

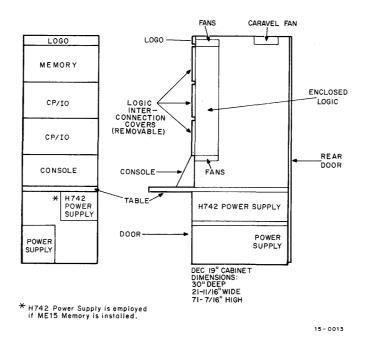

- g. PDP-15/C Compact System consists of 48K core memory, central processor, I/O processor, and high-speed paper-tape reader/punch (see Figure 1-7).

#### 1.3 CENTRAL PROCESSOR

#### 1.3.1 KP15 Central Processor

The KP15 Central Processor functions as the main component of the computer by carrying on bidirectional communication with both the memory and I/O Processor. Provided with the capability to perform all required arithmetic and logical operations, the central processor controls and executes stored programs. It accomplishes this with an extensive complement of registers, control lines, and logic.

#### 1.3.2 Teletype Control

This provides the control for the console Teletype which may be an ASR or KSR Type 33 or 35 Teletype. Logic is provided for the hardware readin of tapes from the Teletype reader in systems without high-speed tape facilities. Characters may be read from the keyboard in either half-duplex mode (characters echoed onto the printer) or full-duplex mode.

#### 1.3.3 KC15 Console

The KC15 Control Console provides facilities for operator initiation of programs, monitoring of central processor (CPU) and I/O Processor (IPU) registers, starting program execution and the manual examination and modification of memory contents.

### 1.3.4 KE15 Extended Arithmetic Element (optional)

The optional KE15 Extended Arithmetic Element (EAE) facilitates high-speed arithmetic operations and register manipulations. The EAE adds an 18-bit multiplier quotient register (MQ) to the system as well as a 6-bit step counter register (SC). Worst case multiplication time is  $7.4 \, \mu s$ ; division time is  $7.65 \, \mu s$ .

|          | H963D<br>(BAY 00)                                                                                                                            |               | H963E<br>(BAY IR)                                                        | H963F<br>(BAY 2R)                 |                    |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------------------------------------------------------------------|-----------------------------------|--------------------|

|          | FAN                                                                                                                                          |               | FAN                                                                      | FAN                               |                    |

|          | MMIS A , MKIS A 8K MEMORY (See Note 1)  KPIS CENTRAL PROCESSOR AND 1/O PROCESSOR, KE IS EXTENDED ARITHMETIC ELEMENT, AND KUSTERAL TIME CLOCK |               | INDICATOR                                                                | INDICATOR                         |                    |

|          |                                                                                                                                              |               | FANS                                                                     |                                   |                    |

|          |                                                                                                                                              |               | KAIS AUTOMATIC<br>PRIORITY INTERRUPT<br>AND<br>KMIS MEMORY<br>PROTECTION | BLANK                             |                    |

|          |                                                                                                                                              |               | BLANK                                                                    | TU56 DUAL<br>DECTAPE<br>TRANSPORT |                    |

|          | KC15<br>CONSOLE<br>TABLE                                                                                                                     |               | PCI5<br>HIGH SPEED<br>PAPER TAPE<br>READER / PUNCH                       | TU56 DUAL<br>DECTAPE<br>TRANSPORT |                    |

| 35 KSR   | PC                                                                                                                                           | H742<br>POWER | BLANK                                                                    | TCI5                              | 33 KSR<br>TELETYPE |

| TELETYPE |                                                                                                                                              | SUPPLY        | FANS                                                                     |                                   |                    |

|          |                                                                                                                                              |               | BAI5 (CONTROL FOR<br>LT I5A AND PCI5)                                    | DECTAPE<br>CONTROL                |                    |

|          | 715<br>POWER                                                                                                                                 |               | BLANK                                                                    |                                   | •                  |

|          | SUPPLY                                                                                                                                       |               | AC UTILITY<br>OUTLETS                                                    | BLANK                             |                    |

15-0327

Figure 1-5 PDP-15/30 System Configuration Diagram

|          | H963B<br>(BAY 2L)                                | H963D<br>(BAY 00)                                 | H963E<br>(BAY IR)                                  | H963F<br>(BAY 2R)                 |          |

|----------|--------------------------------------------------|---------------------------------------------------|----------------------------------------------------|-----------------------------------|----------|

|          | FAN                                              | FAN                                               | FAN                                                | FAN                               |          |

|          | INDICATOR                                        | MM15A, MK15A                                      | INDICATOR                                          | INDICATOR                         |          |

|          | RF15                                             | 8K MEMORY<br>(See Note 1)                         | FANS                                               |                                   |          |

|          | DECDISK                                          | KP15 CENTRAL                                      | KA15 AUTOMATIC<br>PRIORITY INTERRUPT               | BLANK                             |          |

|          | RS09                                             | PROCESSOR AND<br>I/O PROCESSOR,<br>KE 15 EXTENDED | AND<br>KM15 MEMORY<br>PROTECTION                   |                                   |          |

|          | DĒCDISK                                          | ARITHMETIC<br>ELEMENT AND<br>KW15 REAL            | BLANK                                              | TU56 DUAL<br>DECTAPE              |          |

|          |                                                  | TIME CLOCK                                        | BEANN                                              | TRANSPORT                         |          |

|          | RSO9<br>DECDISK                                  | KC15<br>CONSOLE                                   | PC15<br>HIGH SPEED<br>PAPER TAPE<br>READER / PUNCH | TU56 DUAL<br>DECTAPE<br>TRANSPORT |          |

| 35 KSR   |                                                  | TABLE                                             | BLANK                                              |                                   | 33 KSR   |

| TELETYPE | İ                                                |                                                   | FANS                                               | TCI5                              | TELETYPE |

|          | AIR DISTRIBUTION<br>SYSTEM AND POWER<br>SUPPLIES |                                                   | BA15 (CONTROL FOR<br>LT15A AND PC15)               | DECTAPE<br>CONTROL                |          |

|          |                                                  | 715<br>POWER                                      | DWI5A I/O BUS<br>CONVERTER                         |                                   |          |

|          |                                                  |                                                   | AC UTILITY<br>OUTLETS                              | BLANK                             |          |

15-0328

Figure 1-6 PDP-15/40 System Configuration Diagram

NOTES

1. An identical BK memory is mounted on the rear door of cabinet H963D.

There is space on this door for mounting two more BK modules.

imes H742 Power Supply is employed when ME15 Memory is installed.

<sup>1.</sup> Two more 8K memory modules are mounted on the rear door of cabinet H963D. There is space on this door for mounting one more 8K module.

<sup>2. 96</sup>K of ME15 Memory may be installed in rear door.

Figure 1-7 PDP-15/C System Configuration Diagram

#### 1.3.5 KF15 Power Fail (optional)

The KF15 Power Fail option offers maximum protection to programs during power failure and recovery of power after failure. It enables the PDP-15 system to store active registers in memory before power diminishes to a point beyond which data will be lost. It also enables the PDP-15, upon the restoration of power, to restore these registers and continue with the program that was previously in progress.

#### 1.4 I/O PROCESSOR

#### 1.4.1 KD15 I/O Processor

The KD15 Processor (IPU) is an autonomous subsystem of PDP-15 which supervises and synchronizes all IOT and Data Channel (DCH) transfers between the devices and the PDP-15 central processor and memory. The I/O Processor contains the arithmetic and control logic hardware to supervise all I/O device activity. The IPU is, however, a passive system in that it responds to requests for activity from devices or the CPU rather than initiating activity.

#### 1.4.2 KW15 Real-Time Clock (optional)

The KW15 Real-Time Clock option gives the user a time reference capability. The real-time clock produces clock pulses at a rate of 1 every 16.7 ms for 60 Hz systems; these systems increment a core location which can be preset and monitored under program control.

#### 1.5 MEMORY

#### 1.5.1 MM15 Memory

The MM15 Memory is the primary storage area for the computer instructions and data. Memory is organized into pages which are paired into memory banks. Each MM15 has 4K 18-bit binary words of high-speed random access magnetic core storage. Each bank is a unit of 8K words. The Central Processor and I/O Processor have provisions to address up to 128K words of core memory with the aid of a MX15 Memory Multiplexer. Any word in memory may be addressed by either the Central Processor or the I/O Processor.

#### 1.5.2 MK15 4K Memory Expander (optional)

This option expands the MM15 memory control from 4K to 8K 18-bit words. It consists of the core memory stack and the necessary read/write circuits and must be used with an MM15.

#### 1.5.3 ME15 Memory

The ME15 Core Memory provides the PDP-15 with up to 96K 18-bit words on the rear door. The ME15 is mounted on the rear door of the CPU cabinet and may be added to PDP-15 installations equipped with MM15 Memory. The MX15 Memory Multiplexer is not required. For additional information regarding the ME15, refer to the ME15 Core Memory Maintenance Manual, DEC-15-HMEMA-A-D.

#### 1.5.4 MP15 Memory Parity (optional)

The MP15 Memory Parity option enables the PDP-15 to continuously check information being read from core memory and determine whether information has been erroneously picked up or dropped. It does this by monitoring all information as it is being sent to the memory for storage, and writing a parity bit. When this word is read from memory, the word and the bit are checked to determine whether any information has been changed, and a parity error flag is raised if a change is detected. Memory parity is not available with the ME15 memory.

#### 1.6 BA15 PERIPHERAL OPTION EXPANDER

This option houses power and I/O bus interface logic for the PC15, LT15A, and VP15 which are described below; only one BA15 is required per system.

#### 1.6.1 PC15 High-Speed Paper-Tape Reader/Punch (optional)

This option includes a PC05 Reader/Punch and the control to interface it to the PDP-15. Characters can be read from paper tape at a maximum rate of 300 characters per second or punched at a rate of 50 characters per second. When this option is installed, the PC15, instead of the TTY, is used for hardware READIN.

#### 1.6.2 LT15A Single Teletype Control (optional)

This option provides the logic to receive and transmit information through a KSR33 or KSR35 Teletype. This provides a second Teletype capability to the PDP-15 system.

#### 1.6.3 VP15 Display Control (optional)

This option interfaces the PDP-15 to various display devices by providing the digital-to-analog converters and the control logic for the x and y positioning as well as the intensification of the VP15A Storage Tube Display, VP15B Oscilloscope Display, or VP15C X-Y Oscilloscope Display.

#### 1.7 BB15 INTERNAL OPTION EXPANDER

This expander houses the power, I/O bus interface, memory bus interface and various control signals from the processor for the operation of the KA15 Automatic Priority Interrupt, KM15 Memory Protect, KT15 Memory Protect and Relocate, and MP15 Memory Parity options. Only one BB15 is required per system.

#### 1.7.1 KA15 Automatic Priority Interrupt (API - optional)

The API option adds 8 additional levels of priority to the PDP-15. The upper 4 levels are assigned to I/O devices and are initiated by flags (interrupt requests) from these devices. The lower four levels are programming levels and are initiated by software requests. High data rate or critical devices are assigned to high priority levels and can interrupt slower device service routines. The API option holds the slower device interrupt request until it can be serviced. The cause of the interrupt is also directly identified eliminating the need for service routines and flag search routines.

#### 1.7.2 KM15 Memory Protect (optional)

The KM15 memory protect provides the PDP-15 core memory with protected memory locations that cannot be accessed by the user. It includes a boundary register and associated control logic to establish the lower limit of the user's program. It has the facility to trap IOT, HALT CAS and chained execute instructions and the addressing of a non-existent memory bank.

#### 1.7.3 KT15 Memory Protect and Relocate (optional)

The memory protect and relocate option is similar to the memory protect option. The KM15 must be used with the KT15. However, it contains a relocation register as well as a core allocation register. The relocation register provides the lower limit of the user program and relocates the user upward from the real machine location by the quantity contained in the relocation register. The core allocation register indicates the last 256 word increment available to the user. Other features of the memory protect option are also included in this option.

#### 1.8 SYSTEM INTERCONNECTIONS

#### 1.8.1 CPU and IPU-to-Memory Bus

The central processor and I/O processor each asynchronously access memory over the same memory data lines (MDL). The priority structure concerning which processor's request is sent to memory is determined by the memory port switch. The I/O processor is given first priority. The memory data lines consist of 18 bi-directional lines over which address and then data information is transmitted to and from memory. Various control signals are on this bus.

#### 1.8.2 IPU-to-I/O Devices (I/O Bus)

The I/O processor communicates with all devices over a common I/O bus which contains bidirectional data lines; address lines; enable, request, and grant lines for API and data channel; and others such as program interrupt and skip request.

#### 1.8.3 Console-to-CPU (I Bus)

The indicator bus contains bi-directional lines to transmit information to the lights on the console and switch information from the console to the central processor. Several control lines are also located on the cable. The ME15 memory does not use the IBus.

#### 1.8.4 BB Option Panel to Central Processor

Because the BB15 Option Panel contains several internal options which deal with the operation of the central processor, a special cable is required so that the option may utilize these internal central processor signals.

#### 1.9 SYSTEM SPECIFICATIONS

#### Functional Characteristics

Word Length

Cycle time Refer to Table 1-1

Core memory capacity 4096 words, expandable to 131,072 words

18 bits

in 4K increments with MM15/MK15 Memory; 8K increments with ME15 Memory.

Core memory access

Page mode

Direct 4096 words

Indirect 32,768 words

Indexed 131,072 words

Bank mode

Direct 8,192 words

Indirect 32,768 words

Computation rate 625,000 additions per second

ASR33 Teletype 10 characters per second

Program-controlled I/O capacity

Up to 256 devices including prewired CPU

and IPU IOTs

Data channel capacity

Up to 8 device controllers

#### Operating Characteristics (H963D Cabinet; CP, I/O and Memory)

PDP-15 power requirements  $115V \pm 15\%$  or  $230V \pm 15\%$ , 50 or

$60 \text{ Hz} \pm 2\%$ , single phase, 18-30A

PDP-15/C power requirements 95-130V or 190-260V, 47-63 Hz,

single phase, 12A

PDP-15 power consumption 4 KW max

PDP-15/C power consumption 1.3 KW max

Power supply outputs after local +5, -6, -24 Vdc

regulation

Logic levels 0-.4V = logic 0 2.4-5V = logic 1

Test temperature range 50°-120°F

Relative humidity 10-95%

PDP-15 heat dissipation 13,650 BTU/hr.

PDP-15/C heat dissipation 4,000 BTU/hr.

#### Dimensions

Cabinet height 71-7/16 in.

Cabinet width 21-11/16 in.

Cabinet depth 30 in.

Shelf widths 19 in.

Shelf depth 19-5/16 in.

Door clearance (rear) 18-7/32 in.

Cabinet weight (loaded) 750 lbs.

Teletype height 8-3/8 in.

Teletype width 22 in.

Teletype depth 18-1/2 in.

Teletype weight 44 lbs.

Table 1-1

PDP-15 Central Processor Cycle Times, Basic and Expanded Configurations\*

|                                                                                | Not In User Mode |         |       |         | In User Mode |         |       |         |

|--------------------------------------------------------------------------------|------------------|---------|-------|---------|--------------|---------|-------|---------|

| Configuration                                                                  | Read             |         | Write |         | Read         |         | Write |         |

|                                                                                | Max              | Typical | Max   | Typical | Max          | Typical | Max   | Typical |

| Basic                                                                          | 800              | 800     | 800   | 800     |              |         |       |         |

| KM15 Memory Protect                                                            | 830              | 800     | 830   | 800     | 830          | 800     | 975   | 920     |

| KM15 Memory Protect and KT15 Memory Protect/Relocate                           | 965              | 880     | 965   | 880     | 1165         | 1080    | 1165  | 1080    |

| MP15 Memory Parity                                                             | 1100             | 1050    | 1100  | 1050    | 1100         | 1050    | 1100  | 1050    |

| MP15 Memory Parity and<br>KM15 Memory Protect                                  | 1130             |         | 1130  |         | 1130         |         | 1255  |         |

| MP15 Memory Parity,<br>KM15 Memory Protect and<br>KT15 Memory Protect/Relocate | 1155             |         | 1155  |         | 1355         |         | 1355  |         |

Note: Cycle times are affected by installation of ME15 memory and by the Unichannel 15 System. Refer to the appropriate maintenance manual for additional information.

<sup>\*</sup>All cycle times are listed in nanoseconds.

# CHAPTER 2 MM15 MEMORY

#### 2.1 INTRODUCTION

The basic PDP-15 computer has a 4096 word, 18-bit memory. It occupies the top four racks of the PDP-15 mainframe (racks A through D). The principal elements comprising rack A are control logic, bus drivers, and INPUT slots for the memory bus cables. The memory address and memory buffer registers, x- and y-select and driver controls, and OUTPUT slots for the memory bus cables comprise rack B. The stack matrix, sense amps and inhibit drivers, and slots for the indicator bus, make up racks C and D.

This basic memory may be expanded to 8192 words by adding a 4K stack, a set of X- and Y-select and driver modules, and a set of inhibit and sense amp modules. The appropriate slots are available in the MM15 and the addition is the option called MK15.

Each 4K unit of memory is called a page. Two 4K pages form an 8K bank. The physical capacity of the mainframe is 32K (32,768) words. One 8K bank of memory is located above the mainframe front panel. The three remaining 8K banks are located on the rear door. This 32K unit is called a block of memory.

#### 2.2 CORE ADDRESSING MATRIX

#### 2.2.1 Stack Dimensions

The MM15 memory stack is a three dimension-three wire matrix (3D-3 wire). The term three dimension refers to an X-current, a Y-current, and an inhibit current. The X- and Y-currents are used to switch the direction of the flux of a core; the inhibit current is used during the writing time to prevent the writing of bits where 0 bits are desired.

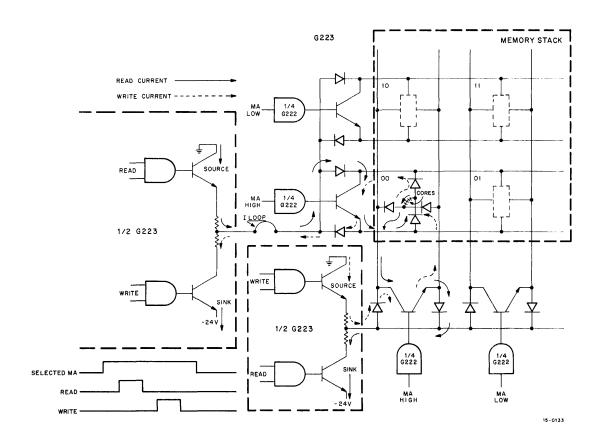

One matrix control network is used for each 4096 core words. The memory address selects which word of the 4096 words is to be read or written into or both. The drive current pulses are generated by G223 Read/Write Drivers. G222 Memory Selectors steer the direction of these currents.

When these currents flow through the core region they pass through 18 planes; the X-current pulse through one set of wires and Y-current pulse through another set of wires. In each plane, the X and Y current pulses intersect at one of the possible 4096 cores (bits). This happens in all 18 planes producing an 18-bit word selection. A nineteenth plane is added for parity options.

The inhibit current pulse occurs only during a write portion of the memory cycle. The inhibit current controls the bit data to be written into the address selected. This control is accomplished by stringing a wire through all the cores of each individual plane to nullify the effect of the Y current at the core intersection point. In addition to using these wires for the inhibit current during a write portion of a memory cycle, they are used for sensing the data during a read portion of a memory cycle.

#### 2.2.2 X-Y Matrix Construction

Each of the 4096 word locations provided by a 64 x 64 X-Y matrix may be referenced by a 12-bit memory address. This memory address is separated into two sections: bits 06-11 for the Y-select and bits 12-17 for the X-select. It is decoded by the G222 modules. The total combination results in a 4096 word selection. The current pulse, generated from the G223s, provides the current needed to change the flux in the core. There is a G223 for each X and Y matrix.

Figure 2-1 shows the current path produced by the combination of the modules and stack. Although this figure represents only one matrix of either X or Y, both matrices run at the same time. The solid arrows show a read current path and the dashed arrows show a write current path through the same selected network. In this figure one can visualize four different core line paths by having pre-selected the gates. Block schematics MM06 through MM09 (Volume 2) show the X and Y matrices contained in a bank of memory. The I Loop is a jumpered wire on the back panel wiring for observation of current waveforms on an oscilloscope. There is a loop for each matrix.

#### 2.2.3 Inhibit/Sensing Construction

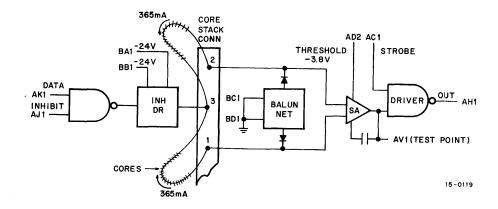

The construction of the sense/inhibit network consists of one wire threaded through all the cores in each plane. The circuitry, for the sensing of a bit during a readtime and inhibiting during a write-time, is contained in the G100 Sense Amplifier and Inhibit Driver modules.

The G100 module contains four sense amplifiers and four inhibit drivers. Five of these modules are used in the PDP-15 for each 4K memory stack. (Refer to block schematics MM10 through MM15.) Each inhibit driver consists of a two-input NAND gate and a high-speed current switch. One driver is used for each bit plane of the memory array. An inhibit signal is received by all inhibit drivers only during a write operation (see Figure 2-2).

Figure 2-1 Current Path Diagram

Figure 2-2 Sense Amplifier/Inhibit Driver, Simplified Diagram

Each driver also receives a signal indicating the state of the corresponding bit in the MB. Inhibit drivers that receive a signal indicating a 0 state in the MB bit are gated on and cause inhibit current to be applied to the associated bit plane of the memory array. Each inhibit driver employs a discharge network to speed up inhibit current cutoff. The output of the inhibit driver is connected to the middle of one core sensing string, which represents one bit plane of the memory array. The balun network at the front end of the sense amplifier ensures equal current at all times through both sides of the core string.

In addition to the balun network, the sense amplifier consists of a differential amplifier and output driver. One sense amplifier is used for each bit plane of the memory array. During a read operation only the signal induced on the sense winding of a core plane by a core-changing state is received by the differential amplifier. The differential amplifier has a nominal threshold of 17 mV. Output pulses of standard amplitude and duration are supplied by the output driver when the sense amplifier reads a logic 1 from the associated core, and is strobed by a standard positive going pulse at AC1. Propagation delay from the input to the sense amplifier to the buffered output is 25 ns (maximum) and from strobe input to buffered output is 15 ns (maximum). These output pulses directly set the MB register.

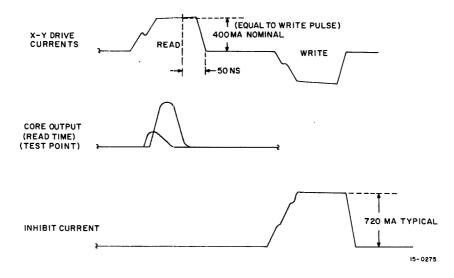

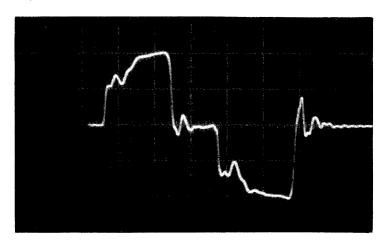

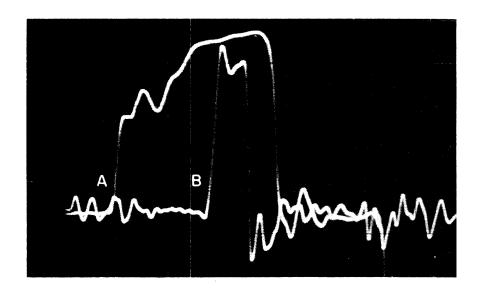

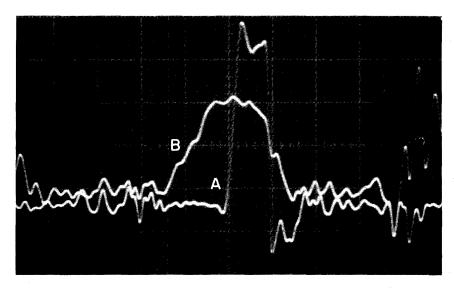

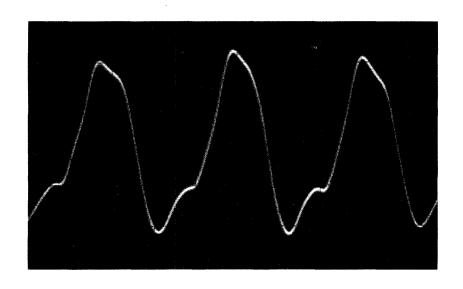

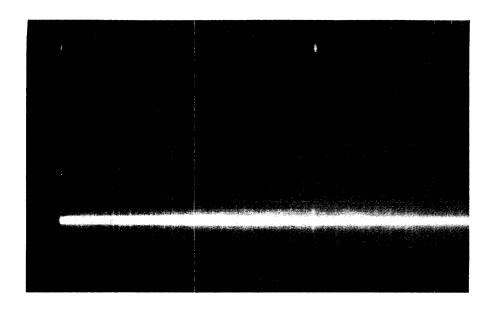

Typical waveforms of the inhibit current and the test point of the sense amplifier during a readtime are shown in Figure 2-3. The only way to look at an inhibit current is to place a current probe around one of the twisted pairs of wires coming out of the stack at the plug end.

Figure 2-3 Typical Inhibit Current Waveforms

#### 2.3 CONTROL LOGIC ARCHITECTURE

The control logic is designed so that each bank can be coupled to one bus network called the memory bus. Each bank responds when address lines 03 and 04 equal the setting of the manual switches on the bank select card. These two switches can be preset by the operator (refer to Volume 2, drawing MM01).

Maintenance hint: Any computer with more than one bank of memory may interchange one addressing bank number with another bank. All that is necessary is to manipulate the toggle switches on each bank of memory. No two should be set to the same number. Volume 2, drawing MM01 shows the logic representation of the switches.

An exchange of signals between the memory and the device requesting access to the memory provides asynchronous operation. The device has to provide five control signals, a 17-bit address (15 bits for 32K addressing and two more bits for the multiplexer option when addressing up to 128K), 18 bits of data, and one more bit for parity, when a parity option is included. In return the memory accepts the signals and notifies the device with a combination of four control signals and 18 bits of data plus one bit for parity checking. Table 2-1 identifies the bus signals and data lines on the memory bus. All signal lines are considered activated when at ground level. All data lines are considered a one when at ground level.

Table 2-1

Memory Bus Signals and Data Lines

| Abbreviation     | Signal & Direction                                                         | Definition                                                                                                                              |  |  |  |  |

|------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| MDL00-17<br>(MA) | Memory Data Lines,<br>00 through 17<br>(Memory Address to<br>memory)       | Sends a seventeen bit word to memory, address-ing up to 128K locations.                                                                 |  |  |  |  |

| (DATA)           | (Data bidirectional)                                                       | Data consisting of 18 bits per word going in both directions on the memory data lines (MDL).                                            |  |  |  |  |

| MWR<br>MRD       | Memory Write<br>Memory Read (to<br>(to memory)                             | Two levels used by the memory to identify what mode of operation the device has selected. There are three:                              |  |  |  |  |

|                  |                                                                            | 1 Read/Restore (MRD ground)<br>(MWR high)                                                                                               |  |  |  |  |

|                  |                                                                            | 2 Clear/Write (MRD high)<br>(MWR ground)                                                                                                |  |  |  |  |

|                  |                                                                            | 3 Read/Pause/Write (MRD ground)<br>(MWR ground)                                                                                         |  |  |  |  |

| M REQ            | Memory Request (to memory)                                                 | The initial signal that begins the memory cycle                                                                                         |  |  |  |  |

| M BUSY B         | Memory Busy on the<br>Bus (from Memory<br>bank to other Mem-<br>ory banks) | This signal inhibits a memory request from being accepted by any memory bank on the same but while any one of the memory banks is busy. |  |  |  |  |

Table 2–1 (Cont)

Memory Bus Signals and Data Lines

| Abbreviation | Signal & Direction                                      | Definition                                                                                                                                                                                                        |

|--------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADR ACK B    | Address Acknow-<br>ledge on the Bus (to<br>device)      | Notifies the device of acceptance of the Memo-<br>ry Request, the Memory Address, and the mode<br>of operation (MRD and MWR signals).                                                                             |

| RD RST B     | Read/Restart on the<br>bus (to device)                  | Notifies the device that the memory data is on<br>the bus for the device to strobe into its buffer.<br>This signal occurs only during a Read/Restore cy<br>cle or Read/Pause/Write cycle.                         |

| DATA ACK     | Data Acknowledge<br>(to memory)                         | Notifies the memory that it may take the memory data off the bus. This signal is only needed during a Read/Restore cycle or a Read/Pause/Write cycle.                                                             |

| MRLS         | Memory Release (to<br>memory)                           | Notifies the memory it has accepted the data from memory during a Read/Restore cycle. During a Clear/Write cycle or a Read/Pause/Write cycle, this signal tells the memory the device has placed data on the bus. |

| MRLS ACK B   | Memory Release<br>Acknowledge on the<br>Bus (to device) | Notifies the device that the memory accepted the data from the device and the memory cycle is terminating.                                                                                                        |

| M PAR        | Memory Parity (bi-<br>directional)                      | This signal line carries a 19th bit of data to be stored into or readout of memory. This bit is used to check data errors when a memory parity option is implemented into the system.                             |

Only one memory is allowed to be activated at a time. In order to guarantee that only one bank will be accessed, a Memory Busy level (refer to Volume 2, MM01 and MM19) is placed on the bus, in-hibiting any other Memory Request from being accepted. The internal timing of this signal, as well as all other signals, is described in Paragraph 2.4.

#### 2.4 CONTROL LOGIC FLOW

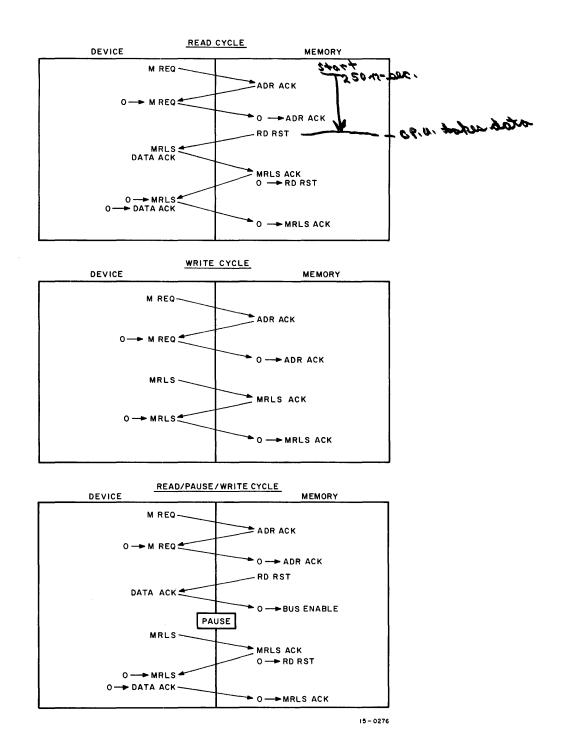

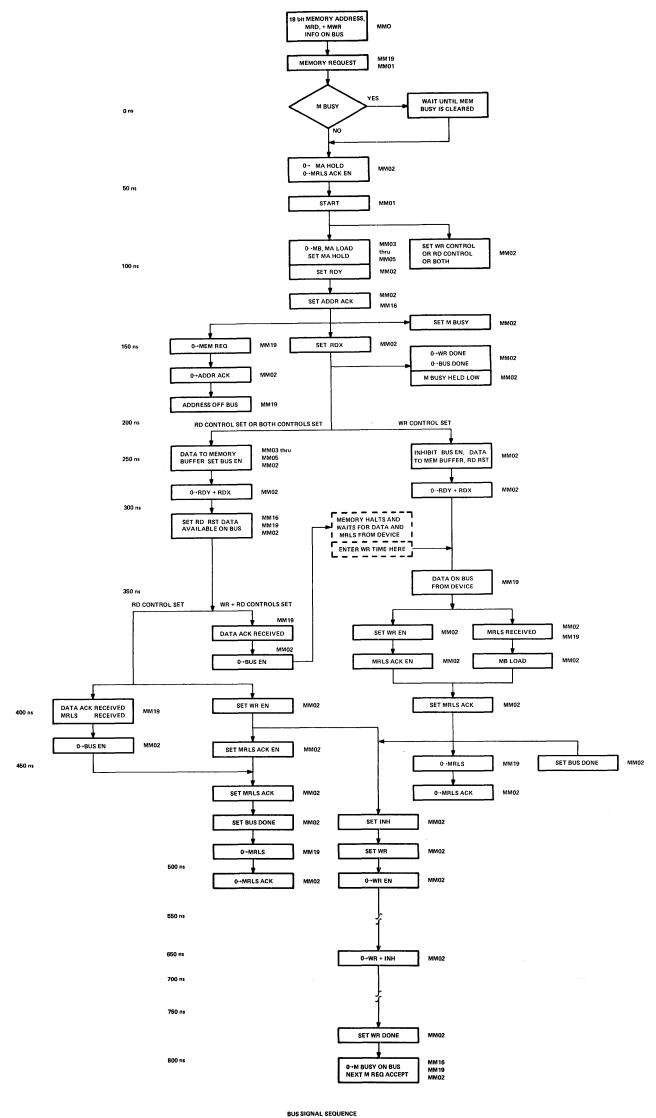

Refer to Figure 2-4. The memory is able to operate in any of three modes: Read/Restore, Clear/Write, or Read/Pause/Write. The mode of operation to be selected depends entirely upon the needs of the device. This can be seen as the sequence of a memory cycle is defined.

Before memory can be started, Memory Busy must not be true and a 17-bit memory address (MDL 00-17) and MRD, MWR, or both must be activated on the bus.

Figure 2-4 Basic Device-Memory Control Signal Flow

The memory cycle starts with the Memory Request level from the device. This level is generated 50 ns after the above levels to allow for settling time on the bus. (Settling time is needed to avoid potential skewing problems.) The device will wait until it receives an acceptance level from the memory called Address Acknowledge (ADR ACK (1) B L). This occurs approximately 110 ns after M REQ. The initiation of this level tells the device that the memory has accepted the request for access to memory, the mode of operation, and has strobed the memory address lines into the MA latch register. The Address Acknowledge causes Memory Busy to go low and also clears the Memory Request level. The fall of the Memory Request level clears the Address Acknowledge level. At this point the sequence of the memory cycle may go into any of the three modes of operation. Each is described in the following paragraphs.

#### 2.4.1 Read/Restore Cycle

For this mode of operation the RD CON (read control) flop would have been set and the memory would proceed to read data from the address requested. The 18 bits of data read from core are strobed into the Memory Buffer register and enabled on the bus (MDL 00-17) approximately 150 ns after ADR ACK is set. A parity bit is also strobed, if the option is present (MDL PAR (1) B L). In order to allow for settling time on the bus, the device only strobes this data when a Read/Restart level (RD RST (1) B L) is placed on the bus by the memory, approximately 100 ns after the data is on the bus. The total data access time is approximately 350 ns.

After a delay, the memory sets the WR EN (write enable) flop which is ANDed with the WR CON (write control) flop on a zero state to begin the write portion of the cycle. The sequence is to rewrite the data from the memory buffer registers into the same location from which it was read. In parallel with the memory data rewrite, the device sends a level called Data Acknowledge (DATA ACK L) which the memory uses to clear the bus enable register, removing data from the bus. A Memory Release level (MRLS L) is sent at the same time as the Data Acknowledge level to tell the memory that the device has accepted the data. When the MRLS level has been received and the write enable flop has been set in the memory, the memory sends to the device an acknowledge called MRLS Acknowledge (MRLS ACK (1) B L). The device uses the MRLS ACK level to clear its MRLS level which, in turn, clears MRLS Acknowledge. (This sequence occurs in every mode of operation.) The memory cycle then terminates with the Memory Bus level (M Busy B L) going high.

#### 2.4.2 Clear/Write Cycle

For this mode of operation the WR CON (write control) flop is set, and the memory proceeds to read the data from the address requested as is done in a Read/Restore cycle. The exceptions are that the data is not loaded into the Memory Buffer, and the bus enable and read/restart flops are not set. The

function of this read is to clear the core location for the writing process. In parallel with this, the device accepts the Address Acknowledge level and places the data to be written into memory on the bus. To ensure settling time on the bus, a 50 ns delay occurs before the MRLS level is sent to memory. In the memory, an MB load pulse is generated with the MRLS level and the data is loaded into the Memory Buffer register. A Data Acknowledge level is not needed at this time with the MRLS level because it is only used to clear the bus enable register.

The MRLS level sets the MRLS ACK flop telling the device that the memory has accepted the data. The MRLS ACK flop ANDed with the Write Enable flop (detecting the termination of the read portion of this cycle) begins the write portion of this cycle, writing the data into the address requested.

During the write portion, a delayed sequence sets the inhibit flop and the write flop. The inhibit flop ANDed with the memory buffer bits produces inhibit currents that are applied to each individual bit plane, depending on the status of the memory buffer bit. A zero bit initiates the current pulse. The memory cycle then terminates with a Memory Busy level going high.

#### 2.4.3 Read/Pause/Write Cycle

For this mode of operation both the read control and write control flops are set. The memory proceeds to read the data from the address requested as in a Read/Restore cycle. When the Read/Restart level is sent out to the device, the device strobes the data into its registers and proceeds to modify the data. The device at this time sends to memory a Data Acknowledge level which in turn clears the bus enable flop taking the memory data off the bus. The MRLS level is not sent at this time. The write enable flop does not initiate a write portion of the cycle. Instead the memory cycle halts. This is called the Pause portion of the Read/Pause/Write cycle.

While the memory is in the Pause state, the device modifies the data it has previously read from the memory and places it back on the bus. In order to provide settling time on the bus, the MRLS level is sent to the memory approximately 50 ns after the data is on the bus. When the memory receives MRLS, the modified data is strobed into the memory buffer registers. The write portion of this cycle begins with the MRLS ACK flop and the Write enable flop set. The data is written into the same address as requested at the beginning of this cycle. A Memory Address Hold flop ensures the address will be saved throughout the cycle. The memory cycle then terminates with a Memory Busy level going high.

The advantage of a Read/Pause/Write cycle is that a memory word may be read, modified, and rewritten in one memory cycle. An example of this is when a device wishes to update a current address location by adding one and restoring it. The flow chart in Figure 2-5 shows these same sequences with a little more attention to the internal logic flow.

Table 2-2 describes control flop and register nomenclature and major responsibilities. It is an aid in understanding the detailed flow chart shown in Figure 2-5.

Table 2–2 Control Flops and Register Responsibilities

| Abbreviation                | Control Flops<br>or Register                                                             | Responsibility                                                                                                                                                                                                                                         |

|-----------------------------|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RD Con<br>WR Con            | Read Control<br>Write Control                                                            | Strobed when a request is accepted. Holds data throughout memory cycle. Tells memory which one of the three modes to pursue.                                                                                                                           |

| MA HOLD                     | Memory Address<br>Hold                                                                   | Cleared and set when a request is accepted. It holds the memory address information in the latches throughout the memory cycle.                                                                                                                        |

| MA00 through MA17           | Memory Address 00<br>through 17 (bus ad-<br>dress to memory di-<br>rection only)         | A set of 18 latches which contain the address to be accessed during the memory cycle.                                                                                                                                                                  |

| ADR ACK                     | Address Acknowledge<br>(bus signal)                                                      | This control flop tells the device that it has accepted the request for memory use and strobed in the address. It will clear itself with the loss of the Memory Request on the bus.                                                                    |