Digital Equipment Corporation Maynard, Massachusetts

PDP-15 Systems Maintenance Manual Volume 1

# **RP15 Disk Pack Control**

digital

DEC-15-H3GB-D

# **PDP-15 SYSTEMS** RP15 DISK PACK CONTROL MAINTENANCE MANUAL VOLUME 1

DIGITAL EQUIPMENT CORPORATION • MAYNARD, MASSACHUSETTS

First Printing January 1971 2nd Printing (rev) October 1971

Copyright © 1971 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

| DEC       | PDP          |

|-----------|--------------|

| FLIP CHIP | FOCAL        |

| DIGITAL   | COMPUTER LAB |

#### CONTENTS

Page

| CHAPTER 1 | SYSTEM DESCRIPTION                     |      |

|-----------|----------------------------------------|------|

| 1.1       | General                                | 1-1  |

| 1.2       | RP15 Control                           | 1-1  |

| 1.3       | Disk System Characteristics            | 1-1  |

| 1.3.1     | Disk vs Drum                           | 1-3  |

| 1.3.2     | Disk Pack Effects on the Drive         | 1-3  |

| 1.4       | RP02 System Characteristics            | 1-3  |

| 1.4.1     | RP02P Disk Pack                        | 1-3  |

| 1.4.2     | RP02 Disk Pack Drive                   | 1-4  |

| 1.5       | PDP-15 Computer System Characteristics | 1-8  |

| 1.6       | Single-Cycle Interface and I/O Bus     | 1-9  |

| 1.7 ·     | Reference Documents                    | 1-10 |

| CHAPTER 2 | CONTROLS AND OPERATIONS                |      |

| 2.1       | General                                | 2-1  |

| 2.2       | Controls and Indicators                | 2-1  |

| 2.3       | Operating Procedures                   | 2-11 |

| 2.3.1     | Loading                                | 2-11 |

| 2.3.2     | Unloading                              | 2-12 |

| 2.3.3     | Storage                                | 2-12 |

| 2.4       | Special Operating Procedures           | 2-12 |

| 2.4.1     | Write Protection                       | 2-12 |

| 2.4.2     | Formatting a Disk                      | 2-13 |

| CHAPTER 3 | PROGRAMMING                            |      |

| 3.1       | General                                | 3-1  |

| 3.1.1     | RP02 Disk Pack Structure               | 3-1  |

| 3.1.2     | IOT Selection                          | 3-4  |

| 3.1.3     | RP15 Status Facility                   | 3-7  |

| 3.2       | Sequence of Operation                  | 3-12 |

| 3.2.1     | Write Function                         | 3-12 |

| 3.2.2     | Read Function                          | 3-16 |

| 3.2.3     | Read All Function                      | 3-17 |

| 3.2.4     | Write All Function                     | 3-18 |

#### CONTENTS (Cont)

|       |                      | Page |

|-------|----------------------|------|

| 3.2.5 | Write Check Function | 3-19 |

| 3.2.6 | Idle Function        | 3-20 |

| 3.2.7 | Seek Function        | 3-20 |

| 3.2.8 | Recalibrate Function | 3-21 |

| 3.3   | Program Loop         | 3-22 |

#### CHAPTER 4 DRAWING CONVENTIONS

| 4.1 | Flow Chart Symbology      | 4-1 |

|-----|---------------------------|-----|

| 4.2 | Block Schematic Symbology | 4-1 |

| 4.3 | Logic Module Symbology    | 4-1 |

#### CHAPTER 5 PRINCIPLES OF OPERATION AND HARDWARE DESCRIPTION

| 5.1    | General                              | 5-1          |

|--------|--------------------------------------|--------------|

| 5.2    | Detailed Block Diagram               | 5-1          |

| 5.3    | Selecting the Controller             | 5-1          |

| 5.4    | Status Monitoring and DCH DATA       | 5-5          |

| 5.5    | Selecting the Drive                  | 5-6          |

| 5.6    | Selected Unit Cylinder Interrogation | 5-6          |

| 5.7    | Addressing the Pack                  | 5 <b>-</b> 7 |

| 5.8    | Cylinder Comparison                  | 5-13         |

| 5.9    | Sequencing the Memory                | 5-13         |

| 5.10   | Commanding the Controller            | 5-14         |

| 5.10.1 | Idle Function                        | 5-16         |

| 5.10.2 | Read Function                        | 5-16         |

| 5.10.3 | Write Function                       | 5-16         |

| 5.10.4 | Recalibrate Function                 | 5-16         |

| 5.10.5 | Seek Function                        | 5-17         |

| 5.10.6 | Read All Function                    | 5-17         |

| 5.10.7 | Write All Function                   | 5-18         |

| 5.10.8 | Write Check Function                 | 5-18         |

| 5.11   | Determining Length of Transfer       | 5-19         |

| 5.12   | Maintaining Disk Format              | 5-20         |

| 5.13   | Processing the Data                  | 5-21         |

| 5.13.1 | Buffer Register                      | 5-21         |

#### CONTENTS (Cont)

|                                              | Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Shift Register                               | 5-23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Longitudinal Parity Register                 | 5 <b>-24</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Controlling Major State                      | 5 <b>-</b> 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Commanding the Drive                         | 5 <b>-31</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Read Data Separation                         | 5-41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Maintaining Controller Format                | 5-55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Controlling Transfer Direction in the PDP-15 | 5-58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Controlling Transfer Direction in the RP02   | 5 <b>-67</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Controlling Transfer Direction in the RP15   | 5 <b>-</b> 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Word Count and Current Address Control       | 5 <b>-94</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Write Protection for the Drive               | 5 <b>-96</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Entire Unit Protection                       | 5-96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Partial Unit Protection                      | 5 <b>-</b> 97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Status Control                               | 5 <b>-</b> 99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Interrupt Control                            | 5-106                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Maintenance Control                          | 5-107                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Interfacing the Drive                        | 5-111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Interfacing the I/O                          | 5-111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                              | Longitudinal Parity Register<br>Controlling Major State<br>Commanding the Drive<br>Read Data Separation<br>Maintaining Controller Format<br>Controlling Transfer Direction in the PDP-15<br>Controlling Transfer Direction in the RP02<br>Controlling Transfer Direction in the RP15<br>Word Count and Current Address Control<br>Write Protection for the Drive<br>Entire Unit Protection<br>Partial Unit Protection<br>Status Control<br>Interrupt Control<br>Maintenance Control<br>Interfacing the Drive |

#### CHAPTER 6 MAINTENANCE

| 6.1     | Introduction                  | 6-1          |

|---------|-------------------------------|--------------|

| 6.2     | Preventive Maintenance        | 6-1          |

| 6.2.1   | Test Equipment Required       | 6-1          |

| 6.2.2   | Mechanical Checks             | 6-2          |

| 6.2.3   | Electrical Checks             | 6-2          |

| 6.2.4   | Margins                       | 6-4          |

| 6.3     | Corrective Maintenance        | 6-4          |

| 6.3.1   | General Corrective Procedures | 6 <b>-</b> 5 |

| 6.3.2   | Diagnostic Testing            | 6-5          |

| 6.3.2.1 | RP15 Instruction Test         | 6 <b>-</b> 5 |

| 6.3.2.2 | RP15 Formatter                | 6-8          |

| 6.3.2.3 | RP15 Address Test             | 6-9          |

| 6.3.2.4 | RP15 Random Data Exerciser    | 6-11         |

| 6.3.2.5 | Vibration Tests               | 6-12         |

٠~,

#### CONTENTS (Cont)

|           |                                                      | Page         |

|-----------|------------------------------------------------------|--------------|

| 6.3.3     | Switch Panel Testing – LOCKOUT, LO, and LOA Switches | 6-12         |

| 6.3.4     | Changing Panel Indicator Bulbs                       | 6-12         |

| CHAPTER 7 | SYSTEM SPECIFICATIONS                                |              |

|           |                                                      |              |

| 7.1       | General                                              | 7-1          |

| 7.2       | Mechanical Description                               | 7-1          |

| 7.3       | Equipment Specifications                             | 7-1          |

| 7.3.1     | Physical                                             | 7-1          |

| 7.3.2     | Environmental                                        | 7-2          |

| 7.3.3     | Electrical                                           | 7-2          |

| 7.3.4     | Performance                                          | 7 <b>-</b> 5 |

| CHAPTER 8 | INSTALLATION                                         |              |

| 8.1       | General                                              | 8-1          |

| 8.2       | Unpacking                                            | 8-1          |

| 8.2.1     | Special Handling                                     | 8-1          |

| 8.2.2     | Inspection                                           | 8-1          |

| 8.2.3     | Power Requirements                                   | 8-1          |

| 8.3       | Installation Procedure                               | 8-3          |

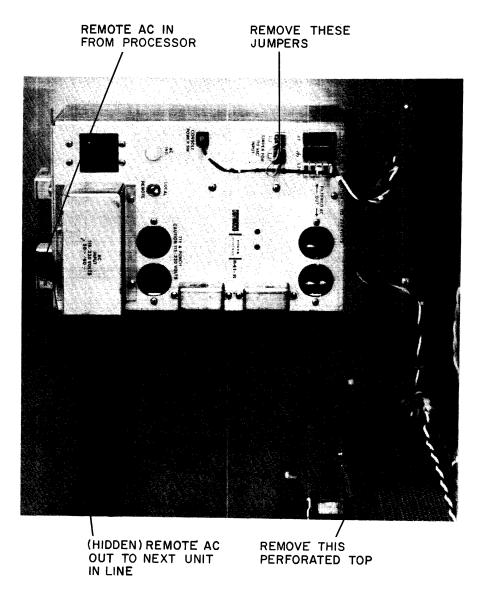

| 8.3.1     | Converting to Another Power Source                   | 8-3          |

| 8.3.2     | Installing the RP15 Cabinet                          | 8-6          |

| 8.3.3     | Installing Cables                                    | 8-6          |

| 8.3.4     | Setting Unit Number Designator                       | 8-9          |

| 8.4       | Turn-On and Checkout                                 | 8-9          |

| 8.4.1     | Built-In Testing Without RP02                        | 8-9          |

| 8.4.2     | Testing With RP02                                    | 8-10         |

|           |                                                      |              |

#### ILLUSTRATIONS

| Figure No. | Title                                                | Art No.          | Page |

|------------|------------------------------------------------------|------------------|------|

| 1-1        | RP15 Disk Pack Controller                            | 5363-3           | 1–2  |

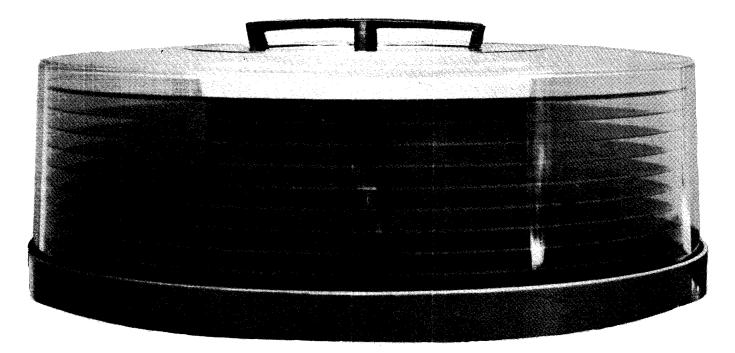

| 1-2        | RP02P Disk Pack                                      | 5363-7           | 1-4  |

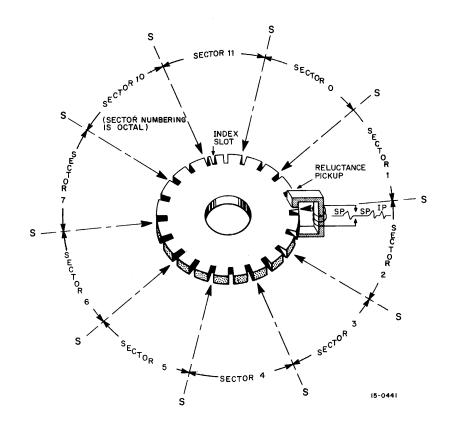

| 1-3        | RP02P Disk Pack Sector and Index Pulse<br>Generation | 15 <i>-</i> 0441 | 1-5  |

| 1-4        | RP02 Disk Pack Drive                                 | 5363-4           | 1-6  |

| Figure No. | Title                                                        | Art No.                    | Page |

|------------|--------------------------------------------------------------|----------------------------|------|

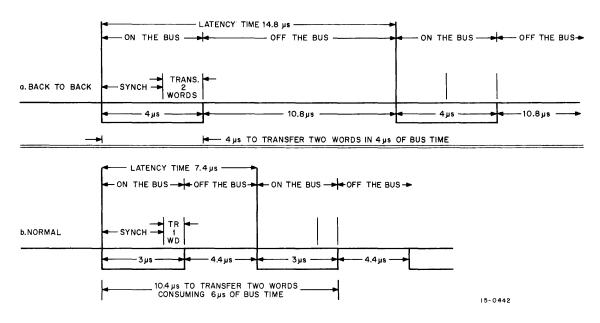

| 1–5        | Latency vs Transfer Time in Normal and<br>Back–To–Back Modes | 15-0442                    | 1-9  |

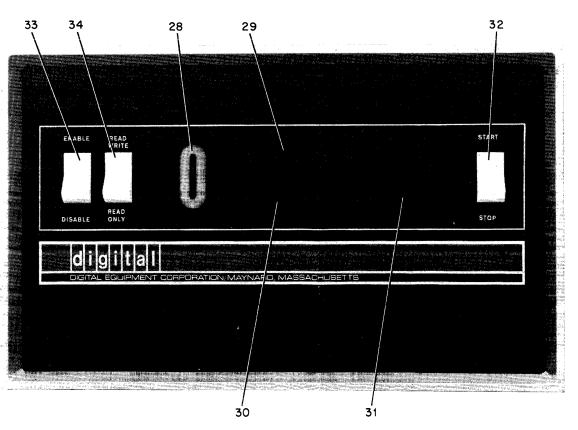

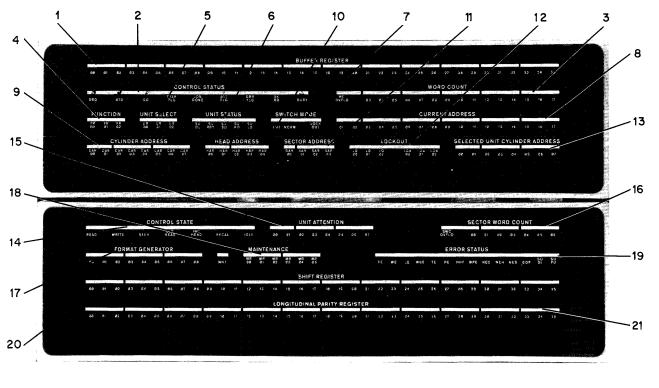

| 2-1        | RP15/02 Controls and Indicators                              | 5144-1<br>4830-1<br>5363-5 | 2-9  |

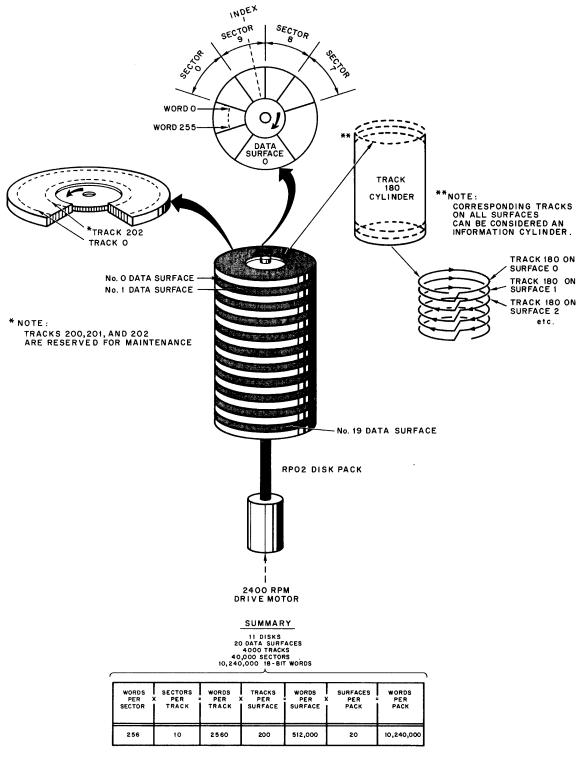

| 3-1        | RPO2 Disk Pack Structure                                     | 09-0343                    | 3-2  |

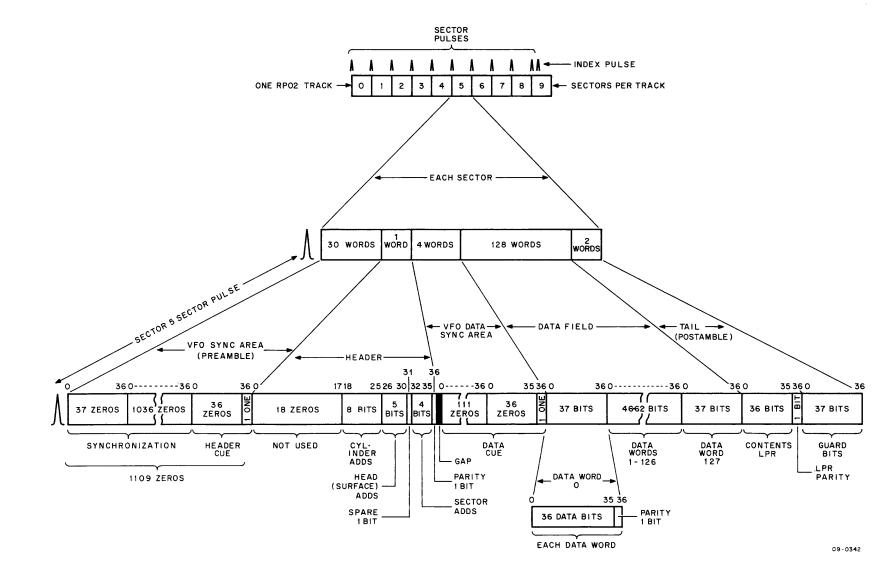

| 3-2        | RP02 Format for RP15 Controller                              | 09-0342                    | 3-3  |

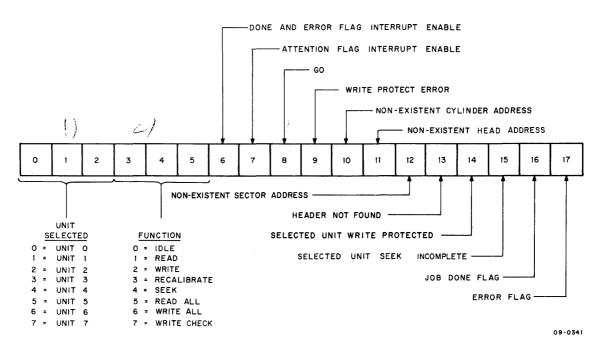

| 3-3        | RP15 Status Register A Bit Assignment                        | 09-0341                    | 3-8  |

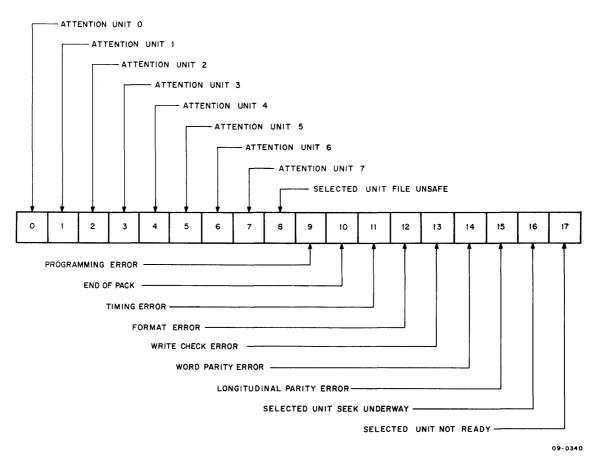

| 3-4        | RP15 Status Register B Bit Assignment                        | 09-0340                    | 3-8  |

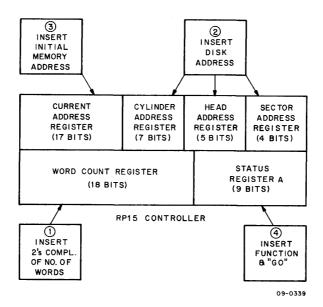

| 3–5        | Insert and Execute Phase                                     | 09-0339                    | 3-13 |

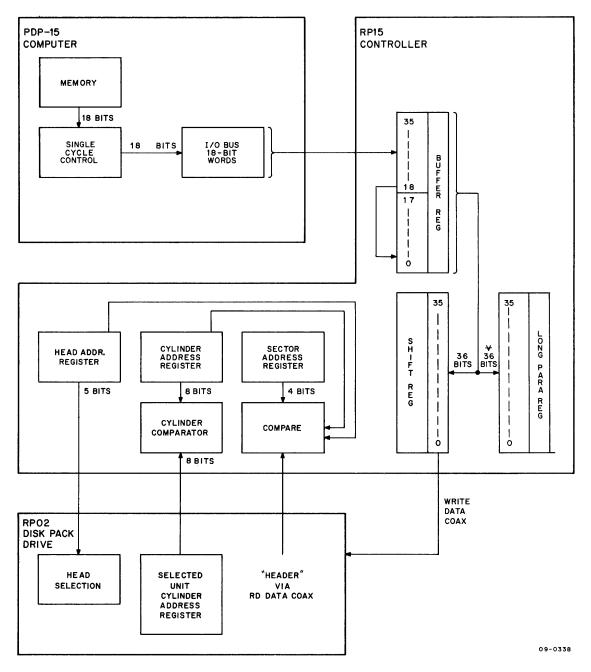

| 3-6        | WRITE Function, SEEK State                                   | 09-0338                    | 3-14 |

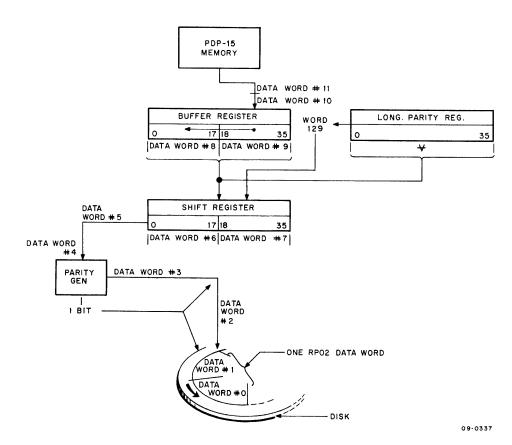

| 3-7        | WRITE Function, Transfer/Write States                        | 09-0337                    | 3-16 |

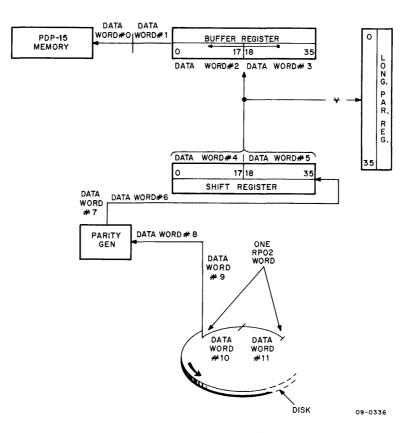

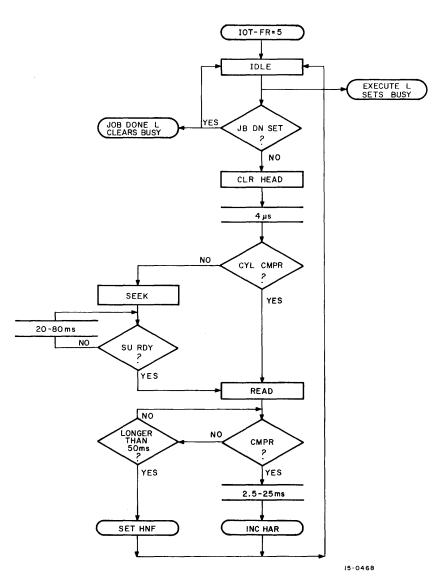

| 3-8        | READ Function, Read/Transfer States                          | 09-0336                    | 3-17 |

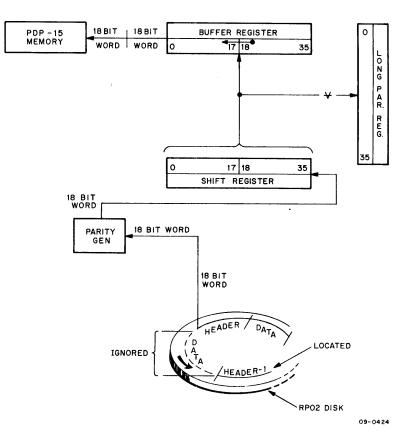

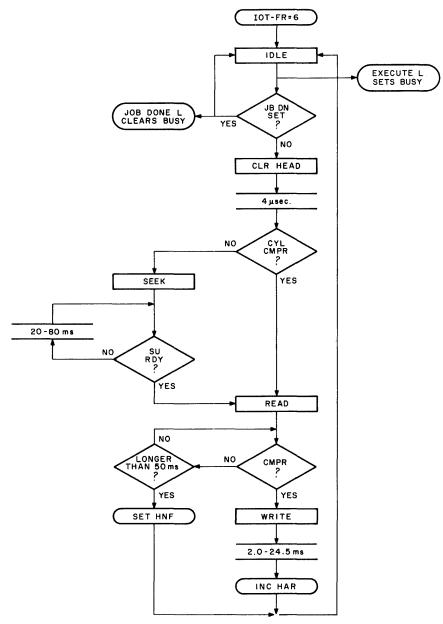

| 3-9        | READ ALL Function, Transfer States                           | 09-0424                    | 3-19 |

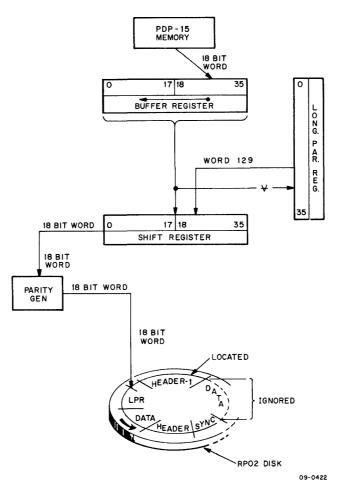

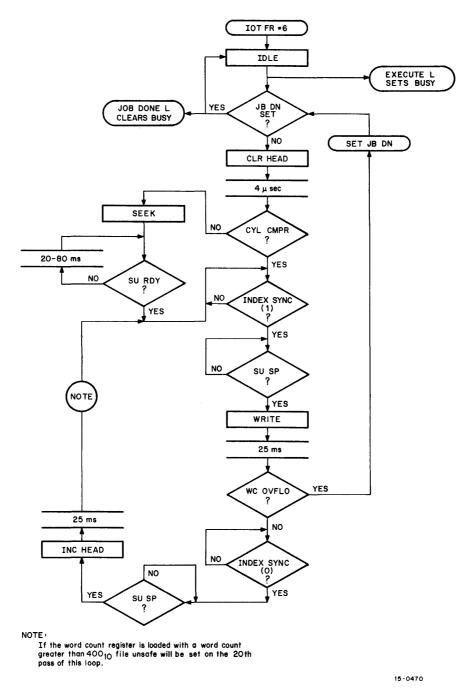

| 3-10       | WRITE ALL Function, Transfer States                          | 09-0422                    | 3-20 |

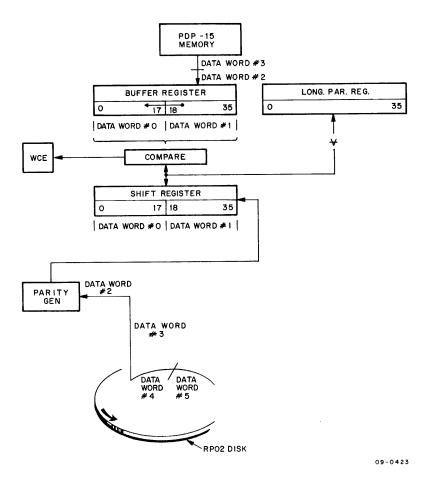

| 3-11       | WRITE CHECK Function, Transfer States                        | 09-0423                    | 3-21 |

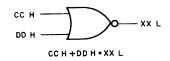

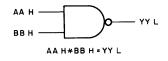

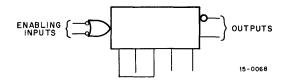

| 4-1        | NAND Gate (M112)                                             | 15-0068                    | 4-4  |

| 4-2        | NAND Gate (M113)                                             |                            | 4-4  |

| 4-3        | NOR Gate (M112)                                              |                            | 4-4  |

| 4-4        | NOR Gate (M113)                                              | 15-0068                    | 4-4  |

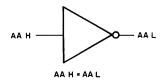

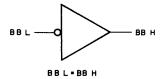

| 4–5        | Inverter (M111, M611)                                        |                            | 4-4  |

| 4-6        | Inverter (M111, M611)                                        |                            | 4-4  |

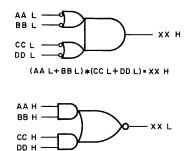

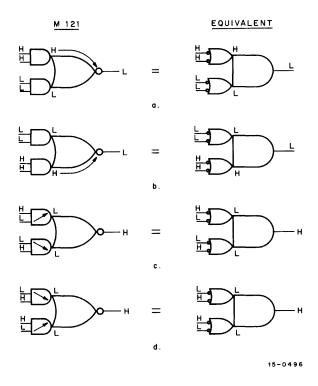

| 4-7        | Basic Logic Relationships (M121)                             |                            | 4-4  |

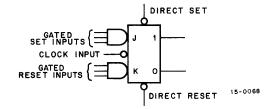

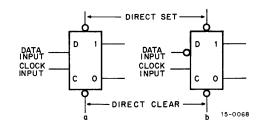

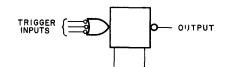

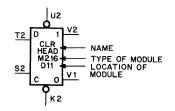

| 4-8        | D Flip-Flop - Edge Triggered (M216)                          | 15-0068                    | 4-4  |

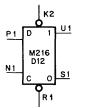

| 4-9        | J–K Master–Slave Flip–Flop (M204)                            | 15-0068                    | 4-4  |

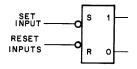

| 4-10       | R-S Flip-Flop (M203)                                         |                            | 4-4  |

| 4-11       | Variable Clock (M401)                                        | 15-0068                    | 4–5  |

| 4-12       | Pulse Amplifier (M602)                                       |                            | 4–5  |

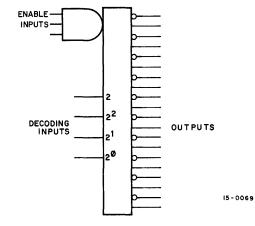

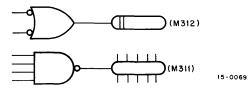

| 4-13       | I/O Bus Receiver (M510)                                      | 15-0069                    | 4–5  |

| 4-14       | Binary to Octal Decoder (M161)                               | 15-0069                    | 4-5  |

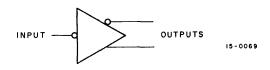

| 4-15       | Delays                                                       | 15-0069                    | 4–5  |

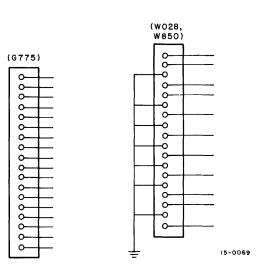

| 4-16       | Connectors                                                   | 15-0069                    | 4–5  |

| 4-17       | NAND Gate                                                    | 15-0443                    | 4-6  |

| 4-18       | CLR HEAD Flip-Flop                                           |                            | 4-6  |

| 4-19       | Synchronizing Flip-Flop                                      | 15 <b>-</b> 0444           | 4-6  |

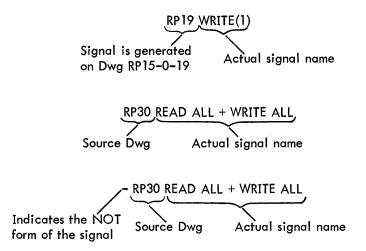

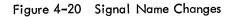

| 4-20       | Signal Name Changes                                          | 15-0445                    | 4-6  |

| Figure No.   | Title                                                     | Art No.          | Page          |

|--------------|-----------------------------------------------------------|------------------|---------------|

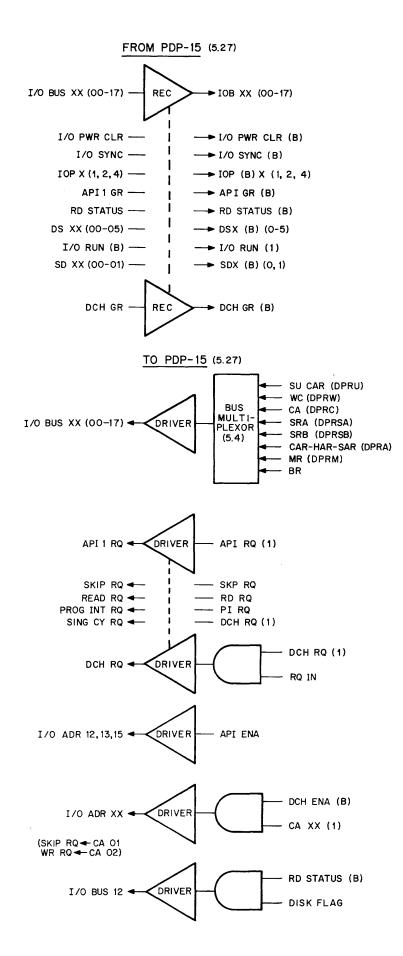

| 5-1          | RP15 General Block Diagram                                | 15-0514          | 5-3           |

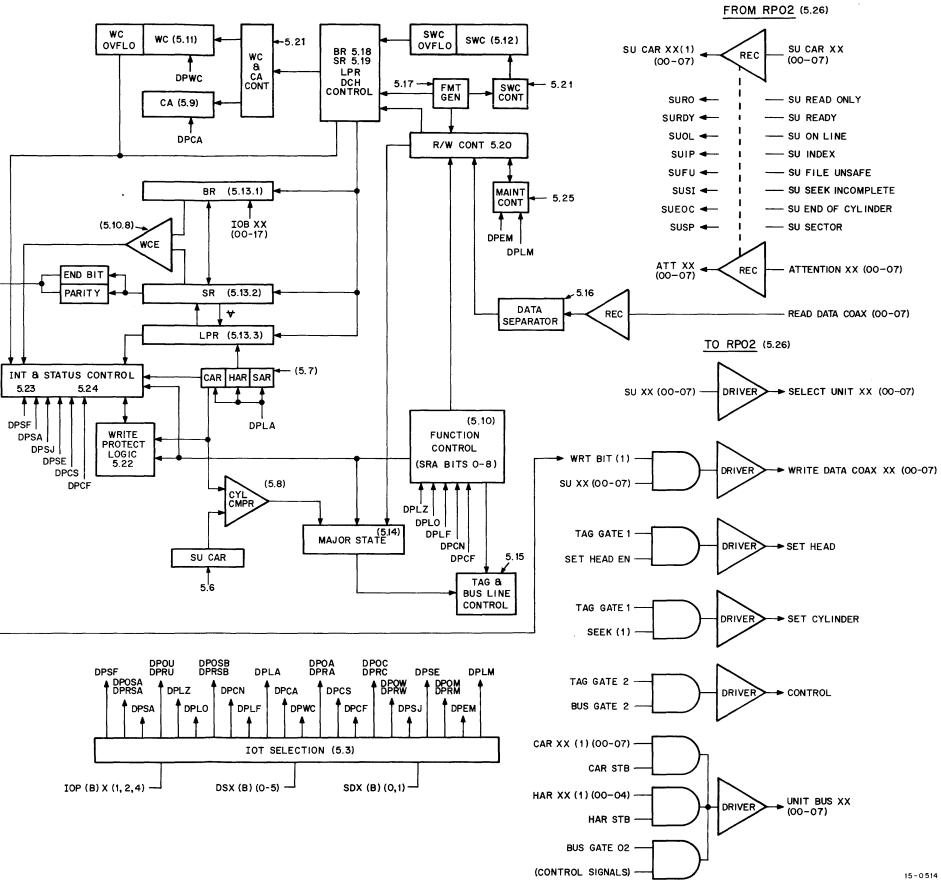

| 5-2          | Unit Selection Circuit                                    | 15-0447          | 5-6           |

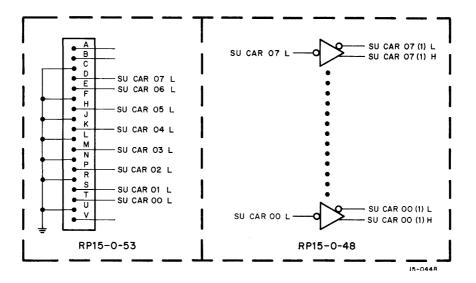

| 5-3          | SU Cylinder Interrogation Circuit                         | 15-0448          | 5-7           |

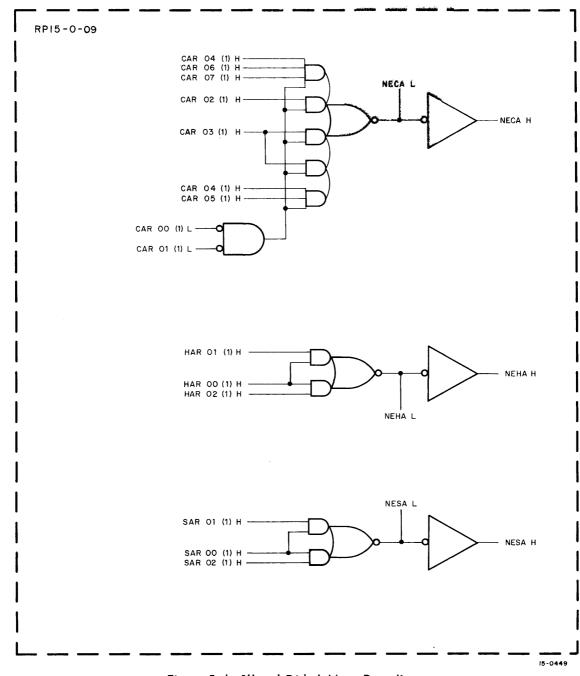

| 5-4          | Illegal Disk Address Decoding                             | 15-0449          | 5 <b>-</b> 9  |

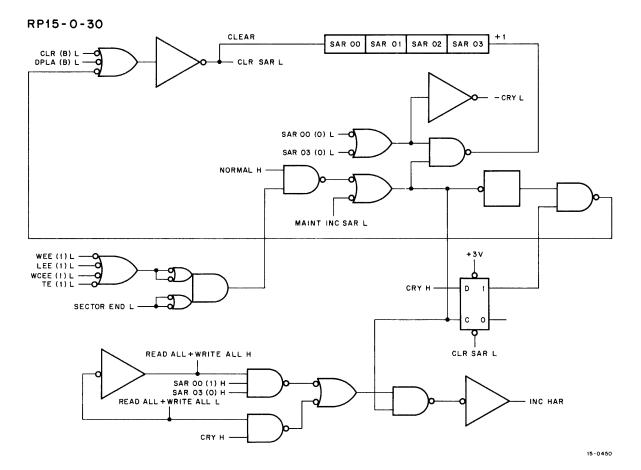

| 5-5          | SAR Control Logic                                         | 15-0450          | 5-10          |

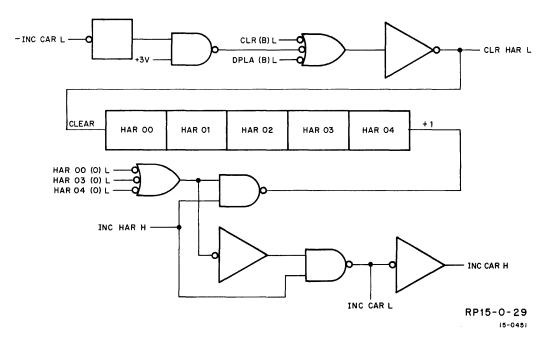

| 5-6          | HAR, Simplified Schematic                                 | 15-0451          | 5-12          |

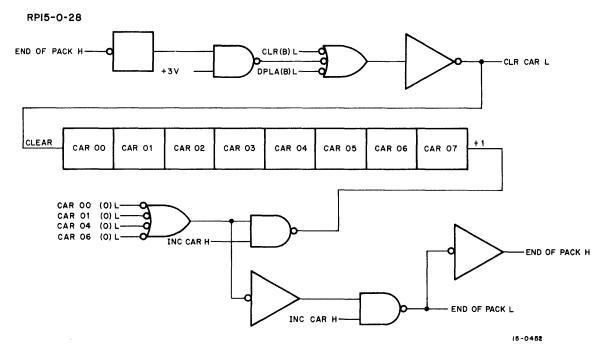

| 5-7          | CAR, Simplified Schematic                                 | 15-0452          | 5-12          |

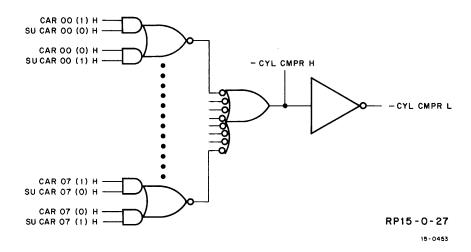

| 5-8          | Cylinder Comparator, Simplified Sche–<br>matic            | 15-0453          | 5-13          |

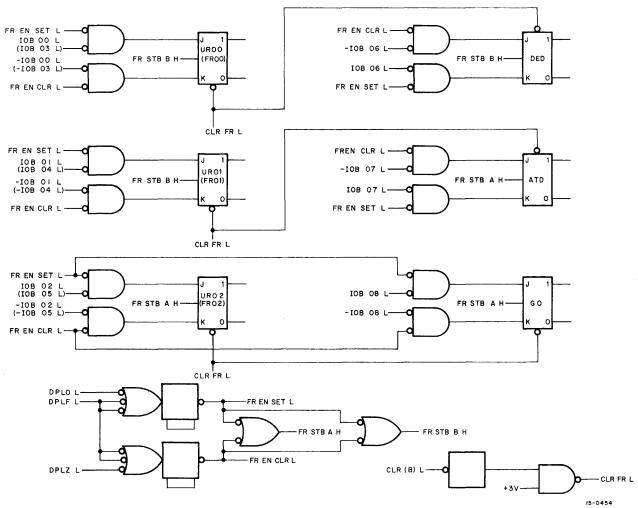

| 5-9          | Function Register, Simplified Schematic                   | 15 <b>-</b> 0454 | 5-15          |

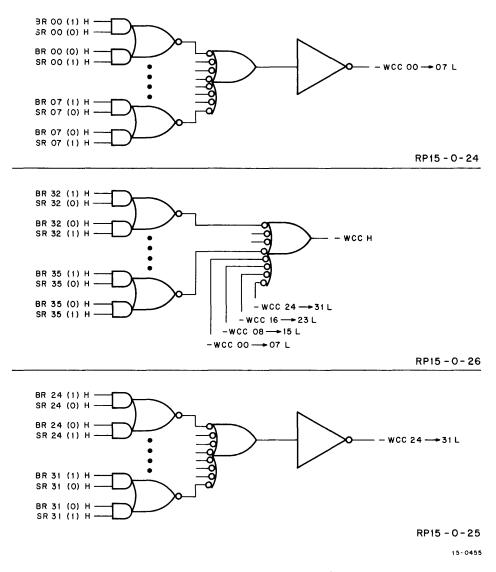

| 5-10         | Write Check Compare, Simplified Diagram                   | 15-0455          | 5 <b>-1</b> 9 |

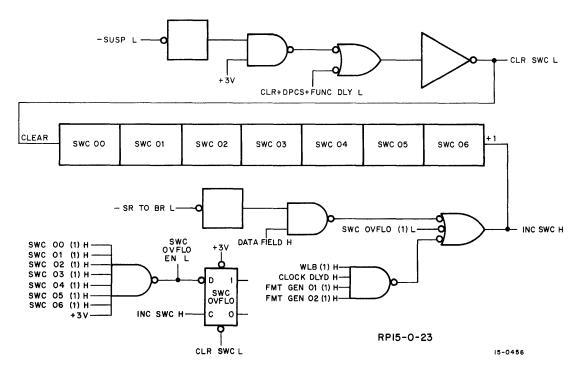

| 5-11         | Sector Word Counter, Simplified Diagram                   | 15-0456          | 5-20          |

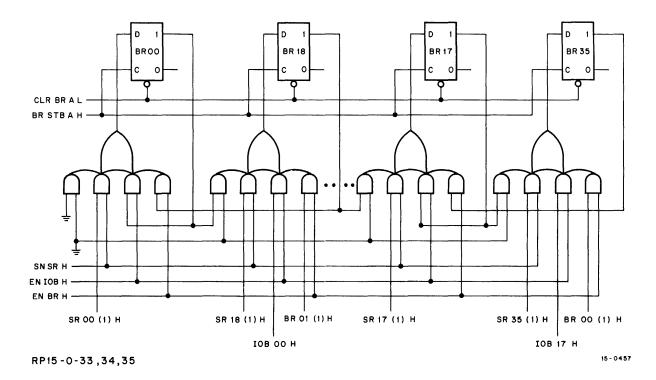

| 5-12         | Buffer Register, Simplified Diagram                       | 15-0457          | 5-22          |

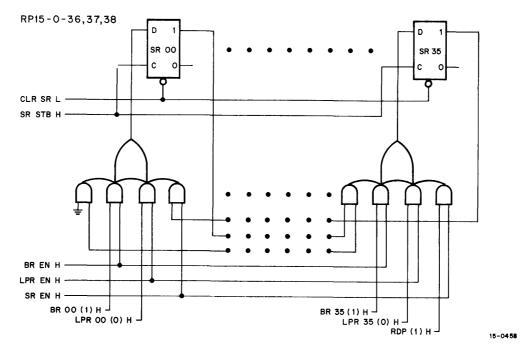

| 5-13         | Shift Register, Simplified Diagram                        | 15-0458          | 5-23          |

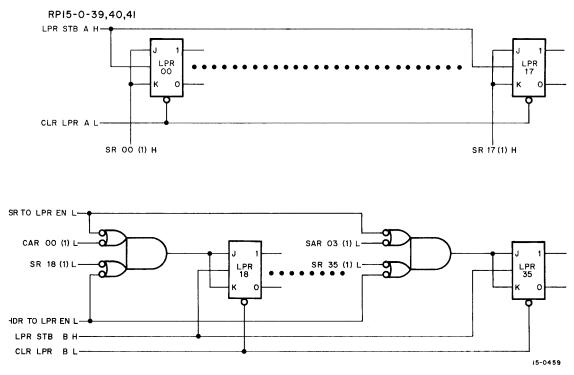

| 5-14         | Longitudinal Parity Register, Simplified<br>Diagram       | 15-0459          | 5 <b>-2</b> 5 |

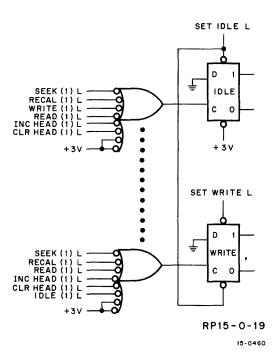

| 5-15         | Major State Control , Simplified Diagram                  | 15-0460          | 5 <b>-2</b> 6 |

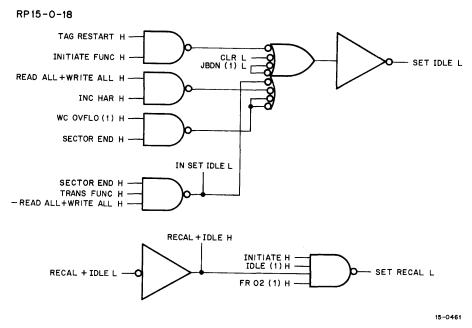

| 5-16         | Set Idle and Set Recal Logic, Simplified<br>Diagram       | 15-0461          | 5 <b>-27</b>  |

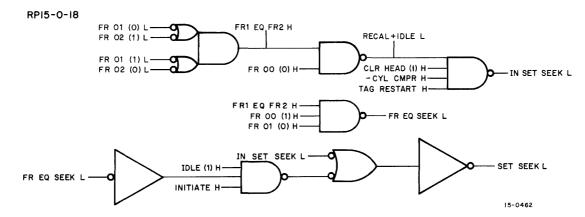

| 5-17         | Set Seek Logic, Simplified Diagram                        | 15-0462          | 5-28          |

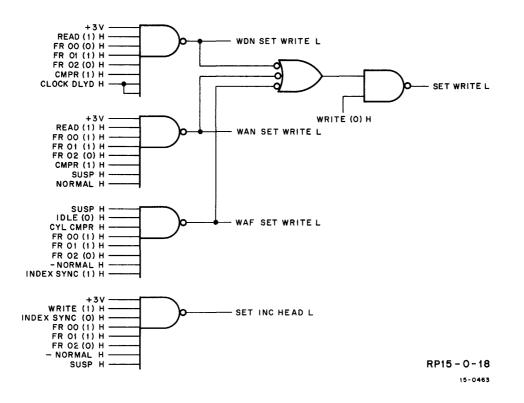

| 5-18         | Set Write and Set Inc Head Logic, Simpli–<br>fied Diagram | 15-0463          | 5-29          |

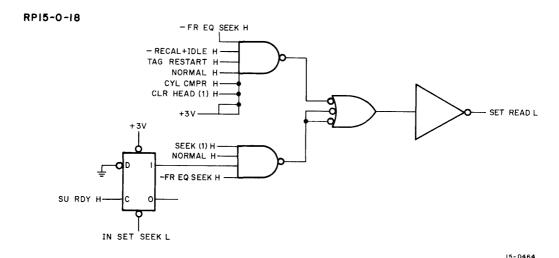

| 5-19         | Set Read Logic, Simplified Diagram                        | 15-0464          | 5-31          |

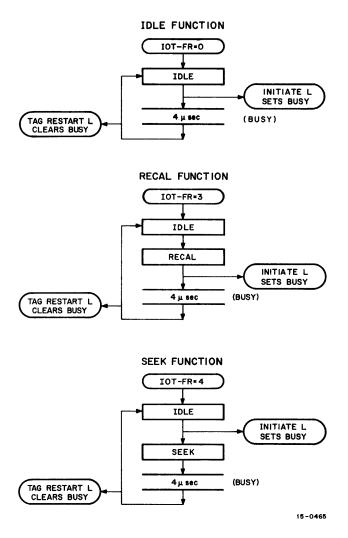

| 5-20         | Initiate Functions, Flow Diagram                          | 15-0465          | 5-32          |

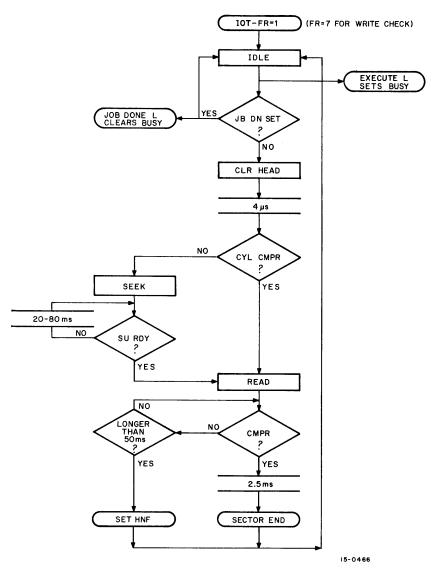

| 5-21         | Read or Write Check Functions, Flow<br>Diagram            | 15-0466          | 5-33          |

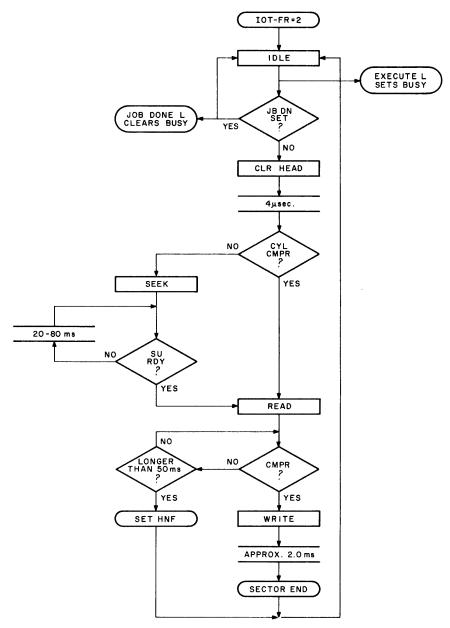

| 5-22         | Write Function, Flow Diagram                              | 15-0467          | 5-34          |

| 5-23         | Read All Function, Flow Diagram                           | 15-0468          | 5-35          |

| 5-24         | Write All Normal Function, Flow Diagram                   | 15-0469          | 5-36          |

| 5-25         | Write All Format Function, Flow Diagram                   | 15-0470          | 5-37          |

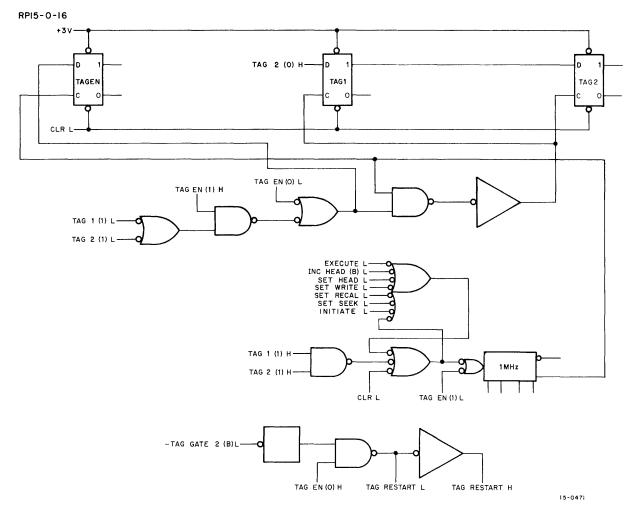

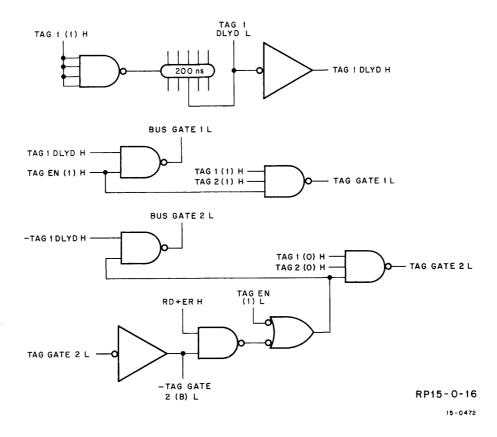

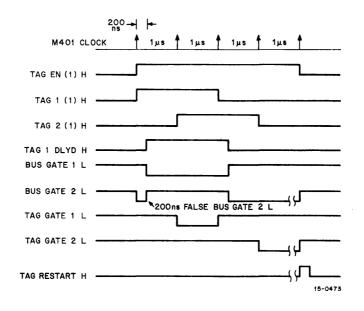

| 5–26         | Tag and Bus Line Control, Simplified Dia-<br>gram         | 15-0471          | 5-38          |

| 5–27         | Tag and Bus Gate Logic , Simplified Dia–<br>gram          | 15-0472          | 5-39          |

| 5-28         | Tag and Bus Line Timing Diagram                           | 15-0473          | 5-39          |

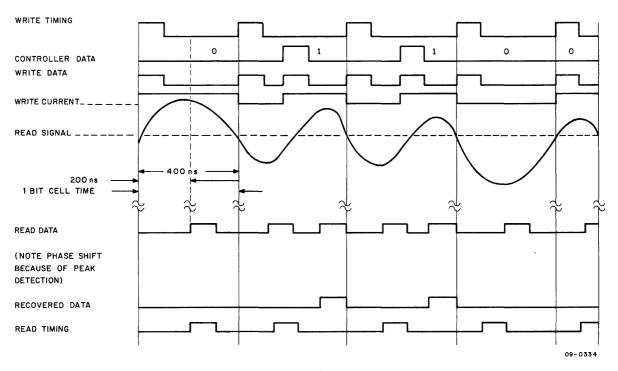

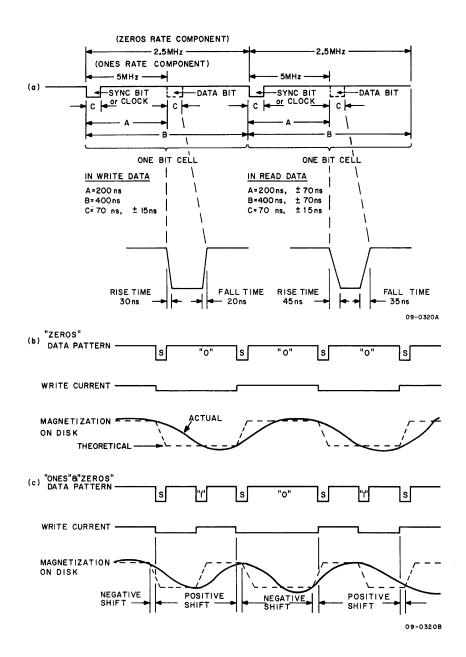

| 5 <b>-29</b> | RP15/02 Read/Write Timing Waveforms                       | 09-0334          | 5-42          |

| Figure No.   | Title                                                                                  | Art No.          | Page          |

|--------------|----------------------------------------------------------------------------------------|------------------|---------------|

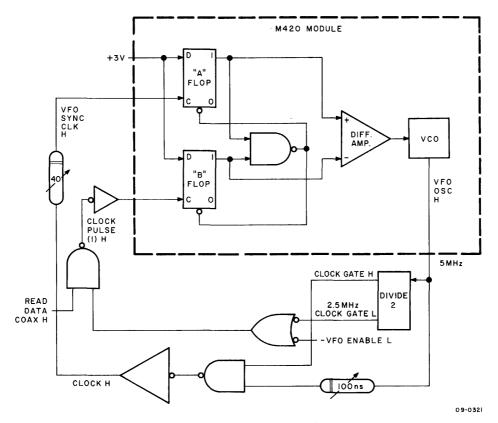

| 5-30         | RP15 VFO Control, Block Diagram                                                        | 09-0321          | 5-43          |

| 5-31         | RP02 Recording Characteristics                                                         | 09-0320          | 5-44          |

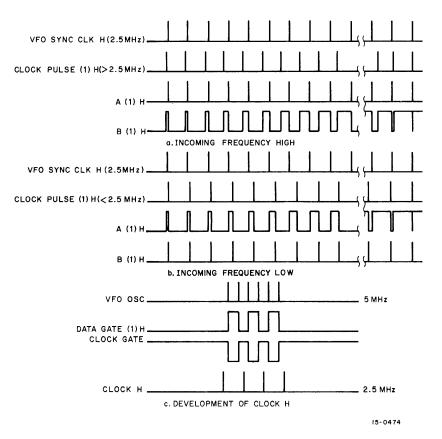

| 5-32         | VFO Timing Waveforms                                                                   | 15 <b>-</b> 0474 | 5-46          |

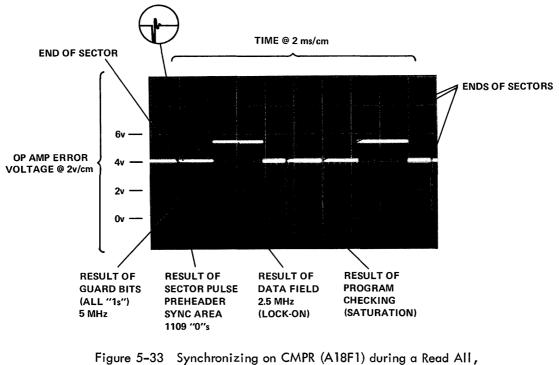

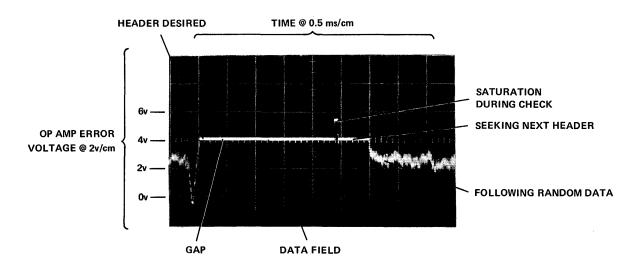

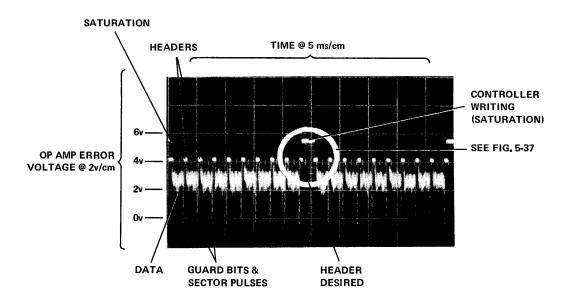

| 5-33         | Synchronizing on CMPR (A18F1) during a<br>Read All, Op Amp Error Voltage Wave-<br>form |                  | 5-48          |

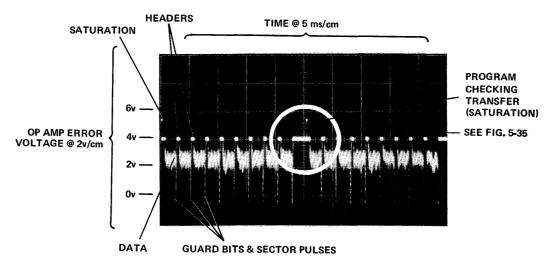

| 5-34         | Synchronizing on CMPR (A18F1) during a<br>Read, Op Amp Error Voltage Waveform          |                  | 5 <b>-49</b>  |

| 5-35         | Synchronizing on CMPR (A18F1) during<br>Read at X10 Expansion(Header Desired)          |                  | 5 <b>–50</b>  |

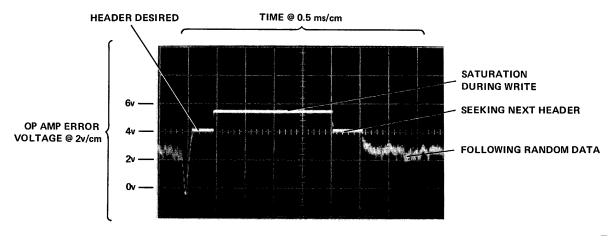

| 5-36         | Synchronizing on CMPR (A18F1) during a<br>Write, Op Amp Error Voltage Waveform         |                  | 5 <b>-51</b>  |

| 5-37         | Synchronizing on CMPR (A18F1) during<br>Write at X10 Expansion (Header Desired)        |                  | 5 <b>-51</b>  |

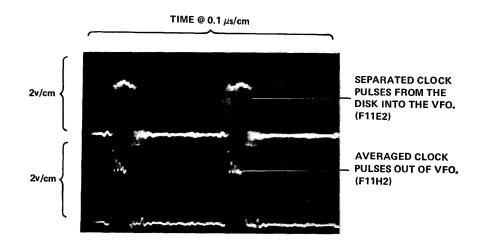

| 5-38         | Clock Pulses In vs Clock Pulses Out,<br>Proper Operation when Synchronizing on<br>CMPR |                  | 5 <b>-52</b>  |

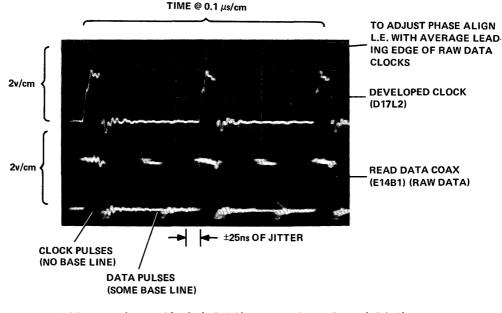

| 5 <b>-39</b> | Developed Clock (D17L2) vs Read Data<br>Coax (E14B1), Phase Adjustment                 |                  | 5-53          |

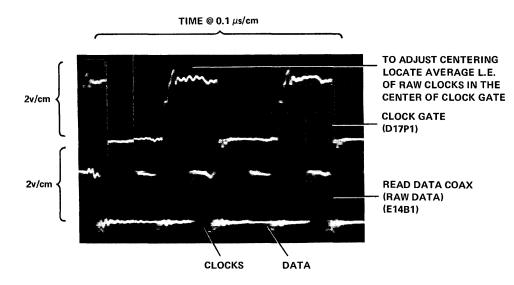

| 5-40         | Clock Gate (D17P1) vs Read Data Coax<br>(E14B1) during Read                            |                  | 5 <b>-</b> 54 |

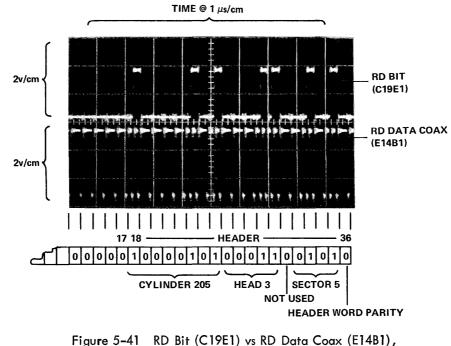

| 5-41         | RD Bit (C19E1)vs RD Data Coax(E14B1),<br>Identifying Header                            |                  | 5-55          |

| 5-42         | Write Format Generator Count                                                           |                  | 5 <b>-56</b>  |

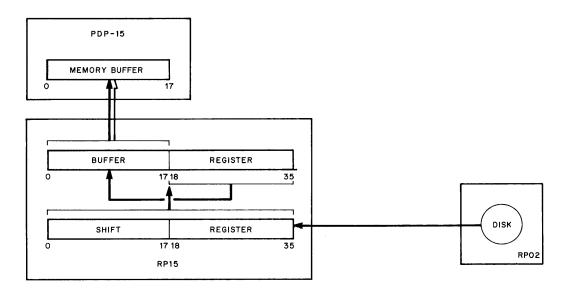

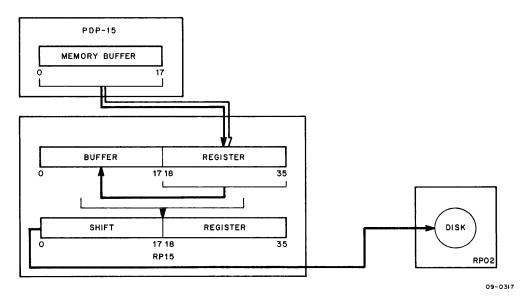

| 5-43         | BR/DCH Data Flow                                                                       | 09-0317          | 5-59          |

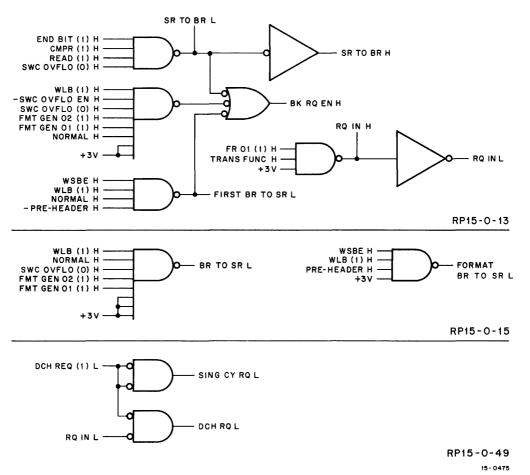

| 5-44         | BR Control Logic, Simplified Diagram                                                   | 15-0475          | 5 <b>-</b> 60 |

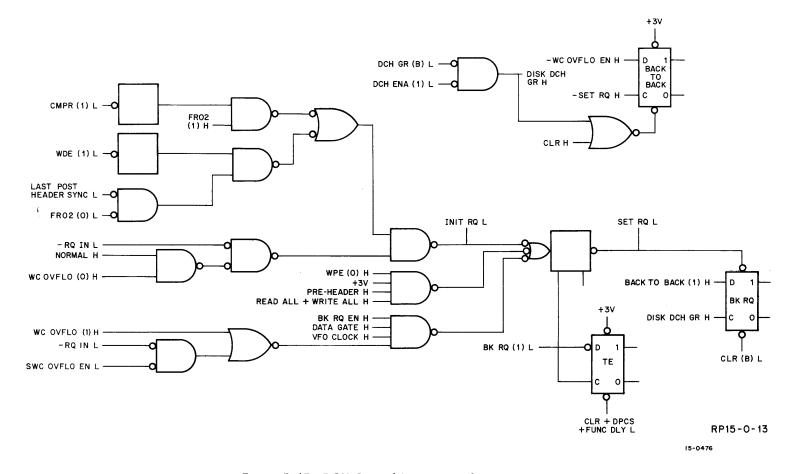

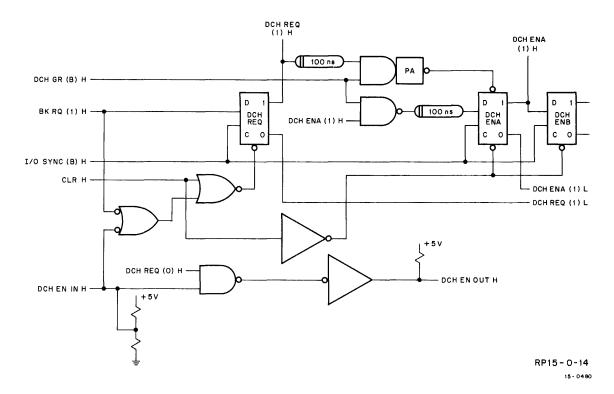

| 5-45         | DCH Control Logic, Simplified Diagram                                                  | 15-0476          | 5-63          |

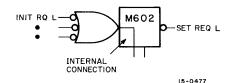

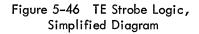

| 5-46         | TE Strobe Logic, Simplified Diagram                                                    | 15-0477          | 5-64          |

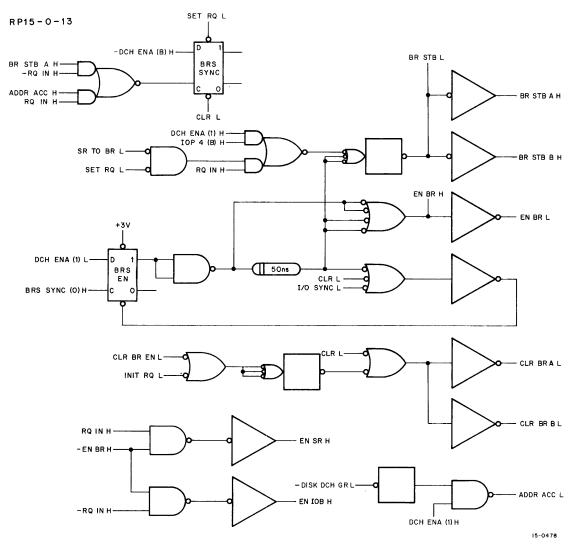

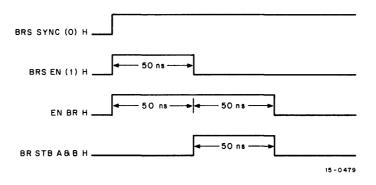

| 5-47         | BR Control Logic, Simplified Diagram                                                   | 15-0478          | 5 <b>-65</b>  |

| 5-48         | BR Control Timing Diagram                                                              | 15-0479          | 5 <b>-66</b>  |

| 5-49         | M104 Block Diagram for DCH                                                             | 15-0480          | 5 <b>-67</b>  |

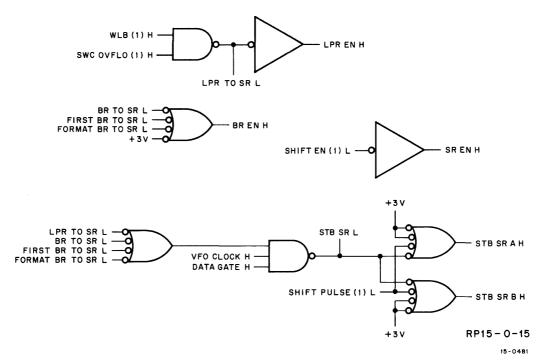

| 5-50         | BR, SR and LPR Enable and Strobe Signals,<br>Simplified Diagram                        | 15-0481          | 5 <b>-6</b> 8 |

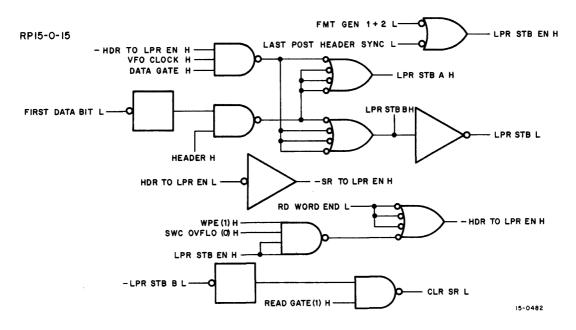

| 5-51         | LPR Control Signals, Simplified Diagram                                                | 15-0482          | 5 <b>-69</b>  |

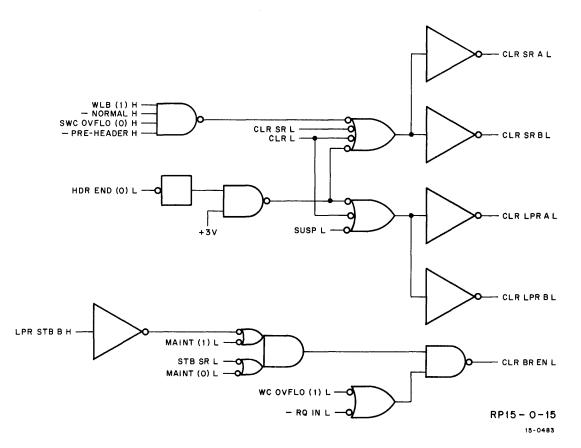

| 5-52'        | BR, LPR and SR Clearing Signals, Simpli-<br>fied Diagram                               | 15-0483          | 5 <b>-</b> 71 |

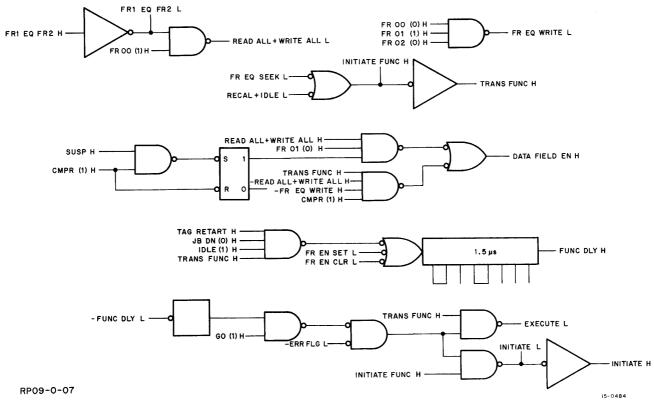

| 5-53         | Read/Write Sector Decoding Logic, Sim–<br>plified Diagram                              | 15-0484          | 5 <b>-73</b>  |

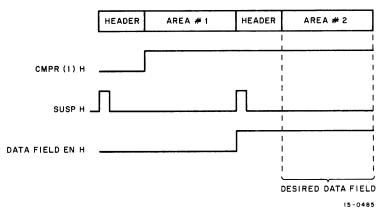

| 5-54         | Read All Function, Desired Data Field                                                  | 15-0485          | 5 <b>-7</b> 4 |

| Figure No.   | Title                                                           | Art No.          | Page          |

|--------------|-----------------------------------------------------------------|------------------|---------------|

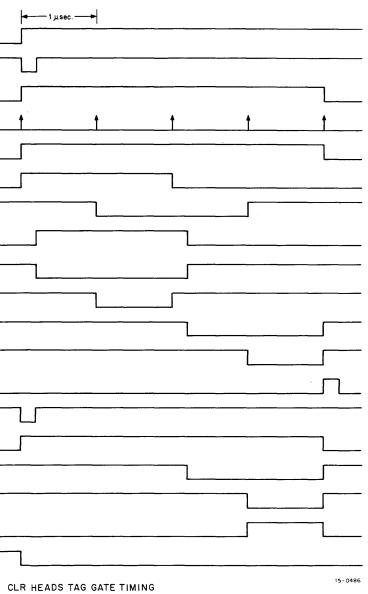

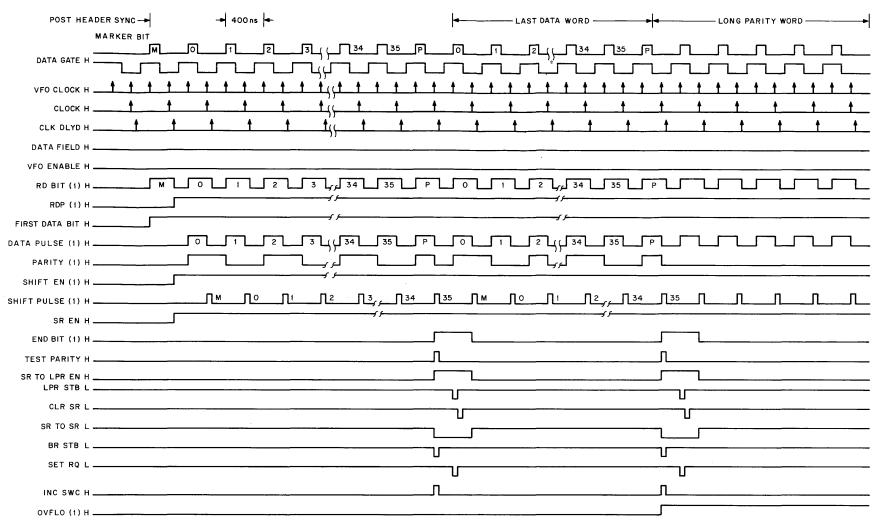

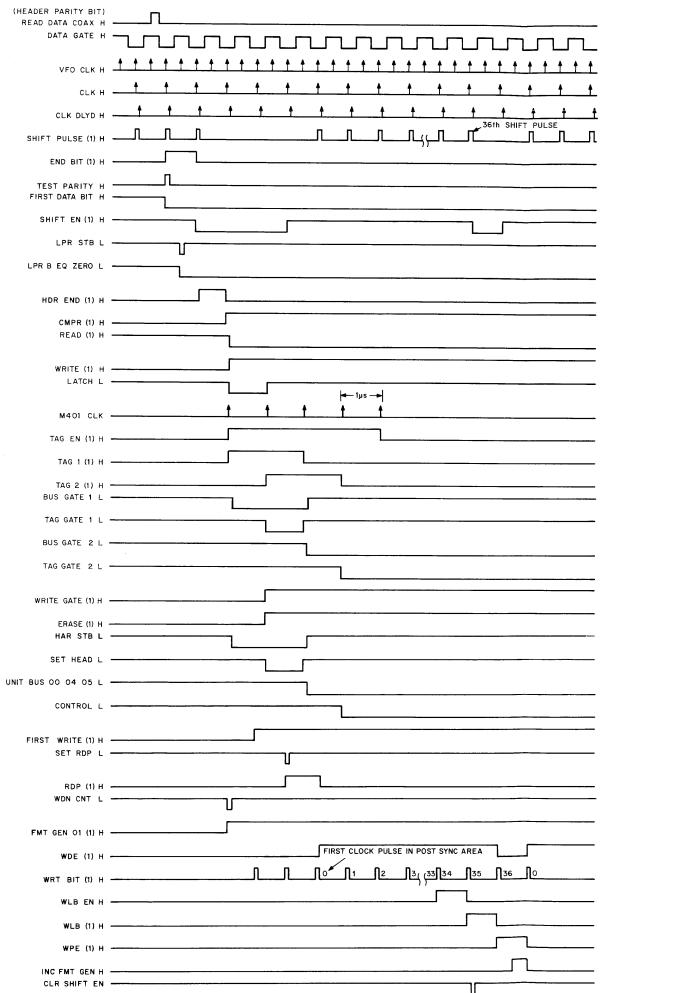

| 5-55         | Timing Diagram Number 1                                         | 15-0486          | 5 <b>-</b> 77 |

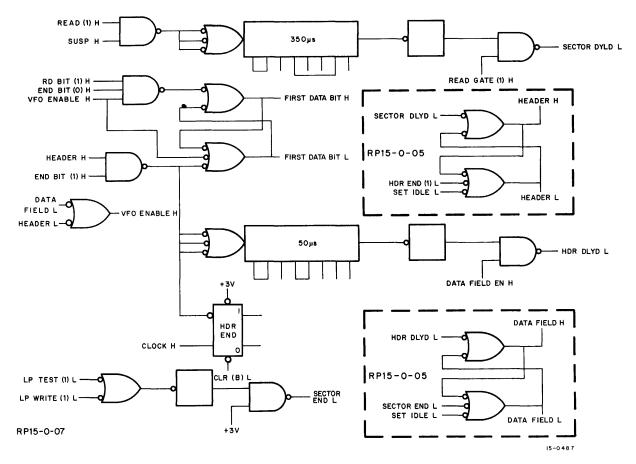

| 5-56         | Header and Data Field Logic, Simplified<br>Diagram              | 15-0487          | 5 <b>-</b> 79 |

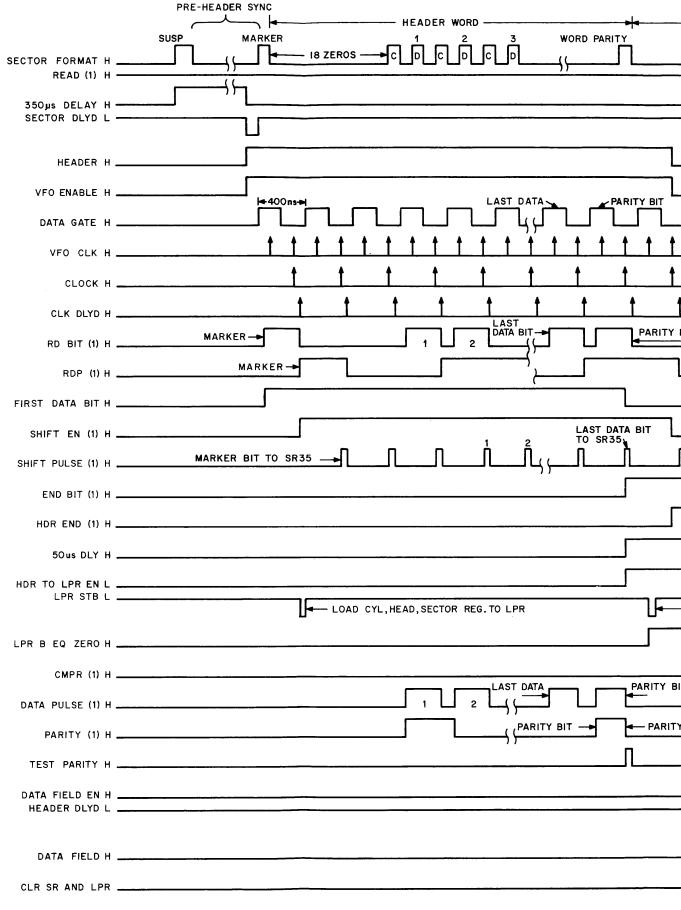

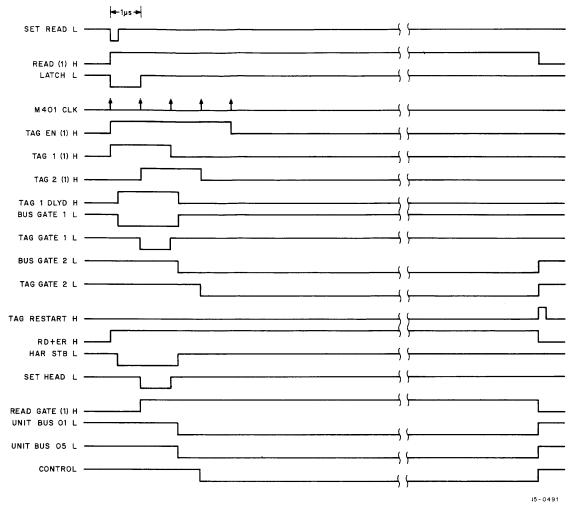

| 5-57         | Timing Diagram Number 2                                         | 15-0488          | 5-81          |

| 5-58         | Timing Diagram Number 3                                         | 15-0489          | 5-83          |

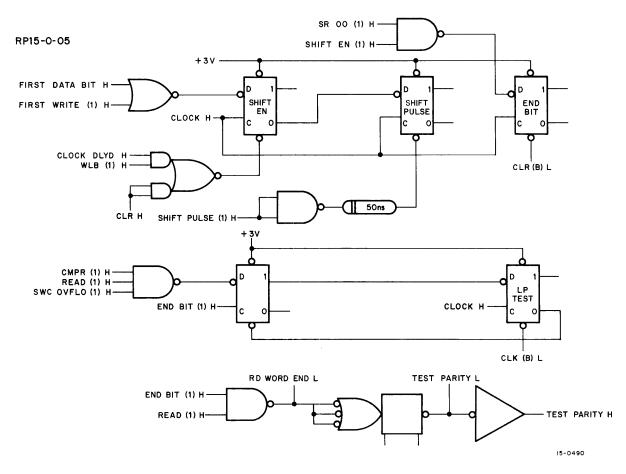

| 5-59         | Word Plus Parity Decoding during Read,<br>Simplified Diagram    | 15-0490          | 5 <b>-</b> 85 |

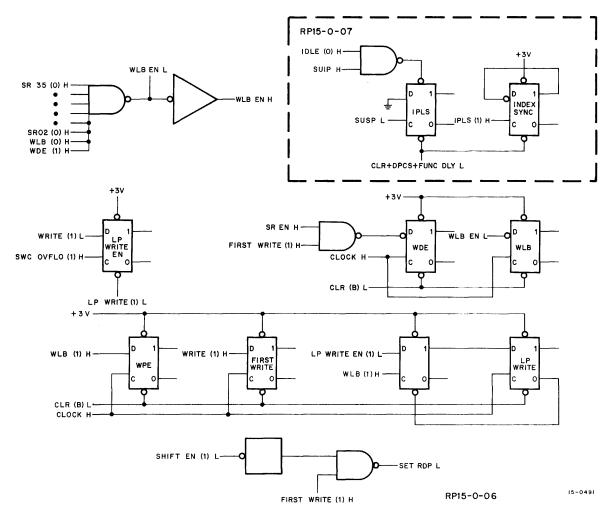

| 5-60         | Word Plus Parity Decoding during Write,<br>Simplified Diagram   | 15-0491          | 5-87          |

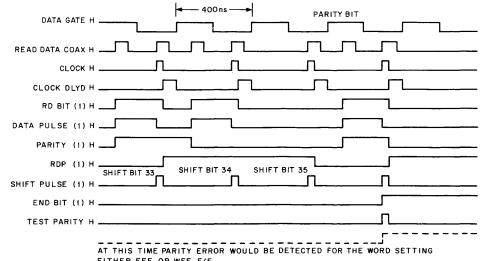

| 5-61         | Timing Diagram Number 4                                         | 15-0491          | 5 <b>89</b>   |

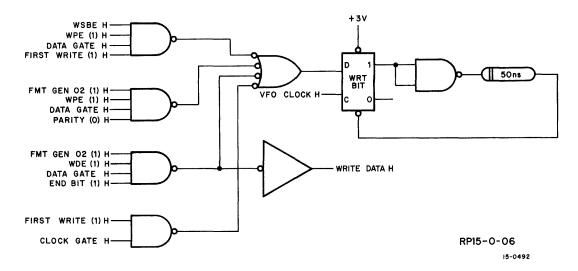

| 5-62         | Clock and Data Bit Decoding during<br>Write, Simplified Diagram | 15-0492          | 5-92          |

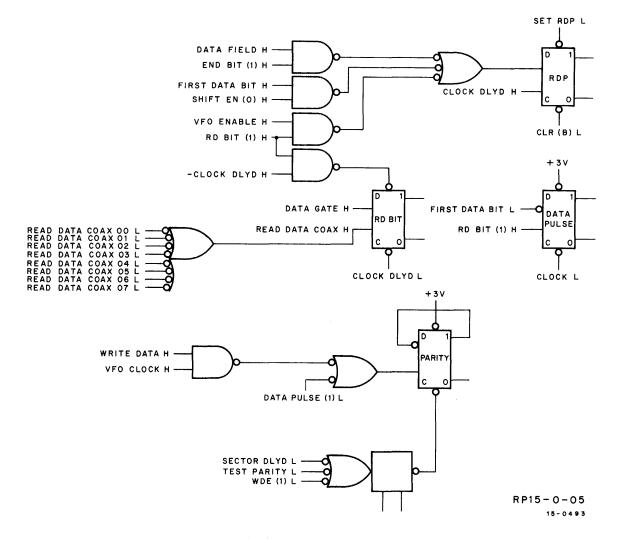

| 5-63         | Clock and Data Bit Decoding in Read,<br>Simplified Diagram      | 15-0493          | 5 <b>-</b> 93 |

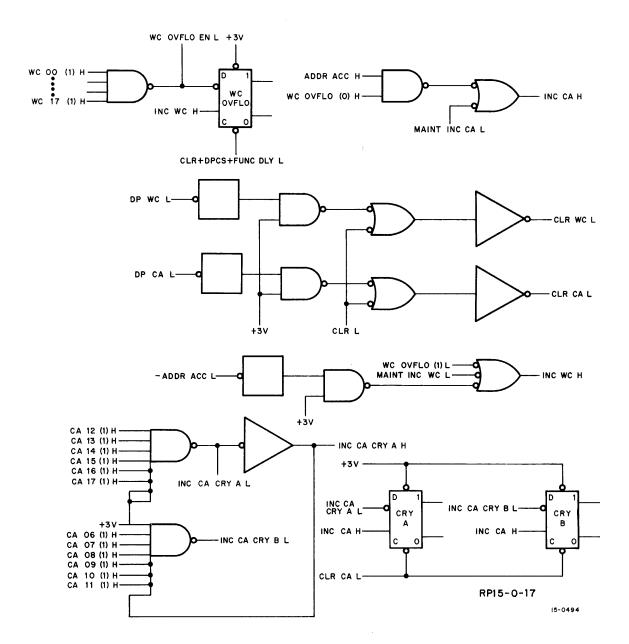

| 5-64         | WC and CA Control, Simplified Diagram                           | 15-0494          | 5-95          |

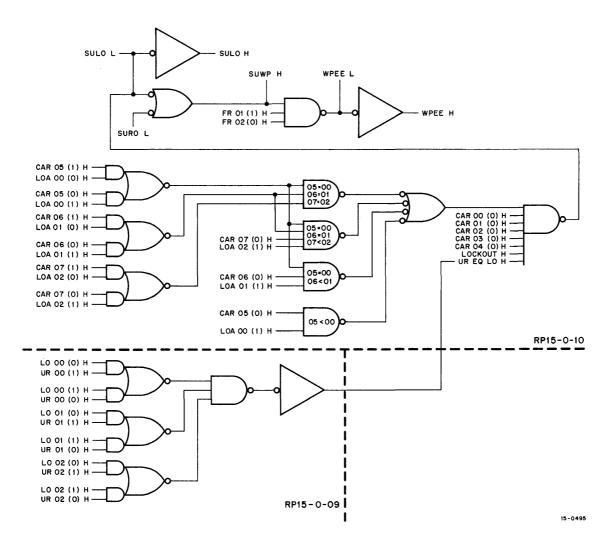

| 5-65         | Write Protection, Simplified Diagram                            | 15 <b>-</b> 0495 | 5-97          |

| 5-66         | Logic Operation of M121 Module                                  | 15-0496          | 5-98          |

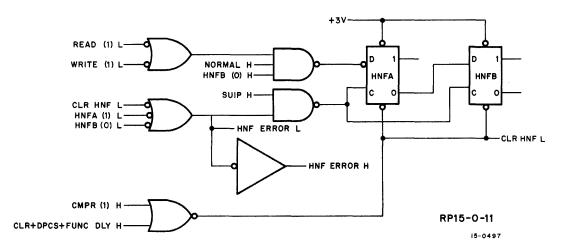

| 5-67         | HNF Status Control, Simplified Diagram                          | 15-0497          | 5-100         |

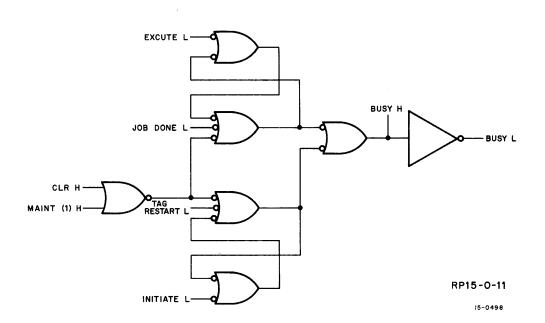

| 5-68         | Busy Status Control, Simplified Diagram                         | 15-0498          | 5-101         |

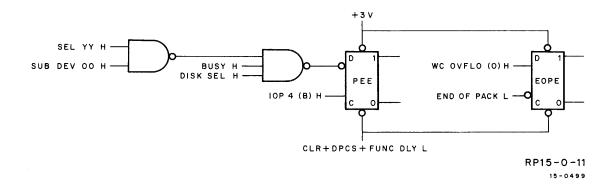

| 5-69         | PEE and EOPE Status Control , Simplified<br>Diagram             | 15-0499          | 5-101         |

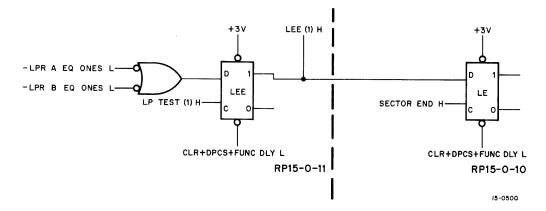

| 5-70         | Longitudinal Error Status Logic, Simpli–<br>fied Diagram        | 15-0500          | 5-102         |

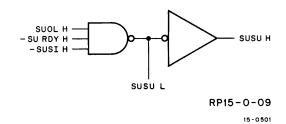

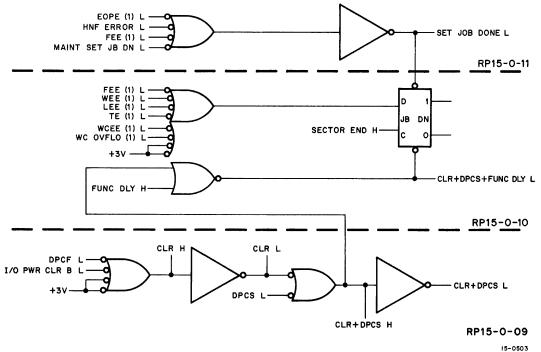

| 5-71         | SUSU Status Control Logic                                       | 15-0501          | 5-103         |

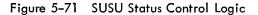

| 5-72         | Status Control Flag Logic, Simplified Di–<br>agram              | 15-0502          | 5-103         |

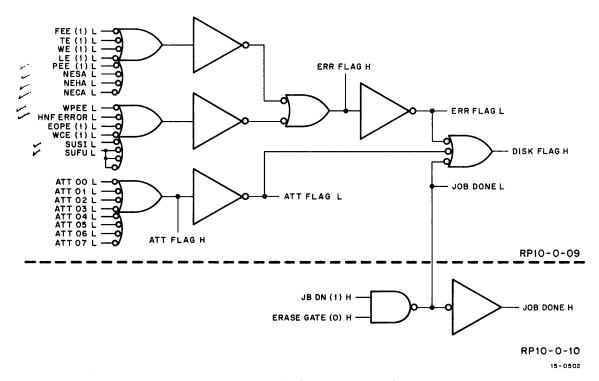

| 5-73         | JB DN Status Control, Simplified Diagram                        | 15-0503          | 5-104         |

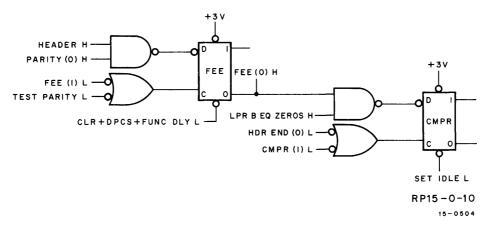

| 5-74         | Format Error/CMPR Status Logic, Simpli–<br>fied Diagram         | 15-0504          | 5-105         |

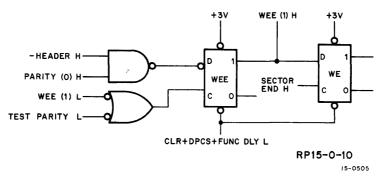

| 5-75         | Word Error Status Logic , Simplified Dia–<br>gram               | 15-0505          | 5-105         |

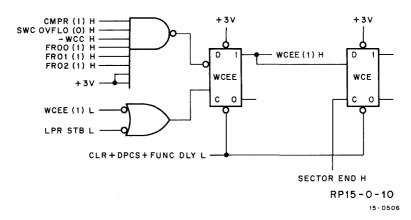

| 5-76         | Write Check Error Status Logic , Simpli–<br>fied Diagram        | 15-0506          | 5-106         |

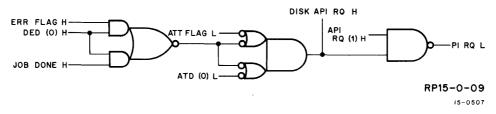

| 5 <b>-77</b> | Priority Interrupt Status Logic , Simplified<br>Diagram         | 15-0507          | 5-106         |

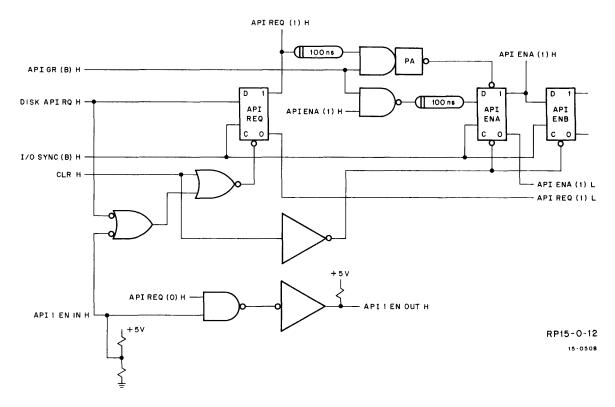

| 5-78         | M104 Block Diagram for API                                      | 15-0508          | 5-107         |

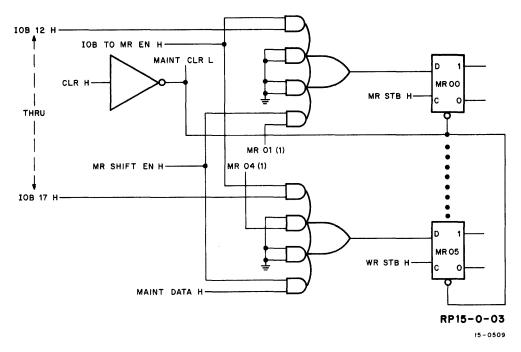

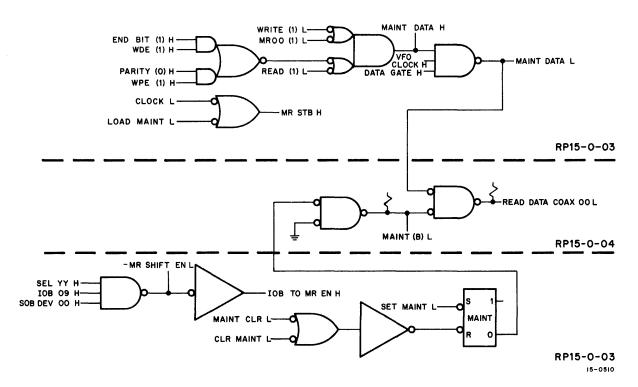

| 5-79         | Maintenance Register, Simplified Diagram                        | 15-0509          | 5-108         |

| 5-80         | Register Control Logic, Simplified Dia–<br>gram                 | 15 <b>-</b> 0510 | 5-108         |

| Figure No. | Title                                    | Art No.         | Page  |

|------------|------------------------------------------|-----------------|-------|

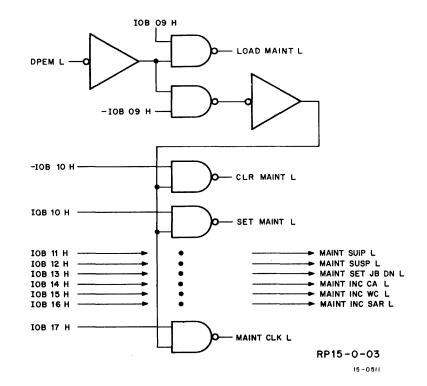

| 5-81       | DPEM Decoding, Simplified Diagram        | 15-0511         | 5-110 |

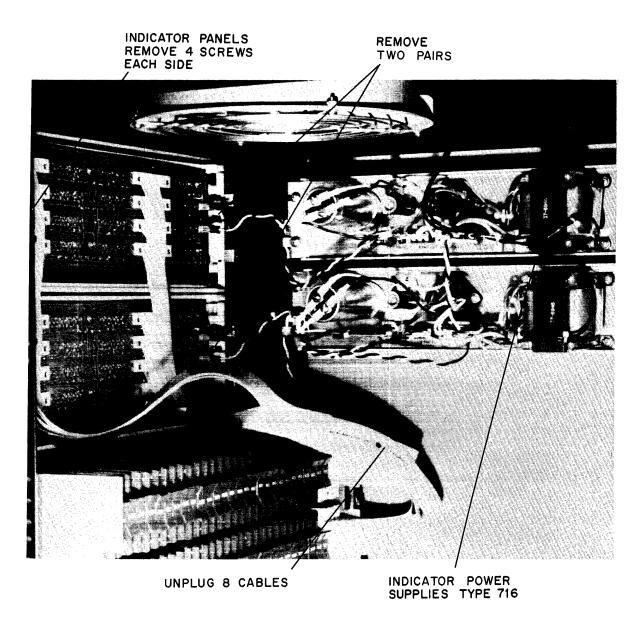

| 6-1        | RP15 Indicator Panels and Power Supplies | 5363-8          | 6-14  |

| 7-1        | Cable Particulars                        | 15-0512         | 7-3   |

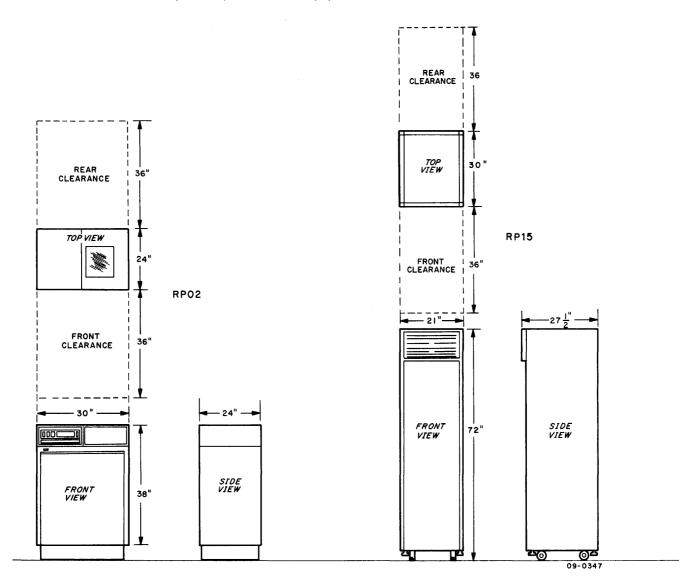

| 8-1        | RP15/02 Overall Dimensions               | 09-0347         | 8-3   |

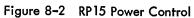

| 8-2        | RP15 Power Control                       | 5363-6          | 8-4   |

| 8–3        | RP15 Logic Power Supply Primary Wiring   | 5363 <b>-</b> 2 | 8-5   |

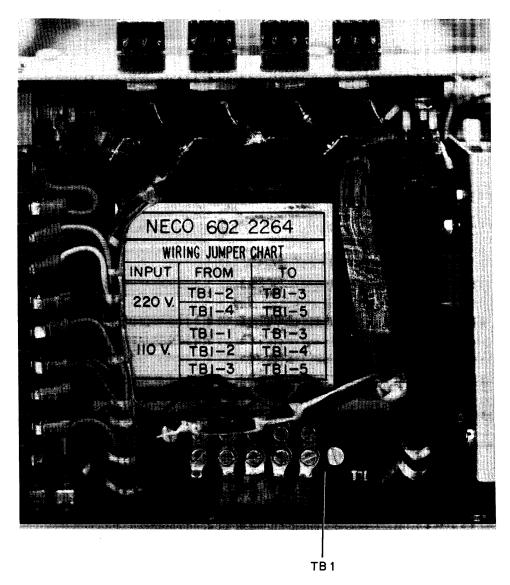

| 8-4        | RP15 Cabinet Bolting Diagram             | 15-0513         | 8-7   |

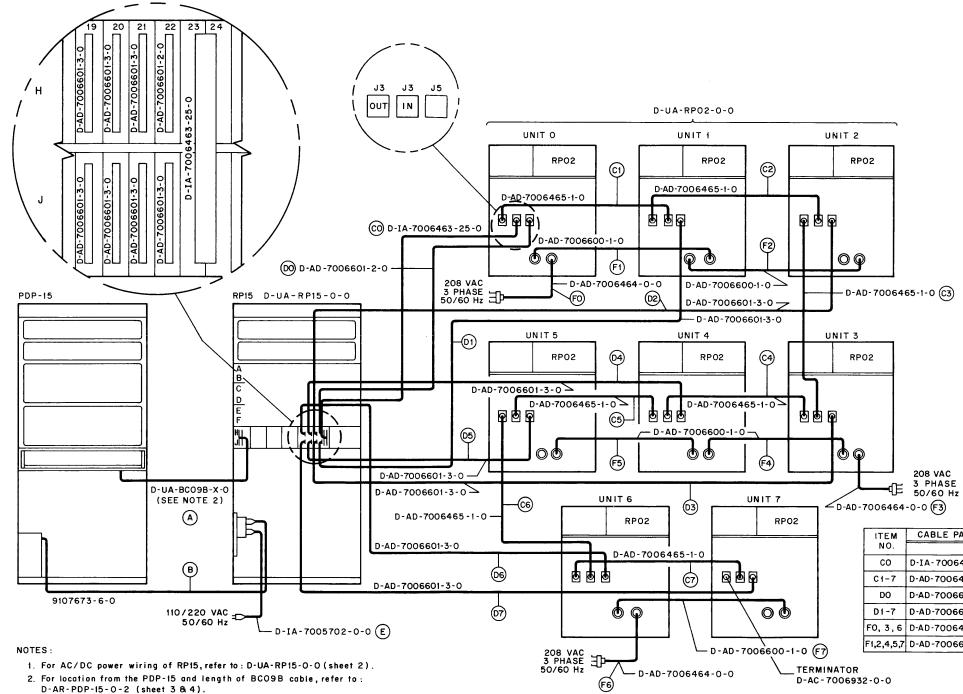

| 8-5        | RP02 Cable Connections to RP15           | 5363-1          | 8-8   |

#### TABLES

| Table No. | Title                                   | Page        |

|-----------|-----------------------------------------|-------------|

| 2-1       | RP15 Indicators                         | 2-1         |

| 2-2       | RP15 Controls                           | 2-6         |

| 2-3       | RP02 Indicators                         | 2-7         |

| 2-4       | RP02 Controls                           | 2-8         |

| 3-1       | Disk Pack IOT Instructions              | 3-5         |

| 3-2       | AC Bit Assignment when Included in DPEM | 3-6         |

| 3-3       | DPLO and DPLZ Truth Tables              | 3-7         |

| 3-4       | Status Register Bit Assignments         | 3-9         |

| 5-1       | <b>RP15</b> Function Arrangement        | 5-15        |

| 6-1       | Test Equipment Required                 | 6-2         |

| 6-2       | RP15 Recommended Spares                 | 6-4         |

| 6-3       | AC Switch Options for Instruction Test  | 6 <b>-6</b> |

| 7-1       | Cable Particulars                       | 7-5         |

| 8-1       | RP15 Checklist                          | 8-2         |

| 8-2       | RP15/RP02 Interface Chart               | 8-8         |

| 8–3       | RP15 I/O Interface Chart                | 8-9         |

|           |                                         |             |

## CHAPTER 1 SYSTEM DESCRIPTION

#### 1.1 GENERAL

This chapter describes the RP15 System in general terms and presents some characteristics of memory storage systems. An overall description is provided of the RP02 Disk Pack System as it interfaces with the PDP-15 Computer System. The remainder of the chapter defines certain controller parameters as they relate to overall system performance.

#### 1.2 RP15 CONTROL

The RP15 Disk Pack Controller interfaces from one to eight RP02 Disk Pack Drives to the PDP-15 Computer (see Figure 1-1). Each RP02, when equipped with an RP02P Disk Pack, provides the PDP-15 Central Processor with an additional  $10.24 \times 10^6$  18-bit words of memory storage at an average data acquisition time of 50 ms (positional) and 12.5 ms (rotational). Data are transferred through the PDP-15 single-cycle data channel provided by the I/O bus. Transfers are double buffered to produce a transfer rate of 14.8 µs for every two words and a latency time of 14.8 µs.

#### **1.3 DISK SYSTEM CHARACTERISTICS**

Modern computer systems use many methods to store information; each method has inherent advantages and disadvantages. Flip-flops and delay schemes are used for short-term data storage; magnetic devices are used for relatively long-term storage of data and instruction because once a magnetic state is established in the medium, it will remain, even after power is removed, until the state is modified or erased.

Core memories provide relatively small storage capacity (4K to 32K words) in minimal space, and offer the advantage of almost instantaneous retrieval. Because of this fact, core memories are used to store data in various computation stages, as well as with instructions of the main operating program.

However, rotating memories, such as magnetic tapes, provide greater capacity (150K to 8M words), but retrieval involves a search phase in a serial fashion by one fixed scanning device. For this reason, tapes are used for the storage of data that requires less frequent retrieval.

Figure 1-1 RP15 Disk Pack Controller

#### 1.3.1 Disk vs Drum

The larger rotating memories (drum and disk) provide massive storage capability but retain the disadvantage of search; access times are orders of magnitude better than for tape. As with tapes, these memories require a synchronizing or clocking scheme that serves as a constant indication of instantaneous scan speed, so that synchronization with the operating system may be achieved.

Rotating memories serve a "scratch pad" or "swapping" function in the overall scheme of the computer; and provide short-term storage of routines, subroutines, or blocks of data in some intermediate state of computation. These memories are also used for long-term storage of tabular functions, catalogues, dictionaries, and other reference material. In time-shared systems, rotating memories serve as temporary repositories of partially completed operations, thereby freeing the'other storage mediums to service a higher priority request.

The drum is usually a non-removable device in which a set of fixed flying heads write the data in a particular format across the outside surface of the cylinder. It has particular application in vibrational environments or in installations where atmospheric conditions are not stringently controlled. The drum has a constant diameter and presents a fixed frequency response characteristic to the data being recorded. The response of the disk is directly proportional to its diameter, and the bit density of the innermost track is much greater than for the outermost track. This disadvantage can be overcome easily and is a small consideration compared to the advantage of increased data capacity.

#### 1.3.2 Disk Pack Effects on the Drive

The use of a removable media device, such as a disk pack, places some constraints on the design of the drive. Basically, the head design is affected because a movable head arrangement must be used so that the heads may be retracted while removing the pack. This requirement dictates that a set of single heads be held in vertical alignment by a common head tower which, in turn, must be actuated hydraulically, pneumatically, or by an electric positioning motor. Positioning means that extra logic must be provided for positioning comparators and servo control of head motion during these operations. The disadvantage of additional machinery and logic is minimal, however, when compared to the unlimited storage capacity provided by being able to remove and store many packs per drive.

#### 1.4 RP02 SYSTEM CHARACTERISTICS

#### 1.4.1 RPO2P Disk Pack

The RP02P Disk Pack, shown in Figure 1–2, is the recording medium used with the RP15 Controller, and it is designed for mounting on an RP02 Disk Pack Drive. The RP02P is comprised of 11 aluminum

Figure 1-2 RP02P Disk Pack

disks coated with magnetic oxide and mounted 1/2-in. apart on a common hub. Information is recorded on the 20 inner surfaces.

The bottom disk is not used for recording and is notched to produce timing pulses for synchronization with the controller (see Figure 1-3). The disk contains 20 evenly spaced notches and a 21st notch called the index. The drive is equipped with a reluctance type pickup that senses these notches and sends a signal to the controller where the pulses are frequency divided to produce 10 sector indicators. An additional circuit then separates the index pulse. Note that the sectors are numbered octally.

#### 1.4.2 RP02 Disk Pack Drive

The RP02 Disk Pack Drive is the mechanism controlled by the RP15 Controller (see Figure 1-4). It comprises two major subassemblies:

- a. The spindle driving mechanism and

- b. The head positioning system.

The spindle driving mechanism is made up of an ac motor, mounted below the baseplate that transmits a rotation of 2400 rpm to the disk pack by driving a conical spindle through a drive pulley and belt loop. The spindle secures the pack with a locking shaft within the spindle and washers below the spindle pulley. A mechanical lock is actuated by raising the cover. A pack-on switch disables spindle-drive motor power until a pack is installed.

Figure 1-3 RP02P Disk Pack Sector and Index Pulse Generation

The head positioning system consists of a linear positioning motor that moves a T-bar tower along a horizontal carriage, either toward or away from the center of drive motor rotation. When the T-bar is fully retracted, it is sensed by a microswitch and braking power is applied. The disk pack may then be removed. The T-bar is used to mount 20 back-to-back head assemblies that are unloaded by camming action when the linear motor is fully retracted. A detenting mechanism stops the head assembly over any cylinder position.

The drive provides a means to monitor head position, drive speed, and rotational position. A cylinder transducer, made up of a 145 kHz excited sensing transformer and a toothed rack that rides with the head assembly and passes the sensing transformer while heads are in motion, produces a modulated signal that is an indication of head position. This signal is fed to an up/down counter in the RP02 logic. Drive speed and rotational position are monitored by a dc reluctance pickup that senses slots in the bottom disk of the pack (see Figure 1-3). This signal is sent back to the controller, to indicate disk position, and to a flip-flop rate sampler within the drive logic to generate an up-to-speed indication to the controller whenever the drive reaches 70 percent of rated speed.

Dynamic braking of the drive motor is accomplished by replacing ac power with dc power for approximately 12 seconds, whenever the STOP switch is depressed. Dynamic braking also occurs whenever the cabinet cover is lifted.

Figure 1-4 RP02 Disk Pack Drive

The read/write heads contain two center-tapped coils (one for the read/write gap and one for the erase pole). Diode switching is used to place ground on the center tap of the selected head. The heads are

gimbal-mounted in the horizontal plane and leaf-spring loaded in the vertical plane; when the disk is up to speed, the heads fly on a cushion of air over the surface of the disk.

There are four basic operations performed by the drive under controller command. They are:

Seek Write Read Recalibrate

The Seek operation is initiated by the receipt of a cylinder address from the controller. The drive logic compares this address with its present address and determines the direction in which the heads must move. Head motion is then accomplished and monitored by a difference count within the drive and is detented in position when the count reaches zero. The time required to locate the next cylinder address is limited to 100 ms by a time delay actuated at the start of the Seek. Failure to re-detent during this time results in a SEEK INCOMPLETE to the controller. When the new address is reached, and after a 3.0-ms damping delay, the drive indicates to the controller its readiness to Read or Write.

When Write is commanded, the controller supplies data to the write-selected head as a double-frequency non-return-to-zero pulse train, together with clock pulses for synchronization. The data and clock information are recorded as reversals in magnetic flux on a side-trimmed 0.006-in. wide track.

When Read is commanded, the same head is read-selected to sense the previously recorded flux changes, producing current reversals in the head windings. This signal, which contains both data and clock pulses, is sent to the controller for processing.

When Recalibrate is commanded, the heads are moved by a forced forward seek that sends the carriage to the forward stop. When the carriage reaches the stop, it executes a normal reverse seek to home position (cylinder 000). The drive signals the controller 3 ms after detent that it is ready for instructions.

#### NOTE

The sequence just described occurs as a "first seek" whenever the drive START switch is depressed and after the motor has reached 70 percent of rated speed.

There are several safety circuits in the RP02 drive. These circuits protect data from being destroyed in the event of component failure. With the exception of ac/dc voltage failure, all conditions will issue a FILE UNSAFE indication to the controller; will deselect heads and terminate Read, Write, or Erase operations; will drop ready; and will light FILE UNSAFE on the panel. The FILE UNSAFE indication can be reset by switching START/STOP to the STOP position. Loss of primary power will remove all dc voltages from the machine. This automatically prevents Write current. If any dc logic voltage is

lost, heads are deselected to prevent writing. If an unsafe condition is present when a drive is turned on, an indication of FILE UNSAFE is given immediately. If the heads are extended when primary ac power fails, STOP is depressed, or the disk compartment door is opened before depressing STOP; the heads will automatically retract.

#### 1.5 PDP-15 COMPUTER SYSTEM CHARACTERISTICS

The PDP-15 Computer System consists of three asynchronous subsystems:

- a. Central Processor (CPU)

- b. Memory

- c. I/O Processor (I/O PU).

The PDP-15 is an 18-bit word length machine with a memory cycle time of 800 ns. Optional features include core memory expansion out to 131,072 words and a memory-protect system.

The CPU conducts bidirectional communication with both the memory and the I/O PU. It performs all required arithmetic and logical operations while controlling and executing stored programs. The core memory is the primary storage area for instructions and data. It is organized into pages and banks, with two pages comprising one bank. A page is capable of storing 4096 18-bit words. The I/O PU provides the timing, control, and data lines between either the memory or the CPU, and the peripheral devices. In addition, it can contain a real-time clock and an automatic priority interrupt system. The I/O PU handles all peripheral data transfers. These transfers are accomplished in three possible I/O modes as follows:

- a. Single-cycle block (up to a million words/second)

- b. Multicycle block (250,000 words/second input and 188,000 words/second output)

- c. Program-controlled (single word to/from CP Accumulator).

The three subsystems operate together under console control. The console provides manual initiation of programs, monitoring of CPU and I/O PU registers, and manual examination and modification of memory contents.

The RP15 interfaces with memory through a single-cycle data channel break. The minimum PDP-15 configuration required for use with the RP15 Disk Pack Controller is the PDP-15/10 augmented by 8K of memory, and a PC15 High-Speed Paper Tape Reader/Punch. This is the first level system. The con-figuration is expandable due to pre-wired facilities that allow additional memory and peripherals to be plugged in at any time.

#### 1.6 SINGLE-CYCLE INTERFACE AND I/O BUS

The RP15 transfers data to and from the PDP-15 via the single-cycle data channel. During a singlecycle transfer, the RP15 keeps track of its own word count (WC Register) and specifies the absolute address from or to which it wishes to transfer (CA Register).

The PDP-15 Permits two modes of single-cycle operation termed "Normal" and "Burst". The Burst mode is used when the device can transfer a word every microsecond.

In the RP15, all transfers are made in the Burst (or back-to-back) mode unless an odd number of words is to be transferred, in which case the last word is transferred in the Normal mode. Such transfers are made possible by a double-buffering scheme that allows assembly of two 18-bit words within the con-troller before they are transferred. This is done to achieve an economy of demand on the I/O bus that allows other devices access to the bus during RP15 assembly time (see Figure 1-5).

Figure 1–5 Latency vs Transfer Time in Normal and Back–To–Back Modes

Because of the rotational speed of the RP02, the latency time for double-buffered transfers is 14.8  $\mu$ s, i.e., in this mode the RP15 must have access to the I/O bus every 14.8  $\mu$ s, as long as it is transferring data on a two-word-per-break basis. If access is not granted in that time, a timing error will be raised.

As shown in Figure 1–5a, the first two words use 4  $\mu$ s of I/O bus time (2  $\mu$ s fixed synchronization + 1  $\mu$ s/word). This leaves 10.8  $\mu$ s of bus time during which other devices may have access to the bus (provided, of course, their latency times are compatible). Figure 1–5b shows the transfer characteristics

for a single word transfer (last word in an odd number of words) in which the latency time is 7.4  $\mu$ s. Note that what is termed the Normal mode of operation is the uncommon mode of operation for the RP15. If single buffering had been used in the RP15, all words would have been transferred on this one-word-at-a-time basis, and only 4.4  $\mu$ s of bus time would have been available for interlacing devices. In addition, 2  $\mu$ s of fixed synchronization time would have been wasted on every second word transferred.

#### **1.7 REFERENCE DOCUMENTS**

The following documents contain information which supplements that contained in this manual:

PDP-15 Interface Manual (DEC-15-HOAB-D) PDP-15 Systems Reference Manual (DEC-15-BRZA-D) PDP-15 Installation Manual (DEC-15-H2AB-D) PDP-15 Operator's Guide (DEC-15-H2CA-D) PDP-15 Module Manual (DEC-15-H2EA-D)

### CHAPTER 2 CONTROLS AND OPERATIONS

#### 2.1 GENERAL

This chapter contains information required to operate the RP15 Controller. Controls and indicators are also identified.

#### 2.2 CONTROLS AND INDICATORS

The RP15 indicators are located on the top front of the unit and are defined in Table 2-1. The controls are located on a logic panel inside the front door (refer to Table 2-2). The RP02 indicators and controls are located on its console panel and are explained in Tables 2-3 and 2-4, respectively. The controls and indicators for both units are shown in Figure 2-1. Power controls and indicators for the RP15 are found on the Type 841B Power Control located inside the RP15 cabinet. These are not included in Tables 2-1 through 2-4, but are shown in Chapter 8.

| Index No. | Name                       | Function                                                                                                                                                      |

|-----------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1         | BUFFER REGISTER            | Thirty–six indicators that light on binary 1s to show<br>the contents of the Buffer Register's two PDP–15<br>words.                                           |

| 2         | CONTROL STATUS comprising: | Nine indicators that show controller status as fol-<br>lows:                                                                                                  |

|           | DED                        | One lamp that lights when the DONE and<br>ERROR flags are disabled from the Program In-<br>terrupt (PI) and the Automatic Priority Interrupt<br>(API) system. |

|           | ATD                        | One lamp that lights when the ATTENTION flag has been disabled from the PI and API sys-<br>tem.                                                               |

|           | GO                         | One lamp that lights when bit 08 of Status Reg-<br>ister A is set, enabling the Function Register to<br>be executed.                                          |

Table 2–1 RP15 Indicators

| Index No.   | Name                                | Function                                                                                                                                                                              |

|-------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2<br>(cont) | DISK FLG                            | One lamp that lights when any error, attention or job done flags have been raised.                                                                                                    |

|             | JOB DONE                            | One lamp that lights when a function is com-<br>plete. (Exceptions are Idle, Recalibrate, and<br>Seek.)                                                                               |

|             | ATT FLG                             | One lamp that lights on an attention flag which<br>is raised whenever any unit attention is raised<br>(OR of UA00–07).                                                                |

|             | ERR FLG                             | One lamp that lights when any error condition occurs (OR of all errors).                                                                                                              |

|             | BK RQ                               | One lamp that lights when a request is made to access memory.                                                                                                                         |

|             | BUSY                                | One lamp that lights when the controller is bus (other than Idle).                                                                                                                    |

| 3           | WORD COUNT Register comprising:     | Sixteen indicators that show the following:                                                                                                                                           |

|             | WC OVFLO                            | One lamp that lights when a word count over-<br>flow has occurred, i.e., when the desired num<br>ber of word transfers are complete.                                                  |

|             | WC 03-17                            | Fifteen lamps that show the 2's complement of<br>the number of 18–bit words yet to be transferred<br>from or to memory.                                                               |

| 4           | FUNCTION Register<br>FR00–02        | Three indicators that light on binary 1s in bits 03,<br>04, and 05 of Status Register A to show a 3-bit<br>octal number corresponding to one of eight func-<br>tions to be performed. |

|             |                                     | 0 = Idle<br>1 = Read<br>2 = Write<br>3 = Recalibrate<br>4 = Seek<br>5 = Read All<br>6 = Write All<br>7 = Write Check                                                                  |

| 5           | UNIT SELECT Register<br>UR00–02     | Three indicators that light on binary 1s in bits 00,<br>01, and 02 of Status Register A to show a 3-bit<br>octal number corresponding to the unit (one of<br>eight) selected.         |

|             |                                     | 0 = Unit 0<br>1 = Unit 1, etc.                                                                                                                                                        |

| 6           | UNIT STATUS Register<br>comprising: | Five indicators that show the status of the unit se-<br>lected as follows:                                                                                                            |

#### Table 2–1 (Cont) RP15 Indicators

| Table | 2-1   | (Cont) |

|-------|-------|--------|

| RP15  | India | cators |

| Index No.   | Name                                                   | Function                                                                                                                                                                                                                 |

|-------------|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6<br>(cont) | SUOL                                                   | One lamp that lights when the selected unit has power and is placed on line by a switch on that unit console.                                                                                                            |

|             | SU RDY                                                 | One lamp that lights when the selected unit is ready for data transfer.                                                                                                                                                  |

|             | SUSU                                                   | One lamp that lights when a seek is underway on the unit selected.                                                                                                                                                       |

|             | SURO                                                   | One lamp that lights when the selected unit is<br>in READ ONLY mode as selected by a switch on<br>that unit console.                                                                                                     |

|             | SULO                                                   | One lamp that lights when the selected unit is<br>locked out, i.e., LOCKOUT switch in LOCK–<br>OUT position, the Unit Select register is equal<br>to the Lock–out register, and the CAR < LOA.                           |

| 7           | SWITCH MODE Register<br>comprising:                    | Three indicators that show the status of the control switches on the RP15 logic as follows:                                                                                                                              |

|             | FMT                                                    | One lamp that lights when the FORMAT/<br>NORMAL switch is in the FORMAT position.                                                                                                                                        |

|             | NORM                                                   | One lamp which lights when the FORMAT/<br>NORMAL switch is in the NORMAL position.                                                                                                                                       |

|             | LOCKOUT                                                | One lamp that lights when the LOCKOUT switch is in the LOCKOUT position indicating that the LO and LOA switches are enabled.                                                                                             |

| 8           | CURRENT ADDRESS Reg-<br>ister<br>CA01-17               | Seventeen indicators that show bits 1–17 of the current memory address.                                                                                                                                                  |

| 9           | CYLINDER ADDRESS<br>Register<br>CAR00–07               | Eight indicators that light on binary 1s showing the contents of the Cylinder Address register in the RP15.                                                                                                              |

| 10          | HEAD ADDRESS Register<br>(Surface Address)<br>HAR00–04 | Five indicators that light on binary 1s to show the current head address.                                                                                                                                                |

| 11          | SECTOR ADDRESS Register<br>SAR00–03                    | Four indicators that light on binary 1s to show the current sector address.                                                                                                                                              |

| 12          | LOCKOUT Register<br>comprising:                        | Six indicators that light on binary 1s as follows:                                                                                                                                                                       |

|             | LO00-02                                                | Three Lockout Unit Lamps that indicate the<br>unit number (0–7) on which writing cannot take<br>place in or below the cylinder address indicated<br>by the Lockout Address Indicators if the LOCK–<br>OUT switch is set. |

|             | LOA00-02                                               | Three Lockout Address Lamps that indicate the cylinder address (in octal) in or below which                                                                                                                              |

#### Table 2–1 (Cont) RP15 Indicators

| Index No.    | Name                                                                  | Function                                                                                                                                                                                 |

|--------------|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12<br>(cont) |                                                                       | writing cannot take place on that unit displayed<br>by the Lockout Unit Indicators if the LOCKOUT<br>switch is set .                                                                     |

| 13           | SELECTED UNIT CYL <del>-</del><br>INDER ADDRESS Register<br>SUCA00-07 | Eight indicators that light on binary 1s from the<br>Cylinder Address Register in the selected RP02,<br>showing the address in that unit at which the heads<br>are presently positioned. |

| 14           | CONTROL STATE<br>Register<br>comprising:                              | Seven indicators that show the current state of the controller as follows:                                                                                                               |

|              | READ                                                                  | One lamp that lights when the control is in Read state.                                                                                                                                  |

|              | WRITE                                                                 | One lamp that lights when the control is in Write state.                                                                                                                                 |

|              | SEEK                                                                  | One lamp that lights when the control begins a Seek.                                                                                                                                     |

|              | CLR HEAD                                                              | One lamp that lights when the control is in<br>Clear Head state, i.e., head select register is<br>cleared in RP02 Drive.                                                                 |

|              | INC HEAD                                                              | One lamp that lights when the control is in<br>Increment Head state, i.e., when the current<br>head is being disabled and the next head se-<br>lected in the RP02 Drive.                 |

|              | RECAL                                                                 | One lamp that lights when the control begins a<br>Recalibrate.                                                                                                                           |

|              | IDLE                                                                  | One lamp that lights when the control is in Idle<br>(non-busy state).                                                                                                                    |

| 15           | UNIT ATTENTION<br>Register<br>UA00–07                                 | Eight indicators that light on binary 1s showing the<br>unit (0–7) from which ATTENTION has been raised<br>as a result of a successfully completed SEEK com-<br>mand.                    |

| 16           | SECTOR WORD COUNT<br>Register<br>comprising:                          | Eight indicator lamps that indicate the following:                                                                                                                                       |

|              | SWC OVFLO                                                             | One lamp that indicates that the sector word<br>counter has overflowed, signaling that the re-<br>quired number of 36-bit words have been trans-<br>ferred to or from the disk.          |

|              | SWC00-06                                                              | Seven lamps that show the number of 36–bit<br>words read or written in a single sector.                                                                                                  |

| 17           | FORMAT GENERATOR<br>Register<br>FMT GEN00-08                          | Nine indicators that light on binary 1s showing the state of the format generator.                                                                                                       |

| Table | 2-1   | (Cont) |

|-------|-------|--------|

| RP15  | India | cators |

| Index No.    | Name                                | Function                                                                                                                                                                                                       |

|--------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17<br>(cont) |                                     | This register controls formatting during WRITE, WRITE ALL, and FORMAT instructions.                                                                                                                            |

| 18           | MAINTENANCE Register<br>comprising: | Seven indicators that show the following:                                                                                                                                                                      |

|              | MNT                                 | One indicator that lights when the controller is in the maintenance mode.                                                                                                                                      |

|              | MR00-05                             | Six indicators that show the binary contents of the Maintenance Register.                                                                                                                                      |

| 19           | ERROR STATUS<br>comprising:         | Fourteen indicators that show that an error has oc-<br>curred as follows:                                                                                                                                      |

|              | FE                                  | One lamp that indicates a Format Error has oc-<br>curred due to a parity error in a header word.                                                                                                               |

|              | WE                                  | One lamp that indicates a Word Error has oc-<br>curred due to a parity error in a data word.                                                                                                                   |

|              | LE                                  | One lamp that indicates a Longitudinal Error has<br>occurred due to a parity error in a bit position<br>of a single sector.                                                                                    |

|              | WCE                                 | One lamp that indicates a Write Check Error has<br>occurred due to no comparison between two 18–<br>bit words read from memory and a paired data<br>word read from the disk.                                   |

|              | TE                                  | One lamp that indicates a Timing Error has oc-<br>curred due to a missed transfer of a data word to<br>or from processor memory.                                                                               |

|              | PE                                  | One lamp that indicates a Programming Error has occurred due to an illegal series of RP15 instruc-<br>tions.                                                                                                   |

|              | HNF                                 | One lamp that indicates a Header Not Found<br>error has occurred due to the traversing of a<br>complete revolution of the disk while searching<br>unsuccessfully for a header word (unique sector<br>address). |

|              | WPE                                 | One lamp that indicates a Write Protect Error<br>has occurred due to a violation of either of two<br>Write Protect functions.                                                                                  |

|              | NEC                                 | One lamp that indicates a Non-Existent Cylin-<br>der address has been commanded. This bit is<br>present as long as an illegal cylinder address re-<br>sides in the CAR.                                        |

|              | NEH                                 | One lamp that indicates a Non-Existent Head<br>(surface) address has been commanded. This bit<br>is present as long as an illegal head address re-<br>sides in the HAR.                                        |

| Table | 2-1  | (Cont) |

|-------|------|--------|

| RP15  | Indi | cators |

| Index No.    | Name                                        | Function                                                                                                                                                                                                                |

|--------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19<br>(cont) | NES                                         | One lamp that indicates a Non-Existent Sector<br>address has been commanded. This bit is present<br>as long as an illegal sector address resides in the<br>SAR.                                                         |

|              | EOP                                         | One lamp that indicates the End Of Pack point has been reached before the word count is com-<br>plete.                                                                                                                  |

|              | SUSI                                        | One lamp that indicates a Selected Unit Seek<br>Incomplete error has occurred due to 100 ms<br>passing while unsuccessfully seeking a particular<br>cylinder address.                                                   |

|              | SUFU                                        | One lamp that indicates a Selected Unit File<br>Unsafe signal has been received from the select–<br>ed RP02.                                                                                                            |

| 20           | SHIFT REGISTER<br>SR00-35                   | Thirty–six indicators that light on binary 1's showing<br>the contents of the Shift Register in the RP15. This<br>register assembles serial data from the disk or<br>serializes the data being transferred to the disk. |

| 21           | LONGITUDINAL PARITY<br>REGISTER<br>LPR00-35 | Thirty–six indicators that light on binary 1s showing<br>the contents of the LPR in the RP15. This register<br>accumulates bit position odd parity for each sector.                                                     |

Table 2–2 RP15 Controls

| Index No. | Name                    | Function                                                                                                                                                                                                                                  |

|-----------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22        | FORMAT/NORMAL<br>Switch | One two-position rocker switch that, in FORMAT<br>position, enables the controller for formatting op-<br>erations and, in NORMAL position, enables the<br>controller for normal operations.                                               |

| 23        | FORMAT/NORMAL<br>Lamp   | One lamp that lights Clear when the FORMAT/<br>NORMAL switch is in FORMAT position.                                                                                                                                                       |

| 24        | LOCKOUT Switch          | One two-position rocker switch that, in LOCKOUT<br>position, enables the controller to write protect<br>disk addresses as selected by the LO and LOA tog-<br>gle switches. The unmarked position is normal for<br>"no lockout" condition. |

| 25        | LOCKOUT Lamp            | One lamp that lights Red when the LOCKOUT switch is in LOCKOUT position.                                                                                                                                                                  |