Digital Equipment Corporation Maynard, Massachusetts

## digital

### **PDP-15 Systems**

# Interface Manual

## **PDP-15** INTERFACE MANUAL

DIGITAL EQUIPMENT CORPORATION • MAYNARD, MASSACHUSETTS

#### Copyright © 1969, 1970 by Digital Equipment Corporation

•

The material in this manual is for information purposes and is subject to change without notice.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

| DEC       | PDP          |

|-----------|--------------|

| FLIP CHIP | FOCAL        |

| DIGITAL   | COMPUTER LAB |

#### CONTENTS

| CHAPTER       | R 1 PDP-15 LOGIC SYMBOLOGY             |  |

|---------------|----------------------------------------|--|

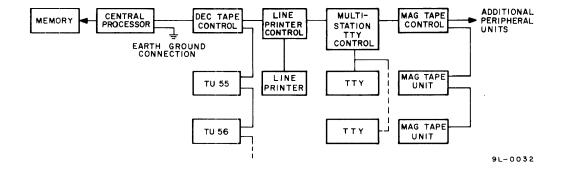

| 1.1           | PDP-15 System Organization             |  |

| 1.2           | Logic Symbology                        |  |

| 1.2.1         | Logic Gates                            |  |

| 1.2.2         | Flip-Flops                             |  |

| 1.2.3         | Variable Clock                         |  |

| 1.2.4         | Pulse Amplifier                        |  |

| 1.2.5         | Miscellaneous Logic Symbology          |  |

| 1.3           | Designators                            |  |

| 1.3.1         | Logic Designators                      |  |

| 1.3.2         | Signal Designators                     |  |

| 1,3.3         | Signal Name Changes                    |  |

| 1.3.4         | The Dash                               |  |

| 1.4           | Line Connections                       |  |

|               |                                        |  |

| CHAPTER       | R 2 PDP-15 INTERFACE MODULES           |  |

| 2.1           | Measurement Definitions                |  |

| 2.2           | Loading                                |  |

| 2.3           | Module Descriptions                    |  |

| 2.3.1         | M104 Multiplexer Module                |  |

| 2.3.2         | M194 Multiplexer Module                |  |

| 2.3.3         | M500 Negative Receiver Module          |  |

| 2.3.4         | M510 Positive Receiver Module          |  |

| 2.3.5         | M622 Positive Driver Module            |  |

| 2.3.6         | M632 Negative Driver Module            |  |

| 2.3.7         | M909 Terminator Card                   |  |

| CHAPTER       | R 3 INTRODUCTION TO PDP-15 INTERFACING |  |

| 3.1           | General Principles                     |  |

| 3.2           | Data Information                       |  |

| 3.3           | Command and Status Information         |  |

| 3.4           | Interrupts                             |  |

| 3.5           | The PDP-15 I/O Bus System              |  |

| 3.6           | Summary of the PDP-15 I/O Processor    |  |

| 3.6.1         | The CPU I/O Controller                 |  |

| 3.6.2         | The Memory I/O Controller              |  |

|               | R 4 PDP-15 INTERFACING                 |  |

| 4.1           | Interfacing to the CPU I/O Controller  |  |

| 4.1.1         | A CPU Interface with API               |  |

| <b>97.1.1</b> |                                        |  |

ü

#### **CONTENTS** (Cont)

|               |                                            | n en | . 1 | Page         |

|---------------|--------------------------------------------|------------------------------------------|-----|--------------|

| 4.1.2         | The Logic                                  |                                          |     | 4-3          |

| 4.2           | Interfacing to the Memory I/O Controller   |                                          | 4   | 4-9          |

| 4.2.1         | The Multi-Cycle Data Channel Peripheral    |                                          | 4   | 4-9          |

| 4.2.2         | Increment Memory                           | •<br>•                                   |     | 4-15         |

| 4.2.3         | The Single-Cycle Data Channel Device       |                                          | 4   | 4-21         |

| 4.3           | System Priority Structures                 | an an an an an                           | 4   | 4-27         |

| 4.4           | Summary of I/O Bus Functions               |                                          | 4   | 4-28         |

| CHAPTER       | R 5 WIRING PRACTICES                       |                                          |     |              |

| 5.1           | Wiring Rules                               |                                          |     | 5-1          |

| 5.1.1         | Single Line Waveform Degradations          | ante<br>A Maria de Calendaria            |     | 5-1<br>5-1   |

| 5.1.2         | Termination Technique                      |                                          |     | 5-1<br>5-1   |

| 5.1.3         | Crosstalk in Parallel Logic Lines          |                                          |     | 5-1<br>5-2   |

| 5.2           | Properties of #30 AWG Wire                 |                                          |     | 5-2<br>5-3   |

| 5.2<br>5.3    | The Ground System                          |                                          |     | 5-3          |

| 5.3.1         | DC Ground System                           |                                          |     | 5-3<br>5-3   |

| 5.3.2         | AC Ground System                           |                                          | -   | 5-3<br>5-4   |

| 5.4           | Cables in Digital Systems                  |                                          |     | 5-4<br>5-5   |

| 5.4.1         | The PDP-15 Positive I/O Bus Cable          | an an an                                 |     | 5-5<br>5-5   |

| 5.5           | General Wire Information                   | n an | -   | 5-5<br>5-6   |

| 5.5.1         | Wire Types                                 | an anna sue en la companya de            | -   | 5-6          |

| 5.5.2         | Wire Types<br>Wire Insulation              |                                          |     | 5-0<br>5-6   |

| 5.5.3         | Wire Insulation Stripping                  |                                          |     | 5-0<br>5-7   |

| 5.5.4         | Wire Data                                  |                                          | -   | 5-8          |

| 5.6           | Solderless Connections                     |                                          |     | 5-0<br>5-11  |

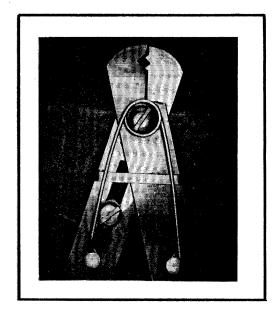

| 5.6.1         | Crimped Connections                        |                                          |     | 5-11<br>5-11 |

| 5.6.2         | Wire Wrap                                  |                                          |     | 5-13         |

| 5.7           | Soldered Connections                       |                                          |     | 5-1 <i>6</i> |

| 5.7.1         | Soldering Irons                            |                                          |     | 5-16         |

| 5.7.2         | Solder                                     |                                          |     | 5-16         |

| 5.7.3         | Soldered Connection Requirements           |                                          |     | 5-16         |

| 5.7. <b>5</b> | Use of Stranded Wire                       |                                          |     | 5-17         |

| 5.7.4         | Use of Stranded Wile                       |                                          | -   | .)-17        |

| CHAPTER       | R 6 THE I/O BUS SYSTEM                     |                                          |     |              |

| 6.1           | The DW15 Bus Adapter                       |                                          | (   | 5-1          |

| 6.2           | PDP-15 I/O Bus Cables and Cable Assemblies |                                          | ŧ   | 5-1          |

| 6.2.1         | The BC09 Cable Characteristics             |                                          | e   | 5-2          |

| 6.2.2         | BC09A Assembly                             |                                          | e   | 5-2          |

| 6.2.3         | BC09B Cable Assembly                       |                                          | ť   | 6-4          |

| 6.2.4         | Cable Lengths                              |                                          | e   | 6-4          |

| 6.3           | Adding Peripherals to the I/O Bus          |                                          | ť   | 5-6          |

iv

#### **CONTENTS** (Cont)

| 6.3.1      | The Electrical Characteristics of the Bus        | 6-6         |

|------------|--------------------------------------------------|-------------|

| 6.3.2      | Device Select Codes                              | 6-6         |

| 6.3.3      | Addresses                                        | 6-6         |

| 6.3.4      | Timing Constraints                               | 6-6         |

| 6.3.5      | System Latency and Priorities                    | 6-6         |

| 6.3.6      | Cable Runs and Terminations                      | 6-6         |

| 6.4        | Designing PDP-15 Devices to Operate on the PDP-9 | 6-10        |

| APPENDIX A | DOCUMENTATION                                    |             |

| A.1        | Drawing Index List                               | <b>A-</b> 1 |

| A.2        | Drawing Categories                               | A-1         |

|            |                                                  |             |

#### **ILLUSTRATIONS**

| 1-1  | NAND Gate                                          | 1-2 |

|------|----------------------------------------------------|-----|

| 1-2  | NAND Gate                                          | 1-2 |

| 1-3  | NOR Gate                                           | 1-2 |

| 1-4  | NOR Gate                                           | 1-2 |

| 1-5  | Inverter                                           | 1-2 |

| 1-6  | Inverter                                           | 1-2 |

| 1-7  | Basic Logic Relationships                          | 1-2 |

| 1-8  | D Flip-Flop – Edge Triggered                       | 1-2 |

| 1-9  | J-K Master-Slave Flip-Flop                         | 1-3 |

| 1-10 | R-S Flip-Flop                                      | 1-3 |

| 1-11 | Variable Clock                                     | 1-3 |

| 1-12 | Pulse Amplifier                                    | 1-3 |

| 1-13 | I/O Bus Receiver                                   | 1-3 |

| 1-14 | Binary to Decimal Decoder                          | 1-3 |

| 1-15 | Delays                                             | 1-4 |

| 1-16 | Connectors                                         | 1-4 |

| 1-17 | NAND Gate                                          | 1-4 |

| 1-18 | Read Flip-Flop                                     | 1-4 |

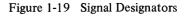

| 1-19 | Signal Designators                                 | 1-4 |

| 1-20 | Signal Name Changes                                | 1-5 |

| 1-21 | The Dash                                           | 1-5 |

| 2-1  | Voltage Spectrum of Negative Logic Systems         | 2-1 |

| 2-2  | Voltage Spectrum of TTL Logic                      | 2-1 |

| 2-3  | Voltage Spectrum for Positive PDP-15 I/O Bus Logic | 2-1 |

| 2-4  | M104 Equivalent Circuit                            | 2-3 |

| 2-5  | M104 Timing                                        | 2-4 |

| 2-6  | M104 Circuit Schematic                             | 2-5 |

Page

#### ILLUSTRATIONS (Cont)

|       |                                                       | Page  |

|-------|-------------------------------------------------------|-------|

| 2-7   | M194 Equivalent Circuit                               | 2-6   |

| 2-8   | M500 Receiver Module                                  | 2-7   |

| 2-9   | M500 Schematic                                        | 2-7   |

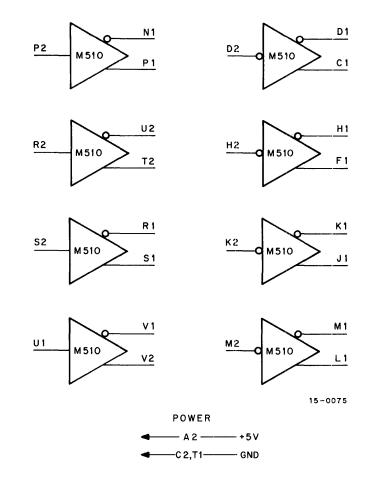

| 2-10  | M510 Receiver Module                                  | 2-8   |

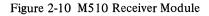

| 2-11  | M510 Schematic                                        | 2-8   |

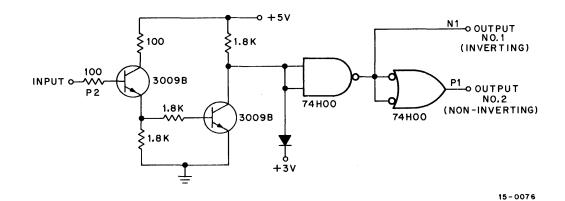

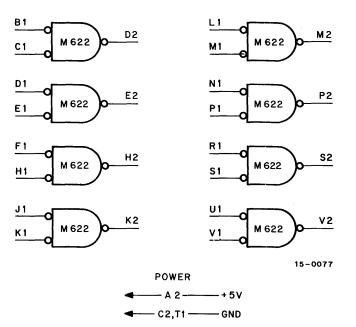

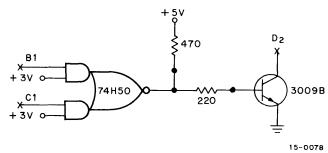

| 2-12  | M622 Driver                                           | 2-9   |

| 2-13  | M622 Schematic                                        | 2-9   |

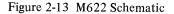

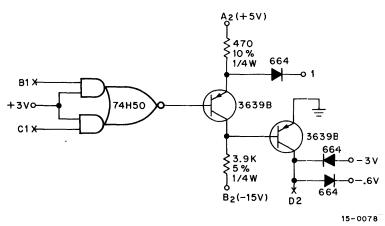

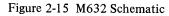

| 2-14  | M632 Driver Module                                    | 2-10  |

| 2-15  | M632 Schematic                                        | 2-10  |

| 2-16  | M909 Terminator Card                                  | 2-11  |

| 3-1   | I/O Bus Schemes                                       | 3-2   |

| 4-1   | IOT Instruction Format                                | 4-1   |

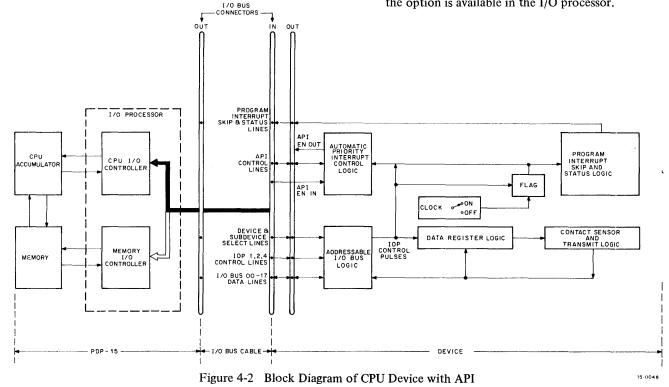

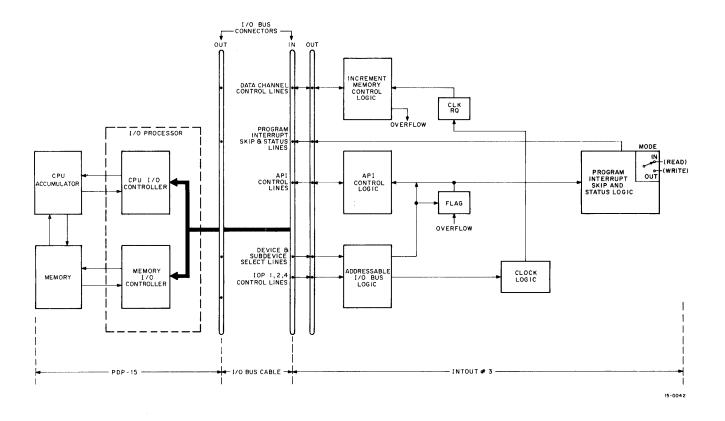

| 4-2   | Block Diagram of CPU Device with API                  | 4-2   |

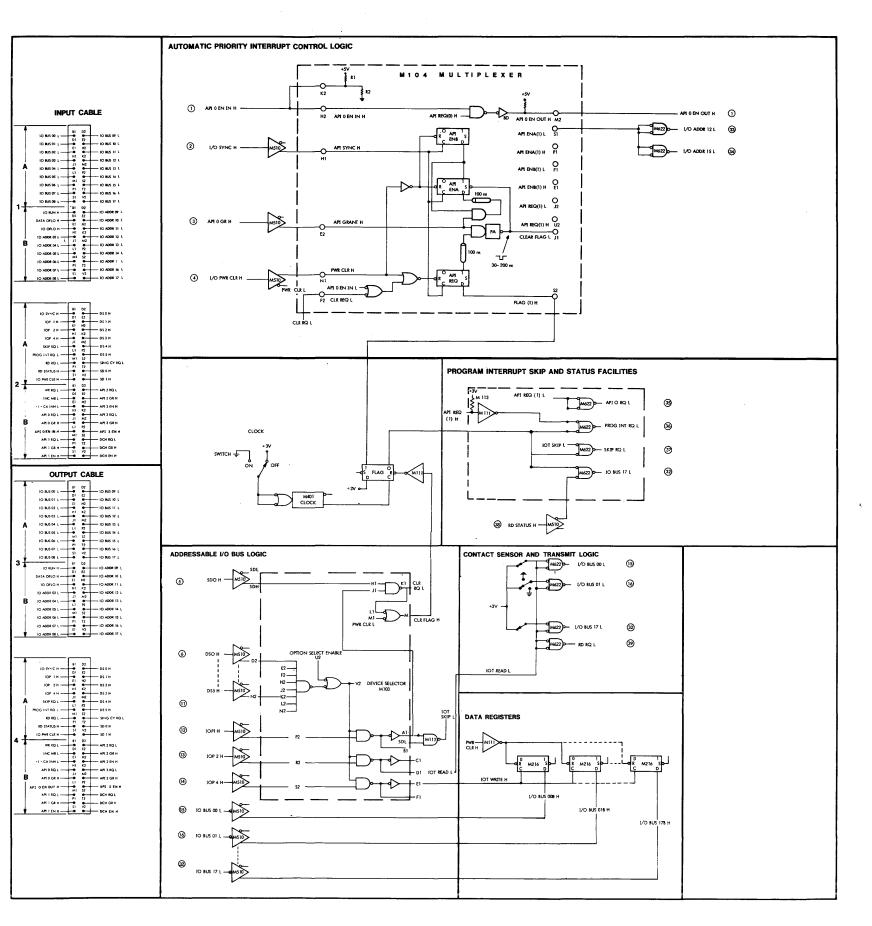

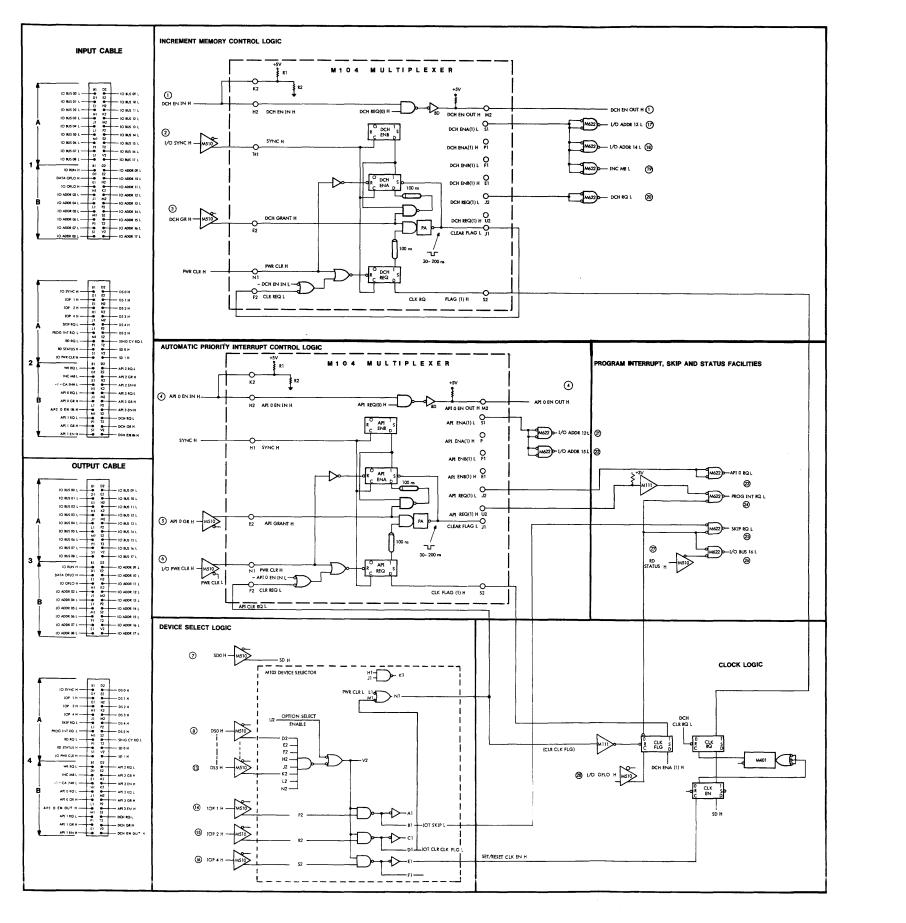

| 4-3   | Logic Diagram of the CPU Device with API              | 4-7   |

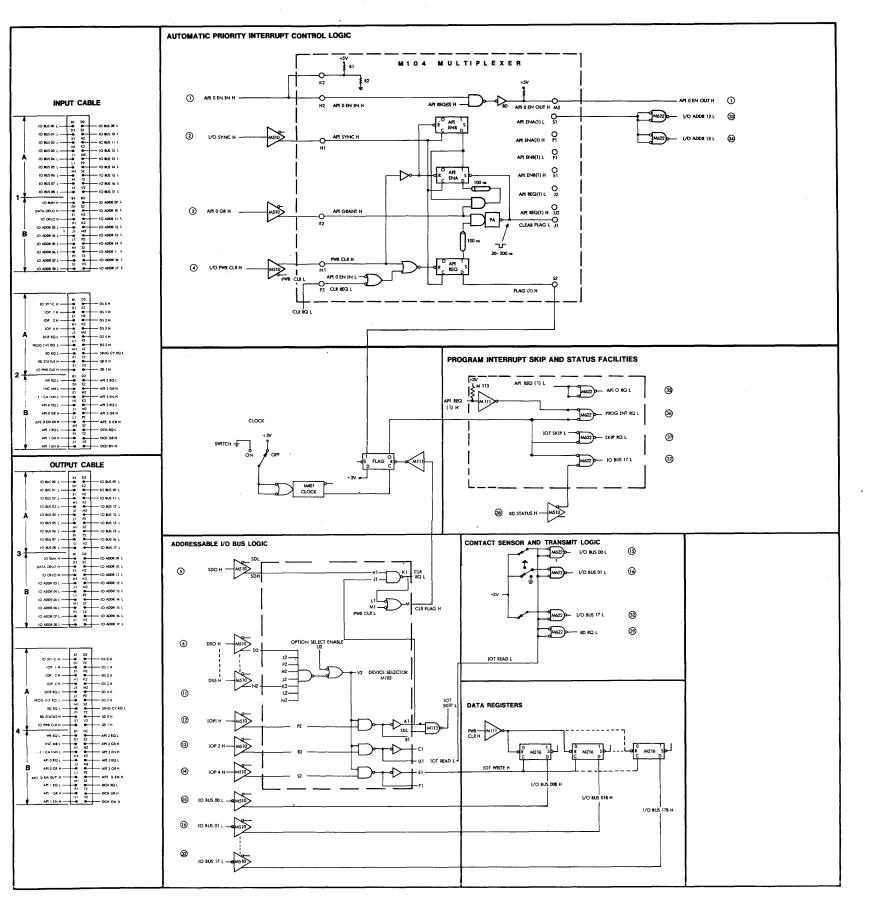

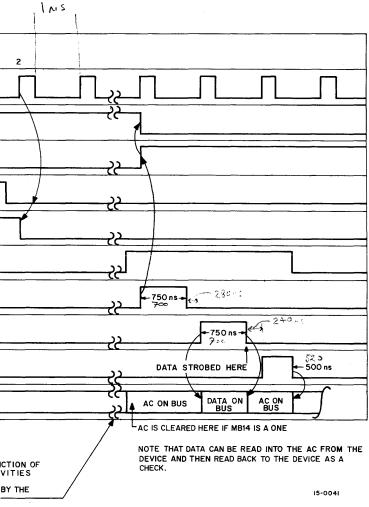

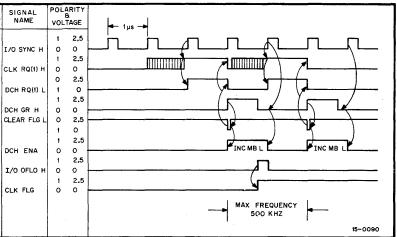

| 4-4   | Timing Diagram of the CPU Device with API             | 4-7   |

| 4-5   | Block Diagram for Multicycle Data Channel Device      | 4-9   |

| 4-6   | Multi-Cycle Data Channel Device Logic                 | 4-13  |

| 4-7   | Multi-Cycle Data Channel Timing                       | 4-13  |

| 4-8   | Block Diagram for Increment Memory                    | 4-15  |

| 4-9   | Increment Memory Device Logic                         | 4-19  |

| 4-10  | Timing Diagram for Increment Memory Devices           | 4-19  |

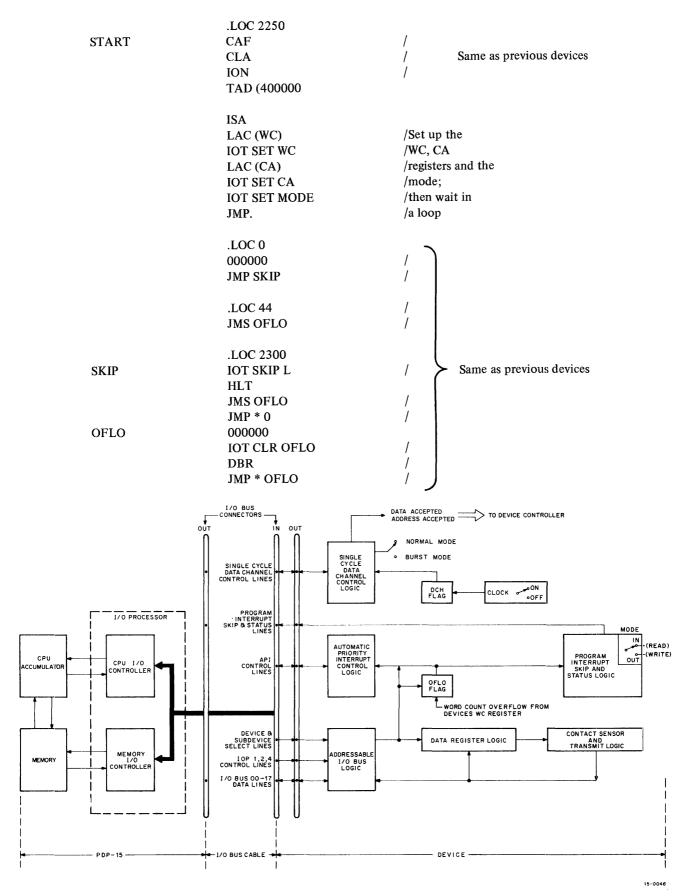

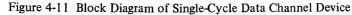

| 4-11  | Block Diagram of Single-Cycle Data Channel Device     | 4-22  |

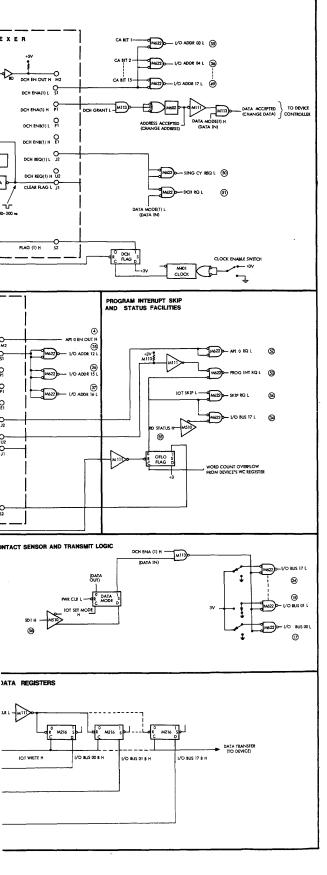

| 4-12  | Logic Diagram of Single-Cycle Data Channel            | 4-25  |

| 4-13a | Timing Diagram for Single-Cycle Device in Normal Mode | 4-25  |

| 4-13b | Single-Cycle Asynchronous Timing                      | 4-25  |

| 5-1   | Terminating Long Wires                                | 5-2   |

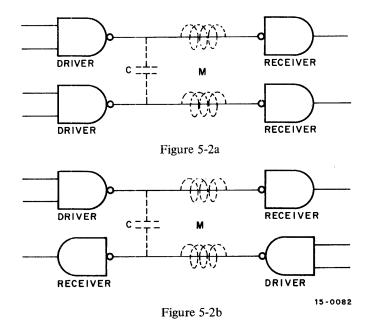

| 5-2   | Capacitance and Inductive Crosstalk Components        | 5-2   |

| 5-3   | The Ground System                                     | 5-4   |

| 5-4   | Typical Ground Mesh System                            | 5-4   |

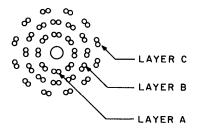

| 5-5   | Wire Distribution                                     | 5-5   |

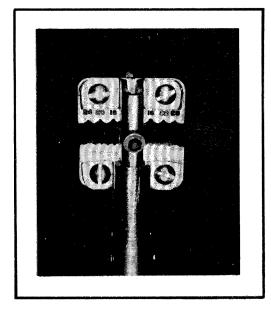

| 5-6   | Non Adjustable Wire Stripper                          | 5-7   |

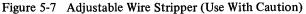

| 5-7   | Adjustable Wire Stripper (Use With Caution)           | 5-7   |

| 5-8   | Stripping Damage                                      | 5-7   |

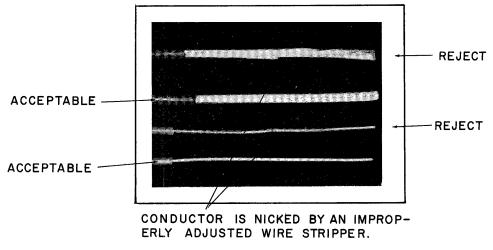

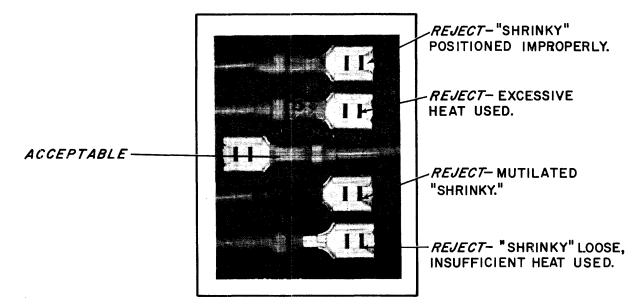

| 5-9   | Crimped Connectors                                    | 5-11  |

| 5-10  | Acceptable and Unacceptable Crimped Connections       | 5-11  |

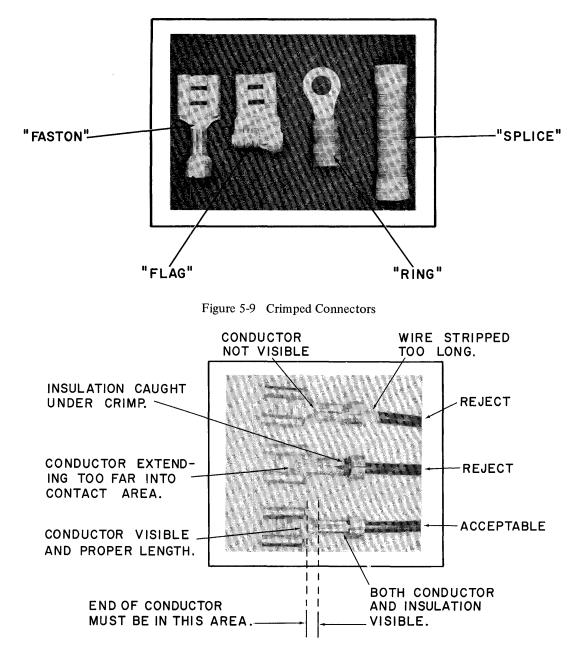

| 5-11  | Properly and Improperly Shrunk Spaghetti              | 5-12  |

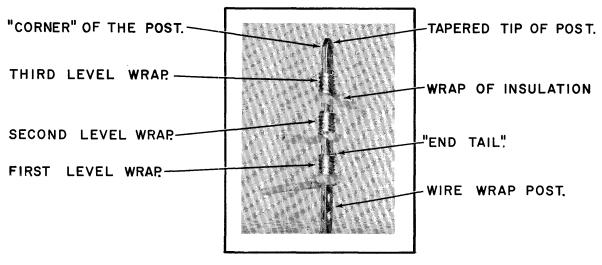

| 5-12  | Wire Wrap Terminology                                 | 5-1.3 |

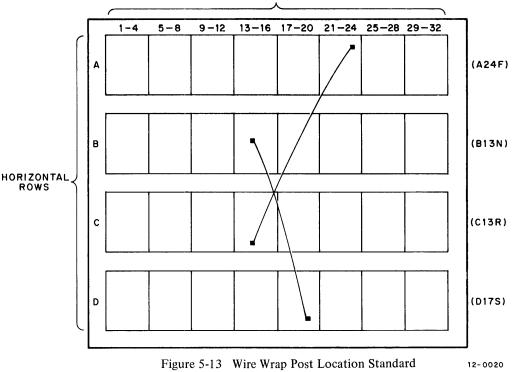

| 5-13  | Wire Wrap Post Location Standard                      | 5-15  |

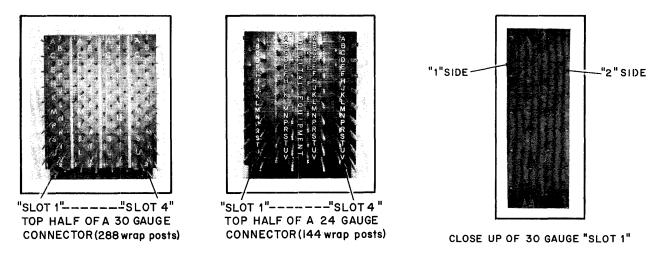

| 5-14  | Examples of 30 and 24 Gauge Connectors                | 5-16  |

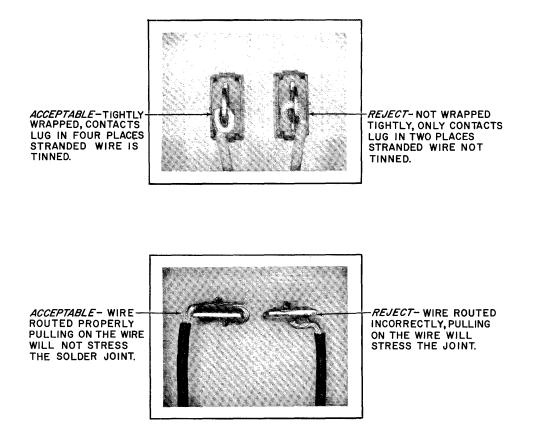

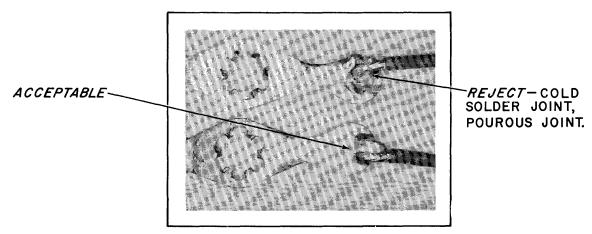

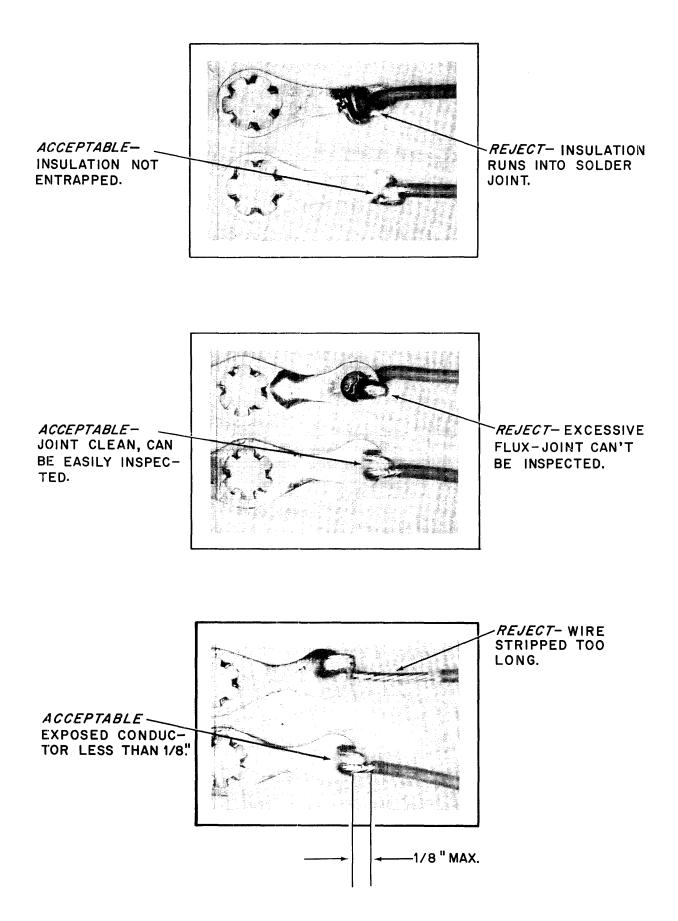

| 5-15  | Example of Wire Joint Before Soldering                | 5-17  |

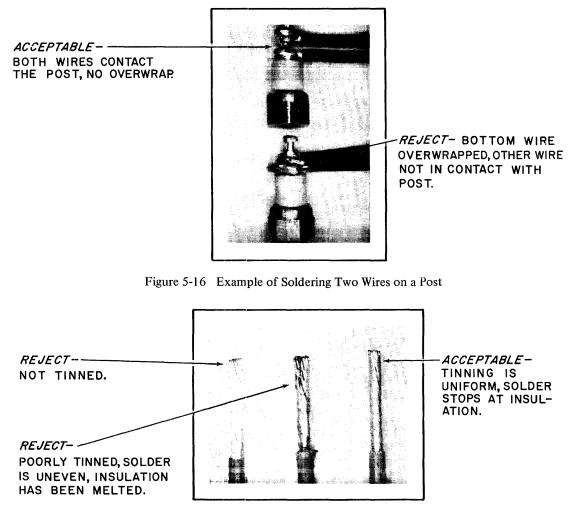

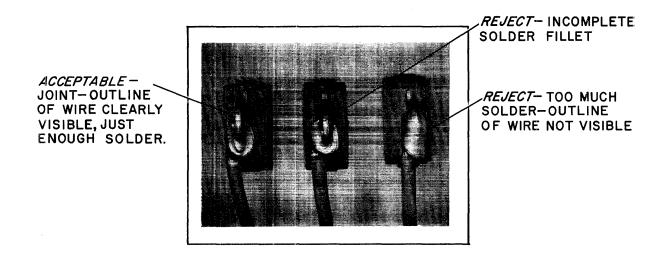

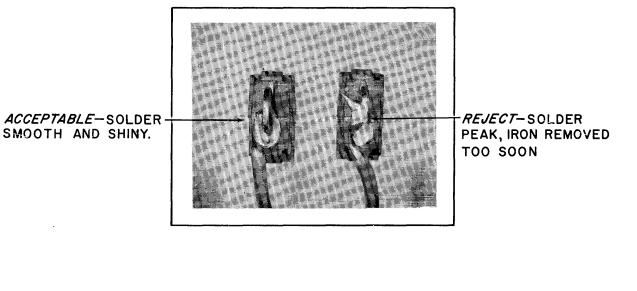

| 5-16  | Example of Soldering Two Wires on a Post              | 5-18  |

vi

#### ILLUSTRATIONS (Cont)

|      |                                                       | Page        |

|------|-------------------------------------------------------|-------------|

| 5-17 | Uses of Stranded Wire                                 | 5-18        |

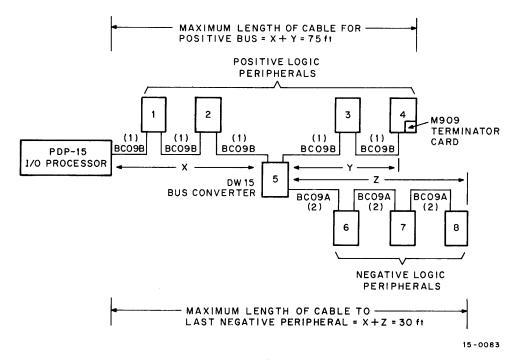

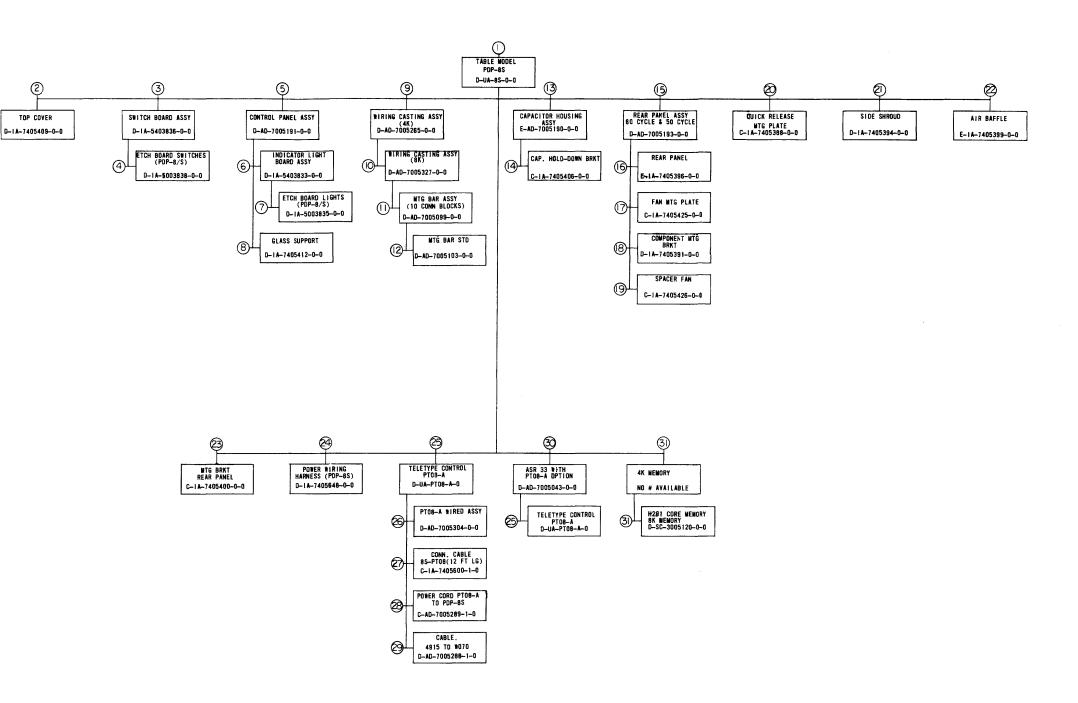

| 6-1  | The I/O Bus Cable System                              | 6-1         |

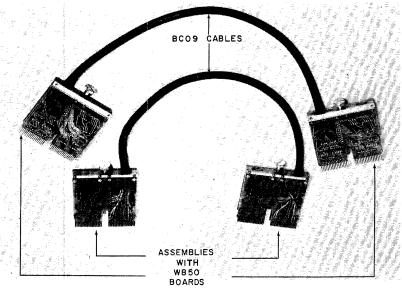

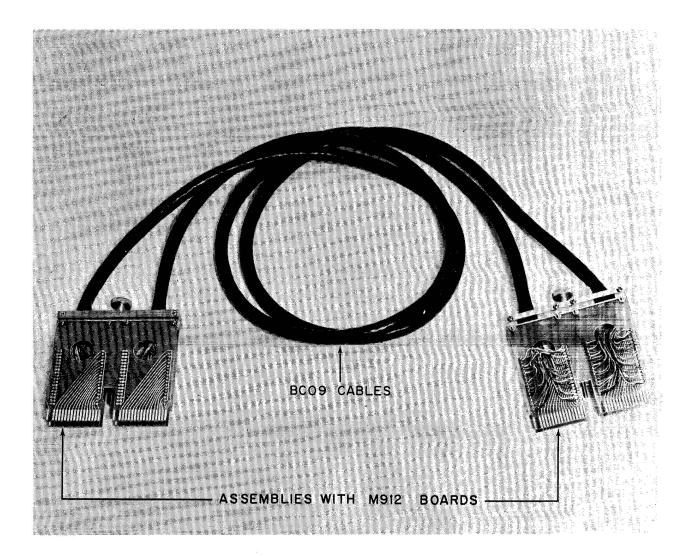

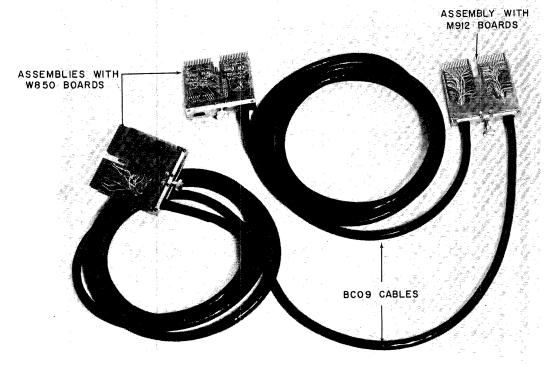

| 6-2  | BC09A Cable Assembly                                  | 6-2         |

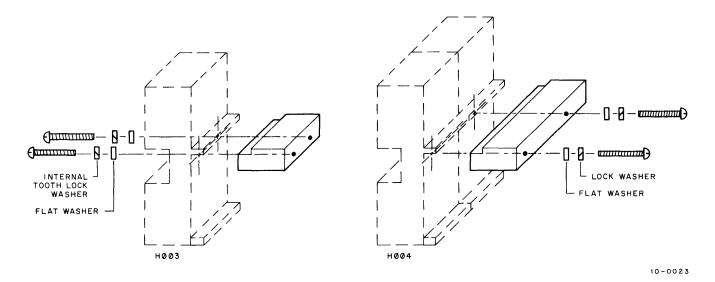

| 6-3  | Retaining Block Kits                                  | 6-3         |

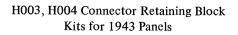

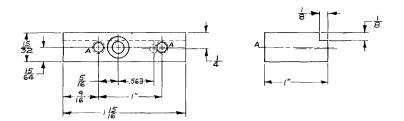

| 6-4  | I/O Connector W850                                    | 6-4         |

| 6-5  | BC09B Cable Assembly                                  | 6-5         |

| 6-6  | M912 PDP-15 I/O Bus Card                              | 6-4         |

| 6-7  | The PDP-15 I/O Bus Drive/Termination Scheme           | 6-9         |

| 6-8  | The BC09C Cable                                       | 6-10        |

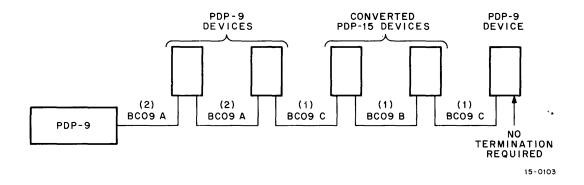

| 6-9  | Cabling Converted PDP-15 Devices to the PDP-9 I/O Bus | 6-11        |

| A-1  | Drawing Index List PDP-8/S                            | A-5         |

| A-2  | Drawing Index List PDP-8/S                            | <b>A-</b> 7 |

#### TABLES

| 3-1 | Summary of PDP-15 Input/Output Facilities                           | 3-6  |

|-----|---------------------------------------------------------------------|------|

| 4-1 | CPU Interface With API                                              | 4-6  |

| 4-2 | Multi-Cycle Data Channel Device                                     | 4-12 |

| 4-3 | Increment Memory Signals                                            | 4-18 |

| 4-4 | Single-Cycle Data Channel Interface                                 | 4-24 |

| 4-5 | Summary of I/O Bus Signal Functions                                 | 4-28 |

| 5-1 | Recommended Maximum Wiring Lengths With Single Wires                | 5-1  |

| 5-2 | Parallel Line Length Limits                                         | 5-3  |

| 5-3 | Properties of Insulation Types                                      | 5-6  |

| 5-4 | Solid and Stranded Wires                                            | 5-8  |

| 5-5 | Wire Color and Application Chart                                    | 5-10 |

| 5-6 | Wire Size, Connector Type and Tools To Use For Crimped Connections  | 5-12 |

| 5-7 | Chart of Tools, Wire Size, and Wrapping Requirements for Connectors | 5-14 |

| 6-1 | BC09 Cable Specifications                                           | 6-2  |

| 6-2 | BC09 Electrical Characteristics                                     | 6-2  |

| 6-3 | Assigned PDP-15 IOT Device Selection Codes                          | 6-7  |

| 6-4 | API Addresses                                                       | 6-8  |

| 6-5 | Data Channel Addresses                                              | 6-8  |

| 6-6 | Worst Case Latency, PDP-15 Peripherals                              | 6-9  |

| 6-7 | Worst Case Latency Figures                                          | 6-9  |

|     |                                                                     |      |

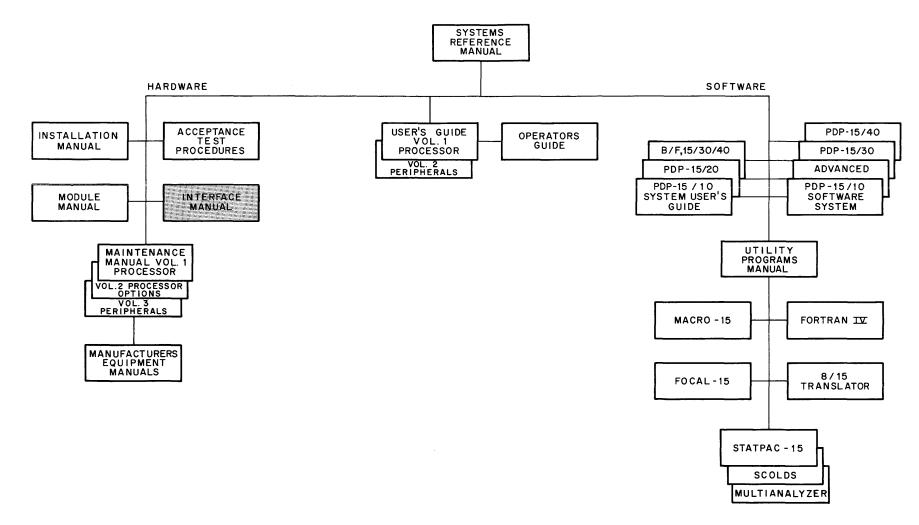

**SYSTEM REFERENCE MANUAL** – Overview of PDP-15 hardware and software systems and options, instruction repertoire, expansion features and descriptions of system peripherals. (DEC-15-GRZA-D)

**USER'S GUIDE VOLUME 1, PROCESSOR** – Principal guide to system hardware includes system and subsystem features, functional descriptions, machine-language programming considerations, instruction repertoire and system expansion data. (DEC-15-H2DA-D)

**VOLUME 2 PERIPHERALS** – Features functional descriptions and programming considerations for peripheral devices. (DEC-15-H2DA-D)

**OPERATOR'S GUIDE** – Procedural data, including operator maintenance, for using the operator's console and the peripheral devices associated with PDP-15 Systems. (DEC-15-H2CA-D)

**PDP-15/10 SYSTEM USER'S GUIDE** - COMPACT and Basic I/O Monitor operating procedures. (DEC-15-GG1A-D)

**PDP-15/20 SYSTEM USER'S GUIDE** – Advanced Monitor System operating procedures. (DEC-15-MG2A-D)

PDP-15/30 SYSTEM USER'S GUIDE - Background/Foreground Monitor System operating procedures. (DEC-15-MG3A-D)

**PDP-15/40 SYSTEM USER'S GUIDE** – Disk-oriented Background/Foreground Monitor System operating procedures. (DEC-15-MG4A-D)

**PDP-15/10 SOFTWARE SYSTEM** – COMPACT software system and Basic I/O Monitor System descriptions. (DEC-15-GR1A-D)

**PDP-15/20 ADVANCED Monitor Software System** – Advanced Monitor System descriptions; programs include system monitor and language, utility and application types; operation, core organization and input/output operations within the monitor environment are discussed. (DEC-15-MR2A-D)

**PDP-15/30 BACKGROUND/FOREGROUND Monitor Software System** – Background/Foreground Monitor description including the associated language, utility and applications programs. (DEC-15-MR3A-D) PDP-15/40 Disk-Oriented BACKGROUND /FOREGROUND Monitor Software System - Background/Foreground Monitor in a disk oriented environment is described; programs include language, utility, and application types. (DEC-15-MR4A-D)

MAINTENANCE MANUAL VOLUME 1, PROCESSOR – Block diagram and functional theory of operation of the processor logic. Preventive and corrective maintenance data. (DEC-15-HB2A-D)

**VOLUME 2, PROCESSOR OPTIONS** – Block diagram and functional theory of operation of the processor options. Preventive and corrective maintenance data. (DEC-15-HB2A-D)

**VOLUME 3, PERIPHERALS (Set of Manuals):** – Block diagram and functional theory of operation of the peripheral devices. Preventive and corrective maintenance data. (DEC-15-HB2A-D)

**INSTALLATION MANUAL** – Power specifications, environmental considerations, cabling and other information pertinent to installing PDP-15 Systems. (DEC-15-H2AA-D)

ACCEPTANCE TEST PROCEDURES – Step by step procedures designed to insure optimum PDP-15 Systems operation.

**MODULE MANUAL** – Characteristics, specifications, timing and functional descriptions of modules used in PDP-15 Systems.

**INTERFACE MANUAL** – Information for interfacing devices to a PDP-15 System. (DEC-15-H0AA-D)

UTILITY PROGRAMS MANUAL – Utility programs common to PDP-15 Monitor systems. (DEC-15-YWZA-D)

MACRO-15 – MACRO assembly language for the PDP-15. (DEC-15-AMZA-D)

**FORTRAN IV** – PDP-15 version of the FORTRAN IV compiler language. (DEC-15-KFZA-D)

FOCAL-15 – An algebraic interactive compiler level language developed by Digital Equipment Corporation. (DEC-15-KJZA-D) PDP-15 FAMILY OF MANUALS

#### CHAPTER 1 PDP-15 LOGIC SYMBOLOGY

- The purpose of this chapter is to explain the organization of the PDP-15 logic diagrams to aid the logic designer or engineer involved in interfacing to a PDP-15 System. The following topics will be discussed:

- *a.* PDP-15 System organization

- b. Logic Symbology

- c. Designators

- *d.* Line connections

#### 1.1 PDP-15 SYSTEM ORGANIZATION

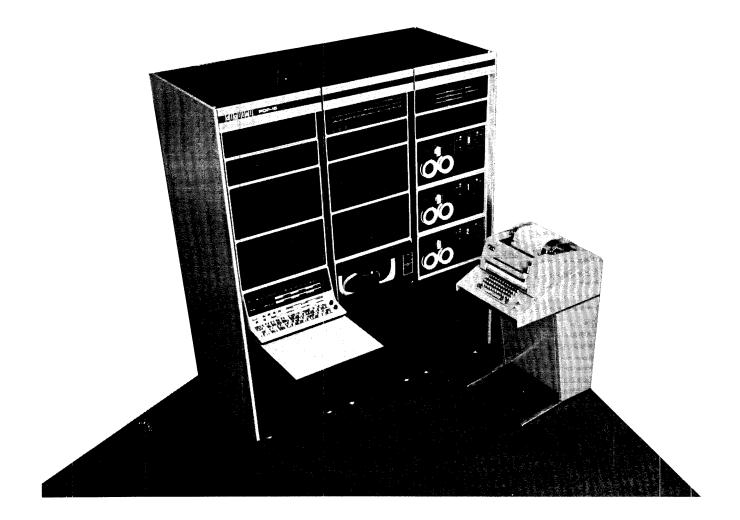

All PDP-15 systems, from the basic system (PDP-15/ 10) through the disk-oriented background/foreground system (PDP-15/40), are organized in three main sections: Central Processor (CP), Memory (Internal Storage), and Input/Output (I/O) Processor. The designations of these three sections are as follows: KP15 Central Processor, MM15 Memory, KD15 Input/Output Processor. All PDP-15 logic diagrams have been drafted utilizing a computer controlled automated drafting system (ADS), and therefore have similar characteristics. The logic diagrams flow from leftto-right wherever possible.

Each logic print has a coordinate marking system to help locate gates. The system is as follows:

- *a.* Numbers 1-8, from right to left, across the top and bottom margins.

- b. Letters A-D, from bottom to top, on left and right margins.

A label at print coordinate A-1 (lower right corner) identifies the logic diagram. The label has three parts:

a. Print name - e.g., Indicator Strobes

- b. Print size and type e.g., D-BS which means D size, Block Schematic

- Print number This is section oriented; e.g., KP15-0-25 which means Print 25 of the Central Processor section.

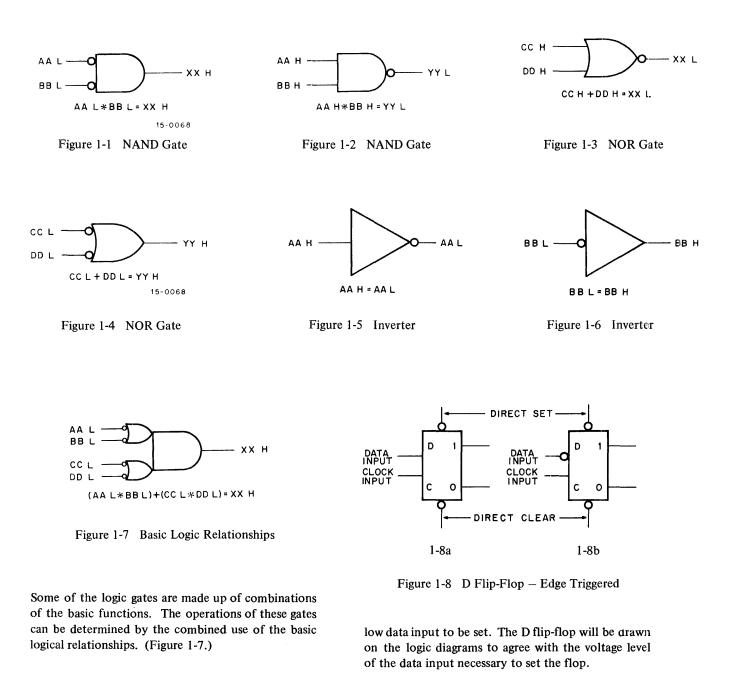

#### 1.2 LOGIC SYMBOLOGY

The logic modules utilized in the PDP-15 are primarily DEC M-series, which is the integrated circuit, positive logic series. The voltages used are:

Low (L) = 0V (0V -+0.4V) High (H) = +3V (+2.4V -+3.6V)

(For specific information on operating frequencies, loading etc., see the individual module specifications.)

The logic symbology used is MIL-STD-806B. The gating symbols use small circles at the inputs of gates to indicate that a low signal activates the function. The absence of a circle indicates that a high signal activates the function. The presence or absence of a circle at the output of a gate indicates that the output is Low (L) or High (H), respectively, when the gate has been activated (its output is true). A gate's output is false if it is at a voltage different from that shown by the gate's polarity indicator (presence or absence of circle). Suffixes L or H indicate the low or high level of a signal when it is true or enabled.

#### 1.2.1 Logic Gates

Boolean functions are symbolized as follows:

- \* Logical AND

- + Logical OR (inclusive)

- Logical negation (the vinculum is not used)

The most commonly used gating symbols are the NAND (Figures 1-1, 1-2); NOR (Figures 1-3, 1-4), and the Inverter (Figures 1-5, 1-6). Each figure shows both the symbol and a Boolean expression of the logical operation it performs.

ing figures illustrate the types of flip-flops used in the PDP-15 System.

The flip-flop in Figure 1-8a requires a high data input when clocked to set; the flip-flop in 1-8b requires a

#### 1.2.2 Flip-Flops

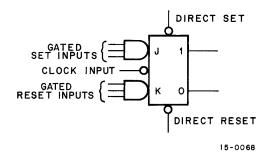

A major part of the work accomplished by the computer's logic is performed by flip-flops. The follow-

Figure 1-9 J-K Master-Slave Flip-Flop

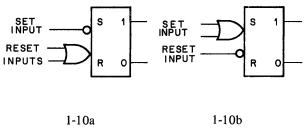

The flip-flop in Figure 1-10a can be reset by either one of two inputs; the flip-flop in Figure 1-10b has the OR gate on its set side.

Figure 1-10 R-S Flip-Flop

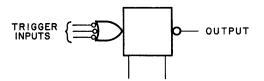

#### 1.2.4 Pulse Amplifier

A typical pulse amplifier as used in the PDP-15 is shown symbolically in Figure 1-12.

Ÿ,

Figure 1-12 Pulse Amplifier

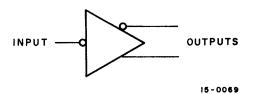

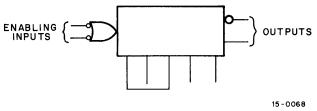

#### 1.2.5 Miscellaneous Logic Symbology

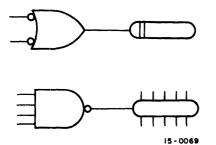

Figure 1-13 I/O Bus Receiver

#### 1.2.3 Variable Clock

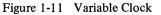

The PDP-15 uses variable clocks to generate timing signals and to control gating functions. Figure 1-11 shows a typical clock configuration.

Figure 1-14 Binary to Decimal Decoder

Figure 1-15 Delays

Figure 1-16 Connectors

#### 1.3 DESIGNATORS

The logic symbology used thus far has not shown any literal designators. The following paragraphs will describe and discuss the information that accompanies the logic symbols.

#### 1.3.1 Logic Designators

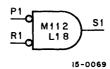

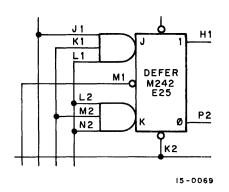

The NAND gate, Figure 1-17, contains the following information:

- a. type (M112)

- b. location in the computer (L18 of applicable section CP, I/O, or MEM)

- c. input pins on specific module (P1, R1)

- d. output pin (S1).

Figure 1-17 NAND Gate

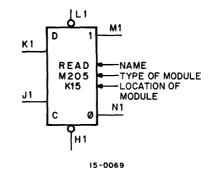

The flip-flop modules also have a name associated with them, such as READ (Figure 1-18).

Figure 1-18 Read Flip-Flop

#### 1.3.2 Signal Designators

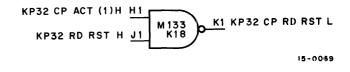

All logical expressions are broken into three parts (Figure 1-19):

a. Prefix – identifies where the signal originated (KP32 - Print 32 of the central Processor).

- b. Signal name RD RST, CP ACT.

- c. Polarity or voltage indicator (H or L). Note that in the case of flip-flops, a (1) or (0) is present to indicate the state of the flip-flop necessary for the desired voltage. For example, KP32 CP ACT (1) H is the 1 side high output of a flip-flop named CP ACT.

When a signal originating from a flip-flop is inverted through an inverter, the signal name will be changed (Figure 1-20).

Figure 1-20 Signal Name Changes

This change in name avoids possible confusion about where the signal actually originated.

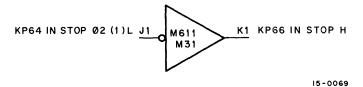

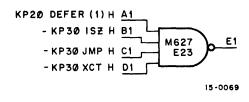

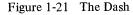

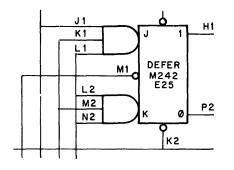

#### 1.3.4 The Dash

Logical NOT or negation is shown by a dash (-) in front of the logical expression. It is never used in front of flip-flop designators. The gate in Figure 1-21 shows negated functions. A true output from the gate is described by the following expression:

DEFER (1) \*

$$\overline{\text{ISZ}}$$

\*  $\overline{\text{JMP}}$  \*  $\overline{\text{XCT}}$

#### NOTE

The vinculum is used only for explanation purposes.

A dash (-) within a logical expression, and not in front of it, does not indicate negation; it represents the word TO and is used in expressions that perform a transfer type function. KP32 MO - MDL H would be read as MO TO MDL.

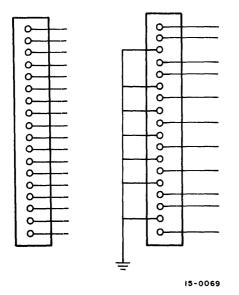

#### 1.4 LINE CONNECTIONS

The conventions used to indicate when lines merely cross over each other, and when there is an electrical connection are as follows:

a. Dotted junctions as shown below are not used.

b. Lines that merely cross each other on the logic diagram are shown as follows:

c. A junction of signal paths, or an electrical connection is indicated as follows:

Figure 1-22a shows an example from the logic prints with lines crossing and junction points. Figure 1-22b has dots drawn at the junction points to show where

junction points are, although dots are never used in the logic symbology.

Figure 1-22a

Figure 1-22b

#### CHAPTER 2 PDP-15 INTERFACE MODULES

This chapter provides descriptions of special modules used to interface the PDP-15 I/O Processor to peripheral devices, or PDP-15 devices to the PDP-9. Rules for wiring these modules together are given in Chapter 5.

DEC builds three series of compatible below-ground logic (the B-, R- and S-series), two series of compatible above-ground logic (K- and M-series), an extensive line of modules to interface different types of logic (W-series), a line of special purpose modules (G-series), and a line of support hardware for its module line (H-series).

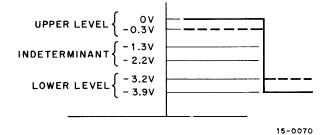

With few exceptions, the DEC below-ground logic operates with logic levels of ground to -0.3V (upper level and -3.2V to -3.9V (lower level) using diode gates which draw input current at ground and supply output current at ground. Figure 2-1 shows the voltage spectrum of negative logic systems.

Figure 2-1 Voltage Spectrum of Negative Logic Systems

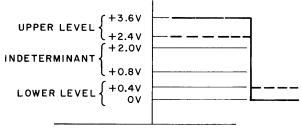

The compatible above-ground logic generally operates with levels of ground to +0.4V, (lower level) and +2.4to +3.6V (upper level) using TTL or TTL-compatible circuits whose inputs supply current at ground and whose outputs sink current at ground. Figure 2-2 shows their voltage spectrum.

15-0070

Figure 2-2 Voltage Spectrum of TTL Logic

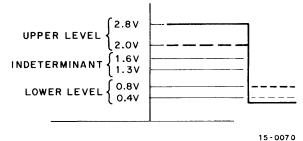

Finally, a set of special modules designed to operate on the PDP-15 I/O bus are available. Figure 2-3 indicates the voltage spectrum that they operate in.

The DIGITAL Logic Handbook, C-105, is recommended reading for those not already familiar with the basic principles of digital logic and the type of circuits used in DEC logic modules.

All modules used in the interface circuits of this manual are M-series. Several are level converters designed to match positive logic to negative logic.

#### 2.1 MEASUREMENT DEFINITIONS

Timing is measured with the input driven by a gate or pulse amplifier of the series under test and with the output loaded with gates of the same series, unless otherwise specified. Percentages are assigned as follows: 0% is the initial steady-state level, 100% is the final steady-state level, regardless of the direction of change. Input/output delay is the time difference between input change and output change, measured from 50%input change to 50% output change. Rise and fall delays for the same module usually are specified separately.

Risetime and falltime are measured from 10% to 90% of waveform change, either rising or falling.

#### 2.2 LOADING

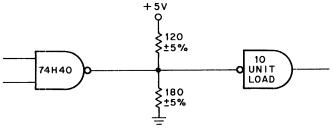

Input loading and output driving are specified in "units", where one unit is 1.6 mA by definition. The inputs to low speed gates usually draw 1 unit of load. High speed gates draw 1-1/4 units or 2 mA.

#### 2.3 MODULE DESCRIPTIONS

#### 2.3.1 M104 Multiplexer Module

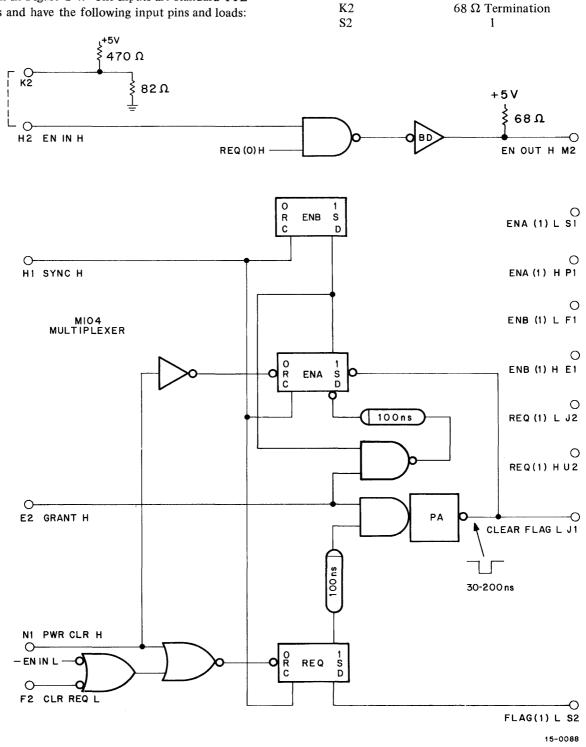

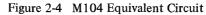

This is an M-series single-height module which contains a single multiplexer subsystem. Its equivalent circuit is shown in Figure 2-4. The inputs are standard TTL voltages and have the following input pins and loads:

**Input Pin**

H2

**S**2

H1

E2

**N**1

F2

Load (Units)

2.5

1

6

3

1

1 - 1/4

2-3

| Output Pin | #Loads it can Drive   |

|------------|-----------------------|

| U2         | 5                     |

| J2         | 8                     |

| P1         | 9                     |

| <b>S</b> 1 | 10                    |

| E1         | 10                    |

| F1         | 10                    |

| M2         | PDP-15 I/O Bus        |

|            | Compatible (30 units) |

| J1         | 7                     |

Outputs: The output gates can drive as follows:

Power: 1 Watt

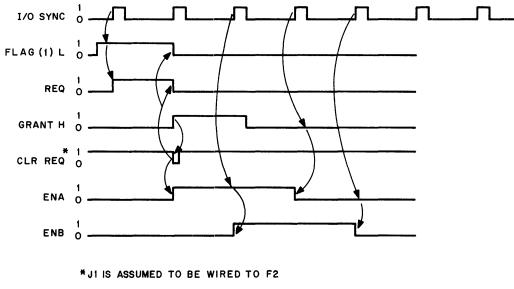

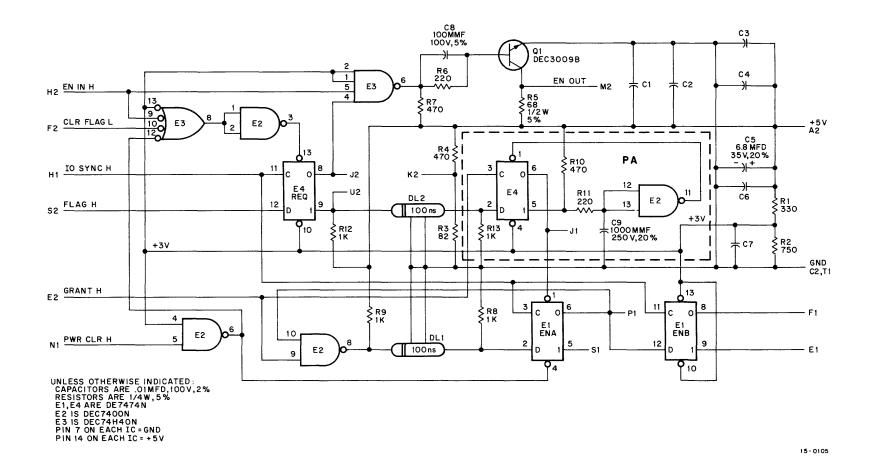

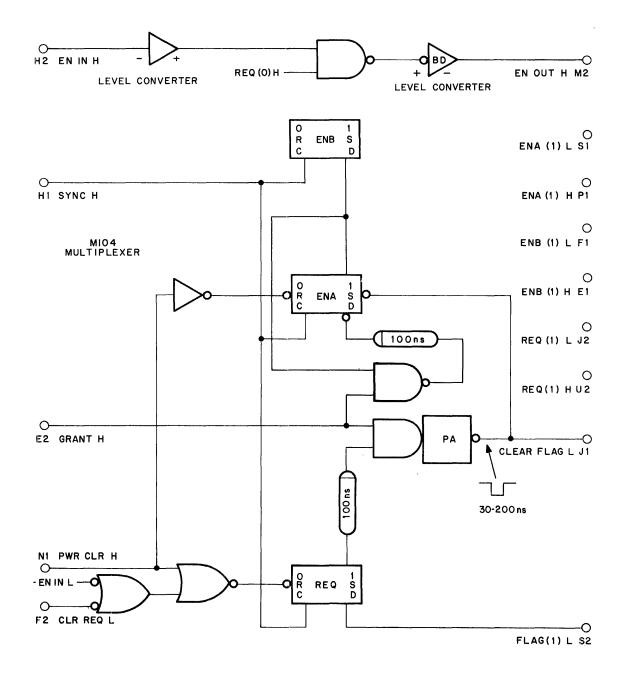

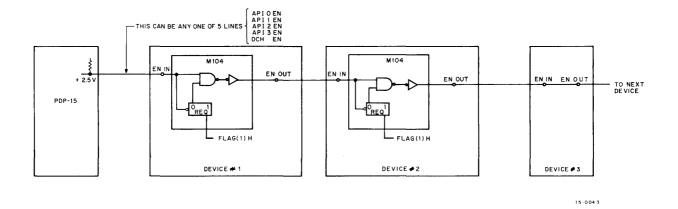

Application: The M104 module has been designed specifically for controllers of PDP-15 peripherals. It is used in all controllers which make use of the API or data channel facilities in the I/O processor. It accepts a request from the controller logic at its FLAG (1) H input and synchronizes this request to the I/O SYNC H pulses issued from the I/O processor. These pulses are fed into SYNC of the M104 and immediately set the REQ flip-flop. The REQ flip-flop can be monitored through pins J2, U2. The I/O processor responds to a request with a GRANT, and ENA is set. This flip-flop is usually used to gate any address information onto the bus; e.g., the API trap address or the word count address of the multicycle data break. Finally, the next SYNC pulse sets ENB.

The REQ flag can be reset through pin F2, called CLR RQ, by the controller logic. Pin N1 should be tied to power clear or its equivalent.

Finally, the enabling level ENABLE IN will hold REQ off if it arrives as a negative level. When REQ is set (if ENABLE IN is positive), then ENABLE OUT will go negative and the next peripheral on the bus will receive it as a negative ENABLE IN. In this way, the M104 establishes priorities among devices on the same API level or among these that use the data channel. A timing diagram is given in Figure 2-5 for the M104.

15 - 0087

Figure 2-5 M104 Timing

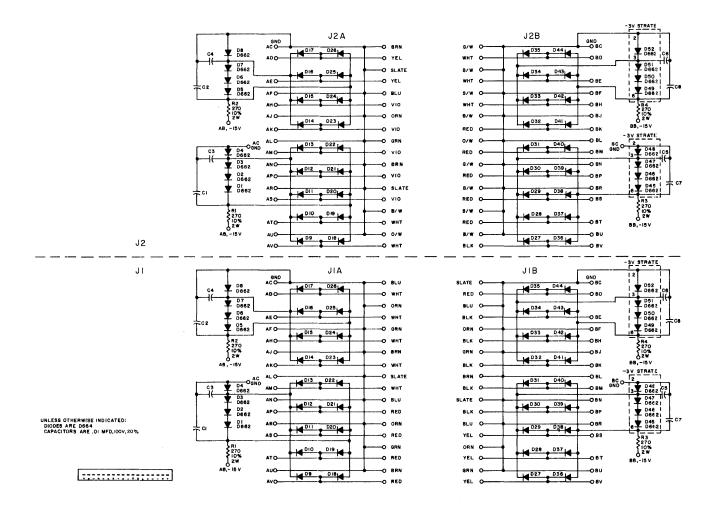

Figure 2-6 M104 Circuit Schematic

#### 2.3.2 M194 Multiplexer Module

This is an M-series single-height module which contains a single multiplexer subsystem. It is pin-compatible with the M104 module. Inputs and outputs have identical loading and driving capabilities as the M104 module with the exceptions of pins H2 and M2. Power dissipation is 1 watt. Application:

The M194 module has been designed for PDP-15 controllers which are to be used on the PDP-9. It is used for exactly the same reasons as the M104. Pins H2 and M2 are level converted from PDP-9 I/O bus levels (pin H2) to TTL, and then back to PDP-9 levels at M2. All other inputs and outputs are identical to those of the M104. Figure 2-7. shows the M194 equivalent circuit.

Figure 2-7 M194 Equivalent Circuit

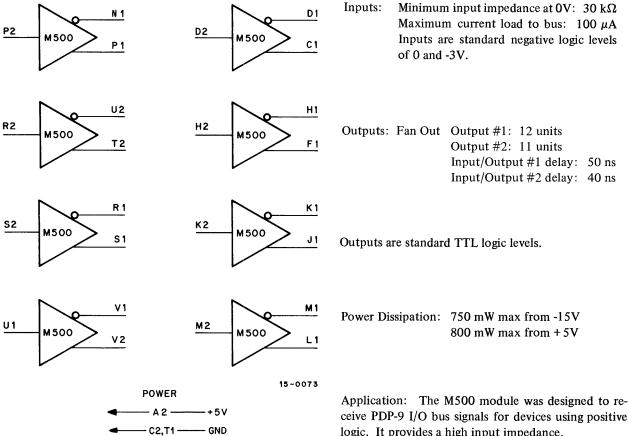

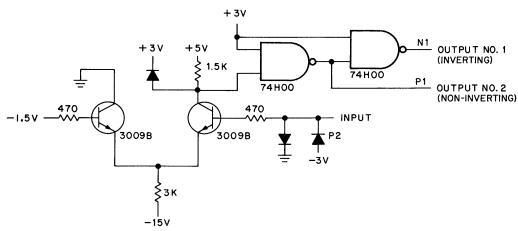

#### 2.3.3 M500 Negative Receiver Module

This is an M-series single-height module containing eight I/O bus receivers which can accept negative logic levels and convert them to positive levels.

Each M500 receiver has a negative input clamped to 0 and -3V. The threshold switching level is -1.5V with an input current of 100  $\mu$ A.

Figure 2-8 M500 Receiver Module

logic. It provides a high input impedance.

15-0074

Figure 2-9 M500 Schematic

#### 2.3.4 M510 Positive Receiver Module

The M510 module is an M-series single-height module containing eight PDP-15 I/O bus receivers.

The receiver circuit consists of a two-stage emitter follower with two TTL output buffer gates to supply both inverted and non-inverted outputs.

Inputs: Minimum input impedance: 22.5 k $\Omega$ Maximum current load to bus: 100  $\mu$ A Inputs are standard PDP-15 I/O Positive Bus levels.

Power Dissipation: 900 mW

Outputs: Fan Out Output #1: 10 units Output #2: 12 units Input/Output #1 delay maximum: 50 ns Input/Output #2 delay maximum: 60 ns Outputs are standard M-series levels.

Application: The M510 module was designed to receive PDP-15 I/O bus signals for devices using positive logic. It provides a high input impedance which yields a switching threshold between the high and low levels of the propogated signals. This feature reduces loading and noise problems.

Figure 2-11 M510 Schematic

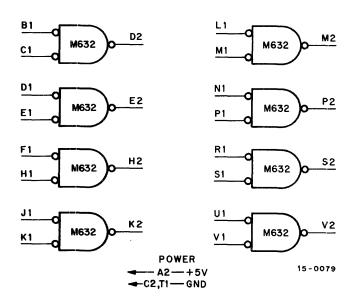

#### 2.3.5 M622 Positive Driver Module

This is an M-series single-height module containing eight positive bus drivers.

Each driver consists of an AND/OR integrated circuit gate and a discrete component open-collector driver.

Outputs: Outputs are standard PDP-15 positive I/O bus signals.

Risetime: 15 ns at the input to the cable. Current sink = 100 mA max. at  $V_{ce}$  sat=

0.4V

Falltime: 10 ns at the input to the cable. Input – Output Delay = 30 ns max

Power Dissipation: 1.05W max from +5V

Figure 2-12 M622 Driver

Inputs: Inputs are standard TTL voltages. The input load at OV is 1-1/4 units. Application: The M622 module was designed specifically to drive PDP-15 I/O bus signals for devices which use positive logic modules.

#### 2.3.6 M632 Negative Driver Module

The M632 is an M-series single-height module containing eight driver circuits. It accepts positive logic signals and converts them to negative logic levels.

Each driver consists of a TTL input gate and a negative open-collector output driver clamped to ground and - 3V.

Inputs: Standard TTL levels - input current load at 0V is 1-1/4 units.

Figure 2-14 M632 Driver Module

Outputs: Outputs are standard negative logic levels. Risetime: 15 ns Falltime: 15 ns with  $1.5k\Omega$  to -15V at output Input – Output Delay = 50 ns max Power Dissipation: 600 mW from -15V max 900 mW from + 5V max

Application: This driver is used to convert positive logic signals to negative logic levels that drive the PDP-9 negative I/O bus. It is pin-compatible with the M622.

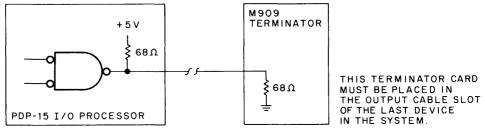

#### 2.3.7 M909 Terminator Card

This is a standard single-height M-series board with 18 terminating resistors of  $68\Omega$  each.

All resistors are 68-1/4W 5%

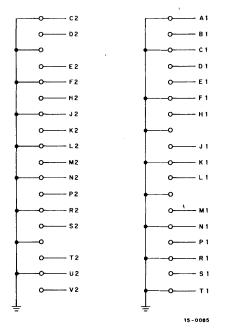

GND Pins are C2 F2 J2 L2 N2 R2 U2 A1 C1 F1 K1 N1 R1 T1

| Inputs:            | There are 18 inputs - one to each resistor. |

|--------------------|---------------------------------------------|

| Outputs:           | There are no outputs.                       |

| Power Dissipation: | 1.8W max                                    |

Application: These boards should replace the output cable of the last peripheral on the positive PDP-15 I/O bus.

Figure 2-16 M909 Terminator Card

#### 3.1 GENERAL PRINCIPLES

The input/output processor of the PDP-15 computer is designed to handle the information flow between the central processor, or its memory and a wide range of peripheral devices. The nature of these peripheral devices varies widely. Some, such as the typewriter, are very slow and require, or give up information at correspondingly slow rates. Others, such as the high speed disk, deal with data at a rate of millions of bits in a second. Although the information needs of such diverse devices vary, their information can be classified into three general categories: commands, data, and status. The nature of each will be illustrated with the following example.

The DECtape system is a low speed 10 (ten) track digital tape recording peripheral. A single central control handles up to eight tape transports. A transport can read or write digital information in either direction of tape movement in one of two modes, normal and continuous. It becomes immediately apparent that the computer must specify a number of DECtape parameters before beginning to read or write its data. These parameters include: the tape transport to be used, where on the tape, in which direction and in what mode the data is to be written. The information written is data and the result of the operation - such as the nature of any detected errors, (did it run out of tape) or special status functions - is called status. The computer commands DECtape to read or write data and report its status.

#### 3.2 DATA INFORMATION

Of the three kinds of information transfers that take

#### CHAPTER 3 INTRODUCTION TO PDP-15 INTERFACING

place in the I/O processor (commands, data and status), the command and status consist typically of one transfer each. The data transfer is usually more complex, for it involves N transfers, where N is defined by the program.

In a typical transfer of N words, the program specifies a storage (starting) address, and a count of the number of words, N, to be transferred. The storage area thus defined is referred to as a data buffer. During the transfer, the I/O processor hardware or device hardware keep track of the current address and data count until all the desired words have been transferred into the buffer. When I/O processor hardware controls the address and count, two locations in core memory are assigned to the device for this purpose. If the device is designed to manage the count and addressing it uses two of its own hardware registers. The PDP-15 has facilities for either I/O processor controlled transfers called multi cycle data breaks, or device controlled transfers called single cycle transfers.

Consider an example of an output transfer. The I/O channel takes data out of the buffer (located in core memory) in ascending sequential order and passes it on to the peripheral (e.g., a disk) in the same order. Two arithmetic operations are necessary for each transfer to the peripheral. After reading data from storage, the I/O processor (for a multi-cycle transfer) or the peripheral (for a single-cycle transfer) add a constant of +1 to the register which specifies the current address, and then add a constant of -1 to the register which specifies the word count equals zero, the transfers are stopped. (In practice, the word count register is loaded with the 2's complement of the count, and a +1 is added until overflow.)

Input transfers are similar except data is written into storage rather than read from storage.

Some peripherals which transfer data do so at such slow rates that the high speed capability of the multi cycle or single cycle data channels is unnecessary. Examples of slow devices such as this are Teletypes and oscilloscope controls. Devices in this class "farm out" their I/O arithmetic to the central processor. This delegation of responsibility slows down the execution of the main program, however, since the program now has to compete with the peripheral for the services of the arithmetic section and the core memory where the data is stored. However, the time lost is tolerable and the hardware design of the device's interface greatly simplified. Such transfers are called program controlled transfers.

#### 3.3 COMMAND AND STATUS INFORMATION

Command information, which was used to select the DECtape transport, the direction of data transfer and the required operation in our example, also occurs infrequently, one word at a time. This type of transfer is carried out by the PDP-15 in the same way as program controlled transfers. Usually, the program or operating system determines the commands, selects the device and, through the central processor, transfers its information to the device's command register for interpretation.

A status information transfer is the reverse. The device requests software intervention at the end of one of its operations, and the program reads a status word into the central processor under program control. The word is then analyzed by the program and further commands are issued.

#### 3.4 INTERRUPTS

Another type of command information referenced in our examples, but not defined, pertains to the ability of a device to request software intervention after it completes an operation and needs further direction. This is a way of interrupting the program from its normal routine, and forcing it to service the device. Again, the program is slowed down while it identifies the requesting device and services it by transferring data under program control or by initializing the data channel for a more complex transfer. In order to reduce the identification period, elaborate program interrupt (PI) and automatic priority interrupt (API) hardware schemes have been devised for the PDP-15 I/O processor. These facilities allow the most urgent requests to be serviced first and as quickly as possible. They are described in detail in the PDP-15 User's Handbook.

#### 3.5 THE PDP-15 I/O BUS SYSTEM

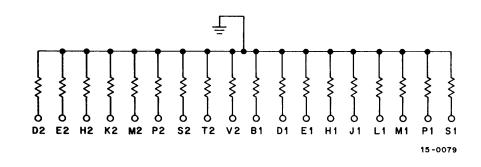

There are two types of bus systems in use on current digital computers (Figure 3-1): the radial system where each peripheral is connected to a physically separate cable or channel and the program identifies the device by a number on that channel; and the parallel system where one I/O cable goes to all peripherals. In the parallel system the cable leaves the I/O processor and is chained to each device on the channel in turn. This distributes the cable connections along the bus and therefore reduces cable congestion at the processor. There is one set of line drivers and receivers in the processor instead of one set per device.

Figure 3-1 I/O Bus Schemes

The PDP-15 uses the parallel bus system where one cable is chained from device to device. Commands (other than program interrupt or automatic priority interrupt) and status are transmitted on the same lines as data, and these lines are used for both program control and data channel transfers. Data, command and status words can be up to 18 bits.

A set of control lines accompanies the data lines to identify the activity on the lines. The control lines identify data channel transfers, program controlled transfers, status or command instructions, program interrupt or API commands or miscellaneous operations such as a pulse to clear all registers prior to set up. There are a total of 72 signals in the cable.

All devices on the I/O bus can be operated concurrently by means of a time-shared multiplexing arrangement wherein the data channel and API automatically interleave services to the various subsystems; and the operating program is designed to interleave services during program-controlled data, command or status transfers.

Essential to this multiplexing system is the idea of a device number or device address. During multi-cycle data channel or API operations, the peripheral transmits its device number to the I/O processor so that the program can address the data buffer appropriate to that device. For a transfer operation, the device number specifies the locations of the word count and current address. For an API request, this number specifies the location that the program must "trap" or jump to. During single-cycle data transfers, the device specifies the core address where it wishes to transfer the current word.

A device number is also used during program-controlled command status and data transfers. In this case, the number is selected by the program through an instruction called an IOT (input/output instruction). Each device is assigned a group of such instructions which include the device number. During the execution of the instruction, the device number is transmitted to each device. Only the correct device will decode the number and carry out the intended transfer; all other devices remain inactive. This facility is called the addressable I/O bus.

All signals on the cable, except a few, which are called ENABLE signals, are broadcast to all devices in parallel. Each device passes on the signal it receives without

amplification, and in a similar fashion all input signals are passed along, and the I/O processor sees a composite of all. Units that are not active transmit logical zeroes which do not cause interference between devices.

• The ENABLE signal is not always passed on; it is the key to the automatic multiplexing scheme used by the data channel and API. This signal is wired in series through each device. When a device receives the ENABLE signal on API or data channel it decides whether or not it wants to communicate with the I/O processor. If communication is desired it traps ENABLE, preventing the signal from passing to the next device on the chain. If no communication is desired it merely passes the signal on as it would any other outbound signal.

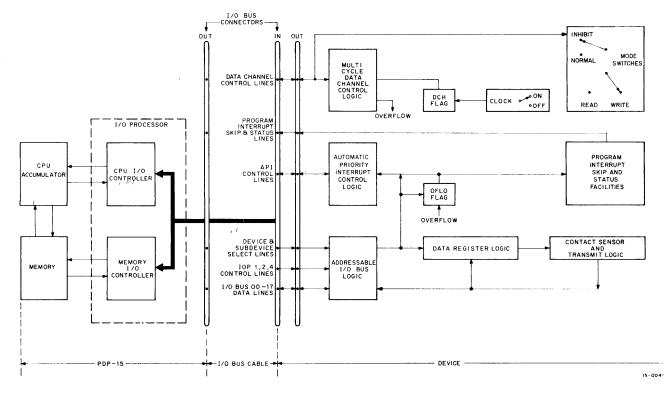

#### 3.6 SUMMARY OF THE PDP-15 I/O PROCESSOR

The PDP-15 I/O processor contains two basic subsystems; a CPU I/O controller\* and a memory I/O controller\*. The former handles all information transfers between the I/O bus and the CPU; this includes any program interrupts on PI or API, all program controlled transfers of data, command or status information and miscellaneous instructions such as CAF (clear all flags).

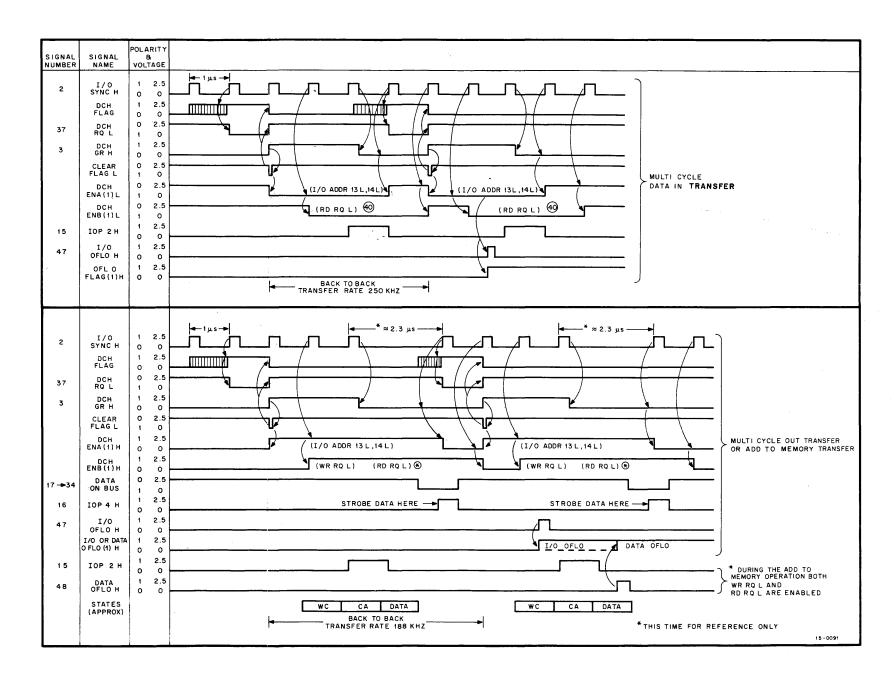

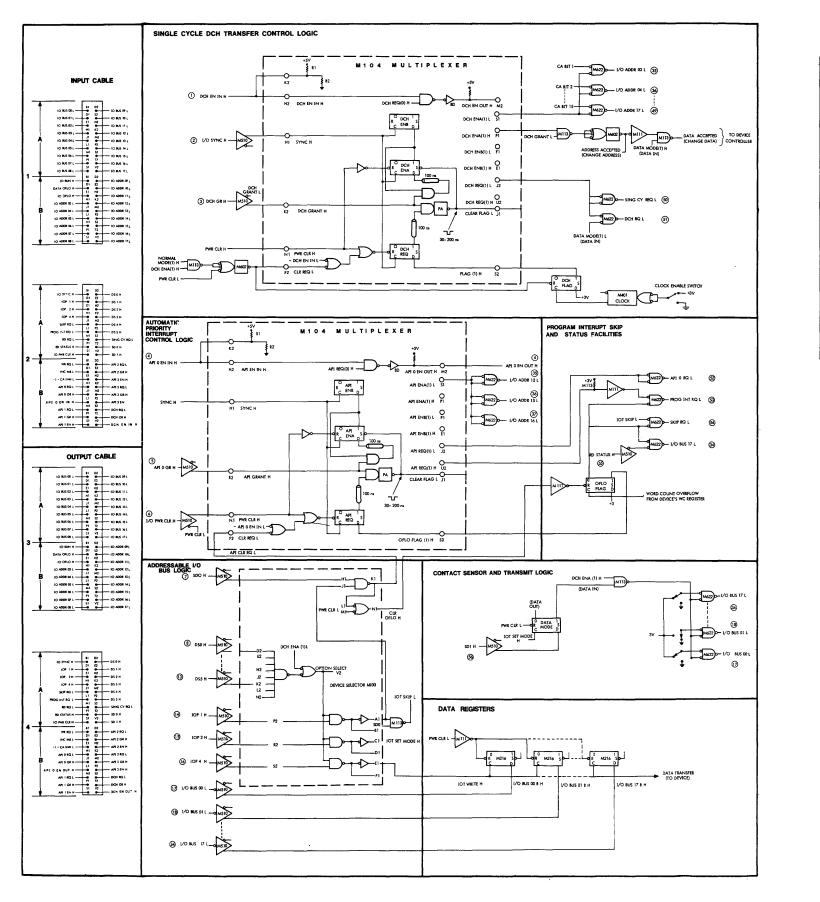

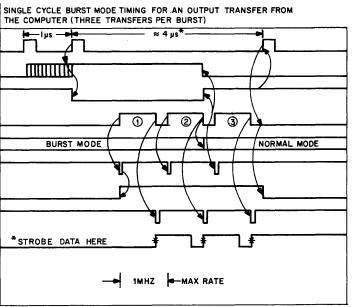

The memory I/O controller carries out the single- or multi-cycle data channel transfers of data, and includes a facility to either increment the content of a device specified location or add a number to its contents. Data in 18-bit words can move in or out of memory at speeds of 1 mHz during single-cycle transfers; 250 kHz during multi-cycle transfers.

#### 3.6.1 The CPU I/O Controller

The PDP-15 CPU I/O controller handles all control and data transfers between the central processor and devices on the I/O bus. It uses the following basic system elements:

a. An addressable I/O bus which includes the shared 18-line data path, 3 IOP control signals, eight device-code lines and a line which specifies an input transfer called RD RQ L.

<sup>\*</sup>Note that these subsystems are functional, and do not have any real physical location.

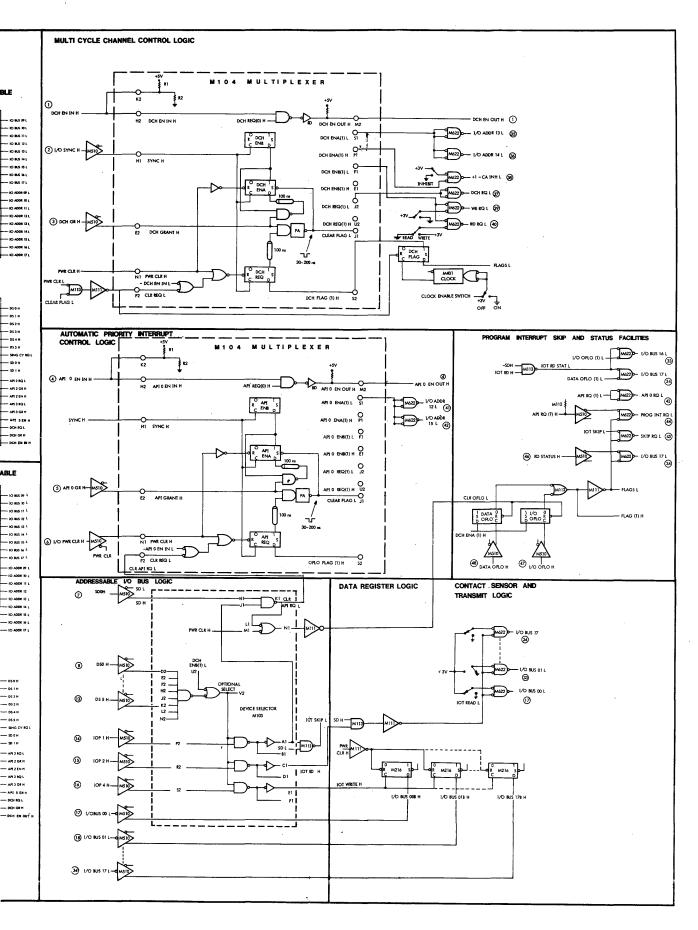

- b. A program interrupt request line (PROG INT RQ L) used by the device to request program intervention. When any device selects this line, the central processor automatically traps to location 0 of bank 0, stores away important current registers under program control and proceeds to execute the contents of location 1 of bank 0.

- c. Skip and status lines which provide a way for the computer to identify a device which causes a program interrupt. This is important since all devices share the same program interrupt line. Having trapped to location 0 on a program interrupt, the program usually jumps to a routine which issues successive IOT SKIP instructions, one for each device. The device which echoes back a pulse on its SKIP RQ L line is identified as the requesting device. The echoed pulse causes the program to skip its next instruction which usually sends the program to that device's service routine.

The status facility of the PDP-15 issues a pulse called RD STATUS H. This is used by a device to gate its status flags onto the I/O bus where they are read into the central processor. This signal can be issued by either an IORS command or by a switch on the console (see PDP-15 User's Handbook).

d. Automatic Priority Interrupt (API) Logic extends the PDP-15 program interrupt capabilities by providing interrupt servicing for as many as 28 I/O devices with minimum programming and maximum efficiency. Its priority structure permits high data-rate devices to interrupt the service routines of slower devices with a minimum of system "overhead". The option permits the device service routines to access directly from hardware-generated entry points, eliminating the need for time-consuming flag searches to identify the device that is causing the interrupt.

The option provides 32 unique channels, or entry points, for the device service routines, and 8 levels of priority. The four higher levels are for fast access to service routines in response to device-initiated service requests. Each of these levels can be multiplexed to handle up to 8 devices assigned an equal priority, up to a maximum of 28. The four lower levels are assigned to program-initiated software routines for transferring control to programs or subroutines on a priority basis. Four of the 32 channels are reserved for these software levels. Each device interfaced to the API option specifies (sends) its "trap address" or unique service routine entry point to the processor when granted an API break by the processor. Core memory locations  $40_8$  through  $77_8$  are assigned as these entry points. JMS or JMS I instructions contained in these locations provide linkage to the actual service routines.

Of the 28 hardware channels, 3 are assigned internally to the paper-tape reader, real-time clock, and optional power-failure detection system.

Each API priority takes precedence over lower API priorities, program interrupts, and the main program. The highest priority program segment interrupts lower priority program segments when activated. The data channel and real-time clock hold highest priority.

The entire API system may be enabled or disabled by a single IOT instruction.

The I/O bus contains 12 lines unique to the API; these include an API RQ L (request), an API GR H (grant) and an API EN H (enable) line for each of the four levels. Other I/O bus signals used by the API include I/O PWR CLR. H, I/O SYNC H, and I/O ADDR 12 L-I/O ADDR 17 L. The API RQ L lines are used by the device to request an interrupt from the computer at a particular priority level. The API GR is the computer's response to an API RQ L. The API EN signal indicates to a device the status of another device on that interrupt level. (There can be as many as eight devices sharing any priority level.) I/O PWR CLR H is used to establish initial conditions, I/O SYNC H is used for timing, and the I/O ADDR 12 L to I/O ADDR 17 L specify the unique entry point or trap address to a device service routine.

#### 3.6.2 The Memory I/O Controller

The PDP-15 memory I/O controller handles all control and data transfers between the internal core memory and peripheral devices. It uses the following basic elements to do this:

a. The Addressable I/O Bus which includes the shared 18-line data path, two IOP control signals (IOP 2 H and IOP 4 H) and two signals signifying the direction of a transfer; RD RQ L for a read into memory and WR RQ L for a write out of memory.

- b. The Multi-Cycle Data Channel Control Lines which include a request line – DCH RQ L; a command to the device to post its address code – DCH GR H, and an ENABLE line – DCH EN H. The multi-cycle facility will transfer data to or from memory at speeds of up to 250 kHz in 18-bit words along 18-line data paths. The control lines also include 15 address lines to specify the address in memory where the word count is stored.

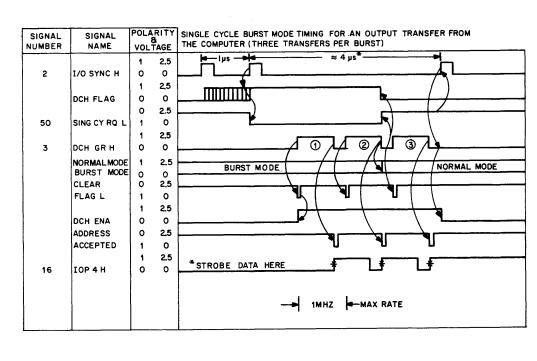

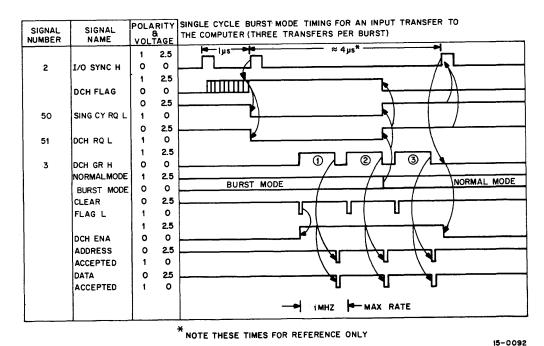

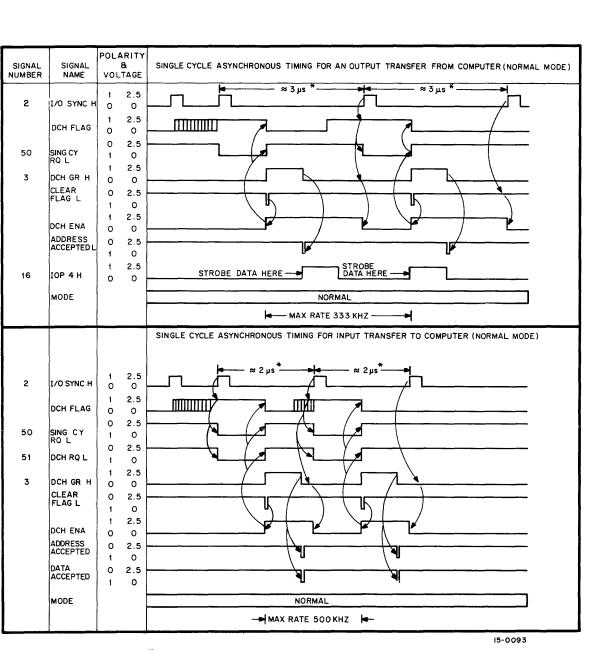

- c. The Single Cycle Data Channel Control Lines which include the control signals used by the multi-cycle data channel, plus one other to signify a single-cycle request as opposed to a multi-cycle request. This is called SING CY RQ L. A device can operate with this facility in one of two modes: burst mode or normal mode. Burst mode allows a device to carry on back to back transfers at 1 mHz in one direction only. If the device needs to either change

direction or slow down, it must drop back into normal mode which requires resynchronization at each transfer and thus has a 3 to 5  $\mu$ s latency.

- d. An Increment Memory Control Line which, when enabled, causes the I/O processor to increment the location normally specified in a multi-cycle data channel request as the word count. However, the cycle stops here. The current address is not incremented and no data is transferred. If the count overflows, the device is notified.

- e. An Add to Memory Control Line which causes the I/O processor to add the contents of the 18 data lines set up by the device on the I/O address lines to the contents of a memory location specified by the device. Both words must be of the same sign. If the sign of the sum is different, then an overflow pulse is sent to the device.

| Facility                         | Remarks                                                                                                                                                                                                                                                                                                                                                               |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                  | Data Transfers To/From Memory                                                                                                                                                                                                                                                                                                                                         |

| Multi-Cycle Data Channel Input   | Used to transfer data directly to core memory in up to 18-bit bytes at high speed (250 kHz). Cost is low but memory overhead is high.                                                                                                                                                                                                                                 |

| Multi-Cycle Data Channel Output  | Used to transfer data directly from memory in up to 18-bit bytes. Cost is low and memory overhead is high. Maximum speed is 188 kHz.                                                                                                                                                                                                                                  |

| Add to Memory                    | Used to add the contents of a device register to the con-<br>tents of a specified core location in 18-bit bytes. Good<br>for signal averaging. Maximum speed is 188 kHz.                                                                                                                                                                                              |

| Increment Memory                 | This facility allows an external device to increment the content of a core location by 1. Useful for generating histograms. Maximum speed is 500 kHz.                                                                                                                                                                                                                 |

| Single-Cycle Data Channel Output | With this facility a device can transfer a burst of data<br>from core memory at 1 mHz in 18-bit bytes. It is ex-<br>pensive to interface to and should be used for very high<br>speed devices.                                                                                                                                                                        |

| Single-Cycle Data Channel Input  | Used to transfer a burst of data from a device to core<br>memory at 1 mHz per 18-bit word. It is expensive to in-<br>terface to and should be used for very high speed devices.                                                                                                                                                                                       |

|                                  | Data Transfers To/From CPU                                                                                                                                                                                                                                                                                                                                            |

| Addressable I/O Bus              | With this facility, devices can transfer data in 18-bit bytes<br>to or from the central processor. Cost of interfacing is<br>minimal. A typical transfer rate is one transfer every<br>$200 \ \mu$ s.                                                                                                                                                                 |

|                                  | Command and Status Transfers                                                                                                                                                                                                                                                                                                                                          |

| Addressable I/O Bus              | Command and status information can be transferred to<br>or from the CPU in the same manner as ordinary data.                                                                                                                                                                                                                                                          |

| Read Status                      | This is a special facility designed to allow the user to<br>monitor all vital flags in the system. Each device is as-<br>signed a bit for its flag(s), which is read onto the address-<br>able I/O bus and into the CPU when the Read Status<br>command is given. No two devices should use the same<br>bit. See the PDP-15 User's Handbook for bit assign-<br>ments. |

| Skip                             | The addressable I/O bus allows the computer to test the status of a flag (typically) by issuing a pulse which will echo if the addressed flag is up. Every flag that posts a program interrupt must be identifiable by the skip facility.                                                                                                                             |

|                                  | Interrupts                                                                                                                                                                                                                                                                                                                                                            |

| Program Interrupt                | All devices share a common program interrupt line.<br>When a device posts an interrupt the computer is forced<br>to location 0, bank 0, and then on to a service routine<br>designed to identify the requesting device using the skip<br>facility. The process requires CPU and memory over-<br>head and takes time.                                                  |

| Automatic Priority Interrupt     | This facility reduces the time to service a requesting de-<br>vice and establishes a hierarcy among devices so that im-<br>portant interrupts can be handled quickly and without<br>interference.                                                                                                                                                                     |

Table 3-1

Summary of PDP-15 Input/Output Facilities

#### CHAPTER 4 PDP-15 INTERFACING

#### 4.1 INTERFACING TO THE CPU I/O CONTROLLER

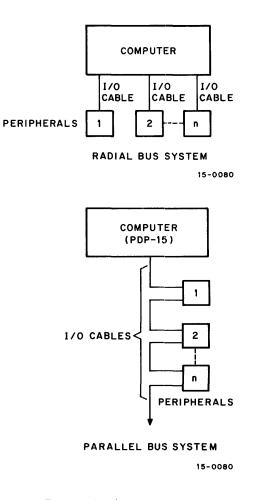

In general, devices rely on the CPU for control and status information, and on memory for high speed data. An extensive monitor system running in the CPU usually commands the operation of the entire computer complex. It can initiate a peripheral such as a disk into the correct operating mode and start it when the entire system is ready. The transfer rates for these commands are low, so that the CPU can afford to provide much of the basic control logic for such transfers, thus simplifying device logic. It does this with an instruction set called IOT instructions (Figure 4-1). Control data or status information is transferred to or from the accumulator of the CPU from the I/O processor under IOT control. The I/O processor passes the data on or off the I/O bus cable to or from the selected device.

Any device which is to interface to the I/O processor for CPU communications must satisfy the needs of four elements:

- *a*. Addressable I/O Bus

- b. Program Interrupt Facility

- c. Status and Skip Facilities

- d. Automatic Priority Interrupt System.

Although API is a system option, any device designed for the I/O bus should always contain API logic to allow for future expansion.

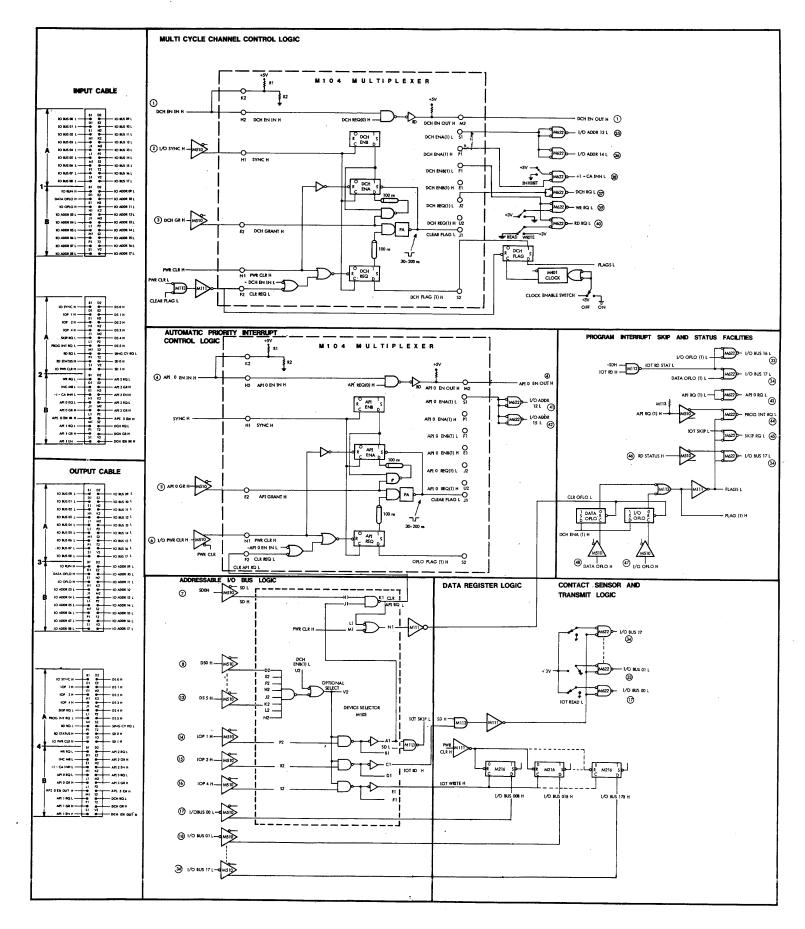

#### 4.1.1 A CPU Interface with API

As an example of an interface for a device to the CPU I/O controller, a very simple peripheral is chosen that can receive into its data buffer an 18-bit word from the accumulator of the CPU, or can transmit the states of its 18 contacts back to the accumulator (Figure 4-2).

This example has five basic components: addressable I/O bus logic, data register logic, contact sensor and transmitter logic, program interrupt skip and status logic, and API control logic.

Figure 4-1 IOT Instruction Format

a. The Addressable I/O Bus Logic – decodes the unique device and subdevice code which originates in the IOT instruction. This device can now respond to the IOP pulses 1, 2 or 4 issued by the same IOT to transfer data or cause some control function such as "skip on flag".

The addressable I/O bus logic also contains input buffers for the 18 data lines on which data is transferred.

- b. Data Register Logic This 18-bit register accepts data from the addressable I/O bus. The data is strobed off the bus with one of the IOP control pulses issued by the IOT instruction.

- c. Contact Sensor and Transmitter Logic 18 switches are sensed by the transmitter logic, and their contents can be transferred to the 18 data lines of the addressable I/O bus logic. An IOP-2 control pulse is used to strobe the data onto the bus.

- d. Program Interrupt Skip and Status Logic The device notifies the computer of its need for CPU attention by posting a program interrupt. All devices share the same program interrupt line so, to determine which device caused the signal, the CPU goes through a polling routine or "skip" chain (refer to PDP-15 User's Handbook) where it issues a skip IOT for each device. The device which echoes back

a SKIP RQ pulse to the processor is identified as the requesting device.

The status logic is used to notify the CPU of the status of each device. By issuing an IORS (read flags) instruction, the CPU can monitor the system status. IORS issues a pulse at IOP-2 time.

Each device should be designed to strobe the "OR" of all its interrupt flags onto a unique pre-assigned I/O bus line when the IORS IOT is issued. IORS is similar to a read IOT in that the data strobed onto the bus is loaded into the accumulator. Since all devices receive IORS simultaneously the I/O bus will see a composite of all device flags, and therefore the status of the entire computer system.

This status facility is useful for checking interrupts when API is not available on the system.

e. The Automatic Priority Interrupt Logic – There are four API levels assigned to peripherals on the I/O bus cable. They extend the capabilities of the program interrupt facility and save CPU time for polling. An API request at any level forces the CPU to jump or "trap" to an address specified by the device. In this way, the device is immediately identified and polling time is saved. The API logic facilitates this option for the device, provided the option is available in the I/O processor.

# 4.1.2 The Logic

Figure 4-3 shows the detailed logic of each of the blocks in Figure 4-2. The following descriptions relate directly to this diagram.

This peripheral can be programmed to either read a data word from the contact sensor switches or write a word from the accumulator into the data buffer according to the whim of its programmer. A clock is provided to post interrupts or API requests at regular intervals, to which the program can respond by issuing read or write IOT's.

This device has no known practical application. It is used here because it illustrates the logic and timing necessary to mate more complex devices to the PDP-15, yet is relatively easy to understand.

The device works in the following way:

- a. The contact sensors are set to whatever word is to be read.

- b. The programmer selects his read or write subroutine.

- c. The M401 clock is enabled.

- d. The clock sets FLAG which enables the API REQ flip-flop of the M104 Multiplexer. On the next I/O SYNC H, an API 0 RQ L and a PROG INT RQ L signal are issued simultaneously. If API is available and enabled, then the CPU will trap to memory location 44. If API is not available, then a program interrupt occurs and the CPU traps to location 00. Each of the signals used by the API control logic is listed in Table 4-1, and the timing is given in Figure 4-4.

- e. If the CPU responded to an API break, then it is programmed to jump to its appropriate read or write routine.

- f. If the CPU could only respond to a program interrupt request (because API was unavailable or disabled), it would jump to a polling routine where it would issue the IOT SKIP instruction. When this IOT selected the device and issued IOP1, then IOT SKIP would be generated and an echo pulse called SKIP RQ L would be sent back to the computer. The CPU would be forced to skip its next instruction, and the program, recognizing this device, could jump to the read or write routine.

- g. If the programmer wants to read in, then the program would issue an IOT with IOP2 selected. The IOT is decoded by the address-

able I/O bus logic and an IOT READ signal strobes the contact switches onto the data lines, I/O BUS 00L to I/O BUS 17L. It also strobes a signal called RD RQ L which tells the CPU of an IN transfer.

- h. If the programmer wants to write, then the program would issue an IOT with IOP4 selected. The IOT is again decoded and an IOT WRITE signal generated. This pulse strobes the data from the accumulator to the data register of this device.

- *i.* When a transfer has been completed, an IOT CLR FLG is issued and both API RQ and FLAG are reset.

Detailed descriptions of each signal and its timing relationships to associated signals are given in Table 4-1 and Figure 4-4. These should be studied in detail before a design is attempted.

The designer should take note of the following points:

- a. All I/O bus signals are received by an M510 module and transmitted by an M622 module with the exception of API EN IN and API EN OUT, which are handled by the M104.

- b. PROG INT RQ and API N RQ are anded together to generate PROG INT RQ. This technique gives each device the option of using API or PI but guarantees that when API is used, it will be honoured over the interrupt. If PROG INT RQ were not gated with API N RQ, then the I/O processor may see the PI request before the API since the former is asynchronous, and service it first.

- c. The logic should be designed so that if the M104 is removed from the device because its corresponding computer does not have the API option, then the PI facility will still operate. This is effected by wiring a pull up resistor of an M113 module to the input of the inverter which drives the corresponding AND gate. This forces a logical one to this gate when the M104 module is pulled.

- d. It is good practice to gate the two subdevice bits into the M103 module with the device bits, when the subdevice codes are not used. This frees up remaining codes for other devices. Note that this practice was not followed in our example.

- e. Make sure that all flags and registers are cleared by I/O PWR CLR, or the device may post

4-3

spurious interrupts during power up. If the device must be powered up while the computer system is on, then an internal power clear signal must be generated to avoid erroneous flagging.

f. Do not clear the interrupt flag(s) with the clear flag (J1) signal in the M104. Clear this flag(s) with an IOT. Otherwise the I/O processor may clear the flag before it acknowledges the request.

The following subroutine illustrates how this device can be programmed. It assumes for simplicity that the device clock is enabled, and that no other programs or devices are operating on the system. If any switch is up on the console switch register, then read operations are performed. Otherwise a write operation is carried out.

| START | .LOC 2000<br>CAF<br>CLA<br>ION<br>TAD (40000<br>ISA<br>JMP.<br>JMP START | /Clear all system flags<br>/Clear the accumulator<br>/Enable the PI<br>/Set up the API control<br>word and enable API<br>/Wait loop<br>/Return to the beginning |

|-------|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | .LOC 0<br>000000<br>JMP SKIP                                             | /PI setup<br>/Go to skip chain                                                                                                                                  |

|       | .LOC 44<br>JMS DATA                                                      | /API trap point                                                                                                                                                 |

| SKIP  | .LOC 2020<br>IOT SKIP L<br>HLT                                           | /Check the flag<br>/This flag was not<br>up. Since there are no other<br>devices operating, something<br>is wrong.                                              |

|       | JMS DATA<br>JMP * 0                                                      | /Go to service routine<br>/Go to beginning                                                                                                                      |

| DATA  | 000000<br>CLA<br>LAS<br>SZA<br>JMP READ<br>JMP WRITE                     | /Subroutine entry point<br>/Clear accumulator<br>/Load switch register<br>/Skip if AC=0<br>/Not zero, go to read<br>/Zero, go to write                          |

| READ  | CLA<br>IOT READ<br>DAC TEMP1<br>DBR<br>JMP * DATA                        | /Clear the AC<br>/Read data in<br>/Store it<br>/Debreak and restore<br>/Return                                                                                  |

| WRITE | CLA<br>LAC WORD<br>IOT WRITE<br>DBR<br>JMP * DATA                        | /Clear the AC<br>/Get the data word<br>/Write it<br>/Debreak and restore<br>/Return                                                                             |

This page intentionally left blank.

#### Table 4-1 CPU Interface With API

| Signal<br>Number | Signal<br>Mnemonic            | Input Cable<br>Pin Number | Signal Definition                                                                                                                                                                                                                                                                                                                                                                         | Signal Function                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------------|-------------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                | API 0<br>EN H<br>(IN and OUT) | 2BL1                      | This enable signal, one of four in the API system,<br>is a dc level originating in the I/O processor and<br>is daisy chained from device to device on the same<br>level. The M104 logic in each controller can<br>interrupt this level, cutting the level off all de-<br>vices that follow it on the bus. A device receives<br>it as API 0 EN IN H and transmits it as<br>API 0 EN OUT H. | Each device can post a request to its API level only<br>if the incoming API EN level is true. By posting a<br>request, the device immediately inhibits all control-<br>lers below it on the bus by removing the enable signal<br>to the next device. In this way, priorities on each<br>level are established when devices request simulta-<br>neously; the first device on this level will have high-<br>est priority, the second next priority, etc. |

| 2                | I/O SYNC H                    | 2AB1                      | The I/O processor clock pulse issued every micro-<br>second. It is a 1 mHz 250-ns pulse.                                                                                                                                                                                                                                                                                                  | This signal is used to synchronize API RQ to the I/O processor.                                                                                                                                                                                                                                                                                                                                                                                        |